Analog Devices AD9012SQ, AD9012SE, AD9012BQ, AD9012BJ, AD9012AQ Datasheet

...

REV. E

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

a

AD9012

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2001

High-Speed 8-Bit

TTL A/D Converter

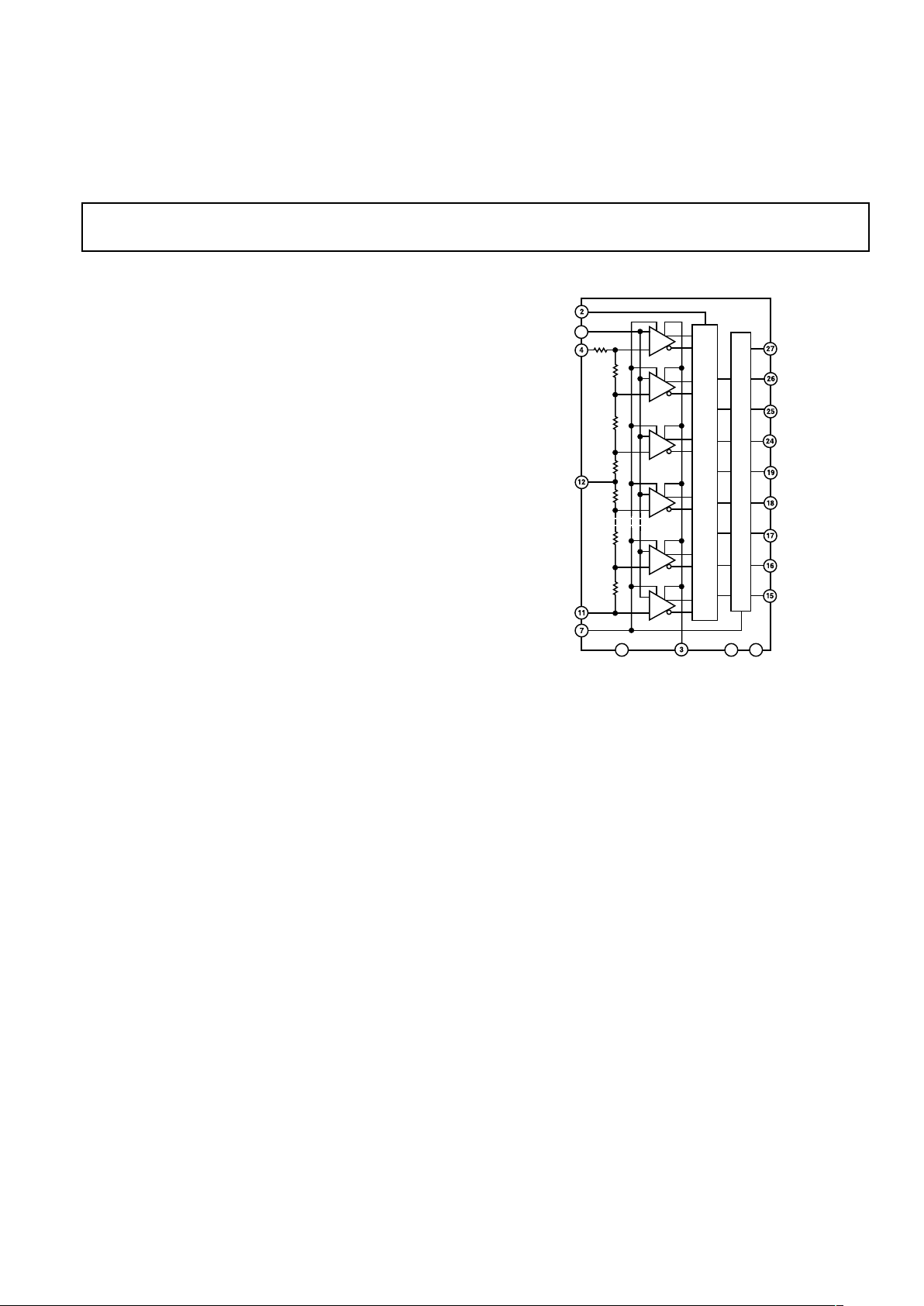

FUNCTIONAL BLOCK DIAGRAM

256

255

128

127

2

1

D

E

C

O

D

I

N

G

L

O

G

I

C

L

A

T

C

H

R

R

R

R/2

R/2

R

R

OVERFLOW

INHIBIT

ANALOG IN

ⴙV

REF

REF

MID

ⴚV

REF

ENCODE

GND HYSTERESIS

ⴚV

S

D

2

D

3

D

4

D

5

D

6

D

7

D8 (MSB)

OVERFLOW

AD9012

D1 (LSB)

ⴙV

S

FEATURES

100 MSPS Encode Rate

Very Low Input Capacitance—16 pF

Low Power—1 W

TTL Compatible Outputs

MIL-STD-883 Compliant Versions Available

APPLICATIONS

Radar Guidance

Digital Oscilloscopes/ATE Equipment

Laser/Radar Warning Receivers

Digital Radio

Electronic Warfare (ECM, ECCM, ESM)

Communication/Signal Intelligence

GENERAL DESCRIPTION

The AD9012 is an 8-bit, ultrahigh speed, analog-to-digital

converter. The AD9012 is fabricated in an advanced bipolar

process that allows operation at sampling rates up to one

hundred megasamples/second. Functionally, the AD9012 is

comprised of 256 parallel comparator stages whose outputs

are decoded to drive the TTL compatible output latches.

The exceptionally wide large-signal analog input bandwidth of

160 MHz is due to an innovative comparator design and very

close attention to device layout considerations. The wide input

bandwidth of the AD9012 allows very accurate acquisition of

high speed pulse inputs without an external track-and-hold.

The comparator output decoding scheme minimizes false codes,

which is critical to high speed linearity.

The AD9012 is available in two grades: one with 0.5 LSB

linearity and one with 0.75 LSB linearity. Both versions are

offered in an industrial grade, –25°C to +85°C, packaged in a

28-lead DIP and a 28-lead JLCC. The military temperature

range devices, –55°C to +125°C, are available in ceramic DIP

and LCC packages and are compliant to MIL-STD-883 Class B.

The AD9012 is available in versions compliant with MIL-STD-

883. Refer to the Analog Devices Military Products Databook

or current AD9012/883B data sheet for detailed specifications.

REV. E

–2–

AD9012–SPECIFICATIONS

Test AD9012AQ/AJ AD9012BQ/BJ AD9012SQ/SE AD9012TQ/TE

Parameter Temp Level Min Typ Max Min Typ Max Min Typ Max Min Typ Max Unit

RESOLUTION 8 8 8 8 Bits

DC ACCURACY

Differential Linearity 25°C I 0.6 0.75 0.4 0.5 0.6 0.75 0.4 0.5 LSB

Full VI 1.0 0.75 1.0 0.75 LSB

Integral Linearity 25°C I 0.6 1.0 0.4 0.5 0.6 1.0 0.4 0.5 LSB

Full VI 1.2 1.2 1.2 1.2 LSB

No Missing Codes Full VI GUARANTEED GUARANTEED GUARANTEED GUARANTEED

INITIAL OFFSET ERROR

Top of Reference Ladder 25°C I 7 15 7 15 7 15 7 15 mV

Full VI 18 18 18 18 mV

Bottom of Reference Ladder 25°C I 6 10 6 10 6 10 6 10 mV

Full VI 13 13 13 13 mV

Offset Drift Coefficient Full V 25 25 25 25 µV/°C

ANALOG INPUT

Input Bias Current

1

25°C I 60 200 60 200 60 200 60 200 µA

Full VI 200 200 200 200 µA

Input Resistance 25°C I 25 200 25 200 25 200 25 200 kΩ

Input Capacitance 25°C III 16 18 16 18 16 18 16 18 pF

Large Signal Bandwidth

2

25°C V 160 160 160 160 MHz

Analog Input Slew Rate

3

25°C V 440 440 440 440 V/µs

REFERENCE INPUT

Reference Ladder Resistance 25°C VI 40 80 110 40 80 110 40 80 110 40 80 110 Ω

Ladder Temperature Coefficient V 0.25 0.25 0.25 0.25 Ω/°C

Reference Input Bandwidth 25°C V 10 10 10 10 MHz

DYNAMIC PERFORMANCE

Conversion Rate 25°C I 75 100 75 100 75 100 75 100 MSPS

Aperture Delay 25°C V 3.8 3.8 3.8 3.8 ns

Aperture Uncertainty (Jitter) 25°C V 15 15 15 15 ps

Output Delay (tPD)

4, 5

25°C I 4 4.9 11 4 4.9 11 4 4.9 11 4 4.9 11 ns

Transient Response

6

25°CV 8 8 8 8 ns

Overvoltage Recovery Time725°CV 8 8 8 8 ns

Output Rise Time

4

25°C I 6.6 8.0 6.6 8.0 6.6 8.0 6.6 8.0 ns

Output Fall Time

4

25°C I 3.3 4.3 3.3 4.3 3.3 4.3 3.3 4.3 ns

Output Time Skew

4, 8

25°C V 3.0 3.0 3.0 3.0 ns

ENCODE INPUT

Logic “1” Voltage

4

Full VI 2.0 2.0 2.0 2.0 V

Logic “0” Voltage

4

Full VI 0.8 0.8 0.8 0.8 V

Logic “1” Current Full VI 250 250 250 250 µA

Logic “0” Current Full VI 400 400 400 400 µA

Input Capacitance 25°C V 2.5 2.5 2.5 2.5 pF

Encode Pulsewidth (Low)

9

25°C I 2.5 2.5 2.5 2.5 ns

Encode Pulsewidth (High)

9

25°C I 2.5 2.5 2.5 2.5 ns

OVERFLOW INHIBIT INPUT

0 V Input Current Full VI 200 250 200 250 200 250 200 250 µA

AC LINEARITY

10

Effective Bits

11

25°C V 7.5 7.5 7.5 7.5 Bits

In-Band Harmonics

dc to 1.23 MHz 25°C I 48 55 48 55 48 55 48 55 dBc

dc to 9.3 MHz 25°C V 50 50 50 50 dBc

dc to 19.3 MHz 25°C V 44 44 44 44 dBc

Signal-to-Noise Ratio

12

25°C I 46 47.6 46 47.6 46 47.6 46 47.6 dBc

Noise Power Ratio

13

25°C V 37 37 37 37 dBc

DIGITAL OUTPUT

Logic “1” Voltage Full VI 2.4 2.4 2.4 2.4 V

Logic “0” Voltage Full VI 0.4 0.4 0.4 0.4 V

POWER SUPPLY

14

Positive Supply Current (+5.0 V) 25°C I 33 45 33 45 33 45 33 45 mA

Full VI 48 48 48 48 mA

Supply Current (–5.2 V) 25°C I 152 179 152 179 152 179 152 179 mA

Full VI 191 191 191 191 mA

Nominal Power Dissipation 25°C V 955 955 955 955 mW

Reference Ladder Dissipation 25°C V 44 44 44 44 mW

Power Supply Rejection Ratio1525°C I 0.85 2.5 0.85 2.5 0.8 2.5 0.8 2.5 mV/V

ELECTRICAL CHARACTERISTICS

(+VS = +5.0 V; –VS = –5.2 V; Differential Reference Voltage = 2.0 V; unless otherwise noted.)

REV. E

–3–

AD9012

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

the AD9012 features proprietary ESD protection circuitry, permanent damage may occur on

devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are

recommended to avoid performance degradation or loss of functionality.

WARNING!

ESD SENSITIVE DEVICE

NOTES

1

Measured with Analog Input = 0 V.

2

Measured by FFT analysis where fundamental is –3 dBc.

3

Input slew rate derived from rise time (10% to 90%) of full-scale step input.

4

Outputs terminated with two equivalent ’LS00 type loads. (See load circuit.)

5

Measured from ENCODE into data out for LSB only.

6

For full-scale step input, 8-bit accuracy is attained in specified time.

7

Recovers to 8-bit accuracy in specified time, after 150% full-scale input overvoltage.

8

Output time skew includes high-to-low and low-to-high transitions as well a

s

bit-to-bit time skew differences.

9

ENCODE signal rise/fall times should be less than 30 ns for normal operation.

10

Measured at 75 MSPS encode rate. Harmonic data based on worst case harmonics.

11

Analog input frequency = 1.23 MHz.

12

RMS signal to rms noise, including harmonics with 1.23 MHz. analog input

signal.

13

NPR measured @ 0.5 MHz. Noise Source is 250 mW (rms) from 0.5 MHz

to 8 MHz.

14

Supplies should remain stable within ± 5% for normal operation.

15

Measured at –5.2 V ± 5% and +5.0 V ± 5%.

Specifications subject to change without notice.

ABSOLUTE MAXIMUM RATINGS

1

Positive Supply Voltage (+VS) . . . . . . . . . . . . . . . . . . . . . . 6 V

Analog to Digital Supply Voltage Differential (–V

S

) . . . 0.5 V

Negative Supply Voltage (–V

S

) . . . . . . . . . . . . . . . . . . . . –6 V

Analog Input Voltage . . . . . . . . . . . . . . . . . . . . –V

S

to +0.5 V

ENCODE Input Voltage . . . . . . . . . . . . . . . . . –0.5 V to +5 V

OVERFLOW INH Input Voltage . . . . . . . . . . . –5.2 V to 0 V

Reference Input Voltage (+V

REF –VREF

)2 . . . –3.5 V to +0.1 V

Differential Reference Voltage . . . . . . . . . . . . . . . . . . . . 2.1 V

Reference Midpoint Current . . . . . . . . . . . . . . . . . . . . ±4 mA

Digital Output Current . . . . . . . . . . . . . . . . . . . . . . . . 30 mA

Operating Temperature Range

AD9012AQ/BQ/AJ/BJ . . . . . . . . . . . . . . . –25°C to +85°C

AD9012SE/SQ/TE/TQ . . . . . . . . . . . . . –55°C to +125°C

Storage Temperature Range . . . . . . . . . . . –65°C to +150°C

Junction Temperature

3

. . . . . . . . . . . . . . . . . . . . . . . . 150°C

Lead Soldering Temperature (10 sec) . . . . . . . . . . . . . 300°C

NOTES

1

Absolute maximum ratings are limiting values, to be applied individually, and

beyond which the serviceability of the circuit may be impaired. Functional

operability under any of these conditions is not necessarily implied. Exposure to

absolute maximum rating conditions for extended periods may affect device

reliability.

2

+V

REF

≥ –V

REF

under all circumstances.

3

Maximum junction temperature (tJ max) should not exceed 150°C for ceramic

and plastic packages:

tJ = PD (θJA) + t

A

PD (θJC) + tc

where

PD = power dissipation

θJA = thermal impedance from junction to ambient (°C/W)

θJC = thermal impedance from junction to case (°C/W)

tA = ambient temperature (°C)

tC = case temperature (°C)

typical thermal impedances are:

Ceramic DIP θ

JA

= 42°C/W; θ

JC

= 10°C/W

Ceramic LCC θJA = 50°C/W; θJC = 15°C/W

JLCC θJA = 59°C/W; θ

JC

= 15°C/W.

Recommended Operating Conditions

Input Voltage

Parameter Min Nominal Max

–V

S

–5.46 –5.20 –4.94

+V

S

+4.75 5.00 +5.25

+V

REF

–V

REF

0.0 V +0.1

–V

REF

–2.1 –2.0 +V

REF

Analog Input –V

REF

+V

REF

V

S

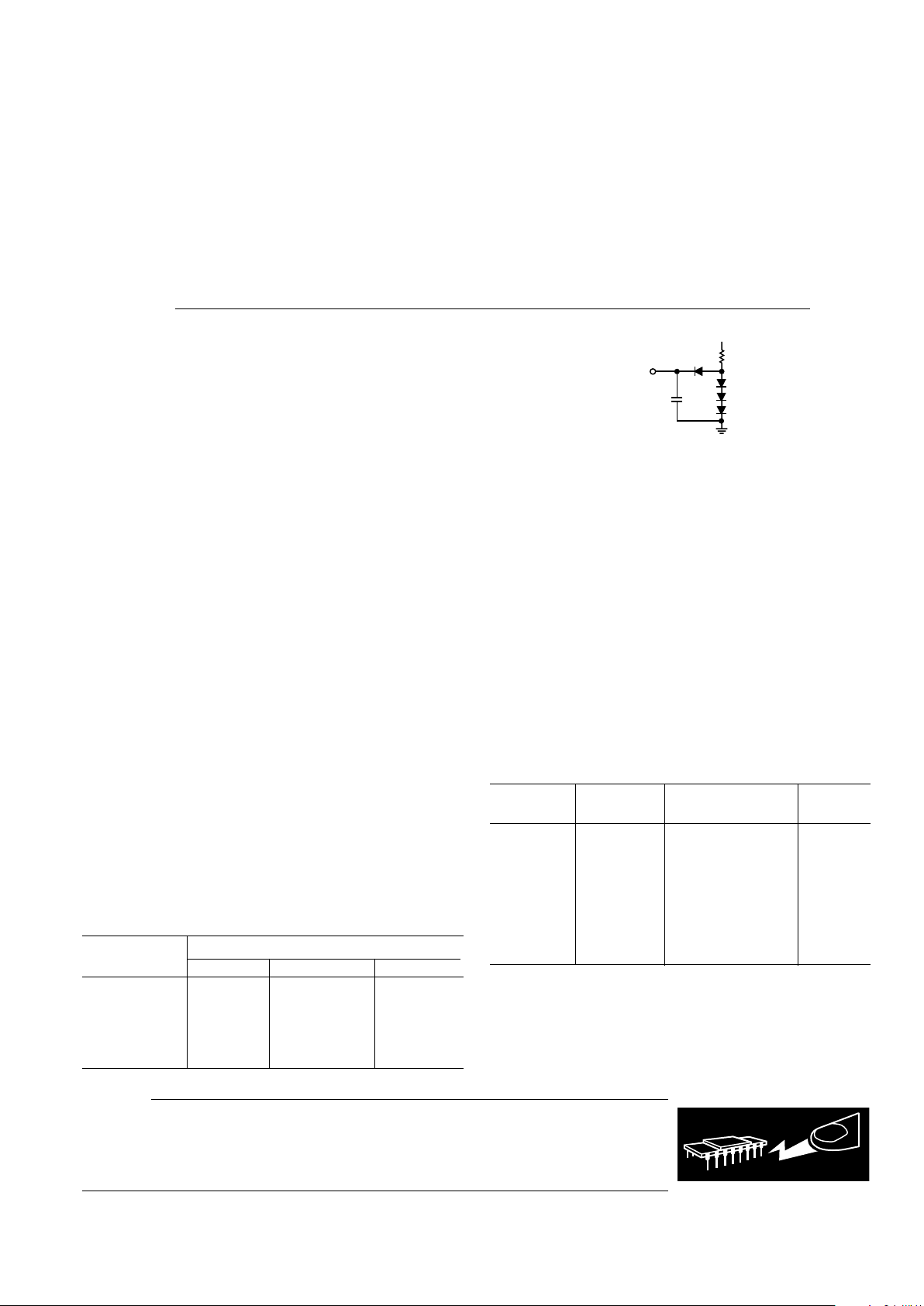

TTL

OUTPUT

15pF

1k⍀

Figure 1. Load Circuit

EXPLANATION OF TEST LEVELS

Test Level

I – 100% production tested.

II – 100% production tested at 25°C, and sample tested at

specified temperatures. AC testing done on sample basis.

III – Sample tested only.

IV – Parameter is guaranteed by design and characterization

testing.

V – Parameter is a typical value only.

VI – All devices are 100% production tested at 25°C. 100%

production tested at temperature extremes for extended

temperature devices; guaranteed by design and

characterization testing for industrial devices.

ORDERING GUIDE

Temperature Package

Device Linearity Ranges Options*

AD9012AQ 0.75 LSB –25°C to +85°C Q-28

AD9012BQ 0.50 LSB –25°C to +85°C Q-28

AD9012AJ 0.75 LSB –25°C to +85°C J-28A

AD9012BJ 0.50 LSB –25°C to +85°C J-28A

AD9012SQ 0.75 LSB –55°C to +125°C Q-28

AD9012SE 0.75 LSB –55°C to +125°C E-28A

AD9012TQ 0.50 LSB –55°C to +125°C Q-28

AD9012TE 0.50 LSB –55°C to +125°C E-28A

*E = Leadless Ceramic Chip Carrier; J = Ceramic Leaded Chip Carrier;

Q = Cerdip.

Loading...

Loading...