500 kSPS, Software Selectable True Bipolar

© 2005

Input, 2-Channel, 12-Bit Plus Sign SAR ADC

Preliminary Technical Data

FEATURES

• 12-Bit Plus Sign SAR ADC

• True Bipolar Analog Inputs

• Software Selectable Input Ranges

± 10V, ± 5V, ± 2.5V, 0 to 10V

• Two Analog Inputs with Channel Sequencer

• Single Ended, True Differential and Pseudo Differential

Capability.

• High Analog Input Impedance

• Low Power: 12 mW

• Full Power Signal Bandwidth: >7 MHz

• Internal 2.5 V Reference

• High Speed Serial Interface

• Power Down Modes

• 14-Lead TSSOP

• iCMOS

TM

Process Technology

GENERAL DESCRIPTION

The AD7321 is a 2-Channel, 12-Bit plus Sign Successive

Approximation ADC. The ADC has a high speed serial interface

that can operate at throughput rates up to 500 ksps.

The AD7321 can accept true bipolar Analog Input signals. The

AD7321 has four software selectable inputs Ranges, ±10V, ±5V,

±2.5V and 0 to 10V. Each analog input channel can be

independently programmed to one of the four input ranges.

FUNCTIONAL BLOCK DIAGRAM

Figure 1.

PRODUCT HIGHLIGHTS

1. The AD7321 can accept True Bipolar Analog Input signals,

±10V, ±5V, ±2.5V and 0 to 10V unipolar signals.

2. The Two Analog Inputs can be configured as Two SingleEnded inputs, One True Differential or One Pseudo Differential

Input. The AD7321 has high Impedance Analog Inputs.

AD7321*

The Analog input channels on the AD7321 can be programmed

to be Single-Ended, true Differential or Pseudo Differential.

The AD7321 contains a 2.5V Internal reference. The AD7321

also allows for external Reference operation. If a 3V reference is

applied the REF

±12V Analog Input. Minimum V

pin the AD7321 can accept a true Bipolar

IN/OUT

and VSS supplies of ±12V are

DD

required for the ±12V Input Range.

* Protected by U.S. Patent No. 6,731,232

TM

iCMOS

Process Technology

For analog systems designers within industrial/instrumentation equipment OEMs who need high performance ICs at higher-voltage levels, iCMOS is a technology platform

that enables the development of analog ICs capable of 30V and operating at +/- 15V supplies while allowing dramatic reductions in power consumption and package size, and

increased AC and DC performance.

Rev. PrA

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective companies.

3. High Speed Serial Interface. SPI/QSPI/DSP/MICROWIRE

Compatible. Throughput Rates up to 500 ksps can be achieved.

4. Low Power, 26 mW at maximum throughput rate of 500 ksps.

Table 1. Related Products

Device

Number

AD7328 1000 12 bit + Sign 8

AD7327 500 12 bit + Sign 8

AD7324 1000 12 bit + Sign 4

AD7323 500 12 bit + Sign 4

AD7322 1000 12 bit + Sign 2

Throughput

Rate - ksps

Number of bits Number of

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.326.8703© 2004 Analog Devices, Inc. All rights reserved.

www.analog.com

Channels

AD7321 Preliminary Technical Data

TABLE OF CONTENTS

AD7321—Specifications.................................................................. 3

Absolute Maximum Ratings............................................................ 6

Pin Functional Descriptions ....................................................... 7

Terminology ...................................................................................... 8

REVISION HISTORY

Revision PrA: Preliminary Version

Theory of Operation.....................................................................9

AD7321 Registers ........................................................................... 12

Serial interface ................................................................................ 17

OUTLINE DIMENSIONS.................................................................. 18

Rev. PrA | Page 2 of 18

AD7321 Preliminary Technical Data

AD7321—SPECIFICATIONS

Table 2. Unless otherwise noted, VDD = + 12V to +16.5V, VSS = -12V to –16.5V, VCC = 2.7V to 5.25V, V

2.5V Internal/External, f

Parameter Specification Units Test Conditions/Comments

DYNAMIC PERFORMANCE F

Signal to Noise Ratio (SNR)

Signal to Noise + Distortion (SINAD)2 75 dB min Differential Mode

71.5 dB min Single-Ended/Pseudo Differential Mode

Total Harmonic Distortion (THD)

Peak Harmonic or Spurious Noise

2

(SFDR)

Intermodulation Distortion (IMD)

Second Order Terms -88 dB typ

Third Order Terms

Aperature Delay

Aperature Jitter2

2

Common Mode Rejection (CMRR)

Channel-to-Channel Isolation

Full Power Bandwidth

DC ACCURACY

Resolution 12+Sign Bits

Integral Nonlinearity

Differential Nonlinearity

Offset Error3 ±8 LSB max Unipolar Range with Straight Binary output coding

Offset Error Match2 ±0.5 LSB max

Gain Error

Gain Error Match

2

2

Positive Full-Scale Error

Positive Full Scale Error Match

Bipolar Zero Error

2

Bipolar Zero Error Match

Negative Full Scale Error2 ±4 LSB max

Negative Full Scale Error Match

ANALOG INPUT See Table 6

Input Voltage Ranges

(Programmed via Range Register)

DC Leakage Current ±10 nA max

Input Capacitance 12 pF typ When in Track, ±10V Range

15 pF typ When in Track, ±5V, 0 to 10V Range

20 pF typ When in Track, ±2.5V Range

3 pF typ When in Hold

REFERENCE INPUT/OUTPUT

Input Voltage Range +2.5 to +3 V min to max

Input DC Leakage Current ±1 µA max

Input Capactiance 20 pF typ

Reference Output Voltage 2.49/2.51 Vmin/max

Reference Temperature Coefficient 25 ppm/°Cmax

10 ppm/°Ctyp

Reference Output Impedance 25

= 10 MHz, fS = 500 ksps TA = T

SCLK

2

2

2

2

2

2

2

2

2

2

2

1

= 2.7V to 5.25V, V

DRIVE

to T

MAX

MIN

= 50 kHz Sine Wave

IN

76 dB min Differential Mode

72 dB min Single-Ended /Pseudo Differential Mode

-80 dB max

-80

F

dB max

= 40.1 kHz, Fb = 41.5 kHz

a

-88 dB typ

10 ns max

50 ps typ

2

TBD dB typ

-80 dB typ F

7

1.5

MHz typ

MHz typ

= TBD kHz

IN

@ 3 dB

@ 0.1 dB

±1.5 LSB max

± 0.95 LSB max Guaranteed No Missing Codes to 13-Bits

±6 LSB max

±0.6 LSB max

±3 LSB max Bipolar Range with Twos Complement Output Coding

±0.6 LSB max

±8 LSB max

±0.5 LSB max

±0.5 LSB max

±10

±5

±2.5

0 to 10

V

V

V

V

Ω typ

V

= +10V min , VSS = -10V min, VCC = 2.7V to 5.25V

DD

V

= +5V min, VSS = -5V min, VCC = 2.7V to 5.25V

DD

V

= +5V min, VSS = - 5V min, VCC = 2.7V to 5.25V

DD

V

= +10V min, VSS = 0 V min, VCC = 2.7V to 5.25V

DD

REF

=

Rev. PrA | Page 3 of 18

AD7321 Preliminary Technical Data

Parameter Specification Units Test Conditions/Comments

LOGIC INPUTS

Input High Voltage, V

Input High Voltage, V

0.4 V max V

Input Current, IIN ± 1 µA max VIN = 0V or VCC

Input Capacitance, C

LOGIC OUTPUTS

Output High Voltage, VOH V

Output Low Voltage, VOL 0.4 V max I

Floating State Leakage Current ±1 µA max

Floating State Output Capacitance

Output Coding

CONVERSION RATE

Conversion Time 1.6 µs max 16 SCLK Cycles with SCLK = 10 Mhz

Track-and-Hold Acquisition Time 250 ns min Sine Wave Input

250 ns min Full Scale Step input

Throughput Rate 500 kSPS max See Serial Interface section

POWER REQUIREMENTS Digital Inputs = 0V or VCC

4

V

DD

4

V

SS

VCC +2.7V/+5.25V V min/max See Table 6

V

+2.7V/+5.25V V min/max

DRIVE

Normal Mode

IDD 300 µA max V

ISS 370 µA max V

ICC 2 mA max V

Auto-Standby Mode F

IDD TBD µA max

ISS TBD µA max

ICC 1.6 mA typ

Auto-Standby Mode F

IDD TBD µA max

ISS TBD µA max

ICC 1 mA typ

Full Shutdown Mode

IDD 0.9 µA max

ISS 0.9 µA max

ICC 0.9 µA max SCLK On or Off

POWER DISSIPATION

Normal Mode 26 mW max V

12 mW typ V

Full Shutdown Mode 35 µW max V

NOTES

1

Temperature ranges as follows: -40°C to +85°C

2

See Terminology

3

Guaranteed by Characterization

4

Functional from VDD = +4.75V and VSS = -4.75V.

Specifications subject to change without notice.

2.4 V min

INH

0.8 V max V

INL

3

IN

10 pF max

- 0.2V V min I

DRIVE

3

10 pF max

Straight

Coding bit set to 1 in Control Register

= 4.75 to 5.25 V

CC

= 2.7 to 3.6 V

CC

= 200 µA

SOURCE

= 200 µA

SINK

Natural

Binary

Two’s

Coding bit set to 0 in Control Register

Complement

+12V/+16.5V V min/max See Table 6

-12V/-16.5V V min/max See Table 6

= +16.5V

DD

= -16.5V

SS

= +5.25V

CC

= TBD

SAMPLE

= TBD

SAMPLE

= +16.5V, VSS = -16.5V, V

DD

= +5V, VSS = -5V, V

DD

= +16.5V, VSS = -16.5V, V

DD

= +5V,

CC

=+ 5.25V,

CC

= +5.25V,

CC

Rev. PrA | Page 4 of 18

AD7321 Preliminary Technical Data

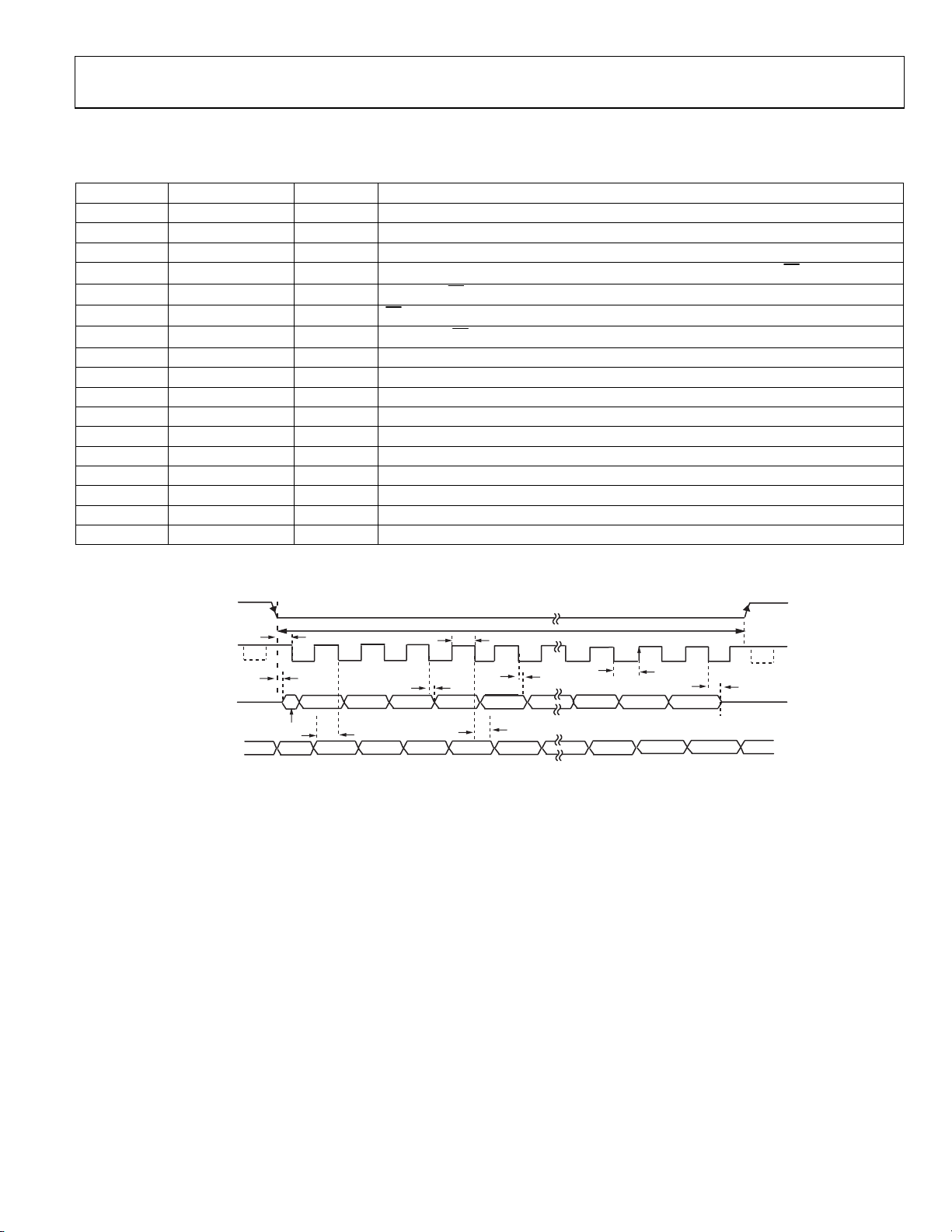

TIMING SPECIFICATIONS

Table 3. Unless otherwise noted,

2.5V Internal/External, T

Parameter Limit at T

f

SCLK

20 kHz min

10 MHz max

t

CONVERT

t

50 ns max

QUIET

16×t

t1 10 ns min

t

2

t

3

t

4

10 ns min

20 ns max

TBD ns max Data Access Time after SCLK Falling Edge.

t5 0.4t

t6 0.4t

T

7

T

8

10 ns min SCLK to Data Valid Hold Time

25 ns max SCLK Falling Edge to D

10 ns min SCLK Falling Edge to D

T

9

T

10

T

1 µs max Power up from Auto Standby

POWERUP

TBD ns min DIN set-up time prior to SCLK falling edge

5 ns min DIN hold time after SCLK falling edge

TBD µs max Power up from Full Shutdown/Auto Shutdown Mode

MIN

ns max T

SCLK

SCLK

ns min SCLK High Pulsewidth

SCLK

VDD = +12V to + 16.5V, VSS = -12V to –16.5V, V

= T

to T

MIN

Unit Description

SCLK

= 1/f

SCLK

Minimum Time between End of Serial Read and Next Falling Edge of CS

Minimum CS Pulse width

CS

to SCLK Setup Time

Delay from CS until D

ns min SCLK Low Pulsewidth

OUT

, T

A

MAX

MAX

=2.7V to 5.25, V

CC

Three-State Disabled

High Impedance

OUT

High Impedance

OUT

=2.7V to 5.25, V

DRIVE

REF

=

+5

SCLK

DOUT

DIN

t

2

3-STATE

ZERO

WRITE

1

t

3

ZERO

34

2

ADD0

ZERO

SIGN

t

9

Reg Sel LSB

MSB

t

DB11

t

convert

t

6

5

4

DB10

t

10

13

t

7

14

t

DB2

5

DB1

DONTC

15

16

t

8

DB0

3-STATE

DONTC

Figure 2. Serial Interface timing Diagram

Rev. PrA | Page 5 of 18

AD7321 Preliminary Technical Data

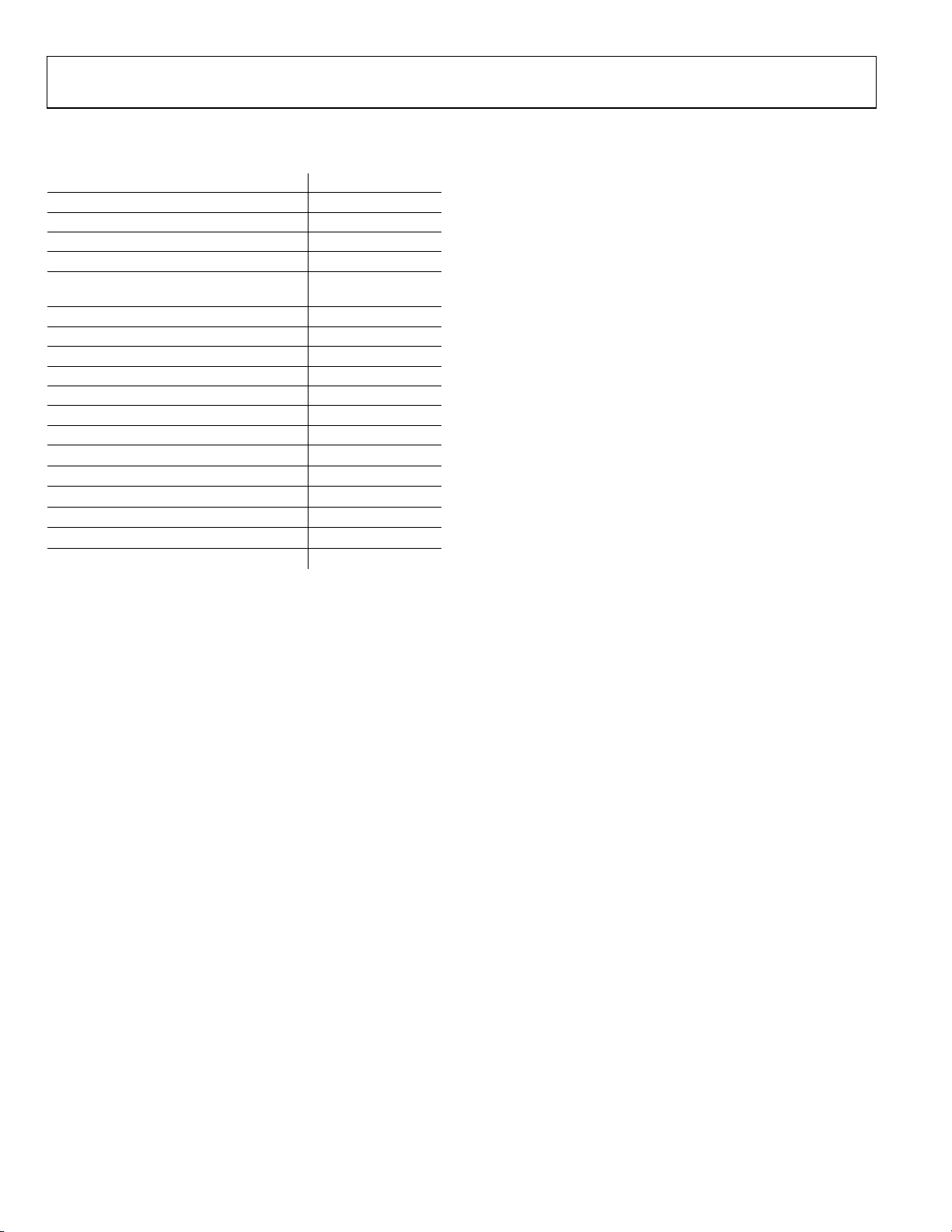

ABSOLUTE MAXIMUM RATINGS

Table 4. TA = 25°C, unless otherwise noted

VDD to AGND, DGND -0.3 V to +16.5 V

VSS to AGND, DGND +0.3 V to –16.5 V

VCC to AGND, DGND -0.3V to +7V

V

to VCC -0.3 V to VCC + 0.3V

DRIVE

AGND to DGND -0.3 V to +0.3 V

Analog Input Voltage to AGND

Digital Input Voltage to DGND -0.3 V to +7 V

Digital Output Voltage to GND -0.3 V to V

REFIN to AGND -0.3 V to VCC +0.3V

Input Current to Any Pin Except Supplies

1

Operating Temperature Range -40°C to +85°C

Storage Temperature Range -65°C to +150°C

Junction Temperature +150°C

TSSOP Package

θJA Thermal Impedance 143 °C/W

θJC Thermal Impedance 45 °C/W

Pb-free Temperature, Soldering

Reflow 260(+0)°C

ESD TBD

1

Transient currents of up to 100 mA will not cause SCR latch-up.

-0.5V to VDD +

V

SS

DRIVE

±10mA

0.5V

+0.3V

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those listed in the operational sections

of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

Rev. PrA | Page 6 of 18

Loading...

Loading...