Dual Picoampere Input

Current Bipolar Op Amp

AD706

FEATURES

High DC Precision

100 V Max Offset Voltage

1.5 V/C Max Offset Drift

200 pA Max Input Bias Current

0.5 V p-p Voltage Noise, 0.1 Hz to 10 Hz

750 A Supply Current

Available in 8-Lead Plastic Mini-DlP

and Surface-Mount (SOIC) Packages

Available in Tape and Reel in Accordance with

EIA-481A Standard

Quad Version: AD704

APPLICATIONS

Low Frequency Active Filters

Precision Instrumentation

Precision Integrators

GENERAL DESCRIPTION

The AD706 is a dual, low power, bipolar op amp that has the

low input bias current of a JFET amplifier, but which offers a

significantly lower I

drift over temperature. It utilizes superbeta

B

bipolar input transistors to achieve picoampere input bias current

levels (similar to FET input amplifiers at room temperature),

while its I

JFET amp, for which I

typically only increases by 5⫻ at 125°C (unlike a

B

doubles every 10°C for a 1000⫻

B

increase at 125°C). The AD706 also achieves the microvolt

offset voltage and low noise characteristics of a precision bipolar

input amplifier.

Since it has < 200 pA of bias current, the AD706 does not

require the commonly used “balancing” resistor. Furthermore,

the current noise is only 50 fA/√Hz, which makes this amplifier

usable with very high source impedances. At 600 A max supply

current (per amplifier), the AD706 is well suited for today’s

high density boards.

The AD706 is an excellent choice for use in low frequency

active filters in 12-bit and 14-bit data acquisition systems, in

precision instrumentation, and as a high quality integrator. The

AD706 is internally compensated for unity gain and is available

in five performance grades. The AD706J is rated over the

commercial temperature range of 0°C to +70°C. The AD706A is

rated for the extended industrial temperature range of –40°C

to +85°C.

The AD706 is offered in two varieties of an 8-lead package:

plastic mini-DIP and surface-mount (SOIC).

CONNECTION DIAGRAM

Plastic Mini-DIP (N) and

Plastic SOIC (R) Packages

AMPLIFIER 1 AMPLIFIER 2

OUTPUT

–IN

IN

1

2

3

4

AD706

TOP VIEW

8

7

6

5

V

OUTPUT

–IN

INV–

PRODUCT HIGHLIGHTS

1. The AD706 is a dual low drift op amp that offers JFET

level input bias currents, yet has the low I

drift of a bipolar

B

amplifier. It may be used in circuits using dual op amps

such as the LT1024.

2. The AD706 provides both low drift and high dc precision.

3. The AD706 can be used in applications where a chopper

amplifier would normally be required but without the

chopper’s inherent noise.

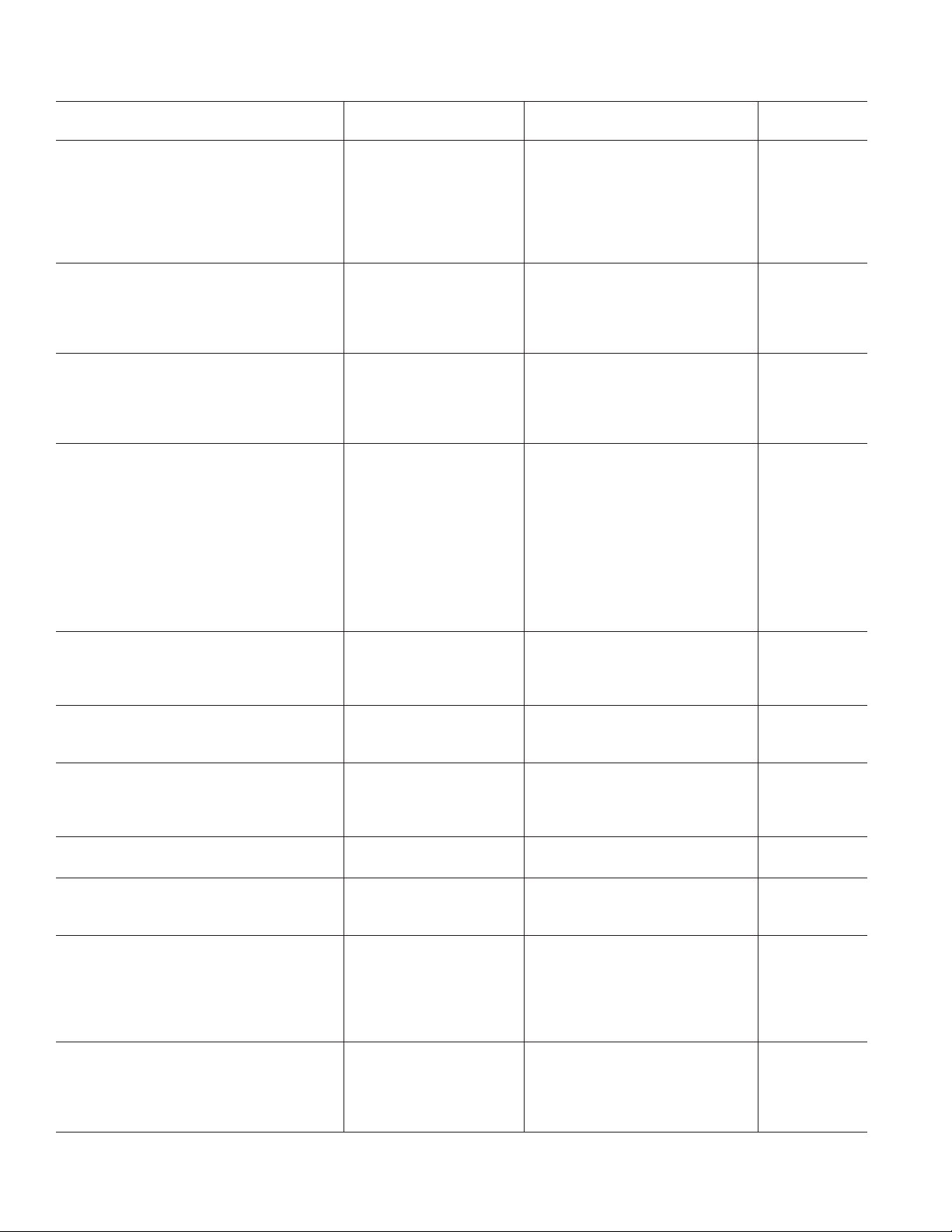

100

10

– nA

B

1

TYPICAL I

0.1

0.01

–55 +125+25 +110

TYPICAL JFET AMP

AD706

TEMPERATURE – C

Figure 1. Input Bias Current vs. Temperature

REV. E

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © 2003 Analog Devices, Inc. All rights reserved.

AD706–SPECIFICATIONS

(@ TA = +25C, VCM = 0 V and 15 V dc, unless otherwise noted.)

AD706J/A

Parameter Conditions Min Typ Max Unit

INPUT OFFSET VOLTAGE

Initial Offset 30 100 µV

Offset T

MIN

to T

MAX

40 150 µV

vs. Temperature, Average TC 0.2 1.5 µV/°C

vs. Supply (PSRR) V

to T

T

MIN

MAX

= ±2 V to ± 18 V 110 132 dB

S

VS = ±2.5 V to ± 18 V 106 126 dB

Long Term Stability 0.3 µV/Month

INPUT BIAS CURRENT

1

VCM = 0 V 50 200 pA

= ±13.5 V 250 pA

V

CM

vs. Temperature, Average TC 0.3 pA/°C

to T

T

MIN

T

MIN

to T

MAX

MAX

INPUT OFFSET CURRENT V

VCM = 0 V 300 pA

VCM = ±13.5 V 400 pA

= 0 V 30 150 pA

CM

= ±13.5 V 250 pA

V

CM

vs. Temperature, Average TC 0.6 pA/°C

to T

T

MIN

T

MIN

to T

MAX

MAX

VCM = 0 V 80 250 pA

VCM = ±13.5 V 80 350 pA

MATCHING CHARACTERISTICS

Offset Voltage 150 µV

Input Bias Current

to T

T

2

MIN

T

MIN

to T

MAX

MAX

250 µV

300 pA

500 pA

Common-Mode Rejection 106 dB

to T

T

MIN

MAX

106 dB

Power Supply Rejection 106 dB

to T

T

MIN

MAX

104 dB

Crosstalk (Figure 2a) @ f = 10 Hz

RL = 2 kΩ 150 dB

FREQUENCY RESPONSE

Unity Gain Crossover Frequency 0.8 MHz

Slew Rate G = –1 0.15 V/µs

T

MIN

to T

MAX

0.15 V/µs

INPUT IMPEDANCE

Differential 40||2 MΩ||pF

Common Mode 300||2 GΩ||pF

INPUT VOLTAGE RANGE

Common-Mode Voltage ±13.5 ±14 V

Common-Mode Rejection Ratio V

= ±13.5 V 110 132 dB

CM

T

MIN

to T

MAX

108 128 dB

INPUT CURRENT NOISE 0.1 Hz to 10 Hz 3 pA p-p

f = 10 Hz 50 fA/√Hz

INPUT VOLTAGE NOISE 0.1 Hz to 10 Hz 0.5 µV p-p

f = 10 Hz 17 nV/√Hz

f = 1 kHz 15 22 nV/√Hz

OPEN-LOOP GAIN V

= ±12 V

O

= 10 kΩ 200 2000 V/mV

R

LOAD

T

MIN

= ±10 V

V

O

R

LOAD =

T

MIN

to T

MAX

2 kΩ 200 1000 V/mV

to T

MAX

150 1500 V/mV

150 1000 V/mV

OUTPUT CHARACTERISTICS

Voltage Swing R

= 10 kΩ±13 ±14 V

LOAD

to T

T

MIN

MAX

±13 ± 14 V

Current Short Circuit ±15 mA

Capacitive Load Drive Capability Gain = +1 10,000 pF

REV. E–2–

AD706

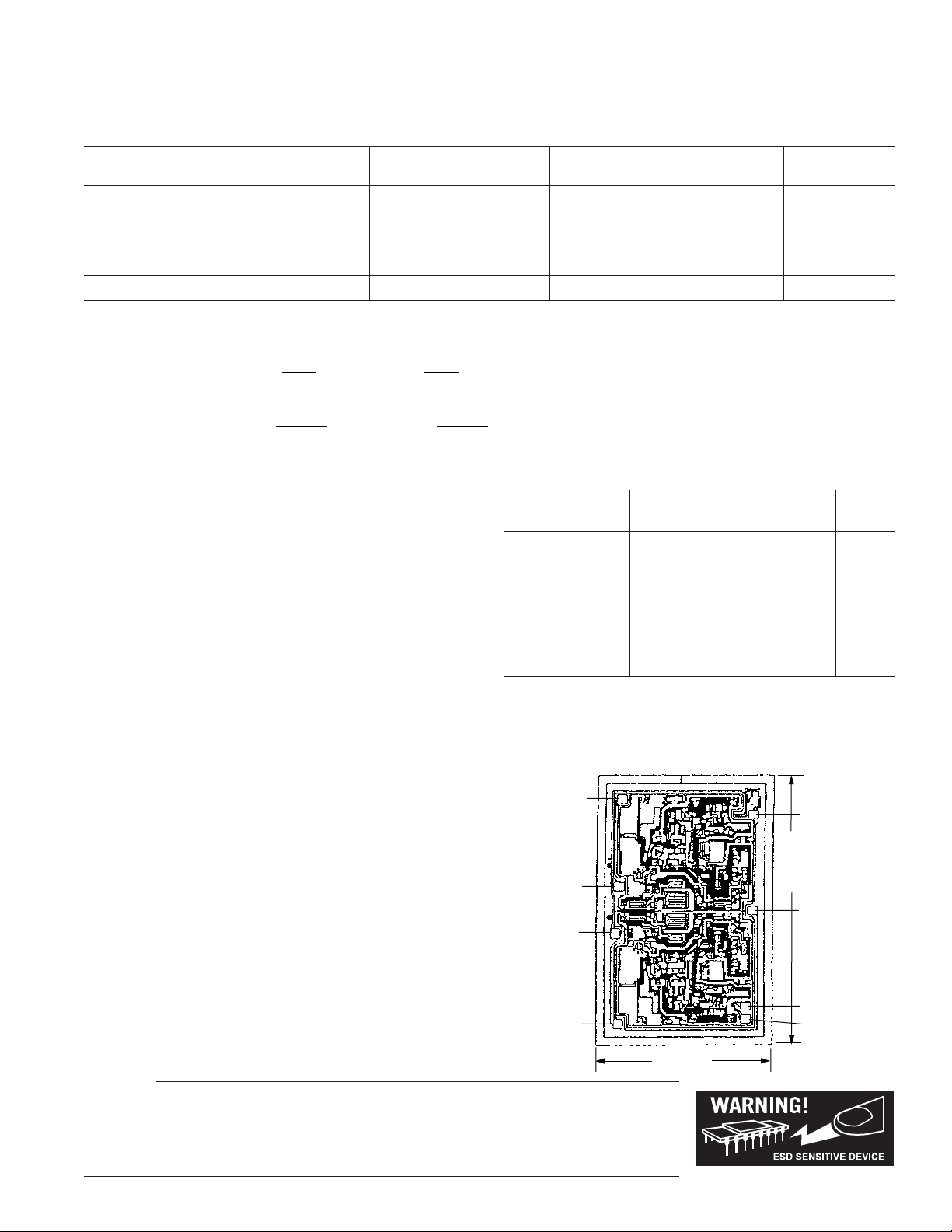

2

1

3

4

5

6

7

8

OUTPUT A

–INPUT A

+INPUT A

–V

S

0.074 (1.88)

OUTPUT B

–INPUT B

+INPUT B

0.118 (3.00)

+V

S

SPECIFICATIONS

(continued)

AD706J/A

Parameter Conditions Min Typ Max Unit

POWER SUPPLY

Rated Performance ±15 V

Operating Range ±2.0 ±18 V

Quiescent Current, Total 0.75 1.2 mA

T

MIN

to T

MAX

0.8 1.4 mA

TRANSISTOR COUNT Number of Transistors 90

NOTES

1

Bias current specifications are guaranteed maximum at either input.

2

Input bias current match is the difference between corresponding inputs (IB of –IN of Amplifier 1 minus IB of –IN of Amplifier 2).

∆∆V

CMRR match is the difference between

PSRR match is the difference between

All min and max specifications are guaranteed.

Specifications subject to change without notice.

ABSOLUTE MAXIMUM RATINGS

OS1

for Amplifier 1 and

V

CM

∆∆V

OS1

V

for Amplifier 1 and

SUPPLY

1

Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±18 V

Internal Power Dissipation

(Total: Both Amplifiers)

2

. . . . . . . . . . . . . . . . . . . . 650 mW

Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ± V

Differential Input Voltage3 . . . . . . . . . . . . . . . . . . . . . . +0.7 V

Output Short Circuit Duration . . . . . . . . . . . . . . . . Indefinite

Storage Temperature Range (N, R) . . . . . . . –65°C to +125°C

Operating Temperature Range

AD706J . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0°C to +70°C

AD706A . . . . . . . . . . . . . . . . . . . . . . . . . . . .–40°C to +85°C

Lead Temperature (Soldering 10 secs) . . . . . . . . . . . . . 300°C

NOTES

1

Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

2

Specification is for device in free air:

8-Lead Plastic Package: θJA = 100°C/W

8-Lead Small Outline Package: θJA = 155°C/W

3

The input pins of this amplifier are protected by back-to-back diodes. If the

differential voltage exceeds ± 0.7 V, external series protection resistors should be

added to limit the input current to less than 25 mA.

∆∆V

OS2

for Amplifier 2, expressed in dB.

V

CM

∆∆V

OS2

for Amplifier 2, expressed in dB.

V

SUPPLY

Model Range Description Option

AD706JN 0°C to 70°C Plastic DIP N-8

AD706JR 0°C to 70°C SOIC R-8

S

AD706JR-REEL 0°C to 70°CTape and Reel R-8

AD706JR-REEL7 0°C to 70°CTape and Reel R-8

AD706AR –40°C to +85°C SOIC R-8

AD706AR-REEL –40°C to +85°CTape and Reel R-8

AD706AR-REEL7 –40°C to +85°CTape and Reel R-8

AD706ARZ-REEL* –40°C to +85°CTape and Reel R-8

*Lead-free part.

ORDERING GUIDE

Temperature Package

METALIZATION PHOTOGRAPH

Dimensions shown in inches and (mm).

Contact factory for latest dimensions.

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although the

AD706 features proprietary ESD protection circuitry, permanent damage may occur on devices

subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended

to avoid performance degradation or loss of functionality.

REV. E

–3–

AD706–Typical Performance Characteristics

(Default Conditions: 5 V, CL = 5 pF, G = 2, Rg = Rf = 1 kΩ, RL = 2 kΩ, VO = 2 V p-p, Frequency = 1 MHz, TA = 25C)

1000

SAMPLE

SIZE: 3000

800

600

400

NUMBER OF UNITS

200

0

–80 –40 0 40 80

INPUT OFFSET VOLTAGE –

V

TPC 1. Typical Distribution

of Input Offset Voltage

V

S

–0.5

–1.0

–1.5

1.5

1.0

(REFERRED TO SUPPLY VOLTAGES)

0.5

INPUT COMMON-MODE VOLTAGE LIMIT – Volts

–V

S

0 5101520

SUPPLY VOLTAGE – Volts

TPC 4. Input Common-Mode Voltage

Range vs. Supply Voltage

1000

SAMPLE

SIZE: 5100

800

600

400

NUMBER OF UNITS

200

0

–160 –80 0 80 160

INPUT BIAS CURRENT – pA

TPC 2. Typical Distribution

of Input Bias Current

35

30

25

20

15

10

5

OUTPUT VOLTAGE – Volts p-p

0

1k 10k 1M

FREQUENCY – Hz

100k

TPC 5. Large Signal Frequency

Response

1000

SAMPLE SIZE: 2400

800

600

400

NUMBER OF UNITS

200

0

–120 –60 0 60 120

INPUT OFFSET CURRENT – pA

TPC 3. Typical Distribution

of Input Offset Current

100

SOURCE RESISTANCE

MAY BE EITHER BALANCED

10

1.0

OFFSET VOLTAGE DRIFT – V/C

0.1

OR UNBALANCED

FOR INDUSTRIAL

TEMPERATURE

RANGE

1k 10k 100M

100k 1M 10M

SOURCE RESISTANCE –

TPC 6. Offset Voltage Drift

vs. Source Resistance

200

SAMPLE SIZE: 375

–55C TO 125C

160

120

80

NUMBER OF UNITS

40

0

–0.8

–0.4 0 0.4 0.8

OFFSET VOLTAGE DRIFT – V/C

TPC 7. Typical Distribution

of Offset Voltage Drift

4

3

2

1

CHANGE IN OFFSET VOLTAGE – V

0

0

1234

WARM-UP TIME – Minutes

TPC 8. Change in Input Offset

Voltage vs. Warm-Up Time

60

40

20

0

–20

INPUT BIAS CURRENT – pA

–40

–60

5

–15

–10 –5 0 5

COMMON-MODE VOLTAGE – Volts

POSITIVE I

NEGATIVE I

B

B

10

15

TPC 9. Input Bias Current vs.

Common-Mode Voltage

REV. E–4–

Loading...

Loading...