ANALOG DEVICES AD5932 Service Manual

现货库存、技术资料、百科信息、热点资讯,精彩尽在鼎好!

A

A

V

Programmable Frequency Scan

Waveform Generator

FEATURES GENERAL DESCRIPTION

Programmable frequency profile

No external components necessary

Output frequency up to 25 MHz

Burst-and-listen capability

Preprogrammable frequency profile minimizes number of

DSP/microcontroller writes

Sinusoidal/triangular/square wave outputs

Automatic or single pin control of frequency stepping

Power-down mode: 20 μA

Power supply: 2.3 V to 5.5 V

Automotive temperature range: −40°C to +125°C

16-lead, Pb-free TSSOP

APPLICATIONS

Frequency scanning/radar

Network/impedance measurements

Incremental frequency stimulus

Sensory applications

Proximity and motion

The AD59321 is a waveform generator offering a programmable

frequency scan. Utilizing embedded digital processing that

allows enhanced frequency control, the device generates

synthesized analog or digital frequency-stepped waveforms.

Because frequency profiles are preprogrammed, continuous

write cycles are eliminated, thereby freeing up valuable

DSP/microcontroller resources. Waveforms start from a known

phase and are incremented phase-continuously, which allows

phase shifts to be easily determined. Consuming only 6.7 mA,

the AD5932 provides a convenient low power solution to

waveform generation.

The AD5932 outputs each frequency in the range of interest for

a defined length of time and then steps to the next frequency in

the scan range. The length of time the device outputs a particular

frequency is preprogrammed, and the device increments the

frequency automatically; or, alternatively, the frequency is

incremented externally via the CTRL pin. At the end of the

range, the AD5932 continues to output the last frequency until

the device is reset. The AD5932 also offers a digital output via

the MSBOUT pin.

AD5932

(continued on Page 3)

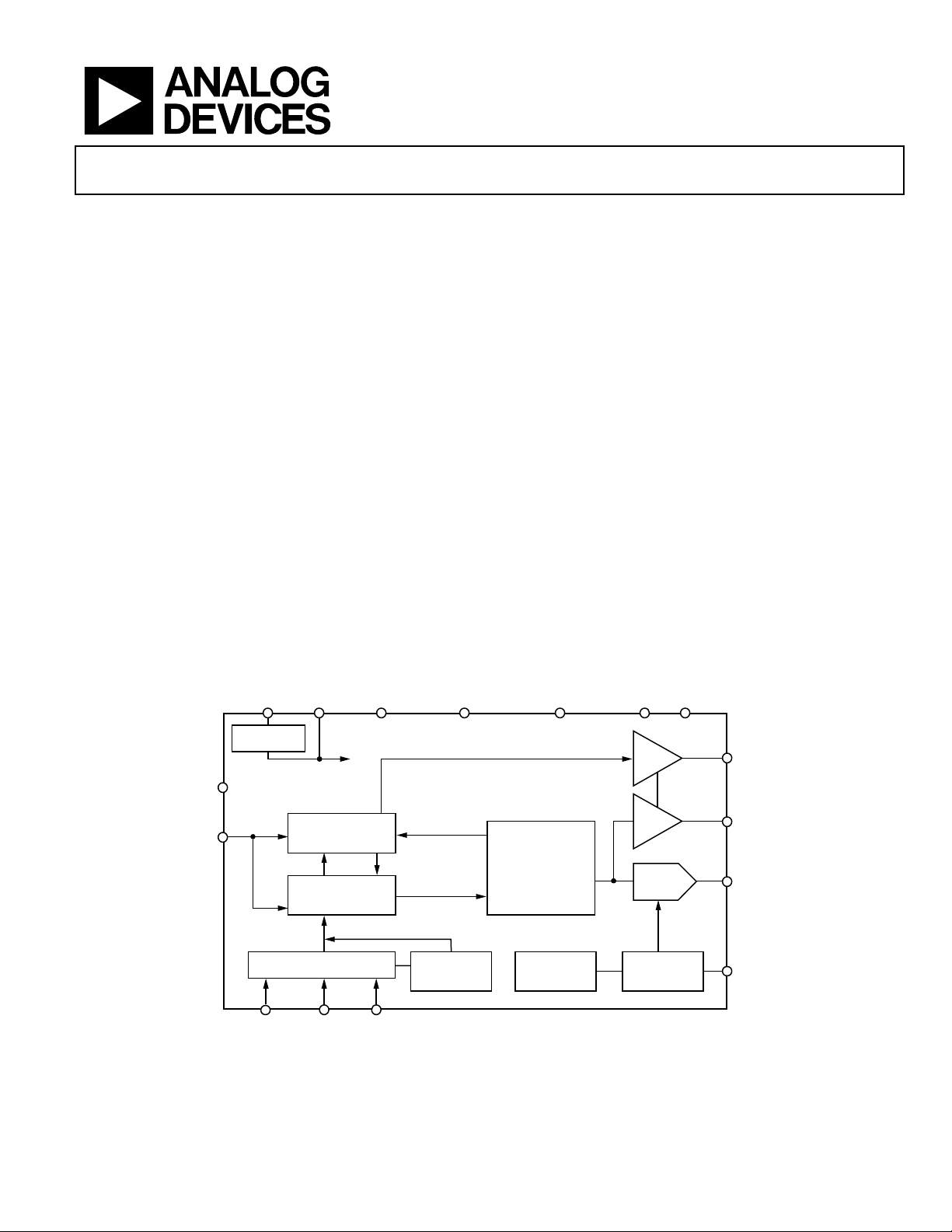

FUNCTIONAL BLOCK DIAGRAM

DVDD CAP/2.5V DGND INTERRUPT STANDBY

REGULATOR

MCLK

CTRL

DATA INCR

SERIAL INTE RFACE

FSYNC

1

Protected by U.S. patent number 6747583; other patents pending.

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

SCLK SDATA

VCC

2.5V

INCREMENT

CONTROLLER

FREQUENCY

CONTROLLER

DATAAND CONTROL

SYNC

/

24

CONTROL

REGISTER

GND

AD5932

BUFFER

BUFFER

24-BIT

PIPELINED

DDS CORE

ON-BOARD

REFERENCE

Figure 1.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2006 Analog Devices, Inc. All rights reserved.

FULL-SCALE

10-BIT

DAC

CONTROL

DD

SYNCOUT

MSBOUT

VOUT

COMP

05416-001

AD5932

TABLE OF CONTENTS

Features.............................................................................................. 1

Serial Interface............................................................................ 15

Applications....................................................................................... 1

General Description ......................................................................... 1

Functional Block Diagram .............................................................. 1

Revision History ............................................................................... 2

Specifications..................................................................................... 4

Specifications Test Circuit........................................................... 5

Timing Specifications .................................................................. 6

Master Clock and Timing Diagrams ......................................... 6

Absolute Maximum Ratings............................................................ 8

ESD Caution.................................................................................. 8

Pin Configuration and Function Descriptions............................. 9

Typical Performance Characteristics ........................................... 10

Terminology .................................................................................... 14

Theory of Operation ...................................................................... 15

Frequency Profile........................................................................ 15

Powering up the AD5932.......................................................... 15

Programming the AD5932........................................................ 16

Setting Up the Frequency Scan................................................. 17

Activating and Controlling the Scan ....................................... 18

Outputs from the AD5932........................................................ 19

Applications..................................................................................... 20

Grounding and Layout.............................................................. 20

AD5932 to ADSP-21xx Interface ............................................. 20

AD5932 to 68HC11/68L11 Interface....................................... 21

AD5932 to 80C51/80L51 Interface.......................................... 21

AD5932 to DSP56002 Interface ............................................... 21

Evaluation Board............................................................................ 22

Schematics................................................................................... 23

Outline Dimensions....................................................................... 25

Ordering Guide .......................................................................... 25

REVISION HISTORY

4/06—Revision 0: Initial Version

Rev. 0 | Page 2 of 28

AD5932

GENERAL DESCRIPTION

(continued from Page 1)

To program the AD5932, the user enters the start frequency, the

increment step size, the number of increments to be made, and

the time interval that the part outputs each frequency. The frequency scan profile is initiated, started, and executed by toggling

the CTRL pin.

The AD5932 is written to via a 3-wire serial interface that operates

at clock rates up to 40 MHz. The device operates with a power

supply from 2.3 V to 5.5 V.

Note that the AVDD and DVDD are independent of each other

and can be operated from different voltages. The AD5932 also

has a standby function that allows sections of the device that are

not in use to be powered down.

The AD5932 is available in a 16-lead, Pb-free TSSOP.

Rev. 0 | Page 3 of 28

AD5932

SPECIFICATIONS

AVDD = DVDD = 2.3 V to 5.5 V; AGND = DGND = 0 V; TA = T

Table 1.

Y Grade

Parameter Min Typ Max Unit Test Conditions/Comments

SIGNAL DAC SPECIFICATIONS

Resolution 10 Bits

Update Rate 50 MSPS

VOUT Peak-to-Peak 0.58 V Internal 200 Ω resistor to GND

VOUT Offset 56 mV From 0 V to the trough of the waveform

V

0.32 V Voltage at midscale output

MIDSCALE

VOUT TC 200 ppm/°C

DC Accuracy

Integral Nonlinearity (INL) ±1.5 LSB

Differential Nonlinearity (DNL) ±0.75 LSB

DDS SPECIFICATIONS

Dynamic Specifications

Signal-to-Noise Ratio 53 60 dB f

Total Harmonic Distortion −60 −53 dBc f

Spurious-Free Dynamic Range (SFDR)

Wide Band (0 to Nyquist) −56 −52 dBc f

Narrow Band (±200 kHz) −74 −70 dBc f

Clock Feedthrough −50 dBc Up to 16 MHz out

Wake-Up Time 1.7 ms From standby

OUTPUT BUFFER

VOUT Peak-to-Peak 0 DVDD V Typically, square wave on MSBOUT and SYNCOUT

Output Rise/Fall Time

2

12 ns

VOLTAGE REFERENCE

Internal Reference 1.15 1.18 1.26 V

Reference TC

LOGIC INPUTS

2

2

90 ppm/°C

Input Current 0.1 ±2 μA

Input High Voltage, V

1.7 V DVDD = 2.3 V to 2.7 V

INH

2.0 V DVDD = 2.7 V to 3.6 V

2.8 V DVDD = 4.5 V to 5.5 V

Input Low Voltage, V

0.6 V DVDD = 2.3 V to 2.7 V

INL

0.7 V DVDD = 2.7 V to 3.6 V

0.8 V DVDD = 4.5 V to 5.5 V

Input Capacitance, CIN 3 pF

LOGIC OUTPUTS

2

Output High Voltage, VOH DVDD − 0.4 V V I

Output Low Voltage, VOL 0.4 V I

Floating-State O/P Capacitance 5 pF

POWER REQUIREMENTS f

AVDD/DVDD 2.3 5.5 V

IAA 3.8 4 mA

IDD 2.4 2.7 mA

IAA + IDD 6.2 6.7 mA

to T

MIN

1

, unless otherwise noted.

MAX

= 50 MHz, f

MCLK

= 50 MHz, f

MCLK

= 50 MHz, f

MCLK

= 50 MHz, f

MCLK

= 1 mA

SINK

= 1 mA

SINK

= 50 MHz, f

MCLK

OUT

OUT

OUT

OUT

OUT

= f

= f

= f

= f

= f

MCLK

MCLK

MCLK

MCLK

MCLK

/4096

/4096

/50

/50

/7

Rev. 0 | Page 4 of 28

AD5932

F

Y Grade

1

Parameter Min Typ Max Unit Test Conditions/Comments

Low Power Sleep Mode Device is reset before putting into standby

20 85 μA

All outputs powered down, MCLK = 0 V,

serial interface active

140 240 μA

All outputs powered down, MCLK active,

serial interface active

1

Operating temperature range is as follows: Y version: −40°C to +125°C; typical specifications are at +25°C.

2

Guaranteed by design, not production tested.

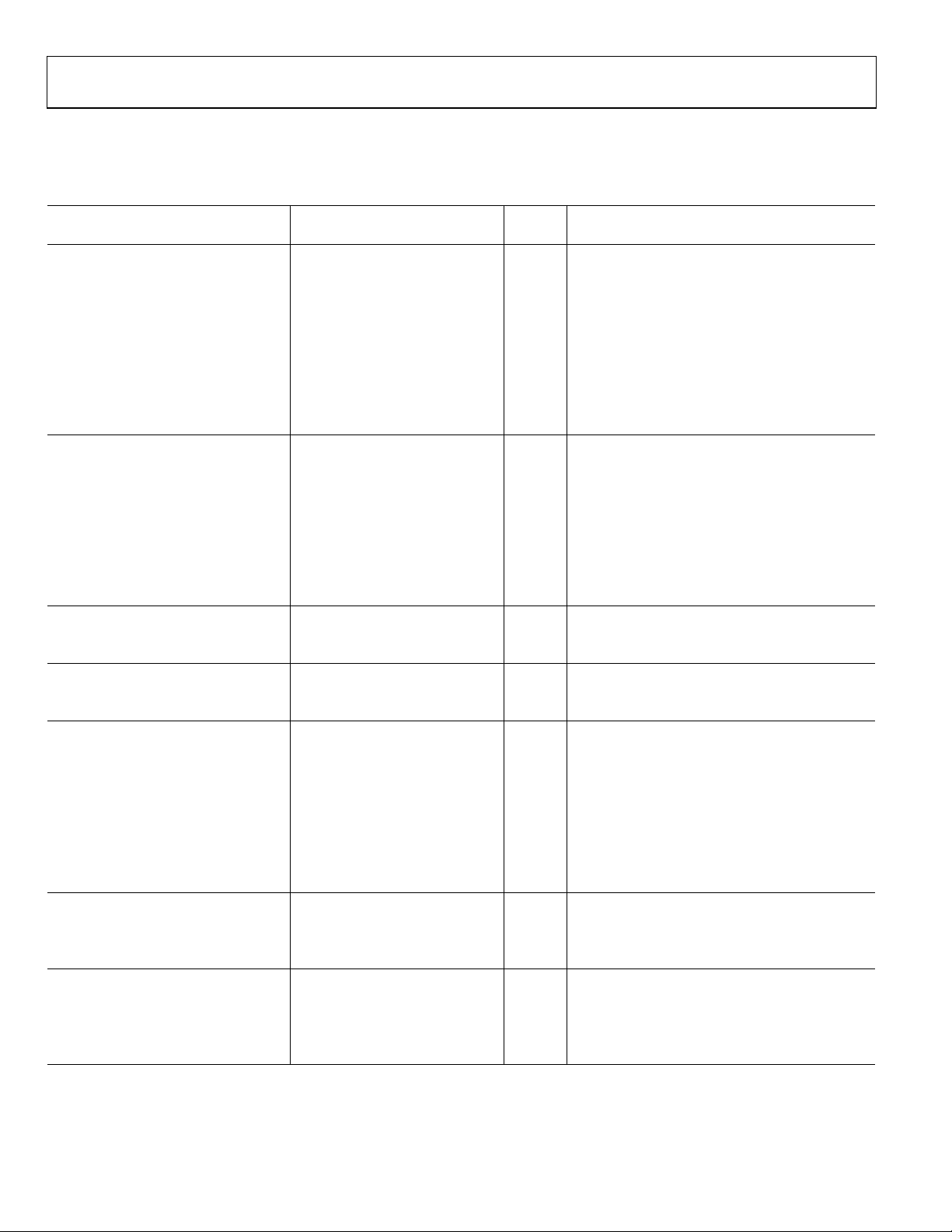

SPECIFICATIONS TEST CIRCUIT

100n

10nF

CAP/2.5V

REGULATOR

12

SIN

ROM

AVDD

10-BIT

DAC

10nF

COMP

AD5932

Figure 2. Test Circuit Used to Test the Specifications

VOUT

20pF

05416-002

Rev. 0 | Page 5 of 28

AD5932

C

TIMING SPECIFICATIONS

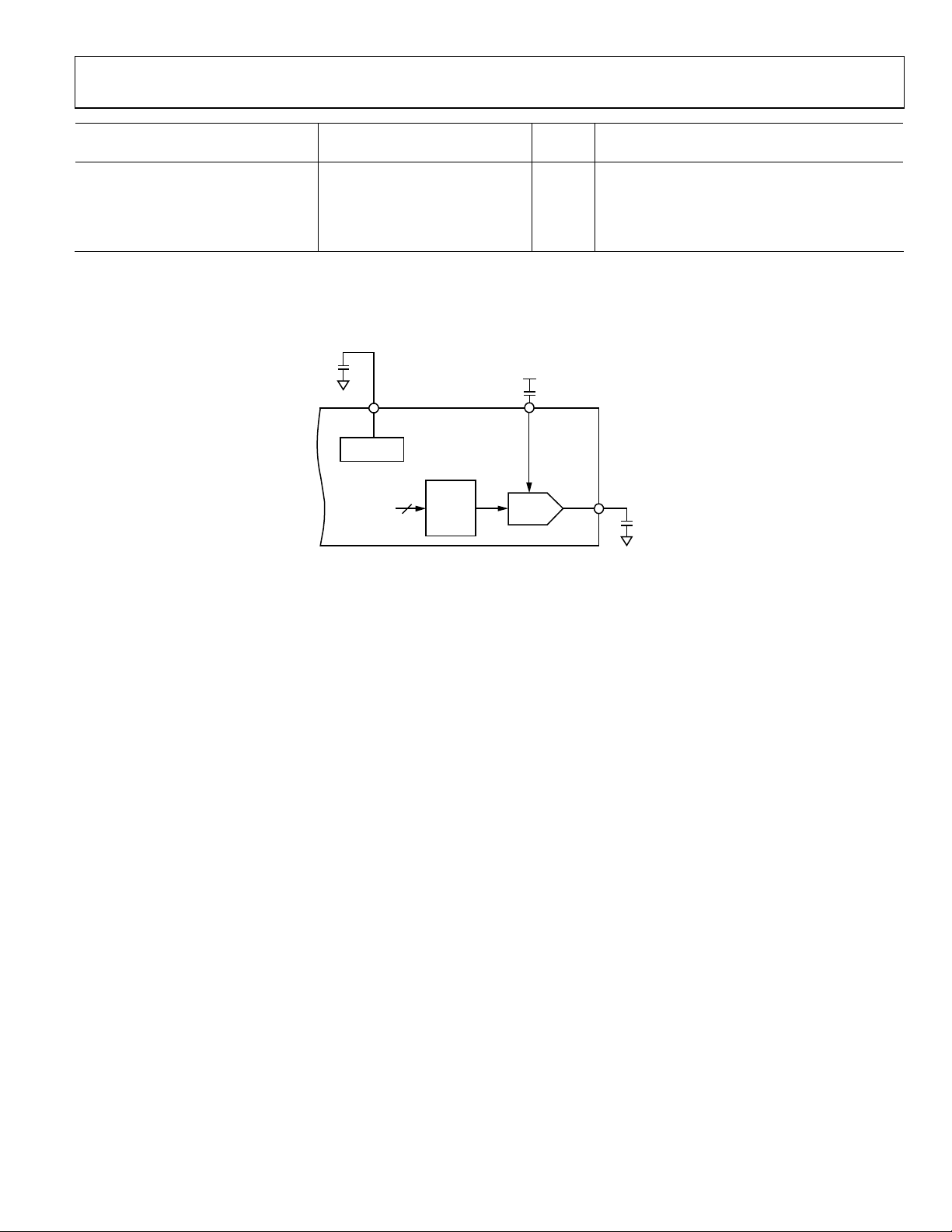

All input signals are specified with tR = tF = 5 ns (10% to 90% of VDD) and are timed from a voltage level of (VIL + VIH)/2 (see Figure 3 to

Figure 6). DVDD = 2.3 V to 5.5 V; AGND = DGND = 0 V; all specifications T

Table 2.

Parameter Limit at T

1

, T

Unit Conditions/Comments

MIN

MAX

t1 20 ns min MCLK period

t2 8 ns min MCLK high duration

t3 8 ns min MCLK low duration

t4 25 ns min SCLK period

t5 10 ns min SCLK high time

t6 10 ns min SCLK low time

t7 5 ns min FSYNC to SCLK falling edge setup time

t8 10 ns min FSYNC to SCLK hold time

t9 5 ns min Data setup time

t10 3 ns min Data hold time

t11 2 × t1 ns min Minimum CTRL pulse width

t12 0 ns min CTRL rising edge to MCLK falling edge setup time

t13 10 × t1 ns typ CTRL rising edge to VOUT delay (initial pulse, includes initialization)

8 × t1 ns typ CTRL rising edge to VOUT delay (initial pulse, includes initialization)

t14 1 × t1 ns typ Frequency change to SYNC output, each frequency increment

t15 2 × t1 ns typ Frequency change to SYNC output, end of scan

t16 20 ns max MCLK falling edge to MSBOUT

1

Guaranteed by design, not production tested.

MIN

to T

, unless otherwise noted.

MAX

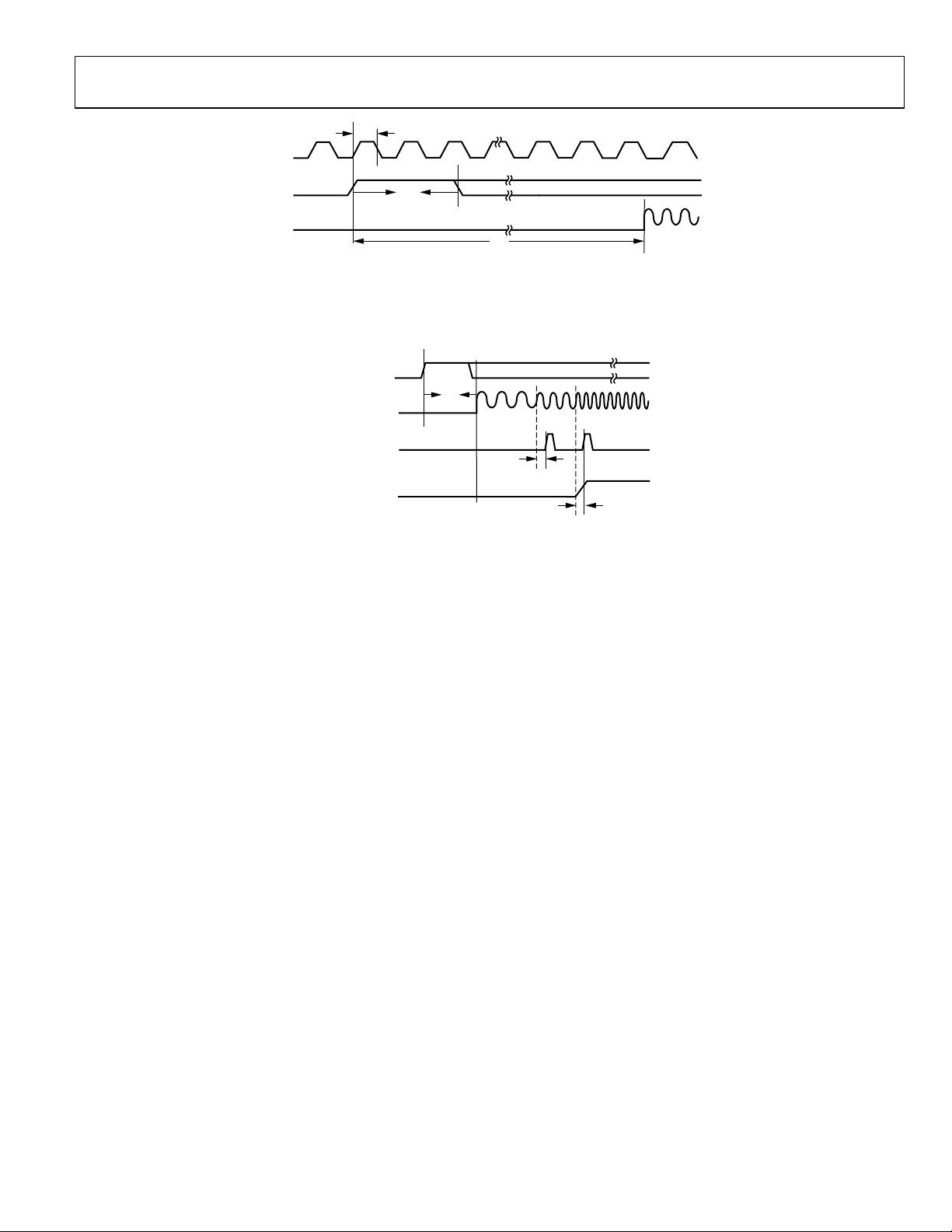

MASTER CLOCK AND TIMING DIAGRAMS

SCLK

t

7

FSYN

SDATA

D15 D14 D2 D1 D0 D15 D14

t

6

MCLK

Figure 3. Master Clock

t

5

Figure 4. Serial Timing

t

1

t

2

t

3

t

4

t

9

05416-003

t

8

t

10

05416-004

Rev. 0 | Page 6 of 28

AD5932

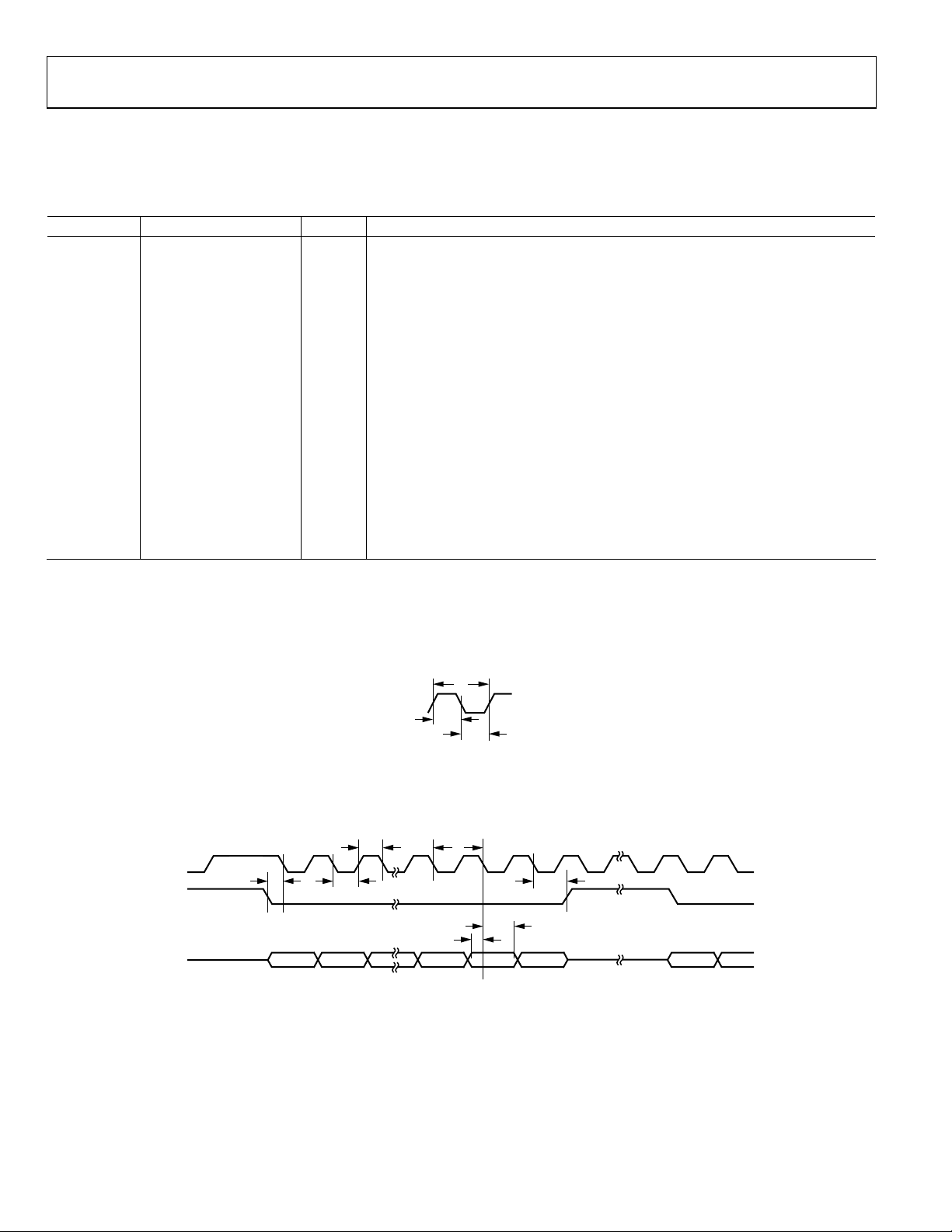

y

t

MCLK

12

CTRL

VOUT

t

11

t

13

05416-005

Figure 5. CTRL Timing

CTRL

t

13

VOUT

SYNCOUT

(Each Freq u en c

Increment)

SYNCOUT

(End of Scan)

Figure 6. SYNCOUT Timing

t

14

t

15

05416-006

Rev. 0 | Page 7 of 28

AD5932

ABSOLUTE MAXIMUM RATINGS

TA = 25°C, unless otherwise noted.

Table 3.

Parameter Rating

AVDD to AGND −0.3 V to +6.0 V

DVDD to DGND −0.3 V to +6.0 V

AGND to DGND −0.3 V to +0.3 V

CAP/2.5 V to DGND −0.3 V to +2.75 V

Digital I/O Voltage to DGND −0.3 V to DVDD + 0.3 V

Analog I/O Voltage to AGND −0.3 V to AVDD + 0.3 V

Operating Temperature Range

Automotive (Y Version) −40°C to +125°C

Storage Temperature Range −65°C to +150°C

Maximum Junction Temperature +150°C

TSSOP (4-Layer Board)

θJA Thermal Impedance 112°C/W

θJC Thermal Impedance 27.6°C/W

Reflow Soldering (Pb-Free) 300°C

Peak Temperature 260(+0/−5)°C

Time at Peak Temperature 10 sec to 40 sec

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the

human body and test equipment and can discharge without detection. Although this product features

proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy

electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance

degradation or loss of functionality.

Rev. 0 | Page 8 of 28

AD5932

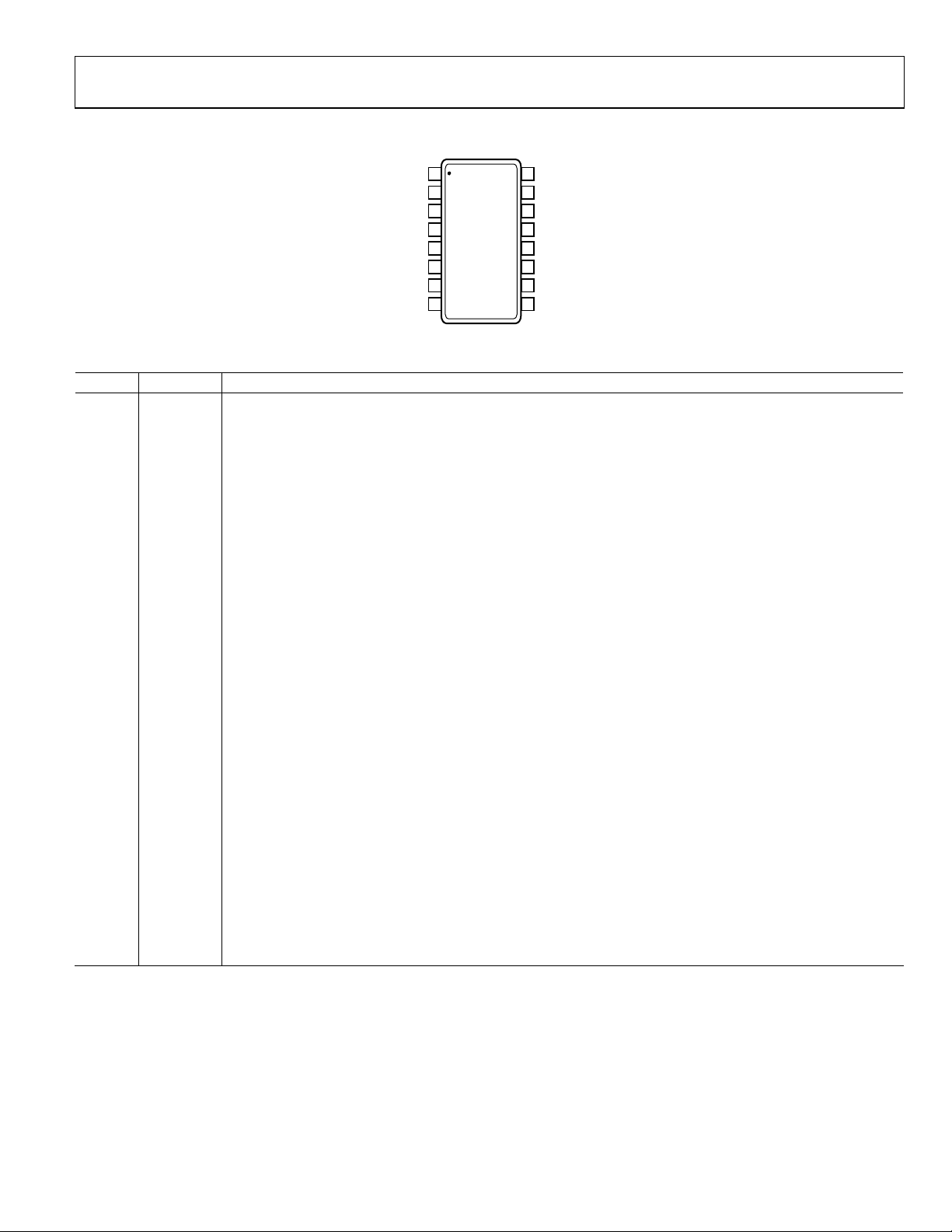

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

1

COMP

2

AVDD

3

DVDD

CAP/2.5V

DGND

MCLK

SYNCOUT

MSBOUT INTERRUPT

AD5932

4

TOP VIEW

(Not to S cale)

5

6

7

8

16

VOUT

15

AGND

14

STANDBY

13

FSYNC

12

SCLK

11

SDATA

10

CTRL

9

05416-007

Figure 7. Pin Configuration

Table 4. Pin Function Descriptions

Pin No. Mnemonic Description

1 COMP DAC Bias Pin. This pin is used for decoupling the DAC bias voltage to AVDD.

2 AVDD

Positive Power Supply for the Analog Section. AVDD can have a value from 2.3 V to 5.5 V. A 0.1 μF decoupling

capacitor should be connected between AVDD and AGND.

3 DVDD

Positive Power Supply for the Digital Section. DVDD can have a value from 2.3 V to 5.5 V. A 0.1 μF decoupling

capacitor should be connected between DVDD and DGND.

4 CAP/2.5V

Digital Circuitry. Operates from a 2.5 V power supply. This 2.5 V is generated from DVDD using an on-board

regulator. The regulator requires a decoupling capacitor of typically 100 nF, which is connected from CAP/2.5V

to DGND. If DVDD is equal to or less than 2.7 V, CAP/2.5V can be shorted to DVDD.

5 DGND Ground for All Digital Circuitry.

6 MCLK

Digital Clock Input. DDS output frequencies are expressed as a binary fraction of the frequency of MCLK.

The output frequency accuracy and phase noise are determined by this clock.

7 SYNCOUT

Digital Output for Scan Status Information. User-selectable for end of scan (EOS) or frequency increments through

the control register (SYNCOP bit). This pin must be enabled by setting the SYNCOUTEN bit in the control register to 1.

8 MSBOUT

Digital Output. The inverted MSB of the DAC data is available at this pin. This output pin must be enabled by

setting the MSBOUTEN bit in the control register to 1.

9 INTERRUPT

Digital Input. This pin acts as an interrupt during a frequency scan. A low-to-high transition is sampled by the

internal MCLK, which resets internal state machines. This results in the DAC output going to midscale.

10 CTRL

Digital Input. Triple function pin for initialization, start, and external frequency increments. A low-to-high transition,

sampled by the internal MCLK, is used to initialize and start internal state machines, which then execute the pre-

programmed frequency scan sequence. When in auto-increment mode, a single pulse executes the entire scan

sequence. When in external increment mode, each frequency increment is triggered by low-to-high transitions.

11 SDATA

Serial Data Input. The 16-bit serial data-word is applied to this input with the register address first, followed by

the MSB to LSBs of the data.

12 SCLK Serial Clock Input. Data is clocked into the AD5932 on each falling SCLK edge.

13 FSYNC

Active Low Control Input. This is the frame synchronization signal for the serial data. When FSYNC is taken low,

the internal logic is informed that a new word is being loaded into the device.

14 STANDBY

Active High Digital Input. When this pin is high, the internal MCLK is disabled, and the reference DAC and regulator

are powered down. For optimum power saving, it is recommended that the AD5932 be reset before it is put into

standby, as this results in a shutdown current of typically 20 μA.

15 AGND Ground for All Analog Circuitry.

16 VOUT

Voltage Output. The analog outputs from the AD5932 are available here. An external resistive load is not required,

because the device has a 200 Ω resistor on board. A 20 pF capacitor to AGND is recommended to act as a low-pass

filter and to reduce clock feedthrough.

Rev. 0 | Page 9 of 28

Loading...

Loading...