Programmable Frequency Sweep and

Preliminary Technical Data

FEATURES

Programmable frequency profile—no external

components necessary

Ouput frequency up to 25 Mhz

Burst and listen capability

Predefined frequency profile minimizes number

of DSP/µcontroller writes

Sinusoidal/triangular/square wave outputs

Automatic or single pin control of frequency stepping

Frequency starts at known phase—increments at 0° phase

or phase continuous

Powerdown mode (20 µA)

+2.3 V to +5.5 V power supply

Extended temperature range −40°C to +105°C

20-lead TSSOP

APPLICATIONS

Frequency Sweeping/Radar

Network/Impedance Measurements

Incremental Frequency stimulus

Sensory Applications—Proximity and Motion

BFSK

Frequency Bursting/Pulse Trains

Output Burst Waveform Generator

AD5930

GENERAL DESCRIPTION

The AD59301 is a waveform generator with programmable

frequency sweep and output burst capability. Utilizing

embedded digital processing allowing enhanced frequency

control the device generates synthesized analog or digital

frequency-stepped waveforms. Because frequency profiles are

preprogrammed continuous write cycles are eliminated, thereby

freeing up valuable DSP/µController resources. Waveforms start

from a known phase and are incremented phase conti0nuously

allowing phase shifts to be easily determined. Consuming only

8mA the AD5930 provides a convenient low power solution to

waveform generation.

The AD5930 can be operated in three modes. In continuous

output mode the device outputs the required frequency for a

defined length of time and then steps to the next frequency.

The length of time the device outputs a particular frequency

can be either preprogrammed and the device increments the

frequency automatically or alternatively can be incremented

externally via the CTRL pin. In Burst mode, the device outputs

it’s frequency for a length of time and then returns to midscale

for a further predefined length of time before stepping to the

next frequency. In MSB mode a digital output is generated.

(continued on Page 3)

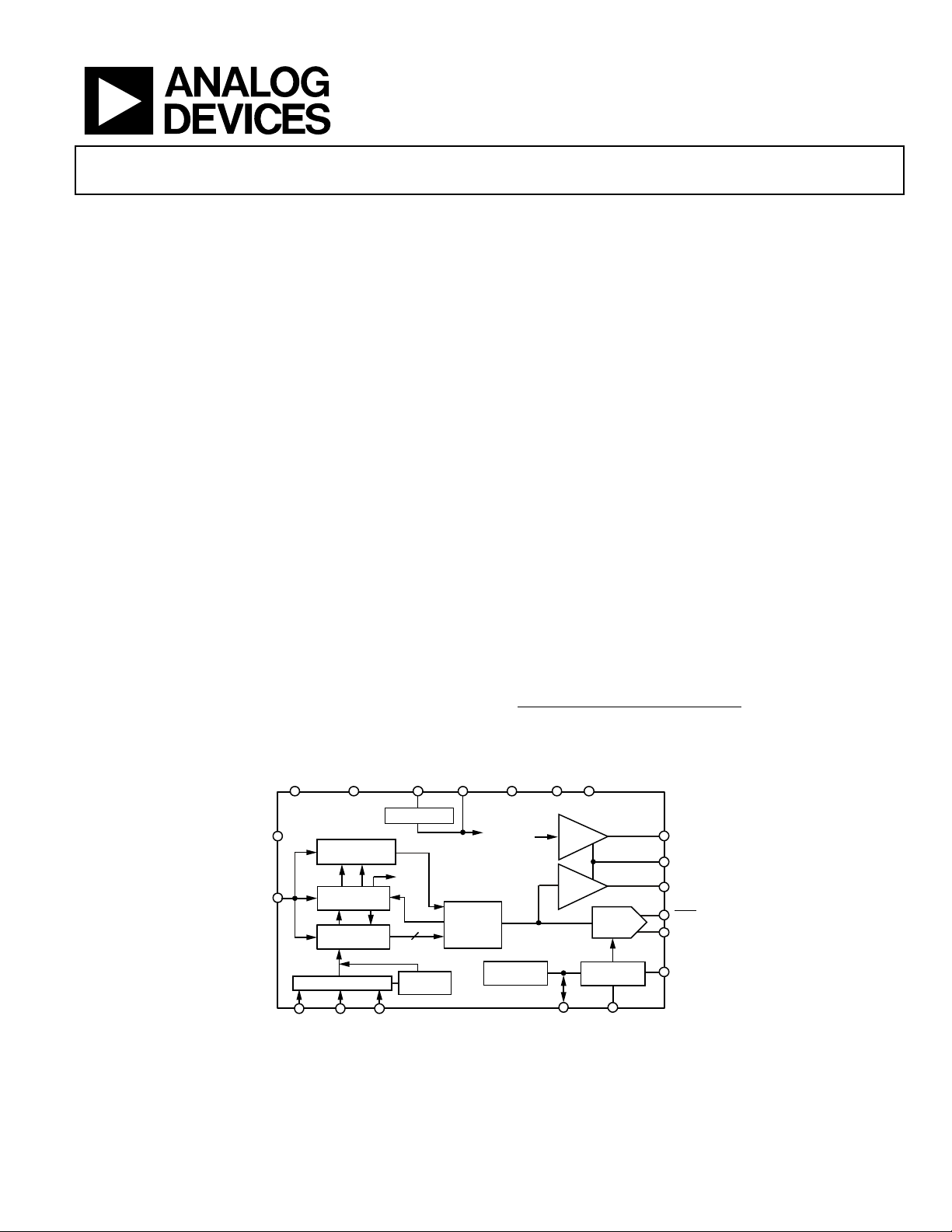

FUNCTIONAL BLOCK DIAGRAM

INTERRUPT STANDBY DVDD CAP/2.6V DGND AGND AVDD

REGULATOR

MCLK

CTRL

Rev. PrF

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

OUTPUT BURST

CONTROLLER

DATA

INCREMENT

CONTROLLER

DATA

FREQUENCY

CONTROLLER

DATA

SERIAL INTERFACE

FSYNC SCLK SDATA

INCR

AND CONTROL

SYNC

24

CONTROL

REGISTER

PIPELINED

DOS CORE

24-BIT

Figure 1.

1

Protected by US Patent Number 6747583, other patents pending.

VCC

SYNC

2.5V

ON-BOARD

REFERENCE

BUFFER

BUFFER

10-BIT

DAC

FULL-SCALE

CONTROL

REF FS ADJUST

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.326.8703 © 2005 Analog Devices, Inc. All rights reserved.

www.analog.com

SYNC OUT

OPDGND

MSB OUT

IOUT

IOUT

COMP

05333-001

AD5930 Preliminary Technical Data

TABLE OF CONTENTS

General Description ......................................................................... 3

Functional Description.............................................................. 11

Specifications..................................................................................... 4

Absolute Maximum Ratings............................................................ 6

ESD Caution.................................................................................. 6

Pin Configurations And Functional Descriptions....................... 7

Terminology ...................................................................................... 9

Detailed Operation......................................................................... 10

REVISION HISTORY

2/05—Revision PrF: Preliminary Version

Outputs from the AD5930........................................................ 11

Programming the AD5930........................................................ 11

Setting up the Sweep.................................................................. 13

Activating and controlling the Sweep...................................... 14

Outline Dimensions....................................................................... 16

Ordering Guide .......................................................................... 16

Rev. PrF | Page 2 of 16

Preliminary Technical Data AD5930

GENERAL DESCRIPTION

(continued from Page 1)

To program the device, the user enters the start frequency, the

increment step size, the number of increments to be made and

the time interval the part stays at each frequency. The frequency

profile can be initiated by toggling the CTRL pin.

A number of different sweep profiles are offered. Frequencies

can be stepped in triangular-sweep mode continuously

sweeping up and down through the frequency range or in sawsweep mode sweeping up but returning to the initial frequency

before initiating the sweep again. In addition a single frequency

or burst can generate without any sweep.

The AD5930 is written to via a 3-wire serial interface, which

operates at clock rates up to 40 MHz. The device operates with a

power supply from 2.3 V to 5.5 V and has a standby function

which allows sections of the device that are not being used to be

powered down.

The AD5930 is available in a 20-lead TSSOP package.

Rev. PrF | Page 3 of 16

AD5930 Preliminary Technical Data

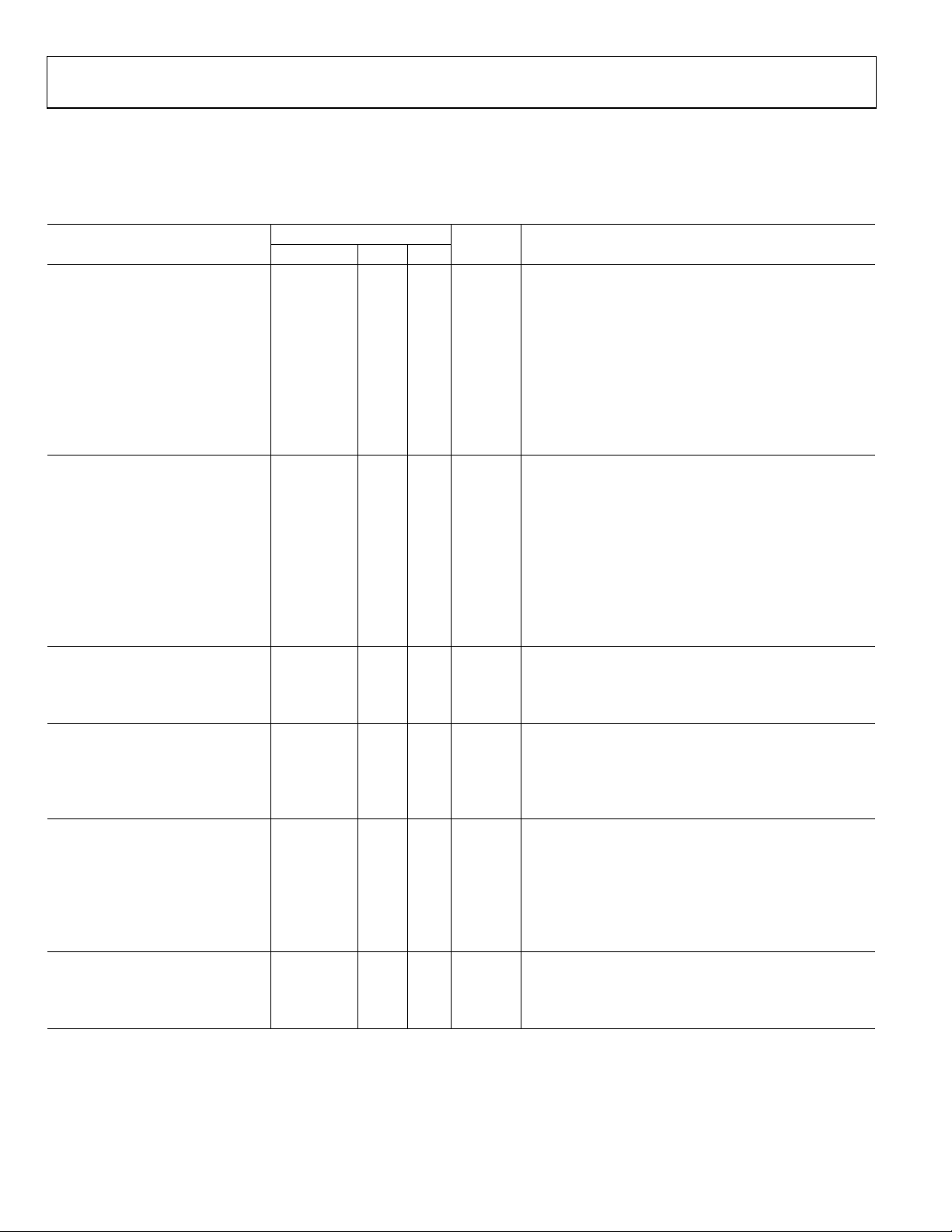

SPECIFICATIONS

A

= D

V

DD

unless otherwise noted.

Table 1.

Y Grade2

Parameter

SIGNAL DAC SPECIFICATIONS

Resolution 10 Bits

Update Rate 50 MSPS

Iout Fullscale3 3.124 4.0 mA

Vout peak-to-peak 0.6 V

Vout offset 30 mV From 0V to the trough of the waveform

Output Compliance 0.8 V AVDD = 2.3 V, Internal reference used

DC Accuracy:

Integral Nonlinearity (INL) ±1 LSB

Differential nonlinearity (DNL) ±0.5 LSB

DDS SPECIFICATIONS

Dynamic Specifications:

Signal to Noise Ratio 55 60 dB

Total Harmonic Distortion −66 −56 dBc

Spurious Free Dynamic Range

(SFDR):

Clock Feedthrough −50 dBc

Wake Up Time 1 ms

OUTPUT BUFFER

Vout peak-to peak D

Output Rise/Fall Time 12 ns

Output Jitter 120 ps rms When DAC data MSB is output

VOLTAGE REFERENCE

Internal Reference 1.12 1.18 1.24 V

External Reference Range 1.3 V

REFOUT Input Impedance 1 k Ω

Reference TC 100 ppm/°C

LOGIC INPUTS

Input current 10 µA

V

INH

2.0 V Vdd = 2.7 V to 5.5 V

V

INL

0.8 V Vdd = 2.7 V to 5.5 V

CIN, input capacitance3 3 pF

LOGIC OUTPUTS

V

OHL

VOL, output low voltage 0.4 V I

Floating-state O/P capacitance 8 pF

= +2.3 V to +5.5 V; AGND = DGND = 0 V; TA = T

V

DD

Min Typ Max

MIN

to T

MAX

; R

SET

= 6.8 kΩ, R

LOAD

Unit Test Conditions/Comments

= 50 MHz, f

f

MCLK

= 50 MHz, f

f

MCLK

OUT

OUT

Wideband (0 to Nyquist) −60 −56 dBc

NarrowBand (± 200 kHz) −78 −67 dBc

V Squarewave on MSB OUT

VDD

= 50 MHz, f

f

MCLK

= 50 MHz, f

f

MCLK

OUT

OUT

, input high voltage 1.7 V Vdd = 2.3 V to 2.7 V

, input low voltage 0.7 V Vdd = 2.3 V to 2.7 V

, output high voltage D

− 0.8 V V I

VDD

= 1 mA

SINK

= 1 mA

SINK

= 200 Ω for IOUT and IOUTB,

= f

/4096

MCLK

= f

/4096

MCLK

= f

/50

MCLK

= f

/50

MCLK

Rev. PrF | Page 4 of 16

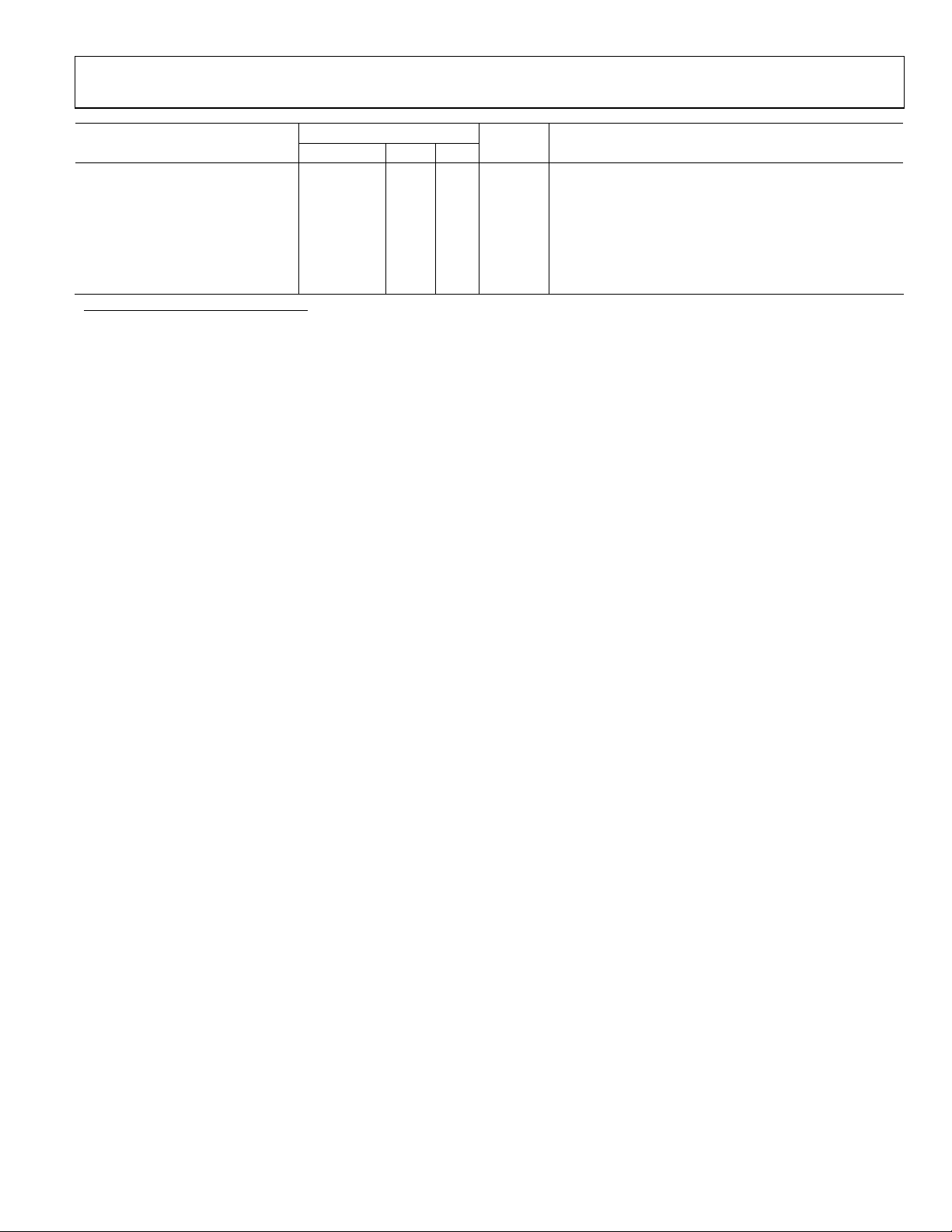

Preliminary Technical Data AD5930

Y Grade2

Parameter

Min Typ Max

POWER REQUIREMENTS

AVDD/DVDD 2.3 5.5 V

IAA 3.8 5 MA

IDD 2.0 3 mA

IAA + IDD 5.8 8 mA

Low Power Sleep Mode 20 µA

2

Operating temperature range is as follows: Y Version: −40°C to + 105°C; typical specifications are at 25°C.

3

Guaranteed by Design.

Unit Test Conditions/Comments

= 50 MHz, f

f

MCLK

OUT

= f

MCLK

/7

All outputs powered down, MCLK =0MHz, Serial interface

active

Rev. PrF | Page 5 of 16

Loading...

Loading...