ANALOG DEVICES AD5694R Service Manual

with 2 ppm/°C Reference, I2C Interface

AD5696R/AD5695R/AD5694R

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

Trademarks and registered trademarks are the property of their respective owners.

Fax: 781.461.3113 ©2012 Analog Devices, Inc. All rights reserved.

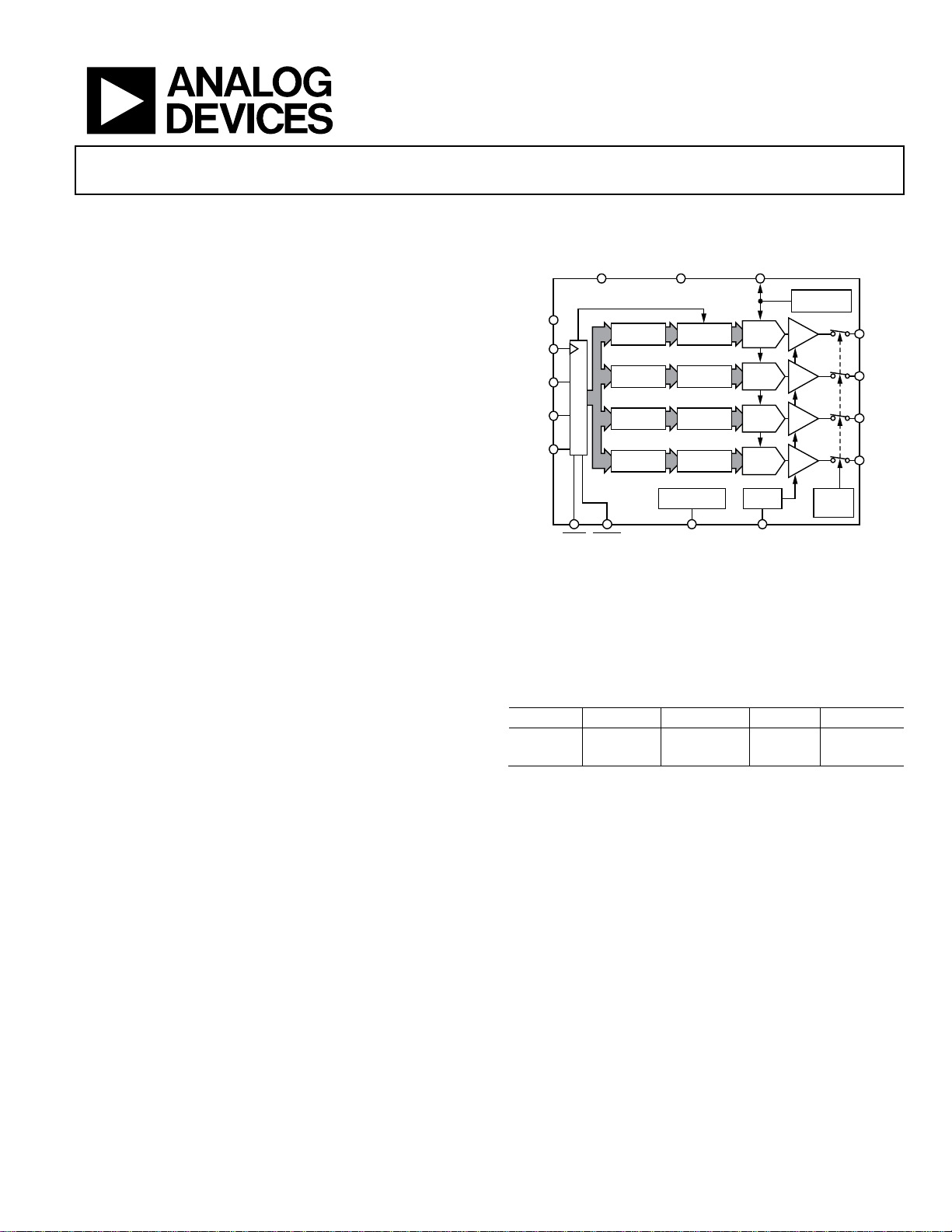

SCL

V

LOGIC

SDA

A1

A0

INPUT

REGISTER

DAC

REGISTER

STRING

DAC A

BUFFER

V

OUT

A

INPUT

REGISTER

DAC

REGISTER

STRING

DAC B

BUFFER

V

OUT

B

INPUT

REGISTER

DAC

REGISTER

STRING

DAC C

BUFFER

V

OUT

C

INPUT

REGISTER

DAC

REGISTER

STRING

DAC D

BUFFER

V

OUT

D

V

REF

GNDV

DD

2.5V

REFERENCE

POWER-

DOWN

LOGIC

POWER-ON

RESET

GAIN =

×1/×2

INTERFACE LOGIC

RSTSEL

GAINLDAC RESET

AD5696R/AD5695R/AD5694R

10486-001

Data Sheet

FEATURES

High relative accuracy (INL): ±2 LSB maximum @ 16 bits

Low drift 2.5 V reference: 2 ppm/°C typical

Tiny package: 3 mm × 3 mm, 16-lead LFCSP

Total unadjusted error (TUE): ±0.1% of FSR maximum

Offset error: ±1.5 mV maximum

Gain error: ±0.1% of FSR maximum

High drive capability: 20 mA, 0.5 V from supply rails

User selectable gain of 1 or 2 (GAIN pin)

Reset to zero scale or midscale (RSTSEL pin)

1.8 V logic compatibility

Low glitch: 0.5 nV-sec

400 kHz I

Robust 3.5 kV HBM and 1.5 kV FICDM ESD rating

Low power: 3.3 mW at 3 V

2.7 V to 5.5 V power supply

−40°C to +105°C temperature range

APPLICATIONS

Optical transceivers

Base-station power amplifiers

Process control (PLC I/O cards)

Industrial automation

Data acquisition systems

2

C-compatible serial interface

Quad 16-/14-/12-Bit nanoDAC+

FUNCTIONAL BLOCK DIAGRAM

Figure 1.

GENERAL DESCRIPTION

The AD5696R/AD5695R/AD5694R family, are low power,

quad, 16-/14-/12-bit buffered voltage output DACs. The devices

include a 2.5 V, 2 ppm/°C internal reference (enabled by

default) and a gain select pin giving a full-scale output of 2.5 V

(gain = 1) or 5 V (gain = 2). All devices operate from a single

2.7 V to 5.5 V supply, are guaranteed monotonic by design, and

exhibit less than 0.1% FSR gain error and 1.5 mV offset error

performance. The devices are available in a 3 mm × 3 mm

LFCSP and a TSSOP package.

The AD5696R/AD5695R/AD5694R also incorporate a poweron reset circuit and a RSTSEL pin that ensures that the DAC

outputs power up to zero scale or midscale and remain there

pin intended for 1.8 V/3 V/5 V logic.

LOGIC

until a valid write takes place. Each part contains a per-channel

power-down feature that reduces the current consumption of

the device to 4 µA at 3 V while in power-down mode.

The AD5696R/AD5695R/AD5694R use a versatile 2-wire serial

interface that operates at clock rates up to 400 kHz, and

includes a V

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without n otice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Table 1. Quad nanoDAC+ Devices

Interface Reference 16-Bit 14-Bit 12-Bit

SPI Internal AD5686R AD5685R AD5684R

I2C Internal AD5696R AD5695R AD5694R

PRODUCT HIGHLIGHTS

1. High Relative Accuracy (INL).

AD5696R (16-bit): ±2 LSB maximum

AD5695R (14-bit): ±1 LSB maximum

AD5694R (12-bit): ±1 LSB maximum

2. Low Drift 2.5 V On-Chip Reference.

2 ppm/°C typical temperature coefficient

5 ppm/°C maximum temperature coefficient

3. Two Package Options.

3 mm × 3 mm, 16-lead LFCSP

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

16-lead TSSOP

www.analog.com

AD5696R/AD5695R/AD5694R Data Sheet

TABLE OF CONTENTS

Features .............................................................................................. 1

Applications ....................................................................................... 1

Functional Block Diagram .............................................................. 1

General Description ......................................................................... 1

Product Highlights ........................................................................... 1

Revision History ............................................................................... 2

Specifications ..................................................................................... 3

AC Characteristics ........................................................................ 5

Timing Characteristics ................................................................ 6

Absolute Maximum Ratings ............................................................ 7

ESD Caution .................................................................................. 7

Pin Configuration and Function Descriptions ............................. 8

Typical Performance Characteristics ............................................. 9

Terminolog y .................................................................................... 16

Theory of Operation ...................................................................... 18

Digital-to-Analog Converter .................................................... 18

Transfer Function ....................................................................... 18

DAC Architecture ....................................................................... 18

Serial Interface ............................................................................ 19

Write and Update Commands .................................................. 20

Serial Operation ......................................................................... 21

Write Operation.......................................................................... 21

Read Operation........................................................................... 22

Multiple DAC Readback Sequence .......................................... 22

Power-Down Operation ............................................................ 23

Load DAC (Hardware

LDAC

Mask Register ................................................................. 24

Hardware Reset (

Reset Select Pin (RSTSEL) ........................................................ 25

Internal Reference Setup ........................................................... 25

Solder Heat Reflow ..................................................................... 25

Long-Term Temperature Drift ................................................. 25

Thermal Hysteresis .................................................................... 26

Applications Information .............................................................. 27

Microprocessor Interfacing ....................................................... 27

AD5696R/AD5695R/AD5694R to ADSP-BF531 Interface .. 27

Layout Guidelines....................................................................... 27

Galvanically Isolated Interface ................................................. 27

Outline Dimensions ....................................................................... 28

Ordering Guide .......................................................................... 29

LDAC

Pin) ........................................... 24

) .......................................................... 25

RESET

REVISION HISTORY

4/12—Revision 0: Initial Version

Rev. 0 | Page 2 of 32

Data Sheet AD5696R/AD5695R/AD5694R

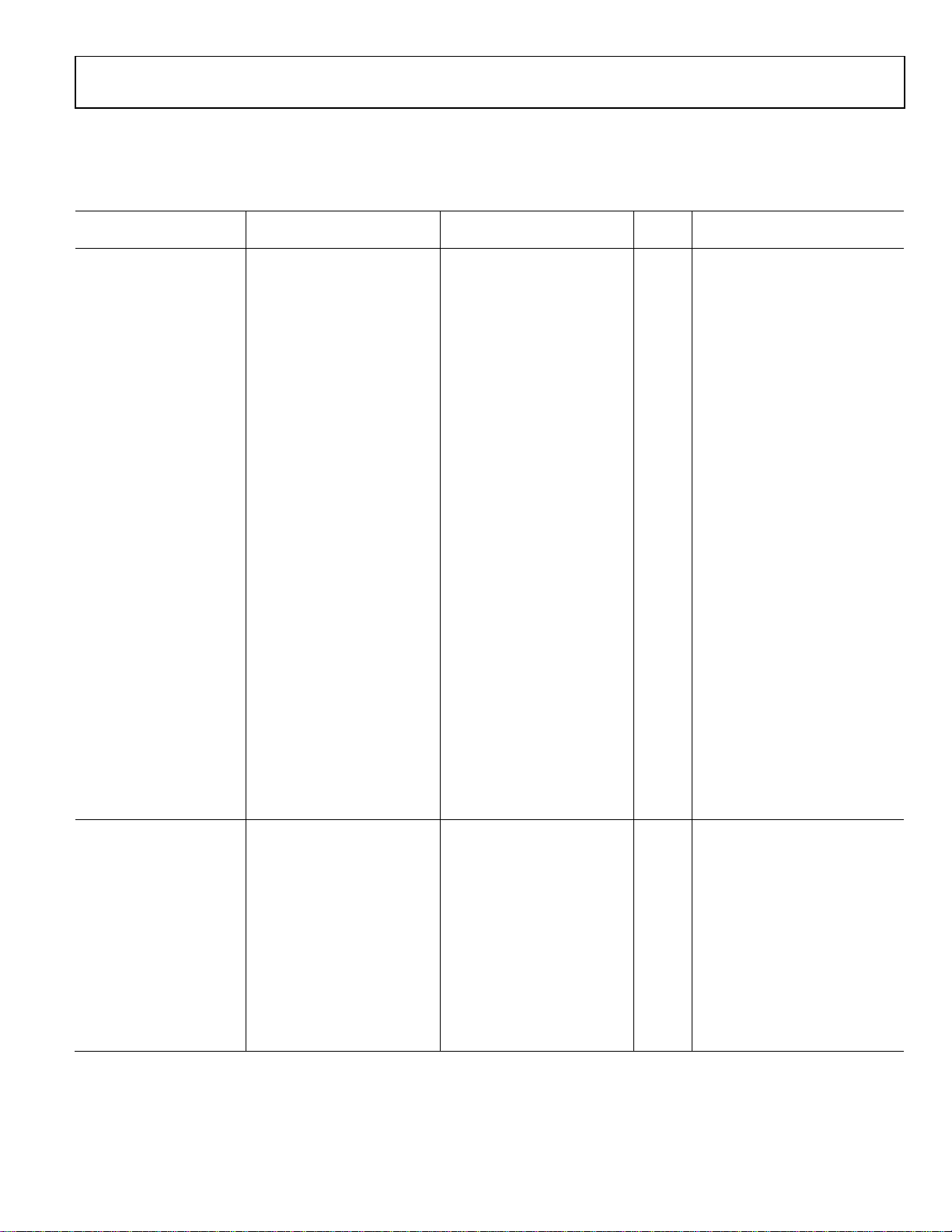

STATIC PERFORMANCE2

AD5696R

Resolution

16

16

Bits

% of

±3

±3 µV/mA

Due to load current change

Load Impedance at Rails6

25

25 Ω

See Figure 31

Power-Up Time

2.5

2.5 µs

Coming out of power-down mode;

SPECIFICATIONS

VDD = 2.7 V to 5.5 V; 1.8 V ≤ V

≤ 5.5 V; all specifications T

LOGIC

MIN

to T

, unless otherwise noted. RL = 2 kΩ; CL = 200 pF.

MAX

Table 2.

1

A Grade1

Parameter Min Typ Max Min Typ Max Unit Test Conditions/Comments

Relative Accuracy ±2 ±8 ±1 ±2 LSB Gain = 2

±2 ±8 ±1 ±3 Gain = 1

Differential Nonlinearity ±1 ±1 LSB Guaranteed monotonic by design

AD5695R

Resolution 14 14 Bits

Relative Accuracy ±0.5 ±4 ±0.5 ±1 LSB

Differential Nonlinearity ±1 ±1 LSB Guaranteed monotonic by design

AD5694R

Resolution 12 12 Bits

Relative Accuracy ±0.12 ±2 ±0.12 ±1 LSB

Differential Nonlinearity ±1 ±1 LSB Guaranteed monotonic by design

Zero-Code Error 0.4 4 0.4 1.5 mV All zeros loaded to DAC register

Offset Error +0.1 ±4 +0.1 ±1.5 mV

Full-Scale Error +0.01 ±0.2 +0.01 ±0.1

Gain Error ±0.02 ±0.2 ±0.02 ±0.1

Total Unadjusted Error ±0.01 ±0.25 ±0.01 ±0.1

±0.25 ±0.2

Offset Error Drift

Gain Temperature

Coefficient

DC Power Supply Rejection

Ratio

3

3

3

DC Crosstalk3

±1 ±1 µV/°C

±1 ±1 ppm Of FSR/°C

0.15 0.15 mV/V DAC code = midscale; V

±2 ±2 µV

B Grade

% of

FSR

% of

FSR

% of

FSR

FSR

All ones loaded to DAC register

External reference; gain = 2; TSSOP

Internal reference; gain = 1; TSSOP

= 5 V ± 10%

DD

Due to single channel, full-scale

output change

±2 ±2 µV Due to powering down (per channel)

OUTPUT CHARACTERISTICS3

Output Voltage Range 0 V

0 2 × V

Capacitive Load Stability 2 2 nF RL = ∞

10 10 nF RL = 1 kΩ

Resistive Load4 1 1 kΩ

Load Regulation 80 80 µV/mA

80 80 µV/mA

Short-Circuit Current5 40 40 mA

0 V

REF

0 2 × V

REF

Rev. 0 | Page 3 of 32

V Gain = 1

REF

V Gain = 2, see Figure 31

REF

5 V ± 10%, DAC code = midscale;

−30 mA ≤ I

3 V ± 10%, DAC code = midscale;

−20 mA ≤ I

VDD = 5 V

≤ 30 mA

OUT

≤ 20 mA

OUT

AD5696R/AD5695R/AD5694R Data Sheet

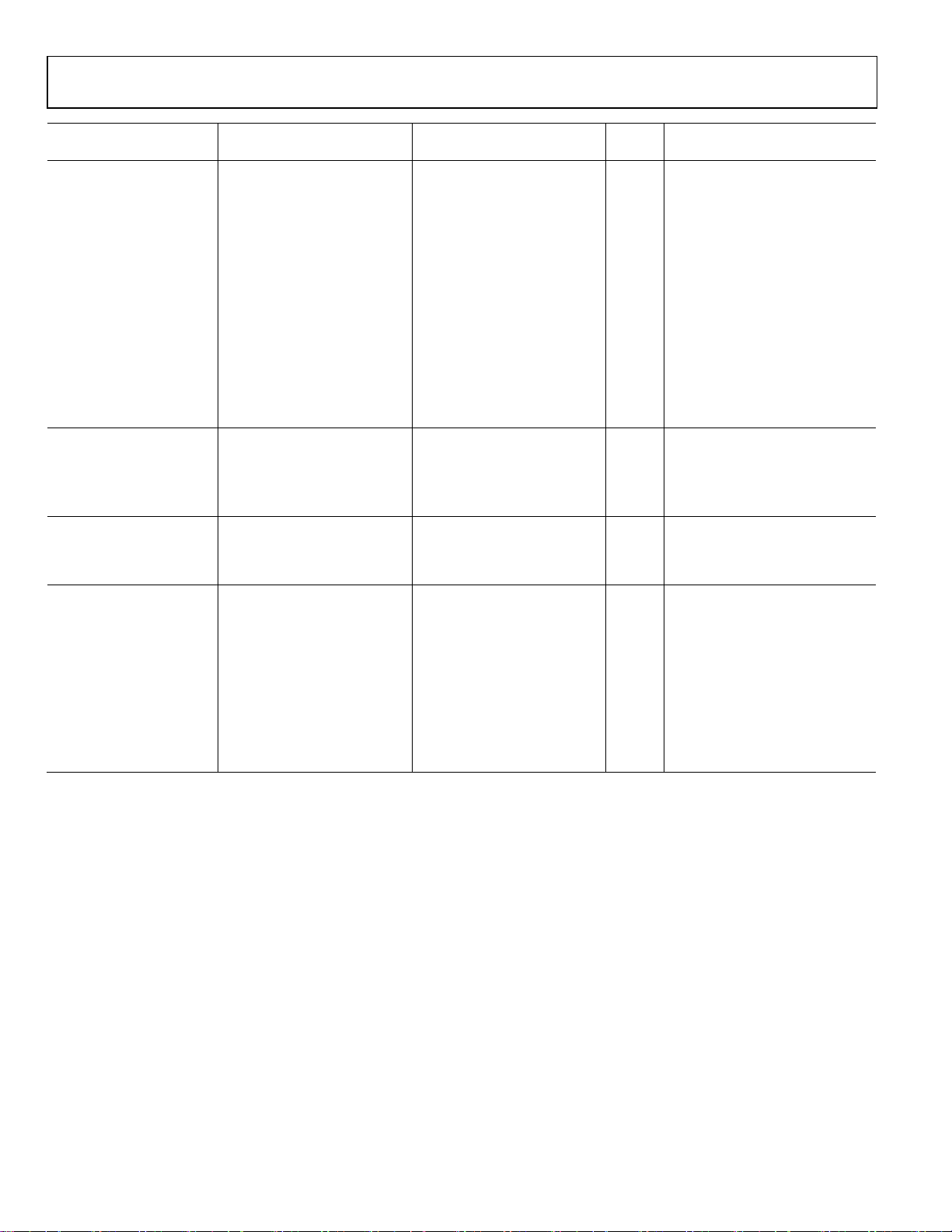

8, 9

20

20

µ

At ambient

125

125 ppm

First cycle

Pin Capacitance

2 2 pF

1

A Grade1

B Grade

Parameter Min Typ Max Min Typ Max Unit Test Conditions/Comments

REFERENCE OUTPUT

Output Voltage7 2.4975 2.5025 2.4975 2.5025 V At ambient

Reference TC

Output Impedance3

Output Voltage Noise3

Output Voltage Noise

Density

Load Regulation Sourcing3

Load Regulation Sinking3

Output Current Load

Capability

Line Regulation3

Long-Term Stability/Drift3

5 20 2 5 ppm/°C See the Terminology section

0.04 0.04 Ω

12 12

3

3

240 240 nV/√Hz

40

±5

40

mA VDD ≥ 3 V

±5

µV p-p

V/mA

µV/mA

0.1 Hz to 10 Hz

At ambient; f = 10 kHz, C

At ambient

100 100 µV/V At ambient

12 12 ppm After 1000 hours at 125°C

= 10 nF

L

Thermal Hysteresis3

25 25 ppm Additional cycles

LOGIC INPUTS3

Input Current ±2 ±2 µA Per pin

V

, Input Low Voltage 0.3 × V

INL

V

, Input High Voltage 0.7 × V

INH

LOGIC OUTPUTS (SDA)3

0.7 × V

LOGIC

Output Low Voltage, VOL 0.4 0.4 V I

Floating State Output

4 4 pF

0.3 × V

LOGIC

V

LOGIC

V

LOGIC

SINK

= 3 mA

Capacitance

POWER REQUIREMENTS

V

I

LOGIC

LOGIC

1.8 5.5 1.8 5.5 V

3 3

µA

VDD 2.7 5.5 2.7 5.5 V Gain = 1

VDD V

+ 1.5 5.5 V

REF

+ 1.5 5.5 V Gain = 2

REF

IDD VIH = VDD, VIL = GND, VDD = 2.7 V to 5.5 V

Normal Mode10 0.59 0.7 0.59 0.7 mA Internal reference off

1.1 1.3 1.1 1.3 mA Internal reference on, at full scale

All Power-Down

11

Modes

1 4 1 4 µA −40°C to +85°C

6 6 µA −40°C to +105°C

1

Temperature range: A and B grade: −40°C to +105°C.

2

DC specifications tested with the outputs unloaded, unless otherwise noted. Upper dead band = 10 mV and exists only when V

with gain = 2. Linearity calculated using a reduced code range of 256 to 65,280 (AD5696R), 64 to 16,320 (AD5695R), and 12 to 4080 (AD5694R).

V

DD

3

Guaranteed by design and characterization; not production tested.

4

Channel A and Channel B can have a combined output current of up to 30 mA. Similarly, Channel C and Channel D can have a combined output current of up to

30 mA up to a junction temperature of 110°C.

5

VDD = 5 V. The device includes current limiting that is intended to protect the device during temporary overload conditions. Junction temperature can be exceeded

during current limit. Operation above the specified maximum operation junction temperature may impair device reliability.

6

When drawing a load current at either rail, the output voltage headroom with respect to that rail is limited by the 25 Ω typical channel resistance of the output

devices. For example, when sinking 1 mA, the minimum output voltage = 25 Ω × 1 mA = 25 mV (see Figure 31).

7

Initial accuracy presolder reflow is ±750 µV; output voltage includes the effects of preconditioning drift. See the Internal Reference Setup section.

8

Reference is trimmed and tested at two temperatures and is characterized from −40°C to +105°C.

9

Reference temperature coefficient calculated as per the box method. See the Terminology section for further information.

10

Interface inactive. All DACs active. DAC outputs unloaded.

11

All DACs powered down.

= VDD with gain = 1 or when V

REF

/2 =

REF

Rev. 0 | Page 4 of 32

Data Sheet AD5696R/AD5695R/AD5694R

Total Harmonic Distortion4

−80 dB

At ambient, BW = 20 kHz, VDD = 5 V, f

= 1 kHz

AC CHARACTERISTICS

VDD = 2.7 V to 5.5 V; RL = 2 kΩ to GND; CL = 200 pF to GND; 1.8 V ≤ V

1

noted.

Table 3.

Parameter2 Min Typ Max Unit Test Conditions/Comments3

Output Voltage Settling Time

AD5696R 5 8 µs ¼ to ¾ scale settling to ±2 LSB

AD5695R 5 8 µs ¼ to ¾ scale settling to ±2 LSB

AD5694R 5 7 µs ¼ to ¾ scale settling to ±2 LSB

Slew Rate 0.8 V/µs

Digital-to-Analog Glitch Impulse 0.5 nV-sec 1 LSB change around major carry

Digital Feedthrough 0.13 nV-sec

Digital Crosstalk 0.1 nV-sec

Analog Crosstalk 0.2 nV-sec

DAC-to-DAC Crosstalk 0.3 nV-sec

Output Noise Spectral Density 300 nV/√Hz DAC code = midscale, 10 kHz; gain = 2

Output Noise 6 µV p-p 0.1 Hz to 10 Hz

SNR 90 dB At ambient, BW = 20 kHz, VDD = 5 V, f

SFDR 83 dB At ambient, BW = 20 kHz, VDD = 5 V, f

SINAD 80 dB At ambient, BW = 20 kHz, VDD = 5 V, f

1

Guaranteed by design and characterization; not production tested.

2

See the Terminology section.

3

Temperature range is −40°C to +105°C, typical @ 25°C.

4

Digitally generated sine wave @ 1 kHz.

≤ 5.5 V; all specifications T

LOGIC

MIN

to T

, unless otherwise

MAX

OUT

= 1 kHz

OUT

= 1 kHz

OUT

= 1 kHz

OUT

Rev. 0 | Page 5 of 32

AD5696R/AD5695R/AD5694R Data Sheet

SCL

SDA

t

1

t

3

LDAC

1

LDAC

2

START

CONDITION

REPEATED START

CONDITION

STOP

CONDITION

NOTES

1

ASYNCHRONOUS LDAC UPDATE MO DE .

2

SYNCHRONOUS LDAC UPDATE MO DE .

t

4

t

6

t

5

t

7

t

8

t

2

t

13

t

4

t

11

t

10

t

12

t

12

t

9

10486-002

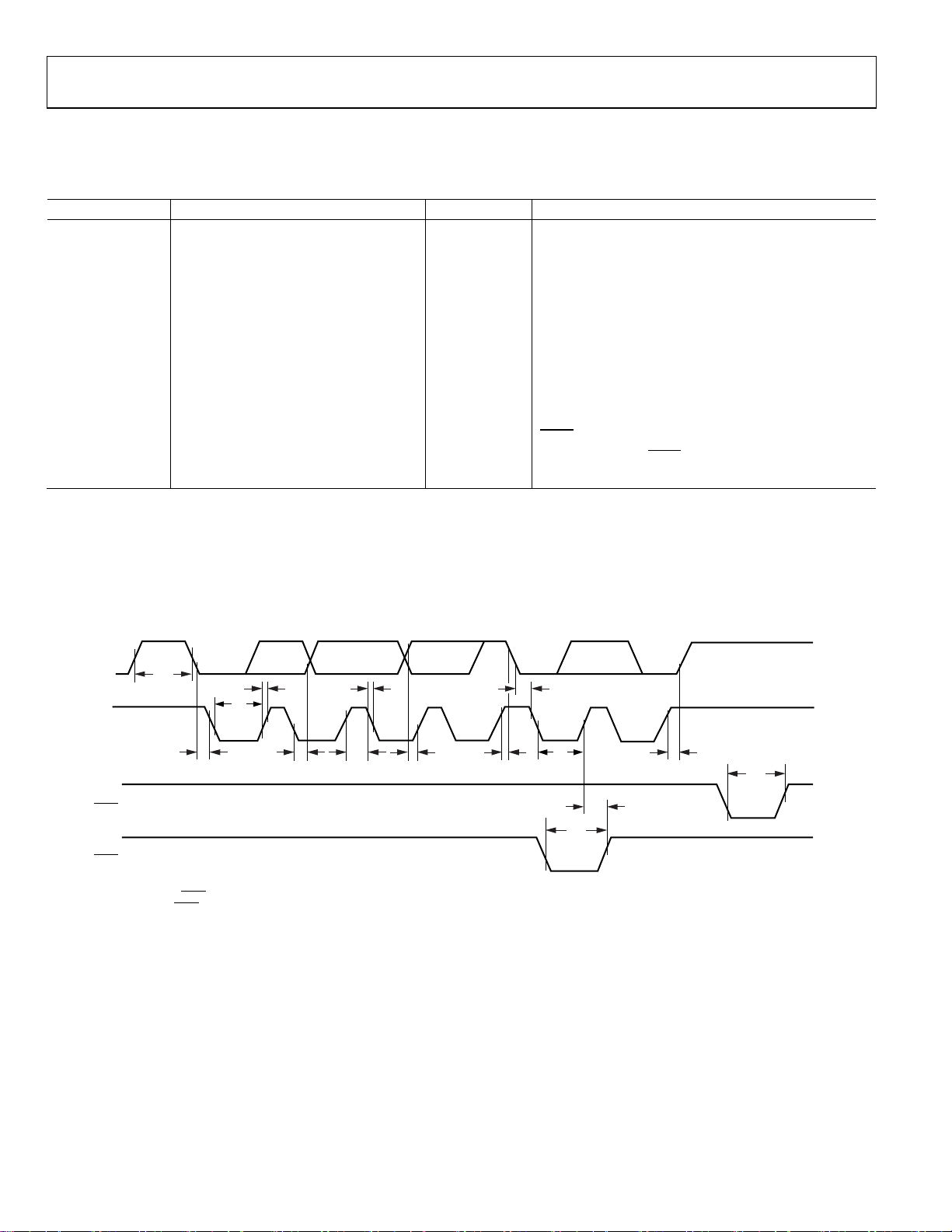

TIMING CHARACTERISTICS

VDD = 2.5 V to 5.5 V; 1.8 V ≤ V

Table 4.

Parameter2

Min Max

t1 2.5 µs SCL cycle time

t2 0.6 µs t

t3 1.3 µs t

t4 0.6 µs t

t5 100 ns t

3

t

0 0.9 µs t

6

t7 0.6 µs t

t8 0.6 µs t

t9 1.3 µs t

t10 0 300 ns tR, rise time of SCL and SDA when receiving

t11 20 + 0.1C

t12 20 ns

t13 400 ns SCL rising edge to

4

C

400 pF Capacitive load for each bus line

B

1

See Figure 2.

2

Guaranteed by design and characterization; not production tested.

3

A master device must provide a hold time of at least 300 ns for the SDA signal (referred to the VIH min of the SCL signal) to bridge the undefined region of SCL’s

falling edge.

4

CB is the total capacitance of one bus line in pF. tR and tF measured between 0.3 VDD and 0.7 VDD.

≤ 5.5 V; all specifications T

LOGIC

MIN

to T

, unless otherwise noted. 1

MAX

Unit Conditions/Comments

, SCL high time

HIGH

, SCL low time

LOW

, start/repeated start condition hold time

HD, STA

, data setup time

SU ,DAT

, data hold time

HD ,DAT

, setup time for repeated start

SU, STA

, stop condition setup time

SU,ST O

, bus free time between a stop and a start condition

BUF

4

300 ns tF, fall time of SDA and SCL when transmitting/ receiving

B

pulse width

LDAC

rising edge

LDAC

Figure 2. 2-Wire Serial Interface Timing Diagram

Rev. 0 | Page 6 of 32

Data Sheet AD5696R/AD5695R/AD5694R

ABSOLUTE MAXIMUM RATINGS

TA = 25°C, unless otherwise noted.

Table 5.

Parameter Rating

VDD to GND −0.3 V to +7 V

V

to GND −0.3 V to +7 V

LOGI C

V

to GND −0.3 V to VDD + 0.3 V

OUT

V

to GND −0.3 V to VDD + 0.3 V

REF

Digital Input Voltage to GND1 −0.3 V to V

LOGI C

+ 0.3 V

SDA and SCL to GND −0.3 V to +7 V

Operating Temperature Range −40°C to +105°C

Storage Temperature Range −65°C to +150°C

Junction Temperature 125°C

16-Lead TSSOP, θJA Thermal

112.6°C/W

Impedance, 0 Airflow (4-Layer Board)

16-Lead LFCSP, θJA Thermal

70°C/W

Impedance, 0 Airflow (4-Layer Board)

Reflow Soldering Peak

260°C

Temperature, Pb Free (J-STD-020)

ESD2 3.5 kV

FICDM 1.5 kV

1

Excluding SDA and SCL.

2

Human body model (HBM) classification.

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

Rev. 0 | Page 7 of 32

AD5696R/AD5695R/AD5694R Data Sheet

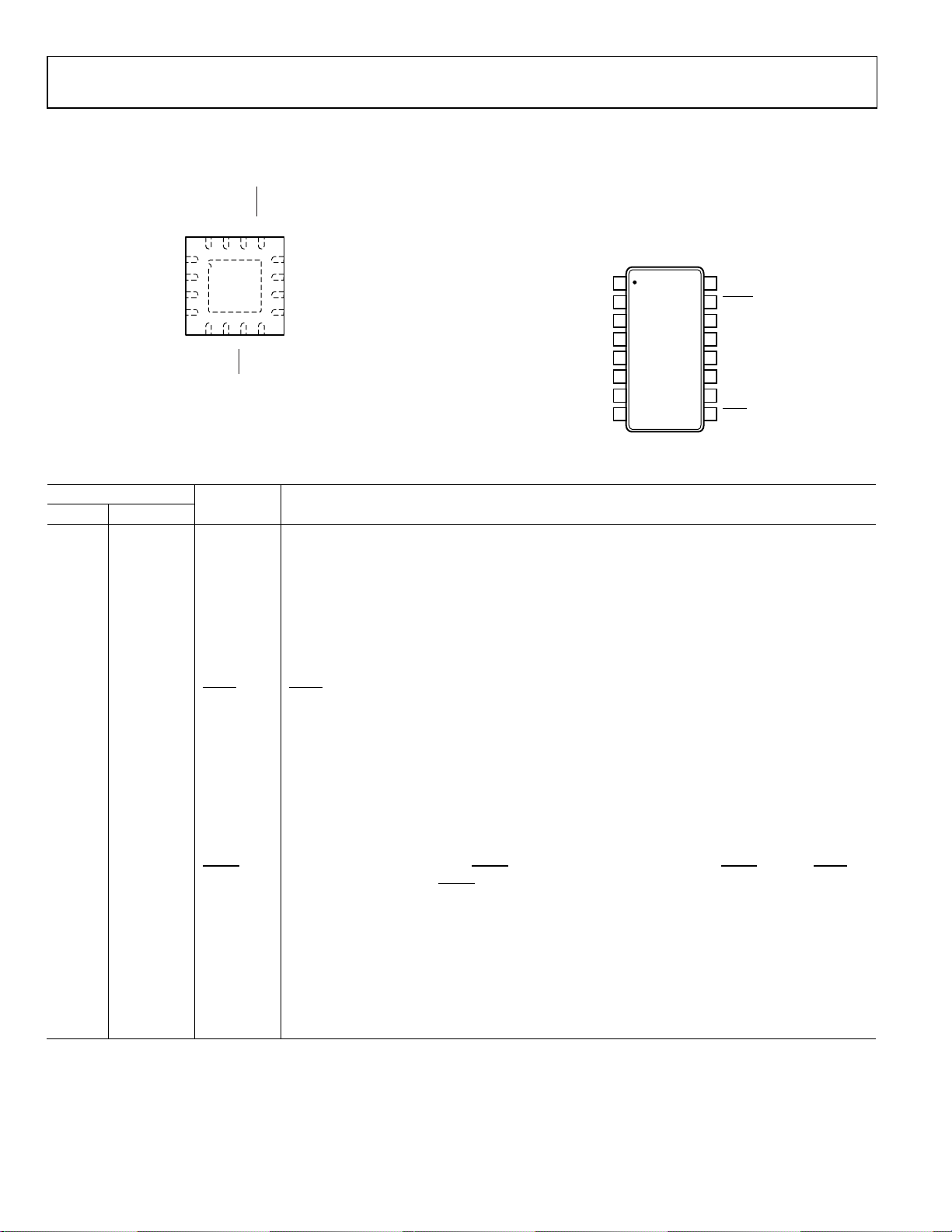

Pin No.

Power-On Reset Pin. Tying this pin to GND powers up all four DACs to zero scale. Tying this pin to

VDD powers up all four DACs to midscale.

12

11

10

1

3

4

A1

SCL

A0

9

V

LOGIC

V

OUT

A

V

DD

2

GND

V

OUT

C

6

SDA

5

V

OUT

D

7

LDAC

8

GAIN

16

V

OUT

B

15

V

REF

14

RSTSEL

13

RESET

AD5696R/AD5695R/AD5694R

NOTES

1. THE EXPOSED PAD MUST BE TIED TO GND.

TOP VIEW

(Not to S cale)

10486-006

1

2

3

4

5

6

7

8

V

OUT

B

V

OUT

A

GND

V

OUT

D

V

OUT

C

V

DD

V

REF

SDA

16

15

14

13

12

11

10

9

RESET

A1

SCL

GAIN

LDAC

V

LOGIC

A0

RSTSEL

TOP VIEW

(Not to S cale)

AD5696R/

AD5695R/

AD5694R

10486-007

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. 16-Lead LFCSP Pin Configuration

Figure 4. 16-Lead TSSOP Pin Configuration

Table 6. Pin Function Descriptions

Mnemonic Description LFCSP TSSOP

1 3 V

A Analog Output Voltage from DAC A. The output amplifier has rail-to-rail operation.

OUT

2 4 GND Ground Reference Point for All Circuitry on the Part.

3 5 VDD Power Supply Input. These parts can be operated from 2.7 V to 5.5 V, and the supply should be

decoupled with a 10 µF capacitor in parallel with a 0.1 µF capacitor to GND.

4 6 V

5 7 V

C Analog Output Voltage from DAC C. The output amplifier has rail-to-rail operation.

OUT

D Analog Output Voltage from DAC D. The output amplifier has rail-to-rail operation.

OUT

6 8 SDA Serial Data Input. This pin is used in conjunction with the SCL line to clock data into or out of the

24-bit input shift register. SDA is a bidirectional, open-drain data line that should be pulled to the

supply with an external pull-up resistor.

7 9

LDAC

can be operated in two modes, asynchronously and synchronously. Pulsing this pin low allows

LDAC

any or all DAC registers to be updated if the input registers have new data. This allows all DAC outputs

to simultaneously update. This pin can also be tied permanently low.

8 10 GAIN Span Set Pin. When this pin is tied to GND, all four DAC outputs have a span from 0 V to V

9 11 V

pin is tied to V

Digital Power Supply. Voltage ranges from 1.8 V to 5.5 V.

LOGIC

, all four DACs output a span of 0 V to 2 × V

DD

REF

.

. If this

REF

10 12 A0 Address Input. Sets the first LSB of the 7-bit slave address.

11 13 SCL Serial Clock Line. This is used in conjunction with the SDA line to clock data into or out of the 24-bit

input register.

12 14 A1 Address Input. Sets the second LSB of the 7-bit slave address.

13 15

Asynchronous Reset Input. The

RESET

pulses are ignored. When

input is falling edge sensitive. When

RESET

is activated, the input register and the DAC register are updated

RESET

RESET

is low, all

LDAC

with zero scale or midscale, depending on the state of the RSTSEL pin.

14 16 RSTSEL

15 1 V

16 2 V

17 N/A EPAD Exposed Pad. The exposed pad must be tied to GND.

Reference Voltage. The AD5696R/AD5695R/AD5694R have a common reference pin. When using

REF

the internal reference, this is the reference output pin. When using an external reference, this is the

reference input pin. The default for this pin is as a reference output.

B Analog Output Voltage from DAC B. The output amplifier has rail-to-rail operation.

OUT

Rev. 0 | Page 8 of 32

Data Sheet AD5696R/AD5695R/AD5694R

–40 –20 0 20 40 60 80 100 120

V

REF

(V)

TEMPERATURE (°C)

DEVICE 1

DEVICE 2

DEVICE 3

DEVICE 4

DEVICE 5

2.4980

2.4985

2.4990

2.4995

2.5000

2.5005

2.5010

2.5015

2.5020

VDD = 5V

10486-212

–40 –20 0 20 40 60 80 120100

V

REF

(V)

TEMPERATURE (°C)

DEVICE 1

DEVICE 2

DEVICE 3

DEVICE 4

DEVICE 5

2.4980

2.4985

2.4990

2.4995

2.5000

2.5005

2.5010

2.5015

2.5020

VDD = 5V

10486-109

90

0

10

20

30

40

50

60

70

80

0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0

NUMBER OF UNI TS

TEMPERAT URE DRIFT (p pm/°C)

VDD = 5V

10486-250

60

0

10

20

30

40

50

2.498 2.499 2.500 2.501 2.502

HITS

V

REF

(V)

0 HOUR

168 HOURS

500 HOURS

1000 HOURS

V

DD

= 5.5V

10486-251

1600

0

200

400

600

800

1000

1200

1400

10 100 1k 10k 100k 1M

NSD (nV/ Hz)

FREQUENCY (MHz)

VDD = 5V

T

A

= 25°C

10486-111

CH1 10µV M1.0s A CH1 160mV

1

T

VDD = 5V

T

A

= 25°C

10486-112

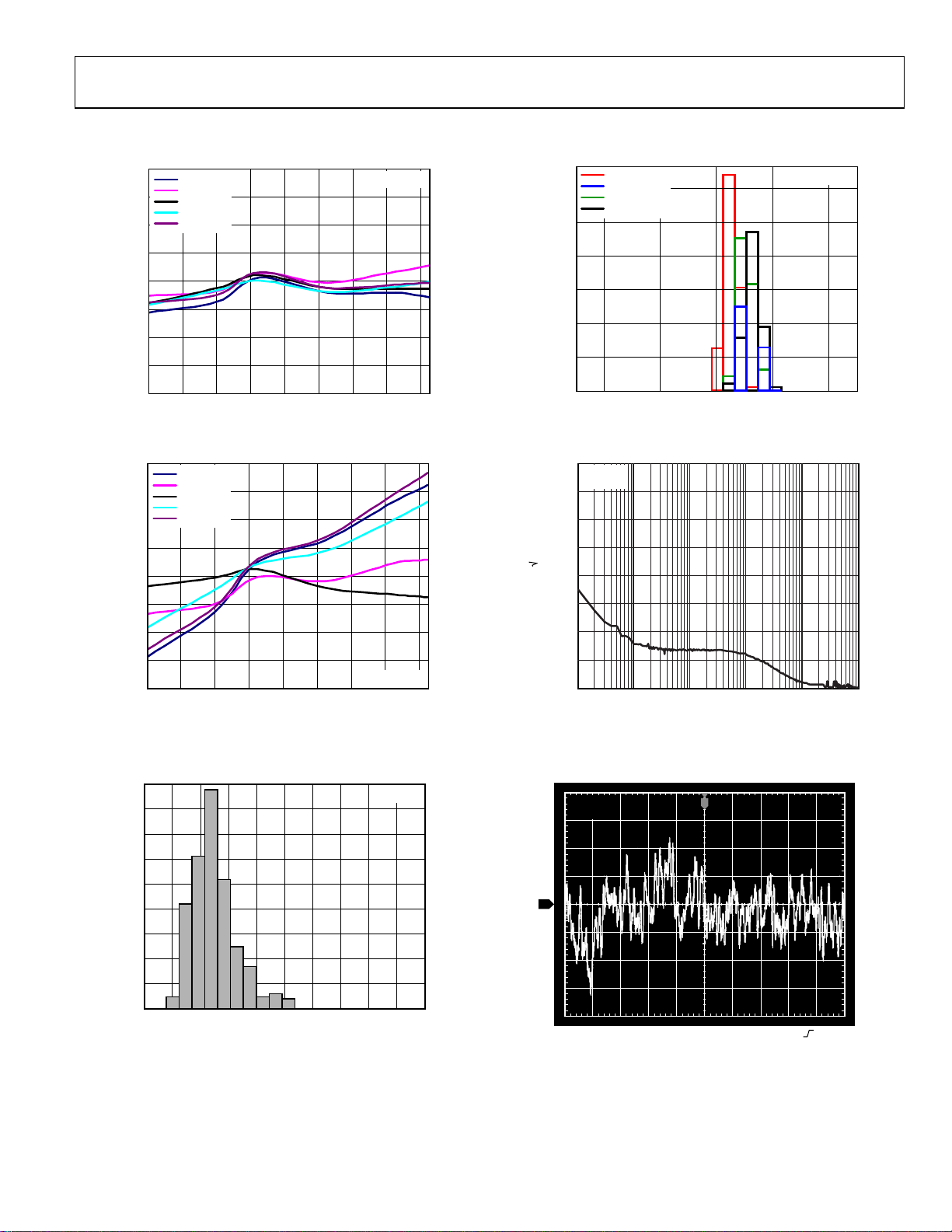

TYPICAL PERFORMANCE CHARACTERISTICS

Figure 5. Internal Reference Voltage vs. Temperature (Grade B)

Figure 6. Internal Reference Voltage vs. Temperature (Grade A)

Figure 8. Reference Long-Term Stability/Drift

Figure 9. Internal Reference Noise Spectral Density vs. Frequency

Figure 7. Reference Output Temperature Drift Histogram

Figure 10. Internal Reference Noise, 0.1 Hz to 10 Hz

Rev. 0 | Page 9 of 32

AD5696R/AD5695R/AD5694R Data Sheet

2.5000

2.4999

2.4998

2.4997

2.4996

2.4995

2.4994

2.4993

–0.005 –0.003 –0.001 0.001 0.003 0.005

V

REF

(V)

I

LOAD

(A)

VDD = 5V

T

A

= 25°C

10486-113

2.5002

2.5000

2.4998

2.4996

2.4994

2.4992

2.4990

2.5 3.0 3.5 4.0 4.5 5.0 5.5

V

REF

(V)

VDD (V)

D1

D3

D2

T

A

= 25°C

10486-117

10

–10

–8

–6

–4

–2

0

2

4

8

6

0 10000 20000 30000 40000 50000 60000

INL (LSB)

CODE

VDD = 5V

T

A

= 25°C

INTERNAL RE FERENCE = 2.5V

10486-118

10

–10

–8

–6

–4

–2

0

2

4

8

6

0 2500 5000 7500 10000 12500 1500016348

INL (LSB)

CODE

VDD = 5V

T

A

= 25°C

INTERNAL RE FERENCE = 2.5V

10486-119

10

–10

–8

–6

–4

–2

0

2

4

8

6

0 625 1250 1875 2500 3125 3750 4096

INL (LSB)

CODE

VDD = 5V

T

A

= 25°C

INTERNAL RE FERENCE = 2.5V

10486-120

1.0

–1.0

–0.8

–0.6

–0.4

–0.2

0

0.2

0.4

0.8

0.6

0 10000 20000 30000 40000 50000 60000

DNL (LSB)

CODE

VDD = 5V

T

A

= 25°C

INTERNAL RE FERENCE = 2.5V

10486-121

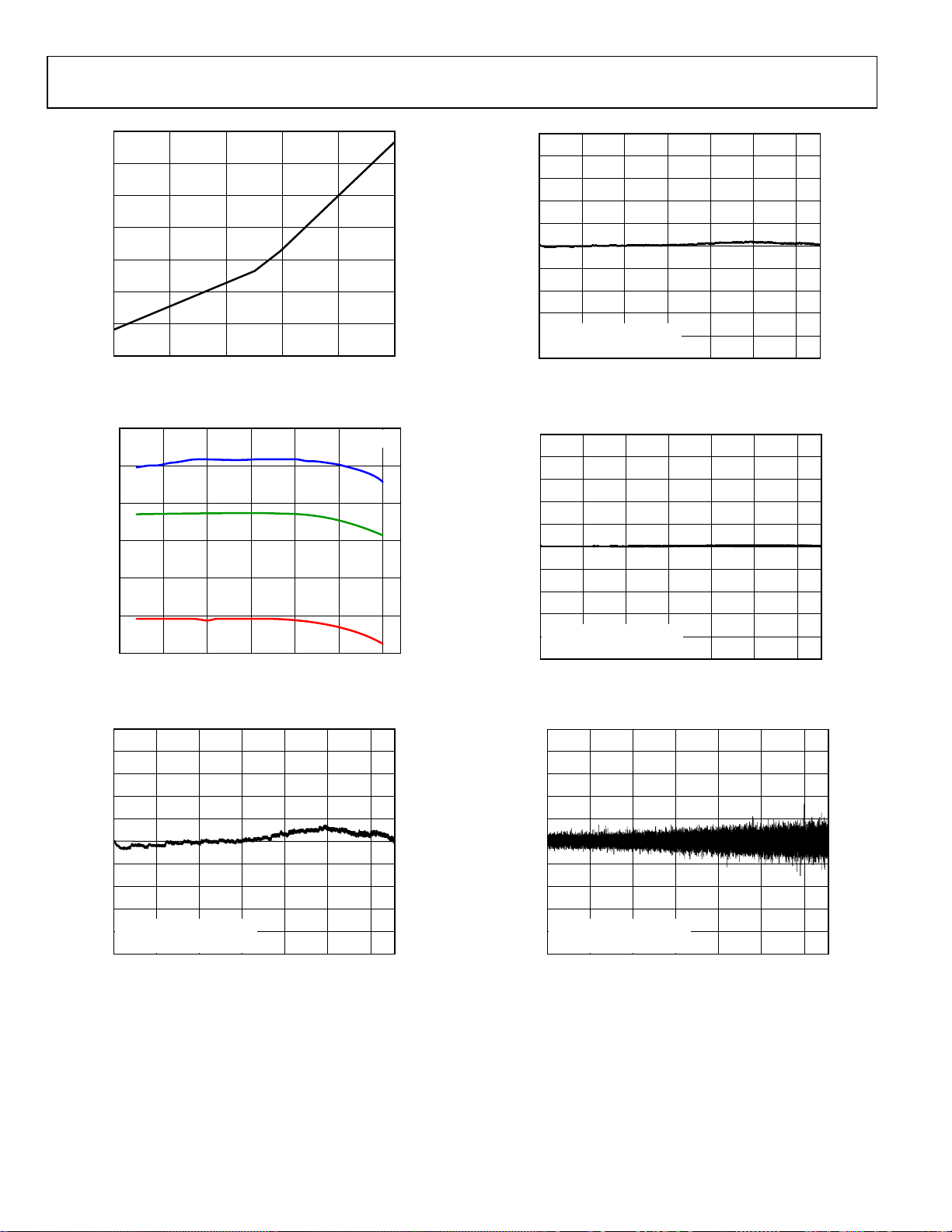

Figure 11. Internal Reference Voltage vs. Load Current

Figure 12. Internal Reference Voltage vs. Supply Voltage

Figure 14. AD5695R INL

Figure 15. AD5694R INL

Figure 13. AD5696R INL

Figure 16. AD5696R DNL

Rev. 0 | Page 10 of 32

Loading...

Loading...