S

查询AD5426供应商

8-/10-/12-Bit High Bandwidth

Multiplying DACs with Serial Interface

FEATURES

3.0 V to 5.5 V Supply Operation

50 MHz Serial Interface

10 MHz Multiplying Bandwidth

ⴞ10 V Reference Input

Low Glitch Energy < 2 nV-s

Extended Temperature Range –40ⴗC to +125ⴗC

10-Lead MSOP Package

Pin Compatible 8-, 10-, and 12-Bit Current

Output DACs

Guaranteed Monotonic

4-Quadrant Multiplication

Power-On Reset with Brownout Detection

Daisy-chain Mode

Readback Function

0.4 A Typical Power Consumption

APPLICATIONS

Portable Battery-Powered Applications

Waveform Generators

Analog Processing

Instrumentation Applications

Programmable Amplifiers and Attenuators

Digitally Controlled Calibration

Programmable Filters and Oscillators

Composite Video

Ultrasound

Gain, Offset, and Voltage Trimming

GENERAL DESCRIPTION

The AD5426/AD5432/AD5443 are CMOS 8-, 10-, and 12-bit

current output digital-to-analog converters, respectively.

These devices operate from a 3.0 V to 5.5 V power supply,

making them suited to battery-powered applications and many

other applications.

These DACs utilize double buffered 3-wire serial interface that

is compatible with SPI

®

, QSPI™, MICROWIRE™, and most

DSP interface standards. In addition, a serial data out pin (SDO)

allows for daisy-chaining when multiple packages are used. Data

readback allows the user to read the contents of the DAC register

via the SDO pin. On power-up, the internal shift register and

latches are filled with 0s and the DAC outputs are at zero scale.

As a result of manufacture on a CMOS submicron process, they

offer excellent 4-quadrant multiplication characteristics, with

large signal multiplying bandwidths of 10 MHz.

AD5426/AD5432/AD5443

*

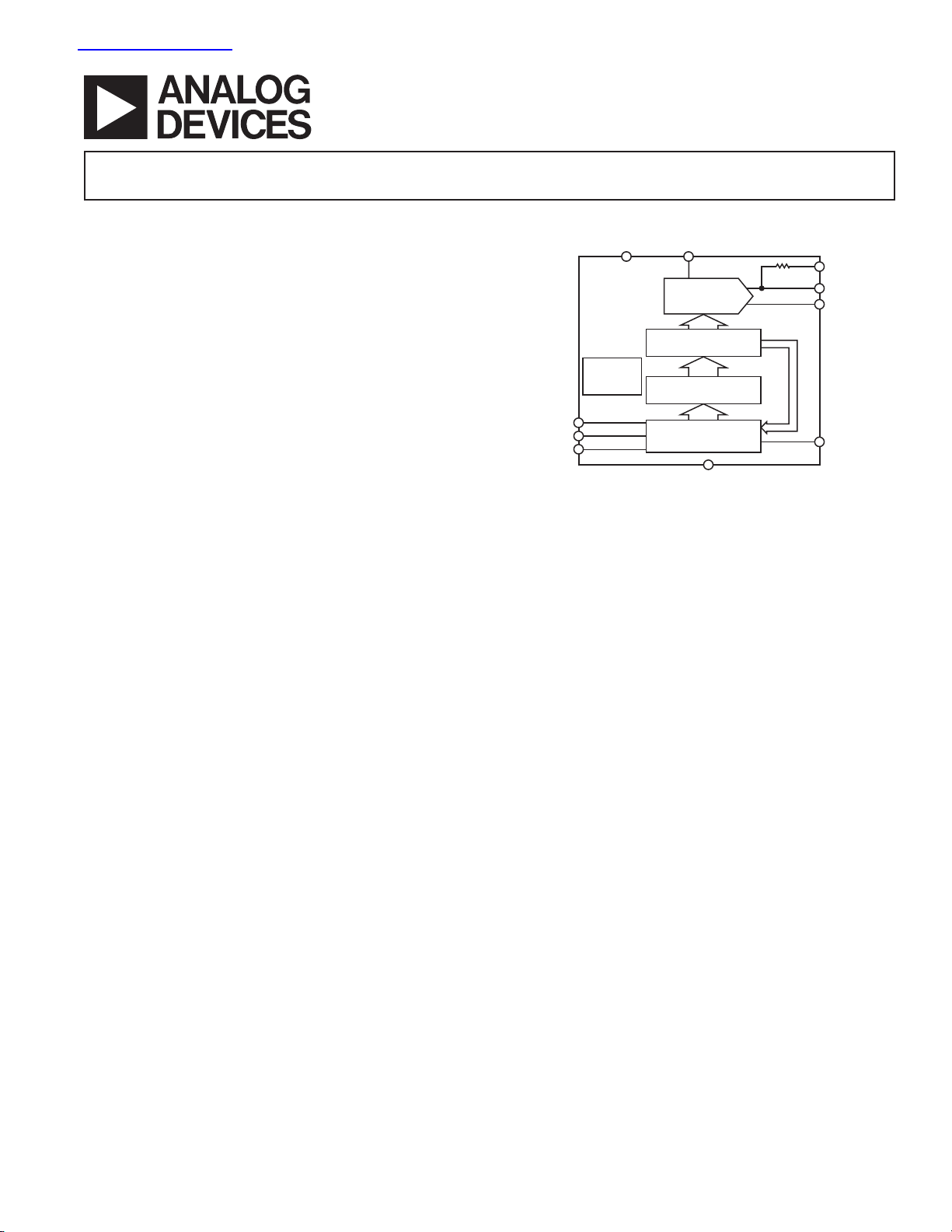

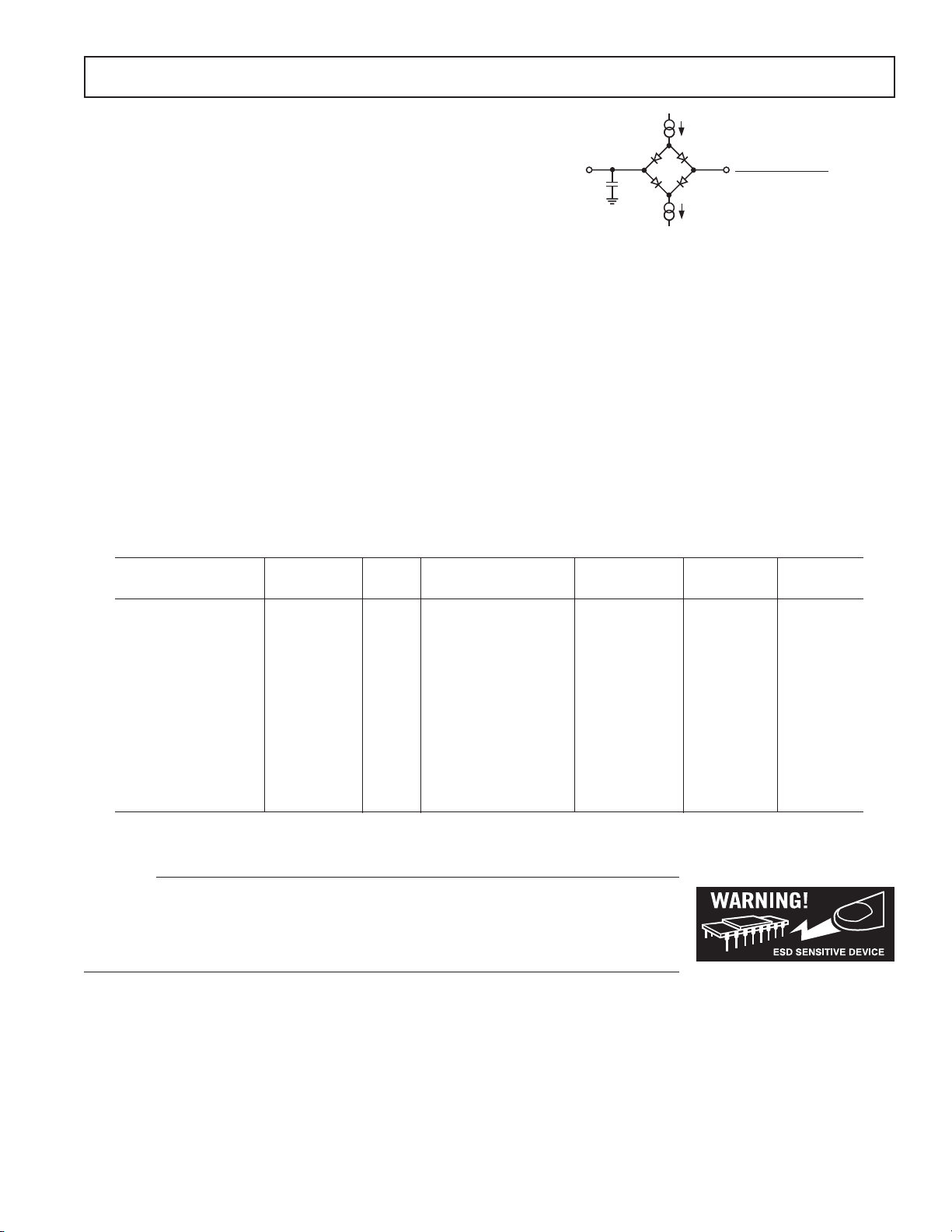

FUNCTIONAL BLOCK DIAGRAM

V

DD

AD5426/

AD5432/

AD5443

POWER-ON

RESET

YNC

SCLK

SDIN

The applied external reference input voltage (V

the full-scale output current. An integrated feedback resistor (R

V

REF

8-/10-/12-BIT

R-2R DAC

DAC REGISTER

INPUT LATCH

CONTROL LOGIC AND

INPUT SHIFT REGISTER

GND

R

) determines

REF

R

FB

I

OUT

I

OUT

SDO

1

2

)

FB

provides temperature tracking and full-scale voltage output when

combined with an external current to voltage precision amplifier.

The AD5426/AD5432/AD5443 DACs are available in small

10-lead MSOP packages.

*U.S. Patent No. 5,689,257

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © 2004 Analog Devices, Inc. All rights reserved.

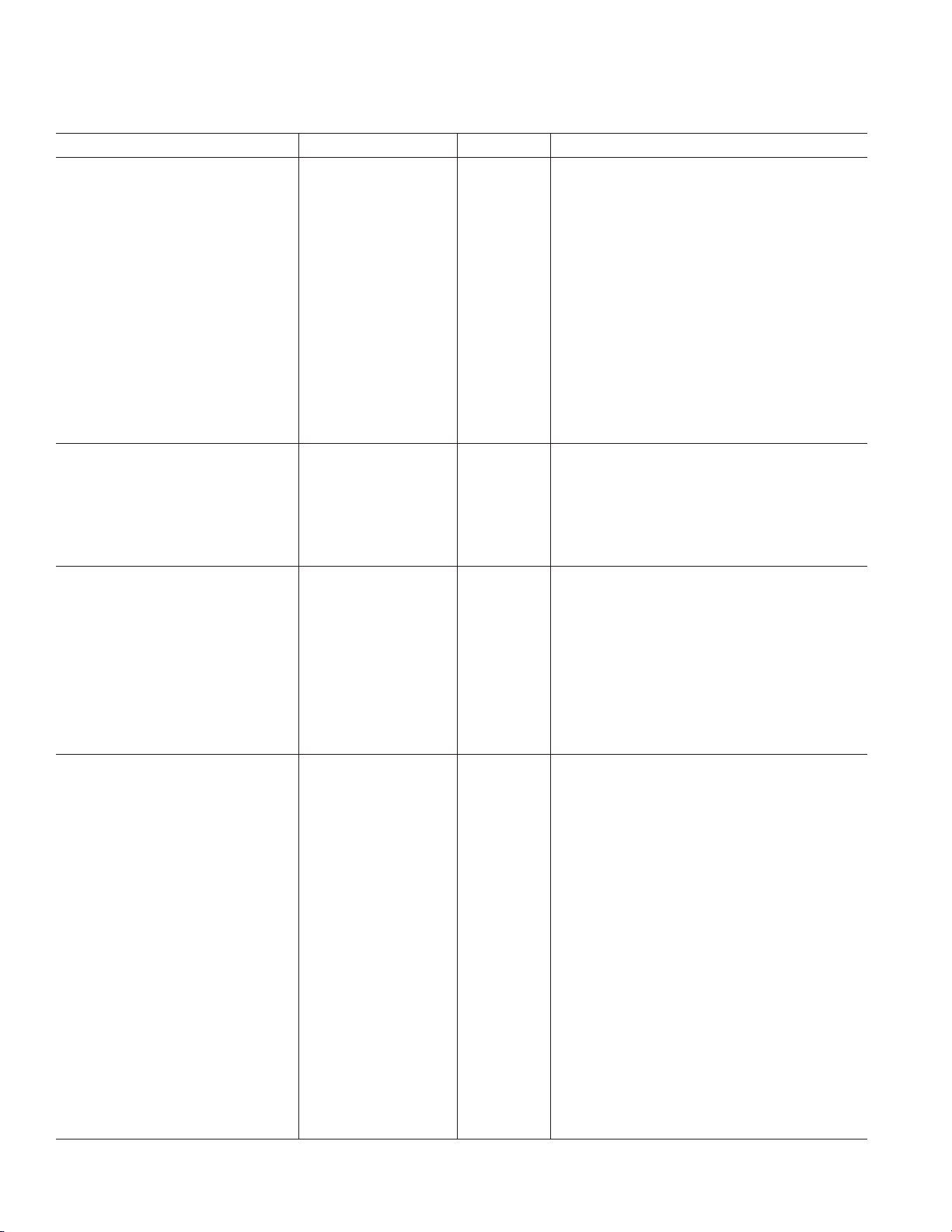

AD5426/AD5432/AD5443–SPECIFICATIONS

1

(VDD = 3 V to 5.5 V, V

performance with AD8038, unless otherwise noted.)

Parameter Min Typ Max Unit Conditions

STATIC PERFORMANCE

AD5426

Resolution 8 Bits

Relative Accuracy ±0.25 LSB

Differential Nonlinearity ±0.5 LSB Guaranteed monotonic

AD5432

Resolution 10 Bits

Relative Accuracy ±0.5 LSB

Differential Nonlinearity ±1 LSB Guaranteed monotonic

AD5443

Resolution 12 Bits

Relative Accuracy ±1 LSB

Differential Nonlinearity –1/+2 LSB Guaranteed monotonic

Gain Error ±10 mV

Gain Error Temperature Coefficient

Output Leakage Current ±5nA Data = 0x0000, T

REFERENCE INPUT

Reference Input Range ±10 V

Input Resistance 8 10 12 kΩ Input resistance TC = –50 ppm/°C

V

REF

Resistance 8 10 12 kΩ Input resistance TC = –50 ppm/°C

R

FB

Input Capacitance

Code All 0s 3 6 pF

Code All 1s 5 8 pF

DIGITAL INPUTS/OUTPUT

Input High Voltage, V

Input Low Voltage, V

Input Leakage Current, I

Input Capacitance 4 10 pF

= 4.5 V to 5.5 V

V

DD

Output Low Voltage, V

Output High Voltage, V

= 3 V to 3.6 V

V

DD

Output Low Voltage, V

Output High Voltage, V

DYNAMIC PERFORMANCE

Reference Multiplying Bandwidth 10 MHz V

Output Voltage Settling Time V

AD5426 50 100 ns Measured to ±16 mV of full scale

AD5432 55 110 ns Measured to ±4 mV of full scale

AD5443 90 160 ns Measured to ± 1 mV of full scale

Digital Delay 40 75 ns Interface Delay Time

10% to 90% Rise/Fall Time 15 30 ns Rise and fall time, V

Digital-to-Analog Glitch Impulse 2 nV-s 1 LSB change around major carry, V

Multiplying Feedthrough Error DAC latch loaded with all 0s. V

Output Capacitance

22225pF All 0s loaded

I

OUT

11217pF All 0s loaded

I

OUT

Digital Feedthrough 0.1 nV-s Feedthrough to DAC output with SYNC high and

Total Harmonic Distortion –81 dB V

Digital THD Clock = 1 MHz

50 kHz f

Output Noise Spectral Density 25 nV/√Hz @ 1 kHz

OUT

= 10 V, I

REF

2

IL

x = O V. All specifications T

OUT

2

2

IH

1.7 V

±5 ppm FSR/°C

to T

MIN

, unless otherwise noted. DC performance measured with OP177, AC

MAX

±25 nA Data = 0x0000, I

= 25°C, I

A

OUT

OUT

0.6 V

IL

OL

OH

OL

OH

2

VDD – 1 V I

VDD – 0.5 V I

2 A

0.4 V I

0.4 V I

= 200 A

SINK

= 200 A

SOURCE

= 200 A

SINK

= 200 A

SOURCE

= ±3.5 V; DAC loaded all 1s

REF

= 10 V; R

REF

= 100 Ω, C

LOAD

REF

= 10 V, R

LOAD

LOAD

= ±3.5 V

REF

= 15 pF

= 100 Ω

= 0 V

REF

70 dB 1 MHz

48 dB 10 MHz

10 12 pF All 1s loaded

25 30 pF All 1s loaded

alternate loading of all 0s and all 1s

= 3.5 V pk-pk; all 1s loaded, f = 1 kHz

REF

73 dB

REV. 0–2–

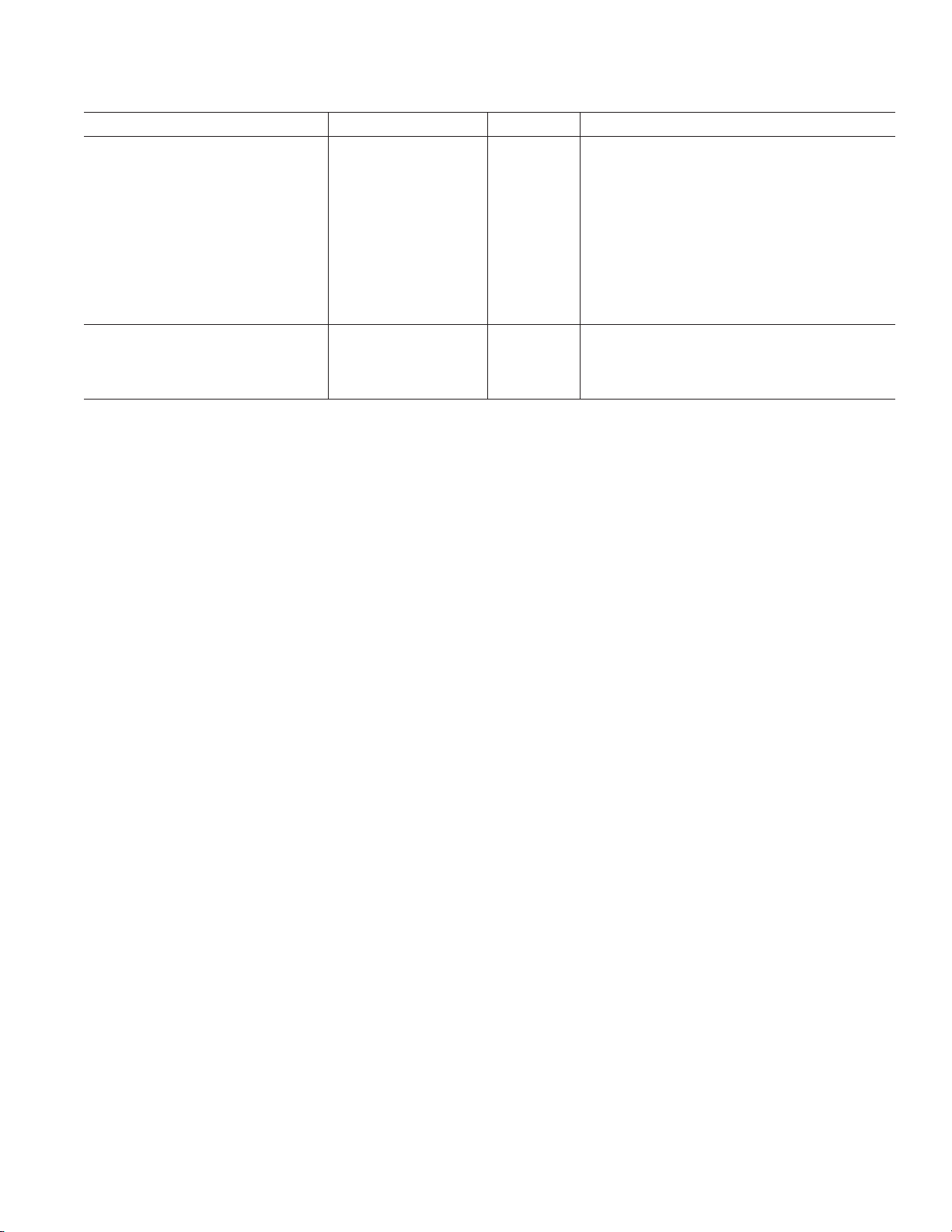

AD5426/AD5432/AD5443

Parameter Min Typ Max Unit Conditions

SFDR Performance (Wide Band) AD5443, 4096 codes V

Clock = 10 MHz

50 kHz f

20 kHz f

OUT

OUT

SFDR Performance (Narrow Band)

Clock = 1 MHz

50 kHz f

20 kHz f

OUT

OUT

Intermodulation Distortion

Clock = 1 MHz

f1 = 20 kHz, f2 = 25 kHz 78 dB

POWER REQUIREMENTS

Power Supply Range 3.0 5.5 V

I

DD

NOTES

1

Temperature range is as follows: Y version: –40°C to +125°C.

2

Guaranteed by design and characterization, not subject to production test.

Specifications subject to change without notice.

75 dB

76 dB

87 dB

87 dB

0.4 5 A Logic inputs = 0 V or V

0.6 AT

= 25°C, logic inputs = 0 V or V

A

= 3.5 V

REF

DD

DD

REV. 0

–3–

AD5426/AD5432/AD5443

S

S

1

TIMING CHARACTERISTICS

(VDD = 3 V to 5.5 V, V

Parameter 3.0 V to 5.5 V 4.5 V to 5.5 V Unit Conditions/Comments

f

SCLK

t

1

t

2

t

3

2

t

4

t

5

t

6

t

7

t

8

3

t

9

50 50 MHz max Max clock frequency

20 20 ns min SCLK cycle time

88 ns min SCLK high time

88 ns min SCLK low time

13 13 ns min SYNC falling edge to SCLK active edge setup time

55 ns min Data setup time

33 ns min Data hold time

55 ns min SYNC rising edge to SCLK active edge

30 30 ns min Minimum SYNC high time

80 45 ns typ SCLK active edge to SDO valid

120 65 ns max

NOTES

1

See Figures 1 and 2. Temperature range is as follows: Y version: –40°C to +125°C. Guaranteed by design and characterization, not subject to production test.

All input signals are specified with tr = tf = 1 ns (10% to 90% of VDD) and timed from a voltage level of (VIL + VIH)/2.

2

Falling or rising edge as determined by control bits of serial word.

3

Daisy-chain and readback modes cannot operate at max clock frequency. SDO timing specifications measured with load circuit as shown in Figure 3.

Specifications subject to change without notice.

SCLK

t

2

YNC

t

8

t

4

= 10 V, I

REF

t

1

t

3

2 = O V. All specifications T

OUT

t

7

MIN

to T

, unless otherwise noted.)

MAX

t

6

t

DIN

ALTERNATIVELY, DATA MAY BE CLOCKED INTO INPUT SHIFT REGISTER ON RISING EDGE OF

SCLK AS DETERMINED BY CONTROL BITS. TIMING AS PER ABOVE, WITH SCLK INVERTED.

DB15 DB0

5

Figure 1. Standalone Mode Timing Diagram

t

1

SCLK

t

t

4

YNC

t

6

t

5

SDIN

SDO

ALTERNATiVELY, DATA MAY BE CLOCKED INTO INPUT SHIFT REGISTER ON RISING EDGE OF SCLK AS

DETERMINED BY CONTROL BITS. IN THIS CASE, DATA WOULD BE CLOCKED OUT OF SDO ON FALLING

EDGE OF SCLK. TIMING AS PER ABOVE, WITH SCLK INVERTED.

DB15 (N) DB0 (N)

2

t

3

DB15

(N+1)

t

9

DB15(N)

DB0 (N+1)

DB0(N)

t

7

t

8

Figure 2. Daisy-chain and Readback Modes Timing Diagram

REV. 0–4–

AD5426/AD5432/AD5443

ABSOLUTE MAXIMUM RATINGS

(TA = 25°C, unless otherwise noted.)

1, 2

VDD to GND . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +7 V

V

REF, RFB

I

OUT

Logic Inputs and Output

to GND . . . . . . . . . . . . . . . . . . . . . . –12 V to +12 V

1, I

2 to GND . . . . . . . . . . . . . . . . . . . . –0.3 V to +7 V

OUT

3

. . . . . . . . . . . –0.3 V to VDD + 0.3 V

Operating Temperature Range

Extended Industrial (Y Version) . . . . . . . . –40°C to +125°C

Storage Temperature Range . . . . . . . . . . . . . –65°C to +150°C

Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . 150°C

10-lead MSOP θ

Thermal Impedance . . . . . . . . . . . 206°C/W

JA

Lead Temperature, Soldering (10 seconds) . . . . . . . . . . 300°C

IR Reflow, Peak Temperature (<20 seconds) . . . . . . . . 235°C

NOTES

1

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of

the device at these or any other conditions above those listed in the operational

sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability. Only one absolute

maximum rating may be applied at any one time.

2

Transient currents of up to 100 mA will not cause SCR latchup.

3

Overvoltages at SCLK, SYNC, and DIN, will be clamped by internal diodes.

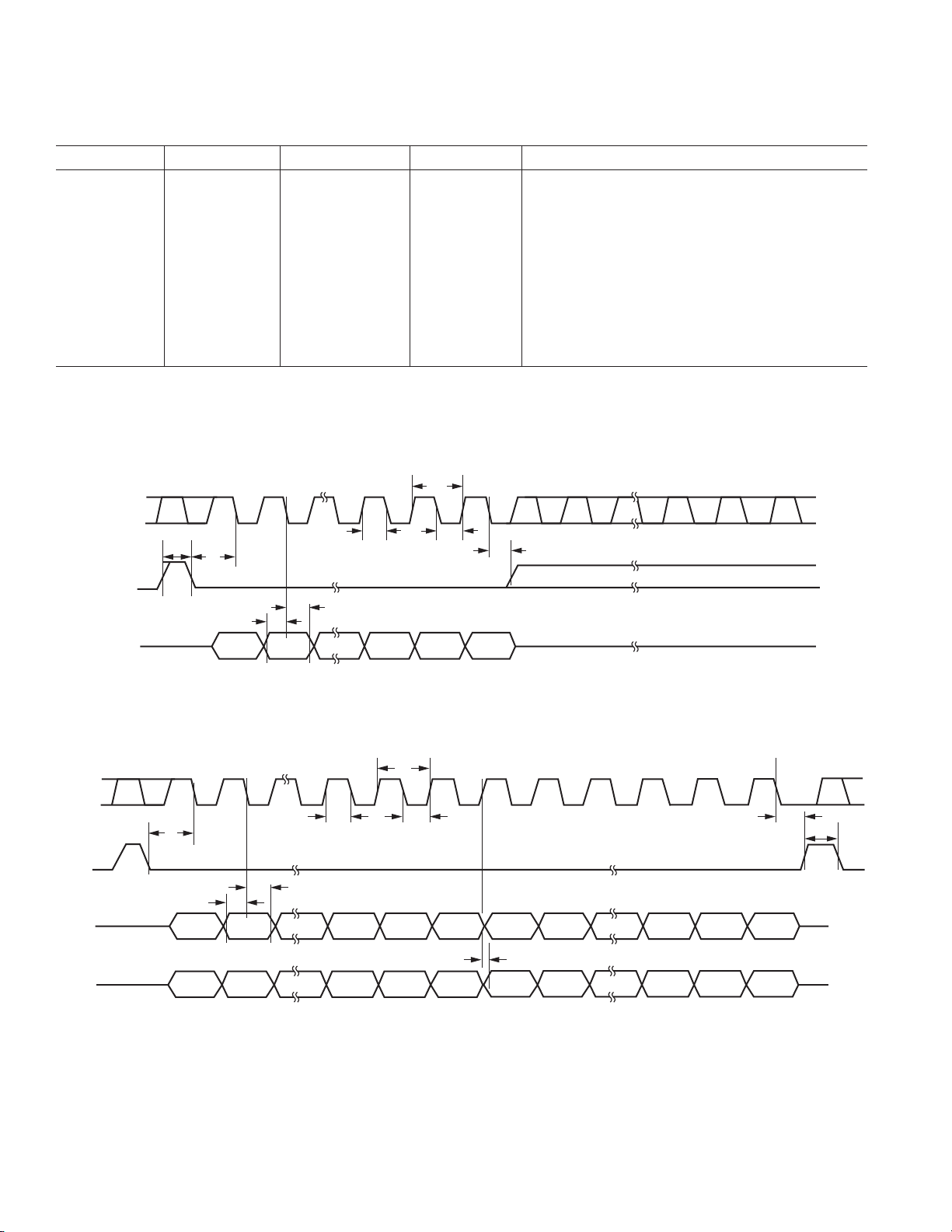

ORDERING GUIDE

I

OL

V

+ V

OH (MIN)

I

OH

OL (MAX)

2

TO

OUTPUT

PIN

C

L

20pF

200A

200A

Figure 3. Load Circuit for SDO Timing Specifications

Resolution INL Package Package

Model (Bit) (LSB) Temperature Range Description Branding Option

AD5426YRM 8 ±0.25 –40°C to +125°C MSOP D1Q RM-10

AD5426YRM-REEL 8 ±0.25 –40°C to +125°C MSOP D1Q RM-10

AD5426YRM-REEL7 8 ± 0.25 –40°C to +125°C MSOP D1Q RM-10

AD5432YRM 10 ± 0.5 –40°C to +125°C MSOP D1R RM-10

AD5432YRM-REEL 10 ± 0.5 –40°C to +125°C MSOP D1R RM-10

AD5432YRM-REEL7 10 ±0.5 –40°C to +125°C MSOP D1R RM-10

AD5443YRM 12 ± 1 –40°C to +125°C MSOP D1S RM-10

AD5443YRM-REEL 12 ± 1 –40°C to +125°C MSOP D1S RM-10

AD5443YRM-REEL7 12 ±1 –40°C to +125°C MSOP D1S RM-10

EVAL-AD5426EB Evaluation Kit

EVAL-AD5432EB Evaluation Kit

EVAL-AD5443EB Evaluation Kit

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although the

AD5426/AD5432/AD5443 features proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions

are recommended to avoid performance degradation or loss of functionality.

REV. 0

–5–

AD5426/AD5432/AD5443

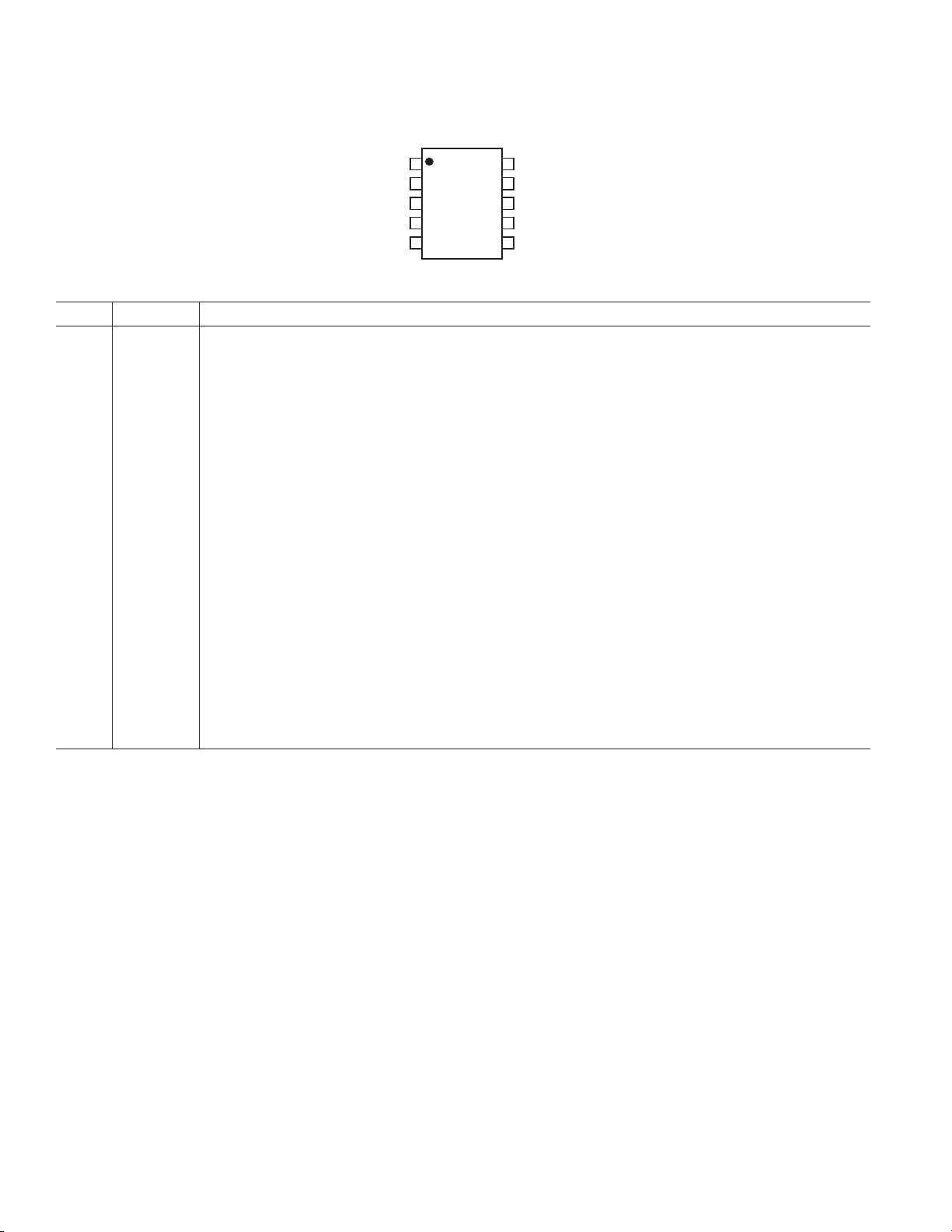

PIN CONFIGURATION

I

1

110

OUT

I

2

29

OUT

GND

SCLK

SDIN

AD5426/

AD5432/

38

AD5443

47

(Not to Scale)

56

PIN FUNCTION DESCRIPTIONS

Pin No. Mnemonic Function

1I

2I

1 DAC Current Output.

OUT

2 DAC Analog Ground. This pin should normally be tied to the analog ground of the system.

OUT

3GND Ground Pin.

4 SCLK Serial Clock Input. By default, data is clocked into the input shift register on the falling edge of the serial

clock input. Alternatively, by means of the serial control bits, the device may be configured such that data is

clocked into the shift register on the rising edge of SCLK.

5SDIN Serial Data Input. Data is clocked into the 16-bit input register on the active edge of the serial clock input.

By default, on power-up, data is clocked into the shift register on the falling edge of SCLK. The control bits

allow the user to change the active edge to rising edge.

6 SYNC Active Low Control Input. This is the frame synchronization signal for the input data. When SYNC goes

low, it powers on the SCLK and DIN buffers, and the input shift register is enabled. Data is loaded to the

shift register on the active edge of the following clocks (power-on default is falling clock edge). In standalone

mode, the serial interface counts clocks and data is latched to the shift register on the 16th active clock edge.

7SDO Serial Data Output. This allows a number of parts to be daisy-chained. By default, data is clocked into the

shift register on the falling edge and out via SDO on the rising edge of SCLK. Data will always be clocked

out on the alternate edge to loading data to the shift register. Writing the Readback control word to the

shift register makes the DAC register contents available for readback on the SDO pin, clocked out on the

opposite edges to the active clock edge.

8V

9V

10 R

DD

REF

FB

Positive Power Supply Input. These parts can be operated from a supply of 3 V to 5.5 V.

DAC Reference Voltage Input.

DAC Feedback Resistor pin. Establish voltage output for the DAC by connecting to external amplifier output.

R

FB

V

REF

V

DD

SDO

SYNC

REV. 0–6–

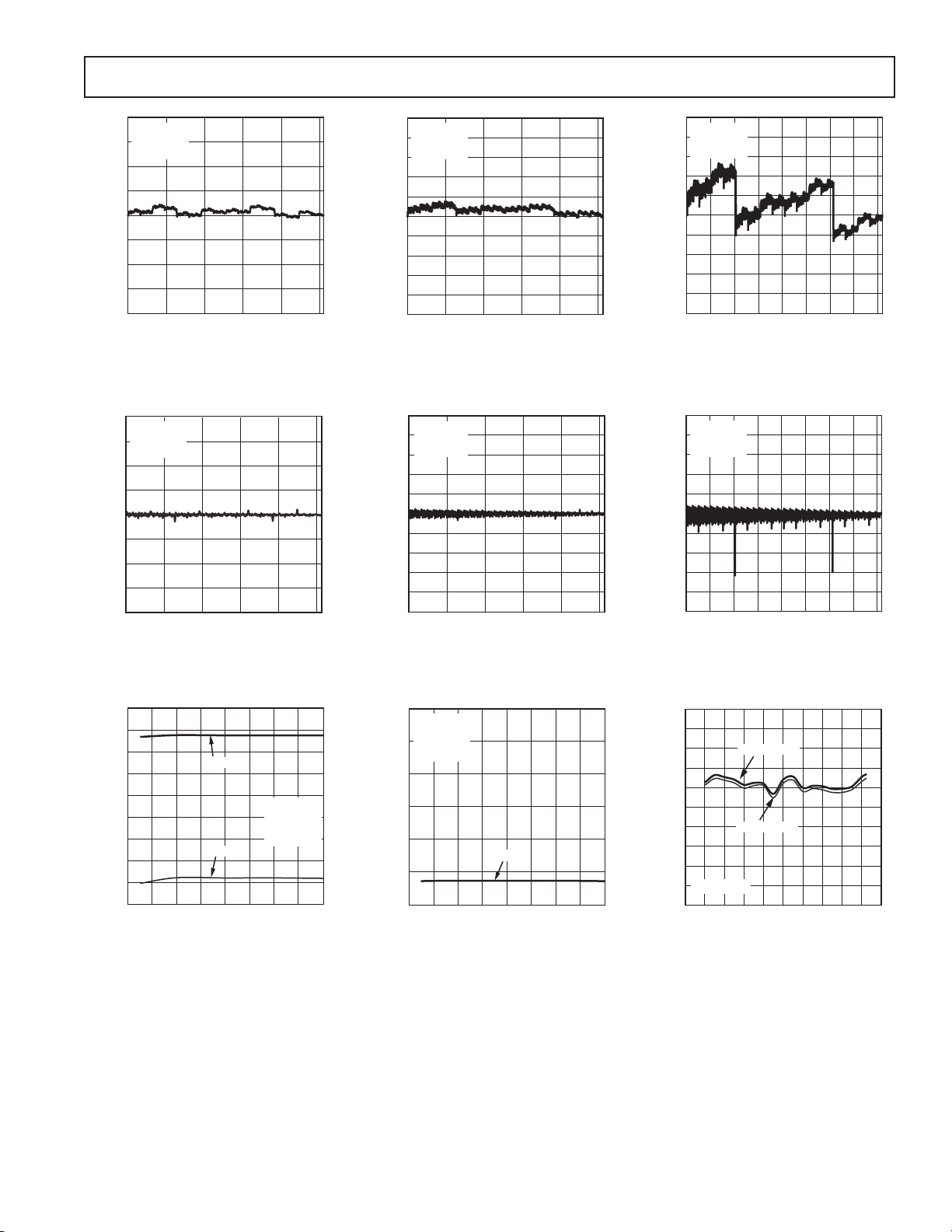

Typical Performance Characteristics–AD5426/AD5432/AD5443

0.20

TA = 25ⴗC

= 10V

V

0.15

REF

= 5V

V

DD

0.10

0.05

0

INL (LSB)

–0.05

–0.10

–0.15

–0.20

050100 150 250200

CODE

TPC 1. INL vs. Code (8-Bit DAC)

0.20

TA = 25ⴗC

= 10V

V

0.15

REF

= 5V

V

DD

0.10

0.05

0

DNL (LSB)

–0.05

–0.10

–0.15

–0.20

0 200

50 100 150 250

CODE

TPC 4. DNL vs. Code (8-Bit DAC)

0.5

TA = 25ⴗC

0.4

0.3

0.2

0.1

INL (LSB)

–0.1

–0.2

–0.3

–0.4

–0.5

= 10V

V

REF

= 5V

V

DD

0

0 200 400 800600 1000

CODE

TPC 2. INL vs. Code (10-Bit DAC)

0.5

TA = 25ⴗC

0.4

0.3

0.2

0.1

–0.1

DNL (LSB)

–0.2

–0.3

–0.4

–0.5

= 10V

V

REF

= 5V

V

DD

0

0 200 400 800600 1000

CODE

TPC 5. DNL vs. Code (10-Bit DAC)

1.0

TA = 25ⴗC

0.8

0.6

0.4

0.2

INL (LSB)

–0.2

–0.4

–0.6

–0.8

–1.0

= 10V

V

REF

= 5V

V

DD

0

0 500 1000 1500 2000 2500 3000 3500 4000

CODE

TPC 3. INL vs. Code (12-Bit DAC)

1.0

TA = 25ⴗC

0.8

0.6

0.4

0.2

–0.2

DNL (LSB)

–0.4

–0.6

–0.8

–1.0

= 10V

V

REF

= 5V

V

DD

0

0 500 1000 2000 2500 3000 35001500 4000

CODE

TPC 6. DNL vs. Code (12-Bit DAC)

0.6

0.5

0.4

0.3

0.2

0.1

INL (LSB)

0

–0.1

–0.2

–0.3

2345678910

MAX INL

MIN INL

REFERENCE VOLTAGE

TA = 25ⴗC

= 10V

V

REF

= 5V

V

DD

AD5443

TPC 7. INL vs. Reference Voltage

–0.40

TA = 25ⴗC

= 10V

V

REF

= 5V

V

–0.45

DD

AD5443

–0.50

–0.55

DNL (LSB)

–0.60

MIN DNL

–0.65

–0.70

2345678910

REFERENCE VOLTAGE

TPC 8. DNL vs. Reference Voltage

5

4

3

2

1

0

–1

ERROR (mV)

–2

–3

–4

V

–5

–60 –40 –20 0 20 40 60 80 100 120 140

REF

= 10V

VDD = 5V

VDD = 3V

TEMPERATURE (ⴗC)

TPC 9. Gain Error vs. Temperature

REV. 0

–7–

AD5426/AD5432/AD5443

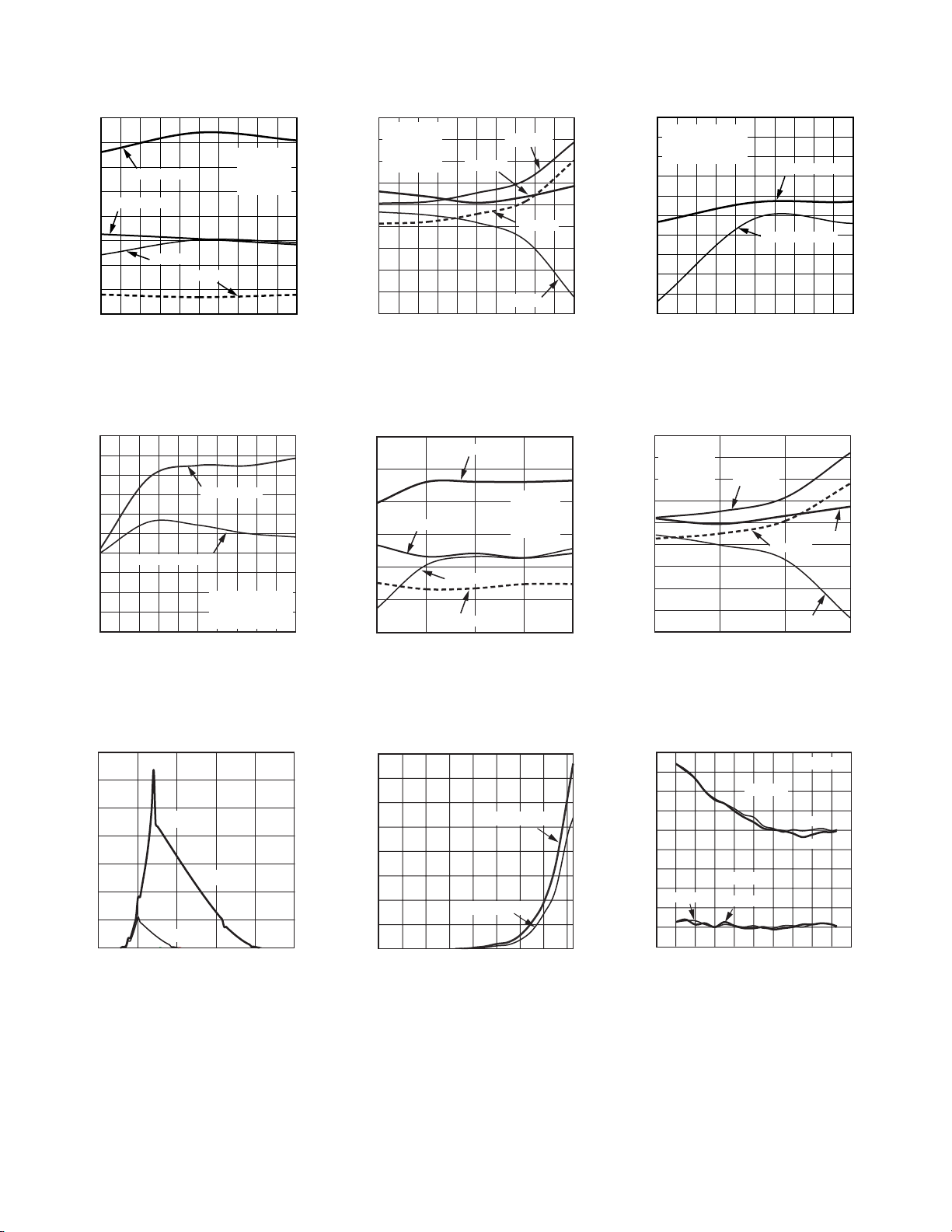

2.0

1.5

LSB

–0.5

–1.0

–1.5

–2.0

1.0

0.5

0

MAX INL

MAX DNL

MIN INL

MIN DNL

0.5 0.6 0.7 0.8 0.9 1.0 1.1 1.2 1.3 1.4 1.5

V

BIAS

TPC 10. Linearity vs. V

Voltage Applied to I

0.5

0.4

0.3

0.2

0.1

0

–0.1

VOLTAGE (mV)

–0.2

–0.3

–0.4

–0.5

OFFSET ERROR

0 0.2 0.4 0.6 0.8 1.0 1.2 1.4 1.6 1.8 2.0

V

BIAS

TA = 25ⴗC

V

REF

V

DD

AD5443

(V)

BIAS

OUT2

GAIN ERROR

TA = 25ⴗC

= 2.5V

V

REF

= 3V AND 5V

V

DD

(V)

= 0V

= 3V

TPC 13. Gain and Offset Errors

vs. V

Voltage Applied to I

BIAS

OUT2

4

TA = 25ⴗC

3

= 2.5V

V

REF

= 3V

V

DD

2

AD5443

1

0

LSB

–1

–2

–3

–4

–5

0 0.2 0.4 0.6 0.8 1.0 1.2 1.4 1.6 1.8 2.0

MAX INL

V

BIAS

(V)

TPC 11. Linearity vs. V

Voltage Applied to I

3

2

1

MAX DNL

0.5 1.0 2.5

LSB

–1

–2

–3

0

MIN INL

MIN DNL

V

BIAS

MAX INL

1.5 2.0

(V)

TPC 14. Linearity vs. V

Voltage Applied to I

MAX DNL

MIN DNL

MIN INL

BIAS

OUT2

TA = 25ⴗC

V

REF

= 5V

V

DD

AD5443

BIAS

OUT2

= 0V

0.5

TA = 25ⴗC

0.4

0.3

0.2

0.1

–0.1

VOLTAGE (mV)

–0.2

–0.3

–0.4

–0.5

= 0V

V

REF

= 3V AND 5V

V

DD

0

0.5 0.6 0.7 0.8 0.9 1.0 1.1 1.2 1.3 1.4 1.5

V

OFFSET ERROR

(V)

BIAS

GAIN ERROR

TPC 12. Gain and Offset Errors vs.

V

Voltage Applied to I

BIAS

4

TA = 25ⴗC

= 2.5V

V

3

REF

= 5V

V

DD

AD5443

2

1

0

LSB

–1

–2

–3

–4

–5

0.5 1.0 1.5 2.0

MAX DNL

V

BIAS

TPC 15. Linearity vs. V

Voltage Applied to I

(V)

OUT2

MIN DNL

MIN INL

OUT2

MAX INL

BIAS

0.7

0.6

0.5

0.4

0.3

CURRENT (mA)

0.2

0.1

0

VDD = 5V

TA = 25ⴗC

VDD = 3V

INPUT VOLTAGE (V)

TPC 16. Supply Current vs.

Logic Input Voltage,

(SCLK, DATA = 0)

SYNC

1.6

1.4

1.2

1.0

0.8

LEAKAGE (nA)

0.6

OUT

I

0.4

0.2

543210

0

–40 –20 0 20 40 60 80 100 120

TPC 17. I

vs. Temperature

I

OUT1 VDD

TEMPERATURE (

Leakage Current

OUT1

I

OUT1 VDD

3V

ⴗ

C)

5V

0.50

0.45

0.40

0.35

A)

0.30

0.25

0.20

CURRENT (

0.15

ALL 1s

0.10

0.05

0

–40

–60 –20 0 20 40 60 80 100 140

VDD = 5V

VDD = 3V

ALL 0s

TEMPERATURE (

ⴗ

C)

ALL 0s

ALL 1s

TA = 25ⴗC

TPC 18. Supply Current vs.

Temperature

120

REV. 0–8–

Loading...

Loading...