40-Channel,16-Bit,

www.BDTIC.com/ADI

FEATURES

40-channel DAC in a 64-lead LFCSP and a 64-lead LQFP

Guaranteed monotonic to 16 bits

Maximum output voltage span of 4 × V

Nominal output voltage span of −4 V to +8 V

Multiple, independent output spans available

System calibration function allowing user-programmable

off

set and gain

Channel grouping and addressing features

Thermal shutdown function

DSP/microcontroller-compatible serial interface

SPI serial interface

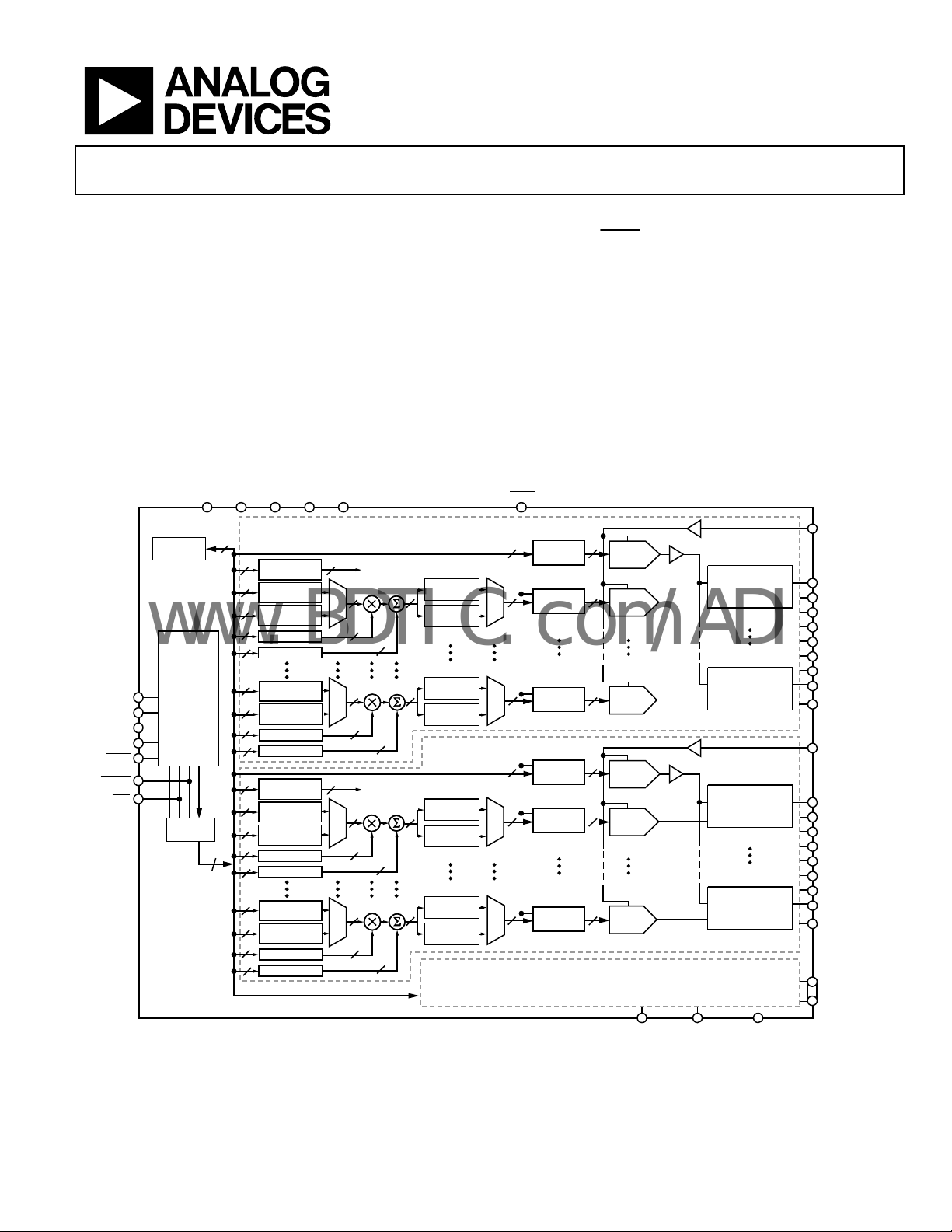

DV

CCVDDVSS

STATE

16

8 8

16

16

16

16

16

16

16

16

8 8

16

16

16

16

16

16

16

16

16

A/B SELECT

REGISTER

X1A

REGISTER

X1B

REGISTER

M REGISTER

C REGIS TER

X1A

REGISTER

X1B

REGISTER

M REGISTER

C REGISTER

A/B SELECT

REGISTER

X1A

REGISTER

X1B

REGISTER

M REGISTER

C REGIS TER

X1A

REGISTER

X1B

REGISTER

M REGISTER

C REGISTER

SYNC

SDI

SCLK

SDO

BUSY

RESET

CLR

CONTROL

REGISTER

SERIAL

INTERFACE

MACHINE

AD5370

(20 V)

REF

AGND DGND

MUX 1MUX 1MUX 1MUX 1

FUNCTIONAL BLOCK DIAGRAM

TO

MUX2

16

16

TO

MUX2

16

16

16

16

16

16

REGISTER

REGISTER

REGISTER

REGISTER

REGISTER

REGISTER

REGISTER

REGISTER

16

16

16

16

16

16

16

16

Serial Input, Voltage Output DAC

2.5 V to 5.5 V digital interface

X2A

X2B

X2A

X2B

X2A

X2B

X2A

X2B

Digital reset (

Clear function to user-defined SIGGNDx

Simultaneous update of DAC outputs

APPLICATIONS

Level setting in automatic test equipment (ATE)

Variable optical attenuators (VOA)

Optical switches

Industrial control systems

Instrumentation

LDAC

1616

OFS0

REGISTER

MUX 2

MUX 2

MUX 2

MUX 2

16

16

16

16

REGISTER

REGISTER

REGISTER

REGISTER

REGISTER

16

DAC 0

16

DAC 7

1616

OFS1

16

DAC 0

16

DAC 7

GROUP 2 TO GROUP 4

ARE THE SAME AS GROUP 1

RESET

OFFSET

DAC 0

DAC 0

DAC 7

OFFSET

DAC 1

DAC 0

DAC 7

)

BUFFER

BUFFER

BUFFER

BUFFER

GROUP 0

OUTPUT BUFFER

AND

POWER-DOW N

CONTROL

OUTPUT BUFFER

AND

POWER-DOW N

CONTROL

GROUP 1

OUTPUT BUFFER

AND

POWER-DOW N

CONTROL

OUTPUT BUFFER

AND

POWER-DOW N

CONTROL

AD5370

VREF0

VOUT0

VOUT1

VOUT2

VOUT3

VOUT4

VOUT5

VOUT6

VOUT7

SIGGND0

VREF1

VOUT8

VOUT9

VOUT10

VOUT11

VOUT12

VOUT13

VOUT14

VOUT15

SIGGND1

VOUT16

TO

VOUT39

Figure 1.

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Anal og Devices for its use, nor for any infringements of patents or ot her

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2008 Analog Devices, Inc. All rights reserved.

SIGGND4SIGGND3SIGGND2

05813-001

AD5370

www.BDTIC.com/ADI

TABLE OF CONTENTS

Features.............................................................................................. 1

Applications....................................................................................... 1

Functional Block Diagram ..............................................................1

Revision History ...............................................................................2

General Description......................................................................... 3

Specifications..................................................................................... 4

Performance Specifications......................................................... 4

AC Characteristics........................................................................ 5

Timing Characteristics ................................................................ 6

Timing Diagrams.......................................................................... 6

Absolute Maximum Ratings............................................................ 9

ESD Caution.................................................................................. 9

Pin Configurations and Function Descriptions......................... 10

Typical Performance Characteristics........................................... 12

Terminology.................................................................................... 14

Theory of Operation ......................................................................15

DAC Architecture....................................................................... 15

Channel Groups.......................................................................... 15

A

/B Registers and Gain/Offset Adjustment............................ 16

Load DAC.................................................................................... 16

Offset DAC Channels ................................................................16

Output Amplifier........................................................................ 17

Transfer Function....................................................................... 17

Reference Selection .................................................................... 17

Calibration................................................................................... 18

Additional Calibration............................................................... 18

Reset Function............................................................................ 19

Clear Function............................................................................ 19

and

LDAC

Functions...................................................... 19

BUSY

Power-Down Mode.................................................................... 19

Thermal Shutdown Function ...................................................19

Toggle Mode................................................................................ 20

Serial Interface ................................................................................ 21

SPI Write Mode .......................................................................... 21

SPI Readback Mode................................................................... 21

Register Update Rates................................................................ 21

Channel Addressing and Special Modes................................. 21

Special Function Mode.............................................................. 23

Power Supply Decoupling......................................................... 25

Power Supply Sequencing .........................................................25

Interfacing Examples ................................................................. 26

Outline Dimensions....................................................................... 27

Ordering Guide .......................................................................... 27

REVISION HISTORY

4/08—Revision 0: Initial Version

Rev. 0 | Page 2 of 28

AD5370

www.BDTIC.com/ADI

GENERAL DESCRIPTION

The AD53701 contains forty 16-bit DACs in a single 64-lead

LFCSP and a 64-lead LQFP. The device provides buffered

voltage outputs with a span that is 4× the reference voltage. The

gain and offset of each DAC channel can be independently

trimmed to remove errors. For even greater flexibility, the device is

divided into five groups of eight DACs. Three offset DAC channels

allow the output range of blocks to be adjusted. Group 0 can be

adjusted by Offset DAC 0, Group 1 can be adjusted by Offset

DAC 1, and Group 2 to Group 4 can be adjusted by Offset DAC 2.

The AD5370 offers guaranteed operation over a wide supply

nge, with V

ra

from −16.5 V to −4.5 V and VDD from +9 V to

SS

+16.5 V. The output amplifier headroom requirement is 1.4 V

operating with a load current of 1 mA.

1

Protected by U.S. Patent No. 5,969,657; other patents pending.

Table 1. High Channel Count Bipolar DACs

Model Resolution Nominal Output Span Output Channels Linearity Error (LSB)

AD5360 16 bits 4 × V

AD5361 14 bits 4 × V

AD5362 16 bits 4 × V

AD5363 14 bits 4 × V

AD5370 16 bits 4 × V

AD5371 14 bits 4 × V

AD5372 16 bits 4 × V

AD5373 14 bits 4 × V

AD5378 14 bits ±8.75 V 32 ±3

AD5379 14 bits ±8.75 V 40 ±3

(20 V) 16 ±4

REF

(20 V) 16 ±1

REF

(20 V) 8 ±4

REF

(20 V) 8 ±1

REF

(12 V) 40 ±4

REF

(12 V) 40 ±1

REF

(12 V) 32 ±4

REF

(12 V) 32 ±1

REF

The AD5370 has a high speed serial interface that is compatible

with SPI, QSPI™, MICROWIRE™, and DSP interface standards

and can handle clock speeds of up to 50 MHz.

The DAC registers are updated on receipt of new data. All the

o

utputs can be updated simultaneously by taking the

LDAC

input low. Each channel has a programmable gain and an offset

adjust register to allow removal of gain and offset errors.

Each DAC output is gained and buffered on chip with respect to

n external SIGGNDx input. The DAC outputs can also be

a

switched to SIGGNDx via the

CLR

pin.

Rev. 0 | Page 3 of 28

AD5370

www.BDTIC.com/ADI

SPECIFICATIONS

PERFORMANCE SPECIFICATIONS

DVCC = 2.5 V to 5.5 V; VDD = 9 V to 16.5 V; VSS = −16.5 V to −8 V; V

R

= open circuit; gain (M), offset (C), and DAC offset registers at default values; all specifications T

L

= 3 V; AGND = DGND = SIGGND = 0 V; CL = open circuit;

REF

MIN

to T

, unless otherwise noted.

MAX

Table 2.

Parameter Min Type Max Unit Test Conditions/Comments

ACCURACY

Resolution 16 Bits

Integral Nonlinearity −4 +4 LSB

Differential Nonlinearity −1 +1 LSB Guaranteed monotonic by design

Zero-Scale Error −10 +10 mV Before calibration

Full-Scale Error −10 +10 mV Before calibration

Gain Error 0.1 % FSR

Zero-Scale Error

Full-Scale Error

Span Error of Offset DAC −35 +35 mV

VOUT Temperature Coefficient

(VOUT0 to VOUT39)

DC Crosstalk

REFERENCE INPUTS (VREF0, VREF1)

VREF Input Current −10 +10 µA Per input, typically ±30 nA

VREF Range 2 5 V ±2% for specified operation

SIGGND INPUT (SIGGND0 to SIGGND4)2

DC Input Impedance 50 kΩ Typically 55 kΩ

Input Range −0.5 +0.5 V

SIGGND Gain 0.995 1.005

OUTPUT CHARACTERISTICS

Output Voltage Range VSS + 1.4 VDD − 1.4 V I

Nominal Output Voltage Range −4 +8 V

Short-Circuit Current 15 mA VOUTx to DVCC, VDD, or VSS

Load Current −1 +1 mA

Capacitive Load 2200 pF

DC Output Impedance 0.5

DIGITAL INPUTS

Input High Voltage 1.7 V DVCC = 2.5 V to 3.6 V

2.0 V DVCC = 3.6 V to 5.5 V

Input Low Voltage 0.8 V DVCC = 2.5 V to 5.5 V

Input Current −1 +1 µA

CLR High Impedance Leakage

Current

Input Capacitance

DIGITAL OUTPUTS (SDO, BUSY)

Output Low Voltage 0.5 V Sinking 200 A

Output High Voltage (SDO) DVCC − 0.5 V Sourcing 200 A

SDO High Impedance Leakage

Current

High Impedance Output

Capacitance

2

2

2

2

2

2

1 LSB After calibration

1 LSB After calibration

See the Offset DAC Channels section for

etails

d

5 ppm FSR/°C Includes linearity, offset, and gain drift

120 µV

2

−20 +20 µA

10 pF

−5 +5 µA

10 pF

Typically 20 µV; measured channel at midscale,

e change on any other channel

full-scal

= 1 mA

LOAD

Excluding the CLR

pin

1

Rev. 0 | Page 4 of 28

AD5370

www.BDTIC.com/ADI

Parameter Min Type Max Unit Test Conditions/Comments

1

POWER REQUIREMENTS

DVCC 2.5 5.5 V

VDD 9 16.5 V

VSS −16.5 −4.5 V

Power Supply Sensitivity

2

Full Scale/VDD −75 dB

Full Scale/VSS −75 dB

Full Scale/DVCC −90 dB

DICC 2 mA

= 5.5 V, VIH = DVCC, VIL = GND; normal

DV

CC

operating conditions

IDD 18 mA Outputs unloaded, DAC outputs = 0 V

20 mA Outputs unloaded, DAC outputs = full scale

ISS −18 mA Outputs unloaded, DAC outputs = 0 V

−20 mA Outputs unloaded, DAC outputs = full scale

Power Dissipation Unloaded (P) 280 mW VSS = −8 V, VDD = +9.5 V, DVCC = 2.5 V

Power-Down Mode Control register power-down bit set

DICC 5 µA

IDD 35 µA

ISS −35 µA

Junction Temperature

1

Temperature range for the AD5370 is −40°C to +85°C. Typical specifications are at 25°C.

2

Guaranteed by design and characterization, not production tested.

3

Where θJA represents the package thermal impedance.

3

130 °C TJ = TA + P

TOTAL

× θJA

AC CHARACTERISTICS

DVCC = 2.5 V; VDD = 15 V; VSS = −15 V; VREF0 = VREF1 = 3 V; AGND = DGND = SIGGND = 0 V; CL = 200 pF; RL = 10 kΩ; gain (M),

offset (C), and DAC offset registers at default values; all specifications T

Table 3. AC Characteristics

1

Parameter Min Typ Max Unit Test Conditions/Comments

DYNAMIC PERFORMANCE

Output Voltage Settling Time 20 µs Settling to 1 LSB from a full-scale change

30 µs DAC latch contents alternately loaded with all 0s and all 1s

Slew Rate 1 V/µs

Digital-to-Analog Glitch Energy 5 nV-s

Glitch Impulse Peak Amplitude 10 mV

Channel-to-Channel Isolation 100 dB VREF0 = VREF1 = 2 V p-p, 1 kHz

DAC-to-DAC Crosstalk 20 nV-s

Digital Crosstalk 0.2 nV-s

Digital Feedthrough 0.02 nV-s Effect of input bus activity on DAC output under test

Output Noise Spectral Density @ 10 kHz 250 nV/√Hz VREF0 = VREF1 = 0 V

1

Guaranteed by design and characterization, not production tested.

MIN

to T

, unless otherwise noted.

MAX

Rev. 0 | Page 5 of 28

AD5370

T

www.BDTIC.com/ADI

TIMING CHARACTERISTICS

DVCC = 2.5 V to 5.5 V; VDD = 9 V to 16.5 V; VSS = −16.5 V to −4.5 V; V

R

= open circuit; gain (M), offset (C), and DAC offset registers at default values; all specifications T

L

Table 4. SPI Interface

Parameter

t1

1, 2, 3

Limit at T

Min Typ Max

20 ns SCLK cycle time

MIN

, T

MAX

Unit Description

t2 8 ns SCLK high time

t3 8 ns SCLK low time

t4 11 ns

t

5

20 ns

t6 10 ns

t

7

5 ns Data setup time

SYNC

Minimum SYNC

24

t8 5 ns Data hold time

4

t

42 ns

9

t

1.5 μs

10

SYNC

BUSY

t11 600 ns Single-channel update cycle time

t12 20 ns

t13 10 ns

t14 3 μs

t15 0 ns

t16 3 μs

SYNC

LDAC

BUSY

BUSY

LDAC

t17 20 30 μs DAC output settling time

t18 140 ns

t19 30 ns

t20 400 μs

t21 270 ns

5

t

25 ns SCLK rising edge to SDO valid

22

t23 80 ns

1

Guaranteed by design and characterization, not production tested.

2

All input signals are specified with tR = tF = 2 ns (10% to 90% of DVCC) and timed from a voltage level of 1.2 V.

3

See Figure 4 and Figure 5.

4

This is measured with the load circuit shown in Figure 2.

5

This is measured with the load circuit shown in Figure 3.

CLR

RESET

RESET

Minimum SYNC

RESET

= 3 V; AGND = DGND = SIGGND = 0 V; CL = 200 pF to GND;

REF

falling edge to SCLK falling edge setup time

high time

th

SCLK falling edge to SYNC rising edge

rising edge to BUSY falling edge

pulse width low (single-channel update); see Table 8

rising edge to LDAC falling edge

pulse width low

rising edge to DAC output response time

rising edge to LDAC falling edge

falling edge to DAC output response time

/RESET pulse activation time

pulse width low

time indicated by BUSY low

high time in readback mode

rising edge to BUSY falling edge

MIN

to T

, unless otherwise noted.

MAX

TIMING DIAGRAMS

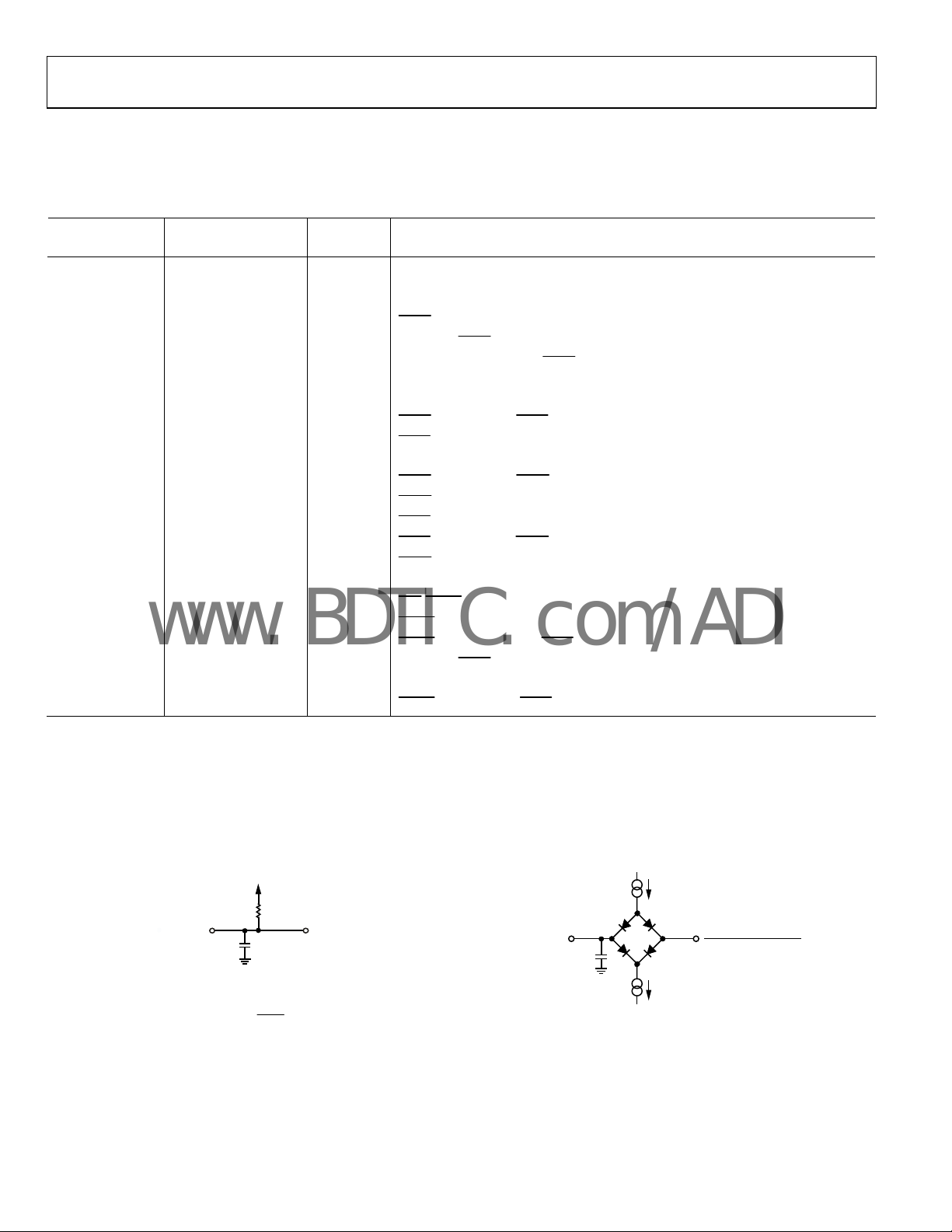

DV

CC

R

L

2.2k

TO

OUTPUT

PIN

Figure 2. Load Circuit for

Ω

C

L

50pF

BUSY

Timing Diagram

V

OL

05813-002

O OUTPUT

PIN

Figure 3. Load Circuit for SDO Timing Diagram

Rev. 0 | Page 6 of 28

50pF

C

200µA I

L

200µA I

OL

VOH (MIN) – VOL (MAX)

OH

2

5813-003

AD5370

www.BDTIC.com/ADI

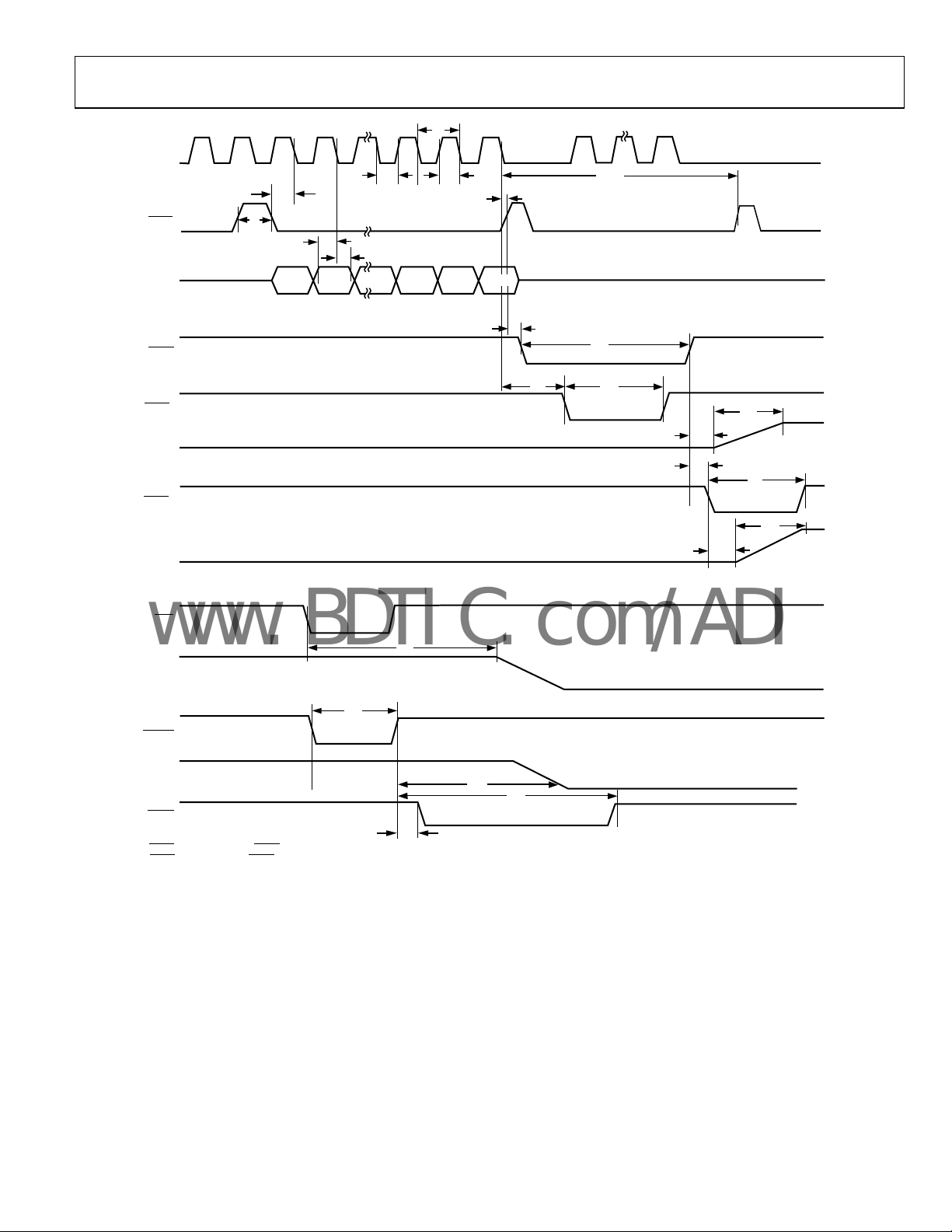

SCLK

SYNC

BUSY

LDAC

VOUTx

LDAC

VOUTx

SDI

1

1

2

2

1

2

t

t

4

t

5

t

7

t

8

DB23

t

1

24

3

t

2

t

6

DB0

t

9

t

1

t

11

t

10

12

t

13

24

t

17

t

14

t

15

t

13

t

17

t

16

CLR

VOUTx

RESET

VOUTx

BUSY

1

LDAC ACTIVE DURI NG BUSY.

2

LDAC ACTIVE AFTER BUSY.

t

18

t

19

t

18

t

20

t

23

05813-004

Figure 4. SPI Write Timing

Rev. 0 | Page 7 of 28

AD5370

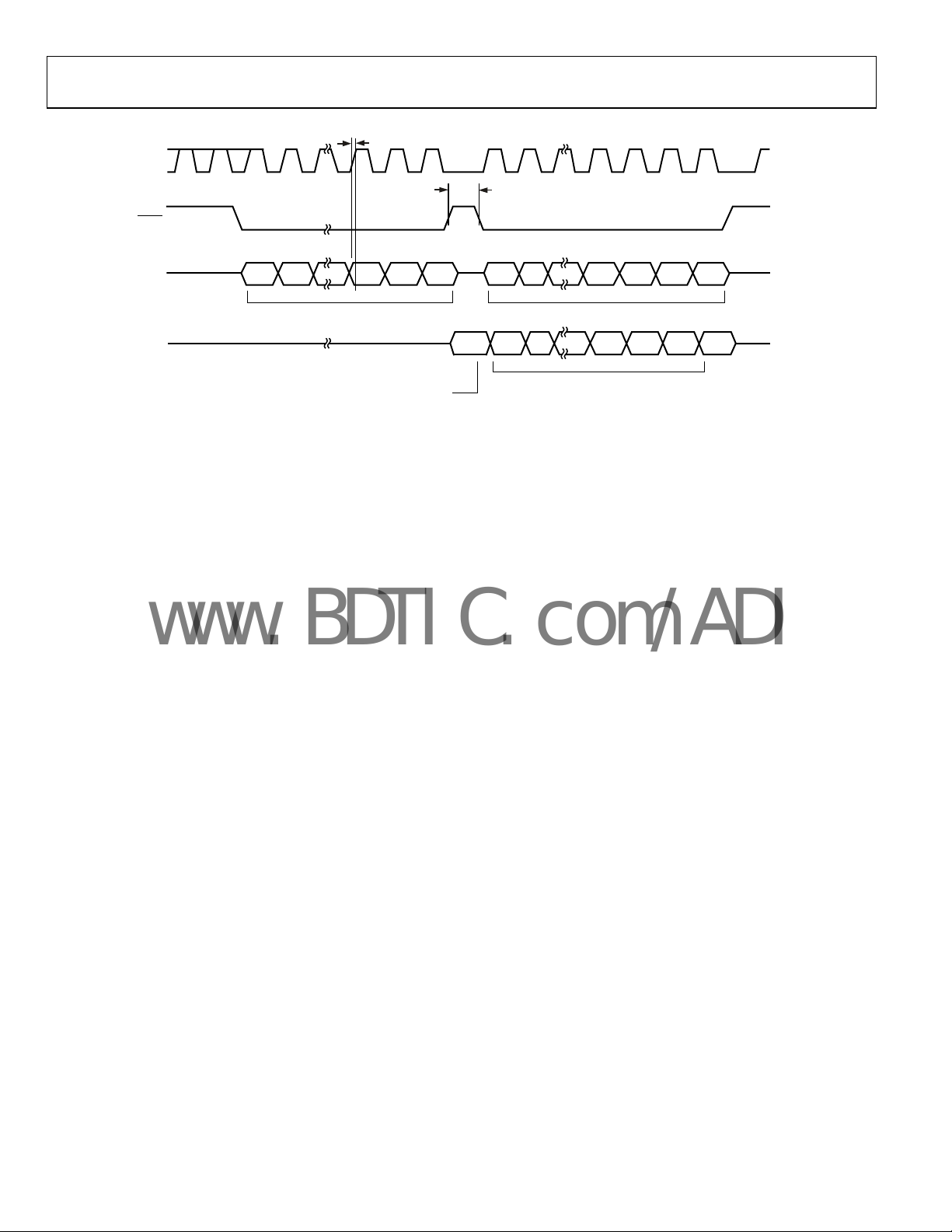

SYNC

www.BDTIC.com/ADI

SCLK

SDI

INPUT WORD SPECIFIES

REGIS TER TO BE READ

SDO

t

22

DB0 DB23DB23

LSB FROM PREVIOUS WRITE

Figure 5. SPI Read Timing

t

21

NOP CONDITIO N

DB0

DB23

SELECTED REG ISTER DAT A CLOCKED OUT

48

DB0

DB0

5813-005

Rev. 0 | Page 8 of 28

AD5370

www.BDTIC.com/ADI

ABSOLUTE MAXIMUM RATINGS

TA = 25°C, unless otherwise noted. Transient currents of up to

60 mA do not cause SCR latch-up.

Table 5.

Parameter Rating

VDD to AGND −0.3 V to +17 V

VSS to AGND −17 V to +0.3 V

DVCC to DGND −0.3 V to +7 V

Digital Inputs to DGND −0.3 V to DVCC + 0.3 V

Digital Outputs to DGND −0.3 V to DVCC + 0.3 V

VREF0, VREF1 to AGND −0.3 V to +5.5 V

VOUT0 through VOUT39 to AGND VSS − 0.3 V to VDD + 0.3 V

SIGGND0 through SIGGND4 to AGND −1 V to +1 V

AGND to DGND −0.3 V to +0.3 V

Operating Temperature Range (TA)

Industrial (B Version) −40°C to +85°C

Storage −65°C to +150°C

Operating Junction Temperature

max)

(T

J

θJA Thermal Impedance

64-Lead LFCSP 25°C/W

64-Lead LQFP 45.5°C/W

Reflow Soldering

Peak Temperature 230°C

Time at Peak Temperature 10 sec to 40 sec

130°C

Stresses above those listed under Absolute Maximum Ratings

may cause permanent damage to the device. This is a stress

rating only; functional operation of the device at these or any

other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect

device reliability.

ESD CAUTION

Rev. 0 | Page 9 of 28

Loading...

Loading...