Loop-Powered

a

FEATURES

4 mA to 20 mA Current Output

®

Compatible

HART

16-Bit Resolution and Monotonicity

ⴞ0.01% Integral Nonlinearity

5 V or 3 V Regulator Output

2.5 V and 1.25 V Precision Reference

750 A Quiescent Current max

Programmable Alarm Current Capability

Flexible High Speed Serial Interface

16-Lead SOIC and PDIP Packages

GENERAL DESCRIPTION

The AD421 is a complete, loop-powered, digital to 4 mA to

20 mA converter, designed to meet the needs of smart transmitter manufacturers in the Industrial Control industry. It provides a high precision, fully integrated, low cost solution in a

compact 16-lead package. The AD421 is ideal for extending the

resolution of smart 4 mA to 20 mA transmitters at very low cost.

The AD421 includes a selectable regulator that is used to power

itself and other devices in the transmitter. This regulator provides either a +5 V, +3.3 V or +3 V regulated output voltage.

The part also contains +1.25 V and +2.5 V precision references.

The AD421 thus eliminates the need for a discrete regulator

and voltage reference. The only external components required

are a number of passive components and a pass transistor to

span large loop voltages.

The AD421 can be used with standard HART FSK protocol

communication circuitry without any degradation in specified

performance. The high speed serial interface is capable of operating at 10 Mbps and allows for simple connection to commonly-used microprocessors and microcontrollers via a standard

three-wire serial interface.

The sigma-delta architecture of the DAC guarantees 16-bit

monotonicity while the integral nonlinearity for the AD421 is

± 0.01%. The part provides a zero scale 4 mA output current

with ± 0.1% offset error and a 20 mA full-scale output current

with ± 0.2% gain error.

The AD421 is available in a 16-lead, 0.3 inch-wide, plastic DIP

and in a 16-lead, 0.3 inch-wide, SOIC package. The part is specified over the industrial temperature range of –40°C to +85°C.

4 mA to 20 mA DAC

AD421

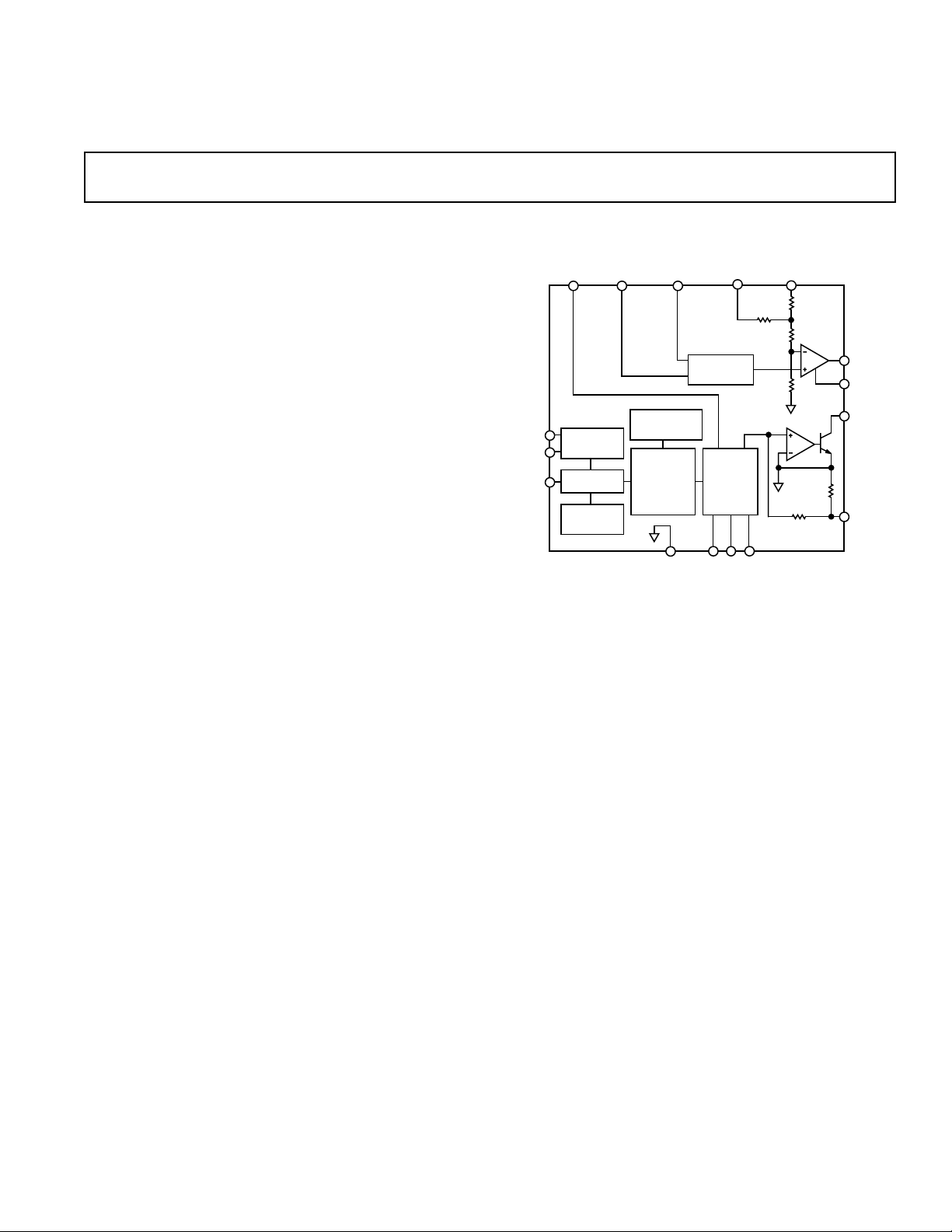

FUNCTIONAL BLOCK DIAGRAM

REF IN

REF OUT1

(+2.5V)

(+1.25V)

DATA

CLOCK

LATCH

INPUT SHIFT

REGISTER

DAC LATCH

POWER-ON

RESET

PRODUCT HIGHLIGHTS

1. The AD421 is a single chip, high performance, low cost

solution for generating 4 mA to 20 mA signals for smart

industrial control transmitters.

2. The AD421’s regulated supply voltage can be used to power

any additional circuits in the transmitter. The regulated

output value is pin selectable as either +3 V, +3.3 V or +5 V.

3. The AD421’s on-chip references can provide a precision

reference voltage to other devices in the system. This reference voltage can be either +1.25 V or +2.5 V.

4. The AD421 is fully compatible with standard HART circuitry or other similar FSK protocols.

5. With the addition of a single discrete transistor, the AD421

can be operated from V

breakdown voltage of the pass transistor.

6. The AD421 converts the digital data to current with 16-bit

resolution and monotonicity. Full-scale settling time to

± 0.1% typically occurs within 8 ms.

7. The AD421 features a programmable alarm current capability that allows the transmitter to send out of range currents to

indicate a transducer fault.

REF OUT2

(+2.5V)

AD421

LOCAL

OSCILLATOR

16-BIT

SIGMA-

DELTA DAC

CC

LV

BANDGAP

REFERENCE

SWITCHED

CURRENT

SOURCES

AND

FILTERING

C1 C2 C3COM

112.5k⍀

134k⍀

121k⍀

V

CC

80k⍀

75k⍀

40⍀

DRIVE

COMP

BOOST

LOOP

RTN

+ 2 V min to a maximum of the

HART is a registered trademark of the HART Communication

Foundation.

REV. C

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2000

(Using DN25D1 as pass transistor as per Figure 3;

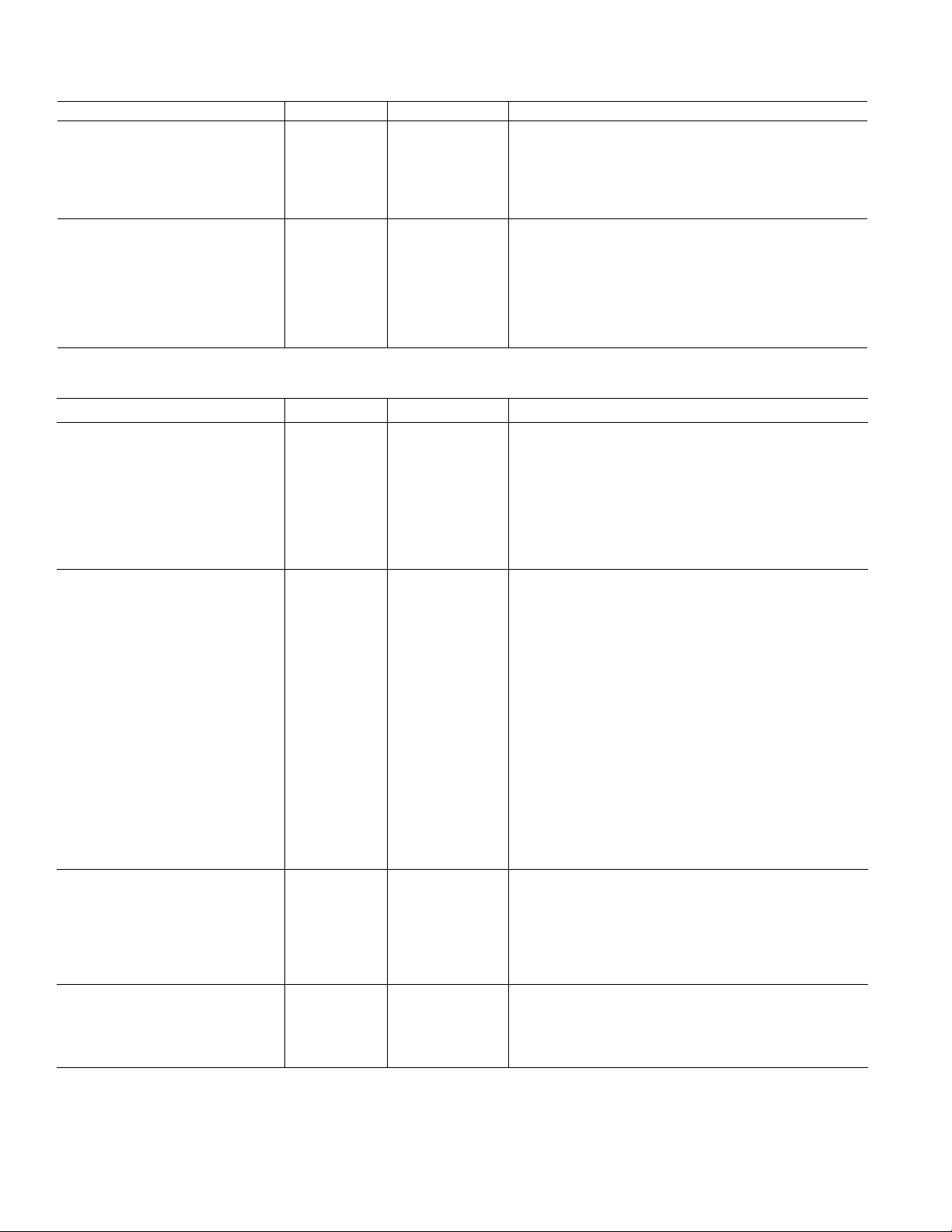

AD421–LOOP-POWERED SPECIFICATIONS

REF IN = REF OUT2; TA = T

Parameter B Versions2Units Conditions/Comments

OUTPUT CHARACTERISTICS

Current Loop Voltage Compliance

3

VCC + 2 V min

350 V max DN25D Breakdown Voltage

Full-Scale Settling Time 8 ms typ Settling Time to ±0.1%, C1 = C2 = 10 nF, C3 = 3.3 nF

Output Impedance 25 MΩ typ

AC Loop Voltage Sensitivity 2 µA/V typ 1200 Hz to 2200 Hz

VOLTAGE REGULATOR

Output Voltage (V

CC

)

3 V Mode 2.95/3.05 V min/V max 3 V Nominal. LV Pin Connected to V

3.3 V Mode 3.25/3.35 V min/V max 3.3 V Nominal. LV Pin Connected Through 0.01 µF to V

5 V Mode 4.95/5.05 V min/V max 5 V Nominal. LV Pin Connected to COM

Externally Available Current 3.25 mA min Assuming 4 mA Flowing in the Loop

Line Regulation 1 µV/V typ

Load Regulation 15 µV/mA typ

MIN

to T

unless otherwise noted)

MAX

CC

CC

DAC SPECIFICATIONS

(VCC = +3 V to +5 V; REF IN = REF OUT2; TA = T

MIN

to T

unless otherwise noted)

MAX

Parameter B Versions2Units Conditions/Comments

ACCURACY

Resolution 16 Bits

Monotonicity 16 Bits min

Integral Nonlinearity ± 0.01 % of FS max FS = Full-Scale Output Current

Offset (4 mA) @ +25°C

Offset Drift ± 25 ppm of FS/°C max Includes On-Chip Reference Drift

Total Output Error (20 mA) @ +25°C

4

± 0.1 % of FS max VCC = 5 V

4

± 0.2 % of FS max VCC = 5 V

Total Output Drift ± 50 ppm of FS/°C max Includes On-Chip Reference Drift

VCC Supply Sensitivity 50 nA/mV max 25 nA/mV Typical

VOLTAGE REFERENCE

REF OUT2

Output Voltage 2.49/2.51 V min/V max 2.5 V Nominal

Drift ± 40 ppm/°C max 20 ppm/°C Typical from –40°C to +25°C and

–2.5 ppm/°C Typical from +25°C to +85°C

Externally Available Current 0.5 mA min

Supply Sensitivity 150 µV/V max 15 µV/V Typical

V

CC

Output Impedance 3 Ω typ

Noise (0.1 Hz–10 Hz) 6 µV (p-p) typ

REF OUT1

Output Voltage 1.24/1.26 V min/V max 1.25 V Nominal, 100 kΩ Load to COM

5

Drift ± 50 ppm/°C max 20 ppm/°C Typical from –40°C to +25°C and

2 ppm/°C Typical from +25°C to +85°C

Externally Available Current 0.5 mA min

Supply Sensitivity 150 µV/V max 15 µV/V Typical

V

CC

Output Impedance 3 Ω typ

Noise (0.1 Hz–10 Hz) 4 µV (p-p) typ

REF IN

Input Resistance 40 kΩ typ

DIGITAL INPUTS

(Logic 1) 0.75 × V

V

IH

(Logic 0) 0.25 × V

V

IL

I

IH

I

IL

CC

CC

± 10 µA max VIN = V

± 10 µA max VIN = 0 V

V min

V max

CC

Data Coding Binary

Data Rate 10 Mbps max

POWER SUPPLIES

Operating Range +2.95 to +5.05 V min to V max Functional to 7 V

Quiescent Current

= 3 V 650 µA max 475 µA Typical

@ V

CC

@ VCC = 5 V 750 µA max 575 µA Typical

NOTES

1

The DN25D is available from Supertex, Inc., 1350 Bordeaux Drive, Sunnyvale, CA 94089.

2

Temperature range is –40°C to +85°C.

3

The max current loop voltage compliance is determined by the pass transistor breakdown voltage and is 350 V for the DN25D.

4

With VCC = 3 V, the transfer function shifts negative by typically 0.25%; a 16 kΩ resistor connected between COM and LOOPRTN will approximately compensate for the V

supply sensitivity in moving from 5 V to 3 V by skewing the gain of the AD421.

5

100 kΩ resistor only required if this reference is being used in application circuits.

Specifications subject to change without notice.

CC

–2–

REV. C

AD421

1, 2, 3

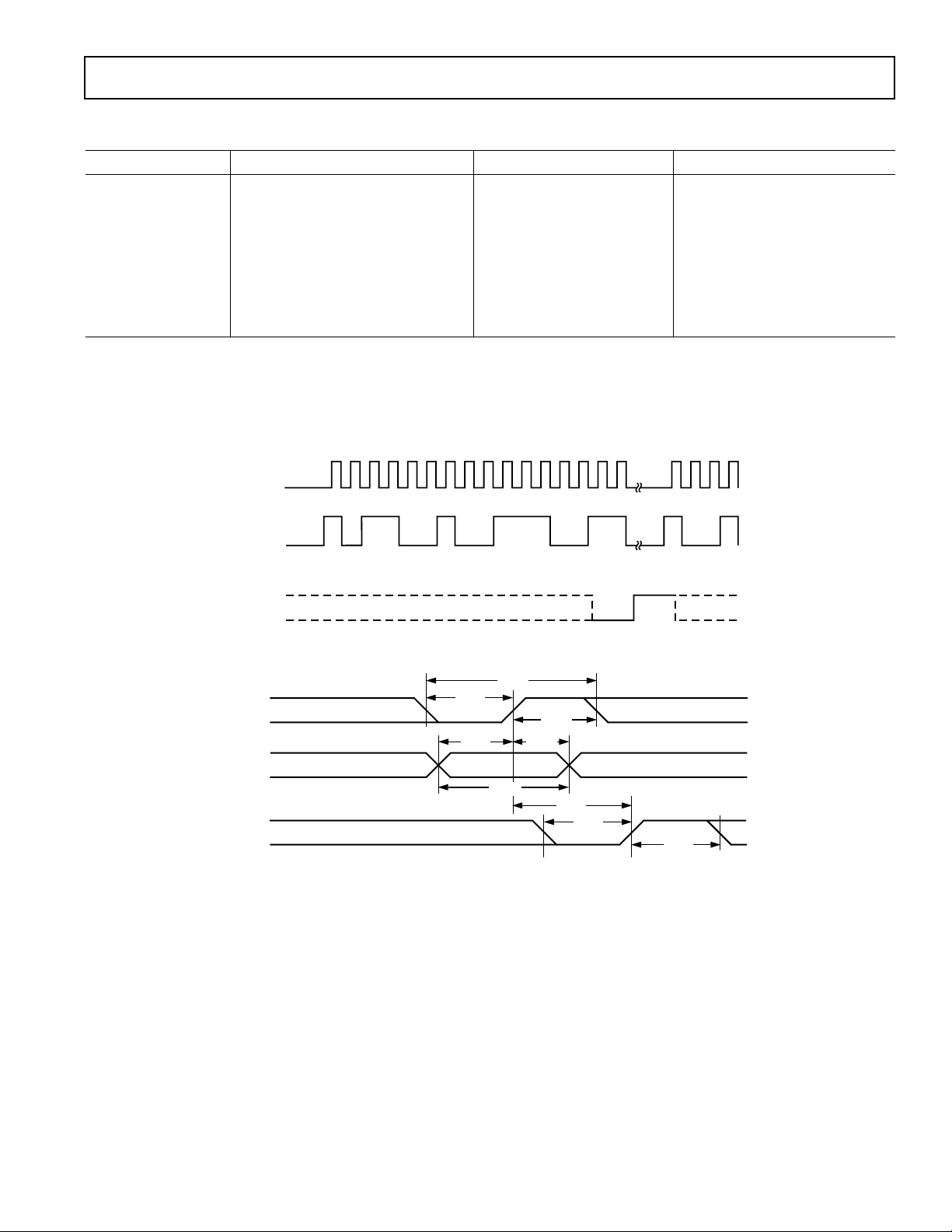

TIMING CHARACTERISTICS

(VCC = +3 V to +5 V, TA = T

Parameter (B Versions) Units Conditions/Comments

t

CK

t

CL

t

CH

t

DW

t

DS

t

DH

t

LD

t

LL

t

LH

NOTES

1

Guaranteed by characterization at initial product release, not production tested.

2

See Figures 1 and 2.

3

All input signals are specified with tr = tf = 5 ns (10% to 90% of VCC) and timed from a voltage level of (VIN + VIL)/2; tr and tf should not exceed 1 µs on any digital

input.

Specifications subject to change without notice.

CLOCK

DATA

100 ns min Data Clock Period

50 ns min Data Clock Low Time

50 ns min Data Clock High Time

30 ns min Data Stable Width

30 ns min Data Setup Time

0 ns min Data Hold Time

50 ns min Latch Delay Time

50 ns min Latch Low Time

50 ns min Latch High Time

WORD "N" WORD "N +1"

10 11 11111

B15

B14

(MSB)

00 00 00 1 00 1

B9

B7

B8

B10

B11

B13

B12

to T

MIN

1

B5

B6

unless otherwise noted)

MAX

B4

B3

B0

B2

B1

(LSB)

B15

B14

B13

B12

LATCH

CLOCK

DATA

LATCH

Figure 1. Serial Interface Waveforms (Normal Data Load)

t

t

t

CK

CL

t

CH

t

DW

DH

t

LD

t

LL

t

DS

t

Figure 2. Serial Interface Timing Diagram

LH

REV. C

–3–

AD421

WARNING!

ESD SENSITIVE DEVICE

ABSOLUTE MAXIMUM RATINGS*

(TA = +25°C unless otherwise noted)

DRIVE, BOOST, COMP to COM . . . –0.5 V to VCC + 0.5 V

LOOP RTN to COM . . . . . . . . . . . . . . . . . . . –2 V to + 0.5 V

Digital Input Voltage to COM . . . . . . . –0.5 V to V

+ 0.5 V

CC

Operating Temperature Range

Commercial (B Version) . . . . . . . . . . . . . . – 40°C to +85°C

Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C

Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . . +150°C

Plastic DIP Package, Power Dissipation . . . . . . . . . . 670 mW

Thermal Impedance . . . . . . . . . . . . . . . . . . . . 116°C/W

θ

JA

Lead Temperature (Soldering, 10 sec) . . . . . . . . . . . . 260°C

SOIC Package, Power Dissipation . . . . . . . . . . . . . . . 450 mW

Thermal Impedance . . . . . . . . . . . . . . . . . . . . 110°C/W

θ

JA

Lead Temperature, Soldering

Vapor Phase (60 sec) . . . . . . . . . . . . . . . . . . . . . +215°C

Infrared (15 sec) . . . . . . . . . . . . . . . . . . . . . . . . . +220°C

*

Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those listed in the operational

sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

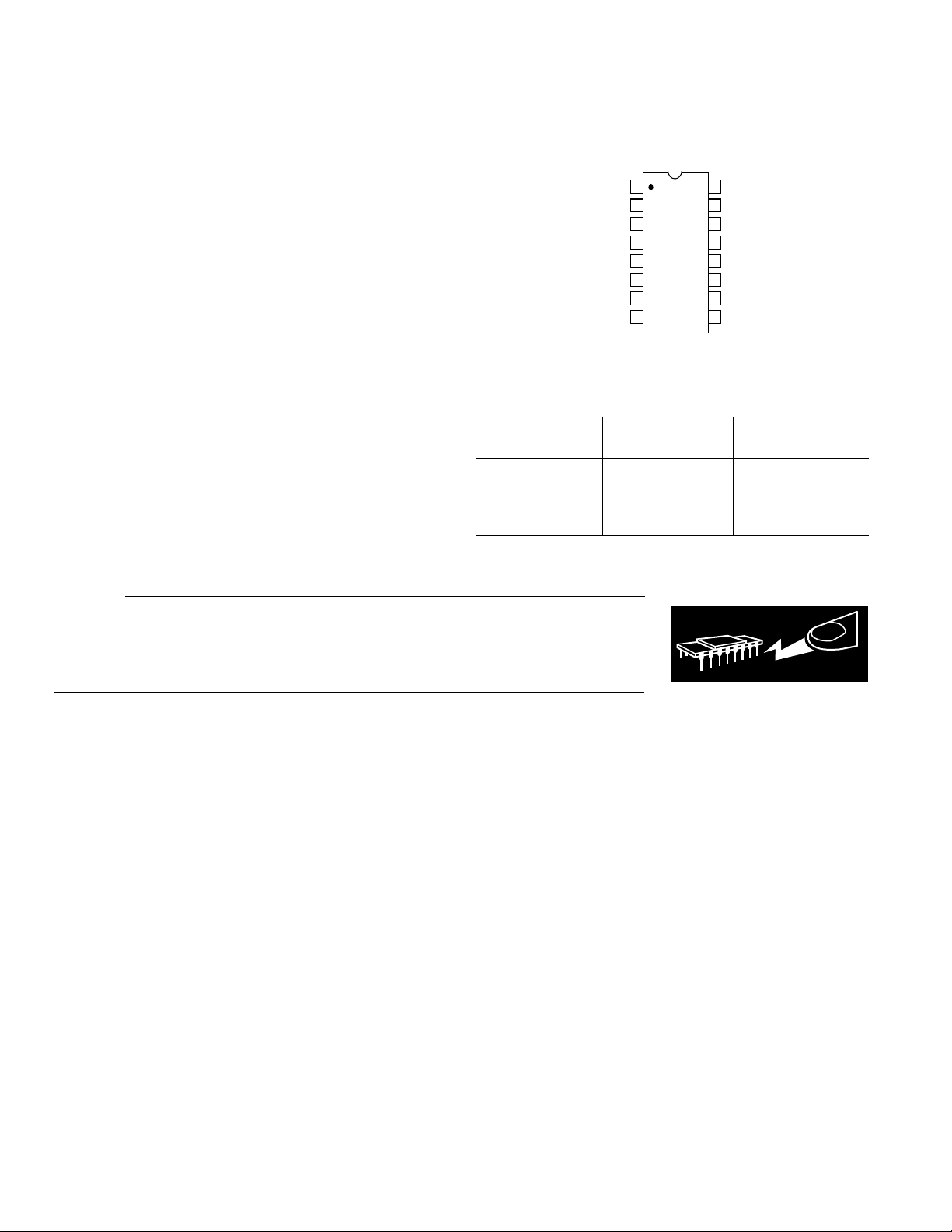

PIN CONFIGURATION

DIP and SOIC

REF OUT1

REF OUT2

REF IN

LATCH

CLOCK

DATA

LOOP RTN

LV

1

2

3

4

AD421

5

TOP VIEW

(NOT TO SCALE)

6

7

8

16

15

14

13

12

11

10

9

V

CC

BOOST

COMP

DRIVE

C1

C2

C3

COM

ORDERING GUIDE

Temperature Package

Model Range Option

*

AD421BN –40°C to +85°C N-16

AD421BR –40°C to +85°C R-16

AD421BRRL –40°C to +85°C R-16; Reeled SOIC

EVAL-AD421EB Evaluation Board

*N = Plastic DIP, R = SOIC.

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection.

Although these devices feature proprietary ESD protection circuitry, permanent damage may

occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD

precautions are recommended to avoid performance degradation or loss of functionality.

–4–

REV. C

AD421

PIN FUNCTION DESCRIPTIONS

Pin

No. Mnemonic Function

1 REF OUT1 Reference Output 1. A precision +1.25 V reference is provided at this pin. It is intended as a precision ref-

erence source for other devices in the transmitter. REF OUT1 is a buffered output capable of providing up

to 0.5 mA to external circuitry. If REF OUT 1 is required to sink current, a resistive load of 100 kΩ to COM

should be added. (See Reference section.)

2 REF OUT2 Reference Output 2. A precision +2.5 V reference is provided at this pin. To operate the AD421 with its

own reference, REF OUT2 should be connected to REF IN. It can also be used as a precision reference

source for other devices in the transmitter. REF OUT2 is a buffered output capable of providing up to

0.5 mA to external circuitry.

3 REF IN Voltage Reference Input. The reference voltage for the AD421 is applied to this pin and it sets the span for

the AD421. The nominal reference voltage for the AD421 is +2.5 V for correct operation. This can be supplied using an external reference source or by using the part’s own REF OUT2 voltage.

4 LV Regulated Voltage Control Input. The LV input controls the loop gain of the servo amplifier to set V

With LV connected to COM, the regulator voltage is set to 5 V nominal. If the LV input is connected through

0.01 µF to V

V

, is 3 V nominal.

CC

, the regulated voltage is nominally 3.3 V. With LV connected to VCC the regulated voltage,

CC

5 LATCH DAC Latch Input. Logic Input. A rising edge of the LATCH signal loads the data from the serial input shift

register to the DAC latch and hence updates the output of the DAC. The number of clock cycles provided

between latch pulses determines whether the DAC is in alarm or normal current mode. (See Digital Interface section.)

6 CLOCK Data Clock Input. Data on the DATA input is clocked into the shift register on the rising edge of this

CLOCK input. The period of this clock equals the input serial data bit rate. This serial clock rate can be up

to 10 MHz. If 16 clock cycles are provided between LATCH pulses then the data on the DATA input is

accepted as normal 4–20 mA data. If more than 16 clock cycles are provided between LATCH pulses, the

data is assumed to be alarm current data (see Digital Interface section).

7 DATA Data Input. The data to be loaded to the AD421 input shift register is applied to this input. Data should be

valid on the rising edge of the CLOCK input.

8 LOOP RTN Loop Return Output. LOOP RTN is the return path for current flowing in the current loop.

9 COM Common. This is the reference potential for the AD421 analog and digital inputs and outputs and for the

voltage regulator output.

10 C3 Filtering Capacitor. A low dielectric absorption capacitor ceramic capacitor should be connected between

this pin and COM for internal filtering of the switched current sources.

11 C2 Filtering Capacitor. See C3 description.

12 C1 Filtering Capacitor. See C3 description.

13 DRIVE Output from the Voltage Regulator Loop. The DRIVE signal controls the external pass transistor to establish and

maintain the correct V

level programmed by the LV inputs while providing the necessary bias as the loop cur-

CC

rent is programmed from 4 mA to 20 mA.

14 COMP Compensation Capacitor Input. A capacitor connected between COMP and DRIVE is required to stabilize

the feedback loop formed with the regulator op amp and the external pass transistor.

15 BOOST This open collector pin sinks the necessary current from the loop so that the current flowing into BOOST

plus the current flowing into COM is equal to the programmed loop current.

16 V

CC

Power Supply. VCC is the power supply input of the AD421 and it also provides the voltage regulator output,

driven by the external pass transistor. It is used both to bias the AD421 itself and to provide power for the

rest of the smart transmitter circuitry. The LV input determines the regulated voltage output to be either

3 V, 3.3 V or 5 V nominal. Alternatively, a separate power supply can be connected to this pin to power the

AD421. VCC should be decoupled to COM with a 2.2 µF capacitor.

CC

.

REV. C

–5–

Loading...

Loading...