Analog Devices AD1896YRSRL, AD1896YRS Datasheet

192 kHz Stereo Asynchronous

a

FEATURES

Automatically Senses Sample Frequencies

No Programming Required

Attenuates Sample Clock Jitter

3.3 V–5 V Input and 3.3 V Core Supply Voltages

Accepts 16-/18-/20-/24-Bit Data

Up to 192 kHz Sample Rate

Input/Output Sample Ratios from 7.75:1 to 1:8

Bypass Mode

Multiple AD1896 TDM Daisy-Chain Mode

Multiple AD1896 Matched-Phase Mode

142 dB Signal-to-Noise and Dynamic Range

(A-Weighted, 20 Hz–20 kHz BW)

Up to –133 dB THD + N

Linear Phase FIR Filter

Hardware Controllable Soft Mute

Supports 256 f

Clock

Flexible Three-Wire Serial Data Port with Left-Justified,

2

S, Right-Justified (16-,18-, 20-, 24-Bits), and TDM

I

Serial Port Modes

Master/Slave Input and Output Modes

28-Lead SSOP Plastic Package

APPLICATIONS

Home Theater Systems, Studio Digital Mixers, Auto-

motive Audio Systems, DVD, Set-Top Boxes, Digital

Audio Effects Processors, Studio-to-Transmitter

Links, Digital Audio Broadcast Equipment, Digital

Tape Varispeed Applications

PRODUCT OVERVIEW

The AD1896 is a 24-bit, high-performance, single-chip, secondgeneration asynchronous sample rate converter. Based upon

Analog Devices Inc. experience with its first asynchronous

sample rate converter, the AD1890, the AD1896 offers improved

performance and additional features. This improved performance

includes a THD + N range of –117 dB to –133 dB depending

on sample rate and input frequency, 142 dB (A-Weighted)

dynamic range, 192 kHz sampling frequencies for both input and

output sample rates, improved jitter rejection, and 1:8 upsampling

and 7.75:1 downsampling ratios. Additional features include

more serial formats, a bypass mode, better interfacing to digital

signal processors, and a matched phase mode.

The AD1896 has a 3-wire interface for the serial input and

output ports that supports left-justified, I

(16-, 18-, 20-, 24-bit) modes. Additionally, the serial output

*Patents pending.

, 512 fS or 768 fS Master Mode

S

2

S, and right-justified

Sample Rate Converter

AD1896*

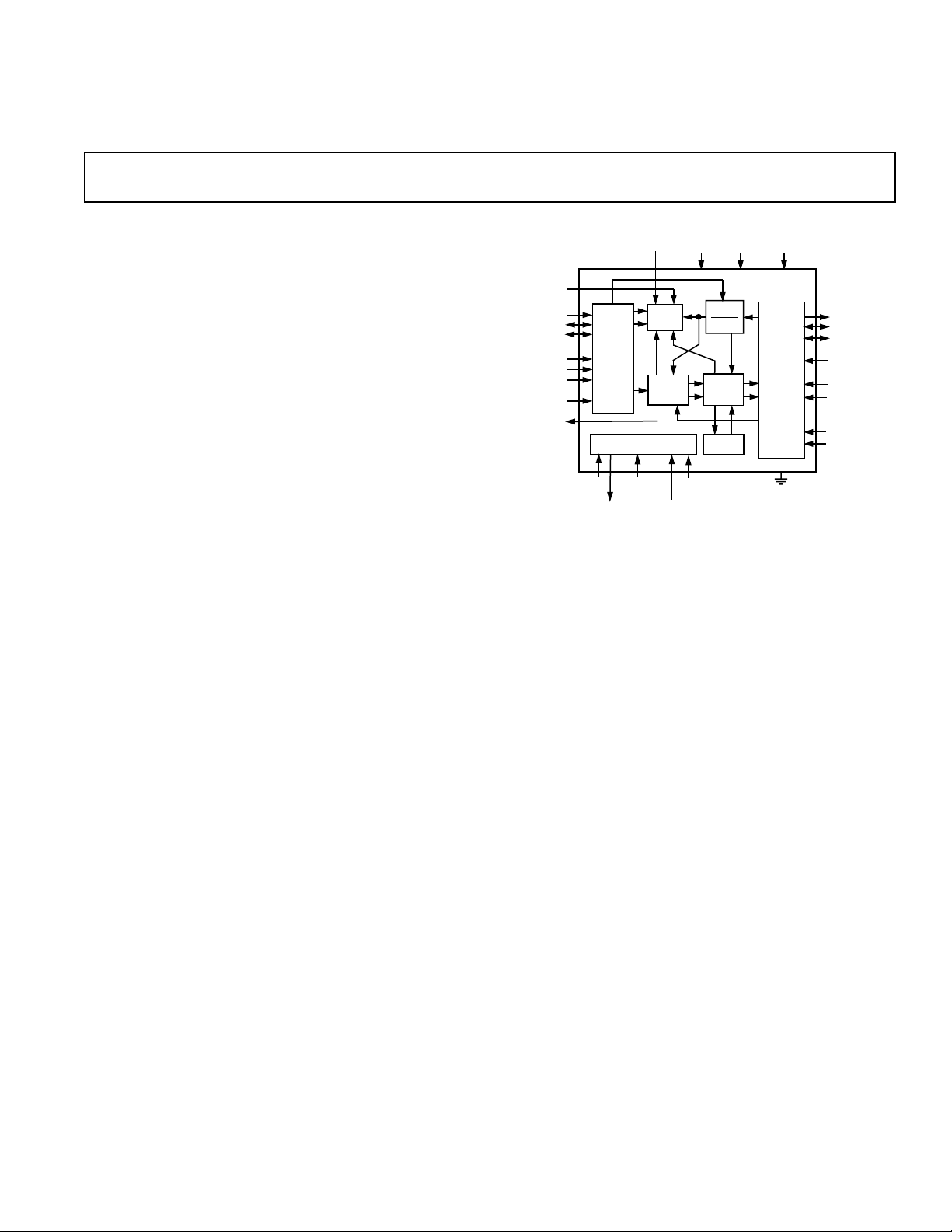

FUNCTIONAL BLOCK DIAGRAM

IN

VDD_CORE

AD1896

SERIAL

OUTPUT

(Continued on page 15)

SDATA_O

SCLK_O

LRCLK_O

TDM_IN

SMODE_O_0

SMODE_O_1

WLNGTH_O_0

WLNGTH_O_1

, 512 × fS and

S

20

MUTE_I

SDATA_I

SCLK_I

LRCLK_I

SMODE_IN_0

SMODE_IN_1

SMODE_IN_2

BYPASS

MUTE_O

MCLK_I

MCLK_O

GRPDLYS VDD_IO

SERIAL

INPUT

CLOCK DIVIDER

MSMODE_0

RESET

FIFO

DIGITAL

PLL

MSMODE_2

MSMODE_1

FS

OUT

FS

FIR

FILTER

ROM

port supports TDM mode for daisy chaining multiple AD1896’s to

a digital signal processor. The serial output data is dithered down

to 20, 18 or 16 bits when 20-, 18- or 16-bit output data is selected.

The AD1896 sample rate converts the data from the serial input

port to the sample rate of the serial output port. The sample rate

at the serial input port can be asynchronous with respect to the

output sample rate of the output serial port. The master clock to

the AD1896, MCLK, can be asynchronous to both the serial

input and output ports.

MCLK can either be generated off-chip or on-chip by the AD1896

master clock oscillator. Since MCLK can be asynchronous to the

input or output serial ports, a crystal can be used to generate

MCLK internally to reduce noise and EMI emissions on the

board. When MCLK is synchronous to either the output or input

serial port, the AD1896 can be configured in a master mode where

MCLK is divided down and used to generate the left/right

and bit clocks for the serial port that is synchronous to MCLK.

The AD1896 supports master modes of 256 × f

768 × f

Conceptually, the AD1896 interpolates the serial input data by

a rate of 2

for both input and output serial ports.

S

20

and samples the interpolated data stream by the

output sample rate. In practice, a 64-tap FIR filter with 2

polyphases, a FIFO, a digital servo loop that measures the time

difference between input and output samples within 5 ps, and a

digital circuit to track the sample rate ratio are used to perform

the interpolation and output sampling. Refer to the Theory of

Operation section. The digital servo loop and sample rate ratio

circuit automatically track the input and output sample rates.

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2001

AD1896–SPECIFICATIONS

TEST CONDITIONS UNLESS OTHERWISE NOTED

Supply Voltages

VDD_CORE 3.3 V

VDD_IO 5.0 V or 3.3 V

Ambient Temperature 25°C

Input Clock 30.0 MHz

Input Signal 1.000 kHz, 0 dBFS

Measurement Bandwidth 20 to f

Word Width 24 Bits

Load Capacitance 50 pF

Input Voltage HI 2.4 V

Input Voltage LO 0.8 V

Specifications subject to change without notice.

DIGITAL PERFORMANCE (VDD_CORE = 3.3 V 5%, VDD_IO = 5.0 V 10%)

Parameter Min Typ Max Unit

Resolution 24 Bits

Sample Rate @ MCLK_I = 30 MHz 6 215 kHz

Sample Rate (@ Other Master Clocks)

Sample Rate Ratios

Upsampling 1:8

Downsampling (Short GRPDLYS) 7.75:1

Downsampling (Long GRPDLYS) 7.0:1

Dynamic Range

(20 Hz to f

2

/2, 1 kHz, –60 dBFS Input) A-Weighted

S_OUT

Worst-Case (192 kHz:48 kHz) 132 dB

44.1 kHz:48 kHz 142 dB

48 kHz:44.1 kHz 141 dB

48 kHz:96 kHz 142 dB

44.1 kHz:192 kHz 141.5 dB

96 kHz:48 kHz 140 dB

192 kHz:32 kHz 140 dB

(20 Hz to f

/2, 1 kHz, –60 dBFS Input) No Filter

S_OUT

Worst-Case (192 kHz:48 kHz) 132 dB

44.1 kHz:48 kHz 139 dB

48 kHz:44.1 kHz 139 dB

48 kHz:96 kHz 139 dB

44.1 kHz:192 kHz 137 dB

96 kHz:48 kHz 137 dB

192 kHz:32 kHz 138 dB

Total Harmonic Distortion + Noise

(20 Hz to f

Worst-Case (32 kHz:48 kHz)

/2, 1 kHz, 0 dBFS Input) No Filter

S_OUT

3

44.1 kHz:48 kHz –123 dB

48 kHz:44.1 kHz –124 dB

48 kHz:96 kHz –120 dB

44.1 kHz:192 kHz –123 dB

96 kHz:48 kHz –132 dB

192 kHz:32 kHz –133 dB

Interchannel Gain Mismatch 0.0 dB

Interchannel Phase Deviation 0.0 Degrees

Mute Attenuation (24 Bits Word Width) –144 dB

NOTES

1

Lower sampling rates than given by this formula are possible, but the jitter rejection will decrease.

2

Refer to the Typical Performance Characteristics section for DNR and THD + N numbers over wide range of Input and Output Sample Rates.

3

For any other sample rate ratio, the minimum THD + N will be better than –117 dB. Please refer to detailed performance plots.

Specifications subject to change without notice.

S_OUT

1

2

/2 Hz

MCLK_I/5000 ≤ f

≤ MCLK_I/138 kHz

S_OUT

–117 dB

–2–

REV. 0

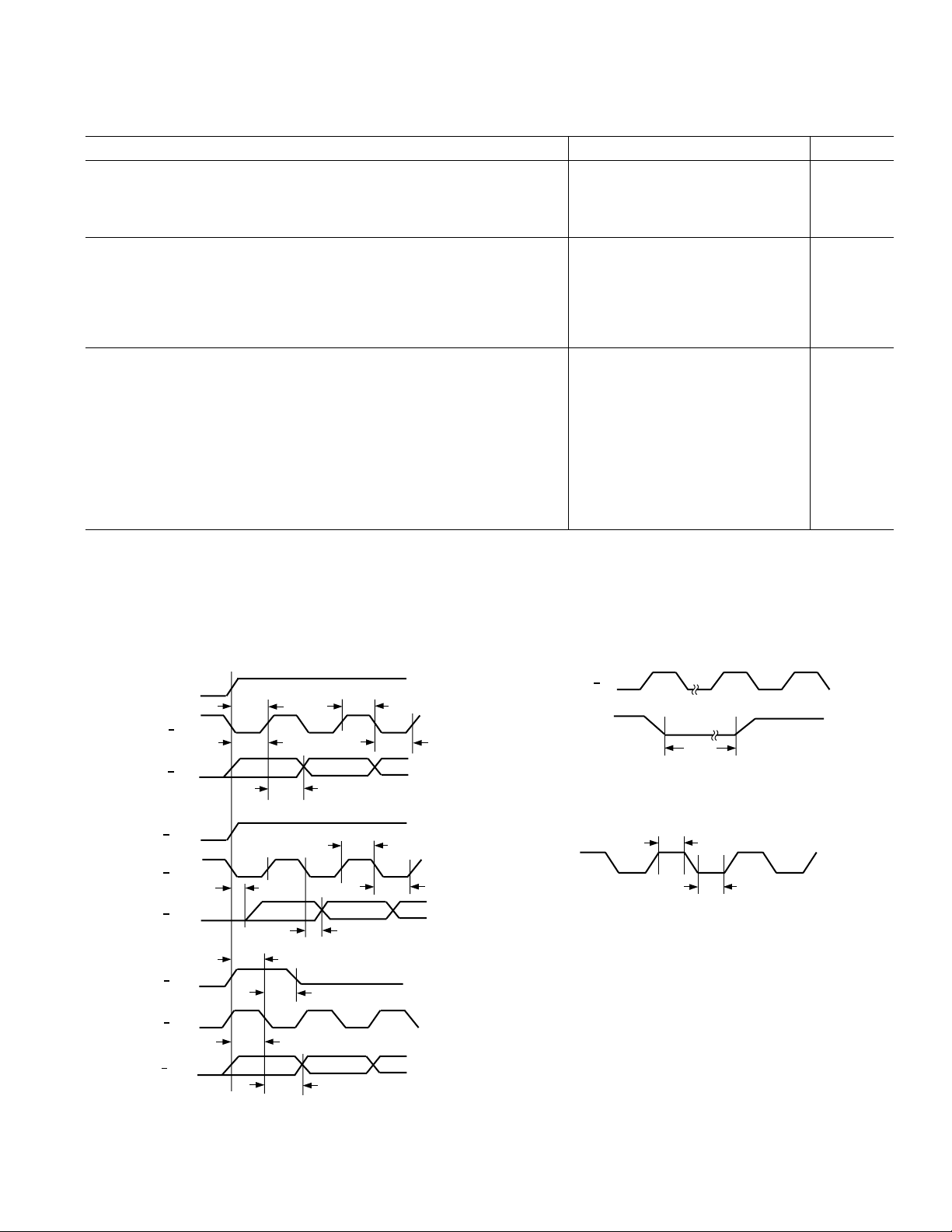

DIGITAL TIMING (–40C < TA < +105C, VDD_CORE = 3.3 V 5%, VDD_IO = 5.0 V 10%)

Parameter

t

MCLKI

f

MCLK

t

MPWH

t

MPWL

1

Min Max Unit

MCLK_I Period 33.3 ns

MCLK_I Frequency 30.0

MCLK_I Pulsewidth High 8 ns

MCLK_I Pulsewidth Low 12 ns

Input Serial Port Timing

t

LRIS

t

SIH

t

SIL

t

DIS

t

DIH

LRCLK_I Setup to SCLK_I 8 ns

SCLK_I Pulsewidth High 8 ns

SCLK_I Pulsewidth Low 8 ns

SDATA_I Setup to SCLK_I Rising Edge 8 ns

SDATA_I Hold from SCLK_I Rising Edge 3 ns

Output Serial Port Timing

t

TDMS

t

TDMH

t

DOPD

t

DOH

t

LROS

t

LROH

t

SOH

t

SOL

t

RSTL

NOTES

1

Refer to Timing Diagram Section.

2

The maximum possible sample rate is: FS

3

f

of up to 34 MHz is possible under the following conditions: 0°C < TA < 70°C, 45/55 or better MCLK_I duty cycle.

MCLK

Specifications subject to change without notice.

TDM_IN Setup to SCLK_O Falling Edge 3 ns

TDM_IN Hold from SCLK_O Falling Edge 3 ns

SDATA_O Propagation Delay from SCLK_O, LRCLK_O 20 ns

SDATA_O Hold from SCLK_O 3 ns

LRCLK_O Setup to SCLK_O (TDM Mode Only) 5 ns

LRCLK_O Hold from SCLK_O (TDM Mode Only) 3 ns

SCLK_O Pulsewidth High 10 ns

SCLK_O Pulsewidth Low 5 ns

RESET Pulsewidth LO 200 ns

= f

MCLK

/138.

MAX

2, 3

AD1896

MHz

TIMING DIAGRAMS

LRCLK_I

t

t

t

DOH

SIH

SOH

t

SIL

t

SOL

SCLK

SDATA

LRCLK

SCLK

SDATA

LRCLK

SCLK

TDM

t

LRIS

I

t

DIS

I

t

DIH

O

O

t

DOPD

O

t

O

O

IN

LROS

t

TDMS

t

LROH

t

TDMH

Figure 1. Input and Output Serial Port Timing (SCLK I/O,

LRCLK I/O, SDATA I/O, TDM_IN)

MCLK I

RESET

t

RSTL

Figure 2.

t

MPWH

RESET

t

MPWL

Timing

Figure 3. MCLK_I Timing

REV. 0

–3–

AD1896–SPECIFICATIONS

DIGITAL FILTERS (VDD_CORE = 3.3 V 5%, VDD_IO = 5.0 V 10%)

Parameter Min Typ Max Unit

Passband 0.4535 f

S_OUT

Passband Ripple ±0.016 dB

Transition Band 0.4535 f

Stop Band 0.5465 f

S_OUT

S_OUT

0.5465 f

S_OUT

Stop Band Attenuation –125 dB

Group Delay Refer to the Group Delay Equations Section

Specifications subject to change without notice.

DIGITAL I/O CHARACTERISTICS (VDD_CORE = 3.3 V 5%, VDD_IO = 5.0 V 10%)

Parameter Min Typ Max Unit

Input Voltage HI (V

Input Voltage LO (V

Input Leakage (I

Input Leakage (I

Input Leakage (I

Input Leakage (I

) 2.4

IH

) 0.8 V

IL

@ VIH = 5 V)

IH

@ VIL = 0 V)

IL

@ VIH = 5 V)

IH

@ VIL = 0 V)

IL

1

1

2

2

+2 µA

–2 µA

+150 µA

–150 µA

Input Capacitance 5 10 pF

Output Voltage HI (V

Output Voltage LO (V

Output Source Current HI (I

@ IOH = –4 mA) VDD_CORE – 0.5 VDD_CORE – 0.4 V

OH

@ IOL = +4 mA) 0.2 0.5 V

OL

)–4mA

OH

Output Sink Current LO (IOL)+4mA

NOTES

1

All input pins except GRPDLYS.

2

GRPDLYS pin only.

Specifications subject to change without notice.

Hz

Hz

Hz

POWER SUPPLIES

Parameter Min Typ Max Unit

Supply Voltage

VDD_CORE 3.135 3.3 3.465 V

VDD_IO* VDD_CORE 3.3/5.0 5.5 V

Active Supply Current

I_CORE_ACTIVE

48 kHz:48 kHz 20 mA

96 kHz:96 kHz 26 mA

192 kHz:192 kHz 43 mA

I_IO_ACTIVE 2 mA

Power-Down Supply Current: (All Clocks Stopped)

I_CORE_PWRDN 0.5 mA

I_IO_PWRDN 10 µA

*For 3.3 V tolerant Inputs, VDD_IO supply should be set to 3.3 V; however, VDD_CORE supply voltage should not exceed VDD_IO.

Specifications subject to change without notice.

–4–

REV. 0

AD1896

WARNING!

ESD SENSITIVE DEVICE

POWER SUPPLIES (VDD_CORE = 3.3 V 5%, VDD_IO = 5.0 V 10%)

Parameter Min Typ Max Unit

Total Active Power Dissipation

48 kHz:48 kHz 65 mW

96 kHz:96 kHz 85 mW

192 kHz:192 kHz 132 mW

Total Power Down Dissipation: (RESET LO) 2 mW

Specifications subject to change without notice.

TEMPERATURE RANGE

Parameter Min Typ Max Unit

Specifications Guaranteed 25 °C

Functionality Guaranteed –40 +105 °C

Storage –55 +150 °C

Thermal Resistance, θJA (Junction-to-Ambient) 109 °C/W

Specifications subject to change without notice.

ABSOLUTE MAXIMUM RATINGS*

Parameter Min Max Unit

Power Supplies

VDD_CORE –0.3 +3.6 V

VDD_IO –0.3 +6.0 V

Digital Inputs

Input Current ±10 mA

Input Voltage DGND – 0.3 VDD_IO + 0.3 V

Ambient Temperature (Operating) –40 +105 °C

*Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions

for extended periods may affect device reliability.

ORDERING GUIDE

Model Temperature Range Package Description Package Option

AD1896YRS –40°C to +105°C 28-Lead SSOP RS-28

AD1896YRSRL –40°C to +105°C 28-Lead SSOP RS-28 on 13" Reel

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

the AD1896 features proprietary ESD protection circuitry, permanent damage may occur on

devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are

recommended to avoid performance degradation or loss of functionality.

REV. 0

–5–

AD1896

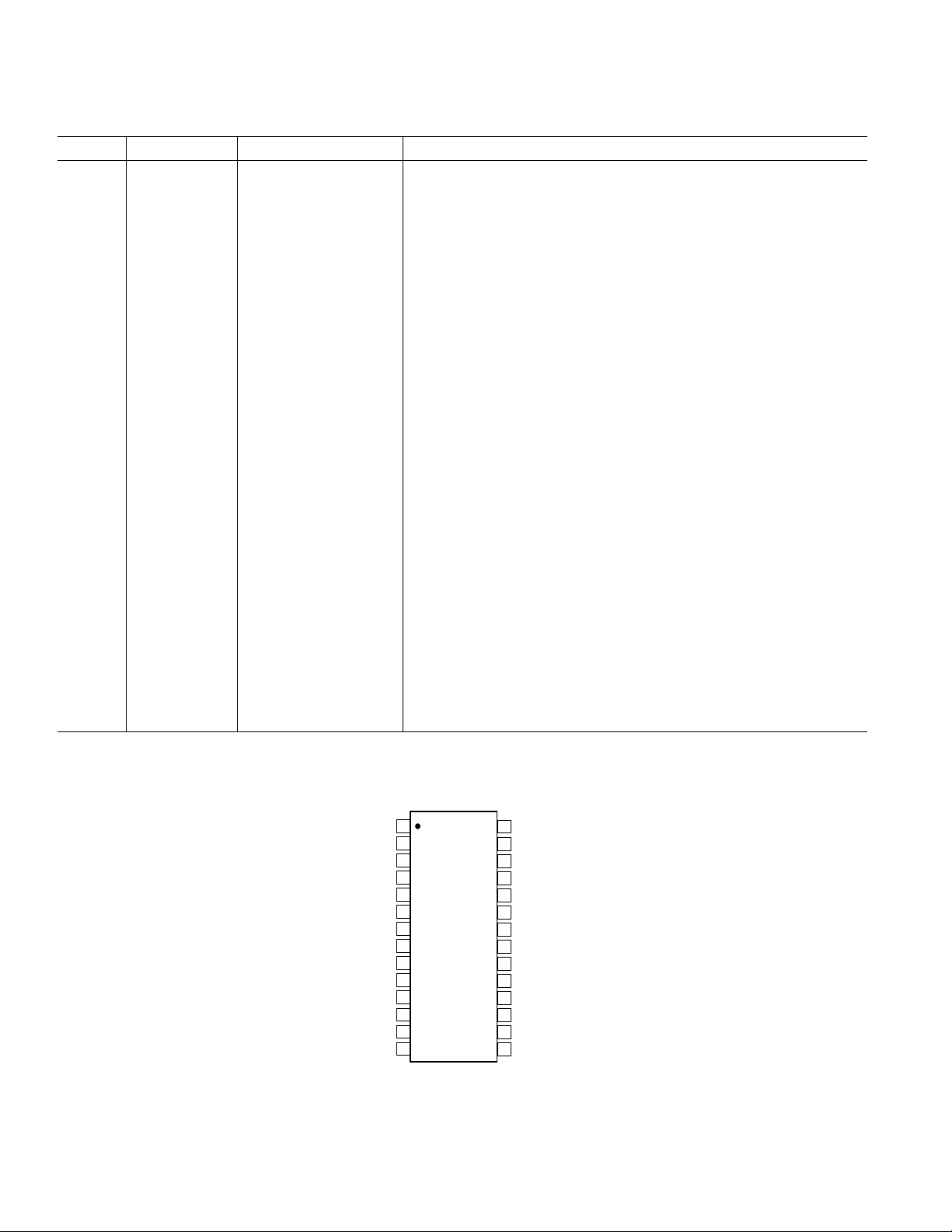

PIN FUNCTION DESCRIPTIONS

Pin No. IN/OUT Mnemonic Description

1 IN GRPDLYS Group Delay HI = Short, LO = Long

2 IN MCLK_IN Master Clock or Crystal Input

3 OUT MCLK_OUT Master Clock Output or Crystal Output

4 IN SDATA_I Input Serial Data (at Input Sample Rate)

5 IN/OUT SCLK_I Master/Slave Input Serial Bit Clock

6 IN/OUT LRCLK_I Master/Slave Input Left/Right Clock

7 IN VDD_IO 3.3 V/5 V Input/Output Digital Supply Pin

8 IN DGND Digital Ground Pin

9 IN BYPASS ASRC Bypass Mode, Active High

10 IN SMODE_IN_0 Input Port Serial Interface Mode Select Pin 0

11 IN SMODE_IN_1 Input Port Serial Interface Mode Select Pin 1

12 IN SMODE_IN_2 Input Port Serial Interface Mode Select Pin 2

13 IN RESET Reset Pin, Active Low

14 IN MUTE_IN Mute Input Pin— Active HI Normally Connected to MUTE_OUT

15 OUT MUTE_OUT Output Mute Control – Active HI

16 IN WLNGTH_OUT_1 Hardware Selectable Output Wordlength—Select Pin 1

17 IN WLNGTH_OUT_0 Hardware Selectable Output Wordlength—Select Pin 0

18 IN SMODE_OUT_1 Output Port Serial Interface Mode Select Pin 1

19 IN SMODE_OUT_0 Output Port Serial Interface Mode Select Pin 0

20 IN TDM_IN Serial Data Input* (only for Daisy Chain Mode). Ground when not used.

21 IN DGND Digital Ground Pin

22 IN VDD_CORE 3.3 V Digital Supply Pin

23 OUT SDATA_O Output Serial Data (at Output Sample Rate)

24 IN/OUT LRCLK_O Master/Slave Output Left/Right Clock

25 IN/OUT SCLK_O Master/Slave Output Serial Bit Clock

26 IN MMODE_0 Master/Slave Clock Ratio Mode Select Pin 0

27 IN MMODE_1 Master/Slave Clock Ratio Mode Select Pin 1

28 IN MMODE_2 Master/Slave Clock Ratio Mode Select Pin 2

*Also used to input matched-phase mode data.

GRPDLYS

MCLK_IN

MCLK_OUT

SDATA_I

SCLK_I

LRCLK_I

VDD_IO

DGND

BYPASS

SMODE_IN_0

SMODE_IN_1

SMODE_IN_2

RESET

MUTE_IN

PIN CONFIGURATION

1

2

3

4

AD1896

TOP VIEW

5

(NOT TO SCALE

6

7

8

9

10

11

12

13

14

28

MMODE_2

27

MMODE_1

26

MMODE_0

25

SCLK_O

24

LRCLK_O

)

23

SDATA_O

22

VDD_CORE

21

DGND

TDM_IN

20

19

SMODE_OUT_0

18

SMODE_OUT_1

17

WLNGTH_OUT_0

16

WLNGTH_OUT_1

15

MUTE_OUT

–6–

REV. 0

–200

0

–180

–160

–140

–120

–100

–80

–60

–40

–20

10 9020 30 40 50 60 70 80

FREQUENCY – kHz

dBFS

–20

–40

–60

–80

–100

dBFS

–120

–140

–160

–180

–200

0

2.5 22.55.0 7.5 10.0 12.5 15.0 17.5 20.0

FREQUENCY – kHz

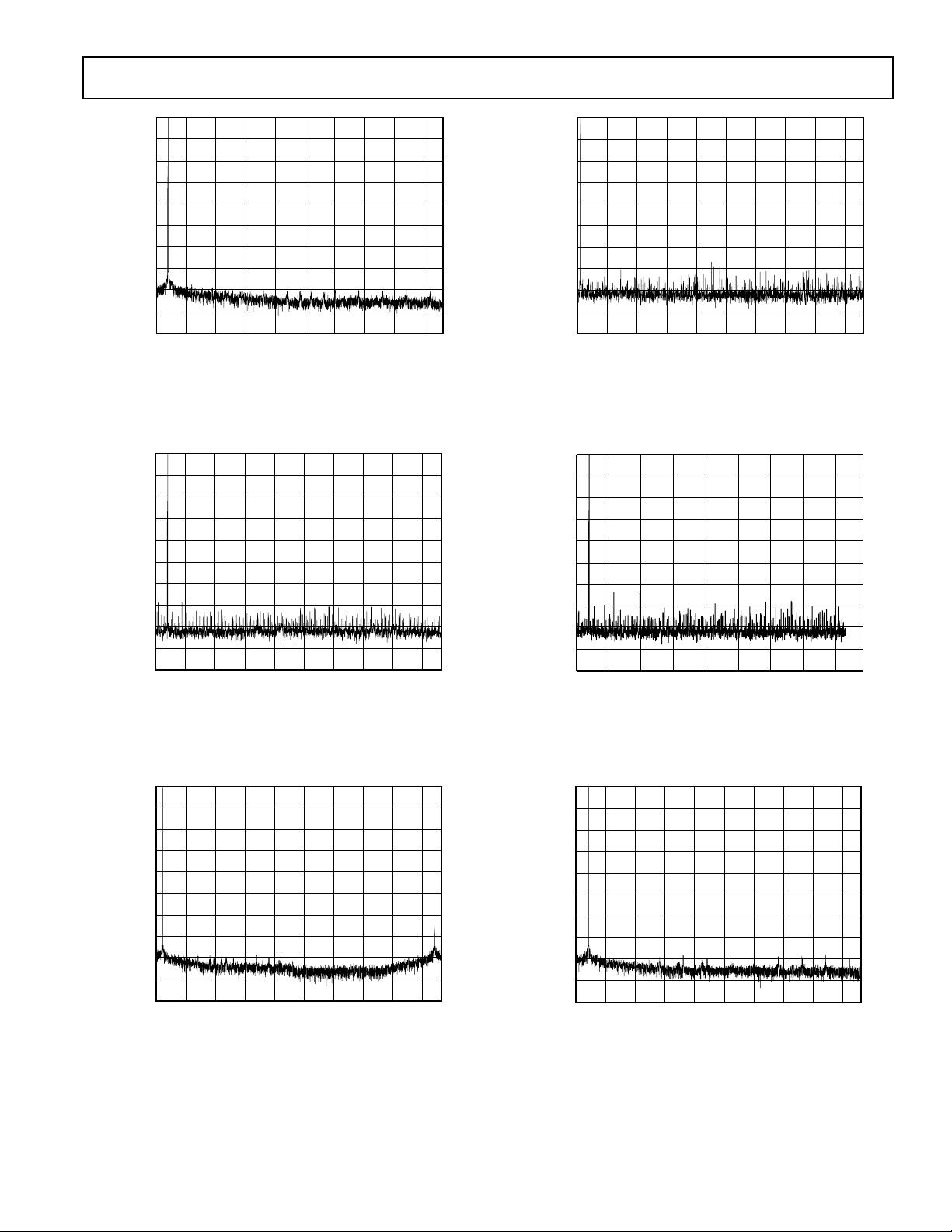

Typical Performance Characteristics–A

D1896

TPC 1. Wideband FFT Plot (16k Points) 0 dBFS 1 kHz Tone,

48 kHz:48 kHz (Asynchronous)

0

–20

–40

–60

–80

–100

dBFS

–120

–140

–160

–180

–200

2.5 22.5

TPC 2. Wideband FFT Plot (16k Points) 0 dBFS 1 kHz Tone,

44.1 kHz:48 kHz (Asynchronous)

0

–20

–40

–60

–80

–100

dBFS

–120

–140

–160

–180

–200

54510 15 20 25 30 35 40

TPC 3. Wideband FFT Plot (16k Points) 48 kHz:96 kHz,

0 dBFS 1 kHz Tone

REV. 0

5.0

7.5 10.0 12.5 15.0 17.5 20.0

FREQUENCY – kHz

FREQUENCY – kHz

TPC 4. Wideband FFT Plot (16k Points) 44.1 kHz:192 kHz,

0 dBFS 1 kHz Tone

0

–20

–40

–60

–80

–100

dBFS

–120

–140

–160

–180

–200

2.5 5.0 7.5 10.0 12.5 15.0 17.5 20.0

FREQUENCY – kHz

TPC 5. Wideband FFT Plot (16k Points) 48 kHz:44.1 kHz,

0 dBFS 1 kHz Tone

0

–20

–40

–60

–80

–100

dBFS

–120

–140

–160

–180

–200

2.5 5.0 7.5 10.0 12.5 15.0 17.5 20.0

FREQUENCY – kHz

TPC 6. Wideband FFT Plot (16k Points) 96 kHz:48 kHz,

0 dBFS 1 kHz Tone

–7–

22.5

AD1896

0

–20

–40

–60

–80

–100

dBFS

–120

–140

–160

–180

–200

2.5 5.0 7.5 10.0 12.5 15.0 17.5 20.0

FREQUENCY – kHz

22.5

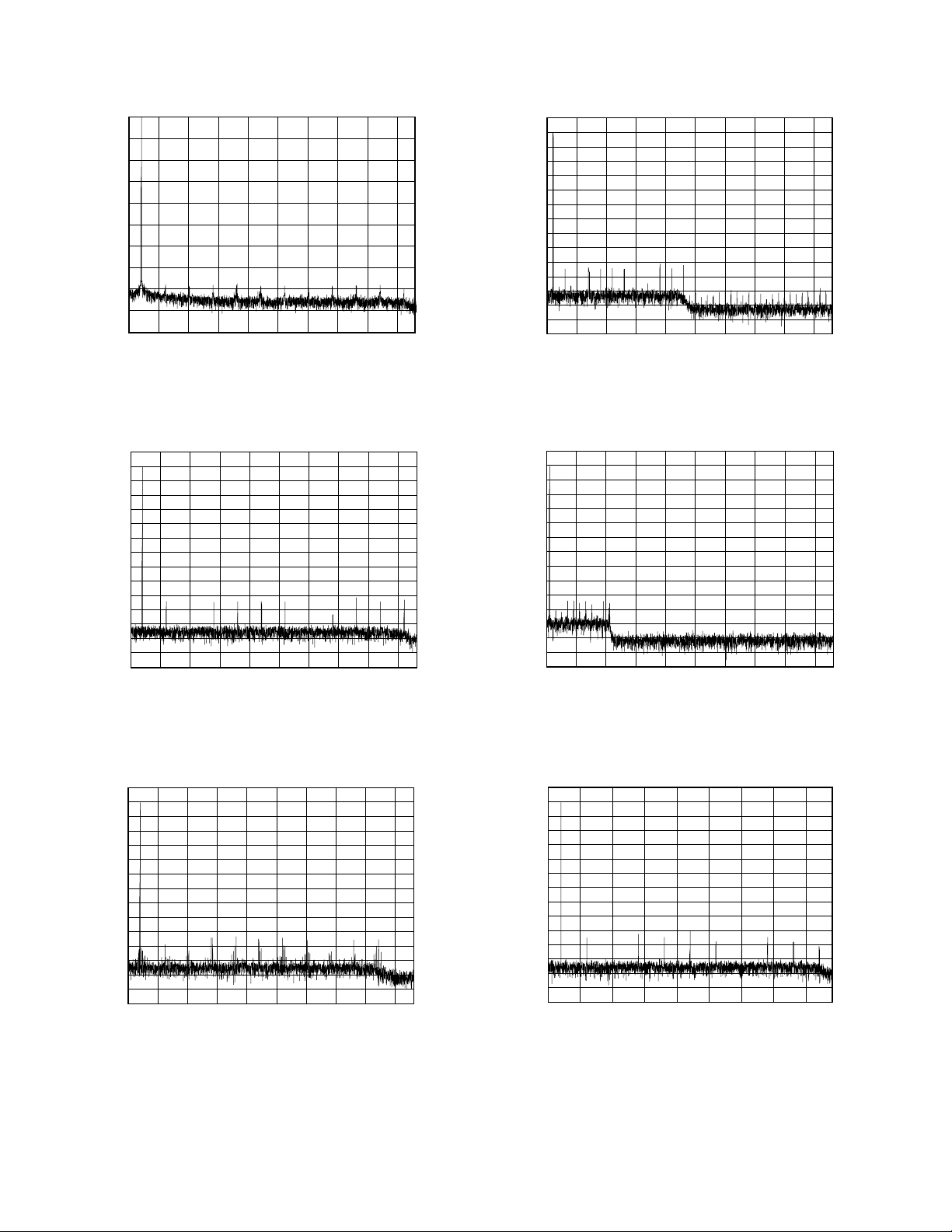

TPC 7. Wideband FFT Plot (16k Points) 192 kHz:48 kHz,

0 dBFS 1 kHz Tone

–50

–60

–70

–80

–90

–100

–110

–120

–130

dBFS

–140

–150

–160

–170

–180

–190

–200

2.5 22.55.0 7.5 10.0 12.5 15.0 17.5 20.0

FREQUENCY – kHz

–50

–60

–70

–80

–90

–100

–110

–120

–130

dBFS

–140

–150

–160

–170

–180

–190

–200

54510 15 20 25 30 35 40

FREQUENCY – kHz

TPC 10. Wideband FFT Plot (16k Points) 48 kHz:96 kHz,

–60 dBFS 1 kHz Tone

–50

–60

–70

–80

–90

–100

–110

–120

dBFS

–130

–140

–150

–160

–170

–180

–190

–200

10 9020 30 40 50 60 70 80

FREQUENCY – kHz

TPC 8. Wideband FFT Plot (16k Points) –60 dBFS 1 kHz

Tone, 48 kHz:48 kHz (Asynchronous)

–50

–60

–70

–80

–90

–100

–110

–120

–130

dBFS

–140

–150

–160

–170

–180

–190

–200

2.5 22.55.0 7.5 10.0 12.5 15.0 17.5 20.0

FREQUENCY – kHz

TPC 9. Wideband FFT Plot (16k Points) 44.1 kHz:48 kHz,

–60 dBFS 1 kHz Tone

TPC 11. Wideband FFT Plot (16k Points) 44.1 kHz:192 kHz,

–60 dBFS 1 kHz Tone

–50

–60

–70

–80

–90

–100

–110

–120

–130

dBFS

–140

–150

–160

–170

–180

–190

–200

2.5 7.5 12.5 17.5

5.0 10.0 15.0 20.0

FREQUENCY – kHz

TPC 12. Wideband FFT Plot (16k Points) 48 kHz:44.1 kHz,

–60 dBFS 1 kHz Tone

–8–

REV. 0

Loading...

Loading...