24-Bit - ADC

0

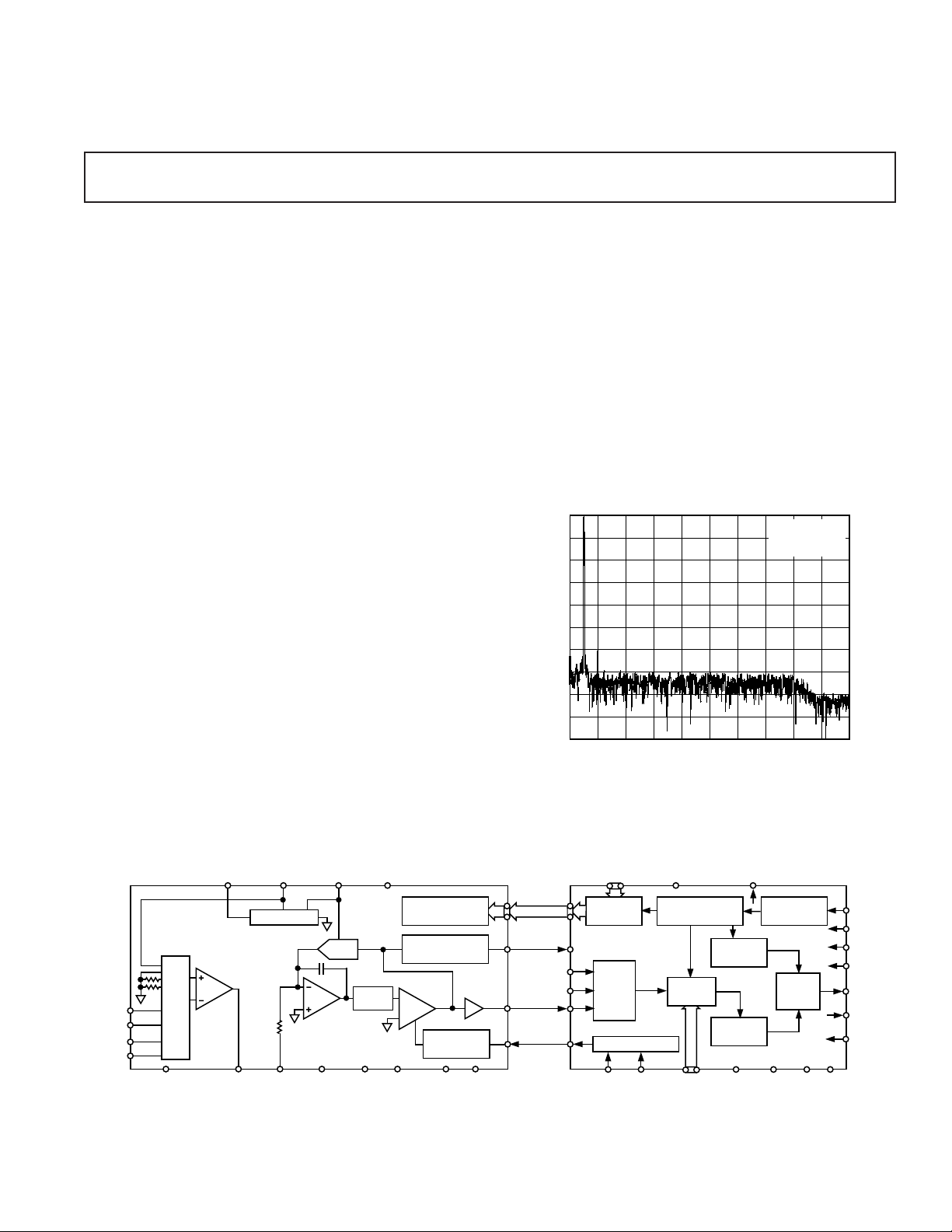

FREQUENCY – Hz

–120

–200

0

50

AMPLITUDE – dBr

100 150 200 250 300

–20

–100

–140

–180

–60

–80

–160

–40

350 400 450 500

fIN = 24.4Hz

SNR = 116.7dB

THD = –120.6dB

a

FEATURES

AD1555

Fourth Order - Modulator

Large Dynamic Range

116 dB Min, 120 dB Typical @ 1 ms

117 dB Typical @ 0.5 ms

Low Input Noise: 80 nV rms @ 4 ms with

Gain of 34,128

Low Distortion: –111 dB Max, –120 dB Typical

Low Intermodulation: 122 dB

Sampling Rate at 256 kSPS

Very High Jitter Tolerance

No External Antialias Filter Required

Programmable Gain Front End

Input Range: 2.25 V

Robust Inputs

Gain Settings: 1, 2.5, 8.5, 34, 128

Common-Mode Rejection (DC to 1 kHz)

93 dB Min, 101 dB Typical @ Gain of 1

77 mW Typical Low Power Dissipation

Standby Modes

AD1556

FIR Digital Filter/Decimator

Serial or Parallel Selection of Configuration

Output Word Rates: 250 SPS to 16 kSPS

6.2 mW Typ Low Power Dissipation

70 W in Standby Mode

Reference Design and Evaluation Board with

Software Available

APPLICATIONS

Seismic Data Acquisition Systems

Chromatography

Automatic Test Equipment

GENERAL DESCRIPTION

The AD1555 is a complete sigma-delta modulator, combined

with a programmable gain amplifier intended for low frequency,

with Low Noise PGA

AD1555/AD1556

high dynamic range measurement applications. The AD1555

outputs a ones-density bitstream proportional to the analog

input. When used in conjunction with the AD1556 digital filter/

decimator, a high performance ADC is realized.

The continuous-time analog modulator input architecture avoids

the need for an external antialias filter. The programmable gain

front end simplifies system design, extends the dynamic range,

and reduces the system board area. Low operating power and

standby modes makes the AD1555 ideal for remote battery-powered data acquisition systems.

The AD1555 is fabricated on Analog Devices’ BiCMOS process

that has high performance bipolar devices along with CMOS

transistors. The AD1555 and AD1556 are packaged, respectively,

in 28-lead PLCC and 44-lead MQFP packages and are specified

from –55°C to +85°C (AD1556 and AD1555 B Grade) and from

0°C to 85°C (AD1555 A Grade).

Figure 1. FFT Plot, Full-Scale AIN Input, Gain of 1

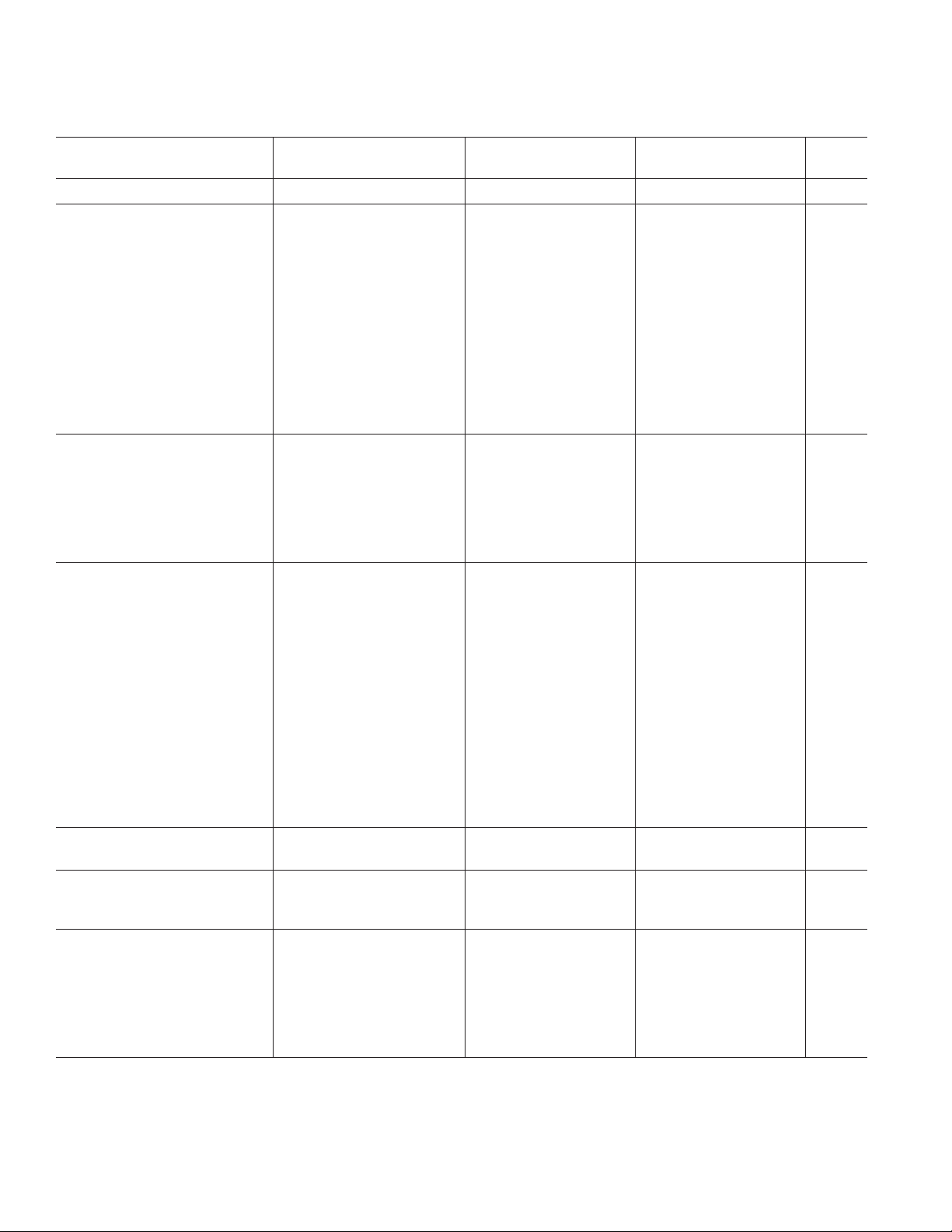

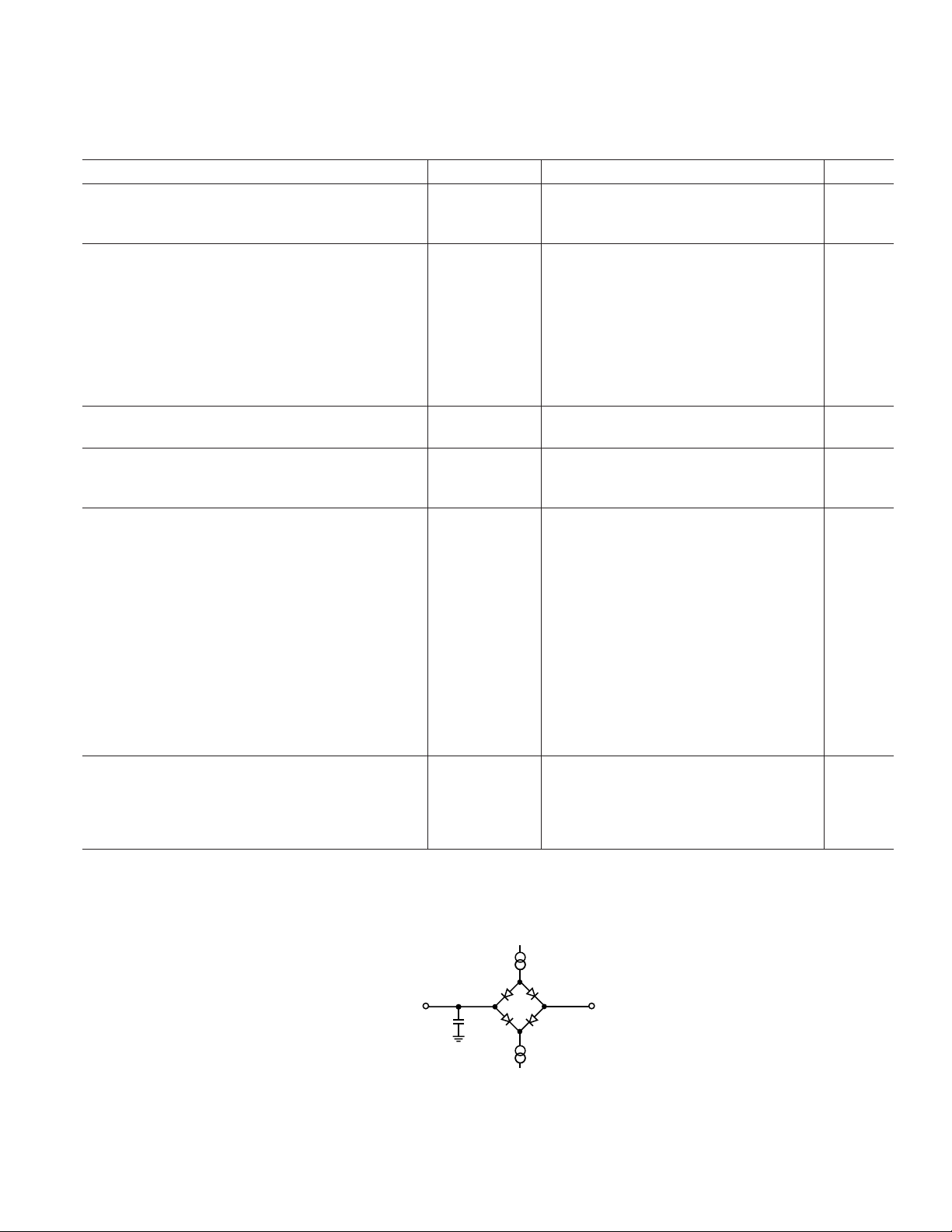

FUNCTIONAL BLOCK DIAGRAM

REFIN REFCAP2 REFCAP1 AGND3

MODE CONTROL

OVERVOLTAGE

DETECTION

–V

A

LOGIC

CLOCK

GENERATION

L

AIN (+)

AIN (–)

TIN (+)

TIN (–)

MUX

PGA

REF DIVIDER

DAC

LOOP

FILTER

AD1555

+V

AGND2MODINPGAOUTAGND1 CLKIN SYNC BW0...BW2 RESET PWRDN GND V

A

REV. B

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

H/S ERRORPGA0...PGA4

CB0...CB4

MFLG

CSEL

TDATA

MDATA

MCLK

DGNDV

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 2002

PGA

CONTROL

INPUT

MUX

CLOCK DIVIDER

CONFIGURATION

REGISTER

STATUS

REGISTER

DIGITAL

FILTER

DATA

REGISTER

INPUT SHIFT

REGISTER

DATA

OUTPUT

MUX

AD1556

DIN

SCLK

CS

R/W

DOUT

DRDY

RSEL

L

AD1555/AD1556

(+VA = +5 V; –VA = –5 V; VL = 5 V; AGND = DGND = 0 V; MCLK = 256 kHz; TA = T

T

AD1555–SPECIFICATIONS

Parameter Notes Min Typ Max Min Typ Max Unit

PGA Gain Settings 1, 2.5, 8.5, 34, 128

AC ACCURACY

Dynamic Range

Total Harmonic Distortion

Jitter Tolerance

Intermodulation Distortion

DC ACCURACY

Absolute Gain Error

Gain Stability Over Temperature

5, 6

Offset

Offset Drift

ANALOG INPUT

Full-Scale Nondifferential Input MODIN ±2.25 ±2.25 V

Input Impedance MODIN 20 20 k⍀

Full-Scale Differential Input PGA Gain of 1 ±2.25 ±2.25 V

Differential Input Impedance AIN, TIN Inputs 140 140 MΩ

Common-Mode Range ±2.25 ±2.25 V

Common-Mode Rejection Ratio V

Power Supply Rejection Ratio

AIN to TIN Crosstalk Isolation f

Differential Input Current 130 130 nA

TEMPERATURE RANGE

Specified Performance T

REFERENCE INPUT

Input Voltage Range 2.990 3.0 3.010 2.990 3.0 3.010 V

Input Current 130 130 µA

DIGITAL INPUTS OUTPUTS

V

IL

V

IH

I

IL

I

IH

V

OL

V

OH

5, 6

1

PGA Gain of 1 116.5 120 116 120 dB

PGA Gain of 2.5 116 119.5 115.5 119.5 dB

PGA Gain of 8.5 114 117.5 114 117.5 dB

PGA Gain of 34 104.5 109.5 104.5 109.5 dB

2

PGA Gain of 128 98 98 dB

PGA Gain of 1 –120 –111 –120 –107 dB

PGA Gain of 2.5 –116 –108 –116 –107 dB

PGA Gain of 8.5 –116 –106 –116 –105 dB

PGA Gain of 34 –115 –101 –115 –101 dB

3

4

5

PGA Gain of 128 –108 –108 dB

PGA Gain of 1 122 122 dB

PGA Gain of 1, 2.5 –3.5 +3.5 –3.5 +3.5 %

PGA Gain of 8.5 –4.5 +4.5 –4.5 +4.5 %

PGA Gain of 34 –10 +10 –10 +10 %

5

All PGA Gain –60 –60 mV

Other PGA Gain Settings

= ±2.25 V, fIN = 200 Hz

CM

PGA Gain of 1 93 101 91 101 dB

PGA Gain of 2.5 95 102 91.5 102 dB

PGA Gain of 8.5, 34 95.5 108 94.5 108 dB

PGA Gain of 128 108 108 dB

7

= 200 Hz 130 130 dB

IN

8

to T

MIN

9

I

SINK

I

SOURCE

MAX

= +2 mA 0.4 0.4 V

= –2 mA 2.4 2.4 V

, unless otherwise noted.)

MAX

AD1555BP AD1555AP

–55 +85 0 85 °C

–0.3 +0.8 –0.3 +0.8 V

2.0 VL + 0.3 2.0 VL + 0.3 V

–10 +10 –10 +10 µA

–10 +10 –10 +10 µA

300 300 ps

±15 ±15 ppm/°C

66µV/°C

See Table I

See Table I

50 50 dB

MIN

to

–2–

REV. B

AD1555/AD1556

AD1555BP AD1555AP

Parameter Notes Min Typ Max Min Typ Max Unit

POWER SUPPLIES

Recommended Operating Conditions

+V

A

–V

A

V

L

Quiescent Currents

Power Dissipation

10

)

I(+V

A

10

I(–VA)

) 30 42 30 42 µA

I(V

L

10

PGA in Standby Mode

In Power-Down Mode

11

11, 12

Reference Input = 3 V 650 650 µW

Reference Input = 0 V 250 250 µW

NOTES

1

Tested at the output word rate FO = 1 kHz. FO is the AD1556 output word rate, the inverse of the sampling rate. See Tables I, Ia, Ib for other output

word rates.

2

Tested with a full-scale input signal at approximately 24 Hz.

3

This parameter is guaranteed by design.

4

Tested at the output word rate FO = 1 kHz with input signals of 30 Hz and 50 Hz, each 6 dB down full scale.

5

This specification is for the AD1555 only and does not include the errors from external components as, for instance, the external reference.

6

This offset specification is referred to the modulator output.

7

Characterized with a 100 mV p-p sine wave applied separately to each supply.

8

Contact factory for extended temperature range.

9

Recommended Reference: AD780BR.

10

Specified with analog inputs grounded.

11

See Table III for configuration conditions.

12

Specified with MCLK input grounded.

Specifications subject to change without notice.

4.75 5 5.25 4.75 5 5.25 V

–5.25 –5 –4.75 –5.25 –5 –4.75 V

4.75 5 5.25 4.75 5 5.25 V

810 810 mA

8 9.5 8 9.5 mA

77 96 77 96 mW

56 70 56 70 mW

AD1556–SPECIFICATIONS

(VL = 2.85 V to 5.25 V; CLKIN = 1.024 MHz; TA = T

MIN

to T

unless otherwise noted.)

MAX

AD1556AS

Parameter Notes Min Typ Max Unit

FILTER PERFORMANCES

Pass-Band Ripple –0.05 +0.05 dB

Stop-Band Attenuation All Filters Except F

=16 kHz –86 dB

F

O

=16 kHz –135 dB

O

Filters Characteristics See Table II

DIGITAL INPUTS OUTPUTS

V

IL

V

IH

I

IL

I

IH

V

OL

V

OH

I

= +2 mA +0.5 V

SINK

I

= –2 mA VL– 0.6 V

SOURCE

–0.3 +0.8 V

+2.0 VL+ 0.3 V

–10 +10 µA

–10 +10 µA

POWER SUPPLIES

Specified Performance

V

L

2.85 5.25 V

Quiescent Currents

) 45mA

I(V

L

Power Dissipation V

= 3.3 V, FO = 1 kHz 6.2 8.5 mW

L

In Power-Down Mode 70 µW

TEMPERATURE RANGE

Specified Performance, T

*

Contact factory for extended temperature range.

Specifications subject to change without notice.

*

MIN

to T

MAX

–55 +85 °C

REV. B

–3–

AD1555/AD1556

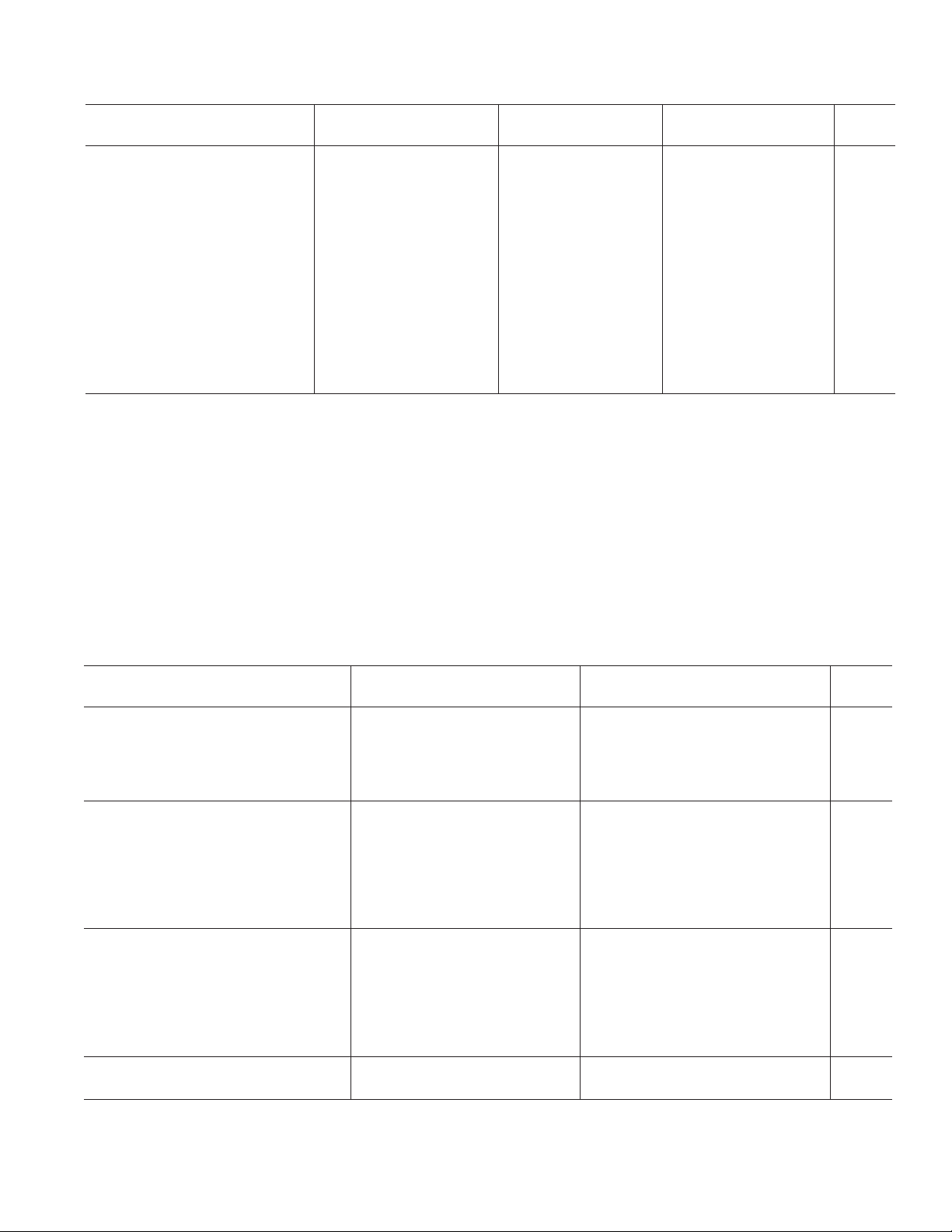

Table I. Dynamic and Noise Typical Performances

Input and Gain MODIN

PGA = 1 (0 dB) PGA = 2.5 (8 dB) PGA = 8.5 (19 dB) PGA = 34 (31 dB) PGA = 128 (42 dB)

Input Range 1.6 V rms 1.6 V rms 636 mV rms 187 mV rms 47 mV rms 12.4 mV rms

Dynamic Range

= 16 kHz (1/16 ms) 40 dB40dB 40dB 40dB 40dB 40dB

F

O

F

= 8 kHz (1/8 ms) 69 dB 69 dB 69 dB 69 dB 69 dB 69 dB

O

= 4 kHz (1/4 ms) 98 dB 98 dB 98 dB 98 dB 97 dB 91 dB

F

O

= 2 kHz (1/2 ms) 117 dB 117 dB 116.5 dB 114.5 dB 106.5 dB 95 dB

F

O

F

= 1 kHz (1 ms) 120 dB 120 dB 119.5 dB 117.5 dB 109.5 dB 98 dB

O

= 500 Hz (2 ms) 123 dB 123 dB 122.5 dB 120 dB 112.5 dB 101 dB

F

O

= 250 Hz (4 ms) 126 dB 126 dB 125.5 dB 123 dB 115.5 dB 104 dB

F

O

Equivalent Input Noise

= 16 kHz (1/16 ms) 15.5 mV rms 15.5 mV rms 6.17 mV rms 1.84 mV rms 470 µV rms 138 µV rms

F

O

= 8 kHz (1/8 ms) 560 µV rms 560 µV rms 220 µV rms 65.5 µV rms 16.4 µV rms 4.5 µV rms

F

O

F

= 4 kHz (1/4 ms) 20 µV rms 20 µV rms 8 µV rms 2.36 µV rms 661 nV rms 351 nV rms

O

= 2 kHz (1/2 ms) 2.25 µV rms 2.25 µV rms 952 nV rms 353 nV rms 225 nV rms 223 nV rms

F

O

= 1 kHz (1 ms) 1.59 µV rms 1.59 µV rms 674 nV rms 250 nV rms 159 nV rms 159 nV rms

F

O

F

= 500 Hz (2 ms) 1.13 µV rms 1.13 µV rms 477 nV rms 187 nV rms 113 nV rms 111 nV rms

O

FO = 250 Hz (4 ms) 797 nV rms 797 nV rms 338 nV rms 133 nV rms 80 nV rms 79 nV rms

Table Ia. Minimum Dynamic Performances (AD1555AP Only )

*

Input and Gain MODIN PGA = 1 (0 dB) PGA = 2.5 (8 dB) PGA = 8.5 (19 dB) PGA = 34 (31 dB)

= 1 kHz (1 ms) 116 116 115.5 114 104.5

F

O

= 500 Hz (2 ms) 119 119 118.5 117 107.5

F

O

FO = 250 Hz (4 ms) 122 122 121.5 120 110.5

*

Not tested in production. Guaranteed by design.

Table Ib. Minimum Dynamic Performances (AD1555BP Only )

*

Input and Gain MODIN PGA = 1 (0 dB) PGA = 2.5 (8 dB) PGA = 8.5 (19 dB) PGA = 34 (31 dB)

F

= 1 kHz (1 ms) 116.5 116.5 116 114 104.5

O

= 500 Hz (2 ms) 119.5 119.5 119 117 107.5

F

O

FO = 250 Hz (4 ms) 122.5 122.5 121 120 110.5

*

Not tested in production. Guaranteed by design.

Table II. Filter Characteristics

Output Word Rate F

O

Pass Band –3 dB Frequency Stop Band Group Delay

(Sampling Rate in ms) (Hz) (Hz) (Hz) (ms)

16000 Hz (1/16 ms) 6000 6480 8000 0.984

8000 Hz (1/8 ms) 3000 3267.5 4000 3

4000 Hz (1/4 ms) 1500 1634 2000 6

2000 Hz (1/2 ms) 750 816.9 1000 12

1000 Hz (1 ms) 375 408.5 500 24

500 Hz (2 ms) 187.5 204.2 250 48

250 Hz (4 ms) 93.75 101.4 125 93

–4–

REV. B

AD1555/AD1556

(+VA = +5 V 5%; –VA = –5 V 5%; AD1555 VL = 5 V 5%, AD1556 VL = 2.85 V to 5.25 V;

TIMING SPECIFICATIONS

CLKIN Frequency

CLKIN Duty Cycle Error 45 55 %

MCLK Output Frequency

SYNC Setup Time t

SYNC Hold Time t

CLKIN Rising to MCLK Output Falling on SYNC t

CLKIN Falling to MCLK Output Rising t

CLKIN Falling to MCLK Output Falling t

MCLK Input Falling to MDATA Falling t

MCLK Input Rising to MDATA and MFLG Valid t

TDATA Setup Time after SYNC t

TDATA Hold Time t

RESET Setup Time t

RESET Hold Time t

CLKIN Falling to DRDY Rising t

CLKIN Rising to DRDY Falling

CLKIN Rising to ERROR Falling t

RSEL to Data Valid t

RSEL Setup to SCLK Falling t

DRDY to Data Valid t

DRDY High Setup to SCLK Falling t

R/W to Data Valid t

R/W High Setup to SCLK Falling t

CS to Data Valid t

CS Low Setup to SCLK Falling t

SCLK Rising to DOUT Valid t

SCLK High Pulsewidth t

SCLK Low Pulsewidth t

SCLK Period t

SCLK Falling to DRDY Falling

CS High or R/W Low to DOUT Hi-Z t

R/W Low Setup to SCLK Falling t

CS Low Setup to SCLK Falling t

Data Setup Time to SCLK Falling t

Data Hold Time after SCLK Falling t

R/W Hold Time after SCLK Falling t

NOTES

1

The gain of the modulator is proportional to f

2

With DRDYBUF low only. When DRDYBUF is high, this timing also depends on the value of the external pull-down resistor.

Specifications subject to change without notice.

1

1

CLKIN = 1.024 MHz; AGND = DGND = 0 V; CL = 50 pF; TA = T

Symbol Min Typ Max Unit

f

CLKIN

1

2

3

4

5

6

7

8

9

10

11

2

2

and MCLK frequency.

CLKIN

12

t

13

14

15

16

17

18

19

20

21

22

23

24

25

26

t

27

28

29

30

31

32

33

to T

MIN

, unless otherwise noted)

MAX

0.975 1.024 1.075 MHz

f

/4

CLKIN

10 ns

10 ns

20 ns

20 ns

20 ns

30 ns

100 ns

5ns

5ns

15 ns

15 ns

20 ns

20 ns

50 ns

25 ns

10 ns

25 ns

10 ns

25 ns

10 ns

25 ns

10 ns

25 ns

25 ns

25 ns

70 ns

20 ns

20 ns

10 ns

10 ns

10 ns

10 ns

10 ns

REV. B

TO OUTPUT

PIN

50pF

1.6mA

C

L

500A

I

OL

1.4V

I

OH

Figure 2. Load Circuit for Digital Interface Timing

–5–

AD1555/AD1556

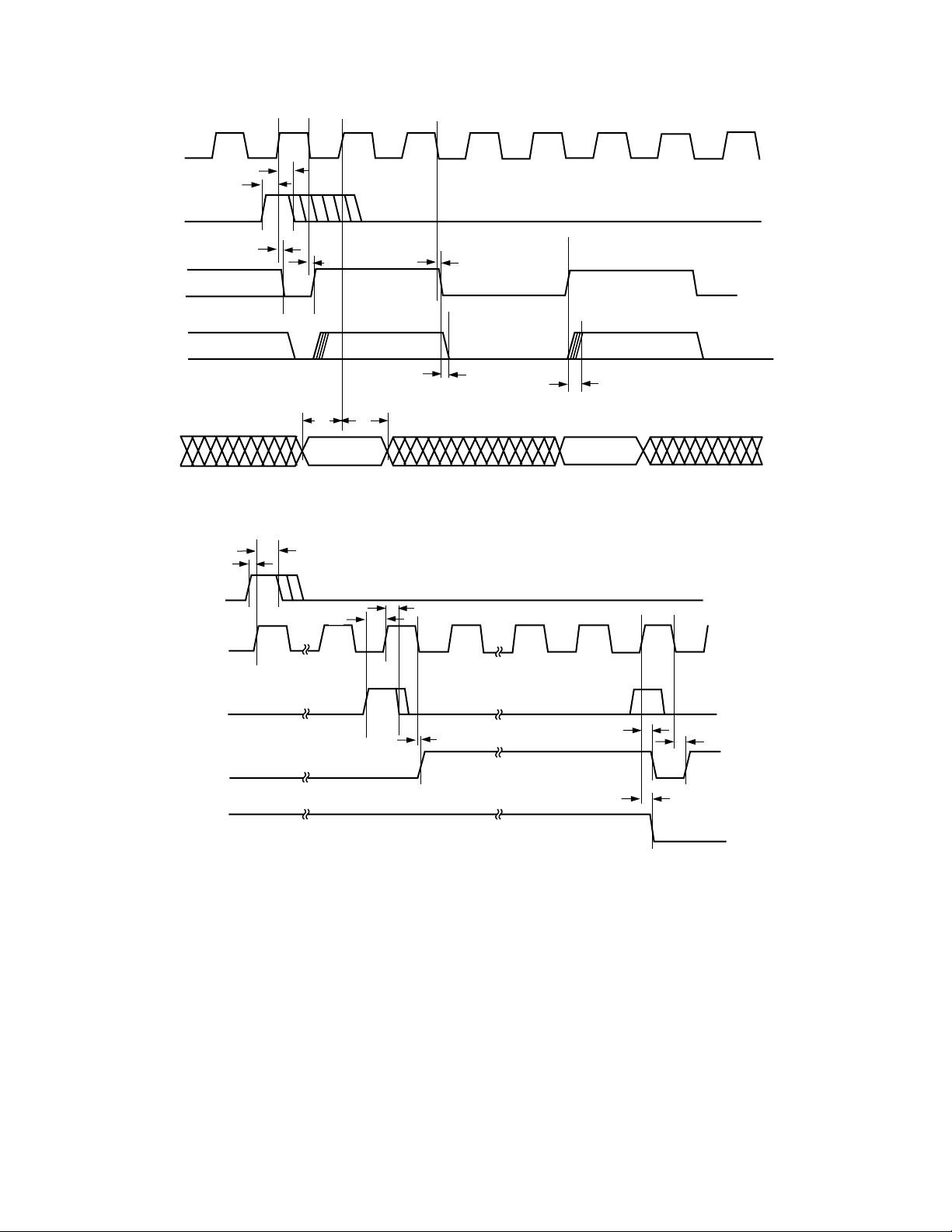

CLKIN

SYNC

MCLK

(FS)

t

t

1

t

3

2

t

4

t

5

MDATA

TDATA

RESET

CLKIN

SYNC

DRDY

DATA VALID DATA VALID

t

6

t

t

8

9

t

7

VALIDVALID

Figure 3. AD1555/AD1556 Interface Timing

t

t

10

11

t

t

1

2

t

t

12

13

t

12

ERROR

Figure 4. AD1556 RESET, DRDY, and Overwrite Timings

–6–

t

14

REV. B

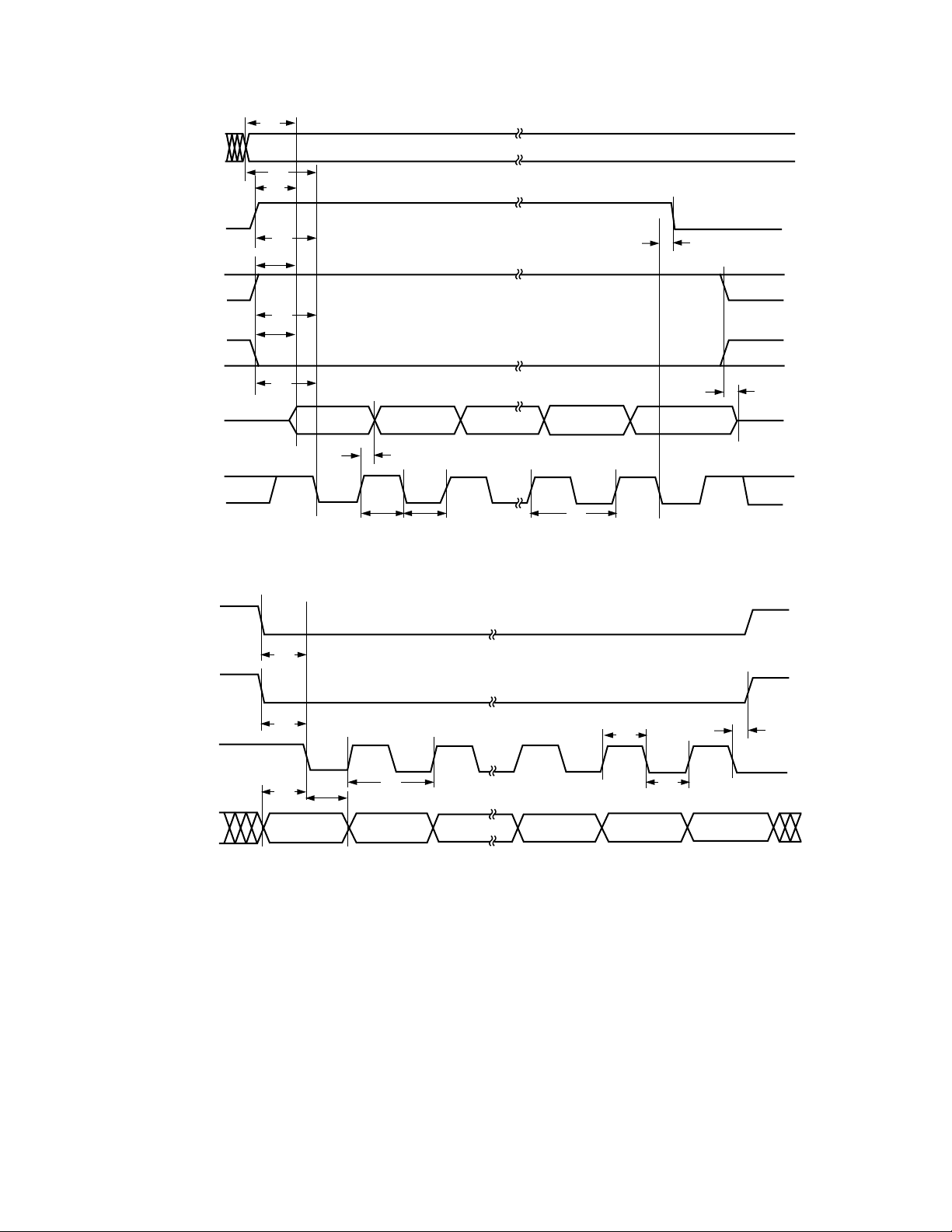

RSEL

DRDY

R/W

DOUT

SCLK

CS

AD1555/AD1556

t

15

t

16

t

17

t

18

t

19

t

20

t

21

t

22

MSB MSB–1 LSB+1 LSB

t

23

t

t

t

24

25

26

Figure 5. Serial Read Timing

t

27

t

28

HI-Z

CS

R/W

SCLK

DIN

t

29

t

30

t

t

t

32

31

MSB MSB–1 LSB+1 LSB

26

t

24

t

25

Figure 6. Serial Write Timing

t

33

REV. B

–7–

AD1555/AD1556

ABSOLUTE MAXIMUM RATINGS

1

Analog Inputs

Pins 7, 8, 23, 24, 25, 28 . . . . . . –V

– 0.3 V to +VA + 0.3 V

A

AIN(+), AIN(–) DC Input Current . . . . . . . . . . . ± 100 mA

AIN(+), AIN(–) 2 µs Pulse Input Current . . . . . . . . ± 1.5 A

Supply Voltages

to –VA . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +14 V

+V

A

to AGND . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +7 V

+V

A

–VA to AGND . . . . . . . . . . . . . . . . . . . . . . . –7 V to +0.3 V

to DGND . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V to +7 V

V

L

Ground Voltage Differences

DGND, AGND1, AGND2, AGND3 . . . . . . . . . . . ±0.3 V

Digital Inputs . . . . . . . . . . . . . . . . . . . . –0.3 V to V

Internal Power Dissipation

2

+ 0.3 V

L

AD1555 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1.8 W

AD1556 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1.8 W

ORDERING GUIDE

Temperature Package Package

Model Range* Description Option

AD1555AP 0°C to 85°C Plastic Lead Chip Carrier P-28A

AD1555APRL 0°C to 85°C Plastic Lead Chip Carrier P-28A

AD1555BP –55°C to +85°C Plastic Lead Chip Carrier P-28A

AD1555BPRL –55°C to +85°C Plastic Lead Chip Carrier P-28A

AD1556AS –55°C to +85 °C Plastic Quad Flatpack S-44A

AD1556ASRL –55°C to +85 °C Plastic Quad Flatpack S-44A

EVAL-AD1555/AD1556EB

AD1555/56-REF Reference Design

*Contact factory for extended temperature range.

Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . . . 150°C

Storage Temperature . . . . . . . . . . . . . . . . . . –65°C to +150°C

Lead Temperature Range

(Soldering 10 sec) . . . . . . . . . . . . . . . . . . . . . . . . . . 300°C

NOTES

1

Stresses above those listed under Absolute Maximum Ratings may cause perma-

nent damage to the device. This is a stress rating only; functional operation of the

device at these or any other conditions above those indicated in the operational

section of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect device reliability.

2

Specification is for device in free air:

28-lead PLCC: θJA = 36°C/W, θJC = 20°C/W

44-lead MQFP: θJA = 36°C/W, θJC = 14°C/W

Evaluation Board

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily

accumulate on the human body and test equipment and can discharge without detection. Although

the AD1555/AD1556 features proprietary ESD protection circuitry, permanent damage may occur

on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are

recommended to avoid performance degradation or loss of functionality.

WARNING!

ESD SENSITIVE DEVICE

–8–

REV. B

Loading...

Loading...