Complete, High Speed

3

FEATURES

Complete 16-bit converters with reference and clock

±0.003% maximum nonlinearity

No missing codes to 14 bits over temperature

Fast conversion

17 µs to 16 bits (AD1376)

10 µs to 16 bits (AD1377)

Short cycle capability

Adjustable clock rate

Parallel outputs

Low power

645 mW typical (AD1376)

585 mW typical (AD1377)

Industry-standard pinout

GENERAL DESCRIPTION

The AD1376/AD1377 are high resolution, 16-bit analog-todigital converters with internal reference, clock, and lasertrimmed thin-film applications resistors. The AD1376/AD1377

are excellent for use in high resolution applications requiring

moderate speed and high accuracy or stability over commercial

temperature ranges (0°C to 70°C). They are packaged in

compact 32-lead, ceramic seam-sealed (hermetic), dual in-line

packages (DIP). Thin-film scaling resistors provide bipolar

input ranges of ±2.5 V, ±5 V, and ±10 V and unipolar input

ranges of 0 V to +5 V, 0 V to +10 V, and 0 V to +20 V.

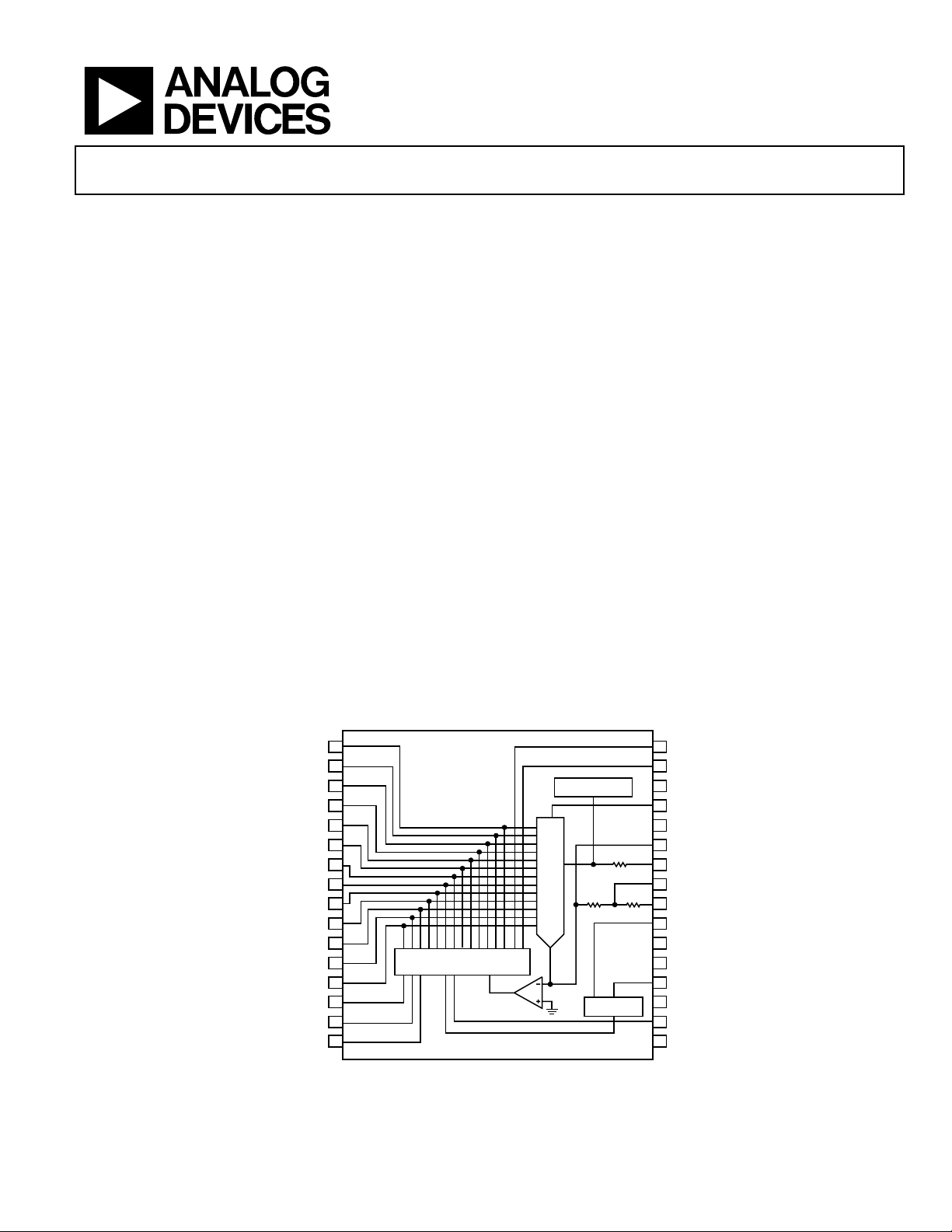

FUNCTIONAL BLOCK DIAGRAM

16-Bit A/D Converters

AD1376/AD1377

Digital output data is provided in parallel form with

corresponding clock and status outputs. All digital inputs and

outputs are TTL-compatible.

For the AD1376, the serial output function is no longer

available after date code 0111. For the AD1377, the serial output

function is no longer available after date code 0210. The option

of applying an external clock on the CONVERT START pin to

slow down the internally set conversion time is no longer

supported for either part.

PRODUCT HIGHLIGHTS

1. The AD1376/AD1377 provide 16-bit resolution with a

maximum linearity error of ±0.003% (1/2 LSB

2. The AD1376 conversion time is 14 µs (typical) short cycled

to 14 bits, and 16 µs to 16 bits.

3. The AD1377 conversion time is 8 µs (typical) short cycled

to 14 bits, and 9 µs to 16 bits.

4. Two binary codes are available on the digital output. They

are CSB (complementary straight binary) for unipolar input

voltage ranges and COB (complementary offset binary) for

bipolar input ranges. Complementary twos complement

(CTC) coding may be obtained by inverting Pin 1 (MSB).

5. The AD1376/AD1377 include internal reference and clock

with external clock rate adjust pin, and parallel digital outputs.

) at 25°C.

14

BIT 2

BIT 3

BIT 4

BIT 5

BIT 6

BIT 7

BIT 8

BIT 9

BIT 10

BIT 11

BIT 12

BIT 15

BIT 16

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

AD1376/AD1377

16-BIT SAR

(MSB) BIT 1

(LSB FOR 13 BITS) BIT 1

(LSB FOR 14 BITS) BIT 14

Rev. D

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

COMPARATOR

Figure 1.

32

SHORT CYCLE

CONVERT START

31

+5V DC SUPPLY V

REFERENCE

3.75kΩ 3.75kΩ

16-BIT DAC

7.5kΩ

CLOCK

30

29

GAIN ADJUST

+15V DC SUPPLY V

28

COMPARATOR I N

27

26

BIPOLAR OFFS ET

+10V

25

+20V

24

23

CLK RATE CTRL

22

ANALOG COMM ON

–15V DC SUPPLY V

21

CLOCK OUT

20

19

DIGITAL COMMON

STATUS

18

NC

17

L

CC

EE

00699-001

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.481.3113 © 2005 Analog Devices, Inc. All rights reserved.

AD1376/AD1377

TABLE OF CONTENTS

Specifications..................................................................................... 3

Input Scaling ..................................................................................7

Absolute Maximum Ratings............................................................ 5

ESD Caution.................................................................................. 5

Description of Operation ................................................................ 6

Gain Adjustment .......................................................................... 6

Zero Offset Adjustment............................................................... 6

Timing............................................................................................ 7

Digital Output Data ..................................................................... 7

REVISION HISTORY

6/05—Rev. C to Rev. D

Updated Format ..................................................................Universal

Updated Outline Dimensions....................................................... 12

6/03—Rev. B to Rev. C

Removed Serial Output Function and

Adjustable Clock Rate........................................................Universal

Updated Format ..................................................................Universal

Changes to General Description .................................................... 1

Changes to Product Highlights....................................................... 1

Changes to Functional Block Diagram.......................................... 1

Inserted ESD Warning ..................................................................... 3

Change to Ordering Guide.............................................................. 3

Change to Figure 7 ........................................................................... 5

Deleted text from Digital Output Data.......................................... 5

Deleted Figure 9 and Renumbered Remainder of Figures.......... 5

Deleted the ‘Using the AD1376 or AD1377 at

Slower Conversion Times’ Section ............................................... 8

Deleted Figure 16.............................................................................. 8

Change to Figure 13 ......................................................................... 9

Change to Figure 14 ......................................................................... 9

Updated Outline Dimensions....................................................... 10

Calibration (14-Bit Resolution Examples).................................8

Grounding, Decoupling, and Layout Considerations ..............9

Clock Rate Control........................................................................9

High Resolution Data Acquisition System.............................. 10

Applications..................................................................................... 11

Outline Dimensions ....................................................................... 12

Ordering Guide .......................................................................... 12

Rev. D | Page 2 of 12

AD1376/AD1377

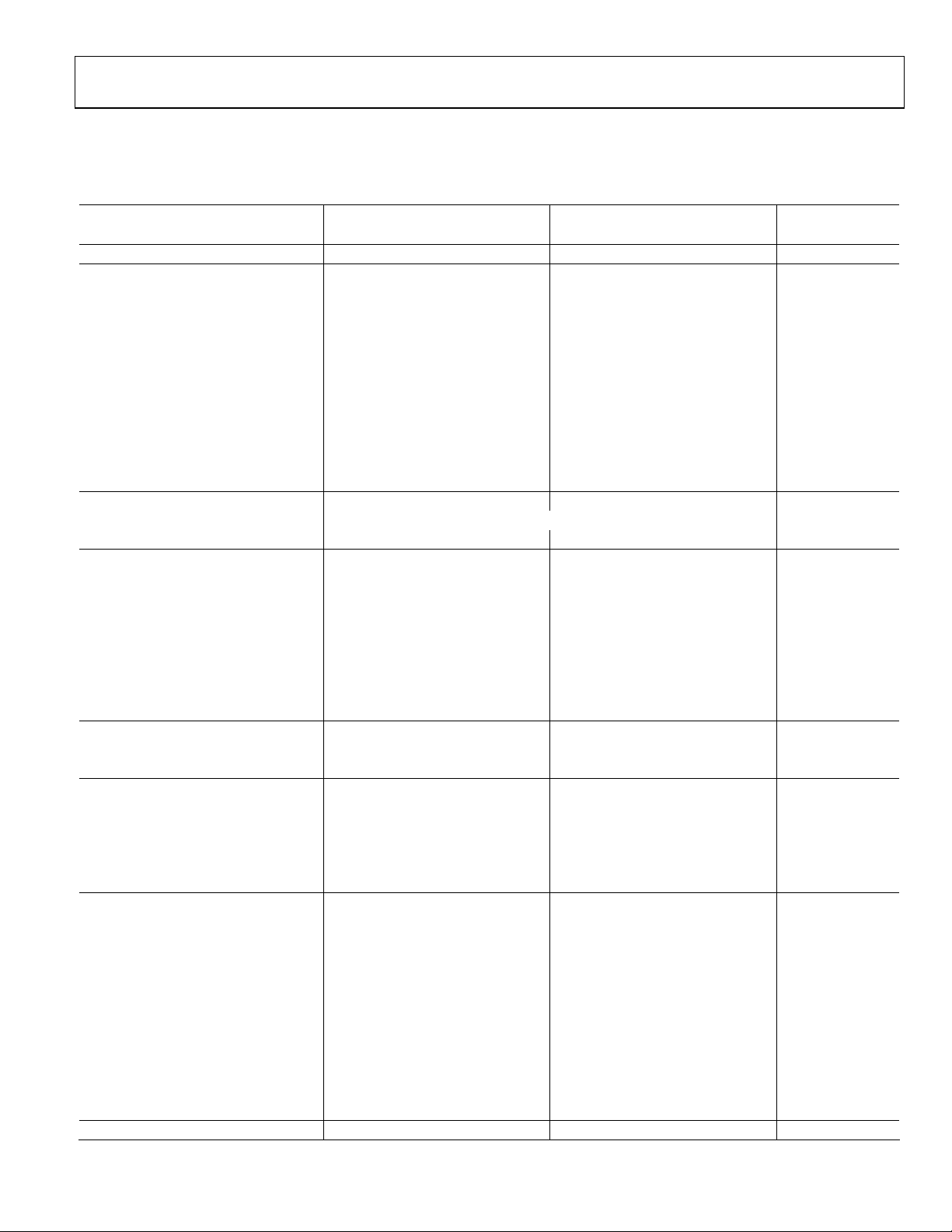

SPECIFICATIONS

Typical at TA = 25°C, VS = ±15 V, +5 V, unless otherwise noted.

Table 1.

AD1376JD/AD1377JD AD1376KD/AD1377KD

Model Min Typ Max Min Typ Max Unit

RESOLUTION 16 16 Bits

ANALOG INPUTS

Voltage Ranges

Bipolar ±2.5 ±2.5 V

±5 ±5 V

±10 ±10 V

Unipolar 0 to 5 0 to 5 V

0 to 10 0 to 10 V

0 to 20 0 to 20 V

Impedance (Direct Input) V

0 V to +5 V, ±2.5 V 1.88 1.88 kΩ

0 V to +10 V, ±5.0 V 3.75 3.75 kΩ

0 V to +20 V, ±10 V 7.50 7.50 kΩ

DIGITAL INPUTS

Convert Command Trailing edge of positive 50 ns (min) pulse

Logic Loading 1 1 LS TTL Load

TRANSFER CHARACTERISTICS

(ACCURACY)

Gain Error ±0.05

Offset Error

Unipolar ±0.053 ±0.1 ±0.053 ±0.1 % of FSR

Bipolar ±0.053 ±0.2 ±0.053 ±0.2 % of FSR

Linearity Error (Max) ±0.006 ±0.003 % of FSR

Inherent Quantization Error ±1/2 ±1/2 LSB

Differential Linearity Error ±0.003 ±0.003 % of FSR

POWER SUPPLY SENSITIVITY

±15 V DC (±0.75 V) 0.0015 0.0015 % of FSR/% ∆V

+5 V DC (±0.25 V) 0.001 0.001 % of FSR/% ∆V

CONVERSION TIME

12 Bits (AD1376) 11.5 13 11.5 13 µs

14 Bits (AD1376) 13.5 15 13.5 15 µs

16 Bits (AD1376) 15.5 17 15.5 17 µs

14 Bits (AD1377) 8.75 8.75 µs

16 Bits (AD1377) 10 10 µs

POWER SUPPLY REQUIREMENTS

Analog Supplies +14.5 +15 +15.5 +14.5 +15 +15.5 V dc

−14.5 −15 −15.5 −14.5 −15 −15.5 V dc

Digital Supply +4.75 +5 +5.25 +4.75 +5 +5.25 V dc

AD1376 Power Consumption 600 800 600 800 mW

+15 V Supply Drain +10 +10 mA

−15 V Supply Drain −23 −23 mA

+5 V Supply Drain +18 +18 mA

AD1377 Power Consumption 600 800 600 800 mW

+15 V Supply Drain +10 +10 mA

−15 V Supply Drain −23 −23 mA

+5 V Supply Drain +18 +18 mA

WARM-UP TIME 1 1 Minutes

1

2

5

3

±0.2 ± 0.053 ± 0.2 %

4

S

S

Rev. D | Page 3 of 12

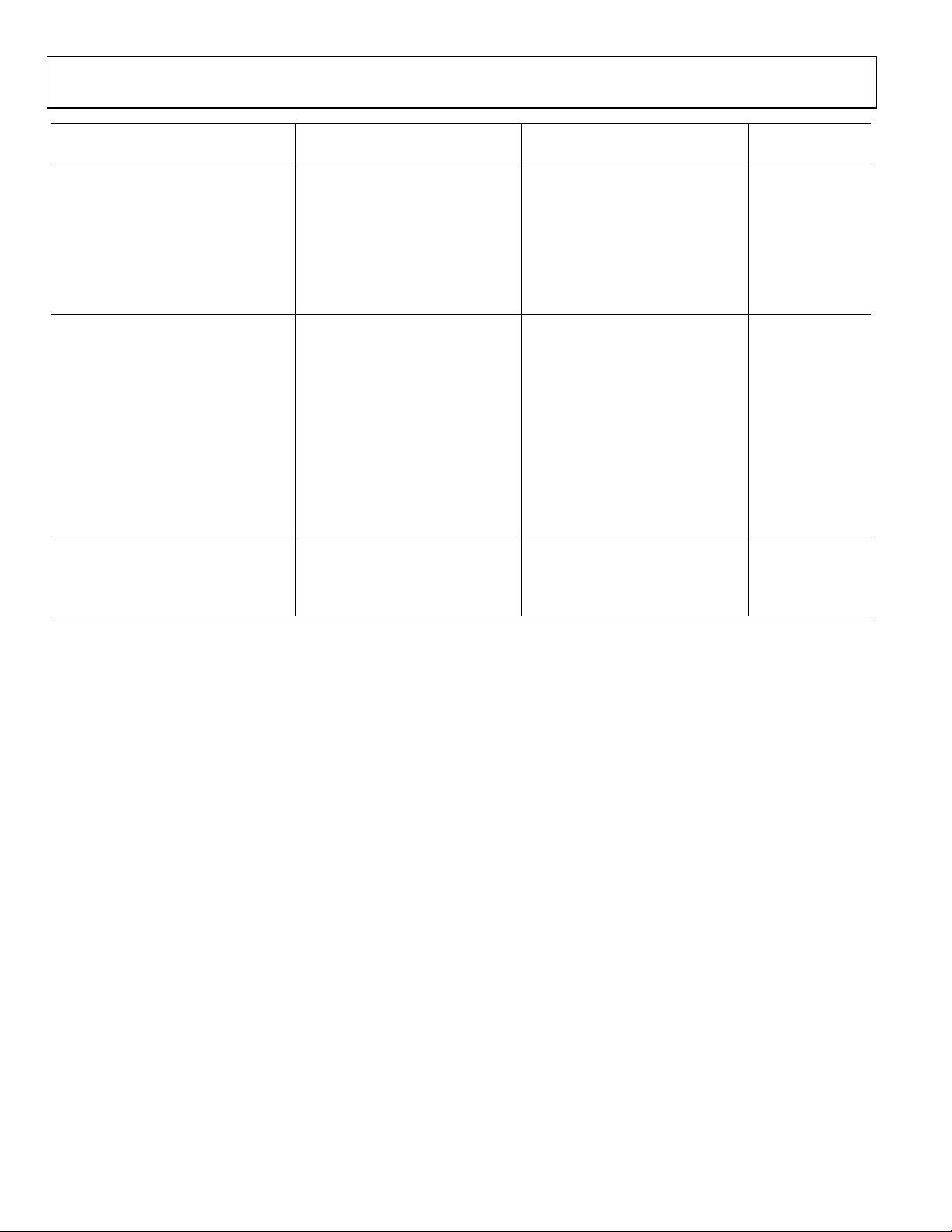

AD1376/AD1377

AD1376JD/AD1377JD AD1376KD/AD1377KD

Model Min Typ Max Min Typ Max Unit

6

DRIFT

Gain ±15 ±5 ±15 ppm/°C

Offset

Unipolar ±2 ±4 ±2 ±4 ppm of FSR/°C

Bipolar ±10 ±3 ±10 ppm of FSR/°C

Linearity ±2 ±3 ±0.3 ±2 ppm of FSR/°C

Guaranteed No Missing Code

Temperature Range 0 to 70 (13 Bits) 0 to 70 (14 Bits) °C

DIGITAL OUTPUT1

(All Codes Complementary)

Parallel Output Codes

7

Unipolar CSB CSB

Bipolar COB, CTC

Output Drive 5 5 LSTTL Loads

Status

Status Output Drive 5 5 LSTTL Loads

Internal Clock

9

Clock Output Drive 5 5 LSTTL Loads

Frequency 1040/1750 1040/1750 kHz

TEMPERATURE RANGE

Specification 0 to 70 0 to 70 °C

Operating −25 to +85 −25 to +85 °C

Storage −55 to +125 −55 to +125 °C

1

Logic 0 = 0.8 V max; Logic 1 = 2.0 V min for inputs. For digital outputs, Logic 0 = 0.4 V max. Logic 1 = 2.4 V min.

2

Tested on ±10 V and 0 V to +10 V ranges.

3

Adjustable to zero.

4

Full-scale range.

5

Conversion time may be shortened with “short cycle” set for lower resolution.

6

Guaranteed but not 100% production tested.

7

CSB–Complementary Straight Binary. COB–Complementary Offset Binary. CTC–Complementary Twos Complement.

8

CTC coding obtained by inverting MSB (Pin 1).

9

With Pin 23, clock rate controls tied to digital ground.

8

Logic 1 During

Conversion

COB, CTC8

Logic 1 During

Conversion

Rev. D | Page 4 of 12

Loading...

Loading...