Page 1

DisplayPort IP Core User Guide

Subscribe

Send Feedback

UG-01131

2015.05.04

101 Innovation Drive

San Jose, CA 95134

www.altera.com

Page 2

TOC-2

Contents

DisplayPort IP Core Quick Reference................................................................ 1-1

About This IP Core..............................................................................................2-1

Getting Started.................................................................................................... 3-1

Device Family Support................................................................................................................................2-2

IP Core Verification.....................................................................................................................................2-2

Performance and Resource Utilization.....................................................................................................2-2

Installing and Licensing IP Cores..............................................................................................................3-1

OpenCore Plus IP Evaluation........................................................................................................ 3-1

Specifying IP Core Parameters and Options............................................................................................3-2

Simulating the Design................................................................................................................................. 3-2

Simulating with the ModelSim Simulator....................................................................................3-3

Compiling the Full Design and Programming the FPGA......................................................................3-3

DisplayPort Source..............................................................................................4-1

Source Overview...........................................................................................................................................4-1

Source Functional Description.................................................................................................................. 4-2

Main Data Path.................................................................................................................................4-3

Embedded DisplayPort (eDP) Support.........................................................................................4-5

Source Parameters........................................................................................................................................4-5

Source Interfaces..........................................................................................................................................4-7

Controller Interface.......................................................................................................................4-11

AUX Interface.................................................................................................................................4-12

Video Interface...............................................................................................................................4-12

TX Transceiver Interface.............................................................................................................. 4-13

Transceiver Reconfiguration Interface....................................................................................... 4-14

Transceiver Analog Reconfiguration Interface..........................................................................4-14

Secondary Stream Interface..........................................................................................................4-14

Audio Interface...............................................................................................................................4-16

MSA Interface.................................................................................................................................4-18

Source Clock Tree......................................................................................................................................4-19

DisplayPort Sink..................................................................................................5-1

Sink Overview...............................................................................................................................................5-1

Sink Functional Description.......................................................................................................................5-1

Embedded DisplayPort (eDP) Support.........................................................................................5-4

Sink Parameters ...........................................................................................................................................5-4

Sink Interfaces.............................................................................................................................................. 5-6

Altera Corporation

Page 3

TOC-3

Controller Interface.......................................................................................................................5-13

AUX Interface.................................................................................................................................5-13

Debugging Interface...................................................................................................................... 5-14

Video Interface...............................................................................................................................5-16

RX Transceiver Interface.............................................................................................................. 5-19

Transceiver Reconfiguration Interface....................................................................................... 5-19

Secondary Stream Interface..........................................................................................................5-19

Audio Interface...............................................................................................................................5-21

MSA Interface.................................................................................................................................5-22

Sink Clock Tree..........................................................................................................................................5-24

DisplayPort IP Core Hardware Demonstration.................................................6-1

Clock Recovery Core...................................................................................................................................6-4

Clock Recovery Core Parameters.................................................................................................. 6-5

Clock Recovery Interface................................................................................................................ 6-6

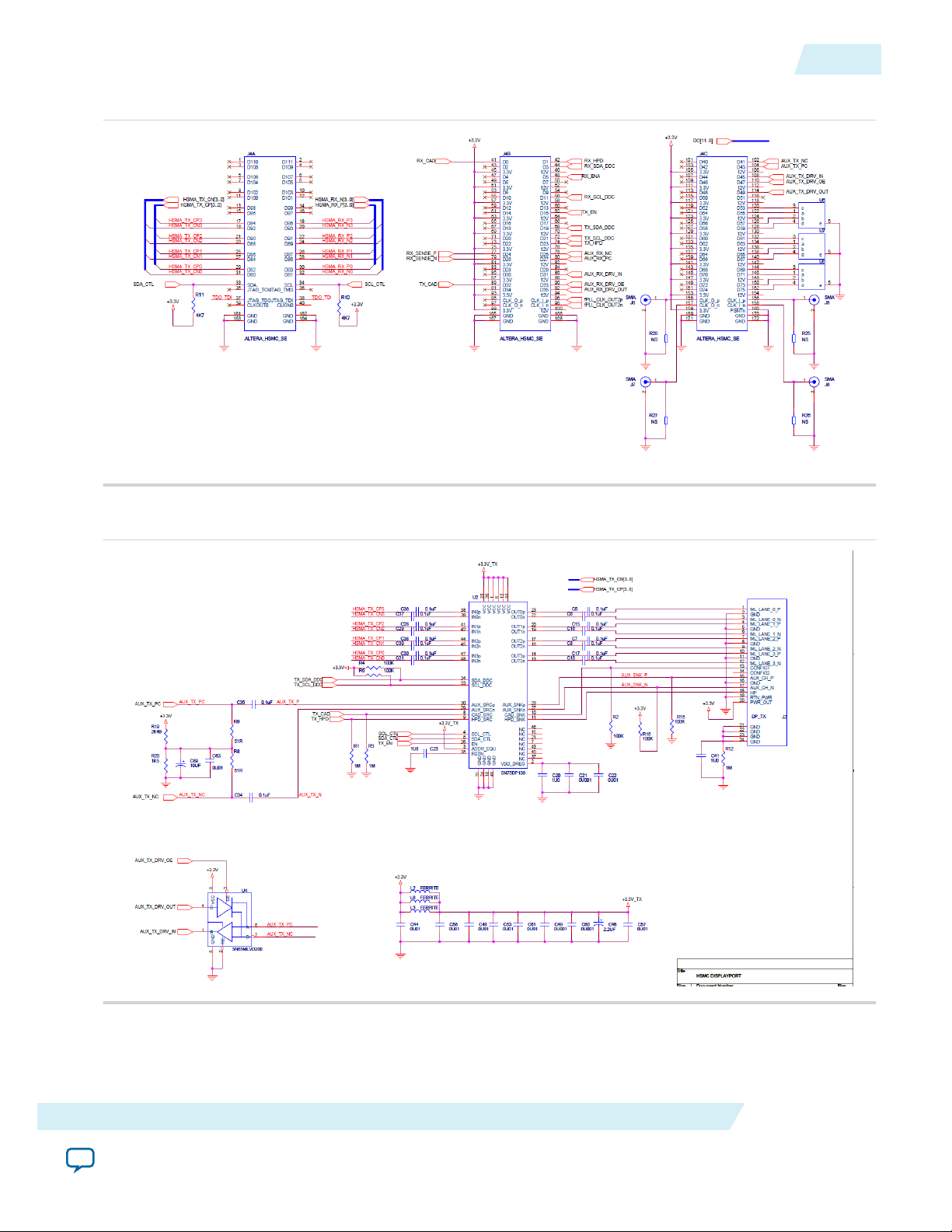

Transceiver and Clocking.........................................................................................................................6-11

Required Hardware................................................................................................................................... 6-14

Design Walkthrough.................................................................................................................................6-22

Set Up the Hardware..................................................................................................................... 6-23

Copy the Design Files to Your Working Directory.................................................................. 6-23

Build the FPGA Design.................................................................................................................6-25

Load, and Run the Software......................................................................................................... 6-25

View the Results.............................................................................................................................6-26

DisplayPort IP Core Simulation Example..........................................................7-1

Design Walkthrough................................................................................................................................... 7-3

Copy the Simulation Files to Your Working Directory..............................................................7-3

Generate the IP Simulation Files and Scripts, and Compile and Simulate..............................7-6

View the Results...............................................................................................................................7-8

DisplayPort API Reference................................................................................. 8-1

Using the Library......................................................................................................................................... 8-1

btc_dprx_syslib API Reference..................................................................................................................8-3

btc_dprx_aux_get_request......................................................................................................................... 8-3

btc_dprx_aux_handler................................................................................................................................8-4

btc_dprx_aux_post_reply...........................................................................................................................8-5

btc_dprx_baseaddr...................................................................................................................................... 8-6

btc_dprx_dpcd_gpu_access........................................................................................................................8-6

btc_dprx_edid_set........................................................................................................................................8-7

btc_dprx_hpd_get........................................................................................................................................8-8

btc_dprx_hpd_pulse....................................................................................................................................8-8

btc_dprx_hpd_set........................................................................................................................................ 8-9

btc_dprx_syslib_add_rx..............................................................................................................................8-9

btc_dprx_syslib_info.................................................................................................................................8-10

btc_dprx_syslib_init..................................................................................................................................8-11

btc_dprx_syslib_monitor..........................................................................................................................8-11

Altera Corporation

Page 4

TOC-4

btc_dptx_syslib API Reference................................................................................................................ 8-12

btc_dptx_aux_i2c_read.............................................................................................................................8-12

btc_dptx_aux_i2c_write............................................................................................................................8-13

btc_dptx_aux_read....................................................................................................................................8-13

btc_dptx_aux_write...................................................................................................................................8-14

btc_dptx_baseaddr.....................................................................................................................................8-15

btc_dptx_edid_block_read.......................................................................................................................8-15

btc_dptx_edid_read...................................................................................................................................8-16

btc_dptx_fast_link_training.....................................................................................................................8-16

btc_dptx_link_training............................................................................................................................. 8-17

btc_dptx_set_color_space.........................................................................................................................8-18

btc_dptx_syslib_init.................................................................................................................................. 8-18

btc_dptx_syslib_monitor..........................................................................................................................8-19

btc_dptx_test_autom.................................................................................................................................8-19

btc_dptx_video_enable.............................................................................................................................8-20

btc_dpxx_syslib Additional Types.......................................................................................................... 8-20

btc_dprx_syslib Supported DPCD Locations........................................................................................8-20

DisplayPort Source Register Map and DPCD Locations................................... 9-1

Source General Registers.............................................................................................................................9-1

DPTX_TX_CONTROL...................................................................................................................9-1

DPTX_TX_STATUS....................................................................................................................... 9-3

Source MSA Registers..................................................................................................................................9-4

DPTX0_MSA_MVID......................................................................................................................9-4

DPTX0_MSA_NVID.......................................................................................................................9-4

DPTX0_MSA_HTOTAL................................................................................................................9-4

DPTX0_MSA_VTOTAL................................................................................................................ 9-5

DPTX0_MSA_HSP..........................................................................................................................9-5

DPTX0_MSA_HSW........................................................................................................................9-5

DPTX0_MSA_HSTART.................................................................................................................9-6

DPTX0_MSA_VSTART................................................................................................................. 9-6

DPTX0_MSA_VSP..........................................................................................................................9-6

DPTX0_MSA_VSW........................................................................................................................9-7

DPTX0_MSA_HWIDTH...............................................................................................................9-7

DPTX0_MSA_VHEIGHT..............................................................................................................9-7

DPTX0_MSA_MISC0.....................................................................................................................9-8

DPTX0_MSA_MISC1.....................................................................................................................9-8

DPTX0_MSA_COLOUR................................................................................................................9-8

Source Link Voltage and Pre-Emphasis Controls...................................................................................9-9

DPTX_PRE_VOLT0........................................................................................................................9-9

DPTX_PRE_VOLT1..................................................................................................................... 9-10

DPTX_PRE_VOLT2..................................................................................................................... 9-10

DPTX_PRE_VOLT3..................................................................................................................... 9-10

DPTX_RECONFIG.......................................................................................................................9-11

Source Timestamp.....................................................................................................................................9-11

Source Audio Registers............................................................................................................................. 9-12

Source CRC Registers................................................................................................................................9-13

Source MST Registers................................................................................................................................9-14

Altera Corporation

Page 5

TOC-5

DPTX_MST_VCPTAB0...............................................................................................................9-15

DPTX_MST_VCPTAB1...............................................................................................................9-15

DPTX_MST_VCPTAB2...............................................................................................................9-16

DPTX_MST_VCPTAB3...............................................................................................................9-17

DPTX_MST_VCPTAB4...............................................................................................................9-17

DPTX_MST_VCPTAB5...............................................................................................................9-18

DPTX_MST_VCPTAB6...............................................................................................................9-18

DPTX_MST_VCPTAB7...............................................................................................................9-19

DPTX_MST_TAVG_TS...............................................................................................................9-20

Source AUX Controller Interface............................................................................................................9-20

DPTX_AUX_CONTROL.............................................................................................................9-20

DPTX_AUX_CMD....................................................................................................................... 9-21

DPTX_AUX_BYTE0.....................................................................................................................9-22

DPTX_AUX_BYTE1.....................................................................................................................9-22

DPTX_AUX_BYTE2.....................................................................................................................9-22

DPTX_AUX_BYTE3.....................................................................................................................9-23

DPTX_AUX_BYTE4.....................................................................................................................9-23

DPTX_AUX_BYTE5.....................................................................................................................9-23

DPTX_AUX_BYTE6.....................................................................................................................9-24

DPTX_AUX_BYTE7.....................................................................................................................9-24

DPTX_AUX_BYTE8.....................................................................................................................9-24

DPTX_AUX_BYTE9.....................................................................................................................9-25

DPTX_AUX_BYTE10...................................................................................................................9-25

DPTX_AUX_BYTE11...................................................................................................................9-25

DPTX_AUX_BYTE12...................................................................................................................9-26

DPTX_AUX_BYTE13...................................................................................................................9-26

DPTX_AUX_BYTE14...................................................................................................................9-27

DPTX_AUX_BYTE15...................................................................................................................9-27

DPTX_AUX_BYTE16...................................................................................................................9-27

DPTX_AUX_BYTE17...................................................................................................................9-28

DPTX_AUX_BYTE18...................................................................................................................9-28

DPTX_AUX_RESET.....................................................................................................................9-28

Source-Supported DPCD Locations....................................................................................................... 9-29

DisplayPort Sink Register Map and DPCD Locations.....................................10-1

Sink General Registers...............................................................................................................................10-1

DPRX_RX_CONTROL.................................................................................................................10-1

DPRX_RX_STATUS.....................................................................................................................10-3

DPRX_BER_CONTROL.............................................................................................................. 10-5

DPRX_BER_CNT0........................................................................................................................10-7

DPRX_BER_CNT1........................................................................................................................10-7

Sink Timestamp......................................................................................................................................... 10-7

Sink Bit-Error Counters............................................................................................................................10-7

DPRX_BER_CNTI0...................................................................................................................... 10-7

DPRX_BER_CNTI1...................................................................................................................... 10-8

Sink MSA Registers....................................................................................................................................10-8

DPRX0_MSA_MVID....................................................................................................................10-9

DPRX0_MSA_NVID.................................................................................................................... 10-9

Altera Corporation

Page 6

TOC-6

DPRX0_MSA_HTOTAL..............................................................................................................10-9

DPRX0_MSA_VTOTAL.............................................................................................................. 10-9

DPRX0_MSA_HSP..................................................................................................................... 10-10

DPRX0_MSA_HSW....................................................................................................................10-10

DPRX0_MSA_HSTART.............................................................................................................10-10

DPRX0_MSA_VSTART.............................................................................................................10-11

DPRX0_MSA_VSP......................................................................................................................10-11

DPRX0_MSA_VSW....................................................................................................................10-11

DPRX0_MSA_HWIDTH...........................................................................................................10-12

DPRX0_MSA_VHEIGHT..........................................................................................................10-12

DPRX0_MSA_MISC0.................................................................................................................10-12

DPRX0_MSA_MISC1.................................................................................................................10-13

DPRX0_VBID.............................................................................................................................. 10-13

Sink Audio Registers............................................................................................................................... 10-14

DPRX0_AUD_MAUD................................................................................................................10-14

DPRX0_AUD_NAUD................................................................................................................10-14

DPRX0_AUD_AIF0....................................................................................................................10-14

DPRX0_AUD_AIF1....................................................................................................................10-15

DPRX0_AUD_AIF2....................................................................................................................10-15

DPRX0_AUD_AIF3....................................................................................................................10-15

DPRX0_AUD_AIF4....................................................................................................................10-16

Sink MST Registers..................................................................................................................................10-16

DPRX_MST_VCPTAB0.............................................................................................................10-17

DPRX_MST_VCPTAB1.............................................................................................................10-18

DPRX_MST_VCPTAB2.............................................................................................................10-19

DPRX_MST_VCPTAB3.............................................................................................................10-19

DPRX_MST_VCPTAB4.............................................................................................................10-20

DPRX_MST_VCPTAB5.............................................................................................................10-20

DPRX_MST_VCPTAB6.............................................................................................................10-21

DPRX_MST_VCPTAB7.............................................................................................................10-22

Sink AUX Controller Interface..............................................................................................................10-22

DPRX_AUX_CONTROL...........................................................................................................10-22

DPRX_AUX_STATUS................................................................................................................10-23

DPRX_AUX_COMMAND........................................................................................................10-24

DPRX_AUX_BYTE0...................................................................................................................10-24

DPRX_AUX_BYTE1...................................................................................................................10-25

DPRX_AUX_BYTE2...................................................................................................................10-25

DPRX_AUX_BYTE3...................................................................................................................10-25

DPRX_AUX_BYTE4...................................................................................................................10-26

DPRX_AUX_BYTE5...................................................................................................................10-26

DPRX_AUX_BYTE6...................................................................................................................10-26

DPRX_AUX_BYTE7...................................................................................................................10-27

DPRX_AUX_BYTE8...................................................................................................................10-27

DPRX_AUX_BYTE9...................................................................................................................10-27

DPRX_AUX_BYTE10.................................................................................................................10-28

DPRX_AUX_BYTE11.................................................................................................................10-28

DPRX_AUX_BYTE12.................................................................................................................10-29

DPRX_AUX_BYTE13.................................................................................................................10-29

DPRX_AUX_BYTE14.................................................................................................................10-29

Altera Corporation

Page 7

TOC-7

DPRX_AUX_BYTE15.................................................................................................................10-30

DPRX_AUX_BYTE16.................................................................................................................10-30

DPRX_AUX_BYTE17.................................................................................................................10-30

DPRX_AUX_BYTE18.................................................................................................................10-31

DPRX_AUX_I2C0.......................................................................................................................10-31

DPRX_AUX_I2C1.......................................................................................................................10-31

DPRX_AUX_RESET...................................................................................................................10-32

DPRX_AUX_HPD...................................................................................................................... 10-32

Sink-Supported DPCD Locations......................................................................................................... 10-33

Additional Information......................................................................................A-1

Document Revision History......................................................................................................................A-1

Altera Corporation

Page 8

2015.05.04

www.altera.com

101 Innovation Drive, San Jose, CA 95134

DisplayPort IP Core Quick Reference

1

UG-01131

Subscribe

Send Feedback

This document describes the Altera® DisplayPort MegaCore®function, which provides support for nextgeneration video display interface technology.

The DisplayPort IP core is part of the MegaCore IP Library, which is distributed with the Quartus® II

software and is downloadable from the Altera website at www.altera.com.

Note:

For system requirements and installation instructions, refer to the Altera Software Installation and

Licensing Manual.

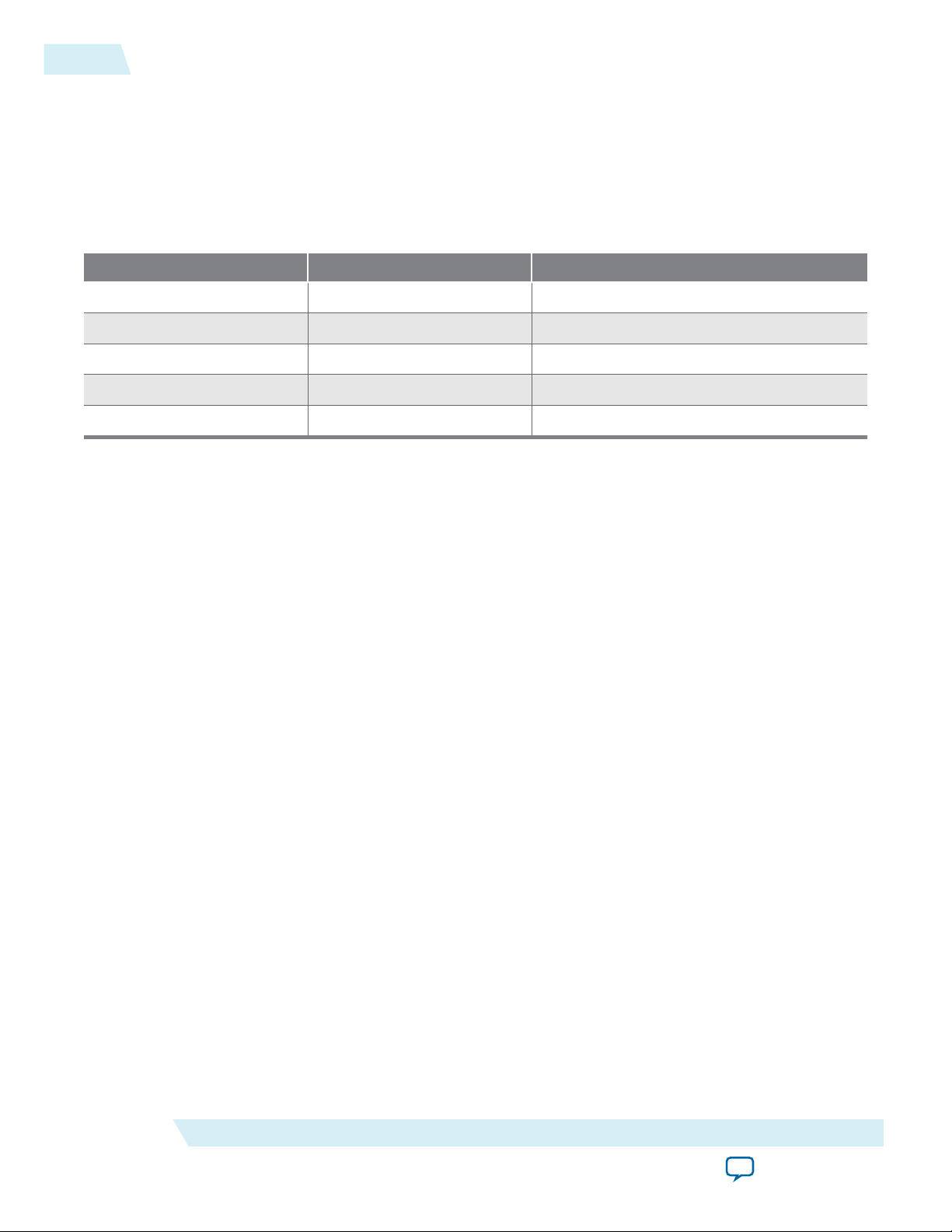

Item Description

Version 15.0

Release Date May 2015

Release Information

Ordering Code IP-DP

Product ID 0109

Vendor ID 6AF7

©

2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

ISO

9001:2008

Registered

Page 9

1-2

DisplayPort IP Core Quick Reference

Item Description

UG-01131

2015.05.04

IP Core Information

Core Features

• Conforms to the Video Electronics

Standards Association (VESA) specifica‐

tion version 1.2a

• Scalable main data link

• 1, 2, or 4 lane operation

• 1.62, 2.7, and 5.4 gigabits per second

(Gbps) per lane with an embedded

clock

• Color support

• RGB 18, 24, 30, 36, or 48 bits per pixel

(bpp) color depths

• YCbCr 4:4:4 24, 30, 36, or 48 bpp color

depths

• YCbCr 4:2:2 16, 20, 24, or 32 bpp color

depths

• 40-bit (quad symbol) and 20-bit (dual

symbol) transceiver data interface

• Support for 1, 2, or 4 parallel pixels per

clock

• Multi-stream support (MST)

• 4Kp60 resolution support

• Source

• Embedded controller AUX channel

operation

• Accepts standard H-sync/V-sync/data

enable RGB and YCbCr input video

formats

• Supports audio and video streams

• Sink

• Finite state machine (FSM) or

embedded controller AUX channel

operation

• Produces a proprietary video output

• Auxiliary channel for 2-way communica‐

tion (link and device management)

• Hot plug detect (HPD)

• Sink announces its presence

• Sink requests the source’s attention

• AC coupling and low EMI

Altera Corporation

DisplayPort IP Core Quick Reference

Send Feedback

Page 10

UG-01131

2015.05.04

DisplayPort IP Core Quick Reference

Item Description

Typical Application • Interfaces within a PC or monitor

• External display connections, including

interfaces between a PC and monitor or

projector, between a PC and TV, or

between a device such as a DVD player

and TV display

Device Family Support Arria® 10 (preliminary), Arria V GX, Arria V

GZ, Cyclone® V, and Stratix® V FPGA

devices.

Refer to the What’s New in Altera IP page of

the Altera website for detailed information.

Design Tools • IP Catalog in the Quartus II software for

IP design instantiation and compilation

• TimeQuest timing analyzer in the

Quartus II software for timing analysis

• ModelSim-Altera software for design

simulation

1-3

Related Information

What’s New in Altera IP

DisplayPort IP Core Quick Reference

Send Feedback

Altera Corporation

Page 11

2015.05.04

Source

Lane 0 Data (1.62, 2.7, or 5.4 Gbps)

Lane 1 Data (1.62, 2.7, or 5.4 Gbps)

Lane 2 Data (1.62, 2.7, or 5.4 Gbps)

Lane 3 Data (1.62, 2.7, or 5.4 Gbps)

AUX Channel (1 Mbps)

Hot Plug Detect

Sink

www.altera.com

101 Innovation Drive, San Jose, CA 95134

About This IP Core

2

UG-01131

Subscribe

Send Feedback

This document describes the Altera® DisplayPort MegaCore® function, which provides support for nextgeneration video display interface technology. The Video Electronics Standards Association (VESA)

defines the DisplayPort standard as an open digital communications interface for use in internal

connections such as:

• Interfaces within a PC or monitor

• External display connections, including interfaces between a PC and monitor or projector, between a

PC and TV, or between a device such as a DVD player and TV display

The Altera DisplayPort source has a scalable main link with 1, 2, or 4 lanes for a total up to 21.6 Gbps

bandwidth. A bidirectional AUX channel with 1 Mbps Manchester encoding provides side-band

communication. The sink uses a hot plug detect (HPD) signal to announce its presence, and the source

uses the same signal to initiate link configuration.

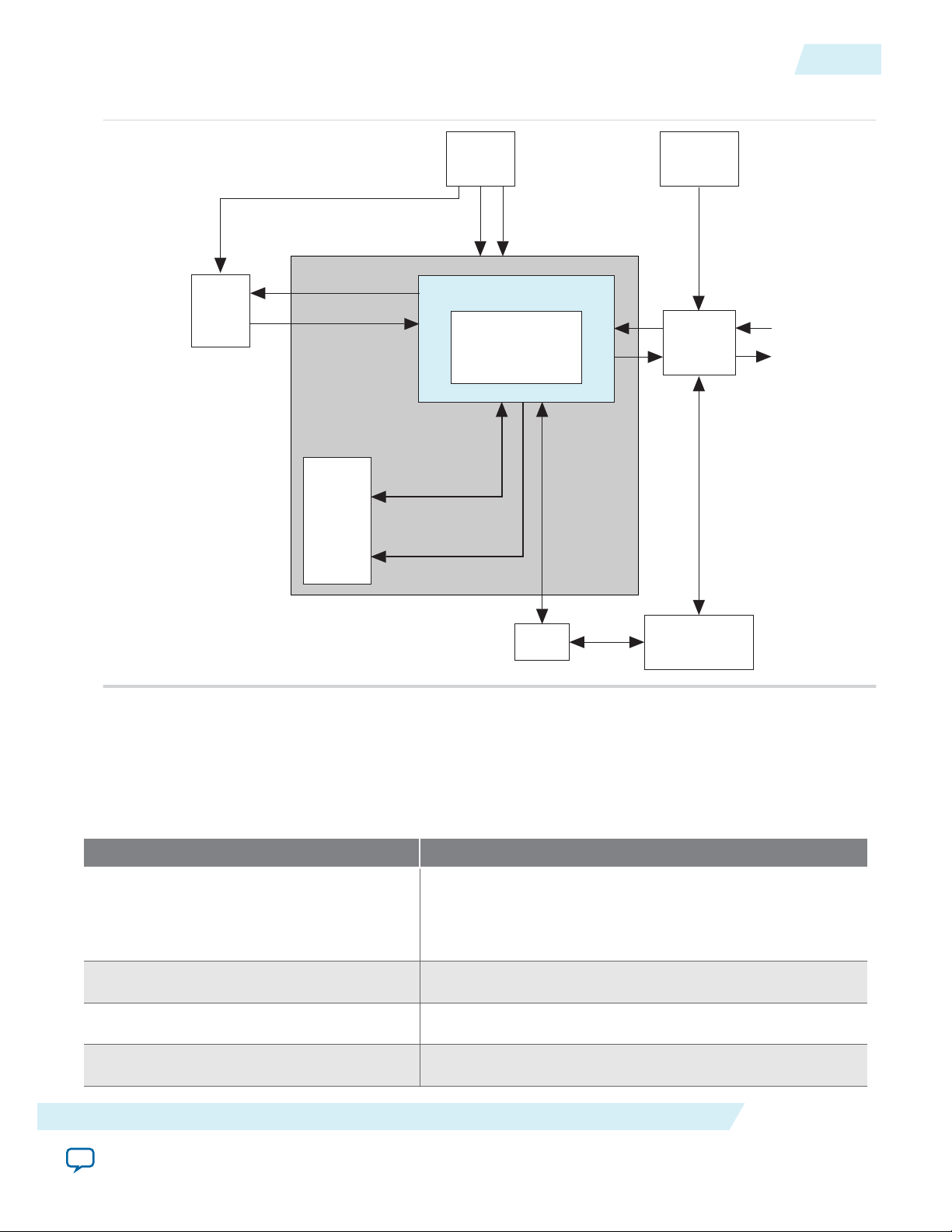

Figure 2-1: DisplayPort Source and Sink Communication

The main link has three selectable data rates: 1.62, 2.7, and 5.4 Gbps.

©

2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

ISO

9001:2008

Registered

Page 12

2-2

Device Family Support

Device Family Support

The following table lists the link rate support offered by the DisplayPort IP core for each Altera device

family.

Table 2-1: Link Rate Support by Device Family

RBR = Reduced Bit Rate, HBR = High Bit Rate

Device Family 20-bit mode 40-bit mode

Arria 10 RBR, HBR, HBR2 RBR, HBR, HBR2

Arria V GX RBR, HBR RBR, HBR, HBR2

Arria V GZ RBR, HBR, HBR2 RBR, HBR, HBR2

Cyclone V RBR, HBR RBR, HBR

Stratix V RBR, HBR, HBR2 RBR, HBR, HBR2

IP Core Verification

UG-01131

2015.05.04

Before releasing a publicly available version of the DisplayPort IP core, Altera runs a comprehensive

verification suite in the current version of the Quartus® II software. These tests use standalone methods

and the Qsys system integration tool to create the instance files. These files are tested in simulation and

hardware to confirm functionality. Altera tests and verifies the DisplayPort IP core in hardware for

different platforms and environments.

The DisplayPort IP core has been tested at VESA Plugtest events and passes the Unigraf DisplayPort Link

Layer CTS tests.

Performance and Resource Utilization

This section contains tables showing IP core variation size and performance examples.

The following table lists the resources and expected performance for selected variations. The results were

obtained using the Quartus II software v15.0 for the following devices:

• Arria V (5AGXFB3H4F40C5)

• Cyclone V (5CGTFD9E5F35C7)

• Stratix V (5SGXEA7K2F40C2)

• Arria 10 (10AX115S2F45I2SGES)

Altera Corporation

About This IP Core

Send Feedback

Page 13

UG-01131

2015.05.04

Performance and Resource Utilization

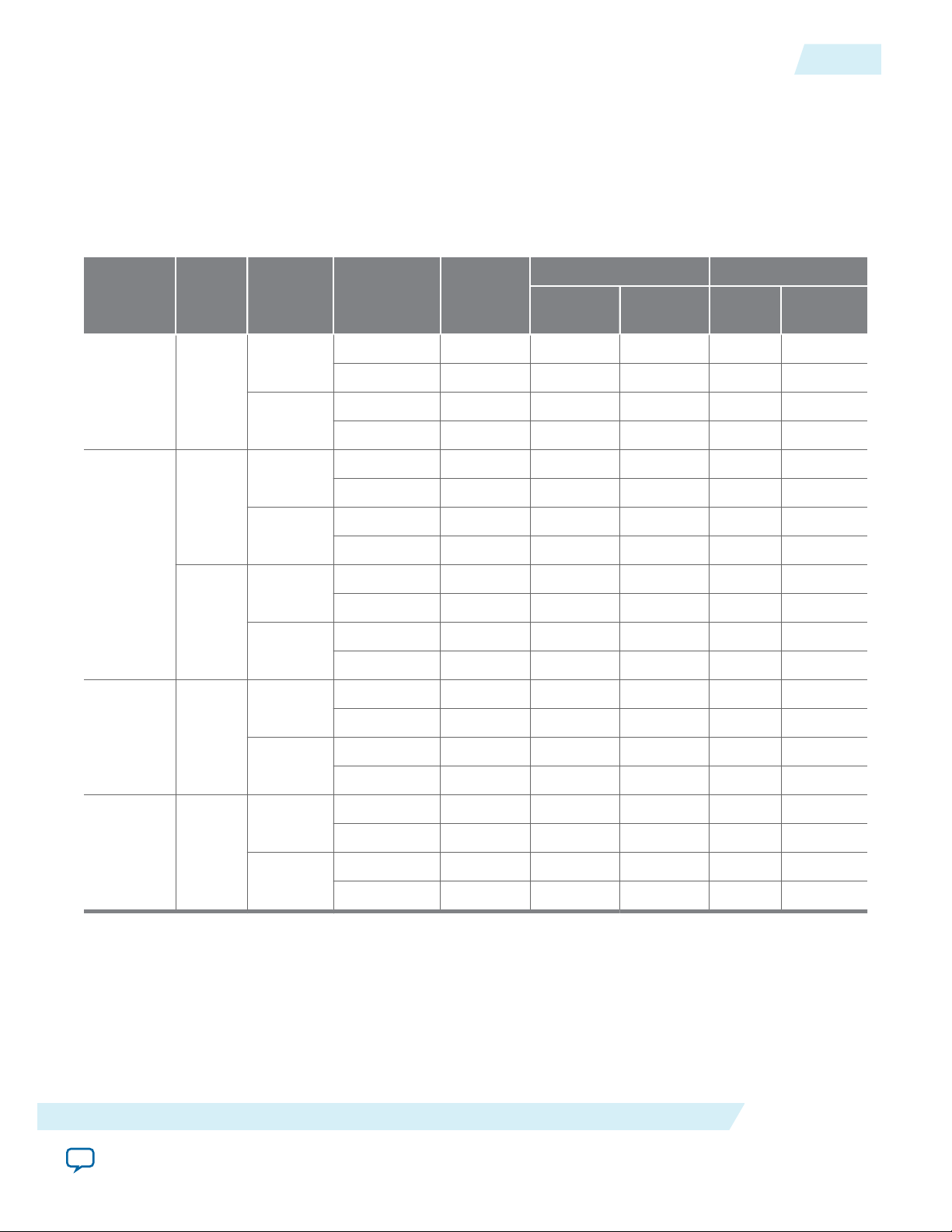

Table 2-2: DisplayPort IP Core FPGA Resource Utilization

The table below shows the resource information for Arria V and Cyclone V devices using M10K; Arria 10 and

Stratix V devices using M20K. The resources were obtained using the following parameter settings:

• Mode = duplex

• Maximum lane count = 4 lanes

• Maximum video input color depth = 24 bits per pixel (bpp)

• Pixel input mode = 1 pixel per clock

2-3

Device Streams Direction

RX

TX

Arria 10

Single

stream

(SST)

RX

SST

TX

Arria V

GX

MST

RX

(2

streams)

TX

RX

Cyclone

V GX

SST

TX

Symbol per

Clock

ALMs

Logic Registers Memory

Primary Secondary Bits M10K or

Dual 7,087 9,580 1,001 16,576 30

Quad 9,957 11,121 1,153 31,424 30

Dual 16,075 10,205 465 27,424 27

Quad 29,075 13,605 646 39,776 40

Dual 7,176 9,432 1,015 16,576 30

Quad 9,881 10,793 1,221 31,424 30

Dual 16,340 10,213 499 27,424 27

Quad 29,258 13,568 715 39,776 40

Dual 13,337 15,901 1,650 30,336 52

Quad 20,913 19,551 1,952 57,472 52

Dual 31,790 20,095 879 47,680 54

Quad 58,333 27,433 1,357 65,472 80

Dual 7,137 9,446 1,035 16,576 30

Quad 9,817 10,886 1,229 31,424 30

Dual 16,343 10,157 604 27,424 27

Quad 29,326 13,537 825 39,776 40

M20K

Stratix

V GX

Related Information

Fitter Resources Reports

More information about Quartus II resource utilization reporting.

About This IP Core

Send Feedback

RX

Dual 7,006 9,569 966 15,552 28

Quad 9,967 11,087 1,065 30,400 28

SST

Dual 16,340 10,213 499 27,424 27

TX

Quad 29,258 13,568 715 39,776 40

Altera Corporation

Page 14

2015.05.04

acds

quartus - Contains the Quartus II software

ip - Contains the Altera IP Library and third-party IP cores

altera - Contains the Altera IP Library source code

<IP core name> - Contains the IP core source files

www.altera.com

101 Innovation Drive, San Jose, CA 95134

Getting Started

3

UG-01131

Subscribe

Send Feedback

This chapter provides a general overview of the Altera IP core design flow to help you quickly get started

with the DisplayPort IP core. The IP core is installed as part of the Quartus II installation process. You can

select and parameterize any Altera IP core from the library. Altera provides an integrated parameter

editor that allows you to customize the DisplayPort IP core to support a wide variety of applications. The

parameter editor guides you through the setting of parameter values and selection of optional ports.

Installing and Licensing IP Cores

The Altera IP Library provides many useful IP core functions for your production use without purchasing

an additional license. Some Altera MegaCore IP functions require that you purchase a separate license for

production use. However, the OpenCore® feature allows evaluation of any Altera IP core in simulation

and compilation in the Quartus II software. After you are satisfied with functionality and perfformance,

visit the Self Service Licensing Center to obtain a license number for any Altera product.

Figure 3-1: IP Core Installation Path

Note:

The default IP installation directory on Windows is <drive>:\altera\<version number>; on Linux it is

<home directory>/altera/ <version number>.

Related Information

• Altera Licensing Site

• Altera Software Installation and Licensing Manual

OpenCore Plus IP Evaluation

Altera's free OpenCore Plus feature allows you to evaluate licensed MegaCore IP cores in simulation and

hardware before purchase. You need only purchase a license for MegaCore IP cores if you decide to take

your design to production. OpenCore Plus supports the following evaluations:

©

2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

ISO

9001:2008

Registered

Page 15

3-2

Specifying IP Core Parameters and Options

• Simulate the behavior of a licensed IP core in your system.

• Verify the functionality, size, and speed of the IP core quickly and easily.

• Generate time-limited device programming files for designs that include IP cores.

• Program a device with your IP core and verify your design in hardware.

OpenCore Plus evaluation supports the following two operation modes:

• Untethered—run the design containing the licensed IP for a limited time.

• Tethered—run the design containing the licensed IP for a longer time or indefinitely. This requires a

connection between your board and the host computer.

Note: All IP cores that use OpenCore Plus time out simultaneously when any IP core in the design times

out.

Specifying IP Core Parameters and Options

Follow these steps to specify the DisplayPort IP core parameters and options.

1. Create a Quartus II project using the New Project Wizard available from the File menu.

2. On the Tools menu, click IP Catalog.

3. Under Installed IP, double-click Library > Interface > Protocols > Audio&Video > DisplayPort.

The parameter editor appears.

4. Specify a top-level name for your custom IP variation. This name identifies the IP core variation files

in your project. If prompted, also specify the targeted Altera device family and output file HDL

preference. Click OK.

5. Specify parameters and options in the DisplayPort parameter editor:

UG-01131

2015.05.04

• Optionally select preset parameter values. Presets specify all initial parameter values for specific

applications (where provided).

• Specify parameters defining the IP core functionality, port configurations, and device-specific

features.

• Specify options for generation of a timing netlist, simulation model, testbench, or example design

(where applicable).

• Specify options for processing the IP core files in other EDA tools.

6. Click Generate to generate the IP core and supporting files, including simulation models.

7. Click Close when file generation completes.

8. Click Finish.

9. If you generate the DisplayPort IP core instance in a Quartus II project, you are prompted to add

Quartus II IP File (.qip) and Quartus II Simulation IP File (.sip) to the current Quartus II project.

Simulating the Design

You can simulate your DisplayPort IP core variation using the simulation model that the Quartus II

software generates. The simulation model files are generated in vendor-specific subdirectories of your

project directory. The DisplayPort IP core includes a simulation example.

The following sections teach you how to simulate the generated DisplayPort IP core variation with the

generated simulation model.

Altera Corporation

Getting Started

Send Feedback

Page 16

UG-01131

2015.05.04

Related Information

DisplayPort IP Core Simulation Example on page 7-1

The Altera DisplayPort simulation example allows you to evaluate the functionality of the DisplayPort IP

Core and provides a starting point for you to create your own simulation. This example targets the

ModelSim SE simulator.

Simulating with the ModelSim Simulator

To simulate using the Mentor Graphics ModelSim simulator, perform the following steps:

1. Start the ModelSim simulator.

2. In ModelSim, change directory to the project simulation directory <variation>_sim/mentor.

3. Type the following commands to set up the required libraries and compile the generated simulation

model:

do msim_setup.tcl

ld

run -all

Simulating with the ModelSim Simulator

3-3

Compiling the Full Design and Programming the FPGA

You can use the Start Compilation command on the Processing menu in the Quartus II software to

compile your design. After successfully compiling your design, program the targeted Altera device with

the Programmer and verify the design in hardware.

Related Information

• Quartus II Incremental Compilation for Hierarchical and Team-Based Design

Provides more information about compiling the design.

• Quartus II Programmer

Provides more information about programming the device.

Getting Started

Send Feedback

Altera Corporation

Page 17

2015.05.04

Source

Lane 0 Data (1.62, 2.7, or 5.4 Gbps)

Lane 1 Data (1.62, 2.7, or 5.4 Gbps)

Lane 2 Data (1.62, 2.7, or 5.4 Gbps)

Lane 3 Data (1.62, 2.7, or 5.4 Gbps)

AUX Channel (1 Mbps)

Hot Plug Detect

Sink

www.altera.com

101 Innovation Drive, San Jose, CA 95134

DisplayPort Source

4

UG-01131

Subscribe

Source Overview

The DisplayPort source has a scalable main link with 1, 2, or 4 lanes for a total up to 21.6 Gbps bandwidth.

A bidirectional AUX channel with 1 Mbps Manchester encoding provides side-band communication.

Figure 4-1: DisplayPort Source

The main link has three selectable data rates: 1.62, 2.7, and 5.4 Gbps. The source device sets the lane count

and link rate combination (referred to as the policy) according to the sink’s capabilities and required

video bandwidth. The IP core transmits the video and audio streams on the main link with embedded

clocking.

Send Feedback

The IP core transmits data in a scrambled ANSI 8B/10B format. The data transmission includes

redundancy for error detection. The secondary data stream, such as an audio stream, uses a ReedSolomon encoder for error correction.

The AUX channel is an AC-coupled differential pair for bidirectional communication. The signaling is a

self-clocked Manchester encoding at 1 Mbps. As in the 100-T Ethernet protocol, the encoder uses a

preceding synchronization pattern in each 16-byte maximum packet.

The AUX channel uses a master-slave hierarchy in which the source (master) initiates all communication.

©

2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

ISO

9001:2008

Registered

Page 18

DisplayPort Source

Encoder

txN_video_in

txN_vid_clk

txN_audio

txN_audio_clk

tx_aux

aux_clk

txN_ss

tx_ss_clk

txN_msa_conduit

tx_aux_debug

tx_xcvr_interface

Video Input

Video Clock

Audio Input

Audio Clock

AUX Interface

AUX Clock

Secondary Stream

(Avalon-ST Interface)

MSA Input

AUX Debug Stream

(Avalon-ST Interface

TX Transceiver Interface

Transceiver Management

tx_analog_reconfig

Controller Interface

tx_mgmt_interruptInterrupt

xcvr_mgmt_clkTransceiver Management Clock

tx_reconfigTX Reconfiguration

tx_mgmt

clk

Avalon-MM Interface

Avalon-MM Interface Clock

TX Analog Reconfiguration

clk_calCalibration Clock

4-2

Source Functional Description

Source Functional Description

The DisplayPort source has a complete set of parameters for optimizing device resources.

The DisplayPort source consists of a DisplayPort encoder block, a transceiver management block, and a

controller interface block with an Avalon-MM interface for connecting with an embedded controller such

as a Nios II processor. You configure the ports using an RTL wrapper instantiation or by implementing

the IP core as a Qsys component.

Figure 4-2: DisplayPort Source Top-Level Block Diagram

UG-01131

2015.05.04

Altera Corporation

DisplayPort Source

Send Feedback

Page 19

8B/10B

Encoder

Multiplexer

Fixed MSA

(txN_msa)

Avalon-MM

(tx_mgmt)

Bidirectional AUX Data

AUX Debug Stream

HPD

40-Bit (Quad Symbol) or

20-Bit (Dual Symbol)

Data to Transceiver

Secondary Data

(txN_ss)

Video Input

(txN_video_in)

Audio Stream

(txN_audio)

Gearbox FIFO Packetize

Throttle

Measure

Video

MSA

Generator

Blank Start

Generator

Video Data

Packet

Generator

Pixel

Steer

Secondary

Stream Encoder

DCFIFO

Controller

Registers

AUX

Controller

tx_ss_clk

clk

txN_vid_clk

aux_clk

txN_audio_clk

Legend

Audio

Encoder

DCFIFO

Training

Pattern 1

Training

Pattern 2

UG-01131

2015.05.04

Figure 4-3: DisplayPort Source Functional Block Diagram

Main Data Path

4-3

DisplayPort Source

The source accepts a standard H-sync, V-sync, and data enable video stream for encoding. The IP core

latches and processes the video data before processing it using the txN_video_in input. N represents the

stream number: tx_video_in (Stream 0), tx1_video_in (Stream 1), tx2_video_in (Stream 2), and

tx3_video_in (Stream 3).

The video data width supports 6 to 16 bits per color (bpc) and is user selectable. If you set the Pixel input

mode option to Dual or Quad, the video input can accept two or four pixels per clock, thereby extending

the pixel clock rate capability.

Main Data Path

The main data path consists of the packetizer, measurement, and blank generator paths. The IP core

multiplexes data from these three paths and outputs it through an 8B/10B encoder.

Send Feedback

Altera Corporation

Page 20

4-4

Packetizer Path

Packetizer Path

The packetizer path provides video data resampling and packetization, and consists of the following steps:

1. The pixel steer block decimates the data to the requested lane count (1, 2, or 4).

2. The DCFIFO crosses the data into the main link clock domain (tx_ss_clk, generated by the

transceiver), which can be 270, 135, 81, 67.5, or 40.5 MHz depending on the actual main link rate

requested and the symbols per clock.

3. The gearbox resamples the video data according to the specified color depth. You can optimize the

gearbox by implementing fewer color depths. For example, you can reduce the resources required to

implement the system by supporting only the color depths you need instead of the complete set of

color depths specified in the DisplayPort specification.

4. The IP core packetizes the re-sampled data. The DisplayPort specification requires data to be sent in a

transfer unit (TU), which can be 32 to 64 link symbols long. To reduce complexity, the DisplayPort

source uses a fixed 64-symbol TU. The specification also requires that the video data be evenly distrib‐

uted within the TUs composing a full active video line. A throttle function distributes the data and

regulates it to ensure that the TUs leaving the IP core are evenly packed.

Note: A minimal DisplayPort system should support both 6 and 8 bpc. The VESA DisplayPort specifica‐

The packetizer punctuates the outgoing 16-bit data stream with the correct packet comma codes.

Internally, the packetizer uses a symbol and a TU counter to ensure that it respects the TU boundaries.

UG-01131

2015.05.04

tion requires support for a mandatory VGA fail-safe mode (640 x 480 at 6 bpc).

Measurement Path

The measurement path determines the video geometry required for the DisplayPort main stream

attributes (MSA), which are sent once every vertical blanking interval. Optionally, the IP core can import

a fixed MSA data parameter from an external port, removing the measurement logic. This feature is useful

for embedded systems that only use known resolutions and synchronous pixel clocks.

Blank Generator Path

The blank generator path determines when to send the blank start comma codes with their corresponding

video data packets. This path can operate in enhanced or standard framing mode.

Multiplexer

The IP core multiplexes the packetized data, MSA data, and blank generator data into a single stream. The

combined data goes through 8B/10B encoding and is available as a 20-bit double-rate or a 40-bit quadrate DisplayPort encoded video port. The 20- or 40-bit port connects directly to the Altera high-speed

output transceiver.

During training periods, the source can send the DisplayPort clock recovery and symbol lock test patterns

(training pattern 1, training pattern 2, and training pattern 3, respectively), upon receiving the request

from downstream DisplayPort sink.

The source also implements an AUX channel controller, which you access using an embedded controller.

The embedded controller acts as an Avalon-MM master and sends read/write commands to the

Avalon-MM slave interface. The IP core clocks the AUX channel using a 16 MHz clock input (aux_clk).

Related Information

Controller Interface on page 4-11

Altera Corporation

DisplayPort Source

Send Feedback

Page 21

UG-01131

2015.05.04

Embedded DisplayPort (eDP) Support

The DisplayPort IP core is compliant with eDP version 1.3. eDP is based on the VESA DisplayPort

standard. It has the same electrical interface and can share the same video port on the controller. The

DisplayPort IP core supports:

• Full (normal) link training—default

• Fast link training—mandatory eDP feature

Source Parameters

You set parameters for the source using the DisplayPort parameter editor.

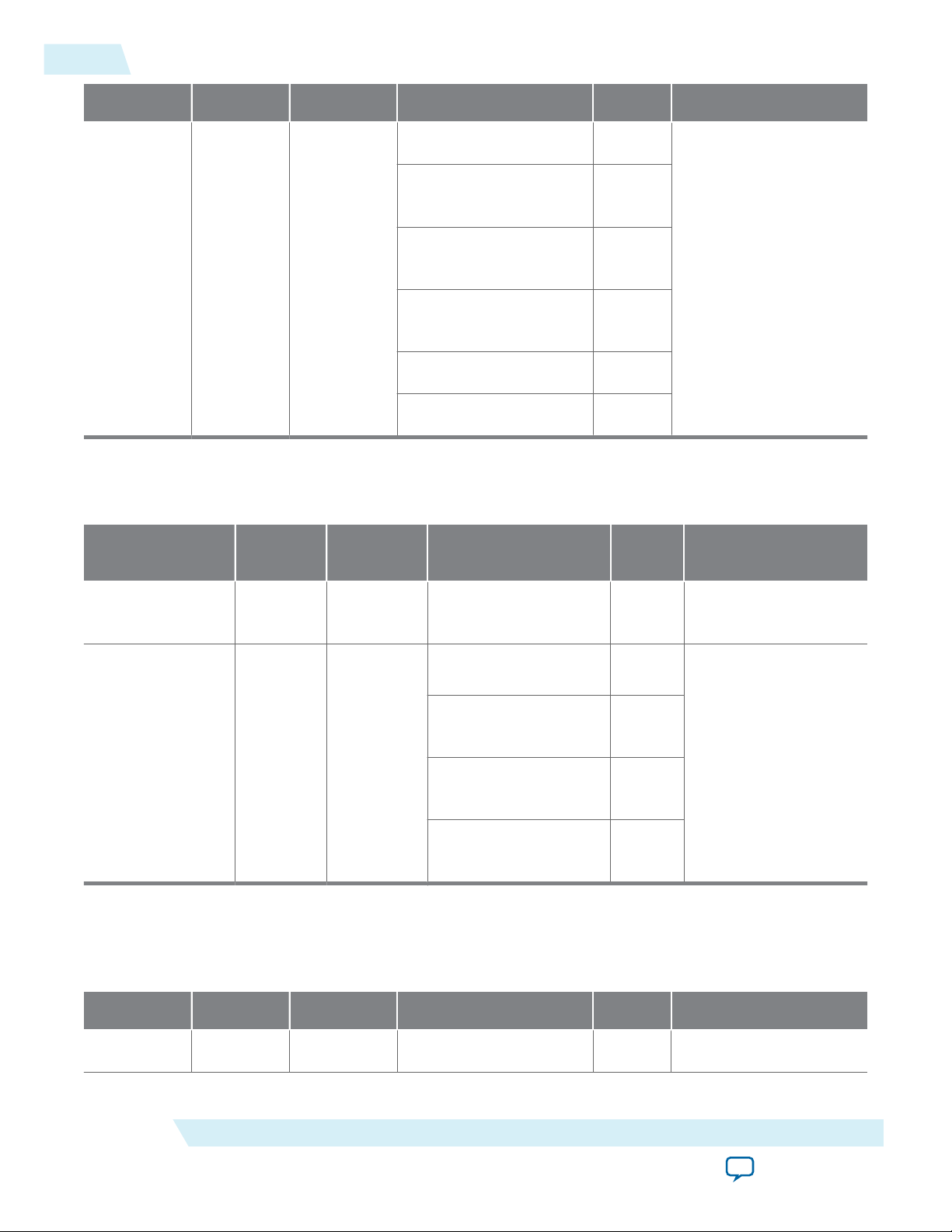

Table 4-1: Source Parameters

Parameter Description

Device family Select the targeted device family—Arria 10, Arria V

Embedded DisplayPort (eDP) Support

GX, Arria V GZ, Cyclone V, or Stratix V—matches

the project device family.

4-5

Support DisplayPort source Turn on to enable DisplayPort source.

Maximum video input color depth Select the video input interface port bits per color.

Determines top-level video input port width (for

example, 6 bpc = 18 bpp, 16 bpc = 48 bpp).

TX maximum link rate Select the the maximum link rate. 5.4 Gbps, 2.7

Gbps, 1.62 Gbps.

Note: Cyclone V devices do not support 5.4

Gbps.

Maximum lane count Select the maximum lanes desired (1, 2, or 4).

Symbol output mode Specify how many symbols are transferred during

each clock cycle: dual or quad symbol, or TX

transceiver data width: dual (20 bits) or quad (40

bits).

Dual symbol mode saves logic resource but requires

the core to run at twice the clock frequency of quad

symbol mode. If timing closure is a problem in the

device, you should consider using quad symbol

mode.

DisplayPort Source

Send Feedback

Altera Corporation

Page 22

4-6

Source Parameters

Parameter Description

Pixel input mode Select the number of pixels per clock (single, dual, or

quad symbol).

• If you select dual pixels per clock, the pixel clock

is ½ of the full rate clock and the video port

becomes two times wider.

• If you select four pixels per clock, the pixel clock

is ¼ of the full rate clock and the video port

becomes four times wider.

Scrambler seed value Specify the initial seed for the scrambler block. Use

16’hFFFF for normal DP and 16’hFFFE for eDP.

Enable AUX debug stream Turn on to send source AUX traffic output to an

Avalon-ST port.

Import fixed MSA Turn on to enable the source to accept a fixed MSA

value from an external port.

UG-01131

2015.05.04

Support CTS test automation Turn on to support CTS test automation.

Support secondary data channel Turn on to enable secondary data.

Support audio data channel Turn on to enable audio packet encoding.

Note: To use this parameter, you must turn on

the Support secondary data channel

parameter.

Number of audio data channels Specify the number of audio channels supported.

6-bpc RGB or YCbCr 4:4:4 (18 bpp) Turn on to support 18 bpp encoding.

8-bpc RGB or YCbCr 4:4:4 (24 bpp) Turn on to support 24 bpp encoding.

10-bpc RGB or YCbCr 4:4:4 (30 bpp) Turn on to support 30 bpp encoding.

12-bpc RGB or YCbCr 4:4:4 (36 bpp) Turn on to support 36 bpp encoding.

16-bpc RGB or YCbCr 4:4:4 (48 bpp) Turn on to support 48 bpp decoding.

8-bpc YCbCr 4:2:2 (16 bpp) Turn on to support 16 bpp encoding.

10-bpc YCbCr 4:2:2 (20 bpp) Turn on to support 20 bpp encoding.

12-bpc YCbCr 4:2:2 (24 bpp) Turn on to support 24 bpp encoding.

Altera Corporation

DisplayPort Source

Send Feedback

Page 23

UG-01131

2015.05.04

16-bpc YCbCr 4:2:2 (32 bpp) Turn on to support 32 bpp encoding.

Support MST Turn on to enable multi-stream support.

Max stream count Select the maximum amount of streams supported

Source Interfaces

The following tables list the source’s port interfaces. Your instantiation contains only the interfaces that

you have enabled.

Table 4-2: Controller Interface

Interface Port Type Clock Domain Port Direction Description

Source Interfaces

Parameter Description

(1-4).

4-7

clk Clock N/A clk

reset Reset

tx_mgmt AV-MM clk

tx_mgmt_

IRQ

clk

clk

reset

tx_mgmt_address[8:0] Input

tx_mgmt_chipselect

tx_mgmt_read Input

tx_mgmt_write Input

tx_mgmt_

writedata[31:0]

tx_mgmt_readdata[31:0] Outp

tx_mgmt_waitrequest Outp

tx_mgmt_irq

irq

Input

Clock for embedded

controller

Input

Reset for embedded

controller

Input

Avalon-MM interface

Input

for embedded

controller

ut

ut

Output Interrupt for

embedded controller

DisplayPort Source

Send Feedback

Altera Corporation

Page 24

4-8

Source Interfaces

Table 4-3: Transceiver Management Interface

n is the number of TX lanes.

Interface Port Type Clock Domain Port Direction Description

UG-01131

2015.05.04

xcvr_

Clock N/A

mgmt_clk

clk_cal Clock N/A

tx_

analog_

reconfig

Conduit

xcvr_mgmt_

clk

xcvr_mgmt_clk Input

clk_cal Input

tx_vod[2n - 1:0] Output

tx_emp[2n - 1:0] Outp

ut

tx_analog_reconfig_req Outp

ut

tx_analog_reconfig_ack Input

tx_analog_reconfig_

busy

Input

Transceiver

management clock

A 50-MHz calibration

clock input. This clock

must be synchronous

to the clock used for

the Transceiver

Reconfiguration block

(xvcr_mgmt_clk),

external to the Display‐

Port sink.

Transceiver analog

reconfiguration

handshaking

tx_link_rate[1:0] Output

tx_

reconfig

Conduit

xcvr_mgmt_

clk

tx_link_rate_

8bits[7:0]

tx_reconfig_req Input

tx_reconfig_ack Input

tx_reconfig_busy Input

Outp

ut

Transceiver link rate

reconfiguration

handshaking

Note: Value of tx_link_rate[1:0]: 0=1.62Gbps, 1=2.70Gbps, 2=5.40Gbps; value of tx_link_rate_8bits[7:0]:

0×06=1.62Gbps, 0×0a=2.70Gbps, 0×14=5.40Gbps.

Note: For devices using a 50-MHz xcvr_mgmt_clk clock, connect the same clock directly also to the

clk_cal signal. For devices using a 100-MHz xcvr_mgmt_clk clock, connect the same clock to

clk_cal signal through a by-2 divider.

Altera Corporation

DisplayPort Source

Send Feedback

Page 25

UG-01131

2015.05.04

Source Interfaces

Table 4-4: Video Interface

v is the number of bits per color, p is the pixels per clock (1 = single, 2 = dual, and 4 = quad). N is the stream

number; for example, tx_vid_clk represents Stream 0, tx1_vid_clk represents Stream 1, and so on.

Interface Port Type Clock Domain Port Direction Description

4-9

txN_vid_

Clock N/A

txN_vid_clk Input

Video clock

clk

txN_vid_data[3v*p-1:0] Input

Video data and

standard H/V synchro‐

nization video port

input

txN_

video_in

Conduit txN_vid_clk

txN_vid_v_sync[p-1:0] Input

txN_vid_h_sync[p-1:0] Input

txN_vid_f[p-1:0] Input

txN_vid_de[p-1:0] Input

Table 4-5: AUX Interface

Interface Port Type Clock Domain Port Direction Description

aux_clk Clock N/A

aux_reset Reset

aux_clk aux_reset Input

tx_aux Conduit aux_clk

aux_clk Input

tx_aux_in Input

tx_aux_out Outp

ut

tx_aux_oe Outp

AUX channel clock

AUX channel reset

AUX channel interface

ut

tx_aux_

debug

DisplayPort Source

Send Feedback

AV-ST aux_clk

tx_hpd Input

tx_aux_debug_

data[31:0]

tx_aux_debug_valid Outp

Output

ut

tx_aux_debug_sop Outp

ut

tx_aux_debug_eop Outp

ut

tx_aux_debug_err Outp

ut

tx_aux_debug_cha Outp

ut

Avalon-ST stream of

AUX data for

debugging

Altera Corporation

Page 26

4-10

Source Interfaces

2015.05.04

Table 4-6: Secondary Interface

N is the stream number; for example, tx_msa_conduit represents Stream 0, tx1_msa_conduit represents Stream

1, and so on.

Interface Signal Type Clock Domain Port Direction Description

UG-01131

tx_ss_clk Clock N/A

MSA

Conduit

(txN_

msa_

conduit)

Secondary

Stream

AV-ST tx_ss_clk

(txN_ss)

Table 4-7: Audio Interface

tx_ss_clk Output

tx_ss_clk txN_msa[191:0] Input

txN_ss_data[127:0] Input

txN_ss_valid Input

txN_ss_ready Outp

ut

txN_ss_sop Input

txN_ss_eop Input

TX transceiver clock

out and clock for

secondary stream

Input port for fixed

MSA parameters

Secondary stream

interface

m is the number of TX audio channels. N is the stream number; for example, tx_audio represents Stream 0,

tx1_audio represents Stream 1, and so on.

Interface Signal Type Clock

Domain

Port Direction Description

Clock N/A txN_audio_clk Input Audio clock

Audio

(txN_audio)

Altera Corporation

Conduit

txN_audio_

clk

txN_audio_lpcm_data

[m*32-1:0]

txN_audio_valid Input

txN_audio_mute Input

Input

Audio sample data

interface

DisplayPort Source

Send Feedback

Page 27

UG-01131

2015.05.04

Table 4-8: TX Transceiver Interface

n is the number of TX lanes, s is the number of symbols per clock.

Note: Connect the DisplayPort signals to the Native PHY signals of the same name.

Controller Interface

4-11

Interface Port Type Clock

Clock N/A tx_std_clkout[n–1:0] Input TX transceiver clock

Conduit tx_std_

clkout

Conduit N/A tx_pll_powerdown Output PLL power down for

Conduit xcvr_mgmt_

TX transceiver

clk

interface

Conduit N/A tx_analogreset[n–

Conduit N/A tx_cal_busy[n–1:0] Input Calibration in

Conduit N/A tx_pll_locked Input PLL locked signal

Domain

Port Direction Description

tx_parallel_

data[n*s*10–1:0]

tx_digitalreset[n–

1:0]

1:0]

out

Output Parallel data for TX

transceiver

TX transceiver

Output Resets the digital TX

portion of TX

transceiver

Output Resets the analog TX

portion of TX

transceiver

progress signal from

TX transceiver

from TX transceiver

Controller Interface

The controller interface allows you to control the source from an external or on-chip controller, such as

the Nios II processor. The controller can control the DisplayPort link parameters and the AUX channel

controller.

The AUX channel controller interface works with a simple serial-port-type peripheral that operates in a

polled mode. Because the DisplayPort AUX protocol is a master-slave interface, the DisplayPort source

(the master) starts a transaction by sending a request and then waits for a reply from the attached sink.

The controller interface includes a single interrupt source. The interrupt notifies the controller of an HPD

signal state change. Your system can interrogate the DP_TX_STATUS register to determine the cause of the

interrupt. Writing to the DP_TX_STATUS register clears the pending interrupt event.

Related Information

• Multiplexer on page 4-4

• DisplayPort Source Register Map and DPCD Locations on page 9-1

DisplayPort source instantiations require an embedded controller (Nios II processor or another

controller) to act as the policy maker.

DisplayPort Source

Altera Corporation

Send Feedback

Page 28

4-12

AUX Interface

AUX Interface

The IP core has three ports that control the serial data across the AUX channel:

• Data input (tx_aux_in)

• Data output (tx_aux_out)

• Output enable (tx_aux_oe). The output enable port controls the direction of data across the bidirec‐

tional link.

These ports are clocked by the source’s 16 MHz clock (aux_clk). The AUX channel’s physical layer is a

bidirectional 2.5 V SSTL Class II interface.

The source’s AUX controller allows you to capture all bytes sent from and received by the AUX channel,

which is useful for debugging. The IP core provides a standard stream interface that you can use to drive

an Avalon-ST FIFO component directly.

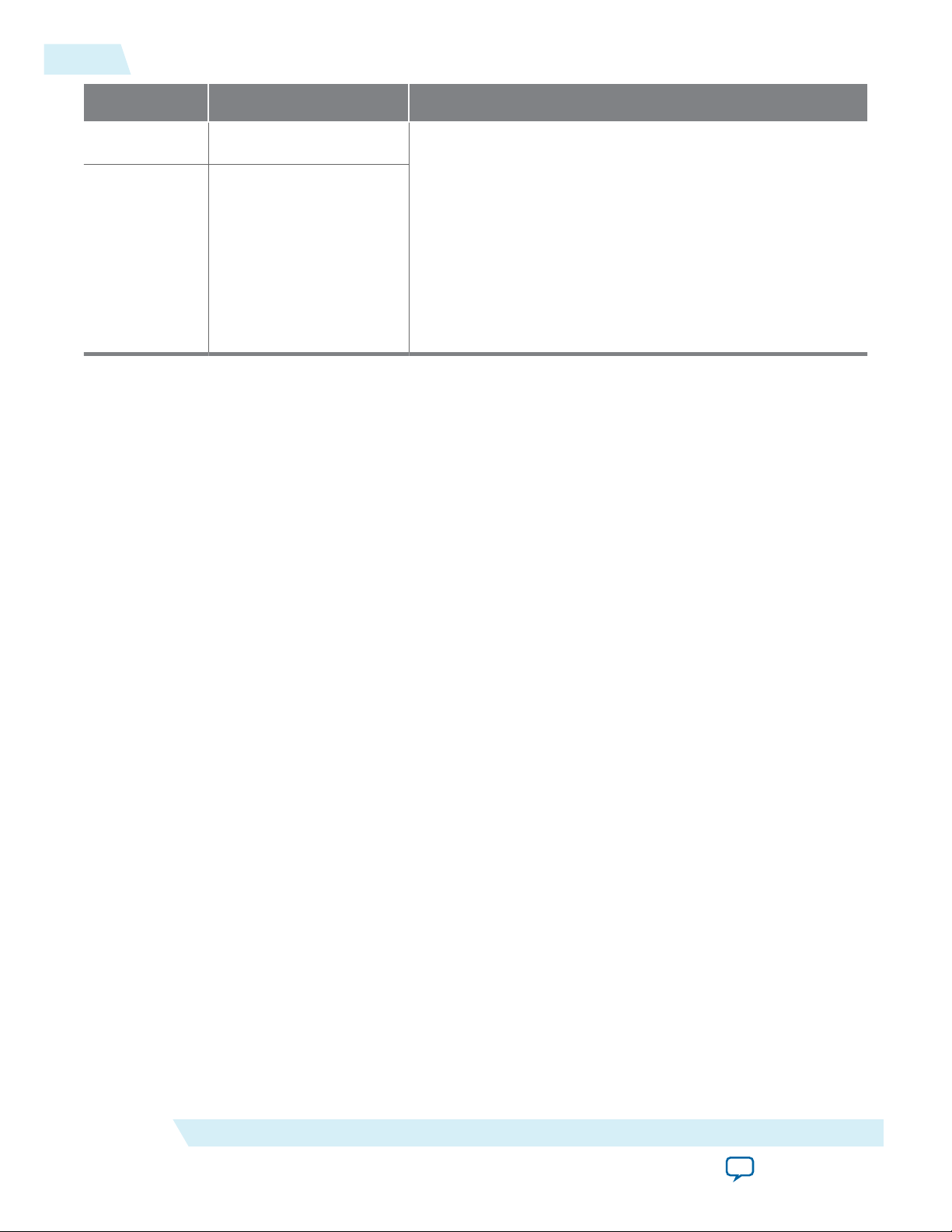

Table 4-9: Source AUX Debug Interface Ports

Port Comments

UG-01131

2015.05.04

tx_aux_debug_data[31:0]

tx_aux_debug_valid

tx_aux_debug_sop

tx_aux_debug_eop

tx_aux_debug_err

tx_aux_debug_cha

Related Information

AN 522: Implementing Bus LVDS Interface in Supported Altera Device Families

Video Interface

The core sends video to be encoded through the txN_video_in interface, which provides a standard Hsync and V-sync input with support for interlaced or progressive video. You specify the data input width

via a parameter. The same input port transfers RGB and YCbCr data in either 4:4:4 or 4:2:2 color format.

Data is most-significant bit aligned and formatted for 4:4:4.

The source AUX debug interface inserts a 1 µs timestamp counter in bits

[31:8]; bits [7:0] represent the byte received or transmitted.

Qualifies valid stream data.

Indicates the message packet’s first byte.

Indicates the message packet’s last byte. The last byte should be ignored

and is not part of the message.

Indicates if the IP core detects an error in the current byte.

Indicates the direction of the current byte. 1 = byte transmitted by the

source, 0 = byte received from the sink.

Altera Corporation

DisplayPort Source

Send Feedback

Page 29

47 32 31 16 15 0

txN_vid_data[47:0]

18 bpp RGB

24 bpp RGB/YCBCr444 (8 bpc)

30 bpp RGB/YCBCr444 (10 bpc)

36 bpp RGB/YCBCr444 (12 bpc)

48 bpp RGB/YCBCr444 (16 bpc)

n/2-1 0n - 1 n/2 txN_vid_data[n - 1:0]

71 48 47 24 23 0

txN_vid_data[95:0]

95 72

Pixel 3 Pixel 2 Pixel 1 Pixel 0

UG-01131

2015.05.04

TX Transceiver Interface

Figure 4-4: Video Input Data Format

18 bpp to 48 bpp port width when txN_video_in port width is 48 (16 bpc, 1 pixel per clock)

The following figure shows the sub-sampled 4:2:2 color format for a video port width of n. The mostsignificant half of the video port always transfers the Y component while the least-significant half of the

video port transfers the alternate Cr or Cb component. If the Y/Cb/Cr component widths are less than

n/2, they must be most-significant bit aligned with respect to the n and n/2-1 boundaries.

Figure 4-5: Sub-Sampled 4:2:2 Color Format Video Port

4-13

If you set the Pixel input mode option to Dual or Quad, the IP core sends two or four pixels in parallel,

respectively. To support video resolutions with horizontal active, front porch or back porch of a length

not divisible by 2 or 4, the following signals are widened:

• Horizontal and vertical syncs

• Data enable

The following figure shows the pixel data order from least significant bits to most significant bits.

Figure 4-6: Video Input Data Alignment

For RGB 18 bpp when txN_video_in port width is 96 (8 bpc, 4 pixels per clock)

TX Transceiver Interface

The transceiver or Native PHY IP core instance is no longer instantiated within the DisplayPort IP core.

The DisplayPort IP uses a soft 8B/10B encoder. This interface provides TX encoded video data

(tx_parallel_data) in either dual symbol (20-bit) or quad symbol (40-bit) mode and drives the digital

DisplayPort Source

Send Feedback

Altera Corporation

Page 30

4-14

Transceiver Reconfiguration Interface

reset (tx_digitalreset), analog reset (tx_analogreset), and PLL powerdown signals

(tx_pll_powerdown) of the transceiver.

Transceiver Reconfiguration Interface

You can reconfigure the transceiver to accept single reference clock. The single reference clock is a 135MHz clock for all bit rates: RBR, HBR, and HBR2.

• During run-time, you can reconfigure the transceiver to operate in either one of the bit rate by

changing TX CMU PLL divide ratio.

When the IP core makes a request, the tx_reconfig_req port goes high. The user logic asserts

tx_reconfig_ack and then reconfigures the transceiver. During reconfiguration, the user logic holds