Page 1

DX-70

Service Manual

CONTENTS

• S P E C IF IC A T IO N S .................................................................................................................. 1

• C I R C U IT D E S C R I P T IO N ................................................................................................. 2

• S E M IC O N D U C T O R D A T A ........................................................................................... 1 2

• E X P L O D E D V I E W ................................................................................................................ 2 1

• P A R T S L IS T .................................................................................................................................. 2 8

• A D J U S T M E N T ............................................................................................................................. 4 2

• P C B O A R D V I E W .................................................................................................................... 4 9

• B L O C K D I A G R A M

• C I R C U IT D IA G R A M ............................................................................................................... 5 9

• E D X -1 ...................................................................................................................................................... 6 5

............................................................................................................... 5 8

A L IN C O , IN C

Page 2

SPECIFICATIONS

1) General

Operating mode

Number o f memory channels

Antenna impedance

Power requirement

Grounding method

Current drain

Operating temperature

Frequency stability

Dimensions

Weight

2) Transmitter

Transmit frequency

coverage

(e.g. U.S. Version)

HF band

j Power

output

50 M Hz

Modulation

system

Receive

Transmit

160 m band

80 m band

40 m band

30 in band

20 m band

17 m band

15 m band

12 m band

10 m band

6 m band

SSB. CW. FM

AM

SSB, CW. FM

band

AM

SSB Balanced modulation

AM

FM

J3E(LSB,USB). A IA (C W ). F3E(FM )

100

50 Q unbalanced

13.8 V DC ± 15% (11.7 to 15.8 V DC)

Negative ground

1.0 A max.

20 A max,

-10 °C to +60 °C

± 10 ppm (-10 “C to +50 °C)

178(w) X 58(h) X 228(d) mm

(179 X 71 X 268 mm for projections included)

Approx. 2.7 kg

1.8000 to 1.9999MHz

3.5000 to 3.9999MHz

7.0000 to 7.2999MH z

10.1000 lo 10.1499M Hz

14.0000 to 14.3499MHz

18.0680 to 18.1679MHz

21.0000 to 21.4499M Hz

24.8900 to 24.9899M Hz

28.0000 to 29.6999M H z

50.0000 to 53.9999M Hz

100 W (high)

Approx. 10 W (low)

40 W (high)

Approx. 4 W (low)

10 W (high)

Approx. 1 W (low)

4 W (high)

Approx. 0.4 W (low )

Lo w power modulation

Reactance modulation

Page 3

Transmitter (continued)

Spurious emission

Carrier Suppression

Sideband suppression

Maximum FM

deviation (default)

Microphone impedance

HF bands Less than -50 dB (-45 dB in 10 MHz band)

50 M H z band

HF bands

50 M H z band

3) Receiver

Receiver circuitry

Receive frequency range

Intermediate frequency

SSB, C W

(S/N 10 dB)

Sensitivity

Selectivity

AM (1 kHz,

30%, Mod,

S/N 10 dB)

FM (1 kHz.

3.5kHz, DEV,

S1NAD 12 dB)

SSB, AM (Na rrow) 2.4 kHz/-6 dB, 4.5 kHz/-60 dB

SSB(Nartow), CW(Standard) 1.0 kHzy-6 dB, 3.0 kHz/-60 dB

CW(Narrow )

AM(Standard), FM

Superiors and image rejection ratio

Audio output power

RIT/TXIT range

0.5 to 1.8 MHz

1.8 to 30 MHz

50 to 54 M Hz

0.5 to 1.8 M H z

1.8 to 30 MHz +6 dB (2 pV)

50 to 54 MH z

28 to 30 M H z -6 dB|i(0.5 |aV)

50 to 54 M H z

Less than -60 dB

More than 40 dB

More than 50 dB (at 1 kHz)

±2 .5 kHz

± 5 kHz

2 kfi

Double conversion superheterodyne

0.1500 MHz to 30.0000 MHz. 50.0000 MHz to 54.0000 MHz

71.75 M H z (1st) 455 kH z(2nd)

0 dB (1 pV)

-12 dB (0.25 (j.V)

-16 dB (0.15 pV)

+20 dB (10n V )

+6 dB (2 |iV)

-10 dBji (0.3 }.iV)

500 Hzy-6 dB, 3.0 kHzA60 dB

9 kHz/-6 dB, 20 kHz/-50 dB

More than 70 dB

More than 2.0 W (at 8 Q, 10% THD)

±1.4 kHz

Page 4

ro

CIRCUIT DESCRIPTION

1. Receiver System

1) F ilte r U nit

a. HF Antenna Input

SA501 and R527 are installed in the input part of HF antenna terminal as the

countermeasure against the thunder.

The electric charge of HF antenna is discharged at R527, and when the voltage

becomes over about 300V, the gap of SA501 is discharged so that the receiving

input circuit is protected.

The input signal from HF antenna is passed through the transmission/reception

selecting relay RL513. The followings are prevented in LPF consisting of 1525,

L526, C580, C581 and C582: 2m band image receiving, passing through the First

IF (71,75MHz) and leaking of the first local oscillating frequency (72~130MHz) to

the antenna terminal.

b. 50MHz Antenna Input

2) Main Unit

a. Front End

The receiving signal from the antenna of 50MHz band is passed through the LPF

for transmission/reception and passed through the transmitting power detection

circuit, then led to transmission/reception switching circuit consisting of D508 and

D509, and to HPF. The signal is amplified about 8dB in Q503. Because the space

noise in 50MHz band is less than it in HF band, its exclusive receiving preamplifier

is equipped to get high sensitivity.

The receiving signal of 50MHz or HF is selected in RL514, then after passing

through the attenuator circuit (ON/OFF) of about 20dB consisting of RL515, R528

and R531 the signal is led to the Main unit.

The receiving signal output from Filter Unit is fed to Main unit through CN2. •

HPF, consisting of L19, L20, C47, C48, C49, C50, C51 and C52, eliminates the

strong radio signal of MW band of 1.6MHz or below. In case of receiving the

signal of 1.6MHz or below, the sensitivity is controlled by the attenuator in R37 and

BPF1, also the signal is separated into 1.6MHz, over or below.

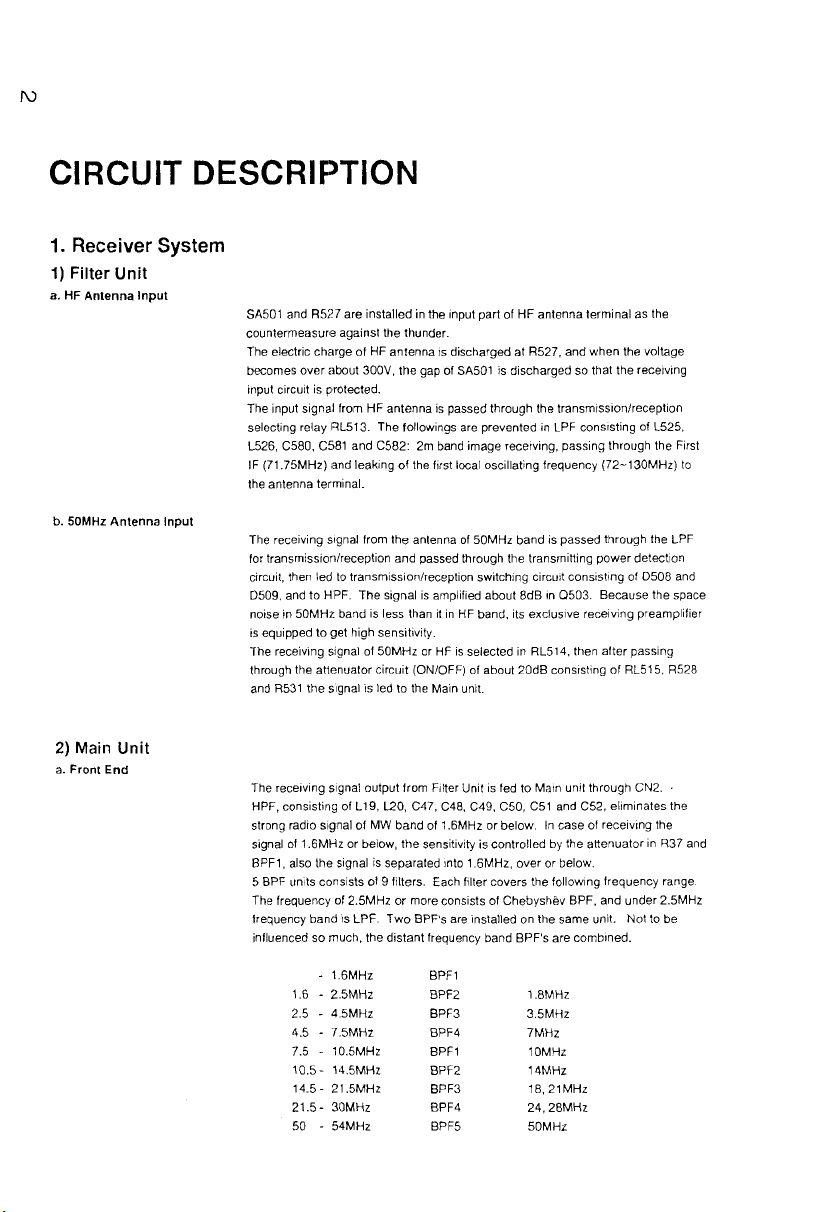

5 BPF units consists of 9 filters. Each filter covers the following frequency range.

The frequency of 2.5MHz or more consists of Chebyshev BPF, and under 2.5MHz

frequency band is LPF. Two BPF's are installed on the same unit. Not to be

influenced so much, the distant frequency band BPF’s are combined.

1.6MHz BPF1

-

1.G -

2..5MH2

2.5 - 4.5MHz BPF3 3.5MHz

4.5 - 7.5 MHz

7.5 - 10.5MHz

14.5MHz

10.5-

14.5- 21.5MHz BPF3 18, 21 MHz

21.5- 30MHz

50 - 54MHz

BPF2

BPF4

BPF1 10MHz

BPF2 14MHz

BPF4

BPF5

1.8MHz

7MHz

24, 2BMHz

50MHz

Page 5

Passing through BPF, the signal turns ON/OFF in the switching diode, D29 and

D30. This preamplifier is the parallel grounded gate operation of Q9 and Q10

(2SK2171), so the unit can obtain a good performance at a high level input signal

with low NF.

The wide range frequency from about 1 MHz to 60MHz is amplified about 10dB.

This lOdB preamplifier and 20dB attenuator in the Filter unit are combined, then by

pressing RF gain switch on the front panel, one of four steps, -20, -10, 0, or +10dB

is selected.

The LPF, consisting of L52, L53, L54, C103, C104, C105, and C106, prevents the

following first receiving mixer from the local oscillation leaking, and also prevents

the first IF and image of the spurious receiving.

The first receiving mixer consisting of Q10 and Q11 is the balanced mixer, in which

the local oscillating signal is fed to the gate of 2SK2171.

7 he 3rd intercept point is about 20dBm, and local oscillator of about 2V P-P is fed

to the gate. The receiving signal is converted into the first IF of 71.75MHz.

As the ratio of the spurious interference is decreased in 50MHz band mode, the

trap of 71.75MHz consisting of L72 and C107 keeps the ratio of spurious interfer

ence 70dB or more in all band.

b. The First IF Amplifier Circuit

c. The Second Mixer Circuit, The Second Amplifier Circuit

d. IF Filter

FL1: A and FL1: B are the crystal filters of 71.75MHz. By the combination of two

filters, the unit has the characteristics of the band width of 15kHz or more/3dB and

the value of guaranteed attenuation of 70dB or more. H ere the image ratio is

determined 70dB or more (approx. 80dB}. The first IF amplifier circuit of Q12 is

located between the crystal filters to prevent the loss in the front-end and mutual

interference.

The first IF amplifier circuit Q12 decides the sensitivity after passing the mixer.

AGC voltage is applied to the second gate.

DBM (Double Balanced Mixer) consists of L14, D7 and L16. The signal is passed

in the opposite direction while receiving or transmitting in this DBM. Approximately

OdBm is as the second \ocat oscitaVing \evel, and the third IP is approximately

lOdBm.

The receiving signal (71.75MHz) and the second local oscillating frequency

(71,295MHz) is mixed, and unwanted signal is eliminated in LPF consisting of L17,

L73 and C36, then the signal of 455kHz is generated. After passing through the

switching diode D8, the signal is amplified in Q22. The source of Q22 is controlled

by the output of the noise blanker circuit.

After passing through the transmission/reception switching diode D9, the signal is

led to one oi three ceramic filters of 455kHz. The selectivity is decided here

except CW narrow.

SSB, AM-NARROW FL3(CFJ455K5) 2.4kHz/-6dB 4.5kHz/-60dB

SSB-NARROW, CW FL2(CFJ455K8) 1.0kHz/-6dB 3.0kHz/-60dB

FM, AM FL.4(CFW455G) 9kHz/-6dB 20kHz/-50dB

Each filter has 4 switching diodes (D3-D48) in front and rear to isolate the filter.

Page 6

The isolation is required the value of guaranteed attenuation of each filter (approx.

70dB) or more. The diode connected in parallel in front and rear of no used filter is

short and the diode connected in series is open. The combination of open and

short is used to get the high isolation.

The modes, transmission/reception and wide/narrow of this filter are selected by

Q36-Q46, D79, D80, D82, D83, D84.

e. The Second IF Amplifier Circuit

f. Demodulation Circuit

g. CW Audio Filter

After passing through the filter, the signal is led to the transmission/reception

switching diode D49, and amplified in Q23 and Q24, then buffered in Q25.

The AGC voltage is applied to the second gate of Q22, Q23 and Q24.

The output level of 025 is fixed because the AGC voltage is added to the receiv

ing signal.

This output signal is used for the demodulation in SSB, AM and CW modes and

AGC detection.

In the FM mode, after passing through the transmission/reception switching diode

of D49, a part of receiving signal is fed to 1C7(MC3357) from C221, then it is IF-

amplified and demodulated. C214 is connected in parallel to the feedback resister

R182, and the resister is de-emphasized. Even in the FM mode, Q23, Q24 and

Q25 are active, also AGC is operated.

In SSB and CW modes, the following local oscillating frequency is supplied from

PLL unit to IC3 balanced mixer, then the signal is demodulated.

The receiving signal is fed to Pint, and local oscillation Pin3, then picked up the

demodulation output of approximately 100mV from Pin7.

USB 456.5kHz

LSB 453.5kHz

CWU 455.8kHz

CWL 454.2kHz

The output is led to the switching circuit of each mode, and to the CW audio filter.

In AM mode, the signal is detected in D51, then led to IC5.

In FM mode, the signal is demodulated and de-emphasized in above-mentioned

IC7, then led to IC5.

IC4 is the active filter, which consists of the combination of low-pass filter and high-

pass filter in the operational amplifier. It has the band width of about 600Hz (-6dB)

centering the trequency of about 800Hz.

SHIFT

+IF

SHIFT

+IF

+1F SHIFT

SHIFT

+IF

h. AF, AGC Time Constant Selection

GO

1C5 is the analogue multiplexer which has 2 circuits with 4 contact points, and

switches the demodulation output in every mode and AGC time constant. The

voltage combined in D55 and D56 is input to Pin9 and Pinl 0, then the output of

1C3 (SSB, CW-W), the modulation output of FM/AM and CW audio filter output

(CW-N) are selected. The voltage of 8V is applied to Pin6 (INHIBIT) when

transmitting, and the modulation output is turned OFF unconditionally.

Page 7

i. AF Amplifier

The voltage that can pass through the analogue switch of IC5 is very low. The

voltage is amplified approximately 20dB in IC12: B to get higher AF input voltage

to following IC13 (voltage controlled electronic volume). Also a part of this output

is picked up and output to Pin6 of microphone as non-squelched audio output.

This output is used as the terminal of packet, RTTY, SSTV, etc.

j. Electronic Volume, AF Amplifier

IC13 is the dual electronic volume controlled by the voltage.

The volume is controlled by the AF GAIN VR on the front panel. Pin5 is the control

terminal. The value of the attenuation is the minimum when the control voltage is

about 3.4V, and the value is 90dB or more at maximum when the control voltage is

about 3.1V.

One of the circuits is for volume control of the demodulation sound, and the other

for the volume control of the beep and sidetone. The beep and sidetone can be

heard even if the volume is set to the minimum point and sound tone is related with

AF GAIN VR.

The squelch circuit (IC14:A, Q14) controls Pin5. The output of IC14: A activates to

close the squelch when transmitting, so Q14 is turned OFF in D85 to control the

volume of the sidetone.

The receiving sound is fed to Pin6 and applied from Pin7. As for the beep and

side tones, Pin2 is for input and Pin 1 for output. These two outputs are combined

with the inpul of LPF amplifier IC12:A. The high tone noise that is generated in IF

amplifier is decreased by LPF amplifier.

The output of IC12: A is attenuated in R309 and R310 to get the same level with

IC20, and also to decrease the noise. IC20 is the AF power ampliiier which can

get the output of 2W or more (THD 10%) at 8£2 load. The ripple filter consists of

Q51 and C260.

The AGC voltage is supplied one stage to first IF amplifier and three stages to

second IF amplifier. These IF amplifiers consist of 3SK131. AGC voltage is

applied to the Gate2. The IF amplifiers are designed that the gain is changed

linearly corresponding to the AGC voltage.

D53 and D54 are the rectifier, and Q26 is DC amplifier. D50, the anode is set to

about 2V in R176, D110, D111 and R177. Usually AGC voltage is applied 2.4V.

The strong signal rectifies D53 and D54 resulting in DC voltage. Q26 decreases

the AGC voltage.

When AGC-FAST is selected in SSB/CW mode, C205 and C206 are connected

between 5V and AGC line in parallel. The attack time of AGC is determined in

R1 67 and C206, then the release time is determined in R168 and C206. The

characteristics are "fast attack" and "slow release". In case of AGC-SLOW, the

analogue switch IC6 is turned ON, then R175 and C287 are connected in parallel.

The release time is lengthened because of C287. In case of AM, C206 is con

nected in parallel, then the attack time is delayed, which is the average type. D110

and D111 is the thermal compensation of D50.

in receiving AM, AGC is the average type not to follow the modulation.

Page 8

I. S Meter, Squelch

The output of Pin 1 and RF meter output are combined in the diode, then it is sent

to the front CPU to display the meter. The output signal of Pin1 is fed to Pin6 of

IC14:A. The voltage of Pin5 is determined by the squelch VR of front unit. Com

paring with this voltage, the squelch is opened or closed.

While the check operation the CPU output decreases the voltage of squelch VR in

front side to open the squelch forcedly. The squelch output controls IC13, at the

same time it is provided to the front unit to light RX LED and led to CPU unit.

m. Noise Blanker Circuit

This circuit eliminates the pulse noise of a car, etc. Because the noise emitting

time is short, in this duration the operation of receiver is stopped to prevent the unit

Irom emitting a noise. The pulse noise is delayed when it is passed through the

narrow band filter, and the emitting time becomes longer. It makes difficult to

eliminate the noise, so it is necessary to eliminate the noise in the earlier stage.

A part of the second mixer output, whose band width is limited, is amplified in Q20,

Q19, 018, and Q16. The signal is detected in D33 and D34, and the AGC voltage

is applied to 019, Q18 and Q16.

The charge time constant of this AGC is determined by R82 and C128, and also

the discharge constant is determined by R81+R82, C128. The voltage of AGC

does not rise suddenly because of the charge constant, so that this voltage is not

applied to almost all the short signals such as pulse noise, but is applied to the

continuous signals such as receiving signal and amplilier gain is decreased.

While emitting the pulse noise, the AGC voltage does not follow the pulse noise,

so the detected voltage is high, then 015 is turned ON in that time.

On the contrary, as for the continuous signal, the detected voltage of D33 and D34

is fixed by AGC, so 015 is turned OFF because of the emitter bias of R85 and

R84.

Namely Q15 is turned ON only the time of the pulse noise, then 021 is turned

OFF. The source of IF amplifier of 022 is biased through R98 and R 102 so that

the gain is decreased and the signal is blanked. When the emitter of Q15 is

biased to high, the Noise Blanker is turned OFF.

Page 9

2. Transmitter System

1) Main Unit

a. Microphone Amplifier

The input signal from microphone is amplified by the low noise amplifier 056

through the mic gain VR1. It is possible to bias (8V) the microphone terminal with

R388 for the microphone which needs the power supply, (solder bridge)

In SSB/AM mode, The gain of IC21 (approx. 15dB) is determined by R329 and

R328.

In FM mode, R330 is connected to R320 in parallel by Q55, then the gain is

increased approximately 34dB. Also the cut off frequency is risen, and the signal

is pre-emphasized and operated as a limitter.

In the SSB/AM mode, C345 and R384 are conntected to the feedback circuit by

Q63 when the speech compressor is turned ON. The gain is increased about

15dB, then IC21:B is operated as the limitter.

When the speech compressor is ON, the low frequency is cut by C345.

In FM mode, the gain is risen enough, so the speech compressor has no effect.

The output of Pin1 of IC21: B is attenuated in R326 and R325. The subaudible

tone from PLL unit is applied through R325. (When the Tone is ON.)

IC21: A is LPF amplifier that is the Splutter filter in FM mode, and it is operated for

speech compressor.

This signal is output to PLL unit as the FM modulation, and output to the balanced

modulation of IC2.

The output to IC2 is muted by Q54 in CW/FM mode.

b. Balanced Mixer

c. IF Filter

!C2 is the balanced mixer, and the carrier is suppressed in SSB mode. To get

more ratio of carrier suppression, the balance adjustment of VR3 and VR4 are

applied.

The carrier is necessary in CW/FM/AM mode, so the input of Pinl is made unbal

anced by applying the DC voltage to obtain the carrier.

By applying the DC in AM/FM mode, or by keying in CW mode, the balance is

broken to obtain the carrier wave. VR11 is used for the adjustment of carrier level.

In the AM mode, the DC and modulation is added simultaneously. In SSB mode,

the modulation is added by R317. In AM mode, D93 is DC-biased and turned ON.

Then the attenuator consisting of R317 and R393 limits the modulation.

After the output of !C2 increases the impedance in C177 and L77, it is passed

through D49 and led into band limit IF filter. D52 is isolated highly by connecting to

the output in parallel at receiving. In SSB mode, the output is DSB signal. (Double

Side Band)

The filter is switched by the selection of above-mentioned diode switch. The signal

is passed through the following filer in each mode.

SSB FL3(CFJ455K5) 2.4kHz/-6dB 4.5kHz/-60dB

CW FL2 (CFJ455K8) 1.0kHz/-6dB 3.0kHz/-60dB

FM, AM FL4 (CFW455G) 9kHz/-6dB 20kHz/-50dB

SSB is obtained by eliminati'ng one of side bands of DSB through the filter.

Page 10

d. IF Amplifier, The Second Mixer

After passing through the filter, the signal is led to D37, Q7, and D6, and passed

through the second mixer in the opposite direction of the receiving, then the signal

of 71.75MHz is obtained. Q6 operates the CW keying.

The voltage of ALC is added to the second gate of Q7.

The local oscillating signal of 71.295MHz and unwanted signal are eliminated in

FL1: A and FL5. The signal is amplified in 05, passed through FL5, then led to the

balanced mixer of Q3 and Q4.

e. The First Transmitting Mixer

f. Power Amplifier

2) PA Unit

a. Power Amplifier

b. Final Stage Power Amplifier

This mixer is the balanced type, and the unwanted signals (IF and local oscillating

signal) are decreased. The best operation is selected by biasing the second gate.

To decrease the spurious, the signal is balanced in VR1.

Passing through tihe mixer, the transmitting signal which has the desired transmit

ting Irequency is passed after switching the LPF tor HF band or BPF tor 50MHz

band. The unwanted signal and especially the leak of local oscillating signal is

decreased as less as possible.

The signal is amplified up to 0~3dBm in Q1. T notch filter consists of C1, C2 and

11. It is tuned to approximately 44MHz while using 50MHz band to decrease the

spurious signal. Then the signal is supplied to PA unit.

The signal input to PA unit is amplified up to approximately 100mW. The idling

current of 0601 flows about 100mA during transmitting as A-class amplifier. The

frequency characteristics are compensated by feedback, besides connecting the

capacitor to emitter resistor in parallel.

The signal is amplified up to 10W in Q602 and Q603.

PA amplifier is the wide band range from 1.8MHz to 50MHz

The idling current flows 100mA (adjusted in VR601), and the amplifier is the push-

pull type.

D601 is connected to Q602 and Q603 thermally, and the idling current is compen

sated for temperature. This output is switched at RL601 in 50MHz, then supplied

to filter unit.

in the final stage amplifier circuit consisting of Q604 and Q605 (2SC2904), the

idling current of about 300mA is flowing. The base bias is made by Q606. D604

and D605 are connected to 0604, 0605 and Q606 thermally, and the idling current

is compensated for temperature.

The feedback circuit, consisting of R621, R622, R623, C633, R627, R628 and

C637, makes the gain flat in the wide range of 1.8MHz~30MHz.

The 100W output is led to filter unit.

The collector cun'ent of 0606 and Q607 is detected by using FB606 and L611.

Then led to the main unit.

U l

Page 11

c. Fan Control

The heat of Q606 and Q607 is detected by the thermistor TH601, and the fan is

controlled. While transmitting, the resistance value is decreased by the rising of

the temperature, then the voltage of inverting input terminal of IC601A/B is de

creased. Non-inverting input is applied with the voltage corresponding to the

temperature. When the temperature goes up to about 50°C or more and the

compared voltage becomes lower than the inverting input voltage, Q607 is turned

ON by the output voltage of comparator, 10601: A. Then the fan starts turning at a

low speed by the value of series resistor (R639).

When the temperature rises more and the voltage becomes much lower than the

compared voltage IC6Q1: B, Q608 is turned ON. Then R639 is turned OFF and

the fan turns at a high speed according to the value of series resistor of R640 to

decrease the compared voltage of IC601: A.

When the temperature goes up to about 100°C and the voltage is decreased

further lower, IC601: A supplies again, then R639 and R640 are connected in

parallel to turn the fan at a higher speed. Although ordinary PDWN is pulled up to

14V by R637, the power output is set to LOW because both cathode terminals of

D608 become LOW when the fan turns at a high speed. Then the signal is sent to

the main unit as the control signal for power down at high temperature.

As the compared voltage of IC601: B is decreased in D611 while receiving,

IC601:B does not work if the temperature does not go up higher than it while

transmitting. The temperature, at which the fan turns at a middle speed or more, is

higher than it while transmitting. At high temperature, fan's turning speed comes

down whiie receiving.

d. Protection Circuit

e. CW Keying Circuit

For the protection of the final power amplifier, the followings are equipped:

SWR detection

Protection against over current

Power down circuit for the temperature detection

As the base voltage of main unit 049 goes down to LOW by CW keying, the

voltage is supplied to collector. This output controls all of the circuit operation by

CW keying.

The collector output of 049 is passed through D95, VR11 and D93, and the

balance is broken by applying DC voltage to the balanced mixer to generate the

carrier. VR11 determines the CW waveform of rise and fall by adjusting the carrier

level in R285 and C248.

At the same time Q48 is turned O N to turn OFF Q6 for keying isolation. C244

makes the OFF time of 06 longer not to influence the keying waveform.

The voltage is applied to IC17: B Pin5 in D95, and the output of Pin7 turns 046 ON

to set PTT line to LOW in D73, then the unit enters the transmitting mode. The

capacitor (C246, C247) is connected between Pin5 of IC17: B and the ground.

The holding time of transmitting is determined according to the discharge time

constant. BK1, BK2, and BK3 are the voltages tor the setting of 3*bit break-in time

constant. 8 stages voltage is obtained by the combination of the resistors R269,

R270 and R271.

In the Full Break-in mode, all of BK1, BK2 and BK3 are set to LOW, in the Semi

Break-in mode, one of BK1, BK2, or BK3 is applied the voltage.

Page 12

When all of the breakers are applied the voltage, it is used as the shortest time

constant.

When in the full break-in mode, all of the voltages of BK1, BK2 and BK3 are low

level, and Q47 is turned OFF. Therefore only C246 is the very short discharge

constant, it is the full break-in mode with short transmitting time. One of BK1, BK2

and BK3 is supplied the voltage, and Q47 is turned OFF, then connected to C247

and C246 in parallel. The discharge time constant is longer, and it is the semi

break-in time constant.

There are 7 stages of the voltage in the semi break-in mode according to the

output voltage of BK1, BK2 or BK3. This is applied to the compared voltage of

IC17: B, then the discharge time constant is changed. Namely when the voltage is

applied to all of BK1, BK2 and BK3, the time constant is the shortest.

When the break-in mode is set to AUTO, BK1 only is supplied, and the compared

voltage of IC17:B is controlled by the output voltage of IC17: B.

In the AUTO mode the keying output is emitted by one-shot multivibrator consist

ing of IC18A aod B whenever the key is pressed. Therefore the average value ot

the output voltage of IC18: A is in proportion to the average speed of keying. To

obtain the average voltage in R281, C245, etc., integrate the voltage. Then this

output is D/C amplified in !C17:A, and provided as the compared voltage of keying.

D97 is used for OFF in the AUTO mode. When the AUTO mode is in the LOW

level, the voltage charged in C245 is short, then the operation in AUTO mode is

stopped.

D107 and R360 are used to get up speed rising when the keying is started. D92

and R280 determine the discharge time constant. While receiving the time

constant is prolonged.

The selection of transmission/reception follows the keying speed from 30 letters/

minute to 200 letters/minute.

The transmitting mode is held between letters, and the unit returns to receiving

mode between words.

f. Power Control, ALC Circuit

The forward wave voltage in proportion to the transmitting power obtained in filter

unit is inverting-input to IC8A, and inverting-amplified. Non-inverting input is

applied the voltage, and the output voltage is shifted by the non-inverting input

voltage.

ALC line is applied the voltage of about 2.7V beforehand, and the ALC voltage is

supplied to the second gate of the amplifier.

When the forward wave voltage is detected, the output voltage of IC8: A is de

creased. If it is about 3V or below, the ALC line voltage is decreased by D63.

VR7 is used for the adjustment of 100W. When the unit is switched to 50W by S i,

Q27 is turned ON and VR5 is connected in parallel to decrease the voltage, then

the unit is adjusted to 50W.

In AM mode, R195 is connected in parallel to decrease the voltage up to about

40 W.

In the iow power mode, R191 is connected in parallel by setting to LOW, and the

voltage is decreased.

029 and VR8 are used for the adjustment to get the required power of about 10W

in the matching operation of external automatic tuner. (The required power

depends on the tuner.)

When the value of SWR is high, the reflected wave voltage turns Q28 ON to

decrease the power. The unit is operated when the SWR is about 3 or more.

Page 13

Compared with the forward wave detection power in HF band of 100 W, the

forward wave voltage in 50MHz band of 10W is set to higher a little.

In SSB mode, "fast attack" is obtained by D63, and the release time of "slow

attack" is obtained by C222 and R130. In AM mode C221 is connected in parallel

by Q30, and the unit is operated in near the average value.

g. Over Current Protection Circuit

h. RF Meter Circuit, ALC Indication

i. Sidetone Circuit

j. Tune Circuit

The final stage collector current which is detected in PA unit is differential-amplified

in IC8: B. The output voltage is decreased according to the increase of the

current. Then ALC line is fallen by D63 and the output power is decreased. The

operational point is decided in VR6.

The forward wave is amplified in IC9: A to obtain the meter output voltage.

The peak is held in D70, R223 and C223, and the meter swings smoothly.

Meter output voltage and S meter output voltage are switched in D71 and D86

automatically.

ALC voltage is inverting voltage amplified in IC9: B.

This output is applied to the base of Q31, then sent to front unit for the detection of

transmission/reception and lighting the transmitting LED. The LED brightness is

changed according to the ALC voltage.

The comparison frequency of the second local oscillator in PLL unit (65kHz~

85kHz) is divided by 10 in IC714, then led to the main unit. In addition the fre

quency is divided by 10 in IC19 of the main unit to obtain the sidetone of 650Hz~

850Hz. The comparison frequency of the second local oscillator is changed

according to the CW offset setting. To relate with the sidetone, comparison

frequency is about 100 times the CW offset. IC19 Pin2 is controlled by Q65 at CW

keying. The time constant is delayed not to give the influence to waveform of the

sidetone.

The following active filter Q50 makes the square wave to sine wave to obtain

better sound. The rise/fall wave of the sidetone is generated by keying controlling

the bias of base and emitter.

When using the external automatic antenna tuner, this circuit controls the matching

start signal and the operation of the unit during tuner matching.

When the tune operation is started, the Tune voltage is supplied to operate the

one-shot multivibrator in IC18: C, D. The voltage of about 8 V is applied to outside

for a fixed time through Q52 as the start signal. In the other hand, Q53 supplies

the tune voltage of sink output, it becomes LOW while tuning. (For the transceiver

made by ICOM, KENWOOD).

As soon as the tuner receives the tune start signal, the tuner provides it as the

tuning signal. (TKEY terminal)

CPU observes the TKEY terminal, and keeps the unit in TUNE mode indicating

that the tuner is operating while it is in the LOW level. CPU releases the TUNE

mode when TKEY terminal is in LOW for 20 seconds or more. In the Tune mode

the unit transmits a signal in AM mode, the microphone output is muted, then the

carrier is kept on outputting about 10W (adjustable).

Page 14

k. Regulated Power Supply Circuit

I. Mode Voltage, Function Control

(BPF/ LPF Selector)

ICt1 is the BV Regulated Power Supply Circuit. T8V that is necessary tor trans

mitting is made in 033, and R8V that is necessary (or receiving is made in Q35.

IC10, 032 and 034 control the transmission/reception. When PTT line is con

nected to the ground through the microphone terminal or CW keying output (Q46),

H level is supplied from IC10: A and it is led to CPU of front unit to detect the

transmission/reception switching.

IC10: C delays the rise of receiving in R227, C224 and D62 and controls in Q32

and Q33.

While receiving, the current is flowing from 13.8V through R230 and D75, then the

base voltage Q33 is approximately 8.7V, and the emitter output is just 8V.

While transmitting, the base voltage of Q33 is OV because Q32 is turned ON, and

R8V is not provided.

While transmitting R8V is short by D77, and it makes the charge voltage such as

electrolytic capacitor discharge momentarily not to remain R8V.

As for 035, as same as R8V the current is flowing from 13.8V through R230 and

D75, then the base voltage of Q35 is approximately 8.7V and the emitter output is

just 8V while receiving. While transmitting, the base voltage is OV because 034 is

turned ON, and T8V is not provided.

While transmitting T8V is short by D77, and it makes the charge voltage such as

electrolytic capacitor discharge momentarily not to remain T8V.

After delayed the transmitting rise time in IC10:B, the.signal is inverted in 1C18:D,

then T8V is controlled in 034.

When Pin8 IC10:A is supplied the voltage, the unit enters PTT lock mode without

changing the output of PinlO even if the PTT line is connected to the ground.

The enable terminals of IC15 and IC16 select the signal ENX or ENY by using

IC24 and Q62.

The data from CPU (DAT2) consists of 16-bit serial data, two 8-bit shift resistors

are connected in series.

IC22 and IC23 control the band selection, ON/OFF of preamplifier, ATT, power, TX

mute function,, etc. They are operated in Low level.

IC15 controls the Mode voltage, and IC16 controls filter, AGC, Break-in, PTT lock,

and Noise blanker. The voltage o1 every mode (USB, LSB, AM, CW, CWU, CWL,

FM, TUNE) turns ON 041, Q42, 043 and Q44 to supply 8V .

m- LPF

HF supplied from PA final stage eliminates harmonics through LPF of filter unit.

Input/Output of this filter is switched by the relay, and Input/Output of unused filter

is short at the relay contact.

LPF control is used the BPF control voltage of the main unit.

Every LPF consists of Chebyshev filter, and double or more harmonics are

attenuated about 40dB or more.

LO ~ 2.5MHz BBO, BB1

L1 2.5MHz~4.0MHz

4.0MHz~7.5MHz BB3 7MHz band

L2

L3

7.5MHz~14.5MHz

BB2 3.5MHz band

BB4, BB5

1.8MHz band

10, 14MHz band

Page 15

L4 14.5MH2~21.5MHz BB6 18,21MHzband

L5 21,5MHz~30.0MHz BB7 24,28MHz band

The transmitting signal, whose spurious is eliminated by passing through LPF, is

led to power detection circuit and supplied to HF antenna terminal passing through

the selection relay.

n. 50MHz Transmission/Reception Selector

o. Power Detection Circuit

p. Dial Rotating Detection

50MHz band performs the transmission/reception selection by the diode of D508

and D509. It is supplied to antenna terminal of 50MHz through LPF.

Both D508 and D509 are turned OFF while receiving, the receiving signal from the

antenna terminal is passed through LPF (L520, L521, C570-C574, L518, C565)

and HPF (L516, C562~C564), then amplified in 0503.

0501 and 0502 are turned ON while transmitting, and D508 and D509 are turned

ON then the transmitting output is passed.

The antenna input of receiving circuit is short because D509 is turned ON. Also as

the parallel resonant circuit consists of L518, D508, etc., the transmitting signal

does not influenced.

The each power detection circuit is equipped with HF band and 50MHz band.

The harmonics are sometimes generated depending on the using diode in the

detection circuit. LPF makes the standing wave, so the circuit is located before the

LPF in 50MHz band whose spurious specification is severe, and after LPF in HF

band.

From now on the operation in HF band is shown, and in 50MHz band the operation

is the same.

L534 is 10-turn bifilar of toroidal core (twisted pairs of AWG). Therefore the both

sides are 20 turns with center tap.

Piercing the center hole of the core means the same with 1 turn. So the trans

former is 1:20.

Therefore R508 is applied the voltage (forward wave voltage) according to the

output voltage, and R509 is applied the voltage (reflected wave) according to the

reflected power. The output power and reflection detect the power to control the

power in the main unit.

The puise generated by the rotation of the main dial is eliminated the chattering in

IC1001: A, B. IC1001: A and B are the Schmitt triggers by the feedback from the

output.

The rise and fall of each output is differentiated in !C1002:A, C, so the pulse

number is doubled. Then it is 4 times the pulse number because of synthesizing in

IC1001: C.

To find the rotation direction, it is detected in 1C1002: B and IC1003 and fed to

CPU. As S1002 generates 50 pulse at 1 rotation, what is input to CPU is 200

pulse/rotation, and 5kHz/rotation in 25Hz step.

The main dial rotates very fast and generates so many pulses. The pulse is

divided in IC1004, and the pulse number is stored as the 6-bit binary digit by each

dividing output. At a high speed rotation the frequency is forwarded by counting

the pulse number stored in IC1004, then the process is finished, the pulse number

Page 16

c»

3) Front Unit

a. Pow er Switch

stored in IC1004 is reset by the output from CPU.

The dial rotation pulse is charged in D1016, R1022 and C1010, and the average

voltage according to the speed is obtained. When the dial rotation speed is fast,

the frequency step per pulse is four times that at normal speed.

When SW1001 is pressed, Q1001 is turned ON, then the contact of RL602 in PA

unit is turned ON to supply the voltage of 13.8V to the front unit. Once the CPU

starts operation, the output from PCONT of CPU turns Q1006 ON to hold ON the

relay of RL602.

When SW1001 is kept pressing while the power is ON, the signal is detected in

PSDET, and the 01006 is turned OFF to cut OFF the power supply.

b. Pow er Supply

c. Dimmer Circuit

d. LCD

e. Others

1C1007 is the regulated power supply of 5V which has the output for CPU reset.

IC1006 is the regulated power supply of 8V which generates the required voltage

for IF shift and volume control.

When the power supply is cut OFF, the output of regulated power supply of 8V is

increased first, and it is detected in D1018 and IC1002:D, then sent to CPU. In

CPU the data is stored in the EEPROM of IC1005 before the output of regulated

power supply of 5V is decreased and the unit is reset. D1019 and C1002 are used

to hold the output voltage of 5V by keeping the input voltage of 5V regulated power

supply as long as possible.

The regulated power supply ol about 10.5V consists of Q1003, Q1004 and Q1005.

Q1003 supplies about 10.5V when the DIMM output from CPU is 5V.

In CPU unit, DIMM is the pulse output, and it switches ON/OFF of the output of

about 10.5V.

At full lighting the output from CPU is fixed to 5V. In ’'LP4" mode the duty is 80%

and in "LP 3 " mode the duty is 60%. In this way the brightness is changed by the

duty in Q1003.

Q1003 is supplied the current by turning ON/OFF. At the maximum the brightness

is the lightest, and the duty is decreased according to the dimmer, then the power

dissipation is decreased. The dimmer can be operated by the small transistor.

The maximum brightness is 10.5V, and it is set to under the regulation voltage

(5.3V x 2) to prolong the life of the lamp. The rush current when the lamp is turned

ON is in pulse mode to decrease the load on the lamp.

The indication such as frequency that is required the speed is performed by the

CPU itself, and the other indications are performed by the LCD driver of 1C1009.

The LCD indication employs the frame frequency of about 128Hz, 1/2 DUTY and

1/2 bias.

X1001 is the ceramic resonator of 8MHz selected not to enter the amateur band in

the harmonics relations.

When the power is ON, the voltage is supplied from Y2 and Y3, to detect whether

Page 17

4) PLL Unit

Summary

it is connected to the outputs DB0-DB6 or not, then the destination is determined.

The currents in YD and Y1, and between DB~DB6 are scanned to detect which

switch on the front panel is pressed.

The both sides of RIT VR are applied 5V, and the location of VR is detected by the

voltage of A/D input terminal.

In the Receiving frequency monitor Q1019 is turned ON by the MONI output from

CPU, the squelch setting voltage programmed by turning the knob on the front

panel is decreased forcedly. Then the squelch is open forcedly without any

relation with VR position.

The output from the main unit (RTXC) lights the LED according to the change of

the ALC voltage. The output cannot be supplied as it is, so it is changed to ON/

OFF signal in Q1009.

Q1011 is the squelch output from the main unit, and it lights RX LED.

The followings are performed in PLL unit:

The generation of carrier signal

The generation of the first and second local oscillating signal

The generation of sidelone CTCSS

Adding the FM modulation

Making the power supply of 5V

Details

(1) There are 3 kinds of power supply as follows:

The voltage of 13V passed through the switch

The voltage of 8V made in the MAIN unit

The voltage of 5V made in the PLL unit

Power supply depending on the MODE comes from the main unit.

(2) First the reference signal of 30MHz is generated in X701 and Q701 according

to the constant of TC701 and L702.

(3) Secondly the signal of 9.420MHz +/- 1.5kHz is generated by the voltage of

D706 in X702, 0721 and Q722.

(4) Thirdly the signal of 9.875MHz +/- 1.5kHz is generated according to the

constant of TC702-TC704, C807, C809, C810, C811 and C812 in Q725 and

Q724.

(5) The frequency of 9.875MHz is changed according to the MODE, transmission/

reception.

[Transmission/Reception of LSB]

CN701 Pin21 (LSB) is applied the voltage of 8V and the signal is passed through

D714, then results in the frequency of 9.8735MHz according to the constant of

TC702 and C812. Also (LSB) 8V is passed through D718, and the voltage is

applied to Q723 to emit the carrier signal.

[Transmission/Reception of USB]

CN701 Pin26 (USB) is applied the voltage of 8V and the signal is passed through

D711, then results in the frequency of 9.8765MHz according to the constant of

TC704 and C807. Also (LSB) 8V is passed through D717, and the voltage is

Page 18

applied to 0723 to emit the carrier signal.

[Reception of AM/FM/TUNE]

CN701 Pin20 (FM) or CN7Q1 Pin22 (AT) is added the voltage of 8V and in the FM

mode the signal is passed through D708, then results in the frequency of

9.875MHz according to the constant of TC703 and C811. 0723 has no voltage,

and carrier signal is never emitted.

[Transmission of AM/TUNE]

CN701 Pin22(AT) is applied 8V and results in the frequency of 9.875MHz accord

ing to the constant of TC703, C811.

The voltage of 8V from CN701 Pin23 (T8V) is passed through D718 to add the

voltage to Q723, then the carrier signal is emitted.

[Transmission of FM]

CN701 Pin20 (FM) and CN701 Pin23 (T8V) are added the voltage of 8V , the

Q729 and Q733 are turned ON, 8V voltage of CN701 Pin20 (FM) is passed

through D708, 0733 and D714, then results in the frequency of 9.8735MHz

according to the constant of TC702 and C812. Here FM is passed through AT and

R814 to turn ON C811, however, as Q733 is also turned ON, 0727 is turned ON

and C811 is shorted.

The voltage of 8V from CN701 Pin23 (T8V) is passed through D718, and led to

Q723 to emit the carrier signal.

The voltage of 8V from Q733 turns ON the analogue switch of IC715.

The modulation signal is passed through R798, IC715, R796 and C801, and it is

FM-modulated in VC02.

[The Transmission of CWU/CWL]

CN701 Pin24 (CWU) or CN701 Pin25 (CWL} is supplied the voltage of 8V, then it

is passed through D716, D732, Q716 (because Q729 is ON) and R814, then

results in the frequency of 9.875MHz according to the constant of TC703 and

C811.

Although here CWU tries to turn C810 ON or CWL tries to turn C809 ON, it can not

be done through 0715 because Q729 is also turned ON.

[The Reception of CWU]

CN701 Pin24 (CWU) is supplied the voltage of 8V, passed through D712, then

resulting in the frequency of 9.8758MHz of frequency according to the constant of

TC703 and C810. Also the voltage of 8V from CN701 Pin24 (CWL) is passed

through D716 and D717 to the Q723, then the carrier signal is emitted.

[The Reception of CWL]

CN701 Pin25 (CWU) is supplied the voltage of 8V, passed through D712, then

resulting in the frequency of 9.8742MHz of frequency according to the constant of

TC7G3 and C809. Also the voltage of 8V from CN701 Pin25 (CWL) is passed

through D716 and D717 to the Q723, then the carrier signal is emitted.

(6) The frequency of 9.42MHz can be changed only while receiving by the IF shift

volume on the front panel.

The voltage supplied to CN701 Pin14 (SHV) is changed by the IF shift volume, and

Page 19

the capacitance of D706 is also changed, then 9.42MHz is changed. The center

frequency of the IF shift volume is determined by VR702.

While transmitting 0715 is turned ON by T8V to eliminate the influence by SHV

and VR 701, then the frequency is decided only by VR701.

In USB CN701 Pin26 (USB) and CN701 Pin 15 (TONS) are supplied the voltage of

8V. As in UT mode TONS becomes the sink, 0735 is turned OFF and USB is

supplied 0V , then Q730 is turned ON and a terminal of R767 is connected to the

ground to decrease the voltage of D706, beside the frequency of 9.42MHz is

decreased about 300Hz less while receiving and about 100Hz less while transmit

ting than the vaiue in USB mode.

In the same manner, in LSB mode the voltages of CN701 Pin21 (LSB) and CN701

Pin 15 (TONS) are 8V. As in LT mode TONS becomes the sink, Q735 is turned

OFF and D729 is supplied the voltage by R767. Then voltage of D706 is in

creased. Beside the frequency of 9.42Hz is increased about 300Hz more while

receiving and about 100Hz more while transmitting than the vaiue in LSB mode.

(7) The Emission of 455kHz Carrier Signal

The above-mentioned 9.875MHz signal is input to Mixer IC712 Pin6, and 9.42MHz

signal is input to IC712 PinB. The difference frequency of 455kHz is output from

IC712 Pin3 and sent to the MAIN unit from J701 after amplified in Q723. The

Output level is approximately -5dB

(Frequency Relations depending on the Mode)

USB{TX RX)

LSB(TX RX) FM(TX)

CWU CWL AM TUNE (TX)

CWU(RX)

CWL(RX)

UT(RX)

LT(RX)

UT(TX)

LTfTX)

AM FM (RX) does not output

{”*): While receiving IF Shift Operation (+/-1.5kHz)

(*): IF Shift Operation (+/-1.5kHz)

9.8765MHz-9.42MHz (**) =

9.8735MHz - 9.42MHz (" ) =

9.8750MHz-9.42MHz

9.8758MHz - 9.42MHz (*) =

9.8742MHz-9.42MHz O =

9.8765MHz-9.4197MHz ( >

9.8735MHz - 9.4203MHz (') =

9.8765MHz-9.4199MHz =

9.8735MHz-9.4201MHz ■

456.5kHz (•*)

453.5kHz D

455.0kHz O

453.5kHz (*)

453.5kHz (*)

456.8kHz (■)

: 453.2kHz (*)

456.6kHz

: 453.4kHz

(8) The Second Loca! Oscillating Signal

In VC02 unit, after the frequency of 71.295MHz is oscillated in 0941 and amplified

in 0949, Q944 and Q945, the signal of approximately 3dB is supplied to MAIN unit

through J702 as the second local oscillating signal.

The signal for PLL loop is supplied from Q942 to PLL unit.

The signal of 71.295MHz is fed to Mixer IC711 Pin7 and the signal of 9.42MHz is

fed to Pin3, so that the deference frequency of 61.875MHi output from Pin6 only is

picked up by Q711, L712 and L711, and fed to PLL IC707, then locked at

61.675MHz.

Therefore, by rotating the IF shift volume, 9.42MHz, and also 71.295MHz are

changed.

The frequency of 30MHz is fed to IC707 through Pin1, and it is divided to get the

following frequency as the reference frequency, and also the frequency of

Page 20

61.875MHz is divided to get the reference frequency, then these two frequencies

are compared.

The reference frequency changes according to the CW sidetone frequency.

When the sidetone frequency is 650Hz, the reference frequency is 64.655kHz.

When the sidetone frequency is 750Hz, the reference frequency is 75.000kHz.

When the sidetone frequency is 850Hz, the reference frequency is 85.227kHz.

(9) The First Local Oscillating Signal

In the HF mode, the frequency oscillated in VC03 is amplified in Q710 and Q714,

and passed through the switching diode D725 and D726. then band-pass filter and

RL701. The signal of approximately 3dB is led to the MAIN unit from J703.

3 VCO's are built in VC03, and it is oscillated under following frequency condi

tions:

150kHz~under 10.5MHz:

The VCO is oscillated within 71.90-82.25MHz by D961.TC961 andQ961.

10.5kHz~under 21.5MHz:

The VCO is oscillated within 82.25~93.25MHz by D963, TC962 and Q963.

21.5kHz~under 30.0MHz:

The VCO is oscillated within 93.25-101,75MHz by D965, TC963 and

0965.

These 3 VOC’s are selected by the serial data of DAT2, CK2 and ENB from CPU.

8 signals from IC716 are reduced up to 3 signals, then VCO is selected by the

switches of VC03, 0962, 0964 and Q966.

When the frequency is 50MHz, in VC03 the oscillated frequency within 76.75-

80.75MHz by D961, TC961 and 0961 are synthesized with the frequency of

45MHz by the DBM (Double Balanced Mixer) in L729, L730 and D730, then the

frequency within 121.75-125.75MHz is generated. It is passed through RL701 by

the band-pass filters of L732, L733. L734 and L735 and Amplifier of 0731 and

0716, then the signal of approximately 3dB is output to J703.

The frequency of 45MHz is generated as follows: The reference signal of 30MHz

is amplified in 0719 and fed to IC701 Pin3, then one half of the signal is supplied

from Pin5. 3 times frequency of the signal only is passed through the filter L720,

L721 and L722, and fed to the center tap of L729, then led to DBM.

The frequency loop of VC03 is locked as follows: VC03 oscillating frequency is

passed through 0712 and input to the mixer 1C709 Pin6, also the signal of 70.65-

70.75MHz (25Hz step) is fed to 1C709 Pin8. Then the signal of 1.1 -31.1 MHz

passed through the amplifier Q713 and led to PLL 1C702 Pin8 as the difference

signal.

This frequency is locked by the following procedure.

1.1 MHz is added to the digit number of 100kHz or more of the operation fre

quency, and divided to obtain 100kHz. Then the frequency is locked after compar

ing with the reference frequency 100kHz. See the examples as shown below.

Operation Frequency: 1MHz

—> PLL The frequency fed to IC702 Pin8: 2.1MHz

Page 21

Operation Frequency: 29MHz

—> PLL The frequency led to IC702 Pin8:

Therefore, as the reference frequency of IC702, the reference frequency of 30MHz

is divided up to 100kHz inside the unit.

In IC702, the operation frequency of 100kHz or more only is controlled.

In 50MHz band, CN701 Pin1 (50M) is sink, Q732 collector is supplied the voltage

of 8V. The power supply of 0731, 0716 is turned ON. 0709 and D730 are turned

ON. 0709, RL701, D724 and D7'24 are turned ON, then D730 is ON and Q724 is

OFF.

The deviation while transmitting is 5kHz/DEV, and 2.5kHz/DEV while HF/FM

transmitting.

In the HF mode, Q717 is ON, and D725 and D726 are turned ON, then D735 is

ON. IC710 Pin4 is supplied about 0.7V so that the operation of IC710 is stopped.

When the unlock signal is emitted from every Pin7 in PLL IC IC702, IC703 and

IC707, the voltage of 8V is supplied from the collector in 0728, and 0718 is turned

ON so that 0714 is turned OFF, then the level of J703 is decreased about 30dB or

more.

(10) 25Hz Step 70.65-70.75MHz

In VC01 Unit, to generate 25Hz step of the first local oscillating, 0931 is used to

oscillate the frequency of 155MHz~175MHz, the signal is passed through Q932

and divided by 20 in IC704, and supplied through Q933. Then the signal is divided

by 10 in IC705, and the frequency of 775~875kHz (25Hz step) is fed to the mixer

IC701, Therefore, the operation frequency of 100kHz digit or below can be

operated in 25Hz step.

Also the frequency is input to PLL unit IC703 Pin8 through Q931 for the PLL loop.

PLL IC divides the frequency of 155.000-174.995MHz to get 5kHz, and it is

compared with the reference frequency of 5kHz to make the loop.

3 0 . 1MH z

Indication of the operation frequency Oscillating frequency

of 100kHz digit or below

.0000(00)

.5000(00)

’ The number in ( ) is the frequency of no indication.

The reference frequency of 30MHz is divided to get 5kHz (25Hz x 200), and used

as the reference frequency in IC703. Because the signal of 9.875MHz is input to

IC701 Pin8, the sum of the frequencies, 10.65-10.75MHz is supplied from IC703

Pin2, and passed through the ceramic filter of 10.7MHz, then fed to IC706 Pin6.

As the double harmonics of reference frequency of 30MHz are generated in Q708,

L710 and L709, and they are fed to 1C7D6 Pin8. The sum of the frequency of

70.65-70.75MHz is supplied from IC703 Pin3. passed through the band-pass filter

of L706, L707 and L708, and fed to IC709 Pin

pari of the loop of the first local oscillating signal.

.9999(75)

8. Then the signal is ncluded in a

155.000MHz

165.000MHz

174.995MHz

Page 22

(11) CTCSS tor only FM transmission

In Tone unit, T type controls the frequency with the DIP Switch SW901 Pin3 - 8,

then it is oscillated between 67-251 Hz, amplified in Q901 and passed through

CN704-1, then led to the MAIN unit from CN701 Pin16.

In this circuit, ON operation is performed when TONS is the sink and IC901 Pin4

is OV, and FM is supplied 8V and tone unit power supply is ON.

The tone level is controlled with the DIP switch SW901 Pin1 and Pin2 to adjust the

level.

(12) FM TX deviation

Default is ± 2.5kHz deviation on 29MHz and ±5kHz deviation on 51 MHz.

a)Short-circuiting collector and emitter of Q734 will make both bands ± 2.5kHz.

b) Short-circuiting the base and emitter of Q734 (and collector and emitter

open) will make both bands ± 5kHz .

Short-circuiting both(a) and (b) will result in the same effect as (a).

Page 23

5) Terminal function of CPU

No. U*e1 ÜM2 U »*3

2

3

4 ; X2

s

6 Vss GNO

7

8

9

10

IR04

P20

11

12 P21

13 P22 PSDET

,4

P23 TKEY

P24

IS

16 P2S MCK

P26 MDAT

P27

19

P30

20 P3i

25

P32

22 P33

P34

23

24

P35

2b P36

P3?

?6

27

28

29 V2

30

31

32

33 PA2 COM3 COM4

34

35

36 P50

37

38 P52

39 P53

40

41

42 P56 SEG7

43

44

45

46 P€2

47

48

49 P65 SEG14

50 P66 SEG15

51 P67 j SEG18 LCOATA

COM4

PA3

PA1 COM2

PAO COM1

SEG1 WKP0 DB0

P51 SEG2

SEG3 WKP2 OB?

SEG4 WKP3 DB3 1

PS4

SEGS

P55

SEG6

P57

SEG6 WKP7

P60

SEG9

P€1

SEG10 Y1 o

SEG1

P63 SEG12 Y3

P64

SEG13 GND 0

Pin Nam*

GNO

AVss

GNO

XTAL, LOSC

XTAL

X1

XTAL

OSC1

OSC2 XTAL

/RST

/RES

SV?

MDO

ADTRG DCK

PCONT POWER ON

UO

UNLK PLL UNLOCK

EXT1N

SCK1

CK1 SER1AL1 CK o

DAT1 SERIAL 1 DATA

Sn

ENH HPLL ENABLE o

SOI

SCK2 ENL

CK2 SERIAL2 CK

SI2

DAT2 SERIAL2 DATA

S02

ENA SERIAL SELECT

STR8

ENB SERIAL SELECT

CS

Vss GNO

V3

V1

Vcc 5V

COM4

COM3

COM3 o LCD COMMON

WKP1 OB1 1

WKP4

0B4 1

WKP5 DBS

WKP6

DB6 1

Y0 o Panel SW (or ON detection

Y2 o

LCDEN 0

LCDCK 0

Remarks

DIAL CLOCK

POWER DfTT

TUNE KEY

EEPROM CK

EEPROM DATA

EXT IN

LPLL ENABLE

I/O

I

I

‘

O

'

’

1

0

I/O

'

o

o

0

o

0 MODE. BPF, etc. data enatxe select »on

o

0 LCD COMMON

o

o LCD COMMON

1

I

1

0

o

0

Description

Mam dial rolaton detection and pulse

number

Power control output

Condition Oetecuon «when power switch is

turned ON.

Detection of worVing external antenna

tuner

PLL unkxx detection

Ctock tor data trans>Tiissio<Vrec©p»ion to

EEPROM

Data Transmission/Reception to

EEPROM

External EEPROM transmission

eoce£*ance

HPL LPLdata tranjimisson ckx*

HPL. LPLdata transmission

HPL data transmission enable

IPL data transmission enable

MODE, BPF, etc. transmits«*' clock

MODE. BPF. etc. data transmission

MODE, BPF. etc. data enable selection

LCD COMMON

SW. initial setting dttection

SW. initial setting defection

SW, initial setting detection

SW, initial setting diitection

SW. initial setting diitection Detection

SW. initial setting detection Detection

SW, initial setting defection

Pane1 SW for ON detection

Output tor initial condrtton settng

detection

Output tor initial condition setting

detection

LCO driver enable

LCD driver d oc*

LCD dnver data

Rise edge

Oeteclon

Power OFF

Dunng power

OFF

At work

Unloc*

EEPROM

L

H

Power ON

During power QN

Waiting

Lock

Acceptance

Enable

Enable

Enatfe i

Enable 2

Detection

Detection

Detection

Detection

Detecvon

Detection

At detecting

At detecting

Page 24

No. Um 1

5?

53 P71

54

55 P73

56 P7-1

57 P7b

58

59 P/7

60 P0O

61 P01

62

63 P83

64

05

fi6 PB6

67 P87

GB

69

70

n

7?

73

74

75

76

77

78 P11

79

eo

61 P U

82 P15

83

fU p i;

8b

86 P i 1

8?

88 P43

89

90 PBO

91

9?

93

94

95

96 PB6

97

98 PCO

99

100 PC2 AN10

1

UM2 U»e3 Pin Name

SEG17 SEG17

P70

SEG10 SEG16

P7 7

SEG19

SEG20 SEG20

SEG?1

SEG22 SEG?? 0

P76

SEG73

SEG2d SEG2d

SEG2S SEG25

SEG?6

P62 SEG27 SEG? 1

SEG20

P8-» SEG29

P65

SEG30 SEG30

SEG31

SEG32

P90

SEG33 SEG33

SEÜ34

P91

P9?

SEG35 SEG35

P93

SEG36 SEG36

P94 SEG3/ M

P95 SEG38 DO SEG38

P96

SEG39 CL? SEG39

P97

SEG40

P10 TMOW MONI

P1? TMOFH BEEP

P13

IRQi

P16

IRQ?

IR03 TMIF SUBB 1

P40

P42

moo POWDN

A NO DOl 1

PBl AN1

PB2

AN2 D03

PB3 AN3 004 1

PB-t Af-M

PBS AN5

AN6 DO

PB7 AM7

AN8

PC' AN9

ANU

PC3

SEG19 0

SEG21

SEG23

SEG26

SEG26

SEG29 o

SEG31

SEG32

SEG34

SEG37 o

SEG40

CL1

5V

Vcc

UT

TMOFL

TMIG SOS

PWM DIMM

TMIÜ TXS 1

SUBA

TMlC

ORST COUNT RESET

SCK3

RXD GND

TXD GND 1

5V

AVcc

DO? 1

00 5

00 6 i

/DO

DSD ET A^D

RIT

U/D A/D

SRF

Remarks

DIMMER 0

POWER DOWN 1

1/0

0

0

O

0

0

0

0

0 Output to LCD Segment

0 Output tr> LCD Segrnem

0 Output to L CD Segment

Description L

Outpui io LCD Sequent

Output 1o LCD Segment

Outpui to LCO Segmenl

Outpui to LCD Segment

Output lo LCD Segment

Output to LCD Segment

Output to LCD Segment

Output lo LCD Segment

Output to LCD Segment

Output to LCD Segment

o Output to LCD Segment

0 Outpui to LCD Seomen!

0 Output to LCD Segment

0

Output to LCD Seomeni

0 Ouiput to LCD Seamcni

0

Outpu t to LCD Segment

0 Output io LCD Segment

Output lo LCD Segment

0 Outout lo LCD Seqment

0

Output io LCD Seomen;

0

Output to LCO Segment

0

Open the squelch forcedly (monitor)

The co nma nd io put out the light

o

forcedly and flashing lo LCD driver

0

Beep sound outpui

Soueicn open/ciosc condition aeiect>on

'

LCD dimmer control

Transmission condition detection

1

MF dial rotation detection

MF d'ai rotation detection

Omi puisc count reset

1

Power OFF detection Power OFF

Dial clock 1/?

Dial clock t/d

1

Dial d or* 1/8

Dial dock 1/16

1

Dial clock 1/3?

Dial clock 1/6*1

1

Dial up rotation

1

Dial down rotation Down

Dial speed öetecton

A/D

RIT VR position detection 0-5V

Mio UPiDOWN oetect'on

A/D

S & RF Meier voltage input

Put out the light

forcedly

Puisc ouiput

Soueich close

Duly control o<

puise output

Transmission

Dunng counting

The voltage

according to the

speed ot rotation.

2-3V down 0-2V up

0-5V

H

Squelch open

torcsdiy

During lighting

Soueich open

Reception

Reset

Power OK

UO

Page 25

SEMICONDUCTOR DATA

1) S7116A (XA0052)

Tone Generator

B lo c k D ia g r a m

P1 P2 P3 P4 P5 P6

Parameter Symbol

Supply voltage

Supply current

Vdd

Iddo VDD=5.0V, CE1=Vdd, CE2=Vss, CG=Co=10pF

Condition Min Typ

3.0

-

Stand by current lODS VDD=5.0V, input: open, Rl=50ki2

Tone output level

Freq.

57.0

71.9

74.4

77.0

79.7

82.5

85. 4 1

80.5

91.5

9-1.8

97. 4 1

100.0

103.5 1 1

107.2

110.9 1000

n i . 8

118.8 1700

123.0

127.3 1800

131.8 1300 1

136.5 2000 1

141.3 2200 1

146.2

151 4

156 7

162 2

167.9

173 8

179.9

VOT

P1 P2 P3

1 186.2

1

i

1

1 '

1

1

1

1

1

1

P4

1

1

1 233.6

1

1

1

1

1 1

1

1

1

1

1

VDD=5.0V, Rl-50kQ

P5 P6

240 340

P1

Freq

192.8 1

203.5 1

210.7 1

218.1 1 1

225.7

241.8

250.3

500

600

700 1 1 1

800 1

900 1

1600 1 1 1

1750 1

2975 1

2550

2295

2125

1275

1445

P2 P3

1

1 1

1

1

1

1 1

1

1 1

1

1

1 1

P4

1 1 1

1 1

*

1

1 1

1 1

1

1

- 10 V

0.4

20 60

P5 P6

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

Max

1.0 mA

440

mV rms

Unit

ma

Page 26

2) MC3357 (XA0063)

Low Power FM IF

Vcc=6V

F=10.7MHz

Icc 3mA

Limit 5^-V -3dB

Vo 350mV Dev=+/-3KHz

3) M5218FP (XA0068)

Dual Low Noise

Operational Amplifiers

Output 1 1 C

Inverting Input 1 2 C

Non Inverting Input 1 3 I

Crystal Osc. C= 1 16

Crystal OSC. cz:

M«ef Output

Vcc

Limiter Input

Decoupling

Limrler Output CZ

Quad Input CZ

2 15

3

c z

c z 4

CZ

5

CZ

6

7

8

W

if

ZZ3

RF Inpul

ZZD

GND

14

ZD Audio Mute

MC3357

ZD

13

Scan Control

12 ZD

Sooettft input

ZD Rlter Output

11

ZD

10

FHIer Input

Demodulate*

9

Output

] a Power Supply Plus

] 7 Output 2

]6 Inverting Input 2

4) NJM78L08UA (XA0075)

8V Voltage Regulator

Power Supply Minus 4 I

U U U

Output Common Input

D

5 Non Inverting Input 2

Page 27

5) p.PC1241H (XA0079)

Audio Power Amplifiers

T e s t C irc u it

6) MC7808CT (XA0082)

8V Voltage Regulator

7) p.PD6345GS (XA0114)

8bit Serial in Parallel Out Driver

Inptrt i

----------

j

fînmmon I [

1 xrtpiit 1 1

O

¡J.PC1241H

1 2 3 4 5 6 7

n

CD O O D.

u l z z 5. 2

O O 3 «

■>4

___

00

o

O o

O

I

TT

Pin Marne Description

No.

1 GND GND terminal

EN Enable terminal

2

3 LAT Latch terminal

4

SO Serial data output terminal

Da\a output \ermina'

Ô8-ÔÎ

5-12

13

14

15 RES

16 Voo

Serial data input terminal

SIN

SCK Serial dock input terminal

Reset input terminal

Power supply terminal

~ u ~

D Z

o> m

CO Ô

CJ1

C D

l Vdd

16

15

ZZ] RES

14

ZD SCK

13 ZD SIN

12 ZZ 01

ZZ 02

11

10 zzi 03

g ZD 04

Page 28

8) TC4S66F (XA0115)

Bilateral Switch

IN/OUT [TJ

OUT/IN [H

VSS |_3_L

>

--

J5] VDD

]£ ) CONT

9) NJM2904M (XA0224)

Dual Operational Amplifiers

B lo c k D ia g r a m

10) BU4052BF (XA0236)

Analog Multiplexer/Demultiplexer

L o g ic D ia g r a m

Vdd(16) o-

INHIB1T { 6 ) o— le v e l

A (10) o— CONVE

RTER

B{9) H

Vss (8) o~

Vee (7) o—

Xo (12) o-

Xt (14) o—

X2{15) cv-

X3 <1 1) O-

Y0 (1) o-

Yi(5)o-

V? (2)

V3(4) o-

(13) X

{3)Y

y° [T

Y2 [T

COMMON Y [T

Y3 [ T

Y1 [T

INHIBIT j T

vee [T

vs s [T

g

b □ □

j :

______

C9

e l

t

ie]voo

Ü]5(2

g«,

13) X COMMOM

12] XQ

ElX3

To] A

T )b

T r u th T a b le

INHIBIT A

L

L H

L L

L

H

X: Don’t Care

B ON SWITCH

L

H

X X NONE

L XO YO

L X1 Y1

H X2 Y2

H X3 Y3

Page 29

11) BU4094BF (XA0246)

8-Stage Shift Register

T ru th T a b le

Output

Clock

— L _

_ J “

- J T -

Strobe Data

enable

X X Z Z 07

L

L X

H I

H H L

H H

H

X X

Parallel outputs

Q1

X Z z

No Chg. No Chg.

X

L

H

H

No Chg.

No Chg.

On

No Chg.

Qn-1 07

Qn-1 07

No Chg. Os

Serial outputs

Qs Q's

No Chg.

Qs

Q7

No Chg.

No Chg.

No Chg.

Z*High Impedance

X=Don*t Care

B lo c k D i a g ra m

PARALLEL

OUTPUTS

12) MC12019D (XA0292)

Two-Modulus Prescaler

B lo c k D i a g ra m

Control

tnput 1

STROBE d 1

SERIAL

Q's-v SERIAL

Os/OUTPUT

IN

CLOCK

d

d

01 d

02

d

Q3 d 6

04

d

Vss d

Characteristics

Toggle Irequency fmax

{Sine wave input)

Supply current

Control input High (1/20) VIH

Control input Low (1/21)

Output voltage swing

Input voltage sensitivity

PLL response time

Symbol

tmin

Icc

VIL

Vout 600

Vin

tPLL

16 d ]

2

3

4

5 12d

7

U3

C

4^

O

<£>

CD

“T1

15 d

14 d

13 d

11 d

10d

8 9 d

Min.

Typ Max Unit

225

- -

-

2.0

- -

- 0.8

200

-

Vdd

Output

Enable

05

06

07

Q8

Q's

Os

MHz

20

mA

7.5

V

V

1200 mVpp

mVpp

800

tout-

ns

70

Page 30

13) MC74HC404QF (XA0293)

12-Stage Binary Ripple Counter

14) MC74HC390F (XA0294)

Dual 4-Siage Binary Ripple Counter 1/2 and 1/5 Sections

Q

c

>C o

D R 0

3 =

-C o

D „ O

_ r

r-v 3. «3

-[>

----

OA

— —08

. 6.1°

--<£>-—Oc

Clock Aa r:_. 1 16 ZZ Vcc

Reset a

QAa z z

Clock Ba r" 4

OBa

QCa

ODa

GND

tz:

2 15Z Z Clock Ab

2

14

Z D

13 Z D QAb

12 Z D Clock Bb

11 Z D

10Z D

9 Z D QDb

z z

z z

z z 7

IZZ

3

o

“n I

m

o

5

Ca>

CO

o

6

T 1

8

Reset b

QBb

QCb

5, 11 ^

6. 10

7.9

T ru th T a b l e

Reset

1/2 and 1/5

Page 31

15) MC14024BF (XA0295)

7-Stage Binary Counter

T ru th T a b le

L

Output State

No Charge

Advance to oes t a ge

Clock Clear

Don't care H All Outpul-'L"

_ r ~

~ L _

16) MC14071BF (XA0296)

Quad 2-Input OR Gate

T ru th T a b le

; = £ > •

: = D -

Clock

Reset CZ 2

Q7 d

Q6

c z

Q5

c z 5

Q4

c z

Vss rzz7

in 1A

In 2A

Out A

Out B

In 1B

In 2B

Vss

W

14 ZD

Vdd

13 ZD

11

10ZD

9 ZD

8 ZD

ZD

ZD

NC

01

02

NC

03

NC

ZD In 2D

ZD in 1D

ZZ Out D

ZD Out C

s

3

o 12

4

o

ISD

4^

CD

n

6

w

1 14 ZD V dd

2 13

2

3 O 12

-X

4 O 11

5 03 10

■n

6 9 ZD In 2C

7 8 ZD In 1C

Page 32

CD

17) MB87086A (XA0297)

PLL Frequency Synthesizer

No. Pin Name

1 OSC*n 1

OSCout

2

3 fv o

4

Vdd Power supply

s Dop 0

6 Vss

7 LD o

fin

8

Clock

10

Data 1

L£

11

1? Do*

13

*

14

NC

bv

15

bR

16

Crystal oscillator

{> -

I/O

Crystal connection terminal

O Crystal connection terrnma1

Comparator drvxJer output terminal

1 Comparator divider input termina1

1

0

o

o

o

Description

Phase comparator input monitor terminal

Passive LPF connection terminal

tr>V Drive mode. Dop»'H"

fr-tv: High impedance

fr<tv: Sink moOe, Dop-'L"

GND terminal

Phase detect ex output terminal

locW H ', Uniock.negative pulse

Senal clock input terminal

Senal data input lerminai

Load enable inpcrt tormina I

Aclive LPF connection terminal

tr>fv Dnve mode, D o* -'L ‘

fr—tv: High impedance

fr<tv Sink mode. Do»-’ H"

Phase comparator input monitor terminal

Re’erence divider oirtput terminal

No connection

Orfterential LPF connection terminal

f*>fv. b R»’L’

bV-‘ H', eR*"H"

tr<tv: oV-"L\ ® R»“H"

= D -

T f t t t t t t t t t t t t t t

16bit Latch I

i i t t i t t t t t i i t t i t .

Reference Divider

O S C o u t LZ Z

H >

©-&>— i-* it,

Amp

T T T ft f tt t tt

—+j lObit uaich j

i l l f f i L .

*| 10pt! Programmable Counter }-

Charge

Charqe

Pump

-►—( F ) Dcp

Doa

— & h

Page 33

18) MB87014A (XA0298)

PLL Frequency Synthesizer

Pin Name I/O Descnption

NO

OSC'N

1

OSCout o

2

N

3

4 Vdd

Dop

5

Vss

ID 0

fin Prescaler input terminal

Clock Senal clock input terminal

9

10 Data Senal data input terminal

LE

12 Do*

13 0

14

NC No connection

15 0V

0R 0

16

1

o

0

1

o

0 Differentia! LPF connection terminal

Crystal connection terminal

Crystal connection terminal

Phase comparator input monitor terminal

Com parator divider output terminal

Power supply

Passive LPF connection terminal

fr>fv: Dnve mode. Dop«'H'"

fr-fv : High impedance

!r<tv Sink mode. Oop-"L"

GND terminal

Phase d etecto r output terminal

Lock» "HUniock «nega tive pulse

Load enable input terminal

Active LPF connection terminal

1r>fv; Sink mode. Doa- 'L ”

fr»tv High impedance

fr<tv. Dnve mode.

Phase COmparalOr input monitor terminal

Reference divid er output terminal

lr>fv. e V- 'H ". aR«"L"

tr-tv e V.-H" , b R.-H ”

tr<tv. bFU'H"

OSCoutCZZ

1

2

3