Page 1

DR-620

Service Manual

CONTENTS

SPECIFICATIONS

1) GENERAL ................................................................ 2

2) TRANSMITTER ........................................................ 2

3) RECEIVER ............................................................... 3

CIRCUIT DESCRIPTION

1) VHF Reception ......................................................... 4

2) UHF Reception ......................................................... 5

3) FM Reception ........................................................... 5

4) V/V (VHF-VHF) Dual Reception................................ 6

5) U/U (UHF-UHF) Dual Reception ............................... 6

6) VHF Squelch Control ................................................ 6

7) UHF Squelch Control................................................ 6

8) Transmit Signal Path ................................................. 7

9) VHF Transmit Signal Path ......................................... 7

10) UHF Transmit Signal Path ......................................... 7

11) VHF Tx APC Circuit .................................................. 7

12) UHF Tx APC Circuit .................................................. 8

13) VHF PTT Circuit........................................................ 8

14) UHF PTT Circuit ....................................................... 8

15) VHF PLL................................................................... 8

16) UHF PLL................................................................... 9

17) Power-on Circuit ....................................................... 9

SEMICONDUCTOR DATA

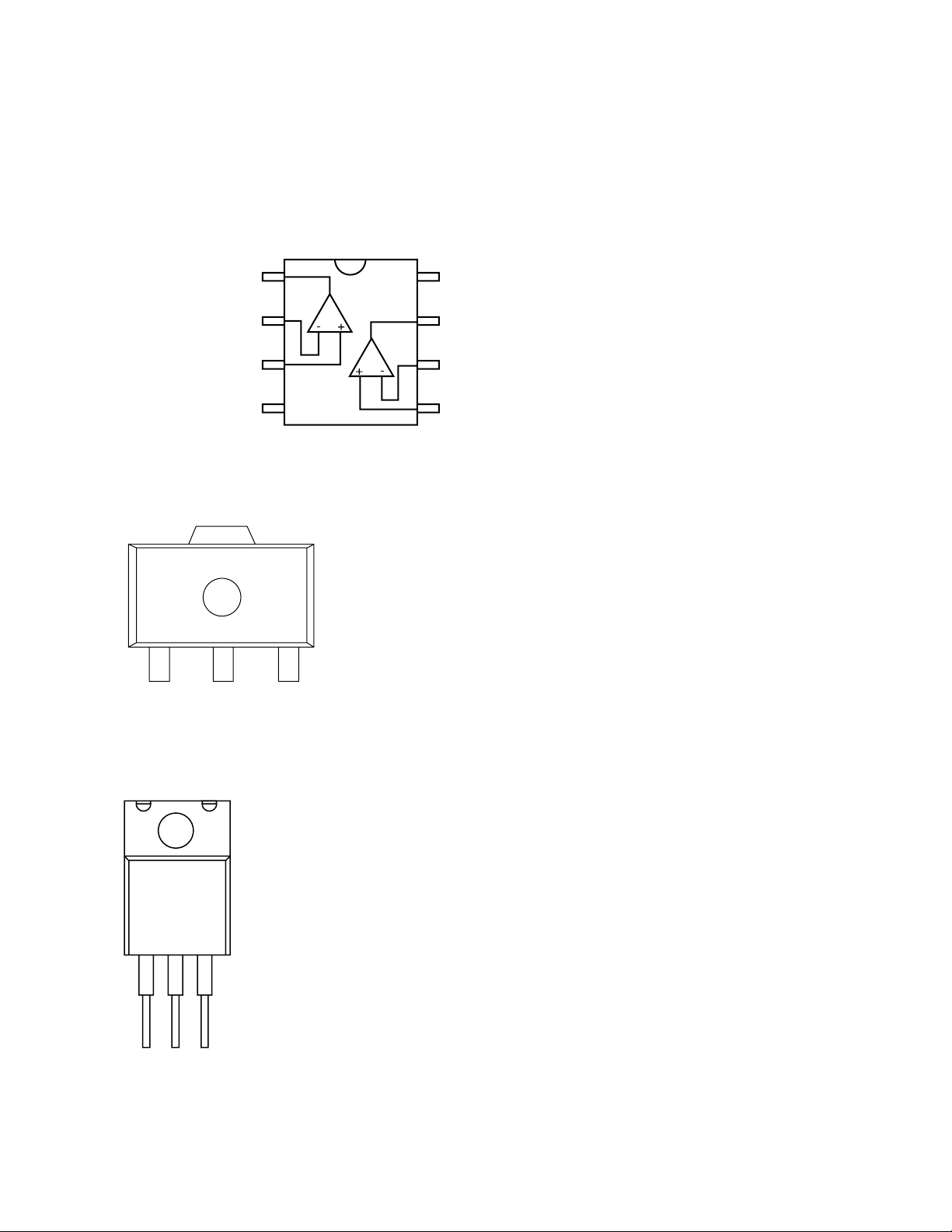

1) M5218FP (XA0068) ................................................ 10

2) NJM78L05UA (XA0098) ......................................... 10

3) NJM7808FA (XA0102) ............................................ 10

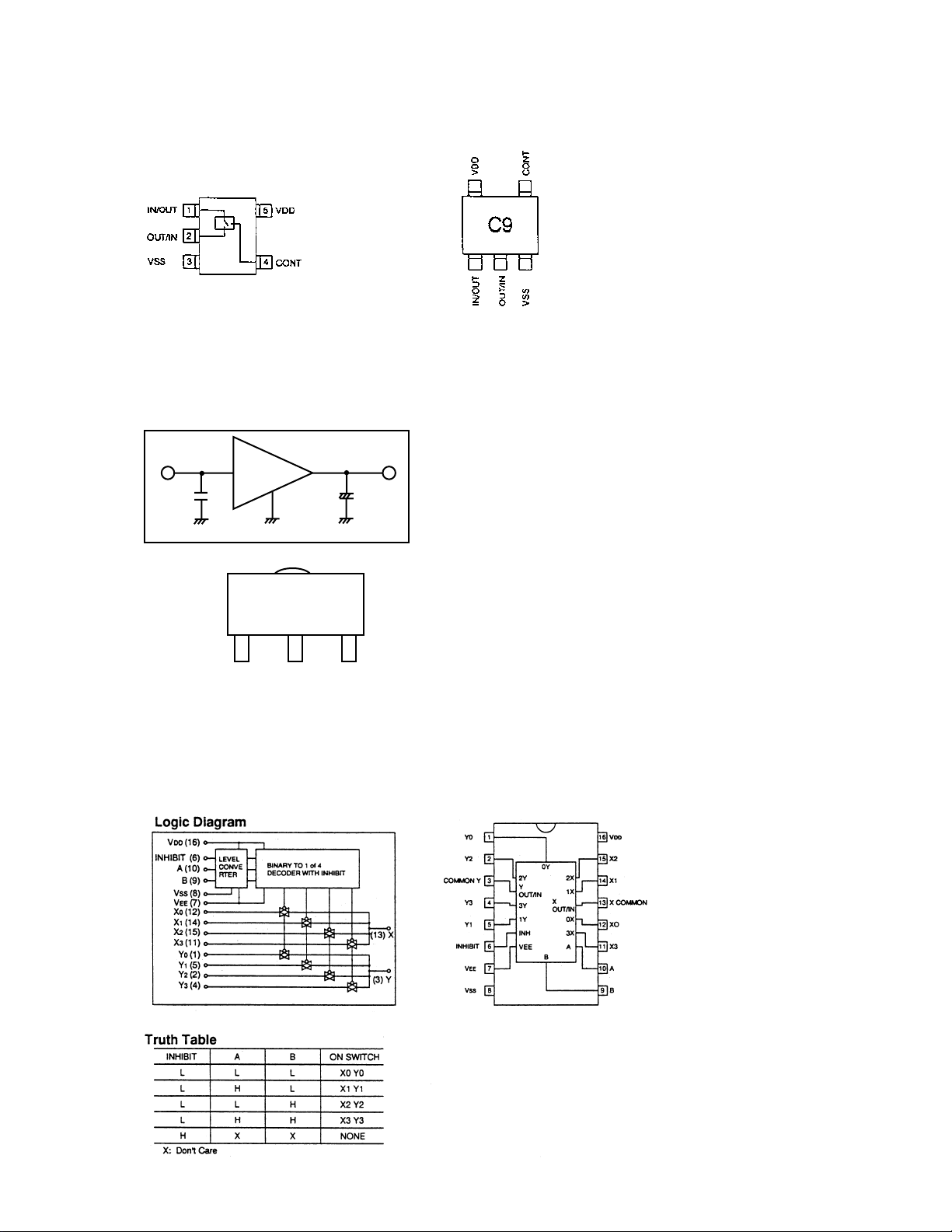

4) TC4S66F (XA0115) ................................................ 11

5) AN8010M (XA0119)................................................ 11

6) BU4052BF (XA0236) .............................................. 11

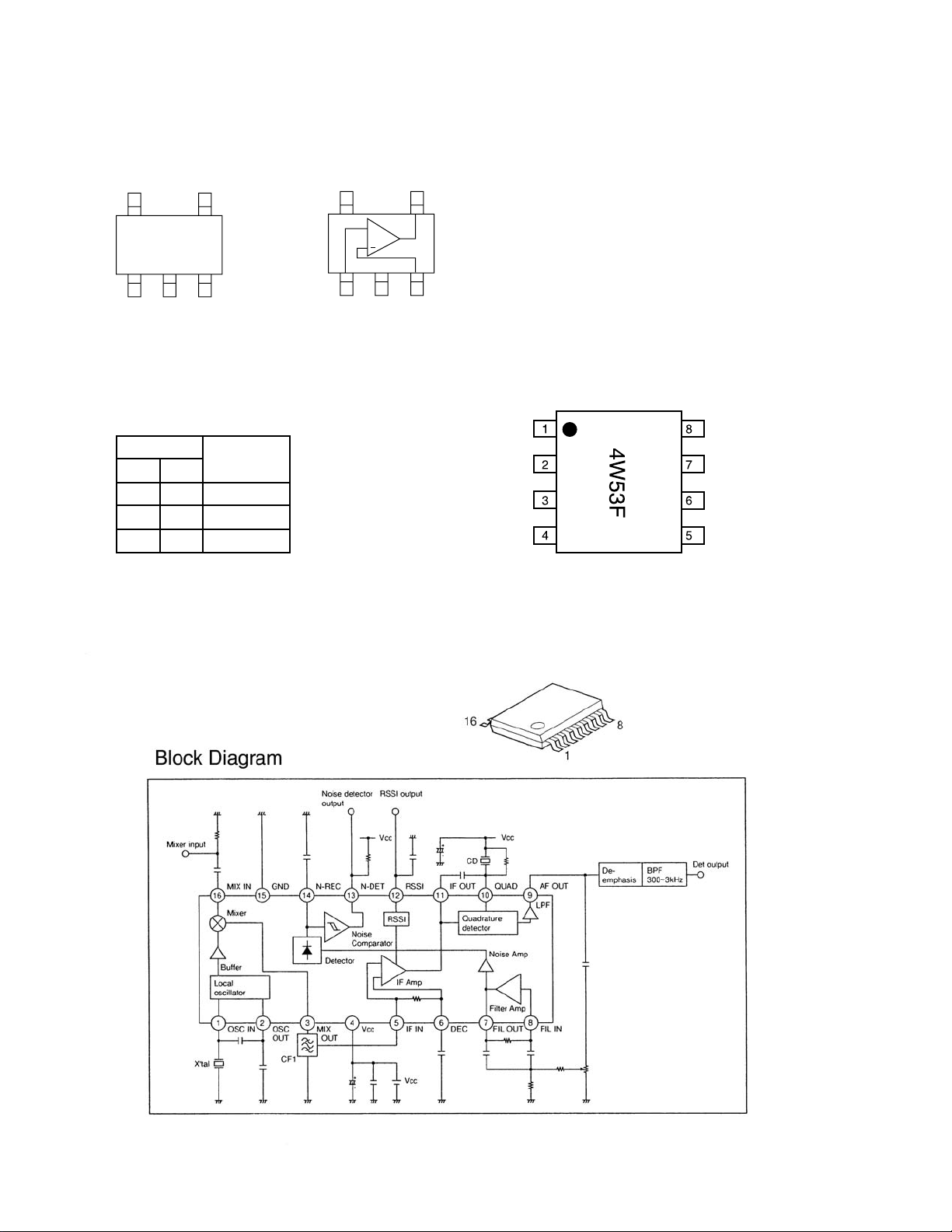

7) TA75S01F (XA0332) ............................................... 12

8) TC4W53FU (XA0348)............................................. 12

9) TA31136FN (XA0404)............................................. 12

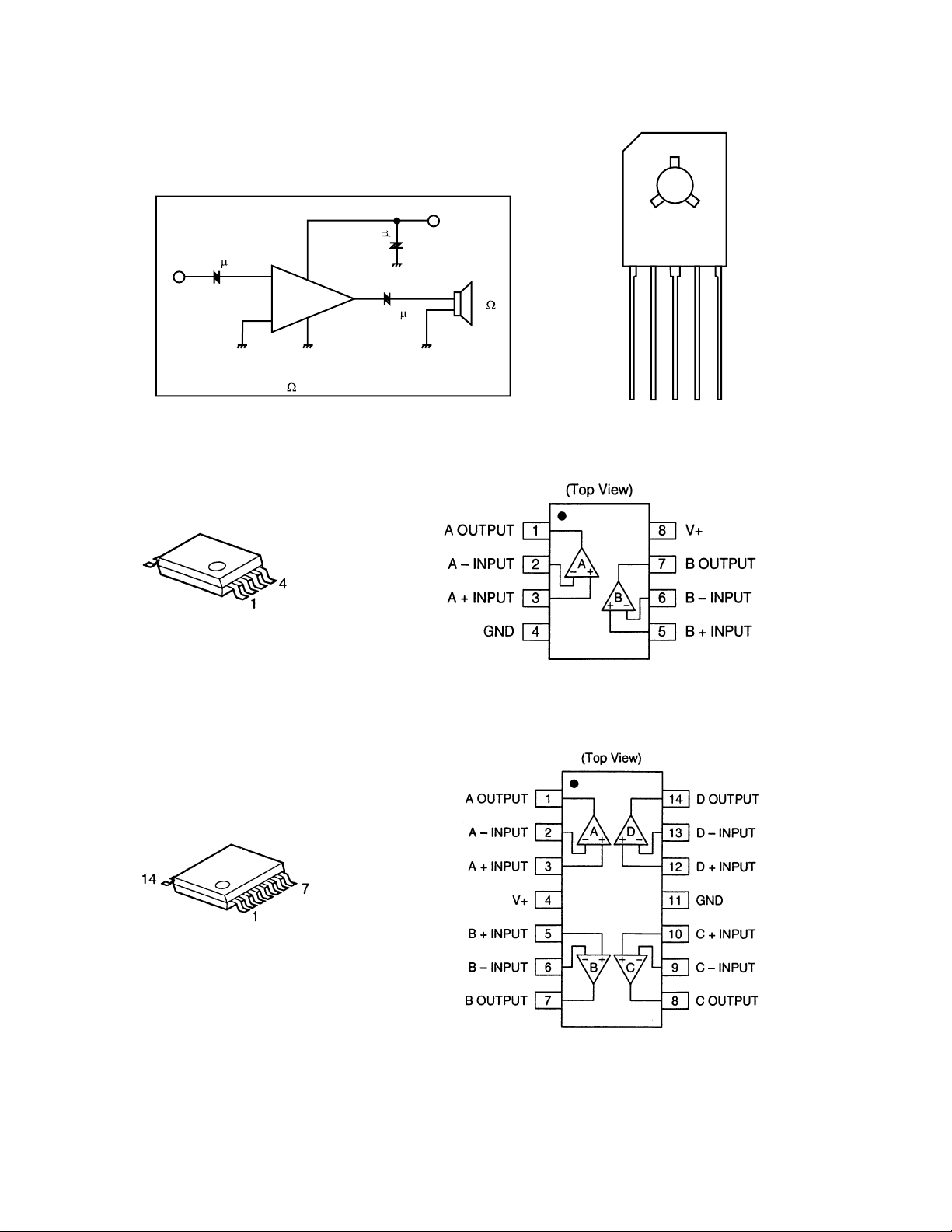

10) LA4425A (XA0410)................................................. 13

11) NJM2904V (XA0573).............................................. 13

12) NJM2902V-TE1 (XA0596) ...................................... 13

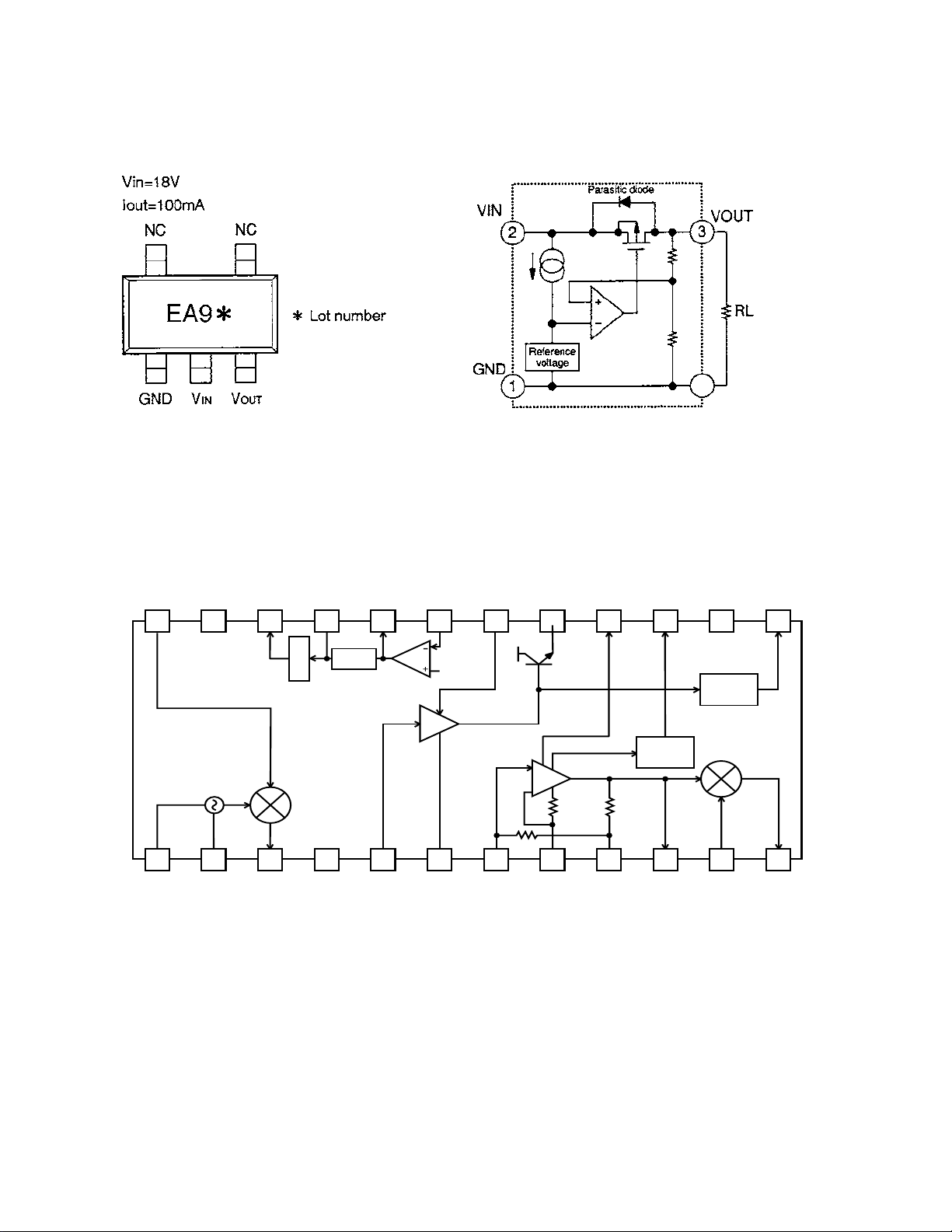

13) S-80845ALMP-EA9-T2 (XA0620) ........................... 14

14) TK10931V (XA0666)............................................... 14

15) BR24C64F-E2 (XA0669) ........................................ 15

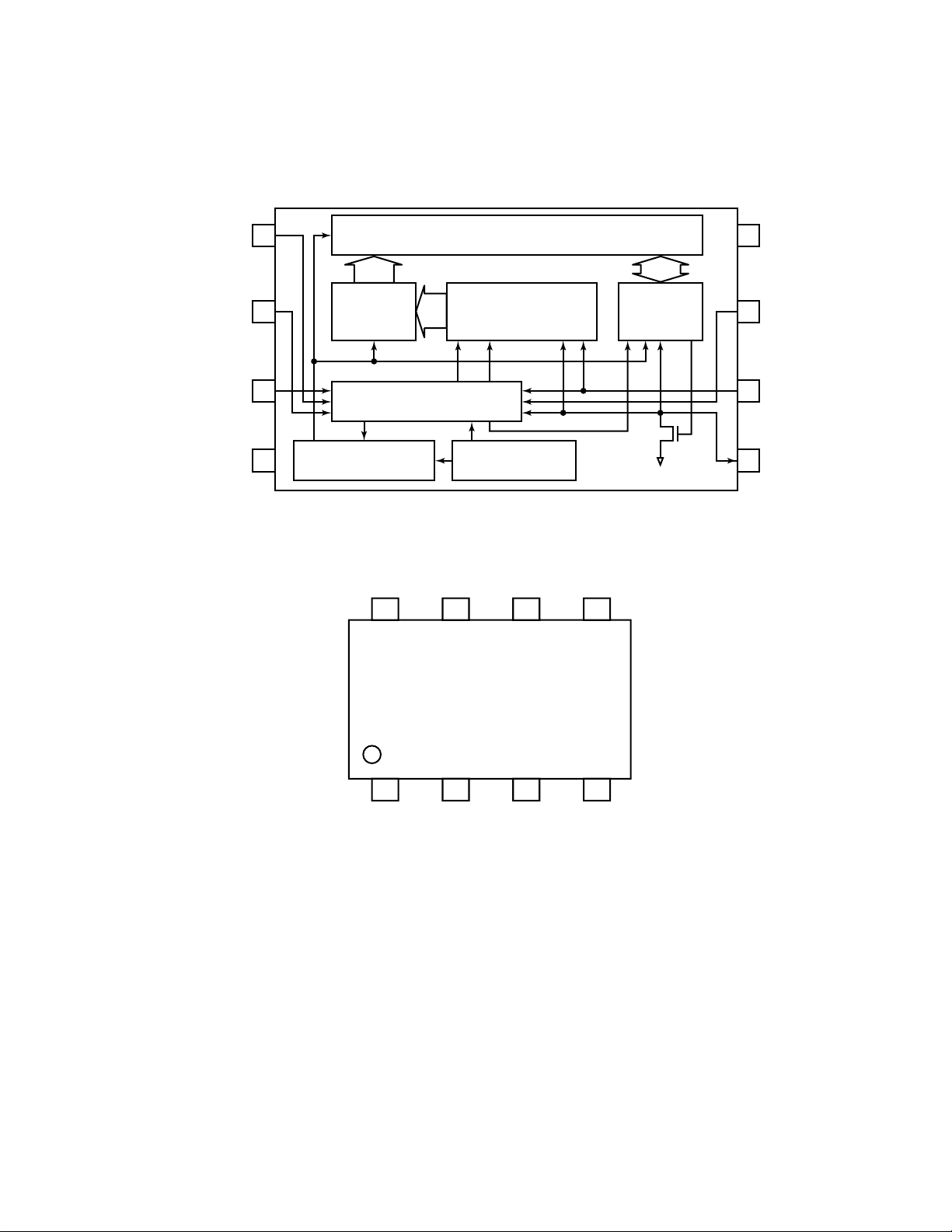

16) LC75884W (XA0899) ............................................. 16

17) M51132FP (XA0900) .............................................. 17

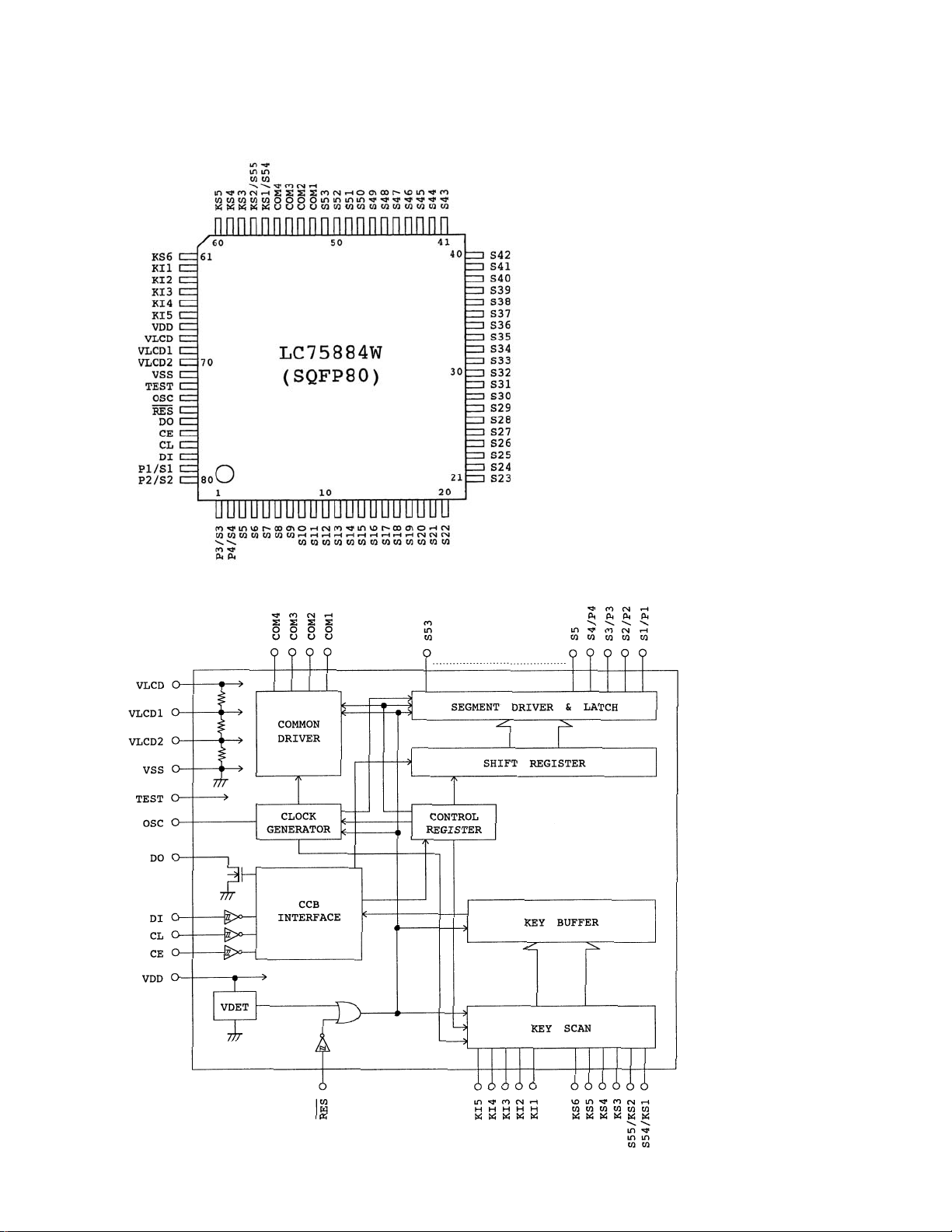

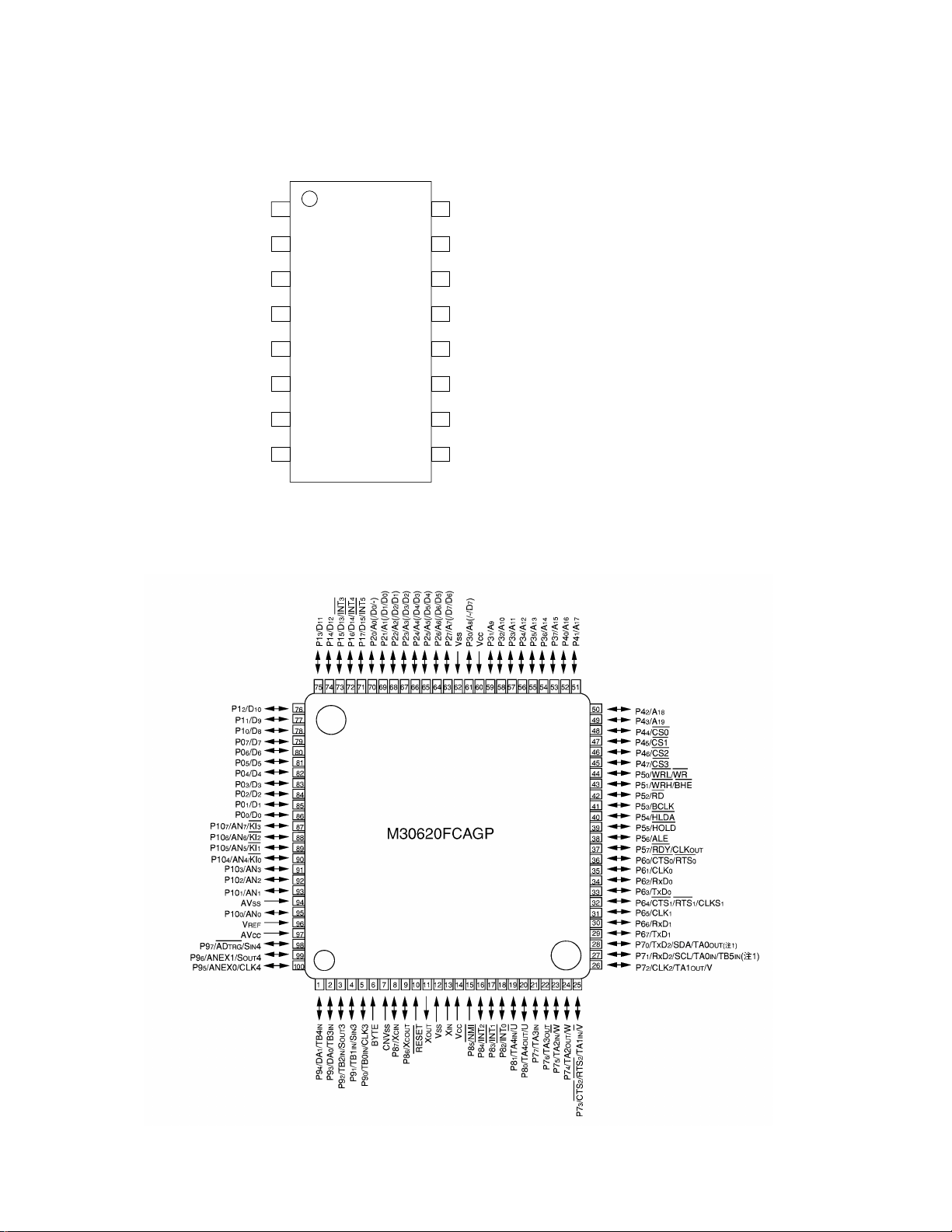

18) M30620FCAGP (XA0913/XA0949)................... 17~19

19) M38503M2H667FP (XA0914)........................... 20~21

20) M64076AGP (XA0915) ........................................... 22

21) S-816A50AMC (XA0925)........................................ 23

22) NJM78M05DL1A (XA0947) .................................... 23

23) Transistor, Diode, and LED Outline Dr awings .... 24~25

24) LCD Connection ............................................... 26~27

EXPLODED VIEW

1) Front V iew............................................................... 28

2) Bottom View............................................................ 29

PARTS LIST

Front Unit......................................................... 30~31

LED Unit ................................................................. 31

Main Unit .......................................................... 31~42

Mechanical Parts .................................................... 42

Packing Parts.......................................................... 42

Accessories (Screw Set)......................................... 42

ADJUSTMENT

1) Adjustment Spot ..................................................... 43

2) Adjustment Mode.................................................... 44

3) VHF Adjustment Specification................................. 45

4) UHF Adjustment Specification ................................ 46

5) VHF Test Specification ............................................ 47

6) UHF T est Specification............................................ 48

PC BOARD VIEW

1) Front Side A............................................................ 49

2) Front Side B............................................................ 49

3) Main Side A ............................................................ 50

4) Main Side B ............................................................ 51

FRONT SCHEMATIC DIAGRAM .............................. 52

MAIN SCHEMATIC DIAGRAM.................................. 53

FRONT BLOCK DIAGRAM ....................................... 54

MAIN BLOCK DIAGRAM........................................... 55

ALINCO,INC.

Page 2

SPECIFICATIONS

1) GENERAL

Frequency coverage 87.500 - 107.995MHz (WFM RX)

DR-620T (U.S amateur) 108.000 - 135.995MHz (AM RX)

136.000 - 173.995MHz (RX)

144.000 - 147.995MHz (TX)

335.000 - 479.995MHz (RX)

430.000 - 449.995MHz (TX)

DR-620E (European amateur) 87.500 - 107.995MHz (WFM)

144.000 - 145.995MHz (RX, TX)

430.000 - 439.995MHz (RX, TX)

Operating mode 16K0F3E (Wide mode) 8K50F3E (Narrow mode)

Frequency resolution 5, 8.33, 10, 12.5, 15, 20, 25, 30, 50, 100kHz

Number of memory channels 200

Antenna impedance 50

Power requirement 13.8V DC

Ground method Negative ground

Current drain Receive 0.6A (Max.) 0.4A (Squelched)

Transmit 11.0A

Operating temperature - 10 to 60 C

Frequency stability

Dimensions 142 (w)

Weight Approx. 1.0kg

Ω unbalanced

±15% (11.7 to 15.8V)

±2.5ppm

× 40 (h) × 174 (d) mm

(w/o knobs)

2) TRANSMITTER

Output power High : 50W (VHF)

35 W(UHF)

Mid : 10W

Low : 5W

Modulation system Variable reactance frequency modulation

Maximum frequency deviation

Spurious emission -60dB

Adjacent channel power -60dB

Modulation Distortion Lass than 3%

Microphone impedance 2k

2

±5kHz (Wide mode) ±2.5kHz (Narrow mode)

Ω

Page 3

3) RECEIVER

Sensitivity -16dBu for 12dB SINAD

Receiver circuitry Double conversion superheterodyne

Intermediate frequency 1

Squelch sensitivity -18dBu

Selectivity (-6dB / -60dB) 12kHz / 24kHz

Spurious and image rejection ratio 70dB

Audio output power 2.0W (8

! Note : All specifications are subject to change without notice or obligation.

st

21.7MHz 2nd 450kHz (VHF)

st

45.1MHz 2nd 455kHz (UHF)

1

Ω, 10% THD)

3

Page 4

CIRCUIT DESCRIPTION

1) VHF Reception

Incoming VHF signals are passed through a low-pass filter network, antenna switching diodes D20

(1SV268), D19 (1SS355) and D26 (DAN235E), and a high-pass filer netw ork, and on to the RF amplifier

Q19 (3SK131). The amplified RF signal is passed through another RF amplifier Q18 (2SC5226) and

band-pass filtered again by varactor-turned resonators L46, L49, L51 and D28, D29, D30 (all HVU359),

then applied to the 1st mixer Q21 (3SK240) along with the first local signal from the PLL circuit.

The first local signal is generated between 122.3 MHz and 126.3 MHz by the VHF VCO, which consists

of Q9 (2SK508) and varactor diodes D10, and D11 (both 1SV282) according to the receiving frequency.

The 21.7 MHz first IF signal is applied to monolithic crystal filters XF and XF2 (both Q2175AD20)

which strip away unwanted mixer products, and the IF signal is applied to the first IF amplifier Q20

(2SC4618). The amplified first IF signal is then delivered to the FM IF subsystem IC IC3 (TK10931V),

which contains the second mixer, limiter amplifier, noise amplifier, and FM detector.

The second local signal is generated by 21.25MHz TCXO, producing the 450 kHz second IF signal

when mixed with the first IF signal within IC3.

The 450 kHz second IF signal is applied to the ceramic filter FL1 (ALFYM450E) which strips away all

but the desired signal, and then passes through the limiter amplifier within IC3 to the discriminator coil

L101, which removes any amplitude variations in the 450 kHz IF signal before detection of speech.

The detected audio then signal is amplified by IC9 (NJM2902V-B) passes through the de-emphasis

network, a high-pass filter consisting of IC9 (NJM2902V-A) and associated circuitry, and low-pass

filter consisting and associated circuitry. The filtered audio signal is switched by IC12 (BU4052), then

passes through the audio volume control IC IC13 (M511312FP) which adjusts the audio sensitivity to

compensate for audio level variations.

The audio signal is amplified by IC8 (LA4425A), then applied to the internal loudspeaker.

4

Page 5

2) UHF Reception

Incoming UHF signals are passed through a low-pass filter network, high-pass filter network, antenna

switching diodes D16 (1SS355) and D18 (1SV268), and on to the band-pass filter netw ork consisting

of varctor diode D49 (HVU359) and L79.

The filtered UHF signal is amplified by RF amplifier Q41 (3SK240) and fed to another band-pass filter

consisting of varactor diode D50 (HVU359) and L80, and then is passed through another RF amplifier

Q43 (2SC5226) to another band-pass filter consisting of varactor diodes D51 and D52 (both HVU359)

and L81/L82.

st

The amplified and filtered UHF signal is applied to the 1

signal from the PLL circuit.

The first local signal is generated between 384.9 MHz and 404.9 (*2) MHz by the UHF VCO, which

consists of Q29 (2SK508) and varactor diodes D38 and D40 (both ISV278), according to the receiving

frequency.

The 45.1MHz first IF signal is applied to monolithic crystal filters XF3A and XF3B (Q4511BD10) which

strip away unw anted mix er products, and the IF signal is applied to the first IF amplifier Q44 (2SC4618).

The amplified first IF signal is then delivered to the FM IF subsystem IC IC5 (TA31136FN), which 2)

The amplified first IF signal is then delivered to the FM IF subsystem IC IC5 (TA31136FN), which

contains the second mixer, limiter amplifier, noise amplifier, and FM detector.

The second local signal is generated by 45.555 MHz crystal X4, producing the 455 kHz second IF

signal within IC5.

The 455kHz second IF signal is applied to the ceramic filter FL4 (CFW455E) which strips away all but

the desired signal, and then passes through the limiter amplifier within IC5 to the discriminator coil

L102 , which removes any amplitude variations in the 455 kHz IF signal before detection of speech.

The detected audio then signal is amplified by IC9 (NJM2902V-C) passes through the de-emphasis

network, a high-pass filter consisting of IC9 (NJM2902V-D) and associated circuitry, and a low-pass

filter consisting and associated circuitry. The filtered audio signal is switched by IC12 (BU4052), then

passes through the audio volume control IC IC13 (M511312FP), which adjusts the audio sensitivity to

compensate for audio level variations.

The audio signal is amplified by IC8 (LA4425A) then applied to the internal loudspeaker.

mixer Q42 (3SK240) along with the first local

3) FM Reception

Incoming FM signals are passed through a low-pass filter network, antenna switching diodes D19

(1SS355), D20 (1SV2685) and D26 (DAN235E), and a high-pass filter network, and on the RF amplifier

Q36 (2SC5066). The amplified RF signal is passed through band-pass filtered L, C, then applied to

st

mixer Q33 (2SC5066) along with the first local signal from the circuit.

the 1

The first local signal is generated between 86.7 MH and 118.7 MHz by the FM VCO, which consists of

Q14 (2SC4808) and varactor diodes D23, and D25, (both 1SV282) according to the receiving frequency.

The 10.7 MHz first IF signal is applied to ceramic filters FL3 (SFT10.7MAS) which strip awa y unwanted

mixer products , and the IF signal is applied to the first IF amplifier Q37 (2SC4618). The amplified first

IF signal is then delivered to the FM IF subsystem IC IC3 (TK10931V), limiter amplifier, noise amplifier,

and FM detector.

The 10.7 MHz first IF signal is applied to the discriminator coil L53, which removes any amplitude

variations in the 10.7 MHz IF signal before detection of speech.

5

Page 6

4) V/V (VHF-VHF) Dual Reception

During V & V operation, the incoming VHF “sub” band signal is passed through a lo w-pass filter network,

antenna switching diode D19 (1SS355), D20 (1SV268) and a high-pass filter netw ork to the RF amplifier

Q19 (3SK131). The amplified RF signal is passed through a high-pass filter network, VHF “sub” RF

amplifier Q31 (2SC5066), and a low-pass filter network, then is applied to the VHF “sub” first mixer

Q32 (2SC5066) along with the 45.1 MHz VHF “sub” first local signal from the VHF “sub” VCO circuit.

The VHF “sub” first local signal is generated between 189.1 MHz and 193.1 MHz by the VHF “sub”

VCO Q38.

The 45.1 MHz VHF “sub” second IF signal is applied to the UHF receiving circuit. The VHF “sub” signal

is amplified, filtered, and demodulated, etc., by the UHF “main” receiving circuit, described previously.

5) U/U (UHF-UHF) Dual Reception

During U/U operation, the incoming UHF “sub” band signal is passed through high-pass and low-pass

filter networks, antenna switching diodes D16 (1SS355) and D18 (ISV268), and another high-pass

filter network to the RF amplifier Q51 (2SC5066). The amplified RF signal is passed through a lowpass filter network, UHF “sub ”RF amplifier Q49 (2SC5066), and low-pass filter netw ork, then is applied

to the UHF “sub” first mixer Q52 (2SC5066) along with the 21.7 MHz UHF “sub” first local signal from

the UHF “sub” VCO.

The UHF “sub” first local signal is generated between 408.3 MHz and 428.3MHz by the UHF “sub”

VCO Q13.

The 21.7 MHz UHF “sub” second IF signal applied to VHF receiving circuit. The UHF “sub” signal is

amplified, filtered, and demodulated, etc., by the VHF receiving circuit, described previously.

6) VHF Squelch Control

When no VHF carrier is being receiv ed, noise at the output of the detector stage in IC3 is amplified and

band-pass filtered by the noise amp section of IC3, then passes through the noise adjust VR (VR8) to

CPU. The resulting DC voltage is applied to pin 88 of main CPU IC19 (M30624FGAGP), which

compares the squelch threshold level to that which set by the font panel VHF SQL knob.

While no carrier is received, pin 55 of IC19 remains “high,” turning on the squelch switch Q108

(DTC363EK) to disable audio output from the speaker.

7) UHF Squelch Control

When no UHF carrier is being received, noise at the output of the detector stage in IC5 is amplified

and band-pass filtered by the noise amp section of IC5, then passes through the noise adjust VR8 to

cpu. The resulting DC voltage is applied to pin 90 of main CPU IC19, which compares the squelch

threshold level to that which set by the front panel UHF SQL knob.

While no carrier is received, pin 56 of IC19 remains “high” turning the squelch s witch Q109 (DTC363EK)

to disable audio output from the speaker.

6

Page 7

8) Transmit Signal Path

The speech signal from the microphone passes through the MIC jack CN601 to AF amplifier IC601

(M5218FP) on the FRONT UNT. The amplified speech signal is subjected to amplitude limiting by

IC601 (M5218FP), then passes through the Front interface jacks CN602 and CN2 to MAIN Unit. On

the MAIN UNIT, the speech signal passes through the audio mute switch IC7 (TC4066F), MIC gain

control VR5 and buffer amplifier IC1 (NJM2902V-C) and a low-pass filter network at IC1 (NJM2902VA) to deviation control VR3 (for VHF Tx audio) or VR4 (for UHF Tx audio).

9) VHF Transmit Signal Path

The adjusted speech signal from VR3 is delivered to VHF VCO Q9, which frequency modulates the

transmitting VCO D6 (1SV278).

The modulated transmit signal passes through buff er amplifier Q7 (2SC5066), a lo w-pass filter network,

and another buffer amplifier Q3 (2SC5226) to another low-pass filter network.

The filtered transmit signal is applied to the Pre-Drive amplifier Q2 (2SK3074) and Drive amplifier Q1

(2SK2975), then finally is amplified by Power amplifier Q4 (RD70HV1) up to 50 Watts. This three

stage power amplifier’s gain is controlled by the APC circuit.

The 50-W att RF signal passes through a low-pass filter network, antenna switch D1 (XB15A407), and

another low-pass filter network, and then is delivered to the ANT jack.

10) UHF Transmit Signal Path

The adjusted speech signal from VR4 is delivered to UHF VCO Q29 which frequency modulates the

transmitting VCO D35 (1SV278).

The modulated transmit signal passes through buffer amplifiers Q28 (2SC5066) and Q7 (2SC5226) to

a high-pas filter network.

The filtered transmit signal is applied to the Pre-Drive amplifier Q2 (2SK3074) and Drive amplifier Q1

(2SK2975), then finally is amplified by Power amplifier Q4 (RD70HV1) up to 35 Watts. This three

stage power amplifier’s gain is controlled by the APC circuit.

The 35-Watt RF signal passes through a high-pass filter network, antenna switch D12 and D13

(UM9401F), low-pass filter and high-pass filter networks, and then is delivered to the ANT jack.

11) VHF Tx APC Circuit

A portion of the power amplifier output is rectified by D8 (MA4S713), D9 (MA4S713) and Q12 (2SC4081),

then delivered to APC IC1 (NJM2902V-D) as a DC voltage which is proportional to the output level of

the power amplifier.

The APC IC1 compares the rectified DC voltage from the power amplifier and the reference voltage

from the main CPU IC19, producing a control voltage f or the A utomatic Power Controller Q8 (RN2107)

and Q11 (RN1107) which regulates supply voltage to the Pre-Drive amplifier Q2, Drive amplifier Q1,

and P ower amplifier Q4, so as to maintain stable output po wer under v arying antenna loading conditions.

7

Page 8

12) UHF Tx APC Circuit

A portion of the power amplifier output is rectified by D9 (M44S713), D22 (MA4S713) and Q12

(2SC4081), then delivered to APCD IC1 (NJM2902V-D) as a DC voltage which is proportional to the

output level of the power amplifier.

The APC IC1 compares the rectified DC voltage from the power amplifier and the reference voltage

from the main CPU IC19, producing a control voltage f or the A utomatic Power Controller Q8 (RN2107)

and Q11 (RN1107) which regulates supply voltage to the Pre-Drive amplifier Q2, Drive amplifier Q1,

and P ower amplifier Q4, so as to maintain stable output po wer under varying antenna loading conditions.

13) VHF PTT Circuit

When the PTT switch is pressed, pin 4 of front CPU IC604 (M38503M) goes “LOW,” which sends the

“PTT” command to the main CPU, IC19. When it receives the “PTT” command, pin71 of Q19 goes

“high” to control local switch D5 (DAN235E), filter switch D2, D3, TX switch D17 (DAN235E), and APC

switch Q8/Q11, which activates the VHF Tx circuit. Meanwhile, pin 69 of IC19 goes “low,” which

disables the VHF Rx circuit.

14) UHF PTT Circuit

When the PTT switch is pressed, pin 4 of FICront CPU IC604 (M38503M) goes “LO” which sends the

“PTT” command to the main CPU, IC19, When it receives the “PTT” command, pin72 of IC19 goes

“high” to controls local switch D5, filter switch D2, D3, TX switch D17 and APC switch Q8/Q11, which

activates the UHF Tx circuit. Meanwhile, pin 70 of Q19 goes “low,” which disables the UHF Rx circuit.

15) VHF PLL

A portion of the output from the VHF VCO Q9 (2SK508) passes through b uff er amplifiers Q7 (2SC5066)

and Q5 (2SC5066) to the programmable divider section of the PLL IC IC2 (M64076AGP), which

divides the frequency according to the frequency dividing data from the main CPU, IC19. It is then

sent to the phase comparator.

The 21.25 MHz frequency of the reference oscillator circuit, made up of TCXO X1, is divided by the

reference frequency divider section of IC2 into 4250 or 3400 parts to become 5 kHz or 6.25 kHz

comparative reference frequencies, which are utilized by the phase comparator.

The phase comparator section of IC2 compares the phase between the frequency-divided oscillation

frequency of the VCO circuit and comparativ e frequency, and its output is a pulse corresponding to the

phase difference.

This pulse is integrated by the charge pump and loop filter of IC2 into a control voltage (VCV) to

control the oscillation frequency of the VHF VCO Q9.

8

Page 9

16) UHF PLL

A portion of the output from the UHF VCO Q29 (2SK508) passes through buffer amplifier Q28 (2SC5066)

and Q39 (2SC5066) to the programmable divider section of the PLL IC IC2 (M64076AGP), which

divides the frequency according to the frequency dividing data from the main PU IC2. It is then sent to

the phase comparator.

The 21.25 MHz frequency of the reference oscillator circuit, made up of TCX0 X1, is divided by the

reference frequency divider section of IC2 into 4250 or 3400 parts to become 5 kHz or 6.25kHz

comparative reference frequencies, which are utilized by the phase comparator.

The phase comparator section of IC2 compares the phase between the frequency-divided oscillation

frequency of the VCO circuit and comparativ e frequency, and its output is a pulse corresponding to the

phase difference.

This pulse is integrated by the charge pump and loop filter of IC2 into a control voltage (VCV) to

control the oscillation frequency of the UHF VCO Q29.

17) Power-on Circuit

When the POWER switch is turned on, pin 18 of man CPU IC19 goes “low .” When pin 18 of IC19 goes

“low,” pin 79 of IC19 goes “high” to activate the power switches Q63 (2SB1386) and Q74 (2SC4081),

which supply the DC power to the radio.

9

Page 10

SEMICONDUCTOR DATA

1) M5218FP (XA0068)

Dual Low Noise

Operational Amplifiers

Output 1

Inverting Input 1

Non Inverting Input 1

Power supply Minus

1

2

3

4

2) NJM78L05UA (XA0098)

5V V oltage Regulator

12

3

3) NJM7808FA (XA0102)

1. OUTPUT

2. COMMON

3. INPUT

Power Supply Plus

8

Output 2

7

Inverting Input 2

6

Non Inverting Input 2

5

8V V oltage Ragulator

Pin Assignment

123

10

1. OUTPUT

2. COMMON

3. INPUT

Page 11

4) TC4S66F (XA0115)

Bilateral Switch

5) AN8010M (XA0119)

10V V oltage Regulator

Test Circuit

Vin Vout

3

0.33µF

AN8010M

1

2

CA

Output Common Input

AN8010M

6) BU4052BF (XA0236)

Analog Multiplexer/Demultiplexer

10µF

11

Page 12

7) TA75S01F (XA0332)

Operational Amplifiers

5

4

S A

3

2

1

8) TC4W53FU (XA0348)

Multiplexer/Demultiplexer

Function T able

Control input

INH

L

L

H

* Don't Care

9) TA31136FN (XA0404)

A

L

H

*

ON channel

ch0

ch1

NONE

VCC

5

1

IN(+) VEE IN(-)

OUT

4

+

3

2

COMMON

INH

VEE

VSS

VDD

ch0

ch1

A

Low Power FM IF

12

Page 13

10) LA4425A (XA0410)

5W Audio Power Amplifiers

Test Circuit

Vcc

13.2V

+

LA4425

2.2

Input

F

1

+

2

5

3

Vcc=13.2V RL=4 Po =5W Gain= 45dB

11) NJM2904V (XA0573)

12) NJM2902V-TE1 (XA0596)

4

+

1000

1000 F

SP

F

4

12345

Quad Single Supply Operational Amplifier

13

Page 14

13) S-80845ALMP-EA9-T2 (XA0620)

Voltage Detector

5

1

4

23

14) TK10931V (XA0666)

Pin Assignment / BLOCK Diagram (Top View)

RF INPUT

24 23 22 21 20 19 18 17 16 15 14 13

GND

COMP OUTPUT

COMP INPUT

COMP

NOISE AMP OUTPUT

RECT

AMP

NOISE AMP INPUT

Vref

AM AGC INPUT

Vcc

AGC

AGC AMP OUTPUT

RF AGC OUTPUT

RSSI OUTPUT

AM

DET

AM SW

AM DET OUT

14

OSC

MIXER

AM

AMP

RSSI

FM

FM DET

AMP

1 2 3 4 5 6 7 8 9 10 11 12

Vcc

OSC(B)

OSC(E)

MIX OUTPUT

AM IF INPUT

DECOUPLING

FM IF INPUT

DECOUPLING

DECOUPLING

LIM OUTPUT

QUAD INPUT

FM DET OUTPUT

Page 15

15) BR24C64F-E2 (XA0669)

EE-P ROM

Block Diagram

A0

1

64Kbit EEPROM ARRAY

8

Vcc

A1

2

A2

3

GND

4

Pin Assignment

13bit

ADDRESS

DECODER

CONTROL CIRCUIT

HIGH VOLT AGE

GENERATOR

Vcc WP SCL SDA

13bit

SLAVE•WORD

ADDRESS REGISTER

STOPSTART

VOLT AGE

DETECTOR

BR24C64/F

REGISTER

ACK

8bit

DATA

7

WP

6

SCL

5

SDA

A0 A1 A2 GND

15

Page 16

16) LC75884W (XA0899)

LCD Driver

Block Diagram

16

Page 17

17) M51132FP (XA0900)

2ch Electronic Volume

Ref. supply out

Filter

Volume 1 cont.

Noise cont.

Volume 2 cont.

VCA SW

NC

GND

1

2

3

4

5

6

7

8

M51132FP

18) M30620FCAGP (XA0913/XA0949)

Main CPU

16

15

14

13

12

11

10

9

Output 1

Input 1

VCC

NC

NC

Input 2

Output 2

Mode SW

17

Page 18

Terminal Function of Main CPU

No. Pin Name Function I/O Logic up Description

1 P94/DA1

2 P93/DA0

3P92

4P91

5P90

6 BYTE

7 CNVss

8P87

9P86

10 RESET

1112Xout

Vss

1314Xin

Vcc

15 P85

16 P84

17 P83

18 P82

19 P81

20 P80

21 P77

22 P76

23 P75

24 P74

25 P73

26 P72

27 P71

28 P70

29 P67

30 P66

31 P65

32 P64

33 P63

34 P62

35 P61

36 P60

37 P57

38 P56

39 P55

40 P54

41 P53

42 P52

43 P51

44 P50

45 P47

46 P46

47 P45

48 P44

49 P43

50 P42

51 P41

52 P40

53 P37

54 P36

55 P35

56 P34

TONE O D/A CTCSS tone output/DCS output

APC O D/A Power output control

DATA O Pulse Serial data output for PLL IC

STB O Pulse Strobe for PLL IC

CLK O

BYTE I

CNVss I H Witer control

-

-

RESET IIL Reset input

XOUT O Main clock output

VSS

XIN I Main clock input

VCC

NMI I Activ high

BU I L

SEC I Aleam(SCR) sinal input

PSW I L Power switch input

CLKS O CPU clock-shift output

MVRC O Pluse Main volume control

LAMP I L up Lighting color selection (H:2color)

SVRC O

-

TUV O Pulse 144MHz Tuning-voltage control

TUU O Pulse 430MHz Tuning-voltage control

RXD2 I Pulse Serial Communication port for Clone

TXD2 O Pulse Serial Communication port for Clone

TXD1 O Pulse Serial Communication port for TNC

RXD1 I Pulse Serial Communication port for TNC

SCLK O Pulse Witer control

BUSY O Pulse Witer control

TXD O Pulse Serial Communication port for Front CPU

RXD I Pulse Serial Communication port for Front CPU

SCL O Pulse Serial clock output for EEPROM

SDA

DUD

SCR I Activ low up Ready sigunal for digital unit

EPM I Activ low up Witer control

PTTM I Activ low up PTT input for TNC

T5 O Activ low TX power output ON/OFF

SQC O Activ low Squelch control for TNC

STBD O Pulse Strobe for Digital unit

DSQ I Squelch signal input for Digital unit

TNCB O Power switch ON/OFF for TNC

VVCS O VHF Main VCO ON/OFF

UVCS O UHF Main VCO ON/OFF

DCSW O DCS switch

C/S O Activ low Digital/TNC mode ON/OFF

VAD O VHF digital ON/OFF

UAD O UHF digital ON/OFF

M/S O MAIN/SUB band select

WIDE O Activ low Wide mode select

NAR O Activ low Narrow mode select

MUTV O Activ low VHF AF mute signal output

MUTU O Activ low VHF AF mute signal output

Pulse Seriai clock output for PLL IC

GND

O

O

-

-

Activ high

Activ high

Pulse Sub volume control

O

O

I/O Pulse Serial dara output for EEPROM

I Activ low up Digital unit detect

Activ high

Activ high

Activ high

Activ high

Activ high

Activ high

Activ high

Activ high

-

-

GND

CPU power terminal

Interruption

Backup signal detection input

18

Page 19

57 P33

58

P32

59

P31

60

Vcc

61 P30

62

Vss

63 P27

64 P26

65 P25

66 P24

67 P23

68 P22

69 P21

70 P20

71 P17

72 P16

73 P15

74 P14

75 P13

76 P12

77 P11

78 P10

79 P07

80 P06

81 P05

82 P04

83 P03

84 P02

85 P01

86 P00

87 P107/AN7

88 P106/AN6

89 P105/AN5

90 P104/AN4

91 P103/AN3

92 P102/AN2

9394P101/AN1

Avss

95 P100/AN0

9697Vref

Avcc

98 P97

99 P96/ANEX1

100 P95/ANEX0

XBR O

DCSV

DCSU O Activ high

O

Activ high

Activ high

XBR mute signal

VHF DCS switch

UHF DCS switch

VCC - CPU power terminal

SCRB O Activ low Power output for Aleam

VSS VMMT O VHF mod mute output

UMMT O UHF mod mute output

Activ high

Activ high

GND

MMUT O Activ low Mic mute output

ULV

ULU

AM O AM mode ON/OFF

5RV

5RU

5TV O VHF TX power ON/OFF

5TU O UHF TX power ON/OFF

14RS O MAIN 144MHz power OM/OFF

S43RS O SUB 430MHz power ON/OFF

FMS O FM power ON/OFF

43RS O MAIN 430MHz power OM/OFF

S14RS O SUB 144MHz power ON/OFF

87RS O Ext band power ON/OFF

5VS O 5V power ON/OFF

C5S O 5V power ON/OFF

Activ high

I VHF unlock input

I UHF unlock input

Activ high

Activ high

Activ high

O VHF RX power ON/OFF

O UHF RX power ON/OFF

Activ high

Activ high

Activ high

Activ high

Activ high

Activ high

Activ high

Activ high

Activ high

Activ high

Activ high

ALAM O Activ low AF mute for Aleam

TB O Pulse ART/Toneburst signal output

BEP1 O Pulse Beep sound 1 output

BEP2 O Pulse Beep sound 2 output

O

FAN O Air FAN power ON/OFF

Activ high

SMTV I A/D VHF S-meter signal input

SQLV I A/D VHF noise input for squelch

SMTU I A/D

UHF S-meter signal input

SQLU I A/D UHF noise input for squelch

TINV I A/D VHF CTCSS/DCS tone input

TINU I A/D UHF CTCSS/DCS tone input

BAT I A/D

Power-supply voltage input

AVSS - AD converter Gnd

BP1 I A/D Band plan

VREF - AD converter ref. power

AVCC - AD converter power

BP2 I Ext.Band plan

BP3 I CH Band plan (L:CH)

THC I A/D PA Temperature detection

19

Page 20

19) M38503M2H667FP (XA0914)

Front CPU

20

Page 21

Terminal Function of Front CPU

No. Pin Name Function I/O Logic Description

1 Vcc

2 Vref VREF

3 Avss AVSS

4 P44 PTT I Activ low PTT key input

5 P43 RE1 I Pulse Dial (rotary encoder) input

6 P42 UP I Key input (UP)

7 P41 DOWN I Key input (DOWN)

8 P40 FUNC I Key input (FUNC)

9 P27 SQL I Key input (SQL)

10 P26 H/L I Key input (H/L)

11 P25/TxD RXD1 I Pulse Serial Communication port for Main CPU

12 P24/RxD TXD1

13 P23 TS/DCS I

14 P22 MHz I

15 CNVss CNVSS

16 P21 CALL I Key input (CALL)

17 P20 BAND I Key input (BAND)

18 RESET RESET Activ low

19 Xin XIN IIPulse CPU clock input

20 Xout XOUT

21 Vss GND

22 P17 V/M I Activ low

23 P16 RED O

24 P15 GREEN

25 P14 TXLED TX LED ON/OFF

26 P13 MRLED MAIN RX LED ON/OFF

27 P12 SRLED SUB RX LED ON/OFF

28 P11 DIM1 O Dommer control 1

29 P10 DIM2 O Dimmer control 2

30 P07

31 P06

32 P05 DO I Pulse Data input for LCD driver IC

33 P04 CE O

34 P03 CL O Pulse Clock output for LCD driver IC

35 P02 DI OOPulse Data output for LCD driver IC

36 P01 MUTE

37 P00 RE2 I Dial (rotary encoder) input

38 P34/AN4

39 P33/AN3

40 P32/AN2

41 P31/AN1 MVR I A/D MAIN volume voltage input

42 P30/AN0 SVR I A/D SUB volume voltage inpput

VCC

Activ low

Activ low

Activ low

Activ low

Activ low

Pulse Serial Communication port for Main CPU

O

Activ low

Activ low

Key input (TS/DCS)

Key input (MHz)

Activ low

Activ low

Reset input

O

CPU clock output

Key input (UP)

O

O

O

O

Activ high

Activ high

Activ high

Activ high

Activ high

Lighting color ON/OFF (RED)

Lighting color ON/OFF (YELLOW)

Activ high

Activ high

Activ high

Activ high

Strobe for LCD driver IC

-

21

Page 22

20) M64076AGP (XA0915)

Dual PLL Synthesizer

A

Equivalent Circuit

Parameter Symbol Condition Min. Typ. Max. Unit

Power supply voltage Vcc

LPF supply voltage VF

Local oscillator input level Vin

Local oscillator input frequency Fin

Xin input level Vxin

Xin input frequency Fxin

Fin=80~520MHz

Vin=-10dBm

Fin=80~520MHz

Vin=-20~-4dBm

Vcc=2.7~5.5V

Vcc=2.7~5.5V

Vcc=2.7~5.5V

Fxin=10~25MHz

Sine wave

Vcc=2.7~5.5V

Vxin=0.4~1.4Vp-p

2.7 - 5.5 V

-912V

-20 - -4 dBm

80 - 520 MHz

0.4 - 1.4 Vp-p

10 - 25 MHz

22

Page 23

21) S-816A50AMC (XA0925)

Voltage Regulator

Top View

5 4

1 2 3

No. Terminal

1 EXT

2 VSS

3 ON/OFF

4 VIN

5 VOUT

A

V

+

-

ON/OFF

EXT

IN

V

OUT

V

SS

22) NJM78M05DL1A (XA0947)

Voltage Regulator

1.INPUT

2.GND

3.OUTPUT

123

A

+

-

V

23

Page 24

23) Transistor, Diode, and LED Outline Drawings

XB15A407AGB

XD0013

MI7

MA2S077-TX

XD0319

5

ISV278

XD0374

T1

2SK3074

XE0044

WA

GDS

2SB1132

XT0061

C

BA

PQ

BCE

2SB1386

XT0190

BHQ

CBE

UDZ5. 1B

XD 0165

A2

DAN235E-TL

XD0320

M

MA4S713-TX

XD0375

M1N

3SK240

XE0048

G1

G2

UN

DS

2SC4081

XT0095

C

BR

BE

DTC363EK

XU0160

C

H27

E

B

MA742

XD0250

M1U

MA2S111-TX

XD0323

A

ISV282

XD0376

TD

VRPG3312X

XL0051

RED

GR

K

2SA1736

XT0099

BLDCE

DTD114EK

XU0173

C

F24

E

B

1SS355

XD0254

A

HSU277TRF

XD0331

MAZS270HL

XD0377

2^

FA1111C

XL0069

2SC5066-O

XT0138

C

M

E

B

RN2107 TE85L

XU0192

C

YM

E

B

DSA3A1

XD0131

ISS362 TE85L

XD0338

C3

2SK508

XE0010

G

K52

SD

FA1111C

XL0077

2SC5226

XT0146

C

LN4

BE

RN1107 TE85L

XU0193

C

XH

E

B

HVU359TRF

XD0314

S

ISS390 TE61

XD0342

3SK131V12

XE0028

G1 G2

V12

DS

FA1111C

XL0091

2SC4808-TX. AR

XT0171

C

3M

E

B

RN1111

XU0197

C

XM

E

B

MA2S728-TX

XD0315

B

UM9401F

XD0373

2SK2975-T11-A

XE0038

MPG338S

XL0092

K

A

2SC4618TLP

XT0172

C

AP

E

B

XP03383-TX

XU0202

D V

24

DTr1

1

2

3

47k

10k

DTr2

4.7k

Page 25

RD70VHF1 (XE0047)

Nch MOS FET

PIN

1

DRAIN

SOURCE

2

GATE

3

1

2

3

ABSOLUTE MAXIMUM RATING

ELECTRICAL CHARACTERISTIC(Ta=25˚C)

Parameter Symbol Test conditions Unit

Saturated drain current

Gate to source leakage current

Threshold voltage

Output power 1

Drain officiency 1

Output power 2

Drain officiency 2

IDSS

IGSS

Vth

Po1

ηD1

Po2

ηD2

Symbol

Pch

VDSS

VGSS

Tj

Tstg

Vds=17V, Vgs=0V

Vds=10V, Vgs=0V

Vds=12V, Ids=1ma

f=175MHz, Pin=6W

Vds=12.5V

Ids(idle)=2.0A

f=520MHz, Pin=10W

Vds=12.5V

Ids(idle)=2.0A

Test conditions

Tc=25˚C

Vgs=0V

Vds=0V

Rating

150

30

±20

+175

-40 ~ +125

Limits

Min Max

300

5

1.3

2.3

70

55

50

50

Unit

W

V

V

˚C

˚C

µA

µA

V

W

%

W

%

25

Page 26

24) LCD Connection

26

Page 27

S1

S2

S3

S4

S5

S6

S7

S8

S9

S10

S11

S12

COM4

COM3

COM2

COM1

S13

S14

S15

S16

S17

S18

S19

S20

S21

S22

S23

S24

S25

S26

S27

S28

S29

S30

S31

S32

S33

S34

S35

S36

S37

S38

S39

S40

S41

S42

S43

S44

S45

S46

S47

S48

S49

S50

S51

S52

S53

S54

S55

S56

COM1 COM2 COM3 COM4

10k

10a

111k

11a

12k

12a

13k

13a

14k

14a

15k

15a

-

-

-

COM1

Q2

15j

Q4

14j

TNC

13j

Q3

12j

Q1

11j

SUB

10j

DCS

T

9j

minus(−)

8j

plus(+)

7j

Nar

6j

Lo

5j

Mj

4j

AM

3a

2a

F

2b

3b

4k

4a

5k

5a

6k

6a

7k

7a

8k

8a

9k

9a

N.C.

10l

10b

11l

11b

12l

12b

13l

13b

14l

14b

15l

15b

-

-

COM2

-

R

15g

15f

14g

14f

13g

13f

12g

12f

11g

11f

10g

10f

SQ

9g

9f

8g

8f

7g

7f

6g

6f

5g

5f

4g

4f

3f

2f

1b,c

2g

3g

4l

4b

5l

5b

6l

6b

7l

7b

8l

8b

9l

9b

-

10h

10c

11h

11c

12h

12c

13h

13c

14h

14c

15h

15c

-

COM3

-

-

Q5

15m

15e

14m

14e

13m

13e

12m

12e

11m

11e

10m

10e

BUSY-2

9m

9r

8m

8e

7m

7e

6m

6e

5m

5e

4m

4e

3e

2e

SQL

2c

3c

4h

4c

5h

5c

6h

6c

7h

7c

8h

8c

9h

9c

-

10p

W-2

11p

W-3

12p

DP2

13p

W-4

14p

W-5

15p

5-2

COM4

15n

15d

14n

14d

13n

13d

12n

12d

11n

11d

10n

10d

W-1

9n

9r

8n

8e

7n

7e

6n

6e

5n

5e

4n

4d

3d

2d

BUSY-1

T-1

T-2

4p

T-3

5p

T-4

6p

DP1

7p

T-5

8p

T-6

9p

5-1

-

-

-

-

-

27

Page 28

EXPLODED VIEW

1) Front View

KB0089

AX0003

UP0448A

FG0358

AX0003

ST0081

NP0140

EL0054

FG0352

FP0153A

TL0029

DG0042

DG0041

UP0448A

FM0034

TL0028

28

NK0073

NK0072

AN0013

DP0145

NK0072

UE0035

NP0139

DG0042

FP0153A

KZ0147

Page 29

2) Bottom View

AA0050

ST0065

ES0017

AV0006

UX1047

FG0327

AV0006

AA0050

AV0006

AA0050

AW0012

AV0006

FM0220

AV0006

AA0050

AV0006

KS0081

AZ0037Y

QB0036

AZ0037Y

FM0216

FP0151

AA0077

AA0077

AA0077

AA0077

AZ0037Y

AZ0037Y

ST0066

TG0034

FG0361

UX1284

FP0198

FP0197

ET0011

AV0006

ET0011

UE0258

SP0008

FP0198

SS0098

FG0361

29

Page 30

PARTS LIST

1

Front Unit

Ref.

Parts No. Parts NameDescription

No. (T) (E)

C601 CU3535 Chip C. GRM36B102K50PT 1 1

C602 CS0424 Chip Tantalum TMCMA1C106MTR 1 1

C603 CU3523 Chip C. GRM36CH101J50PT 1 1

C604 CU0108 Chip C. LMK212BJ105KG 1 1

C605 CU3551 Chip C. GRM36B223K16PT 1 1

C606 CU3535 Chip C. GRM36B102K50PT 1 1

C607 CS0424 Chip Tantalum TMCMA1C106MTR 1 1

C608 CU3535 Chip C. GRM36B102K50PT 1 1

C609 CU0108 Chip C. LMK212BJ105KG 1 1

C610 CU3535 Chip C. GRM36B102K50PT 1 1

C611 CU3535 Chip C. GRM36B102K50PT 1 1

C612 CU3535 Chip C. GRM36B102K50PT 1 1

C613 CU3535 Chip C. GRM36B102K50PT 1 1

C614 CU3535 Chip C. GRM36B102K50PT 1 1

C615 CS0424 Chip Tantalum TMCMA1C106MTR 1 1

C616 CU3535 Chip C. GRM36B102K50PT 1 1

C617 CS0424 Chip Tantalum TMCMA1C106MTR 1 1

C618 CU3533 Chip C. GRM36B681K50PT 1 1

C619 CU3535 Chip C. GRM36B102K50PT 1 1

C620 CU3535 Chip C. GRM36B102K50PT 1 1

C621 CU3535 Chip C. GRM36B102K50PT 1 1

C622 CU3535 Chip C. GRM36B102K50PT 1 1

C623 CU3543 Chip C. GRM36B472K25PT 1 1

C624 CU3543 Chip C. GRM36B472K25PT 1 1

C625 CU3551 Chip C. GRM36B223K16PT 1 1

C626 CU3023 Chip C. C1608CH1H101JT-AS 1 1

C627 CU3023 Chip C. C1608CH1H101JT-AS 1 1

CN601 UE0035 Connector FM214-8SMPY 1 1

CN602 UJ0052 Jack HJC0163-01-022 1 1

CN603 UE0456 Connector PI28A08M 1 1

D601 XD0254 Chip Diode 1SS355 TE17 1 1

D606 XD0254 Chip Diode 1SS355 TE17 1 1

D611 XL0069 Chip LED FA1111C-TR 1 1

D612 XL0091 Chip LED FY1111C-433-TR 1 1

D613 XL0069 Chip LED FA1111C-TR 1 1

D614 XL0092 LED MPG3338S 1 1

D618 XL0051 LED VRPG3312X 1 1

D620 XD0254 Chip Diode 1SS355 TE17 1 1

IC601 XA0068 IC M5218AFP/600E 1 1

IC602 XA0947 IC NJM78M05DL1A-TE1 1 1

IC603 XA0899 IC LC75884W 1 1

IC604 XA0914 IC M38503M2H667FP 1 1

LCD60

EL0054 LCD LCD DR620 1 1

Q601 XT0095 Chip Transistor 2SC4081 T106R 1 1

Q602 XT0095 Chip Transistor 2SC4081 T106R 1 1

Q603 XU0193 Chip Transistor RN1107 TE85L 1 1

Q604 XT0095 Chip Transistor 2SC4081 T106R 1 1

Q605 XU0193 Chip Transistor RN1107 TE85L 1 1

Q606 XU0192 Chip Transistor RN2107 TE85L 1 1

Q607 XU0173 Chip Transistor DTD114EK-T146 1 1

Q608 XU0173 Chip Transistor DTD114EK-T146 1 1

Q609 XT0095 Chip Transistor 2SC4081 T106R 1 1

Q610 XU0193 Chip Transistor RN1107 TE85L 1 1

Q611 XT0095 Chip Transistor 2SC4081 T106R 1 1

Q612 XU0193 Chip Transistor RN1107 TE85L 1 1

R601 RK3566 Chip R. ERJ2GEJ224X 1 1

R602 RK3550 Chip R. ERJ2GEJ103X 1 1

R603 RK3551 Chip R. ERJ2GEJ123X 1 1

Qty

Ref.

Parts No. Parts NameDescription

No. (T) (E)

R604 RK3538 Chip R. ERJ2GEJ102X 1 1

R605 RK3560 Chip R. ERJ2GEJ683X 1 1

R606 RK3543 Chip R. ERJ2GEJ272X 1 1

R607 RK3550 Chip R. ERJ2GEJ103X 1 1

R608 RK3550 Chip R. ERJ2GEJ103X 1 1

R609 RK3538 Chip R. ERJ2GEJ102X 1 1

R610 RK3550 Chip R. ERJ2GEJ103X 1 1

R611 RK3550 Chip R. ERJ2GEJ103X 1 1

R612 RK3526 Chip R. ERJ2GEJ101X 1 1

R613 RK3522 Chip R. ERJ2GEJ470X 1 1

R614 RK3501 Chip R. ERJ2GE0R00X 1 1

R615 RK3546 Chip R. ERJ2GEJ472X 1 1

R616 RK3550 Chip R. ERJ2GEJ103X 1 1

R617 RK3546 Chip R. ERJ2GEJ472X 1 1

R618 RK3550 Chip R. ERJ2GEJ103X 1 1

R619 RK3550 Chip R. ERJ2GEJ103X 1 1

R620 RK3550 Chip R. ERJ2GEJ103X 1 1

R621 RK3550 Chip R. ERJ2GEJ103X 1 1

R622 RK3550 Chip R. ERJ2GEJ103X 1 1

R623 RK3550 Chip R. ERJ2GEJ103X 1 1

R624 RK3550 Chip R. ERJ2GEJ103X 1 1

R625 RK3550 Chip R. ERJ2GEJ103X 1 1

R626 RK3550 Chip R. ERJ2GEJ103X 1 1

R627 RK3550 Chip R. ERJ2GEJ103X 1 1

R628 RK3550 Chip R. ERJ2GEJ103X 1 1

R629 RK3550 Chip R. ERJ2GEJ103X 1 1

R630 RK3546 Chip R. ERJ2GEJ472X 1 1

R631 RK3550 Chip R. ERJ2GEJ103X 1 1

R632 RK3542 Chip R. ERJ2GEJ222X 1 1

R633 RK3526 Chip R. ERJ2GEJ101X 1 1

R634 RK3526 Chip R. ERJ2GEJ101X 1 1

R635 RK3558 Chip R. ERJ2GEJ473X 1 1

R636 RK3538 Chip R. ERJ2GEJ102X 1 1

R637 RK3538 Chip R. ERJ2GEJ102X 1 1

R639 RK3026 Chip R. MCR03EZHJ101 1 1

R640 RK3550 Chip R. ERJ2GEJ103X 1 1

R641 RK3570 Chip R. ERJ2GEJ474X 1 1

R642 RK3538 Chip R. ERJ2GEJ102X 1 1

R643 RK3574 Chip R. ERJ2GEJ105X 1 1

R645 RK3030 Chip R. MCR03EZHJ221 1 1

R646 RK3534 Chip R. ERJ2GEJ471X 1 1

R651 RK3530 Chip R. ERJ2GEJ221X 1 1

R652 RK3530 Chip R. ERJ2GEJ221X 1 1

R653 RK3535 Chip R. ERJ2GEJ561X 1 1

R654 RK3535 Chip R. ERJ2GEJ561X 1 1

R655 RK3528 Chip R. ERJ2GEJ151X 1 1

R656 RK3535 Chip R. ERJ2GEJ561X 1 1

R657 RK3528 Chip R. ERJ2GEJ151X 1 1

R658 RK3550 Chip R. ERJ2GEJ103X 1 1

R659 RK3550 Chip R. ERJ2GEJ103X 1 1

R660 RK3026 Chip R. MCR03EZHJ101 1 1

R661 RK3538 Chip R. ERJ2GEJ102X 1 1

R662 RK3030 Chip R. MCR03EZHJ221 1 1

R663 RK3538 Chip R. ERJ2GEJ102X 1 1

R666 RK3538 Chip R. ERJ2GEJ102X 1 1

R667 RK3538 Chip R. ERJ2GEJ102X 1 1

R668 RK3538 Chip R. ERJ2GEJ102X 1 1

R669 RK3538 Chip R. ERJ2GEJ102X 1 1

Qty

30

Page 31

Ref.

3

4

5

6

7

8

9

Parts No. Parts NameDescription

No. (T) (E)

RE601 UR0015 Dial RH90N74E20-A90770 1 1

SW601 UU0015Z Switch EVQPPPA25 1 1

SW602 UU0015Z Switch EVQPPPA25 1 1

SW60

UU0015Z Switch EVQPPPA25 1 1

SW60

UU0015Z Switch EVQPPPA25 1 1

SW60

UU0015Z Switch EVQPPPA25 1 1

SW60

UU0015Z Switch EVQPPPA25 1 1

SW60

UU0015Z Switch EVQPPPA25 1 1

SW60

UU0015Z Switch EVQPPPA25 1 1

SW60

UU0015Z Switch EVQPPPA25 1 1

VR601 RV0035 Variable R. EVUF2JFK4B14 1 1

VR602 RV0035 Variable R. EVUF2JFK4B14 1 1

X601 XB0029 Ceramic OSC EF0S4914E5 1 1

TL0029 DIFFUSION SHEET 1 1

FG0358 LCD CUSHION DR620 2 2

ST0081 LCD HOLDER DR620 1 1

DG0041 LCD LIGHT DR620 1 1

FG0352 LCD RUBBER CONNECTOR 1 1

FM0034 MIC GND PLATE 1 1

FP0034 MIC SPACER DR110 1 1

TL0028 REFLECTIVE SHEET 1 1

Qty

LED Unit

Ref.

Parts No. Description Parts Name

No. (T) (E)

D602 XL0077 Chip LED FA1111C-732-TR 1 1

D603 XL0077 Chip LED FA1111C-732-TR 1 1

D604 XL0077 Chip LED FA1111C-732-TR 1 1

D605 XL0091 Chip LED FY1111C-433-TR 1 1

D607 XL0077 Chip LED FA1111C-732-TR 1 1

D608 XL0091 Chip LED FY1111C-433-TR 1 1

D609 XL0077 Chip LED FA1111C-732-TR 1 1

D610 XL0077 Chip LED FA1111C-732-TR 1 1

D615 XL0091 Chip LED FY1111C-433-TR 1 1

D616 XL0091 Chip LED FY1111C-433-TR 1 1

D617 XL0091 Chip LED FY1111C-433-TR 1 1

D619 XL0091 Chip LED FY1111C-433-TR 1 1

R647 RK3028 Chip R. MCR03EZHJ151 1 1

R648 RK3028 Chip R. MCR03EZHJ151 1 1

R649 RK3028 Chip R. MCR03EZHJ151 1 1

R650 RK3026 Chip R. MCR03EZHJ101 1 1

R664 RK3026 Chip R. MCR03EZHJ101 1 1

R665 RK3026 Chip R. MCR03EZHJ101 1 1

Qty

Main Unit

Ref.

Parts No. Description Parts Name

No. (T) (E)

C1 CU3035 Chip C. C1608JB1H102KT-AS 1 1

C3 CU3535 Chip C. GRM36B102K50PT 1 1

C4 CU3031 Chip C. C1608JB1H471KT-AS 1 1

C5 CU4008 Chip C. GRM42-6CH070D500PT 1 1

C6 CU3019 Chip C. C1608CH1H470JT-AS 1 1

C8 CU3035 Chip C. C1608JB1H102KT-AS 1 1

C9 CU7046 Chip C. UC232H0270C-T 1 1

C10 CU3035 Chip C. C1608JB1H102KT-AS 1 1

C11 CU3035 Chip C. C1608JB1H102KT-AS 1 1

C12 CU3057 Chip C. C1608CH1H130JT-A 1 1

C13 CU3057 Chip C. C1608CH1H130JT-A 1 1

Qty

Ref.

Parts No. Description Parts Name

No. (T) (E)

C14 CU4023 Chip C. GRM42-6CH101J500PT 1 1

C15 CU7052 Chip C. UC232H0820F-T 1 1

C16 CU3507 Chip C. GRM36CH060D50PT 1 1

C17 CU3018 Chip C. C1608CH1H390JT-AS 1 1

C18 CU3535 Chip C. GRM36B102K50PT 1 1

C19 CU3535 Chip C. GRM36B102K50PT 1 1

C20 CU4023 Chip C. GRM42-6CH101J500PT 1 1

C21 CU3535 Chip C. GRM36B102K50PT 1 1

C22 CU3511 Chip C. GRM36CH100D50PT 1 1

C23 CU3035 Chip C. C1608JB1H102KT-AS 1 1

C26 CU3535 Chip C. GRM36B102K50PT 1 1

C27 CU3515 Chip C. GRM36CH220J50PT 1 1

C29 CU3515 Chip C. GRM36CH220J50PT 1 1

C30 CU3535 Chip C. GRM36B102K50PT 1 1

C31 CU3535 Chip C. GRM36B102K50PT 1 1

C32 CU3024 Chip C. C1608CH1H121JT-AS 1 1

C33 CU3024 Chip C. C1608CH1H121JT-AS 1 1

C35 CU4016 Chip C. GRM42-6CH270J500PT 1 1

C36 CU4015 Chip C. GRM42-6CH220J500PT 1 1

C38 CU4016 Chip C. GRM42-6CH270J500PT 1 1

C39 CU4014 Chip C. GRM42-6CH180J500PT 1 1

C40 CU7050 Chip C. UC232H0560F-T 1 1

C42 CU3513 Chip C. GRM36CH150J50PT 1 1

C43 CU3518 Chip C. GRM36CH390J50PT 1 1

C44 CU3515 Chip C. GRM36CH220J50PT 1 1

C45 CU3035 Chip C. C1608JB1H102KT-AS 1 1

C46 CU3001 Chip C. C1608CH1H0R5CT-AS 1 1

C48 CU3001 Chip C. C1608CH1H0R5CT-AS 1 1

C49 CU4013 Chip C. GRM42-6CH150J500PT 1 1

C51 CU3511 Chip C. GRM36CH100D50PT 1 1

C52 CU0108 Chip C. LMK212BJ105KG 1 1

C53 CU0108 Chip C. LMK212BJ105KG 1 1

C54 CU3035 Chip C. C1608JB1H102KT-AS 1 1

C55 CU3515 Chip C. GRM36CH220J50PT 1 1

C56 CU3511 Chip C. GRM36CH100D50PT 1 1

C57 CU4011 Chip C. GRM42-6CH100J500PT 1 0

C57 CU4012 Chip C. GRM42-6CH120J500PT 0 1

C58 CU3509 Chip C. GRM36CH080D50PT 1 1

C59 CU3510 Chip C. GRM36CH090D50PT 1 1

C60 CU3514 Chip C. GRM36CH180J50PT 1 1

C61 CU3514 Chip C. GRM36CH180J50PT 1 1

C62 CE0339 Electrolytic C. 16MV 10SWB+TS 1 1

C63 CU4015 Chip C. GRM42-6CH220J500PT 1 1

C64 CU3535 Chip C. GRM36B102K50PT 1 1

C65 CS0424 Chip Tantalum TMCMA1C106MTR 1 1

C66 CU3503 Chip C. GRM36CK020C50PT 1 1

C67 CU3535 Chip C. GRM36B102K50PT 1 1

C68 CU3019 Chip C. C1608CH1H470JT-AS 1 1

C69 CU3530 Chip C. GRM36B391K50PT 1 1

C70 CE0339 Electrolytic C. 16MV 10SWB+TS 1 1

C71 CU3011 Chip C. C1608CH1H100DT-AS 1 1

C72 CU3012 Chip C. C1608CH1H120JT-AS 1 1

C73 CU3015 Chip C. C1608CH1H220JT-AS 1 1

C74 CU3035 Chip C. C1608JB1H102KT-AS 1 1

C75 CU3514 Chip C. GRM36CH180J50PT 1 1

C76 CU3514 Chip C. GRM36CH180J50PT 1 1

C78 CU3531 Chip C. GRM36B471K50PT 1 1

C79 CU3535 Chip C. GRM36B102K50PT 1 1

C80 CU3535 Chip C. GRM36B102K50PT 1 1

C81 CU3511 Chip C. GRM36CH100D50PT 1 1

C82 CU3547 Chip C. GRM36B103K16PT 1 1

C83 CU3535 Chip C. GRM36B102K50PT 1 1

C84 CU3035 Chip C. C1608JB1H102KT-AS 1 1

C85 CU3035 Chip C. C1608JB1H102KT-AS 1 1

Qty

31

Page 32

Ref.

Parts No. Description Parts Name

No. (T) (E)

C86 CU3535 Chip C. GRM36B102K50PT 1 1

C87 CU3035 Chip C. C1608JB1H102KT-AS 1 1

C88 CU3035 Chip C. C1608JB1H102KT-AS 1 1

C89 CU3111 Chip C. C1608JB1C104KT-N 1 1

C91 CU3502 Chip C. GRM36CK010C50PT 1 1

C92 CU3547 Chip C. GRM36B103K16PT 1 1

C93 CU3035 Chip C. C1608JB1H102KT-AS 1 1

C94 CU3511 Chip C. GRM36CH100D50PT 1 1

C95 CU3111 Chip C. C1608JB1C104KT-N 1 1

C96 CU3035 Chip C. C1608JB1H102KT-AS 1 1

C97 CU3535 Chip C. GRM36B102K50PT 1 1

C98 CS0220 Chip Tantalum TMCMA1C225MTR 1 1

C99 CU3035 Chip C. C1608JB1H102KT-AS 1 1

C100 CU3035 Chip C. C1608JB1H102KT-AS 1 1

C101 CU3535 Chip C. GRM36B102K50PT 1 1

C102 CU3506 Chip C. GRM36CH050C50PT 1 1

C103 CU4019 Chip C. GRM42-6CH470J500PT 1 1

C104 CS0220 Chip Tantalum TMCMA1C225MTR 1 1

C105 CU3512 Chip C. GRM36CH120J50PT 1 1

C106 CU4008 Chip C. GRM42-6CH070D500PT 1 1

C107 CU3551 Chip C. GRM36B223K16PT 1 1

C108 CU3035 Chip C. C1608JB1H102KT-AS 1 1

C109 CU3535 Chip C. GRM36B102K50PT 1 1

C110 CU3547 Chip C. GRM36B103K16PT 1 1

C111 CU0002 Chip C. C2012CH1H010CT-A 1 1

C112 CU4006 Chip C. GRM42-6CH050C500PT 1 1

C113 CU3502 Chip C. GRM36CK010C50PT 1 1

C114 CS0063 Chip Tantalum TMCSA1V104MTR 1 1

C115 CU3004 Chip C. C1608CH1H030CT-AS 1 0

C115 CU3005 Chip C. C1608CH1H040CT-AS 0 1

C116 CU4010 Chip C. GRM42-6CH090D500PT 1 1

C117 CU4007 Chip C. GRM42-6CH060D500PT 1 1

C118 CU3547 Chip C. GRM36B103K16PT 1 1

C119 CE0420 Electrolytic C. 16MV22SZ 1 1

C120 CU3535 Chip C. GRM36B102K50PT 1 1

C121 CU3535 Chip C. GRM36B102K50PT 1 1

C122 CU3535 Chip C. GRM36B102K50PT 1 1

C123 CU3035 Chip C. C1608JB1H102KT-AS 1 1

C124 CU4006 Chip C. GRM42-6CH050C500PT 1 1

C125 CU4001 Chip C. GRM42-6CK010C500PT 1 1

C126 CU4007 Chip C. GRM42-6CH060D500PT 1 1

C127 CU4005 Chip C. GRM42-6CH040C500PT 1 1

C128 CU3511 Chip C. GRM36CH100D50PT 1 1

C129 CU3001 Chip C. C1608CH1H0R5CT-AS 1 1

C130 CU3001 Chip C. C1608CH1H0R5CT-AS 1 1

C131 CU4019 Chip C. GRM42-6CH470J500PT 1 1

C132 CU3535 Chip C. GRM36B102K50PT 1 1

C133 CU3035 Chip C. C1608JB1H102KT-AS 1 1

C134 CU3035 Chip C. C1608JB1H102KT-AS 1 1

C135 CS0063 Chip Tantalum TMCSA1V104MTR 1 1

C136 CU3531 Chip C. GRM36B471K50PT 1 1

C137 CU3535 Chip C. GRM36B102K50PT 1 1

C138 CU3523 Chip C. GRM36CH101J50PT 1 1

C139 CU3035 Chip C. C1608JB1H102KT-AS 1 1

C141 CU3035 Chip C. C1608JB1H102KT-AS 1 1

C142 CU3523 Chip C. GRM36CH101J50PT 1 1

C143 CU3035 Chip C. C1608JB1H102KT-AS 1 1

C144 CU3035 Chip C. C1608JB1H102KT-AS 1 1

C145 CU3535 Chip C. GRM36B102K50PT 1 1

C146 CU3535 Chip C. GRM36B102K50PT 1 1

C147 CU3523 Chip C. GRM36CH101J50PT 1 1

C148 CU3547 Chip C. GRM36B103K16PT 1 1

C149 CU3535 Chip C. GRM36B102K50PT 1 1

C150 CU3111 Chip C. C1608JB1C104KT-N 1 1

Qty

Ref.

Parts No. Description Parts Name

No. (T) (E)

C151 CU3523 Chip C. GRM36CH101J50PT 1 1

C152 CU3547 Chip C. GRM36B103K16PT 1 1

C153 CU3512 Chip C. GRM36CH120J50PT 1 1

C154 CU3007 Chip C. C1608CH1H060CT-A 1 1

C155 CU3535 Chip C. GRM36B102K50PT 1 1

C156 CU3023 Chip C. C1608CH1H101JT-AS 1 1

C157 CU3006 Chip C. C1608CH1H050CT-AS 1 1

C159 CU3506 Chip C. GRM36CH050C50PT 1 1

C160 CU3007 Chip C. C1608CH1H060CT-A 1 1

C161 CU3035 Chip C. C1608JB1H102KT-AS 1 1

C162 CU3508 Chip C. GRM36CH070D50PT 1 1

C163 CU3504 Chip C. GRM36CJ030C50PT 1 1

C164 CU3547 Chip C. GRM36B103K16PT 1 1

C165 CU3503 Chip C. GRM36CK020C50PT 1 1

C166 CU3535 Chip C. GRM36B102K50PT 1 1

C167 CU3535 Chip C. GRM36B102K50PT 1 1

C168 CU3535 Chip C. GRM36B102K50PT 1 1

C169 CU3547 Chip C. GRM36B103K16PT 1 1

C170 CU3513 Chip C. GRM36CH150J50PT 1 1

C171 CU3547 Chip C. GRM36B103K16PT 1 1

C173 CU3515 Chip C. GRM36CH220J50PT 1 1

C174 CU3511 Chip C. GRM36CH100D50PT 1 1

C175 CU3511 Chip C. GRM36CH100D50PT 1 1

C176 CS0237 Chip Tantalum TMCMA1A475MTR 1 1

C177 CU3503 Chip C. GRM36CK020C50PT 1 1

C178 CU3515 Chip C. GRM36CH220J50PT 1 1

C179 CU3503 Chip C. GRM36CJ020C50PT 1 1

C180 CU3502 Chip C. GRM36CK010C50PT 1 1

C181 CU3502 Chip C. GRM36CK010C50PT 1 1

C182 CU3512 Chip C. GRM36CH120J50PT 1 1

C183 CU3535 Chip C. GRM36B102K50PT 1 1

C184 CU3529 Chip C. GRM36B331K50PT 1 1

C185 CU3527 Chip C. GRM36CH221J25PT 1 1

C186 CU3111 Chip C. C1608JB1C104KT-N 1 1

C187 CU3535 Chip C. GRM36B102K50PT 1 1

C188 CU3513 Chip C. GRM36CH150J50PT 1 1

C189 CU3516 Chip C. GRM36CH270J50PT 1 1

C190 CU3523 Chip C. GRM36CH101J50PT 1 1

C191 CU3504 Chip C. GRM36CJ030C50PT 1 1

C192 CU3535 Chip C. GRM36B102K50PT 1 1

C193 CU3513 Chip C. GRM36CH150J50PT 1 1

C194 CU3511 Chip C. GRM36CH100D50PT 1 1

C195 CU3511 Chip C. GRM36CH100D50PT 1 1

C196 CS0049 Chip Tantalum TMCSA1C105MTR 1 1

C197 CS0063 Chip Tantalum TMCSA1V104MTR 1 1

C198 CU3535 Chip C. GRM36B102K50PT 1 1

C199 CU3515 Chip C. GRM36CH220J50PT 1 1

C200 CU3517 Chip C. GRM36CH330J50PT 1 1

C201 CU3519 Chip C. GRM36CH470J50PT 1 1

C202 CU3507 Chip C. GRM36CH060D50PT 1 1

C203 CU3547 Chip C. GRM36B103K16PT 1 1

C205 CU3517 Chip C. GRM36CH330J50PT 1 1

C206 CU3547 Chip C. GRM36B103K16PT 1 1

C207 CU3535 Chip C. GRM36B102K50PT 1 1

C208 CU3111 Chip C. C1608JB1C104KT-N 1 1

C209 CU3111 Chip C. C1608JB1C104KT-N 1 1

C210 CU3111 Chip C. C1608JB1C104KT-N 1 1

C211 CU3547 Chip C. GRM36B103K16PT 1 1

C213 CU3535 Chip C. GRM36B102K50PT 1 1

C214 CU3535 Chip C. GRM36B102K50PT 1 1

C215 CU3535 Chip C. GRM36B102K50PT 1 1

C216 CU3517 Chip C. GRM36CH330J50PT 1 1

C218 CU3517 Chip C. GRM36CH330J50PT 1 1

C219 CU3517 Chip C. GRM36CH330J50PT 1 1

Qty

32

Page 33

Ref.

Parts No. Description Parts Name

No. (T) (E)

C220 CU3535 Chip C. GRM36B102K50PT 1 1

C221 CU3547 Chip C. GRM36B103K16PT 1 1

C222 CU3535 Chip C. GRM36B102K50PT 1 1

C223 CU3535 Chip C. GRM36B102K50PT 1 1

C224 CU3111 Chip C. C1608JB1C104KT-N 1 1

C225 CU3535 Chip C. GRM36B102K50PT 1 1

C226 CU3515 Chip C. GRM36CH220J50PT 1 1

C227 CU3111 Chip C. C1608JB1C104KT-N 1 1

C228 CU3511 Chip C. GRM36CH100D50PT 1 1

C229 CU3111 Chip C. C1608JB1C104KT-N 1 1

C230 CU3111 Chip C. C1608JB1C104KT-N 1 1

C231 CU3111 Chip C. C1608JB1C104KT-N 1 1

C232 CU3111 Chip C. C1608JB1C104KT-N 1 1

C233 CU3111 Chip C. C1608JB1C104KT-N 1 1

C234 CU3111 Chip C. C1608JB1C104KT-N 1 1

C235 CU3111 Chip C. C1608JB1C104KT-N 1 1

C236 CU0108 Chip C. LMK212BJ105KG 1 1

C237 CU3535 Chip C. GRM36B102K50PT 1 1

C238 CU3551 Chip C. GRM36B223K16PT 1 1

C239 CU3535 Chip C. GRM36B102K50PT 1 1

C240 CU3531 Chip C. GRM36B471K50PT 1 1

C242 CU3523 Chip C. GRM36CH101J50PT 1 1

C243 CU3503 Chip C. GRM36CK020C50PT 1 1

C244 CU3535 Chip C. GRM36B102K50PT 1 1

C245 CS0424 Chip Tantalum TMCMA1C106MTR 1 1

C246 CU3535 Chip C. GRM36B102K50PT 1 1

C247 CU3506 Chip C. GRM36CH050C50PT 1 1

C248 CU3547 Chip C. GRM36B103K16PT 1 1

C249 CU3511 Chip C. GRM36CH100D50PT 1 1

C250 CU3531 Chip C. GRM36B471K50PT 1 1

C251 CU3502 Chip C. GRM36CK010C50PT 1 1

C252 CU3519 Chip C. GRM36CH470J50PT 1 1

C253 CS0424 Chip Tantalum TMCMA1C106MTR 1 1

C254 CU3547 Chip C. GRM36B103K16PT 1 1

C255 CS0220 Chip Tantalum TMCMA1C225MTR 1 1

C256 CU3547 Chip C. GRM36B103K16PT 1 1

C257 CS0220 Chip Tantalum TMCMA1C225MTR 1 1

C258 CU3535 Chip C. GRM36B102K50PT 1 1

C259 CU3515 Chip C. GRM36CH220J50PT 1 1

C260 CU3514 Chip C. GRM36CH180J50PT 1 1

C261 CU3535 Chip C. GRM36B102K50PT 1 1

C262 CU3111 Chip C. C1608JB1C104KT-N 1 1

C263 CU3523 Chip C. GRM36CH101J50PT 1 1

C264 CU3535 Chip C. GRM36B102K50PT 1 1

C265 CS0063 Chip Tantalum TMCSA1V104MTR 1 1

C266 CU3524 Chip C. GRM36CH121J50PT 1 1

C267 CU3547 Chip C. GRM36B103K16PT 1 1

C268 CU3515 Chip C. GRM36CH220J50PT 1 1

C269 CU3519 Chip C. GRM36CH470J50PT 1 1

C270 CU3516 Chip C. GRM36CH270J50PT 1 1

C271 CU3535 Chip C. GRM36B102K50PT 1 1

C272 CU3535 Chip C. GRM36B102K50PT 1 1

C273 CU3504 Chip C. GRM36CJ030C50PT 1 1

C274 CU3535 Chip C. GRM36B102K50PT 1 1

C275 CU3535 Chip C. GRM36B102K50PT 1 1

C276 CU3535 Chip C. GRM36B102K50PT 1 1

C278 CU3513 Chip C. GRM36CH150J50PT 1 1

C279 CU3535 Chip C. GRM36B102K50PT 1 1

C280 CU3547 Chip C. GRM36B103K16PT 1 1

C281 CU3514 Chip C. GRM36CH180J50PT 1 1

C282 CU3518 Chip C. GRM36CH390J50PT 1 1

C283 CU3524 Chip C. GRM36CH121J50PT 1 1

C284 CU3504 Chip C. GRM36CJ030C50PT 1 1

C285 CU3524 Chip C. GRM36CH121J50PT 1 1

Qty

Ref.

Parts No. Description Parts Name

No. (T) (E)

C286 CU3511 Chip C. GRM36CH100D50PT 1 1

C287 CU3547 Chip C. GRM36B103K16PT 1 1

C288 CU3547 Chip C. GRM36B103K16PT 1 1

C289 CU3535 Chip C. GRM36B102K50PT 1 1

C290 CU3518 Chip C. GRM36CH390J50PT 1 1

C291 CU3535 Chip C. GRM36B102K50PT 1 1

C292 CU3518 Chip C. GRM36CH390J50PT 1 1

C293 CU3506 Chip C. GRM36CH050C50PT 1 1

C294 CU3514 Chip C. GRM36CH180J50PT 1 1

C295 CU3547 Chip C. GRM36B103K16PT 1 1

C296 CU3547 Chip C. GRM36B103K16PT 1 1

C298 CU3547 Chip C. GRM36B103K16PT 1 1

C300 CU3512 Chip C. GRM36CH120J50PT 1 1

C301 CU3535 Chip C. GRM36B102K50PT 1 1

C302 CU3535 Chip C. GRM36B102K50PT 1 1

C303 CU3535 Chip C. GRM36B102K50PT 1 1

C305 CU3511 Chip C. GRM36CH100D50PT 1 1

C306 CU3547 Chip C. GRM36B103K16PT 1 1

C308 CU3535 Chip C. GRM36B102K50PT 1 1

C309 CU3535 Chip C. GRM36B102K50PT 1 1

C310 CU3547 Chip C. GRM36B103K16PT 1 1

C311 CU3535 Chip C. GRM36B102K50PT 1 1

C312 CU3511 Chip C. GRM36CH100D50PT 1 1

C313 CU3502 Chip C. GRM36CK010C50PT 1 1

C314 CU3535 Chip C. GRM36B102K50PT 1 1

C315 CU3503 Chip C. GRM36CK020C50PT 1 1

C316 CU0108 Chip C. LMK212BJ105KG 1 1

C317 CU3535 Chip C. GRM36B102K50PT 1 1

C318 CS0063 Chip Tantalum TMCSA1V104MTR 1 1

C319 CU3111 Chip C. C1608JB1C104KT-N 1 1

C320 CU3502 Chip C. GRM36CK010C50PT 1 1

C321 CU3547 Chip C. GRM36B103K16PT 1 1

C322 CU3547 Chip C. GRM36B103K16PT 1 1

C323 CU3511 Chip C. GRM36CH100D50PT 1 1

C324 CU0108 Chip C. LMK212BJ105KG 1 1

C325 CU0071 Chip C. C2012CH1H101JT-A/M 1 1

C326 CU3507 Chip C. GRM36CH060D50PT 1 1

C327 CU3511 Chip C. GRM36CH100D50PT 1 1

C328 CU3508 Chip C. GRM36CH070D50PT 1 1

C329 CU3512 Chip C. GRM36CH120J50PT 1 1

C330 CU3507 Chip C. GRM36CH060D50PT 1 1

C331 CU3515 Chip C. GRM36CH220J50PT 1 1

C332 CU3535 Chip C. GRM36B102K50PT 1 1

C333 CU3111 Chip C. C1608JB1C104KT-N 1 1

C334 CU3505 Chip C. GRM36CH040C50PT 1 1

C335 CU3511 Chip C. GRM36CH100D50PT 1 1

C337 CU3111 Chip C. C1608JB1C104KT-N 1 1

C338 CU3512 Chip C. GRM36CH120J50PT 1 1

C339 CS0237 Chip Tantalum TMCMA1A475MTR 1 1

C340 CU3508 Chip C. GRM36CH070D50PT 1 1

C342 CU3547 Chip C. GRM36B103K16PT 1 1

C344 CU3507 Chip C. GRM36CH060D50PT 1 1

C345 CU3535 Chip C. GRM36B102K50PT 1 1

C346 CU3535 Chip C. GRM36B102K50PT 1 1

C347 CU3111 Chip C. C1608JB1C104KT-N 1 1

C348 CU3535 Chip C. GRM36B102K50PT 1 1

C349 CU3523 Chip C. GRM36CH101J50PT 1 1

C350 CU3535 Chip C. GRM36B102K50PT 1 1

C353 CU3504 Chip C. GRM36CJ030C50PT 1 1

C354 CU3547 Chip C. GRM36B103K16PT 1 1

C355 CU3535 Chip C. GRM36B102K50PT 1 1

C356 CU3547 Chip C. GRM36B103K16PT 1 1

C357 CU3547 Chip C. GRM36B103K16PT 1 1

C358 CU3535 Chip C. GRM36B102K50PT 1 1

Qty

33

Page 34

Ref.

Parts No. Description Parts Name

No. (T) (E)

C359 CU3522 Chip C. GRM36CH820J50PT 1 1

C360 CU3551 Chip C. GRM36B223K16PT 1 1

C361 CU3527 Chip C. GRM36CH221J25PT 1 1

C362 CS0424 Chip Tantalum TMCMA1C106MTR 1 1

C363 CU3535 Chip C. GRM36B102K50PT 1 1

C364 CS0237 Chip Tantalum TMCMA1A475MTR 1 1

C365 CS0424 Chip Tantalum TMCMA1C106MTR 1 1

C366 CU3535 Chip C. GRM36B102K50PT 1 1

C367 CU3511 Chip C. GRM36CH100D50PT 1 1

C368 CU3111 Chip C. C1608JB1C104KT-N 1 1

C369 CU3111 Chip C. C1608JB1C104KT-N 1 1

C370 CU3535 Chip C. GRM36B102K50PT 1 1

C371 CU3543 Chip C. GRM36B472K25PT 1 1

C372 CU3527 Chip C. GRM36CH221J25PT 1 1

C373 CU3111 Chip C. C1608JB1C104KT-N 1 1

C374 CU3111 Chip C. C1608JB1C104KT-N 1 1

C375 CU3547 Chip C. GRM36B103K16PT 1 1

C376 CU3535 Chip C. GRM36B102K50PT 1 1

C377 CU3547 Chip C. GRM36B103K16PT 1 1

C378 CU3101 Chip C. C1608JB1C473KT-NS 1 1

C379 CU3111 Chip C. C1608JB1C104KT-N 1 1

C380 CU3511 Chip C. GRM36CH100D50PT 1 1

C381 CU3509 Chip C. GRM36CH080D50PT 1 1

C382 CU3505 Chip C. GRM36CH040C50PT 1 1

C383 CU3523 Chip C. GRM36CH101J50PT 1 1

C384 CU3520 Chip C. GRM36CH560J50PT 1 1

C386 CU3526 Chip C. GRM36CH181J25PT 1 1

C387 CU3047 Chip C. C1608JB1H103KT-N 1 1

C389 CU3538 Chip C. GRM36B182K50PT 1 1

C390 CU3523 Chip C. GRM36CH101J50PT 1 1

C391 CU3503 Chip C. GRM36CK020C50PT 1 1

C392 CU3512 Chip C. GRM36CH120J50PT 1 1

C393 CU3506 Chip C. GRM36CH050C50PT 1 1

C394 CU3507 Chip C. GRM36CH060D50PT 1 1

C395 CU3535 Chip C. GRM36B102K50PT 1 1

C396 CU3547 Chip C. GRM36B103K16PT 1 1

C397 CU3535 Chip C. GRM36B102K50PT 1 1

C398 CU3504 Chip C. GRM36CJ030C50PT 1 1

C399 CU3535 Chip C. GRM36B102K50PT 1 1

C401 CU3505 Chip C. GRM36CH040C50PT 1 1

C402 CU3511 Chip C. GRM36CH100D50PT 1 1

C403 CU3111 Chip C. C1608JB1C104KT-N 1 1

C404 CU3547 Chip C. GRM36B103K16PT 1 1

C405 CU3505 Chip C. GRM36CH040C50PT 1 1

C406 CU3511 Chip C. GRM36CH100D50PT 1 1

C407 CS0424 Chip Tantalum TMCMA1C106MTR 1 1

C408 CU3102 Chip C. C1608JB1C333KT-NS 1 1

C409 CU3549 Chip C. GRM36B153K16PT 1 1

C410 CU3111 Chip C. C1608JB1C104KT-N 1 1

C411 CU3535 Chip C. GRM36B102K50PT 1 1

C412 CU3111 Chip C. C1608JB1C104KT-N 1 1

C413 CU3549 Chip C. GRM36B153K16PT 1 1

C414 CU3535 Chip C. GRM36B102K50PT 1 1

C415 CU3523 Chip C. GRM36CH101J50PT 1 1

C416 CU3523 Chip C. GRM36CH101J50PT 1 1

C417 CU0002 Chip C. C2012CH1H010CT-A 1 1

C418 CU3503 Chip C. GRM36CK020C50PT 1 1

C419 CU3504 Chip C. GRM36CJ030C50PT 1 1

C420 CU3506 Chip C. GRM36CH050C50PT 1 1

C421 CU3506 Chip C. GRM36CH050C50PT 1 1

C422 CU3506 Chip C. GRM36CH050C50PT 1 1

C423 CU3503 Chip C. GRM36CK020C50PT 1 1

C425 CU3506 Chip C. GRM36CH050C50PT 1 1

C426 CU3503 Chip C. GRM36CK020C50PT 1 1

Qty

Ref.

Parts No. Description Parts Name

No. (T) (E)

C427 CU3535 Chip C. GRM36B102K50PT 1 1

C428 CU3512 Chip C. GRM36CH120J50PT 1 1

C429 CU3502 Chip C. GRM36CK010C50PT 1 1

C430 CU3535 Chip C. GRM36B102K50PT 1 1

C431 CS0237 Chip Tantalum TMCMA1A475MTR 1 1

C432 CU3535 Chip C. GRM36B102K50PT 1 1

C434 CU3503 Chip C. GRM36CK020C50PT 1 1

C435 CS0237 Chip Tantalum TMCMA1A475MTR 1 1

C436 CS0424 Chip Tantalum TMCMA1C106MTR 1 1

C437 CS0237 Chip Tantalum TMCMA1A475MTR 1 1

C438 CU3505 Chip C. GRM36CH040C50PT 1 1

C439 CS0424 Chip Tantalum TMCMA1C106MTR 1 1

C440 CU0108 Chip C. LMK212BJ105KG 1 1

C441 CU3535 Chip C. GRM36B102K50PT 1 1

C442 CE0364 Electrolytic C. 16MV 47SWB+TS 1 1

C443 CU3551 Chip C. GRM36B223K16PT 1 1

C444 CU3551 Chip C. GRM36B223K16PT 1 1

C445 CE0342 Electrolytic C. 16MV 470HC+TS 1 1

C446 CU0108 Chip C. LMK212BJ105KG 1 1

C447 CU3535 Chip C. GRM36B102K50PT 1 1

C448 CU0108 Chip C. LMK212BJ105KG 1 1

C449 CU3535 Chip C. GRM36B102K50PT 1 1

C450 CU3547 Chip C. GRM36B103K16PT 1 1

C451 CU3551 Chip C. GRM36B223K16PT 1 1

C453 CS0424 Chip Tantalum TMCMA1C106MTR 1 1

C454 CS0424 Chip Tantalum TMCMA1C106MTR 1 1

C455 CU3547 Chip C. GRM36B103K16PT 1 1

C456 CU3535 Chip C. GRM36B102K50PT 1 1

C457 CU3535 Chip C. GRM36B102K50PT 1 1

C458 CE0339 Electrolytic C. 16MV 10SWB+TS 1 1

C459 CS0423 Chip Tantalum TMCMB1C226MTR 1 1

C460 CE0100 Electrolytic C. 16MV 22UW 1 1

C461 CU3551 Chip C. GRM36B223K16PT 1 1

C462 CU3551 Chip C. GRM36B223K16PT 1 1

C463 CU3111 Chip C. C1608JB1C104KT-N 1 1

C464 CU3547 Chip C. GRM36B103K16PT 1 1

C465 CU3111 Chip C. C1608JB1C104KT-N 1 1

C466 CU3102 Chip C. C1608JB1C333KT-NS 1 1

C467 CU3535 Chip C. GRM36B102K50PT 1 1

C468 CU3035 Chip C. C1608JB1H102KT-AS 1 1

C469 CU3027 Chip C. C1608CH1H221JT-AS 1 1

C470 CE0418 Electrolytic C. 16MV2200CA 1 1

C471 CU3535 Chip C. GRM36B102K50PT 1 1

C472 CE0339 Electrolytic C. 16MV 10SWB+TS 1 1

C473 CE0364 Electrolytic C. 16MV 47SWB+TS 1 1

C474 CU3535 Chip C. GRM36B102K50PT 1 1

C475 CU3551 Chip C. GRM36B223K16PT 1 1

C476 CU3549 Chip C. GRM36B153K16PT 1 1

C477 CS0424 Chip Tantalum TMCMA1C106MTR 1 1

C478 CU3547 Chip C. GRM36B103K16PT 1 1

C479 CU3535 Chip C. GRM36B102K50PT 1 1

C480 CE0364 Electrolytic C. 16MV 47SWB+TS 1 1

C481 CS0049 Chip Tantalum TMCSA1C105MTR 1 1

C482 CU3047 Chip C. C1608JB1H103KT-N 1 1

C483 CU3541 Chip C. GRM36B332K50PT 1 1

C484 CU3538 Chip C. GRM36B182K50PT 1 1

C485 CU3544 Chip C. GRM36B562K25PT 1 1

C486 CU3540 Chip C. GRM36B272K50PT 1 1

C487 CU3535 Chip C. GRM36B102K50PT 1 1

C488 CS0049 Chip Tantalum TMCSA1C105MTR 1 1

C489 CU3551 Chip C. GRM36B223K16PT 1 1

C490 CU3544 Chip C. GRM36B562K25PT 1 1

C491 CU3542 Chip C. GRM36B392K50PT 1 1

C492 CU0108 Chip C. LMK212BJ105KG 1 1

Qty

34

Page 35

Ref.

Parts No. Description Parts Name

No. (T) (E)

C493 CU3551 Chip C. GRM36B223K16PT 1 1

C494 CU3549 Chip C. GRM36B153K16PT 1 1

C495 CS0049 Chip Tantalum TMCSA1C105MTR 1 1

C496 CU3547 Chip C. GRM36B103K16PT 1 1

C497 CU3047 Chip C. C1608JB1H103KT-N 1 1

C498 CU3047 Chip C. C1608JB1H103KT-N 1 1

C499 CU3531 Chip C. GRM36B471K50PT 1 1

C500 CS0424 Chip Tantalum TMCMA1C106MTR 1 1

C501 CU3551 Chip C. GRM36B223K16PT 1 1

C502 CU3111 Chip C. C1608JB1C104KT-N 1 1

C503 CU3535 Chip C. GRM36B102K50PT 1 1

C504 CE0364 Electrolytic C. 16MV 47SWB+TS 1 1

C505 CU3111 Chip C. C1608JB1C104KT-N 1 1

C506 CU3538 Chip C. GRM36B182K50PT 1 1

C507 CU3544 Chip C. GRM36B562K25PT 1 1

C508 CU3540 Chip C. GRM36B272K50PT 1 1

C509 CU3535 Chip C. GRM36B102K50PT 1 1

C510 CU3541 Chip C. GRM36B332K50PT 1 1

C511 CU3551 Chip C. GRM36B223K16PT 1 1

C512 CU3551 Chip C. GRM36B223K16PT 1 1

C513 CU3542 Chip C. GRM36B392K50PT 1 1

C514 CU3544 Chip C. GRM36B562K25PT 1 1

C515 CU3523 Chip C. GRM36CH101J50PT 1 1

C516 CU3111 Chip C. C1608JB1C104KT-N 1 1

C517 CS0424 Chip Tantalum TMCMA1C106MTR 1 1

C518 CU3111 Chip C. C1608JB1C104KT-N 1 1

C519 CU0108 Chip C. LMK212BJ105KG 1 1

C520 CU3506 Chip C. GRM36CH050C50PT 1 1

C521 CU3535 Chip C. GRM36B102K50PT 1 1

C522 CE0339 Electrolytic C. 16MV 10SWB+TS 1 1

C523 CU3511 Chip C. GRM36CH100D50PT 1 1

C524 CU3509 Chip C. GRM36CH080D50PT 1 1

C525 CU3527 Chip C. GRM36CH221J25PT 1 1

C527 CU3547 Chip C. GRM36B103K16PT 1 1

C530 CU3515 Chip C. GRM36CH220J50PT 1 1

C531 CU3535 Chip C. GRM36B102K50PT 1 1

C532 CU3535 Chip C. GRM36B102K50PT 1 1

C533 CS0424 Chip Tantalum TMCMA1C106MTR 1 1

C534 CS0424 Chip Tantalum TMCMA1C106MTR 1 1

C536 CU3502 Chip C. GRM36CK010C50PT 1 1

C537 CU3515 Chip C. GRM36CH220J50PT 1 1

C538 CU3535 Chip C. GRM36B102K50PT 1 1

C539 CU3506 Chip C. GRM36CH050C50PT 1 1

C540 CS0220 Chip Tantalum TMCMA1C225MTR 1 1

C541 CS0230 Chip Tantalum TMCMA1E105MTR 1 1

C542 CS0049 Chip Tantalum TMCSA1C105MTR 1 1

C543 CU3535 Chip C. GRM36B102K50PT 1 1

C545 CS0423 Chip Tantalum TMCMB1C226MTR 1 1

C546 CS0423 Chip Tantalum TMCMB1C226MTR 1 1

C547 CU3535 Chip C. GRM36B102K50PT 1 1

C548 CU3506 Chip C. GRM36CH050C50PT 1 1

C549 CU0108 Chip C. LMK212BJ105KG 1 1

C550 CU0108 Chip C. LMK212BJ105KG 1 1

C551 CU3535 Chip C. GRM36B102K50PT 1 1

C552 CU3551 Chip C. GRM36B223K16PT 1 1

C553 CU0108 Chip C. LMK212BJ105KG 1 1

C555 CU3017 Chip C. C1608CH1H330JT-AS 1 1

C556 CU3035 Chip C. C1608JB1H102KT-AS 1 1

C558 CU7047 Chip C. UC232H0330F-T 1 1

C559 CU4004 Chip C. GRM42-6CH050C300PT 1 0

C559 CU4006 Chip C. GRM42-6CH050C500PT 0 1

C560 CU4004 Chip C. GRM42-6CJ030C500PT 1 1

C561 CU3031 Chip C. C1608JB1H471KT-AS 1 1

C562 CE0341 Electrolytic C. 16MV 100HC+TS 1 1

Qty

Ref.

Parts No. Description Parts Name

No. (T) (E)

C563 CU3547 Chip C. GRM36B103K16PT 1 1

C567 CU3035 Chip C. C1608JB1H102KT-AS 1 1

C568 CU3011 Chip C. C1608CH1H100DT-AS 1 1

C569 CU3111 Chip C. C1608JB1C104KT-N 1 1

CN1 RD0108 Jumper J1/6Z 1 1

CN2 UJ0051 Jack HJC0212-01-022 1 1

CN3 UE0214 Connector AXN420C530P 1 1

CN4 UE0393 Connector PI28A11M 1 1

CN5 UE0043 Connector PI22A02M 1 1

CN6 UE0043 Connector PI22A02M 1 1

CN7 UA0037Y DC CABLE UA0037 1 1

CN8 UE0455 Connector PI28A10M 1 1

CN9 UE0226 Connector B2B-PH-K-S 1 1

CN10 UE0043 Connector PI22A02M 1 1

CN11 UE0043 Connector PI22A02M 1 1

D1 XD0013 Diode XB15A407AGB 1 1

D2 XD0320 Chip Diode DAN235E-TL 1 1

D3 XD0320 Chip Diode DAN235E-TL 1 1

D5 XD0320 Chip Diode DAN235E-TL 1 1

D6 XD0374 Chip Diode 1SV278 TPH2 1 1

D7 XD0342 Chip Diode 1SS390 TE61 1 1

D8 XD0375 Chip Diode MA4S713-TX 1 1

D9 XD0375 Chip Diode MA4S713-TX 1 1

D10 XD0376 Chip Diode 1SV282 TPH2 1 1

D11 XD0376 Chip Diode 1SV282 TPH2 1 1

D12 XD0373 Chip Diode UM9401F 1 1

D13 XD0373 Chip Diode UM9401F 1 1

D14 XD0331 Chip Diode HSU277TRF 1 1

D15 XD0331 Chip Diode HSU277TRF 1 1

D16 XD0331 Chip Diode HSU277TRF 1 1

D17 XD0320 Chip Diode DAN235E-TL 1 1

D18 XD0254 Chip Diode 1SS355 TE17 1 1

D19 XD0331 Chip Diode HSU277TRF 1 1

D20 XD0254 Chip Diode 1SS355 TE17 1 1

D21 XD0374 Chip Diode 1SV278 TPH2 1 1

D22 XD0375 Chip Diode MA4S713-TX 1 1

D23 XD0376 Chip Diode 1SV282 TPH2 1 1

D24 XD0374 Chip Diode 1SV278 TPH2 1 1

D25 XD0376 Chip Diode 1SV282 TPH2 1 1

D26 XD0320 Chip Diode DAN235E-TL 1 1

D27 XD0320 Chip Diode DAN235E-TL 1 1

D28 XD0314 Chip Diode HVU359TRF 1 1

D29 XD0314 Chip Diode HVU359TRF 1 1

D30 XD0314 Chip Diode HVU359TRF 1 1

D31 XD0377 Chip Diode MAZS0270HL 1 1

D32 XD0338 Chip Diode 1SS362(TE85L) 1 1

D33 XD0320 Chip Diode DAN235E-TL 1 1

D34 XD0342 Chip Diode 1SS390 TE61 1 1

D35 XD0374 Chip Diode 1SV278 TPH2 1 1

D37 XD0320 Chip Diode DAN235E-TL 1 1

D38 XD0374 Chip Diode 1SV278 TPH2 1 1

D39 XD0165 Chip Diode UDZSTE-17 5.1B 1 1

D40 XD0374 Chip Diode 1SV278 TPH2 1 1

D41 XD0342 Chip Diode 1SS390 TE61 1 1

D42 XD0250 Chip Diode MA742 TX 1 1

D43 XD0319 Chip Diode MA2S077-TX 1 1

D45 XD0323 Chip Diode MA2S111-TX 1 1

D46 XD0374 Chip Diode 1SV278 TPH2 1 1

D47 XD0374 Chip Diode 1SV278 TPH2 1 1

D48 XD0320 Chip Diode DAN235E-TL 1 1

D49 XD0314 Chip Diode HVU359TRF 1 1

D50 XD0314 Chip Diode HVU359TRF 1 1

D51 XD0314 Chip Diode HVU359TRF 1 1

D52 XD0314 Chip Diode HVU359TRF 1 1

Qty

35

Page 36

Ref.

Parts No. Description Parts Name

No. (T) (E)