Page 1

SERVICE MANUAL

Model:

PDP4216M Monitor

Safety Precaution

Technical Specifications

Block Diagram

Circuit Diagram

Basic Operations & Circuit Description

Main IC Specifications

Trouble Shooting Manual of PDP Module

Spare Part list

Exploded View

If You Forget Your V-CHIP Password

Software Upgrade

This manual is the latest at the time of printing, and does not

include the modification which may be made after the printing,

by the constant improvement of product.

Page 2

Safety Precaution

CAUTION

RISK OF ELECTRIC SHOCK

DO NOT OPEN

The lightning flash with arrowhead symbol,

within an equilateral triangle, is intended to

alert the user to the presence of uninsulated

“dangerous voltage” within the product’s enclo

sure that may be of sufficient magnitude to

constitute a risk of electric shock to persons.

CAUTION: TO REDUCE THE RISK OF

ELECTRIC SHOCK, DO NOT REMOVE COVER

(OR BACK). NO USER-SERVICEABLE PARTS

INSIDE. REFER SERVICING TO QUALIFIED

SERVICE PERSONNEL ONLY.

PRECAUTIONS DURING

SERVICING

1. In addition to safety, other parts and

assemblies are specified for conformance with

such regulations as those applying to spurious

radiation. These must also be replaced only

with specified replacements.

Examples: RF converters, tuner units, antenna

selection switches, RF cables, noise-blocking

capacitors, noise-blocking filters, etc.

2. Use specified internal Wiring. Note especially:

1) Wires covered with PVC tubing

2) Double insulated wires

3) High voltage leads

3. Use specified insulating materials for hazardous

live parts. Note especially:

1) Insulating Tape

2) PVC tubing

3) Spacers (insulating barriers)

4) Insulating sheets for transistors

5) Plastic screws for fixing micro switches

4. When replacing AC primary side components

(transformers, power cords, noise blocking

capacitors, etc.), wrap ends of wires securely

about the terminals before soldering.

5. Make sure that wires do not contact heat

generating parts (heat sinks, oxide metal film

resistors, fusible resistors, etc.)

6. Check if replaced wires do not contact sharply

edged or pointed parts.

7. Make sure that foreign objects (screws, solder

droplets, etc.) do not remain inside the set.

The exclamation point within an equilateral

triangle is intended to alert the user to the

presence of important operating and

maintenance (servicing) instructions in the

literature accompanying the appliance.

MAKE YOUR CONTRIBUTION

TO PROTECT THE

ENVIRONMENT

Used batteries with the ISO symbol

for recycling as well as small accumulators

(rechargeable batteries), mini-batteries (cells) and

starter batteries should not be thrown into the

garbage can.

Please leave them at an appropriate depot.

WARNING:

Before servicing this TV receiver, read the

SAFETY INSTRUCTION and PRODUCT

SAFETY NOTICE.

SAFETY INSTRUCTION

The service should not be attempted by anyone

unfamiliar with the necessary instructions on this

apparatus. The following are the necessary

instructions to be observed before servicing.

1. An isolation transformer should be connected in

the power line between the receiver and the

AC line when a service is performed on the

primary of the converter transformer of the set.

2. Comply with all caution and safety related

provided on the back of the cabinet, inside the

cabinet, on the chassis or picture tube.

3. To avoid a shock hazard, always discharge the

picture tube's anode to the chassis ground

before removing the anode cap.

4. Completely discharge the high potential voltage

of the picture tube before handling. The picture

tube is a vacuum and if broken, the glass will

explode.

Page 3

5. When replacing a MAIN PCB in the cabinet,

always be certain that all protective are

installed properly such as control knobs,

adjustment covers or shields, barriers, isolation

resistor networks etc.

6. When servicing is required, observe the original

lead dressing. Extra precaution should be given

to assure correct lead dressing in the high

voltage area.

7. Keep wires away from high voltage or high

tempera ture components.

8. Before returning the set to the customer,

always perform an AC leakage current check

on the exposed metallic parts of the cabinet,

such as antennas, terminals, screwheads,metal

overlay, control shafts, etc., to be sure the set

is safe to operate without danger of electrical

shock. Plug the AC line cord directly to the

AC outlet (do not use a line isolation

transformer during this check). Use an AC

voltmeter having 5K ohms volt sensitivity or

more in the following manner.

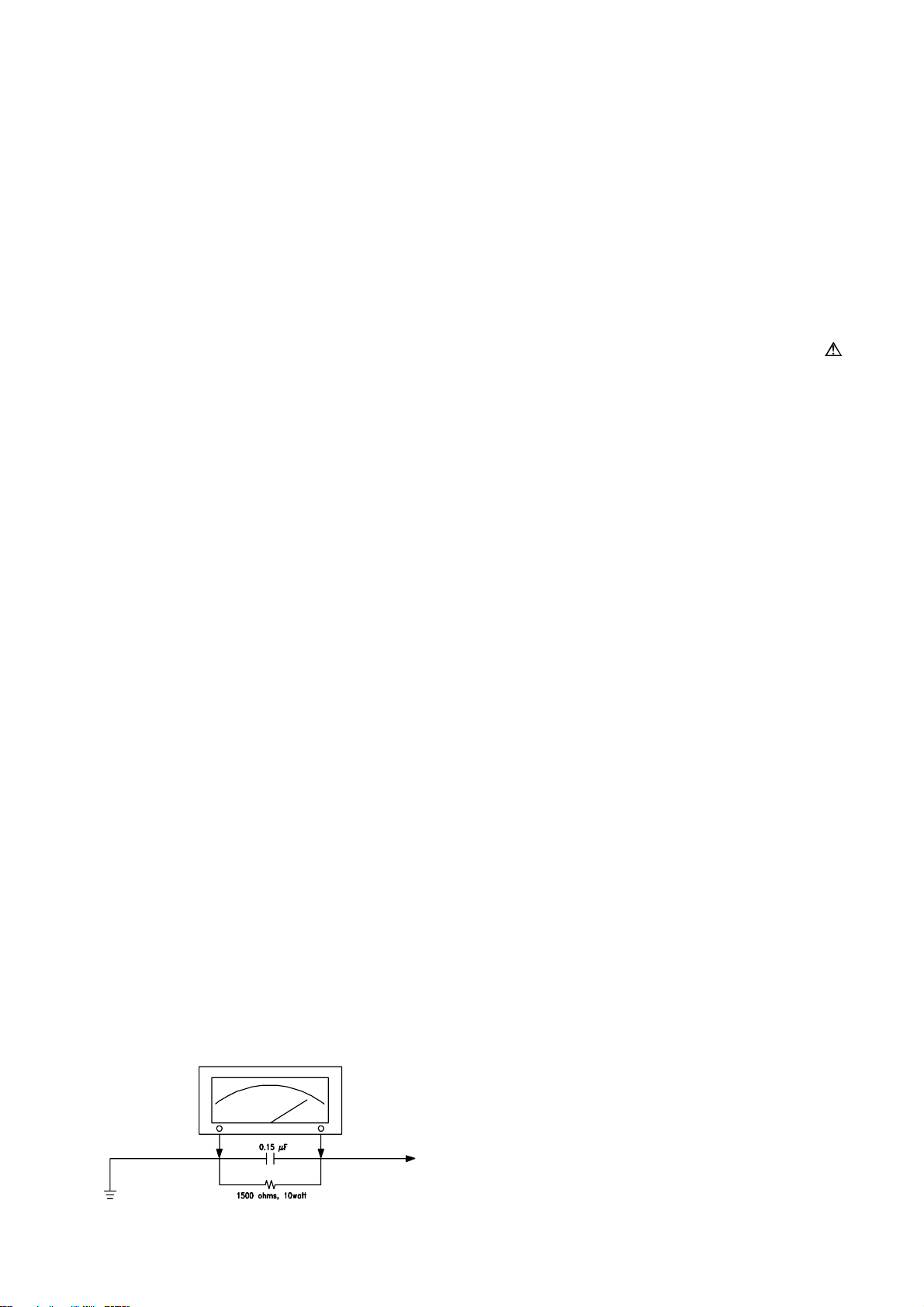

Connect a 1.5K ohm 10 watt resistor paralleled

by a 0.15µF AC type capacitor, between a

good earth ground (water pipe, conductor etc.,)

and the exposed metallic parts, one at a time.

Measure the AC voltage across the combination

of the 1.5K ohm resistor and 0.15 uF

capacitor. Reverse the AC plug at the AC

outlet and repeat the AC voltage measurements

for each exposed metallic part.

The measured voltage must not exceed 0.3V

RMS.

This corresponds to 0.5mA AC. Any value

exceeding this limit constitutes a potential

shock hazard and must be corrected

immediately.

The resistance measurement should be done

between accessible exposed metal parts and

power cord plug prongs with the power switch

"ON". The resistance should be more than

6M ohms.

AC VOLTMETER

PRODUCT SAFETY NOTICE

Many electrical and mechanical parts in this

apparatus have special safety-related

characteristics.

These characteristics are offer passed

unnoticed by visual spection and the protection

afforded by them cannot necessarily be obtained

by using replacement components rates for a

higher voltage, wattage, etc.

The replacement parts which have these

special safety characteristics are identified by

marks on the schematic diagram and on the parts

list.

Before replacing any of these components,

read the parts list in this manual carefully. The

use of substitute replacement parts which do not

have the same safety characteristics as specified

in the parts list may create shock, fire, or other

hazards.

9. Must be sure that the ground wire of the AC

inlet is connected with the ground of the

apparatus properly.

Good earth ground

such as the water

pipe, conductor,

etc.

AC Leakage Current Check

Place this probe

on each exposed

metallic part

Page 4

Technical Specifications

MODEL :

PDP4216M Monitor

42” Plasma Display

DATE FIRST ISSUED

10

ISSUE

1

RAISED BY

CHECKED BY

NUMBER OF PAGE

NOTE :

R & D DEPARTMENT

COMMERCIAL DEPARTMENT

PRODUCTION DEPARTMENT

Q/A DEPARTMENT

CUSTOMER

SIGNATURE :

Only documents stamped “Controlled Document” to be used for manufacture of production parts.

......................................................................................

......

......................................................................................

......

......................................................................................

.......

......................................................................................

.......

......................................................................................

.......

DATE :

...........................

...

...........................

...

...........................

...

...........................

...

...........................

...

Page 5

Technical Specifications

PDP4216M

CONTINUATION PAGE

NUMBER

2 OF 10 PAGES

1. Standard Test Conditions

All tests shall be performed under the following conditions, unless otherwise specified.

1.1 Ambient light

≦0.1Cd/m

: 150ux (When measuring IB, the ambient luminance

2

)

1.2 Viewing distance

: 50cm in front of PDP

1.3 Warm up time

: 30 minutes

1.4 PDP Panel facing

: no restricted

1.5 Measuring Equipment

: PC, Chroma 2225 signal generator (with Chroma digital

additional card) or equivalent, Minolta CA100 photometer

1.6 Magnetic field

: no restricted

1.7 Control settings

: Brightness, Contrast, Tint, Color set at Center(50)

1.8 Power input

: 100~120Vac 60Hz

1.9 Ambient temperature : 20°C ± 5°C (68°F ± 9°F)

1.10 Display mode

: Resolution 1024 x 768

1.11 Other conditions

:

1.11.1 With image sticking protection of PDP module, the luminance will descend

by time on a same still screen and rapidly go down in 5 minutes. When

measuring the color tracking and luminance of a same still screen, be sure t

o accomplish the measurement in one minute to ensure its accuracy.

1.11.2 Due to the structure of PDP, the extra-high-bright same screen should not

hold over 5 minutes for fear of branding on the panel.

Page 6

Technical Specifications

PDP4216M

CONTINUATION PAGE

NUMBER

3 OF 10 PAGES

ELECTRICAL CHARACTERISTICS

2. Power Input

2.1 Voltage

: 100 ~120VAC 60Hz

2.2 Input Current

: 5.0 /2.5A

2.3 Maximum Inrush Current

: <30 A (FOR AC110V ONLY)

Test condition : Measured when switched off for at least 20 mins

2.4 Frequency

: 50Hz to 60Hz(±3Hz)

2.5 Power Consumption

: 330W Typical

Test condition : full white display with maximum brightness and

contrast

2.6 Power Factor

: Meets IEC1000-3-2

2.7 Withstanding voltage

: 1.5kVac or 2.2kVdc for 1 sec

3. Display

3.1 Screen Size : 42” Plasma display

3.2 Aspect Ratio : 16:9

3.3 Pixel Resolution : 1024x768

3.4 Peak Brightness : 1000 cd/m² (Typical, Panel only)

3.5 Contrast Ratio (Dark room) : 5000:1 (Ratio, Typical, in a dark room, Panel only)

3.6 Viewing Angle : Over 160°

3.7 OSD language : English,Spanish,French

4. Signal

4.1 AV & Graphic input

4.1.1 Composite signal : CVBS

4.1.2 Y,C Signal : S-Video

4.1.3 Component signal : YPbPr x 2, HDMI,VGA compatible

4.1.4 Graphic I/P : Analog: D-sub 15pin detachable cable

Digital:HDMI

4.1.5EDID compatibility : DDC 1.3

4.1.6 I/P frequency : f

: 31.5kHz to 60kHz/f

H

: 56.25Hz to 75Hz(1024x768

V

recommended)

Page 7

Technical Specifications

4.2 Audio input VGA(D-Sub 15 Pin Type)×1

PDP4216M

CONTINUATION PAGE

NUMBER

4 OF 10 PAGES

D-Sub 9 Pin (RS-232 Input) × 1

HDMI (Ver. 1.1) connector × 1

S-Video (Mini Din 4 Pin) × 1

CVB Input (RCA Type) × 1

YPbPr × 2

Stereo/Audio × 6

4.3 Audio output Audio&Video Output (RCA Type) × 1 SPDIF (Optical) × 1

PIP/POP/PBP, Picture size, Picture Still, Sound mode,Last

memory, Timer, MTS

5. Environment

5.1 Operating environment

5.1.1 Temperature : 5º to 33°C

5.1.2 Relative humidity: 20% to 85%(non-condensing)

5.2 Storage and Transport

5.2.1 Temperature : -20°C to 60°C(-4º to 140°F)

5.2.2 Relative humidity: 5% to 95%

6. Panel Characteristics

6.1 Type : LGX2A

6.2 Size : 42”,1106.5mm(W)X622.1mm(H)

(W/Ostand)

6.3 Aspect ratio : 16:9

6.4 Viewing angle : Over 160°

6.5 Resolution : 1024X768

6.6 Weight : 22.0kg ±0.5 kg (Net)

6.7 Color : 16.7 millions of colors (R/G/B each 256 scales)

6.8 Contrast : Average 60:1 (In a bright room with 150Lux at center)

Typical 5000:1 (In a dark room 1/100 White Window

pattern at center).

6.9 Peak brightness : Typical 1000cd/㎡ (1/25 White Window)

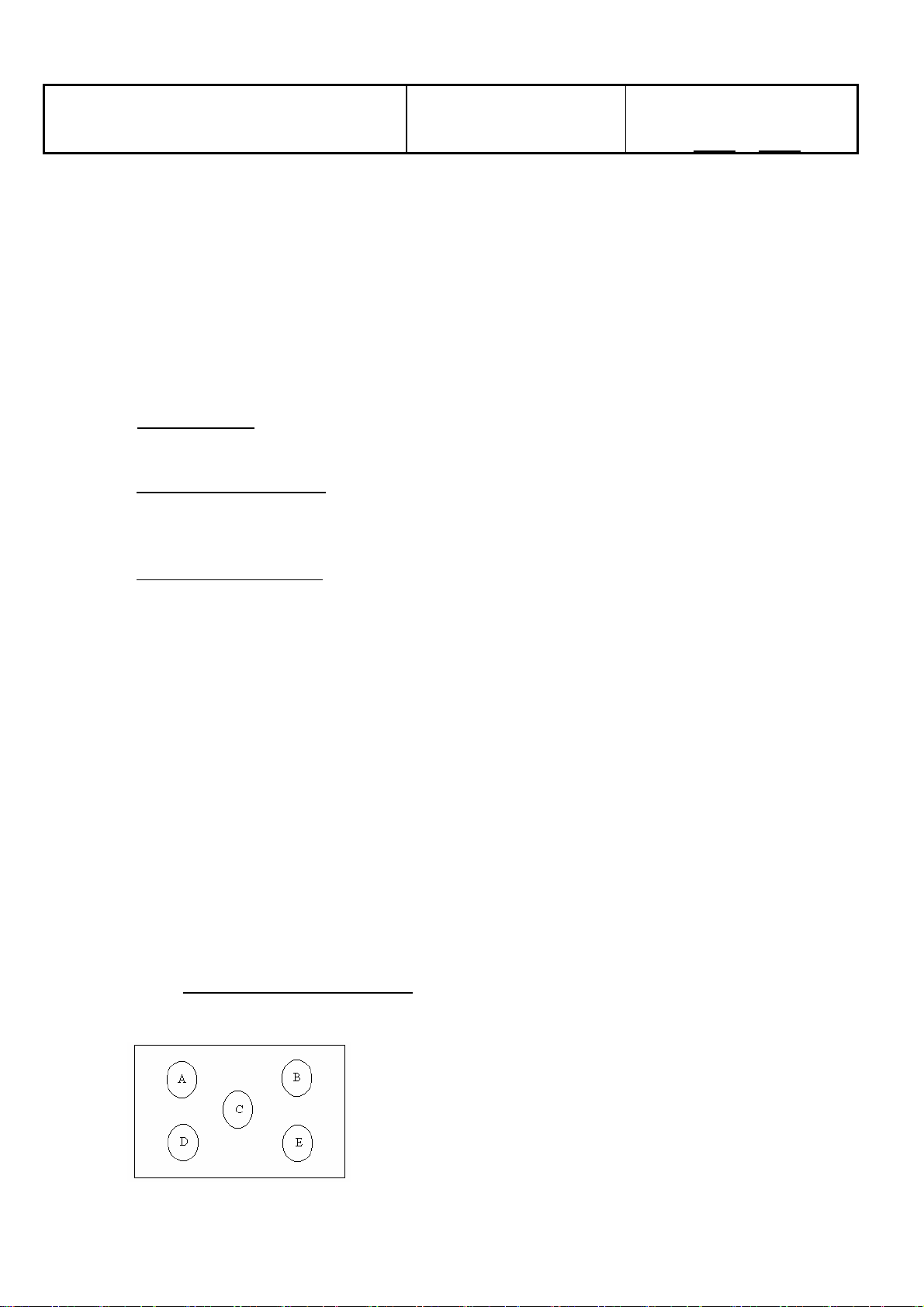

6.10 Color Coordinate Uniformity

: Contrast; Brightness and Color control at normal

setting

Test Pattern : Full white pattern

Average of point A,B,C,D and E +/- 0.01

Page 8

Technical Specifications

PDP4216M

CONTINUATION PAGE

NUMBER

5 OF 10 PAGES

6.11 Color temperature

: Contrast at center (50); Brightness center (50);

Color temperature set at Natural

x=0.285±0.02

y=0.290±0.02

6.12 Cell Defect Specifications

Subject to Panel supplier specification as appends.

7. Front Panel Control Button

7.1 SEL. Up / Down Button : Push the key to select Item up or down.

When selecting the item on OSD menu.

VOL. Left/Right Button : Push the key to increase the volume left or right.

When selecting the adjusting item on OSD menu

increase or decrease the data-bar.

MENU Button : Display or Exit the OSD menu.

Source Select Button : Press this button and use up/down button to sellect

the signal sources. AV, S-Video, YPbPr1,YPbPr2

VGA or HDMI.

7.2 STANDBY Button : Switch on main power, or switch off to enter power

Saving modes.

7.3 Main Power Switch : Turn on or off the unit.

8. OSD Function

8.1 Picture : Brightness; Contrast; Saturation; Phase; Frequency;

Picture Mode (Normal, Bright, Cinema, User);

Color Temp (Warm, Normal, Cool); etc.

8.2 Window : Image Size (Fill All, Force 4:3, Letter Box, Wide, Anamorphic, etc);

H Position; V Position; Freeze Window (Off, On)

8.3 Audio : Balance; Audio Mode (SRS TSXT, Cinema, Music, News, User)

Speaker (Internal, External); AVC (Off, On)

Equalizer (120Hz, 200Hz, 500Hz, 1.2kHz, 3kHz, 7.5kHz, 12kHz)

8.4 Options : Osd Timeout (5 Sec, 15 Sec, 60 Sec); Menu Background (Opaque,

Translucent); Language (English, French, Spanish); Default Setting;

Close Caption Mode (CC1, CC2, T1, T2, Xds); Close Caption (Off, On,

On Mute); Content Blocking; Timer

8.5 Layout : Full Screen; PIP; Split Screen

Page 9

Technical Specifications

PDP4216M

9. Agency Approvals

Safety UL/FCC/cUL

Emissions FCC class B

10. Reliability

11.1 MTBF

: 20,000 hours(Use moving picture signal at 25°C ambient)

11. Accessories : User manual x1, Remote control x1,

Stand x 1, Battery x 2, AC Cable x 1

CONTINUATION PAGE

NUMBER

6 OF 10 PAGES

Page 10

Technical Specifications

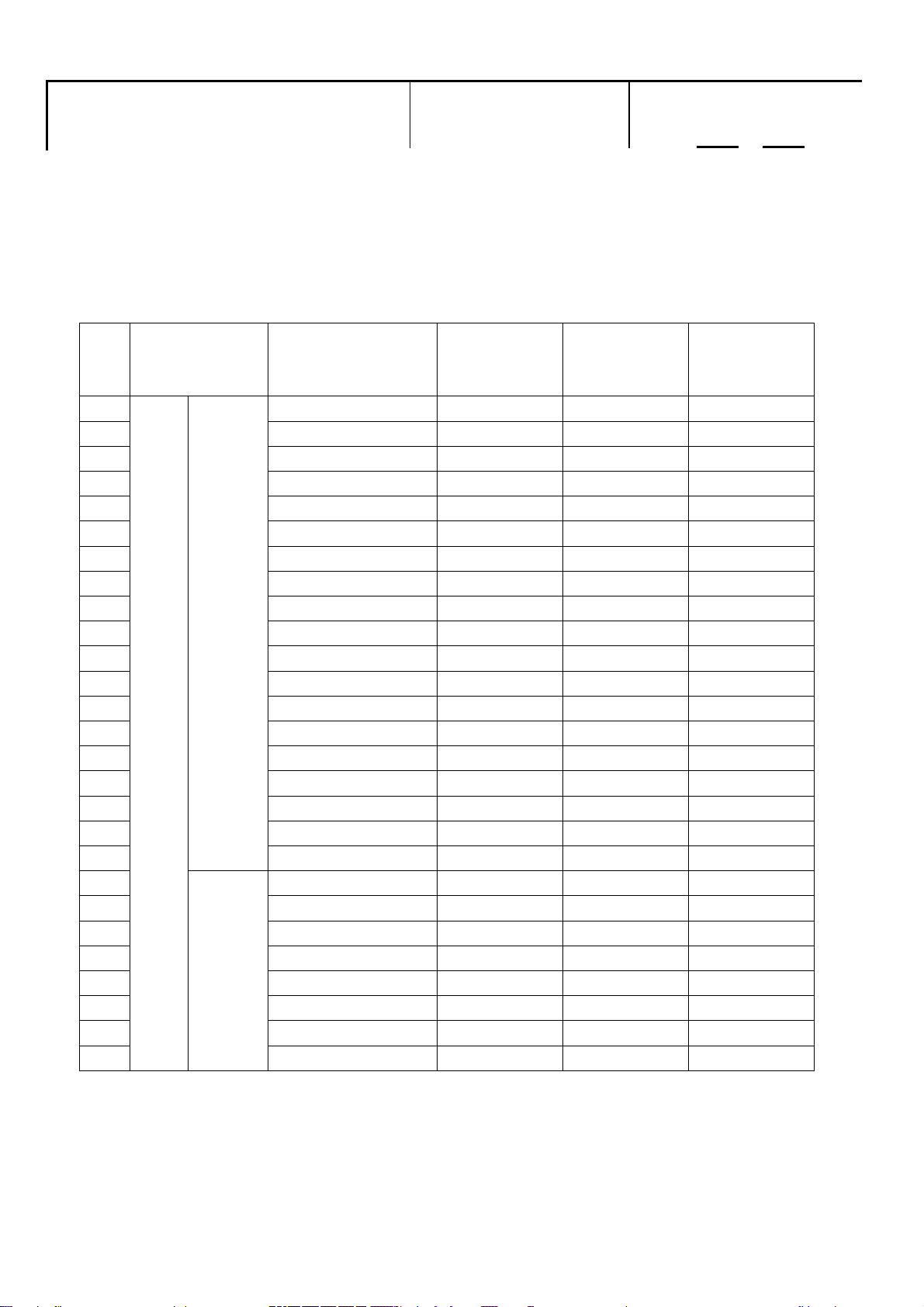

12. Support the Signal Mode

A. HDMI Mode / D-Sub Mode (VGA or DVI) / HDTV Mode (YpbPr1 or YpbPr2)

No Mode Resolution Horizontal

1 640x400 31.47 70.08 25.17

2 640x480 31.50 60.00 25.18

3 640x480 35.00 67.00 30.24

4 640x480 37.50 75.00 31.50

5 640x480 37.86 72.81 31.50

6 720x400 31.47 70.08 28.32

7 800x600 31.56 56.25 36.00

8 800x600 37.90 60.32 40.00

9 800x600 46.90 75.00 49.50

10 800x600 48.08 72.19 50.00

11 832x624 49.00 74.00 57.27

12 1024x768 48.84 60.00 65.00

13 1024x768 56.50 70.00 75.00

14 1024x768 60.00 75.00 78.75

15 1152x864 54.53 61.13 80.37

HDMI

Mode

16 1152x864 63.86 70.02 94.51

17 1152x864 67.52 75.02 108.03

18 1280x960 60.02 60.02 108.04

19

20 1080i (1920x1080) 33.75 60.00 74.25

21 1080i (1920x1080) 28.125 50.00 74.25

22 720P (1280x720) 45.00 60.00 74.25

23 720P (1280x720) 37.50 50.00 74.25

24 576p (720x576) 31.25 50.00 27.00

25 480p (720x480) 31.468 59.94 27.00

26 576i 15.625 50.00 13.50

27

D-Sub

Mode

(VGA or

DVI)

1280x1024 64.00 60.01 108.00

HDTV

Mode

(YpbPr1/

YpbPr2)

480i 15.734 59.94 13.50

PDP4216M

Frequency

(KHz)

NUMBER

Vertical

Frequency

(KHz)

CONTINUATION PAGE

7 OF 10 PAGES

Dot Clock

Frequency

(MHz)

Page 11

Technical Specifications

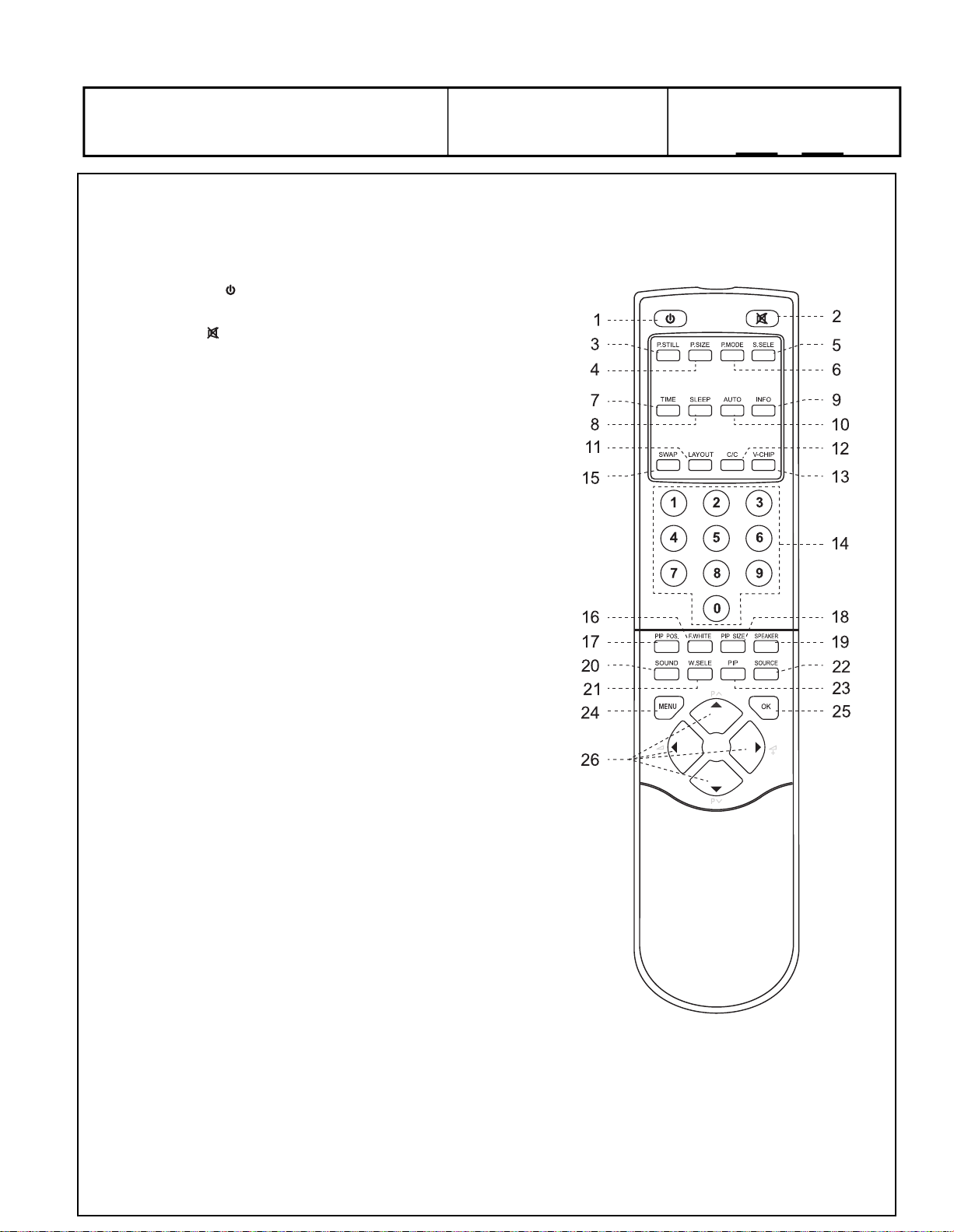

4.4 Remote Control

1 POWER( ): Press this button to turn off to

standby and turn on from standby.

2 MUTE(

system. Press again to reactivate the

sound system.

3 P.STILL: Press this button to hold on the

screen. Press again to normal.

4 P.SIZE: When the input source is

YPbPr 2, VGA or HDMI, press this button,

the picture will change according to Fill All,

Force 4:3, Letter Box, Wide or Anamorphic.

When the input source is AV or S-Video, press

this button, the picture will change according to

Fill All, 4:3, Letter Box, Wide or Anamorphic.

S.SELE: Press this button to select the sound

5

output from Main Window or Sub Window.

6 P.MODE : Press the button to select different

picture effect.

TIME: Press this button to pop up the “Clock

7

Set” menu.

SLEEP: Press this button to

8

time.

INFO: Press the button to display the

9

source information.

10 AUTO: The Display automatically adjusts the

phase, vertical / horizontal position when

pressing this button in VGA mode.

11 LAYOUT: Press this button to pop up Layout

menu.

12 C/C: Press this button to enter the Closed

Caption Function. (Only for AV or S-Video)

13 V-CHIP: Press this button to enter the V-Chip

Function. (Only for AV or S-Video)

14 Number buttons: Use these buttons to enter

the password.

): Press this button to quiet the sound

YPbPr 1,

select

the sleep

PDP4216M

CONTINUATION PAGE

NUMBER 8 OF

10

PAGES

(Continued on next page)

Page 12

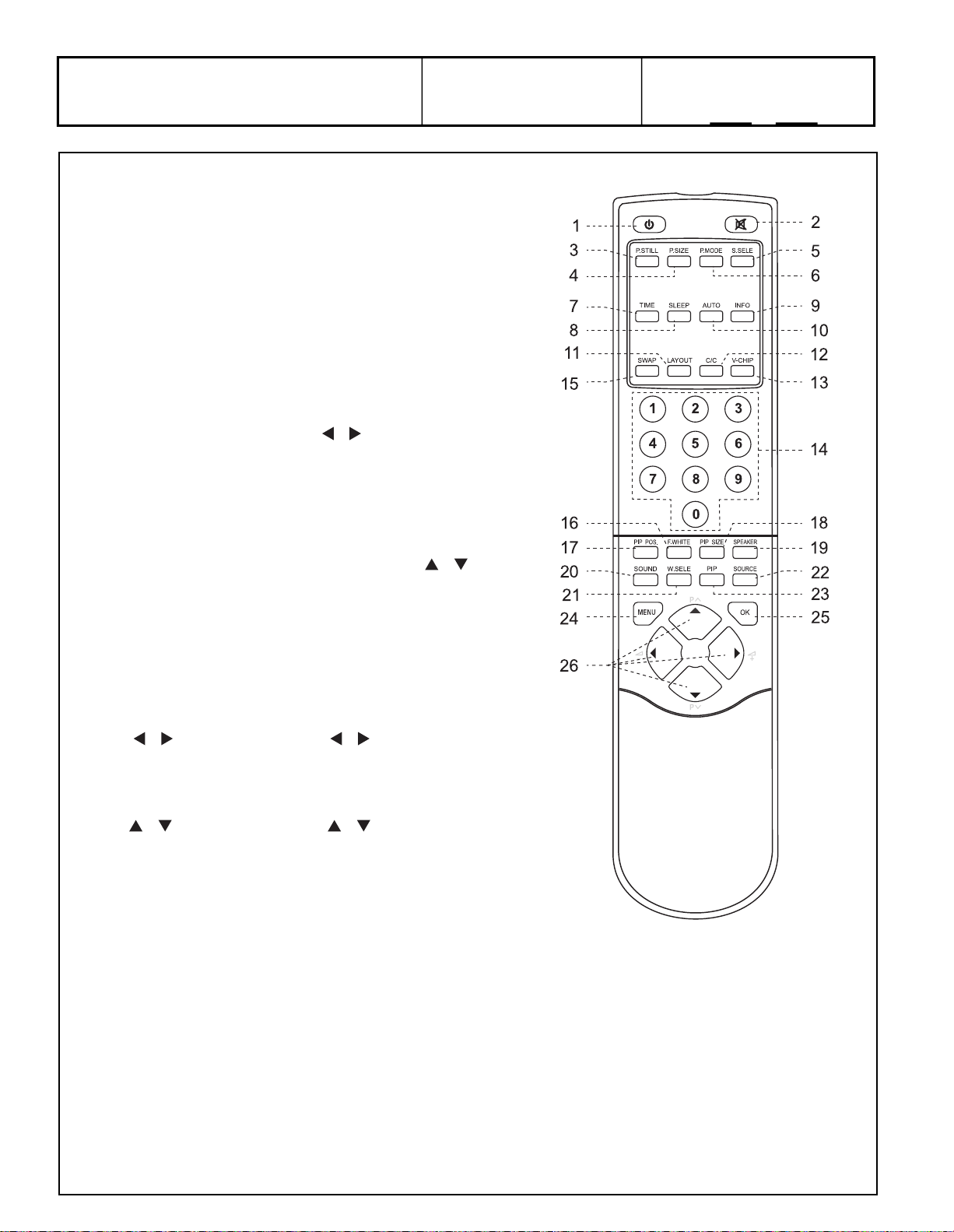

15 SWAP: Press this button to switch the Main

window or Sub window pictures in

PIP and

Split Screen

.

16 F.WHITE: Press this button to show a full

white picture.

17

PIP POS. : Press the button to select different

Image Position in PIP Mode.

18 PIP SIZE : Press the button to select different

Image Size in PIP Mode.

19 SPEAKER: Press this button to pop up the

“Speaker” menu, use the

/ button to select

“Internal” or “External”.

20 SOUND: Press the button to select different

sound effect.

21 W.SELE: Press this button to select the Main

Window or Sub Window.

22 SOURCE: Press this button and use

/

button to select the signal sources. AV, S-Video,

YPbPr 1, YPbPr 2, VGA or HDMI.

23 PIP: Press this button to change different

Picture Mode.

24

MENU: Press this button to pop up the OSD

Menu and press it again to exit the OSD Menu.

25 OK : Press to enter or confirm.

26

/ : They are used as / buttons in the

OSD Menu screen and they can be used for

the adjustment of volume when the OSD Menu

is not shown on the screen.

/ : They are used as / buttons in the

OSD Menu screen.

They also can be used for the selection of the

program when the OSD Menu is not shown on

the screen, but only for the Model with Tuner.

Technical Specifications

PDP4216M

CONTINUATION PAGE

NUMBER

9 OF 10 PAGES

Page 13

Technical Specifications

PHYSICAL CHARACTERISTICS

14. Power Cord

Length : 1.8m nominal

Type : optional

15. Cabinet

PDP4216M

CONTINUATION PAGE

NUMBER 10

OF 10 PAGES

15.1 Color

: black colour as defined by colour plaque reference number

15.2 Weight(W/Ostand)

Net weight : 34kg

Gross weight :

15.3 Dimensions (W/O stand&speak)

Width : 1024mm

Height : 692mm

Depth : 286mm

Page 14

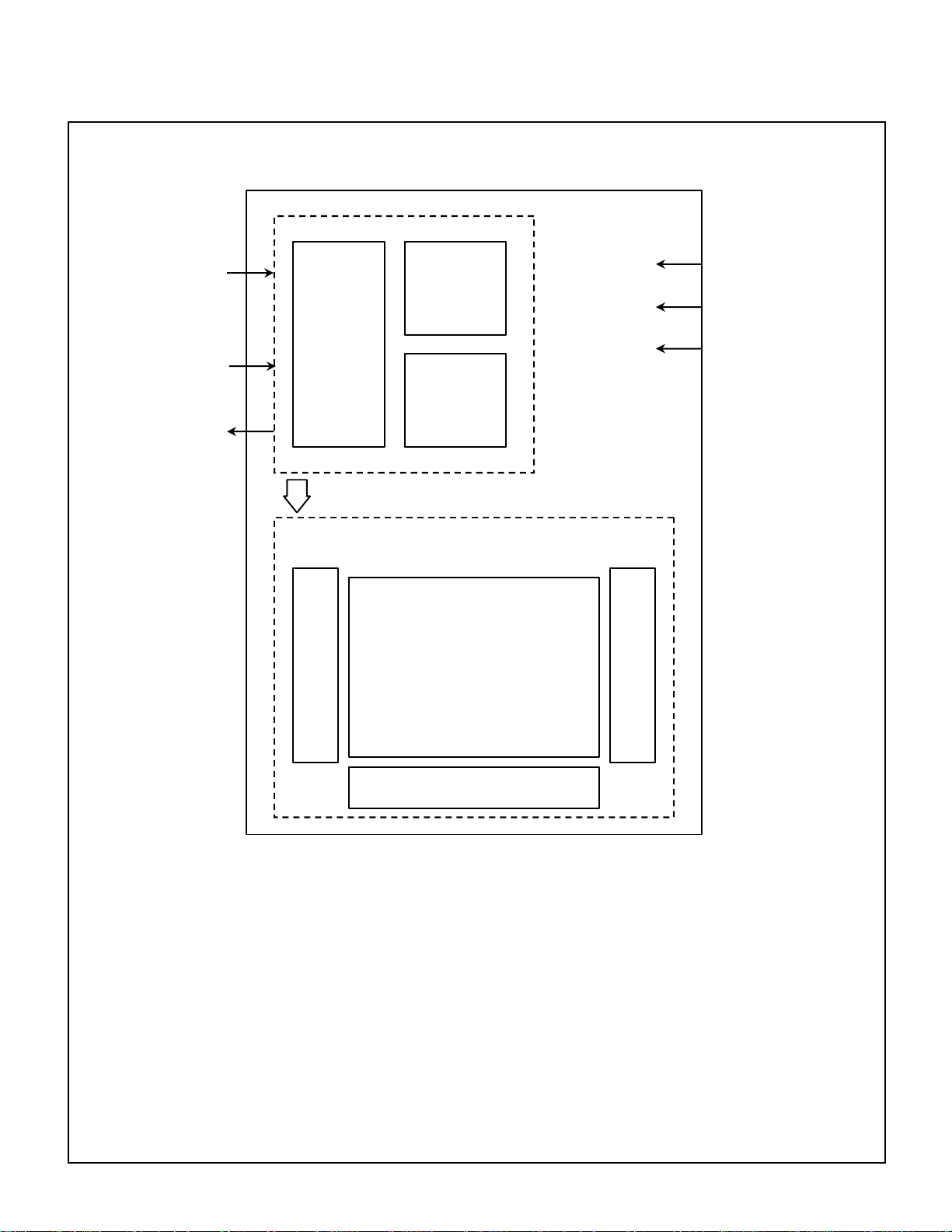

Block Diagram

Product Specification of PDP Module

LVDS Input

Control Signal

(Serial Interface)

APL Data

Memory

Input

Controller

Interface

Controller

Driver

Timing

Controller

Display data, Driver timing

Color Plasma Display Panel

1366 X 768 pixels

Scan Driver

Vs(180V~190V)

Va(55V~65V)

Vcc(+5V)

Common sustain driver

Address Driver

☞ Applied Voltage level is specified at the time when Full-White pattern is displayed on the panel.

Page 15

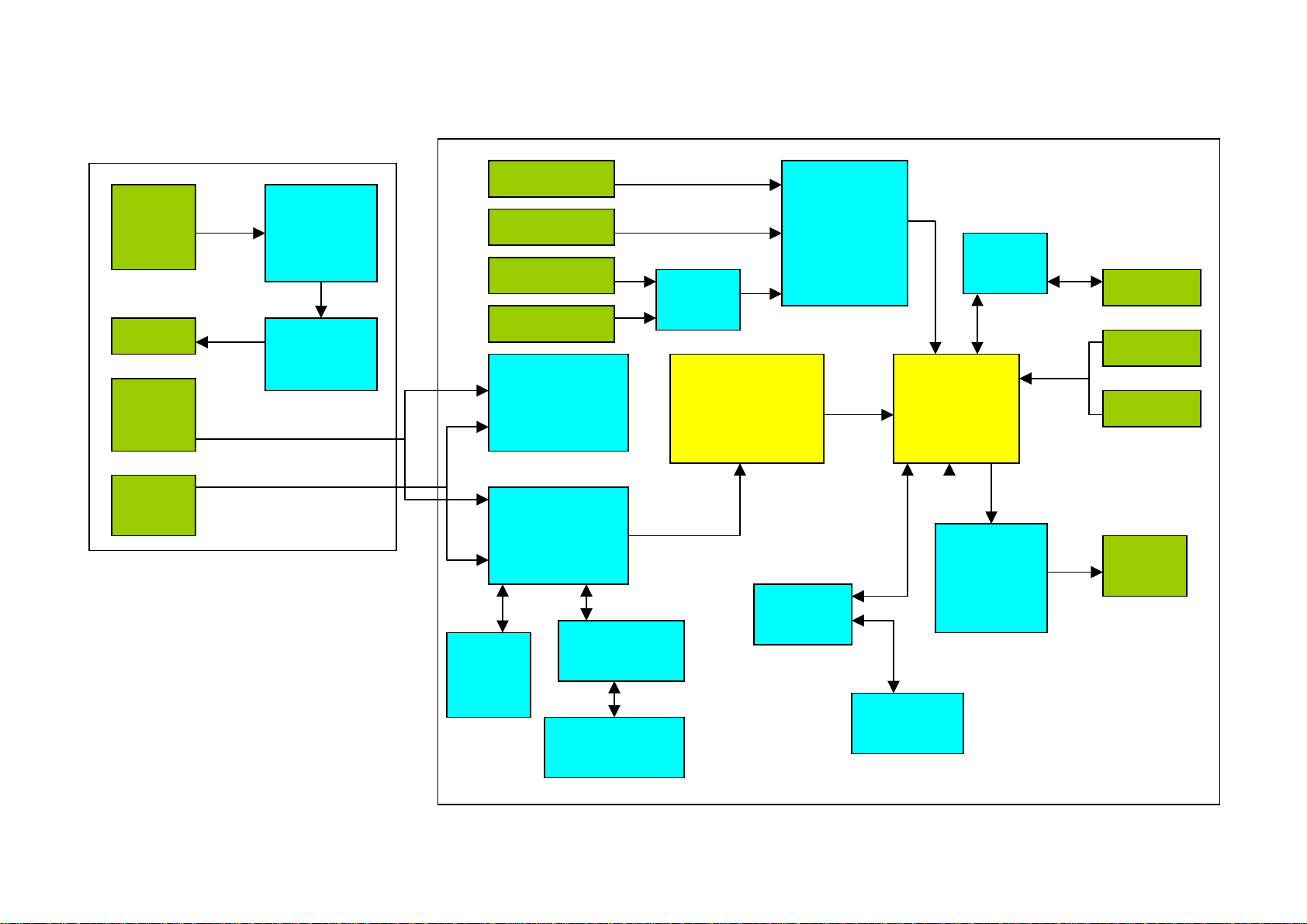

Stereo

Audio

Input

Speaker

Video

Input

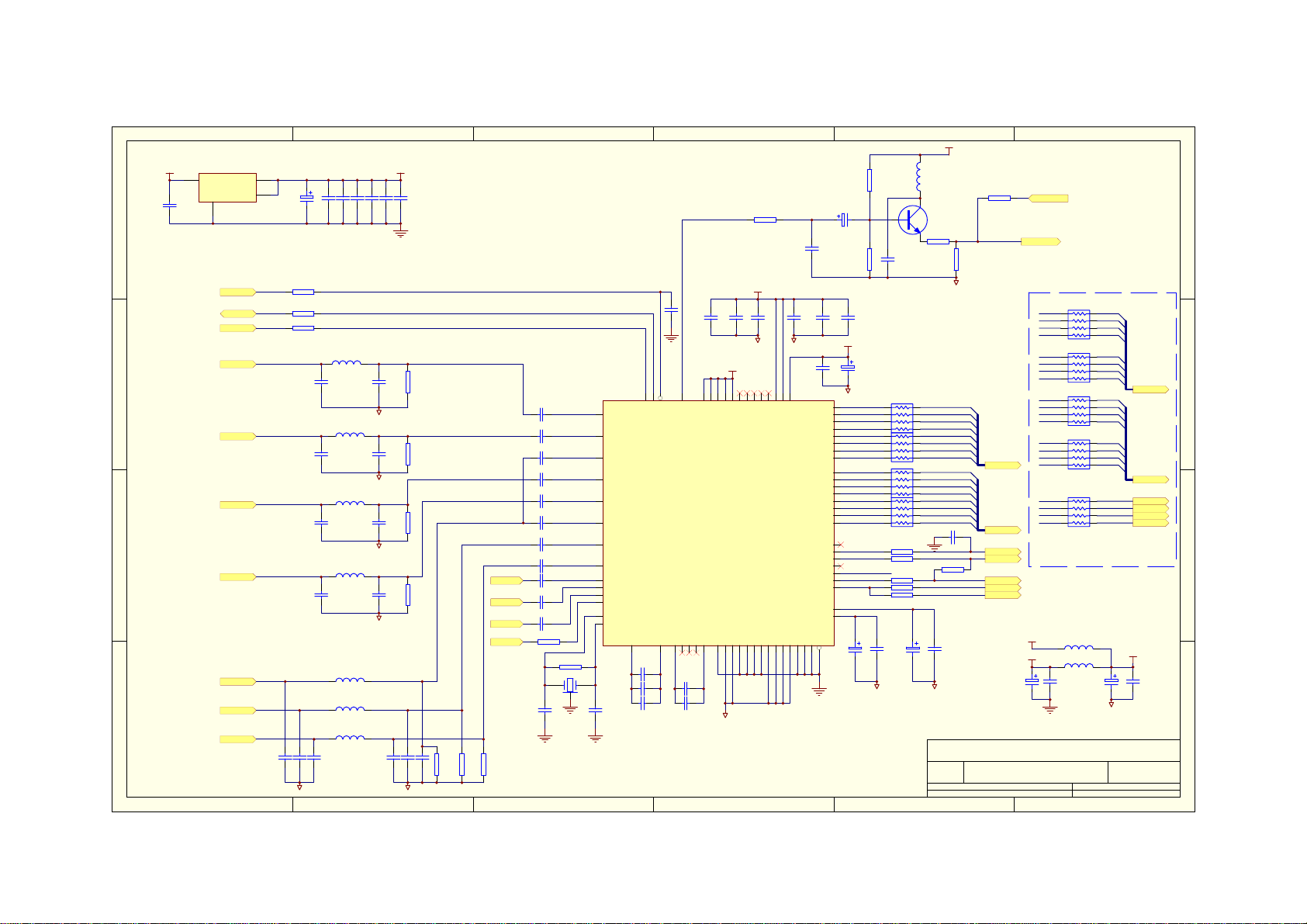

Block Diagram MAIN / AUDIO BOARD

PI5V330

Switch

PW1231

De-Interlace

AD9880

ADC & HDMI

Receive

Max232

RS232C

PW181

Image

Processor

MSP44XXG

Audio

decoder

TDA 2616

Audio Amp

HDMI Input

HD1 Input

HD2 Input

D-Sub15

VPC3230D

Video decoder

D-SUB9

1R

Keypad

S-Video

Input

286229

V-Chip /

CCD

VPC3230D

Video decoder

SAA5316

TV TEXTPRO

LP262S20480T

SRAM

AT24C32

EEPROM

HT48R06A

mcu

THc63LVD

M83

LVDS

Transmitter

LVDS

Header

Page 16

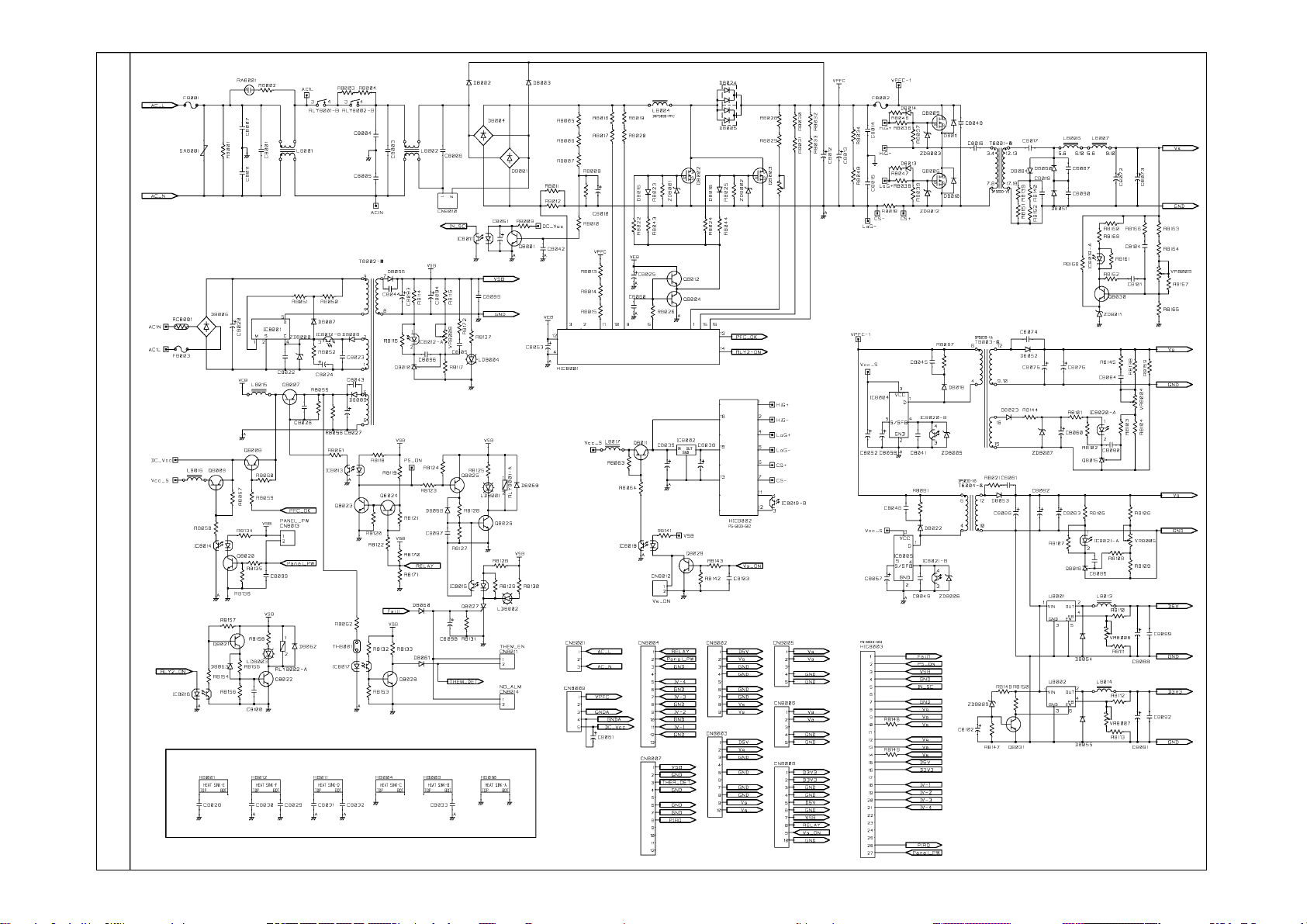

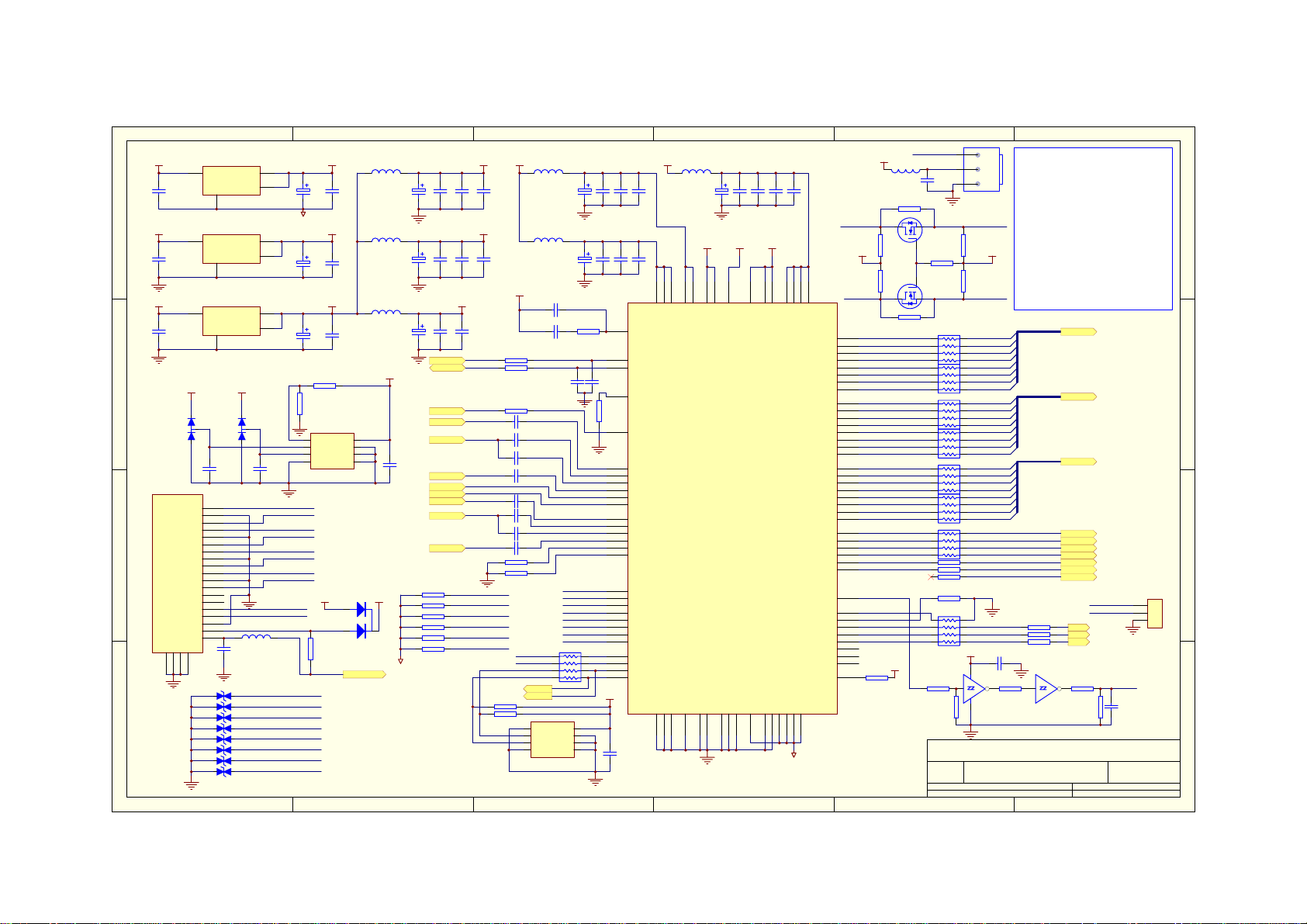

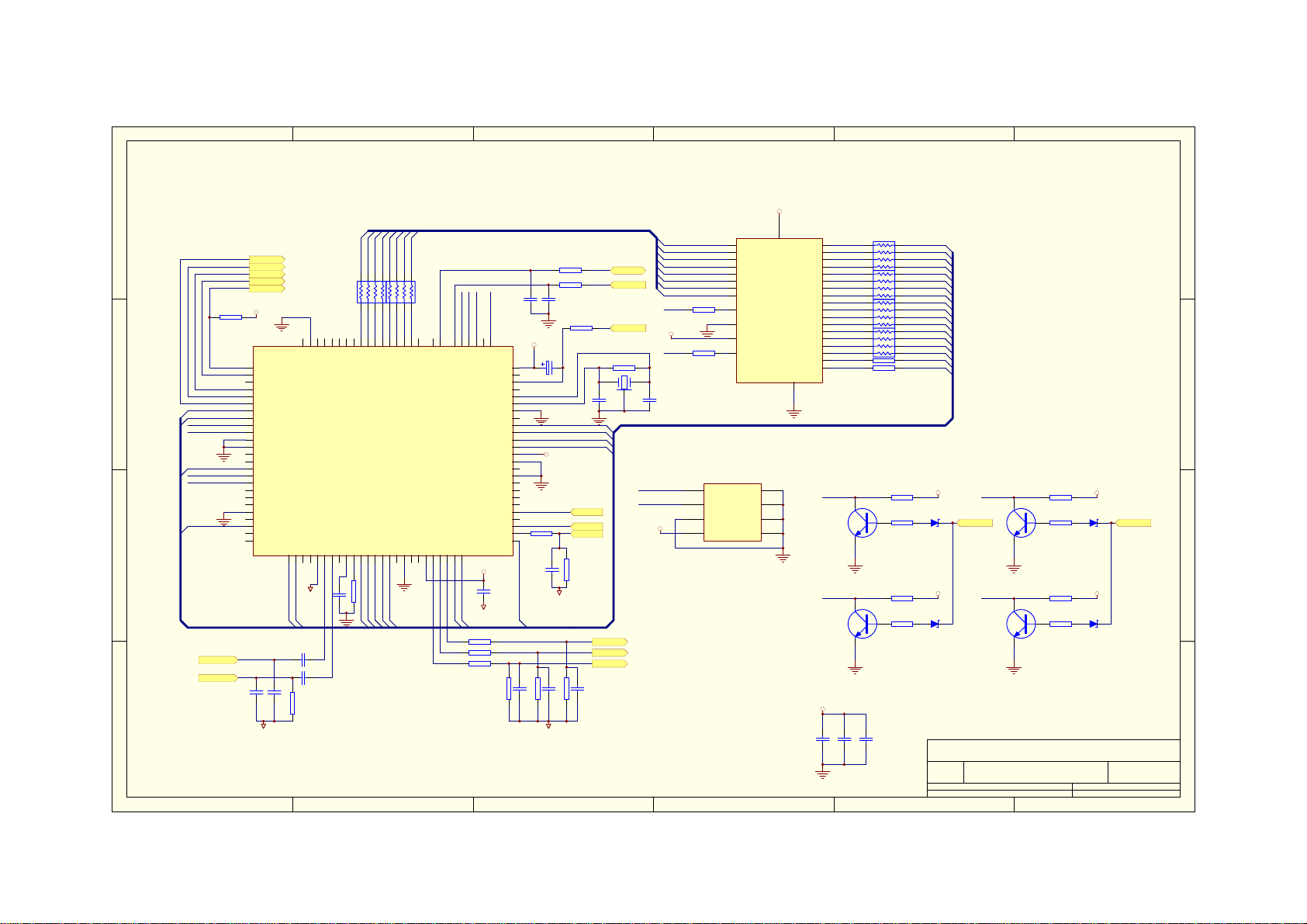

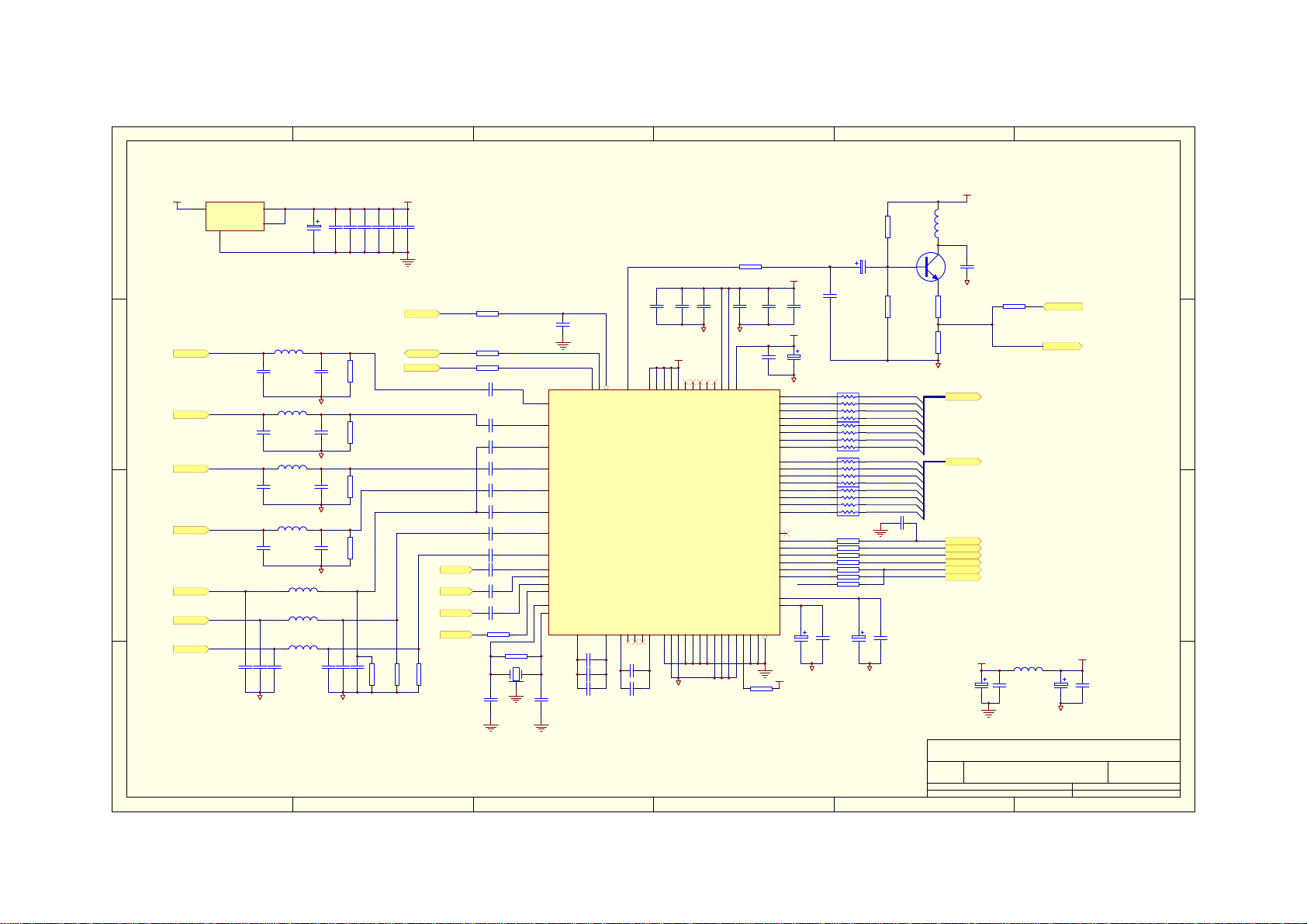

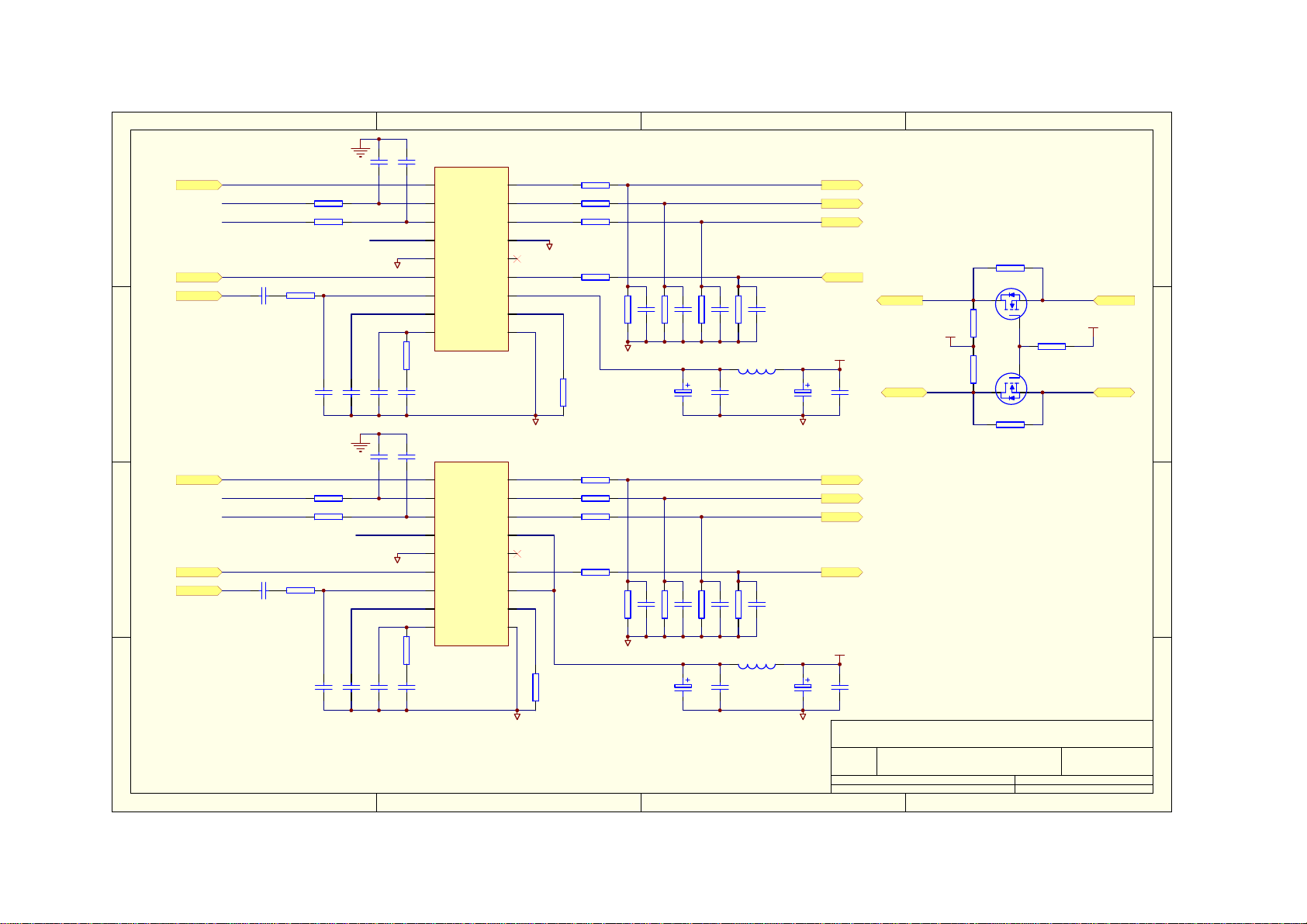

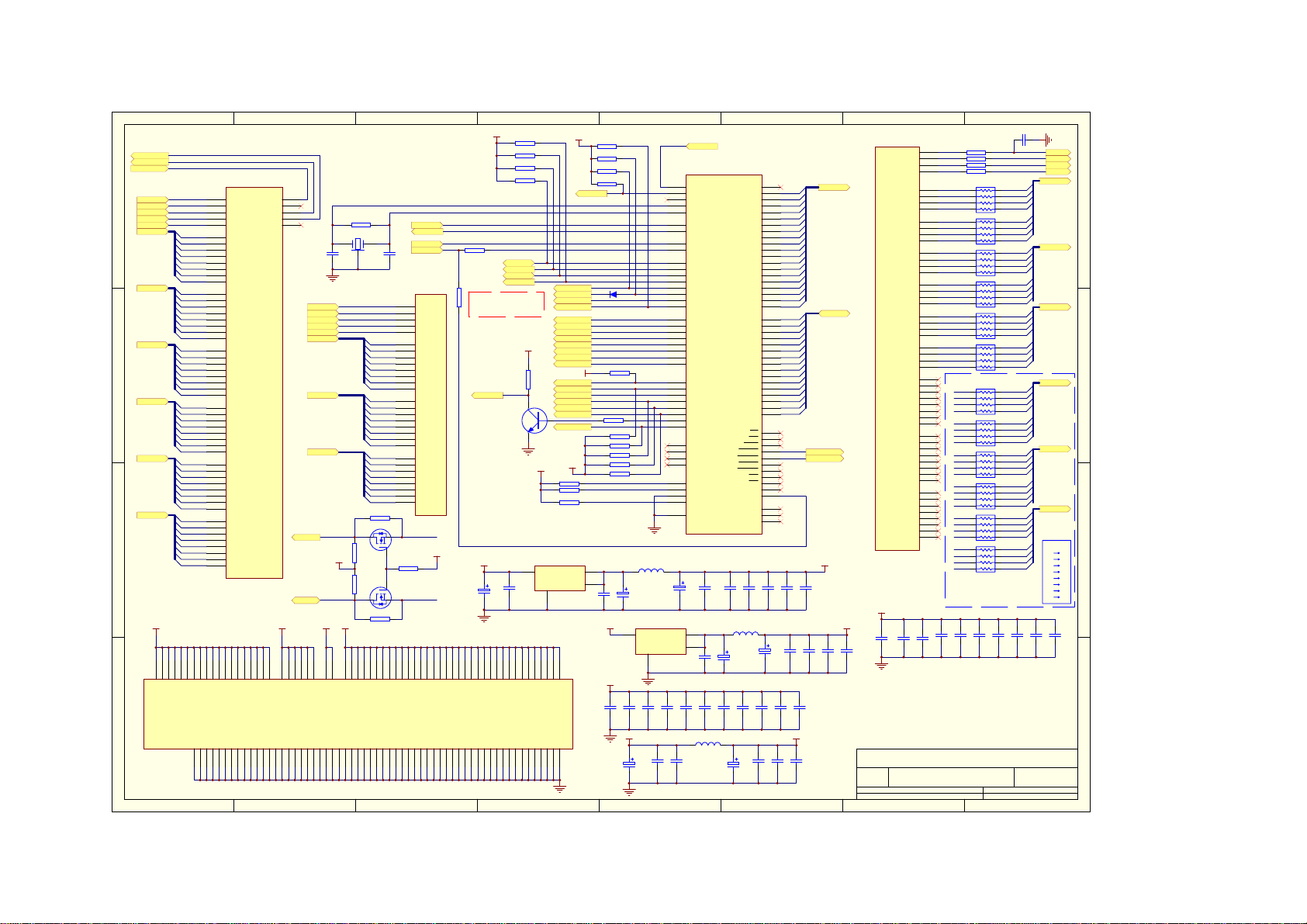

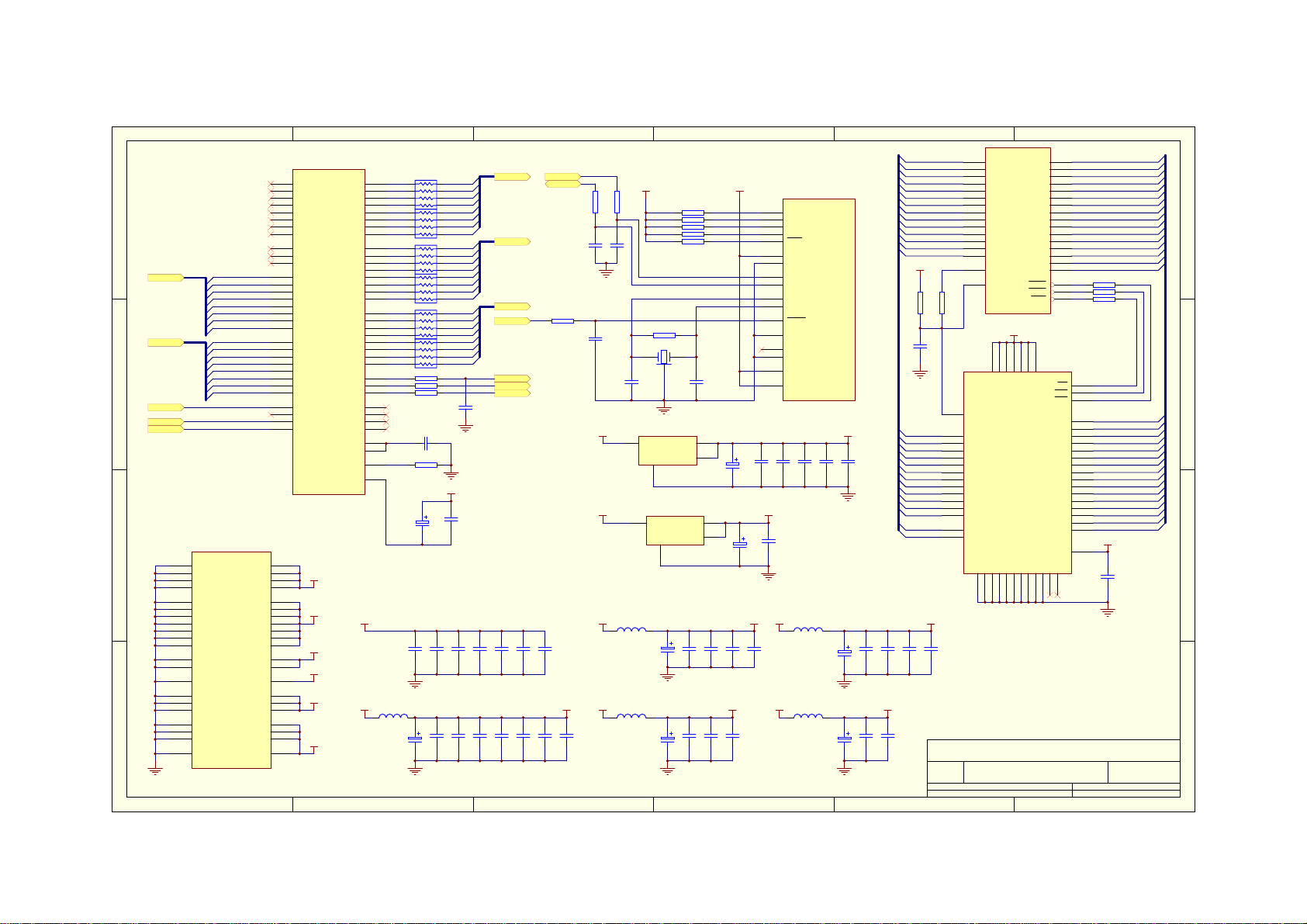

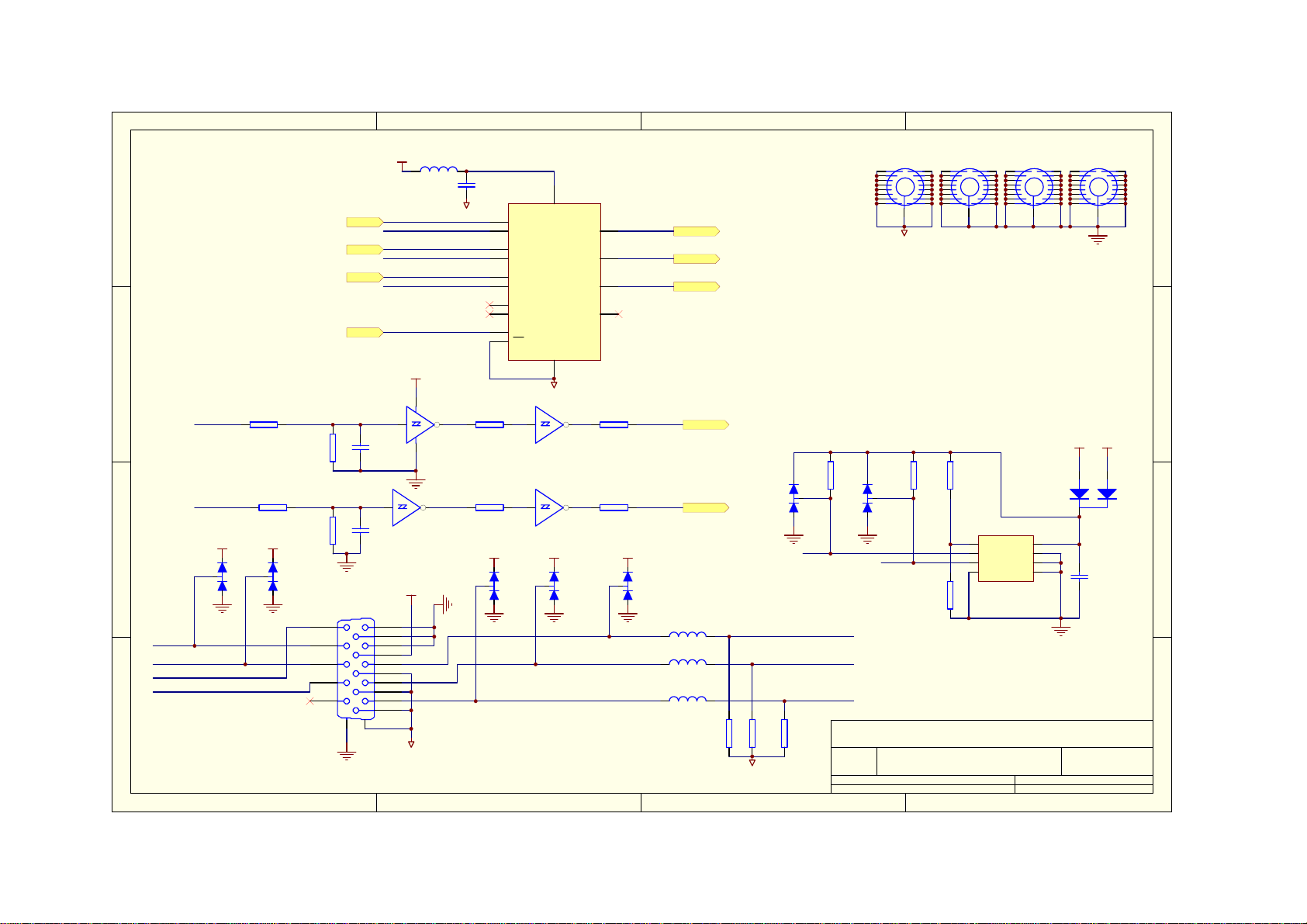

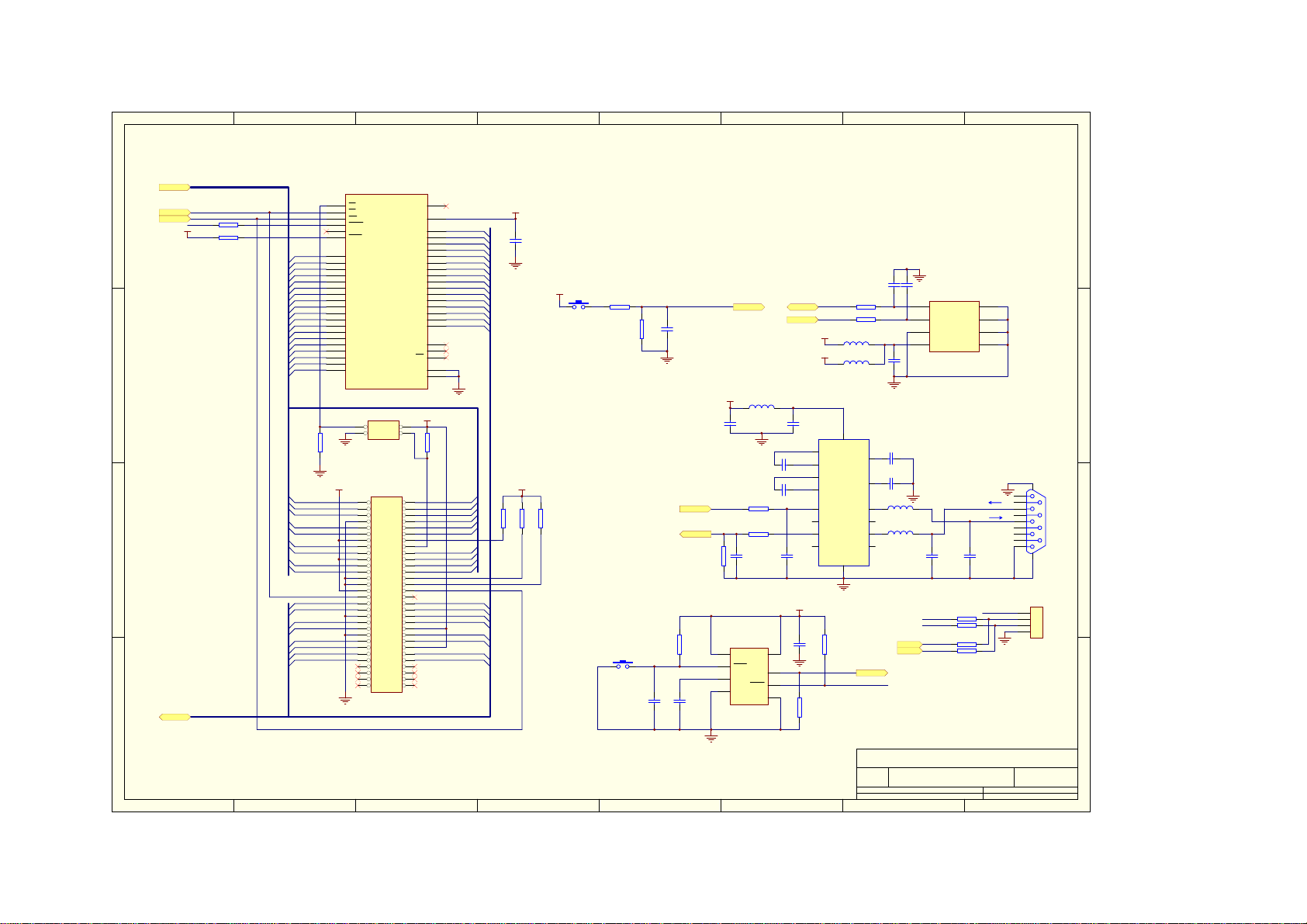

Circuit Diagram

- Power supply board of Audio Amplifier, MPT012A

- Main (Video) board

- Audio/Tuner board

- Keypad board

- Remote control receiver board

- Remote control board

Page 17

Page 18

GRE[7..0]

W

GGE[7..0]

GBE[7..0]

GPEN

GFBK

GHS

GVS

FIELD

GCLK

GSOG

C2

V2

Y2

R933

6

DDC_SCL5

DDC_SDA5

SPDIFOUT

D

C

B

JP903

3

2

1

C953R931 R934

A

54321

5V

D

5V

D3V3B

C

JP901

B

A

U902

3

INPUT

OUTPUT

TAB

C910

C912

C914

D901 D902

CEC/GND

T120T221T322T4

GND

1

U903

3

INPUT

OUTPUT

TAB

GND

1

U904

3

INPUT

OUTPUT

TAB

GND

1

DDC5V DDC5V

DDC_SCL5

DDC_SDA5

C947C948

1

DATA2+

2

DATA2S

3

DATA2-

4

DATA1+

5

DATA1S

6

DATA1-

7

DATA0+

8

DATA0S

9

DATA0-

10

CLK+

11

CLKS

12

CLK-

13

CEC

14

NC

15

SCL

16

SDA

17

18

+5V

19

HPDET

23

L913

C930

D903

D904

D905

D906

D907

D908

D909

D910

1 2 3 4 56

OVDD3.3V# OVDD3.3V#

2

4

C911

C901

SGND

AVDD3.3V#

2

4

C913

C902

C903

HDMI_D2+

HDMI_D2-

HDMI_D1+

HDMI_D1-

HDMI_D0+

HDMI_D0-

HDMI_CK+

HDMI_CK-

DDC_SCL5

DDC_SDA5

HDMI_5V

HDMI_D0+

HDMI_D0HDMI_D1+

HDMI_D1HDMI_D2+

HDMI_D2HDMI_CK+

HDMI_CK-

HDMI-1.8V

C915

R903

R947

U905

7

VCLK

6

SCL

5

SDA

4

GND

R915

HPD_DET

2

4

VCC

NC1

NC2

NC3

2

1

D911

8

1

2

3

HPD_DET

L900

C904

L901

C905

L902

C906

DDC5V

C929

R941

DDC5V5V

R942

R943

R944

3

R945

R946

SGND

DVDD1.8V

C922

SCL_H5V

SDA_H5V

GCOAST

HD1_R/Pr

HD1_G/Y

HD1_B/Pb

VGA_VS

VGA_HS

GYCbCr_Cr

GYCbCr_Y

GYCbCr_Cb

PLL1.8V

C917C916

CVDD1.8V

C920C919

C923

HD1_R/Pr

HD1_G/Y

HD1_B/Pb

GYCbCr_Cr

GYCbCr_Y

GYCbCr_Cb

GYCbCr_Cr

GYCbCr_Y

GYCbCr_Cb

C918

C921

R909

R910

HD1_R/Pr

HD1_G/Y

HD1_B/Pb

R912

R913

R908

C939

C940

C941

C942

C945

PLL1.8V

R905

R906

C943

C944

C946

DDC_SCL3

DDC_SDA3

HDCP_SCL

HDCP_SDA

SDA#SO

SCL#SO

7

6

5

4

L904

VCLK

SCL

SDA

GND

C935

C936

L903

HD2_Cr

HD2_Y

HD2_Cb

RP909

U906

C938

VCC

NC1

NC2

NC3

C907

C908

R904

HDMI_D0HDMI_D0+

HDMI_D1HDMI_D1+

HDMI_D2HDMI_D2+

HDMI_CK+

HDMI_CK-

8

1

2

3

C924

C926

57

82

83

C937

46

R907

62

79

74

73

68

61

64

77

71

70

66

60

63

34

35

37

38

40

41

43

44

49

50

51

52

TVDD3.3V

C934

TVDD3.3V

C925

OVDD3.3V

C927 C928

FILT

SCL

SDA

RTERM

COAST/EXTCK

RAIN0

GAIN0

SOG0

BAIN0

VS0

HS0

RAIN1

GAIN1

SOG1

BAIN1

VS1

HS1

RX0RX0+

RX1RX1+

RX2RX2+

RXC+

RXC-

DDC_SCL

DDC_SDA

MCL

MDA

C956

AVDD3.3V#

10

90

100

OVDD1

OVDD2

OGND1

OGND2

1

11

91

OVDD3

OGND3

L914

33

TVDD1

DGND1

29

C909

45

TVDD2

CGND1

31

32

CVDD1

CGND2

47

48

CVDD2

U901

TGND1

36

30

DVDD

TGND2

39

TGND3

42

AVDD3.3V

C950C949 C951 C952

PLL1.8VDVDD1.8VCVDD1.8V

59

56

54

PVDD2

PVDD1

ALVDD

ALGND

PGND1

PGND2

53

55

58

65

67

AVDD1

AGND2

AGND1

69

SGND

72

76

AVDD2

AVDD3

VSOUT/A0

MCLKOUT

AGND3

AGND4

75

78

80

AVDD4

HSOUT

SOGOUT

FIELD

DCLK

S/PDIF

MCLKIN

SCLK

LRCLK

I2S0

I2S1

I2S2

I2S3

PWRDN

R7

R6

R5

R4

R3

R2

R1

R0

G7

G6

G5

G4

G3

G2

G1

G0

B7

B6

B5

B4

B3

B2

B1

B0

DE

L915

DDC_SCL5

DDC5V

DDC_SDA5

92

93

94

95

96

97

98

99

2

3

4

5

6

7

8

9

12

13

14

15

16

17

18

19

88

87

86

85

84

89

28

20

21

22

23

27

26

25

24

81

ADCR7

ADCR6

ADCR5

ADCR4

ADCR3

ADCR2

ADCR1

ADCR0

ADCG7

ADCG6

ADCG5

ADCG4

ADCG3

ADCG2

ADCG1

ADCG0

ADCB7

ADCB6

ADCB5

ADCB4

ADCB3

ADCB2

ADCB1

ADCB0

ADC_DE

ADC_HS

ADC_SOG

ADC_VS

ADC_FIELD

ADC_DCLK

R914

5V

R919

R920

S/PDIF

AVDD3.3V

R923

R924

SPDIFOUT

G

G

RP905

RP906

RP903

RP904

RP901

RP902

RP907

R925

R918

R917

R916

JP902

1

VIN

Using digital interface:

2

C954

3

SD

Q901

R921

R922

Q902

SD

R929

RP908

I2S_SCLK

I2S_LRCLK

I2S_DATA

OVDD3.3V

R930

1 2

7 14

Title

9-HDMI-R

Number RevisionSize

B

Date: 14-Oct-2005 She et of

File: F:\4228\4228_temp_ddb\4228_Temp.DDB Drawn By:

VCC

DVdd (1.8V) (DVdd+CVdd) 130mA 234mW

GND

PVd (1.8V) (PVd+ALVdd) 30mA 54mW

Vd (3.3V) (Avdd+TVdd) 80mA 264m W

DDC_SCL3

Vdd (3.3V) (Ovdd) 10-120mA, 30mA typical

99mW

Using analog interface:

TVDD3.3V

DVdd 60mA 108mW

PVd 20mA 36mW

DDC_SDA3

Vd 270mA 891m

GRE7

GRE6

GRE5

GRE4

GRE3

GRE2

GRE1

GRE0

GGE7

GGE6

GGE5

GGE4

GGE3

GGE2

GGE1

GGE0

GBE7

GBE6

GBE5

GBE4

GBE3

GBE2

GBE1

GBE0

GPEN

GFBK

GHS

GVS

FIELD

GCLK

GSOG

R928

R927

R926

C955

3 4

R932

U907A

U907B

Page 19

54321

6

I/O8

I/O7

I/O6

I/O5

I/O4

I/O3

I/O2

I/O1

/WE

/CE1

CE2

/OE

GND

D3V3D

8

VCC

GND

9

A17

10

A16

7

RP1503

A15

11

A14

4

A13

12

A12

1

RP1504

A11

31

A10

2

A9

3

A8

13

RP1505

A7

14

A6

15

A5

16

A4

RP1506

17

A3

18

A2

R1508

19

A1

R1509

20

A0

A17_SRAM

A16_SRAM

A15_SRAM

A14_SRAM

A13_SRAM

A12_SRAM

A11_SRAM

A10_SRAM

A9_SRAM

A8_SRAM

A7_SRAM

A6_SRAM

A5_SRAM

A4_SRAM

A3_SRAM

A2_SRAM

A1_SRAM

A0_SRAM

24

4

3

NC2

2

NC1

1

NC0

Q1501

Q1503

R1516

R1517

R1522

R1523

D3V3D

D1501

D3V3D

D1503

SC2_SW

SC1_SW0SC1_SW1

Q1502

SC2_SW0SC2_SW1

Q1504

R1519

R1520

R1525

R1526

D3V3D

D1502

D3V3D

D1504

SC1_SW

D3V3D

C1506 C1507 C1508

Title

15_TELETEXT_DECODER

Number RevisionSize

B

Date: 14-Oct-2005 She et of

File: F:\4228\4228_temp_ddb\4228_Temp.DDB Drawn By:

D

D3V3D

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

A16_SRAM

C1512

R1528

C1519

C1511

C1513

XTALOUT

XTALIN

A8_SRAM

A9_SRAM

A10_SRAM

A11_SRAM

D3V3D

SGND

R1514

R1515

R1513

TT_VVVS

TT_VVHS

TT_FSO

R1529

SDA_S3V

SCL_S3V

R1505

TT_R

TT_G

TT_B

SDA_S3V

SCL_S3V

3450_rest

/WR_SRAM

D3V3D

/RD_SRAM

X1501

C1505C1504

SDA_NVRAM

SCL_NVRAM

D3V3D

GPIO_P33

GPIO_P32

GPIO_P31

GPIO_P30

TT_SEL

R1527

D3V3D

100

99

1

P2.7

2

P3.0

3

A17_LN

A7_SRAM

SCL_NVRAM

SDA_NVRAM

A6_SRAM

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

P3.1

P3.2

P3.3

A15_LN

A14

/RD

/WR

VSSC

VSSP

P0.5

NC

A7

SCL_NVRAM

SDA_NVRAM

P0.2

NC

NC

VPE

P0.3

A6

P0.4

P3.7

C

A15_SRAM

A14_SRAM

/RD_SRAM

/WR_SRAM

B

P2.0

VSSC

A526A427P0.628P0.729VSSA30CVBS031CVBS132A15_BK33SYNC_FILTER34IREF35A1336A1237A338A239A140FRAME41VPE42/COR43P3.444VDDA45B46G47R48A049RAMBK1

SGND

A5_SRAM

A4_SRAM

TV_CVBS_M#

TV_CVBS_S#

C1503

C1502

D7_SRAM

D6_SRAM

D5_SRAM

D4_SRAM

D3_SRAM

D2_SRAM

D1_SRAM

D0_SRAM

RP1502RP1501

SC1_SW0

SC1_SW1

SC2_SW0

92

98

P2.193P2.294P2.395P2.496P2.597P2.6

82

84

P1.483P1.5

AD085AD186AD287AD388AD489AD590AD691AD7

U1501

SC2_SW1

76

80

77

81

P1.0

P1.178P1.279P1.3

SCL

SDA

RAMBANK0

D3V3_TT_A

50

VDDP

A16_LN

RESET

/RESET

XTALOUT

XTALIN

OSCGND

VDDC

VSSC

VSSP

VSYNC

HSYNC

VDS

NC

NC

A8

A9

A10

A11

NC

P3.6

NC

NC

NC

P3.5

C1510

R1501

C1501

CVBS0

CVBS1

A13_SRAM

A12_SRAM

A3_SRAM

A2_SRAM

A1_SRAM

B_OUT

G_OUT

R_OUT

A0_SRAM

R1510

R1511

R1512

A17_SRAM

SGND

D7_SRAM

D6_SRAM

D5_SRAM

D4_SRAM

D3_SRAM

D2_SRAM

D1_SRAM

D0_SRAM

5

6

7

8

R1506

R1507

U1502

U1503

SDA

SCL

WP

VCC

29

28

27

26

25

23

22

21

5

30

6

32

C1514

R1502

R1503

R1504

C1516

C1517

C1515

R1521

A

SGND SGND

C1518

1 2 3 4 56

D

C

B

A

Page 20

54321

A5V

U1101

5V

3

INPUT

GND

C1108

D

1

OUTPUT

TAB

2

4

C1105

C1109

C1110

C1111

C1112

C1113

VV33

C1114

CVBS_O

R1114

R1112

C1164

R1113 R1106

C1171

L1112

Q1101 R1104

C1163

R1121

3230_VO

TV_CVBS_M#

3230_VO

6

D

MREST

SDA_S3V

SCL_S3V

V_AVCVBS

C

V_TVCVBS

V_SVideo_C

B

V_SVideo_Y

VYCbCr_Y

VYCbCr_Cb

A

VYCbCr_Cr

1 2 3 4 56

R1103

R1101

R1102

C1160

C1150 C1151

C1128

C1154

C1173

C1172

C1174

SGND

L1111

L1104

L1105

L1106

L1107

L1108

L1102

C1159

C1149

C1156

SGND

SGND

SGND

SGND

C1125

R1117

SGND

R1115

R1116

R1118

C1126

C1127

V_TT_G

V_TT_B

V_TT_R

V_TT_FSO

R1126R1125R1124

R1127

C1116

C1117

C1115

C1118

C1119

C1120

C1121

C1122

C1166

C1167

C1168

R1119

X1101

C1124

70

15

14

13

74

VIN3

SCL

SDA

73

VIN2

75

VIN4

71

CIN

72

VIN1

5

Y2/G2

4

U2/B2

6

V2/R2

2

Y1/G1

1

U1/B1

3

V1/R1

79

FBIN1

62

XTALI

63

XTALO

VDDCAP9GNDCAP

C1132

C1123

C1140

C1131C1130

10

RST#

VOUT

U1102

ADR:0x88

CLK560FPDAT58CLK2024ASGND7ASGND64GND

APGND25APVDD26PLGND30YGND35CGND46SPGND51AFGND65ISGND68ISGND77ISGND80I2CSEL

12

C1133

C1134

5VVV

C1141 C1142 C1143 C1144C1145C1146

SGND

SGND

VV33

23

20

29

VDD

PLVDD

11

SGND

52

45

YVDD36CVDD

SPVDD

19

FFIE

21

FFWE

FFRST

59

76

69

FFRE22FFOE

ISVDD

AFVDD

VSTBY

SGND

5VVV

C1147C1148

RP1101

RP1102

RP1103

31

32

33

34

37

38

39

40

41

42

43

44

47

48

49

50

27

28

56

53

#VPEN

54

R1107

55

R1105

57

R1108

REF_V

78

66

SGND SGND

RP1104

R1109

C1138 C1136

VY7

VY6

VY5

VY4

VY3

VY2

VY1

VY0

VY[7..0]

VUV7

VUV6

VUV5

VUV4

VUV3

VUV2

VUV1

VUV0

C1139

VUV[7..0]

VVCLK

R1110

VVHS

VVVS

Title

B

Date: 14-Oct-2005 She et of

File: F:\4228\4228_temp_ddb\4228_Temp.DDB Drawn By:

VVCLK

R1123

VVHS

TT_VVHS

VVVS

TT_VVVS

C1103

11-DECODERV

Number RevisionSize

SGND

Y7

Y6

Y5

Y4

Y3

Y2

Y1

Y0

UV7

UV6

UV5

UV4

UV3

UV2

UV1

UV0

LLC2

LLC

HS

INTLC

AVO

HCLP

VS

VREF

VRT

VGAV

OE#

TEST

C1137 C1135

17

18

16

67

RP1105

L1101

C1106

RP1106

RP1107

RP1108

RP1109

L1103

C1104

VG7

VG6

VG5

VG4

VG3

VG2

VG1

VG0

VB7

VB6

VB5

VB4

VB3

VB2

VB1

VB0

SGND

5VVV

VY7

VY6

VY5

VY4

VY3

VY2

VY1

VY0

VUV7

VUV6

VUV5

VUV4

VUV3

VUV2

VUV1

VUV0

#VPEN

VVVS

VVHS

VVCLK

Install RP1105~RP1109 if cancel deinterlace IC

A5V

5V

C1107

VG[7..0]

VB[7..0]

VPEN

VVS

VHS

VCLK

C

B

A

Page 21

54321

6

U1401

5V

3

D

C

B

A

INPUT

GND

1

G_AVCVBS

G_SVideo_C

G_SVideo_Y

GYCbCr_Cb

G_AVCVBS

G_TVCVBS

GYCbCr_Y

GYCbCr_Y

GYCbCr_Cb

GYCbCr_Cr

GYCbCr_Cr

1 2 3 4 56

2

OUTPUT

4

TAB

C1405

L1407

C1460 C1459

L1408

C1450 C1451

L1402

C1428 C1449

L1411

C1454 C1456

L1404

L1405

L1406

C1473

C1474

C1472

SGND

SGND

SGND

SGND

SGND

C1425

C1409

SGND

C1410

R1415

R1416

R1418

C1426

R1417

C1427

C1411

C1412

C1413

GV33

C1414

MREST

SDA_S3V

SCL_S3V

R1426R1425R1424

G_TT_G

G_TT_B

G_TT_R

G_TT_FSO

R1403

R1401

R1402

R1427

C1416

C1417

C1415

C1418

C1419

C1420

C1421

C1422

C1466

C1467

C1468

R1419

X1401

C1431C1430

74

73

75

71

72

79

62

63

C1424

5

4

6

2

1

3

VIN3

VIN2

VIN4

CIN

VIN1

Y2/G2

U2/B2

V2/R2

Y1/G1

U1/B1

V1/R1

FBIN1

XTALI

XTALO

C1432

C1423

C1440

CVBS_S_O

14

13

SCL

10

15

70

SDA

RST#

VOUT

U1402

ADR:0x8E

VDDCAP9GNDCAP

CLK560FPDAT58CLK2024ASGND7ASGND64GND

APGND25APVDD26PLGND30YGND35CGND46SPGND51AFGND65ISGND68ISGND77ISGND80I2CSEL

12

C1433

C1434

C1441 C1442 C1443 C1444C1445C1446

SGND

SGND

GV33

69

23

20

52

SPVDD

76

19

21

FFIE

FFRE22FFOE

FFWE

FFRST

ISVDD

AFVDD

VDD

29

PLVDD

11

45

YVDD36CVDD

SGND

59

R1414

VSTBY

67

17

R1420

LLC2

INTLC

HCLP

VREF

VGAV

TEST

16

AVO

UV7

UV6

UV5

UV4

UV3

UV2

UV1

UV0

VRT

Y7

Y6

Y5

Y4

Y3

Y2

Y1

Y0

LLC

HS

VS

OE#

18

5VVG

5VVG

5VVG

C1447C1448

SGND

31

RP1401

32

33

34

37

RP1402

38

39

40

RP1403

41

42

43

44

47

RP1404

48

49

50

27

R1409

28

56

R1410

R1408

53

54

R1407

55

R1422

57

R1405

R1423GHS

78

66

C1437 C1435

SGND SGND

C1464

C1471

REF_G

C1438 C1436

R1413

C1439

R1412

GHS

TT-GHS

GGE7

GGE6

GGE5

GGE4

GGE3

GGE2

GGE1

GGE0

GBE7

GBE6

GBE5

GBE4

GBE3

GBE2

GBE1

GBE0

Q1401

A5V

L1412

C1463

SGND

R1404

R1406

SGND

GGE[7..0]

GBE[7..0]

GCLK

GHS

FIELD

GPEN

TT-GHS

GVS

C1403

Title

14-DECODER_G

B

Date: 14-Oct-2005 She et of

File: F:\4228\4228_temp_ddb\4228_Temp.DDB Drawn By:

R1421

TV_CVBS_S#

TV_CVBS_S

TV_CVBS_S

C1404

5VVG

C1407

SGND

5V

L1401

C1406

Number RevisionSize

D

C

B

A

Page 22

321

4

C860 C861

TT_VVVS

D

TT_VVHS

3230_VO

C

B

TV_CVBS_S

GVS

TT-GHS

SDA_S5V

SCL_S5V

C855

SDA_S5V

SCL_S5V

C809

R855

R856

R857

R801

R802

R803

C856

C810

C857

5V_G_CCD

C811

13

14

15

5V_V_CCD

SGND

R858

C858 C859

C814 C815

13

14

15

SGND

R804

C812 C813

Vin/INTRO

SDA

SCK

4

SEN

6

SMS

5

HIN

7

VIDEO

8

CSYNC

LPF9VSS(A)

Vin/INTRO

SDA

SCK

4

SEN

6

SMS

5

HIN

7

VIDEO

8

CSYNC

LPF9VSS(A)

U803

U802

I2C/SEL

SDO

BOX

VDD

RREF

I2C/SEL

SDO

BOX

VDD

RREF

18

2

3

1

16

17

12

10

11

SGND

18

2

3

1

16

17

12

10

11

SGND

R805

R860

R861

R862

R863

5V_V_CCD

R859

R806

R807

R808

R809

5V_G_CCD

R864

SGND

R810

SGND

C862

C817

C804

C802

R865

R811

C863

C818

R866

R812

C864

C819

R

G

B

R

G

B

C807

C808

R867

L801

R813

L802

C865

C820

V_TT_R

V_TT_G

V_TT_B

V_TT_FSO

C803

G_TT_R

G_TT_G

G_TT_B

G_TT_FSO

C801

SGND

V_TT_R

V_TT_G

V_TT_B

V_TT_FSO

A5V

G_TT_R

G_TT_G

G_TT_B

G_TT_FSO

A5V

C806

C805

SCL_S5V

SDA_S5V

SCL_S5V

SDA_S5V

D

R815

SD

R814

Q801

G

R852

G

Q802

SD

R854

5V

R853

SCL_S3V

V33SW

C

SDA_S3V

B

Title

A

1 2 34

SGND

SGND

8-CCD_DECODER

Number RevisionSize

A4

Date: 14-Oct-2005 Sheet of

File: F:\4228\4228_temp_ddb\4228_T emp.DDB Drawn By:

A

Page 23

C1354

DRE1

DRE5

DRE6

DRE0

DRE7

DRE3

DRE2

DRE4

DGE1

DGE0

DGE3

DGE2

DGE7

DGE6

DGE5

DGE4

DBE0

DBE3

DBE1

DBE2

DBE4

DBE7

DBE6

DBE5

DRE3

DRE7

DRE0

DRE2

DRE1

DRE5

DRE4

DRE6

DGE3

DGE2

DGE5

DGE4

DGE1

DGE0

DGE7

DGE6

DBE2

DBE5

DBE3

DBE4

DBE6

DBE1

DBE0

DBE7

8

DCLK

DVS

DHS

DEN

DRE[7..0]

D

DGE[7..0]

DBE[7..0]

C

DRE[7..0]

DGE[7..0]

DBE[7..0]

181 LVDS

B

R6

R0

R7

R1

R2

R0

R3

R1

R4

R2

R5

R3

R6

R4

R7

R5

A

7654321

D3V3B

R1305

GCOAST

GBLKSPL

GFBK

U1301A

A10

GCLK

D

GPEN

GVS

GHS

GSOG

GRE[7..0]

GRE0

GRE1

GRE2

GRE3

GRE4

GRE5

GRE6

GRE7

GGE[7..0]

GGE0

GGE1

GGE2

GGE3

GGE4

GGE5

GGE6

GGE7

GBE[7..0]

GBE0

GBE1

GBE2

GBE3

C

B

A

GBE4

GBE5

GBE6

GBE7

GRO[7..0]

GRO0

GRO1

GRO2

GRO3

GRO4

GRO5

GRO6

GRO7

GGO[7..0]

GGO0

GGO1

GGO2

GGO3

GGO4

GGO5

GGO6

GGO7

GBO[7..0]

GBO0

GBO1

GBO2

GBO3

GBO4

GBO5

GBO6

GBO7

M16

T8

VIO16R6VIO17R7VIO18R8VIO19

1 2 3 4 5 6 78

GCLK

B9

GPEN

A9

GVS

C10

GHS

B10

GSOG

E4

GRE0

C3

GRE1

B1

GRE2

F4

GRE3

C2

GRE4

C1

GRE5

D3

GRE6

D2

GRE7

C11

GGE0

B12

GGE1

B11

GGE2

A8

GGE3

B8

GGE4

C8

GGE5

A7

GGE6

B7

GGE7

B18

GBE0

A20

GBE1

B17

GBE2

A19

GBE3

B16

GBE4

A17

GBE5

A16

GBE6

A15

GBE7

A6

GRO0

C7

GRO1

B6

GRO2

A5

GRO3

D7

GRO4

B5

GRO5

C6

GRO6

A4

GRO7

C13

GGO0

B15

GGO1

A14

GGO2

B14

GGO3

A13

GGO4

C12

GGO5

B13

GGO6

A12

GGO7

C18

GBO0

E17

GBO1

C17

GBO2

B19

GBO3

E16

GBO4

C16

GBO5

C15

GBO6

D14

GBO7

F14

F15

G6

G15

G16

J16

L16

VIO7

VIO8G5VIO9

VIO10

VIO11

VIO12

VIO13

VIO14M5VIO15

GND52

GND53

GND54

GND55

GND56R5GND57

GND58

GND59

Y7

P17

N12

N13

N17

N18

U12

U14

GFBK

GREF

GBLKSPL

GCOAST

GHSFOUT

PW181 Graphics Port

VIO1E6VIO2E8VIO3F5VIO4F6VIO5F7VIO6

GND47N8GND48N9GND49

GND50

GND51

N10

N11

M13

A11

D10

C14

A18

C9

SCL_H5V

SDA_H5V

T16

U11

U13

VCC3U5VCC4U9VCC5

VCC6

GND44

GND45

GND46

M10

M11

M12

R1301

X1301

C1301

VCLK

VVS

VHS

FIELD

VPEN

VR[7..0]

VG[7..0]

VB[7..0]

VCC1A2VCC2

PW818 POWER AND GROUND

GND40

GND41M8GND42M9GND43

L13

L18

SCL_H5V

5Vstby

SDA_H5V

C4

VPP1B4VPP2

GND37

GND38

GND39

L11

L12

C1302

VR0

VR1

VR2

VR3

VR4

VR5

VR6

VR7

VG0

VG1

VG2

VG3

VG4

VG5

VG6

VG7

VB0

VB1

VB2

VB3

VB4

VB5

VB6

VB7

R1334

R1314

R1315

R1335

V15V15pV25D3V3B

T11

T12

T13

T14

T15

VDD31

VDD32

VDD33

VDD34

VDD35

GND31

GND32

GND33

GND34L8GND35L9GND36

L10

K11

K12

K13

RXD

TXD

IR_181

NMI

U1301B

E1

E3

F3

D1

N2

E2

F1

F2

G3

G2

H3

H2

G1

J4

H1

J3

J2

J1

K3

K2

K1

L2

L1

L3

L4

M3

M1

N1

M2

SD

SCL_H3V

Q1301

G

G

Q1302

SD

SDA_H3V

R13

R14

R15

T10

VDD24

VDD25

VDD26

VDD27T6VDD28T7VDD29T9VDD30

GND24

GND25

GND26

GND27K4GND28K8GND29K9GND30

J11

J12

J13

K10

VCLK

VVS

VHS

FIELD

VPEN

VR0

VR1

VR2

VR3

VR4

VR5

VR6

VR7

VG0

VG1

VG2

VG3

VG4

VG5

VG6

VG7

VB0

VB1

VB2

VB3

VB4

VB5

VB6

VB7

P16

J10

D3V3C

R1316

P15

VDD23

R1303

R1304

PW181 Video Port

C1324

N15

N16

VDD19

VDD20P5VDD21P6VDD22

GND18

GND19

GND20

GND21J8GND22J9GND23

H10

H11

H12

H13

R1306

R1307

R1308

SDA_H3V

SCL_H3V

SDA_S3V

SCL_S3V

REMARK:

HARDWARE I2C: SD A1 SCL1

SOFTWARE I2C: VSDA VSCL

D3V3B

MREST

Q1303

5V

3

C1303

E14

E15

F16

H16

K16

VDD8

VDD9

VDD10H5VDD11

VDD12J5VDD13K5VDD14

VDD15L5VDD16N5VDD17N6VDD18

GND9

GND10

GND11

GND12G4GND13

GND14H4GND15H8GND16H9GND17

D11

D12

D13

D15

G17

VDD7

D3V3B

R1329

R1321

R1322

R1323

VGASEL

SDA_H3V

SCL_H3V

GAFEOE

MUTE

SEL1

SEL0

KEY0

KEY1

KEY2

KEY3

KEY4

KEY5

KEY6

SP_RELAY

R1309

D3V3B

COMMUNIC

P_SCLK

P_SDATA

P_SLE

DTXON

HPD_DET

3450_rest

D3V3B

D3V3B

R1311

R1312

R1313

U1302

INPUT

OUTPUT

GND

1

E10

E11

E12

E13

VDD1E7VDD2E9VDD3

VDD4

VDD5

VDD6

GND1A1GND2B2GND3B3GND4D4GND5D5GND6D8GND7D9GND8

D1302

R1333

R1310

R1325

R1332

R1331

R1326

R1324

L1302

2

4

TAB

C1355

C1326

U1303

D3V3B

3

INPUT

U1301E

V15

C1333 C1334 C1335 C1336 C1337 C1338 C1339 C1340 C1341 C1342 C1343

V15

12

C1346

C1325

GND

1

C1349 C1350

RESET

U1301D

Y11

RESET

E5

MCKEXT

D6

DCKEXT

A3

XI

C5

XO

Y12

RXD

V12

TXD

V11

IRRCVR0

W11

IRRCVR1

V13

PORTA0

W13

PORTA1

Y13

PORTA2

Y14

PORTA3

W14

PORTA4

Y15

PORTA5

W15

PORTA6

V15

PORTA7

R17

PORTB0

W18

PORTB1

V18

PORTB2

Y18

PORTB3

U18

PORTB4

Y19

PORTB5

W19

PORTB6

T18

PORTB7

T17

PORTC0

V16

PORTC1

W16

PORTC2

Y16

PORTC3

V17

PORTC4

U17

PORTC5

W17

PORTC6

Y17

PORTC7

P1

CPUTMS

Y2

CPUTCK

M4

CPUDI

N3

CPUDO

U16

MODE0

N4

MODE1

T5

MODE2

P2

MODE3

U15

ADR24B

RNMI2

C1304 C1305 C1306 C1307 C1308 C1309

2

OUTPUT

4

TAB

C1357

L1301

PW181 MISC

BHEN

ROMOE

ROMWE

RAMOE

RAMWE

EXTINT

DNC1

DNC2

DNC3

L1304

C1312

C1332

U4

A0

T4

A1

V3

A2

U3

A3

Y1

A4

W2

A5

T3

A6

V2

A7

U2

A8

W1

A9

R4

A10

V1

A11

P4

A12

R3

A13

T2

A14

U1

A15

T1

A16

R2

A17

R1

A18

P3

A19

V10

D0

Y10

D1

Y9

D2

W9

D3

V9

D4

Y8

D5

W8

D6

V8

D7

W7

D8

U8

D9

V7

D10

W6

D11

Y6

D12

V6

D13

U7

D14

U6

D15

W3

RD

Y3

WR

W12

V5

W4

W5

Y5

Y4

CS1

V4

CS0

U10

W10

NMI

B20

C19

V14

C1344

C1351 C1352 C1353

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

C1331

V15p

A[19..1]

D[15..0]

ROMOEn

ROMWEn

V25

C1330 C1329 C1328

U1301C

D3V3B

V15

Title

13-SCALER

A3

Date: 14-Oct-2005 Sheet of

File: F:\4228\4228_temp_ddb\4228_Temp.DDBDrawn By:

DCLK

DVS

DHS

DEN

DRE1

DRE5

DRE6

DRE0

DRE7

DRE3

DRE2

DRE4

DGE1

DGE0

DGE3

DGE2

DGE7

DGE6

DGE5

DGE4

DBE0

DBE3

DBE1

DBE2

DBE4

DBE7

DBE6

DBE5

DRO0

DRO1

DRO2

PW181 Display Port

DRO3

DRO4

DRO5

DRO6

DRO7

DGO0

DGO1

DGO2

DGO3

DGO4

DGO5

DGO6

DGO7

DBO0

DBO1

DBO2

DBO3

DBO4

DBO5

DBO6

DBO7

Number RevisionSize

J17

R1317

R1318

C20

R1319

D18

R1320

N19

RP1302

DR1

Y20

DR5

W20

DR6

V20

DR0

V19

DR7

RP1303

U20

U19

DR3

DR2

R16

DR4

R18

RP1304

DG1

T20

DG0

T19

R20

DG3

R19

DG2

RP1305

P20

DG7

P19

DG6

P18

DG5

M18

DG4

RP1306

M17

DB0

L17

DB3

N20

DB1

M20

DB2

RP1307

M19

DB4

L20

DB7

L19

DB6

K17

DB5

K19

K20

DR1

K18

J20

DR5

J18

DR6

DR0

J19

H20

H19

DR7

DR3

H18

DR2

H17

DR4

G20

G19

DG1

G18

DG0

F20

DG3

F19

DG2

F18

DG7

E20

DG6

E19

DG5

E18

DG4

F17

D20

DB0

D19

DB3

D16

DB1

D17

DB2

DB4

DB7

DB6

DB5

For Samsung/Formosa panel

2005.05.22

C1322 C1321 C1320 C1319 C1318 C1317 C1316

C1315C1314C1313

RP1308

RP1309

RP1310

RP1311

RP1312

RP1313

Page 24

54321

31RAMA0

40

MA0

U1201A

82

VB0

83

VB1

84

VB2

85

VB3

86

VB4

D

VY[7..0]

VUV[7..0]

C

VVCLK

VVVS

VVHS

VY0

VY1

VY2

VY3

VY4

VY5

VY6

VY7

VUV0

VUV1

VUV2

VUV3

VUV4

VUV5

VUV6

VUV7

87

VB5

88

VB6

89

VB7

92

SVHS

93

SVVS

94

SVCLK

95

VG0

96

VG1

97

VG2

98

VG3

99

VG4

100

VG5

101

VG6

102

VG7

109

VR0

110

VR1

111

VR2

112

VR3

113

VR4

114

115

116

105

106

107

108

PW1231 VIDEO BLOCK

VR5

VR6

VR7

PVCLK

CREF

PVVS

PVHS

ADR:0x64

B

A

8

VSS0

71

VSS1

104

VSS2

134

53

79

91

122

147

78

76

123

11

29

32

17

20

23

14

U1201D

VSS3

1

PVSS0

9

PVSS1

PVSS2

PVSS3

PVSS4

PVSS5

PVSS6

DPAVSS

DPDVSS

MPAVSS

PW1231 POWER AND GROUND

ADDVSS

ADAVSS

ADGVSS

AVS33B

AVS33G

AVS33R

AVS33SVM

AVD33SVM

1 2 3 4 56

VDD0

VDD1

VDD2

VDD3

PVDD0

PVDD1

PVDD2

PVDD3

PVDD4

PVDD5

PVDD6

DPAVDD

DPDVDD

MPAVDD

ADDVDD

ADAVDD

ADGVDD

AVD33B

AVD33G

AVD33R

7

70

V25SW

103

133

30

52

80

V33SW1

90

121

146

160

AV25p1

77

75

AV25p2

124

10

28

AV25a

31

16

19

22

AV331

13

DR0

DR1

DR2

DR3

DR4

DR5

DR6

DR7

DG0

DG1

DG2

DG3

DG4

DG5

DG6

DG7

DB0

DB1

DB2

DB3

DB4

DB5

DB6

DB7

DCLK

DVS

DHS

ADSVM

ADR

ADG

ADB

VREFIN

VREFOUT

RSET

COMP

V33SW

157

RP1201

158

159

2

3

RP1202

4

5

6

149

RP1203

150

151

152

153

RP1204

154

155

156

139

RP1205

140

141

142

143

RP1206

144

145

148

136

R1212

R1211

137

138

R1213

12

21

18

15

26

C1203

27

R1214

24

25

C1243

C1247

AV331

C1211

C1210 C1212 C1213 C1214 C1215 C1216 C1217

C1227 C1228 C1229 C1230 C1231 C1232 C1233

VR[7..0]

VR0

VR1

VR2

VR3

VR4

VR5

VR6

VR7

VG[7..0]

VG0

VG1

VG2

VG3

VG4

VG5

VG6

VG7

VB[7..0]

VB0

VB1

MREST

VB2

VB3

VB4

VB5

VB6

VB7

VCLK

VVS

VHS

C1251

SCL_S3V

SDA_S3V

R1203

V33SW1V33SW

V33SW

R1202R1201

R1204

R1205

R1206

L1201

L1204L1203

R1207

R1208

R1215

X1201

U1202

3

INPUT

OUTPUT

TAB

GND

1

U1204

3

INPUT

OUTPUT

GND

1

C1249

C1248

C1201 C1202

C1244

5V V25SW

5V

V25SW

V25SW

V33SW

C1218C1241

2

C1242

4

2

C1245

4

TAB

AV25A

C1219 C1220 C1221 C1223

AV25P1

C1234 C1235 C1236

127

128

129

130

131

119

120

125

126

117

118

132

73

72

135

74

81

C1205

V33SW

C1222

TDO

TCK

TDI

TMS

TRST

I2CA1

I2CA2

SCL

SDA

XTALI

XTALO

RESET

DEN

TESTCLK

TEST

CGMS

MACRO

C1206 C1207 C1208

L1205

L1202

U1201B

PW1231 HOST IF BLOCK

C1209

C1250

C1246

V33SW

C1204

31RAMA0

31RAMA1

31RAMA2

31RAMA3

31RAMA4

31RAMA5

31RAMA6

31RAMA7

31RAMA8

31RAMA9

31RAMA10

31RAMA11

31RAMA12

31RAMA13

C1237 C1238 C1239 C1240

AV25P2V25SW

C1224 C1225

38

31RAMA1

36

31RAMA2

34

31RAMA3

33

31RAMA4

35

31RAMA5

37

31RAMA6

39

31RAMA7

41

31RAMA8

43

31RAMA9

42

31RAMA10

45

31RAMA11

46

31RAMA12

44

31RAMA13

47

51

R1209 R1210

38

CLK

23

A0

24

A1

25

A2

26

A3

29

A4

30

A5

31

A6

32

A7

33

A8

34

A9

22

A10

35

A11

20

BA0

21

BA1

VssQ

6

AV331V33SW

Title

12-DEINTERLACE

Number RevisionSize

B

Date: 14-Oct-2005 She et of

File: F:\4228\4228_temp_ddb\4228_Temp.DDB Drawn By:

MA1

MA2

MA3

MA4

MA5

MA6

MA7

MA8

MA9

MA10

MA11

MA12

PW1231 MEMORY BLOCK

MA13

MCLKFB

MCLK

U1201C

V33SW

3

9

1

14

Vdd

Vdd

VddQ

VddQ

U1203

VssQ

Vss

Vss

VssQ

VssQ

12

28

41

46

52

MD15

MD14

MD13

MD12

MD11

MD10

MD9

MD8

MD7

MD6

MD5

MD4

MD3

MD2

MD1

MD0

MRAS

MCAS

MWE

43

49

27

Vdd

VddQ

VddQ

CAS

RAS

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

CKE

DQML

/CS

NC

DQMH39NC

Vss

15

19

36

40

54

6

68

66

64

62

60

58

56

54

55

57

59

61

63

65

67

69

48

49

50

WE

R1216

R1217

R1218

31RAMD15

31RAMD14

31RAMD13

31RAMD12

31RAMD11

31RAMD10

31RAMD9

31RAMD8

31RAMD7

31RAMD6

31RAMD5

31RAMD4

31RAMD3

31RAMD2

31RAMD1

31RAMD0

16

31WEn

17

31CASn

18

31RASn

2

31RAMD0

31RAMD1

4

31RAMD2

5

7

31RAMD3

8

31RAMD4

10

31RAMD5

11

31RAMD6

31RAMD7

13

42

31RAMD8

44

31RAMD9

45

31RAMD10

47

31RAMD11

48

31RAMD12

31RAMD13

50

51

31RAMD14

31RAMD15

53

V33SW

37

C1226

D

C

B

A

Page 25

321

4

A5V

C1026L1004

D

YPbPr_Pr

YPbPr_Y

YPbPr_Pb

VGASEL

C

VGAHS

VGAVS

B

R1005

R1006

5V

D1001 D1002

R1015

5V

JP1001

15

VGAVS

VGAHS

DDCC

DDCD

A

1 2 34

14

13

12

11

17

YPbPr_Pr

VGA R

YPbPr_Y

VGA G

YPbPr_Pb

VGA B

VGASEL

TVDD3.3V

1 2

C1041

11 10

C1042R1016

VGA5V

5

10

4

9

3

8

2

7

1

6

16

SGND

7 14

U1007C

SGND

2

3

5

6

11

10

14

13

1

15

R1007 R1009

U1007A

R1008 R1010

5V

16

S1A

VCC

S2A

S1B

S2B

S1C

S2C

S1D

S2D

IN

EN

3 4

13 12

D1003 D1004 D1005

U1004

8

SGND

5V

DA

DB

DC

DD

GND

U1007B

U1007D

4

7

9

12

HD1_R/Pr

HD1_G/Y

HD1_B/Pb

VGA_HS

VGA_VS

5V

HD1_R/Pr

HD1_G/Y

HD1_B/Pb

VGA_HS

VGA_VS

L1001

L1002

L1003

R1011 R1012 R1013

SGND

AGND

R1019

D1006 D1007

DDCC

VGA B

VGA G

VGA R

Title

Date: 14-Oct-2005 Sheet of

File: F:\4228\4228_temp_ddb\4228_T emp.DDB Drawn By:

DDCD

Number RevisionSize

A4

SC101 SC103 SC104SC102

R1021

R1020

U1008

7

VCLK

SCL

SDA

GND

VCC

NC1

NC2

NC3

R1022

6

5

4

10-PROGRESSIVE_ADC

D1015

8

1

2

3

1

3

C1003

D

C

VGA5V5V

2

B

A

Page 26

7654321

8

A[19..1]

D

C

B

A

ROMOEn

ROMWEn

RESETn

D3V3B

R401

R402

D[15..0]

1 2 3 4 5 6 78

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A12

A14

A17

A19

U401

26

CE

28

OE

11

WE

12

RESET

14

NC

47

BYTE

25

A0

24

A1

23

A2

22

A3

21

A4

20

A5

19

A6

18

A7

8

A8

7

A9

6

A10

5

A11

4

A12

3

A13

2

A14

1

A15

48

A16

17

A17

16

A18

FLASH_8M

JP401

1 2

D3V3B

3 4

JP402

1 2

3 4

5 6

7 8

9 10

11 12

13 14

15 16

17 18

19 20

21 22

23 24

25 26

27 28

29 30

31 32

33 34

35 36

37 38

39 40

41 42

43 44

45 46

47 48

49 50

51 52

53 54

55 56

57 58

59 60

R409

D15

D14

D5

D4

D3

D2

D9

D8

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

RY/BY

13

NC

37

Vdd

29

DQ0

31

DQ1

33

DQ2

35

DQ3

38

DQ4

40

DQ5

42

DQ6

44

DQ7

30

DQ8

32

DQ9

34

36

39

41

43

45

9

A19

10

NC

15

46

Vss

27

Vss

D3V3B

R410

A1A2

A3A4

A5A6

A7

A8A9

A10A11

A13

A15

A16

A18

D7

D6

D13

D12

D11

D10

D1

D0

D3V3B

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

C401

SW402

D3V3B

1 2

D3V3B

R411

R413R412

R404

SW401

1 2

TXD

RXD

R418

7

2

3

1

NMI

5V

C420

C416 C415

U403

SENCE

RESin

CT

CONTROL

R405

C406

TXD

RXD

R414

RSTINn

TLCCT

C407

C408

ADR:0xA0/MEMORY

ADR:0xD0/COMPANION

R408

R407

L404

5Vstby

5V

L405

5V#

16

U404

1

C1+

VCC

3

4

5

11

10

12

9

V+

C1C2+

V-

C2-

T1_IN

T1_OUT

T2_IN

T2_OUT

R1_OUT

R1_IN

R2_OUT

R2_IN

GND

15

R415

RESET

RESET

RESETn

Title

A3

Date: 14-Oct-2005 Sheet of

File: F:\4228\4228_temp_ddb\4228_Temp.DDBDrawn By:

L401

RESET

RESET

SDA_H5V

SCL_H5V

C417

C409

C410

R417

R416

D3V3B

C405

8

Vdd

6

5

4

GND

R406

C419C418

C402

C411

2

C412

6

L403

14

7

L402

13

8

SDA#SO

SCL#SO

4-FLASH

Number RevisionSize

D

U402

232_OUT

232_IN

R419

R420

R421

R422

4

GND

3

NC2

2

NC1

1

NC0

C

JP403

1

6

2

7

3

8

4

9

5

C414C413

10 11

JP404

4

5V

3

2

1

B

A

5

SDA

6

SCL

7

WP

8

VCC

TXD

RXD

SDA#SO

SCL#SO

Page 27

For sumsung panel standard LVDS jack

D

C

For sumsung panel

B

A

NC

DRE0

DRE1

DRE2

DRE3

DRE4

DRE5

DRE6

DRE7

DGE0

DGE1

DGE2

DGE3

DGE4

DGE5

DGE6

DGE7

DBE0

DBE1

DBE2

DBE3

DBE4

DBE5

DBE6

DBE7

TX0TX0+

TX1TX1+

TX2TX2+

CKCK+

TX3TX3+

SGND

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Formosa panel CPUGO

P_SDATA

Formosa panel PDPGO

P_DISPEN

TAB

4

RELAY_ON#

P_SDATA

VS_ON#

P_SCLK

P_SLE

P_DISPEN

2

4

C506

LVD33

ANDY

D

C

C507

00

B

A

321

R512

LVD33

DCLK

DRE[7..0]

DGE[7..0]

DBE[7..0]

DHS

DVS

DEN

DCLK

DHS

DVS

DEN

1 2 34

L501

L502

C502C501

For LG panel

DRE2

DRE3

DRE4

DRE5

DRE6

DRE7

DRE0

DRE1

DGE2

DGE3

DGE4

DGE5

DGE6

DGE7

DGE0

DGE1

DBE2

DBE3

DBE4

DBE5

DBE6

DBE7

DBE0

DBE1

LVD_PLL33

C520

C522

C524

LVD_VCC

C521

C523

C525

R501

RS

R502

34

1

9

26

44

31

TxCLK_IN

VCC

VCC

51

TxIN0

52

TxIN1

54

TxIN2

55

TxIN3

56

TxIN4

3

TxIN6

50

TxIN27

2

TxIN5

4

TxIN7

6

TxIN8

7

TxIN9

11

TxIN12

12

TxIN13

14

TxIN14

8

TxIN10

10

TxIN11

15

TxIN15

19

TxIN18

20

TxIN19

22

TxIN20

23

TxIN21

24

TxIN22

16

TxIN16

18

TxIN17

27

TxIN24

28

TxIN25

30

TxIN26

25

TxIN23

VCC

LVDS_VCC

TxCLKOUT-

TxCLKOUT+

PWR_DWN

U501

/ DS90C385AMTD

LVDS_GND

LVDS_GND

LVDS_GND

GND

GND

GND

GND

5

13

21

29

53

TxOUT0-

PLL_VCC

TxOUT0+

TxOUT1TxOUT1+

TxOUT2TxOUT2+

TxOUT3TxOUT3+

R_FB

PLL_GND

PLL_GND

GND

48

47

46

45

42

41

38

37

40

39

32

17

35

33

49

43

36

1 2

TX0-

3 4

TX0+

5 6

TX1-

7 8

TX1+

9 10

TX2TX2+

CKCK+

TX3TX3+

TX0TX0+

TX1TX1+

TX2TX2+

TX3TX3+

CKCK+

DTXON

LVD33

JP501

11

13

15

17

19

21

R508

R509

22

DTXON

R503

R504

R510

R511

P_SDATA#

12

P_SCLK#

14

P_SLE#

16

18

P_DISPEN#

20

For LG panel standard LVDS jack

TX0TX0+

TX1TX1+

TX2TX2+

CKCK+

TX3TX3+

p_dispen#

p_sdata#

p_sclk#

p_sle#

NC

SGND

CPUGO

SCL_S3V

SDA_S3V

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

PDPGO

PDWN

5V

C510

Title

Number RevisionSize

A4

Date: 14-Oct-2005 Sheet of

File: F:\4228\4228_temp_ddb\4228_Temp.DDB Drawn By:

L504

C527

R513

L505

C528

L506

IRQ

C529

L503

C526

U502

3

INPUT

C505

5-LVDS&TMDS

P_SCLK

P_SLE

OUTPUT

GND

1

Page 28

5V

L611

L612

L613

L614

L615

L616

L617

54321

L602

L608

C618

C626

RELAY_ON

L623

L624

VS_ON

5VDetect

L625

5Vstby

Q603

5V

R627

R624

5Vstby

IR_mcu

R632

IR_181

R631

R633

5Vstby

R608

C633

Title

B

Date: 14-Oct-2005 She et of

File: F:\4228\4228_temp_ddb\4228_Temp.DDB Drawn By:

L620

L621

L622

R611

R612

C634

C635

C636

6-POWER MANAGE

Number RevisionSize

C637

R613

C617C625

C648C649 C650

C644

LED_G

IR_5V

D3V3B

R614

C638

C639 C640

D3V3B

C614C623

D

C

B

A

D3V3C

C624

D3V3D

C630C631

D3V3_TT_A

C642C643

VS_ON

SB_5VCN key_stby

5VDetect

P_ON/SLEEP

P_DISPEN

COMMUNIC

IR_mcu

D3V3B

R601

P_ON/SLEEP

1 2 3 4 56

L607

R602

R607

SGND

1

2

3

4

5

6

7

8

L606

L628

L629

U602

PA3

PA2

PA1

PA0

PB2

PB1/_BZ

PB0/BZ

VSS

PC0/_INT9PC1/TMR

Q601

R603

R604

OSCO

OSCI

VDD

/RES

D3V3#

C621

mut#

18

PA4

17

PA5

16

SDA#

PA6

15

SCL#

PA7

14

OSCO

13

OSCI

5V_mcu

12

11

RST

10

5Vstby

R605

R606

Q602

2

4

C613C622

VS_ON

5VDetect

P_ON/SLEEP