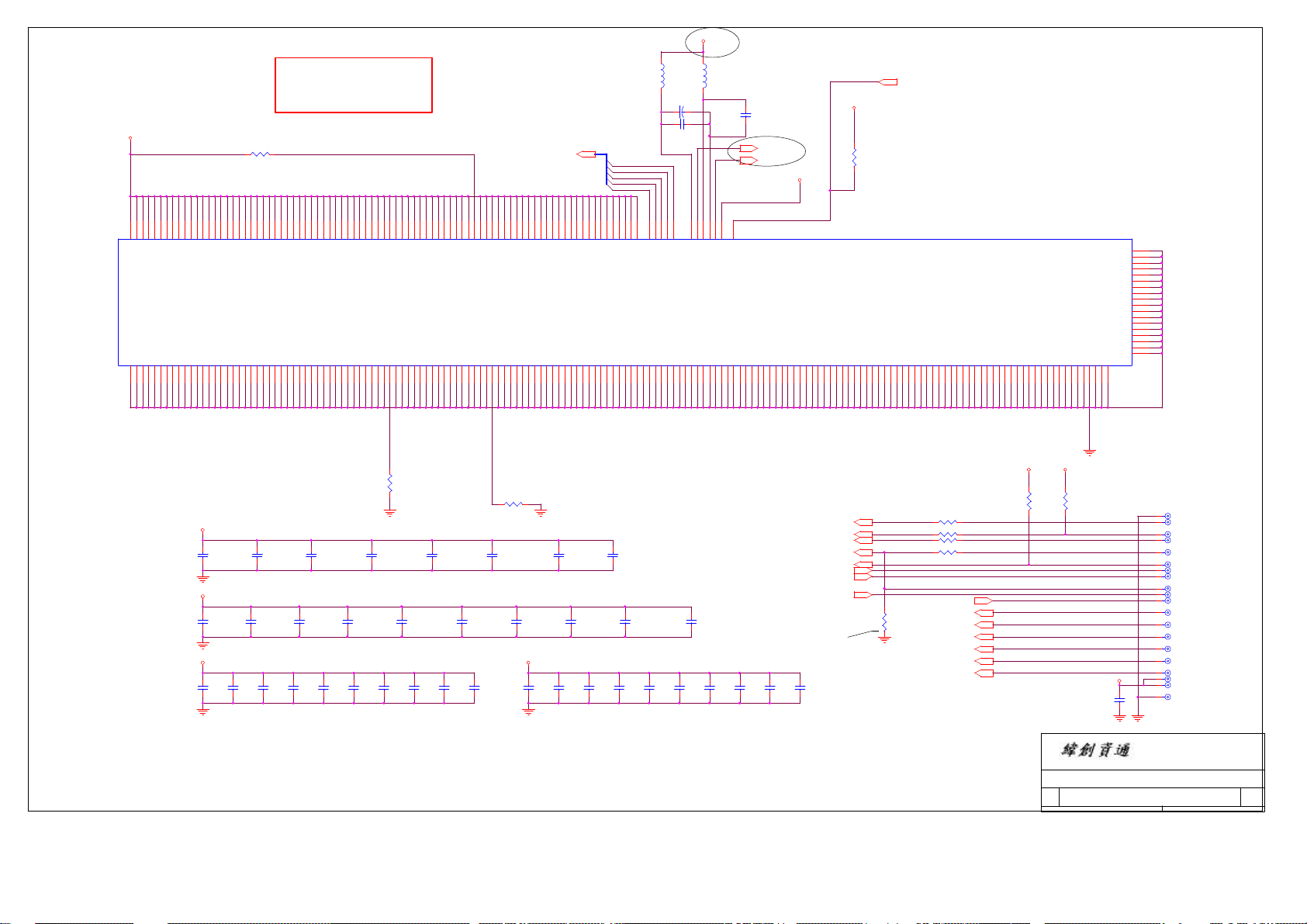

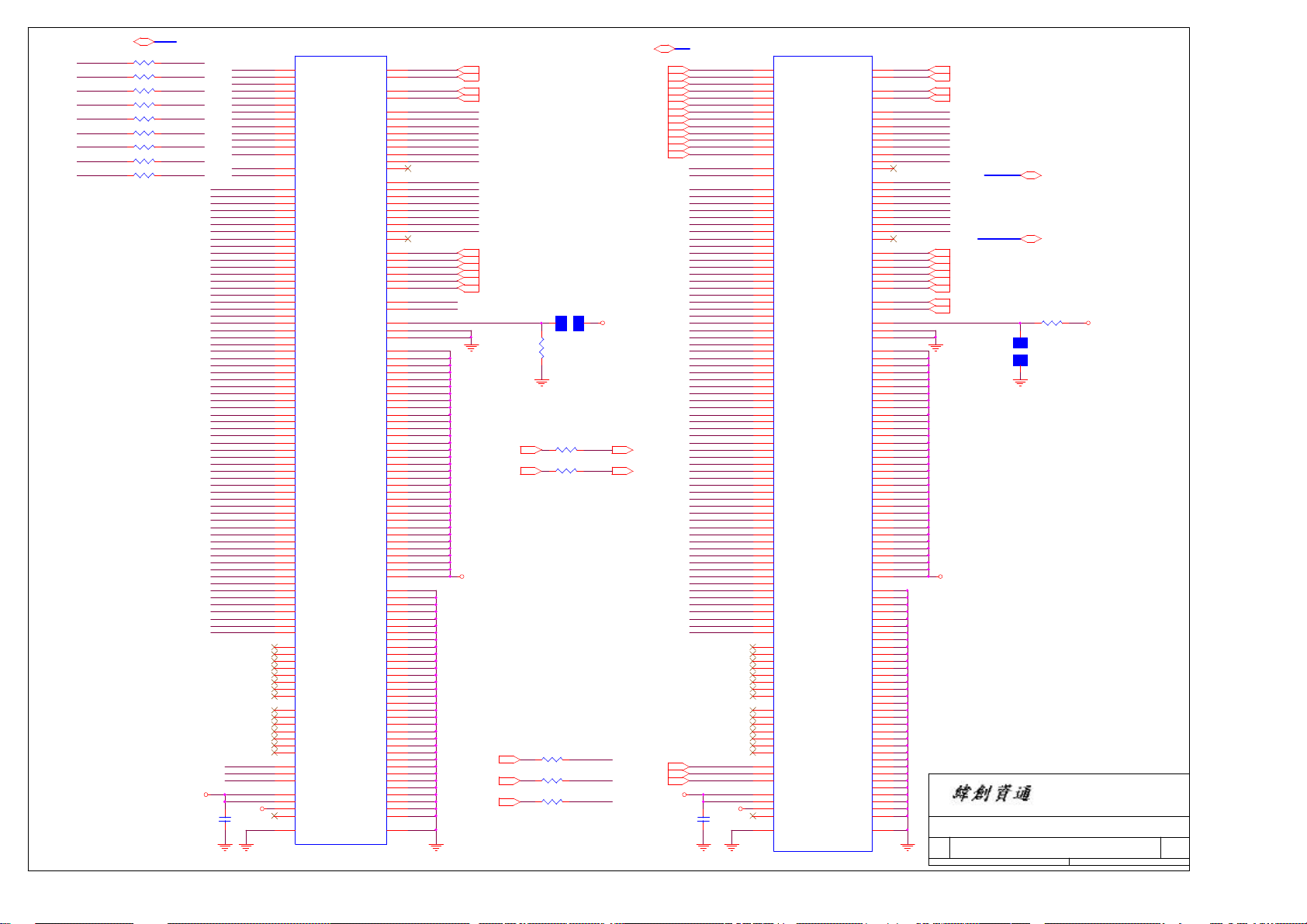

Acer TravelMate 240, TravelMate 5F250 Schematics

A

B

C

D

E

SYSTEM DC/DC

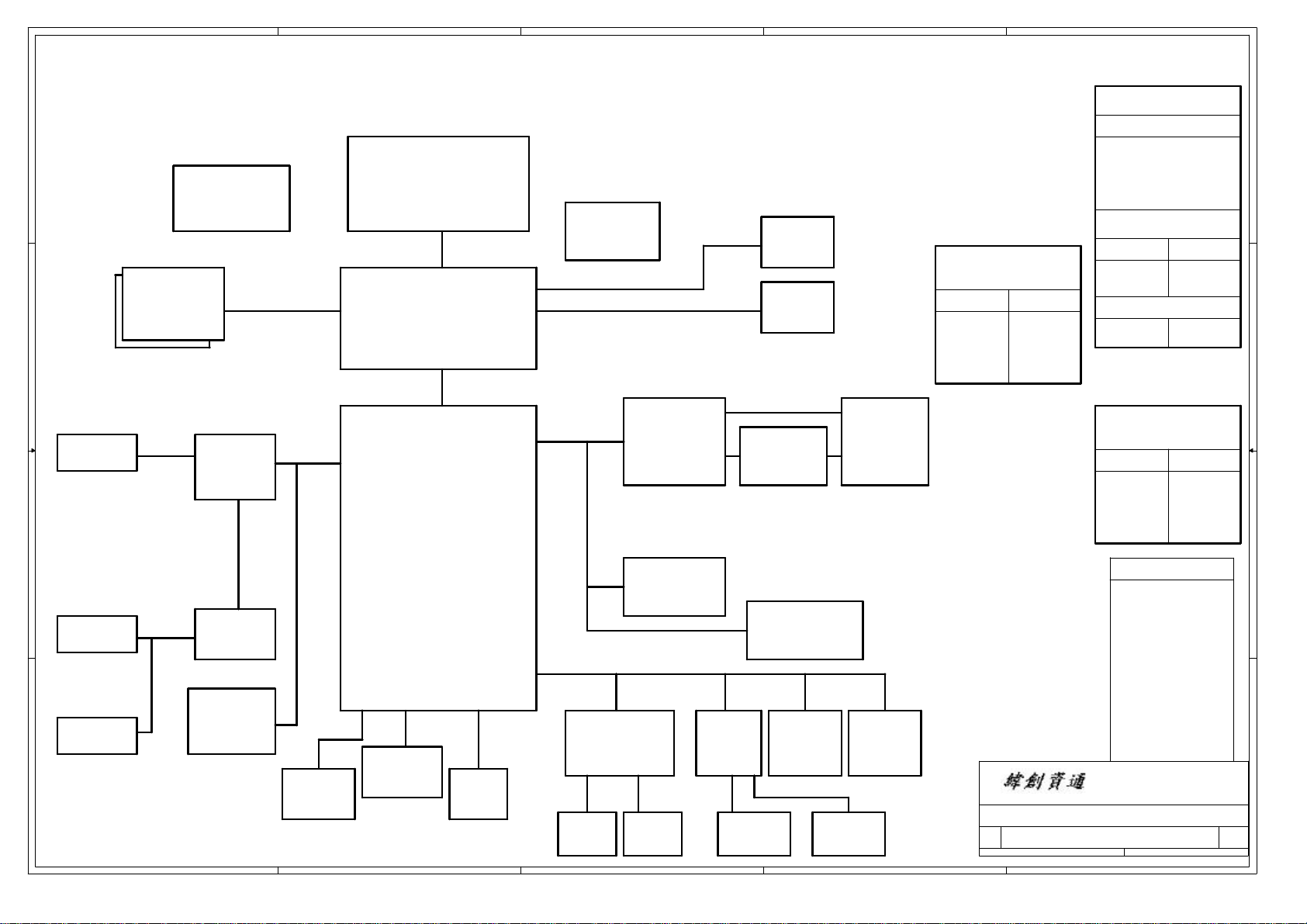

YUHINA Block Diagram

4 4

Mobile CPU

CLK GEN.

CY28346

3 4, 5

DDR*2

333MHz

9,10

3 3

266/33 3MHz

Portability

Mobile P4

HOST BUS

133MHz

GMCH

Montara-GT

6,7,8

HUB I/F

66MHz

G768D

16

RGB

LVDS

Project code: 91.49V01.001

PCB P/N : 48.49V01.0SC

REVISION : 03207-SC

CRT

CONN

12

LCD

XGA/SXGA+

11

CPU DC/DC

MAX1546ETL

CM2843ACIM25

INPUTS

DCBATO UT

31,32

31

OUTPUTS

+VCC_CORE

1.3V 44A

+VID

1.2V 0 .3A

MAX1999

INPUTS

DCBATO UT

SYSTEM DC/DC

MAX1715

INPUTS OUTPUTS

DCBATO UT

LP2996

OUTPUTS

5V_S5

5V_S3

5V_S0

3D3V_S 5

3D3V_S 3

3D3V_S 0

3D3V_LAN AC

2D5V_S 3

1D5V_S 0

1D25V_ S02D5V_S 3

33

30

30

MAXIM CHARGER

Line In

Mic In

PCI BUS

23

AC'97

CODEC

CS4299XQ

AC-Link

22

CARDBUS

PCI 1520

GHK

25/B/1

PWR SW

TPS2224A

26

ICH4-M

2 2

LAN

RTL 8101L

21/D/4

Line Out

23

OP AMP

G1421

23

LPC BUS

13,14,15

MODEM+BT

INT.SPKR

1 1

23

MDC Card

18

A

PIDE

HDD

CD ROM

17

SIDE

B

17

USB

4 PORT

NS SIO

PC87392

18

PRN

Port

29

FIR

28

C

19,20

KBC

M38857

Mini-PCI

802.11A /B/G

Touch

Pad

25 25

FWH

4MB

PLCC32

SOIC40

CARDBUS

TWO SLOT

27 27

21

LPC

DEBUG

CONN.

24 242528

INT KB

D

MAX1645

DCBATO UT

34

OUTPUTSINPUTS

BT+

18V 4 .0A

UP+5V

5V 10 0mA

PCB LAYER

L1:

Signal 1

L2:

VCC/GN D

L3:

Signal 2

L4:

Signal 3

L5:

GND

L6:

Signal 4

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Title

BLOCK DIAGRAM

Size Document Number Rev

Custom

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

YUHINA

E

1 39Monday, April 28, 2003

SC

1D2V_VID

1D5V_S0

1D5V_S5

2D5V_S0

2D5V_S3

1D2V_VID 4,5,31

1D5V_S0 6,7,8,13,15,24,30,39

1D5V_S5 15,33

2D5V_S0 8,36

2D5V_S3 6,8,9,10,30,36

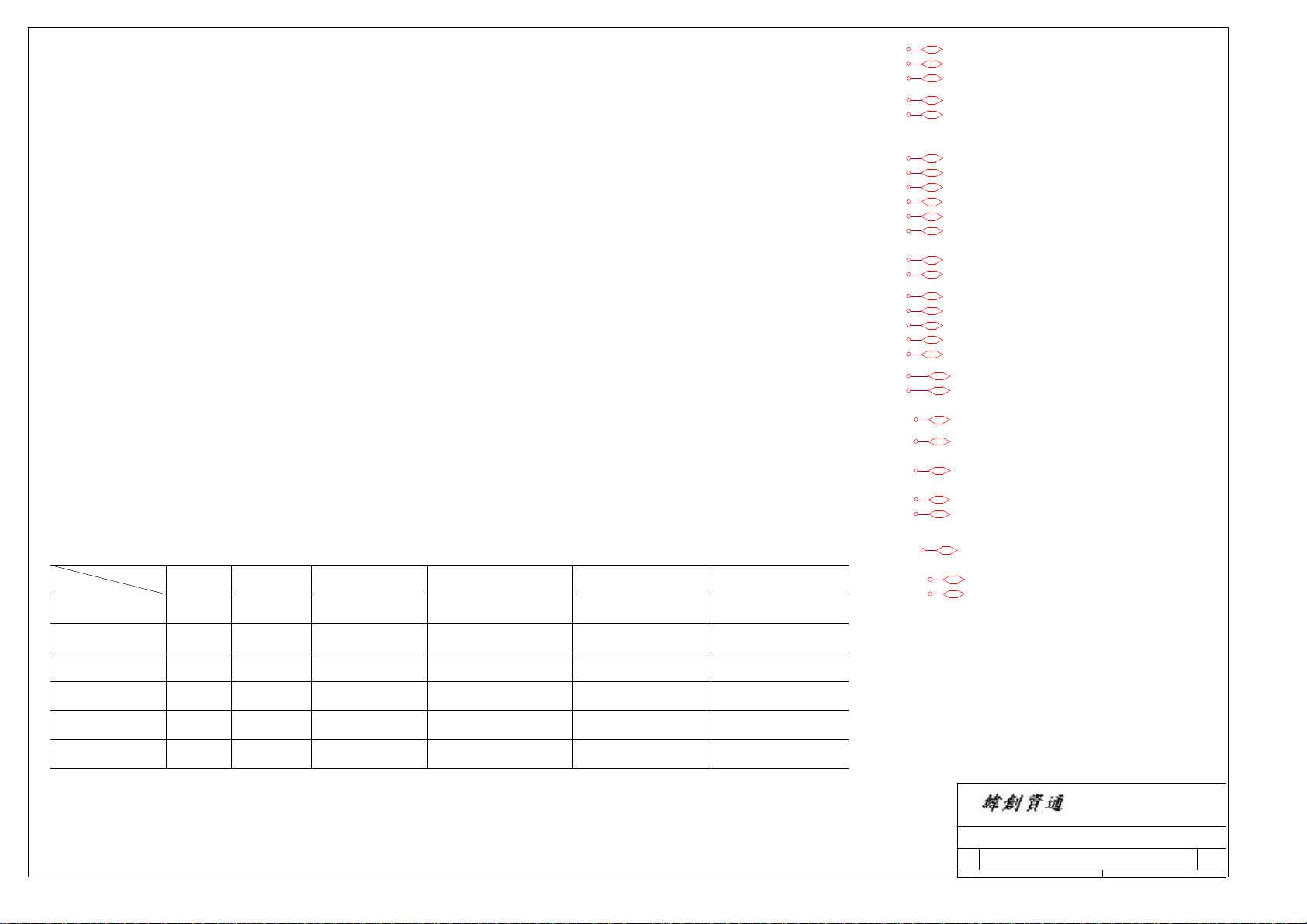

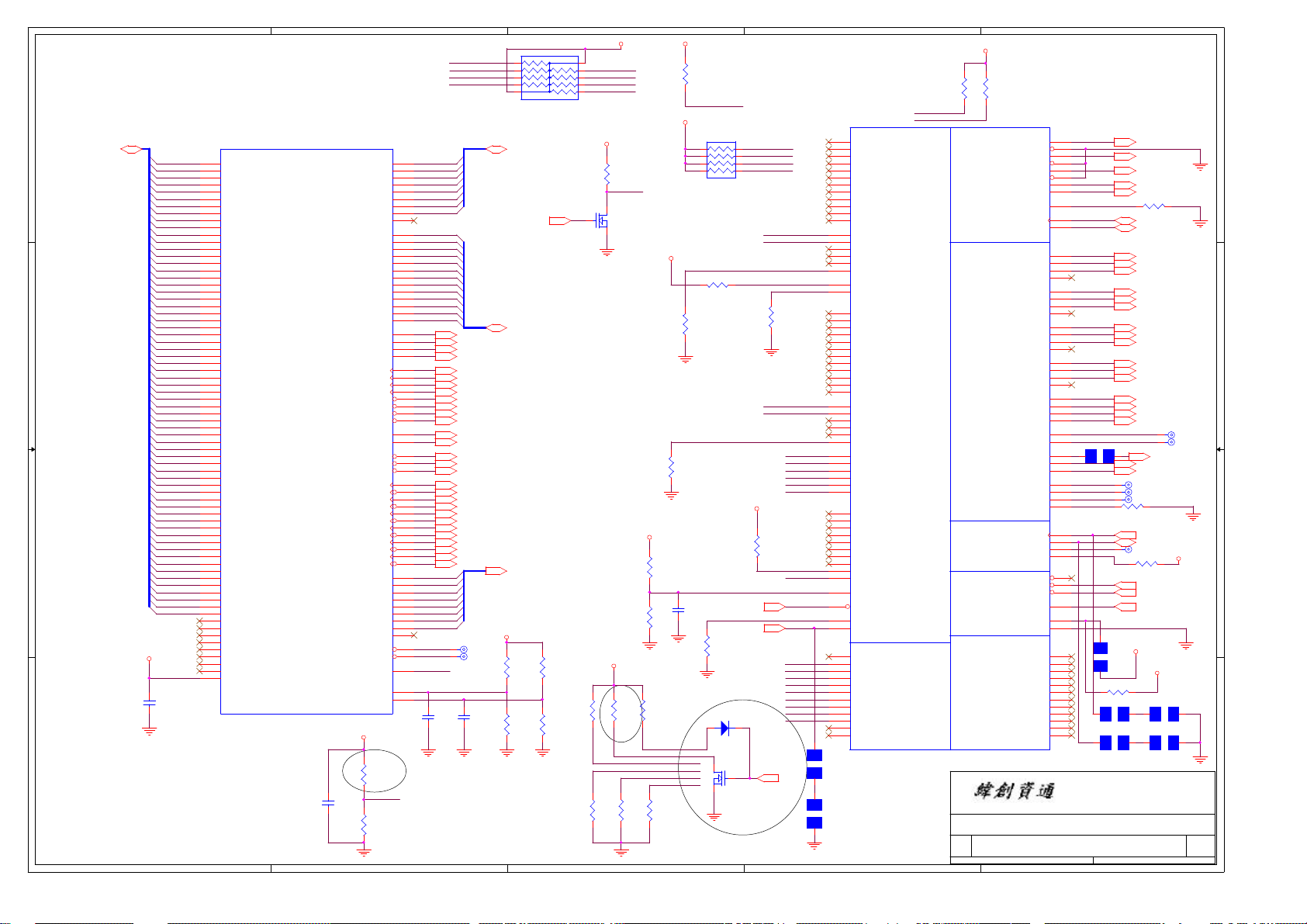

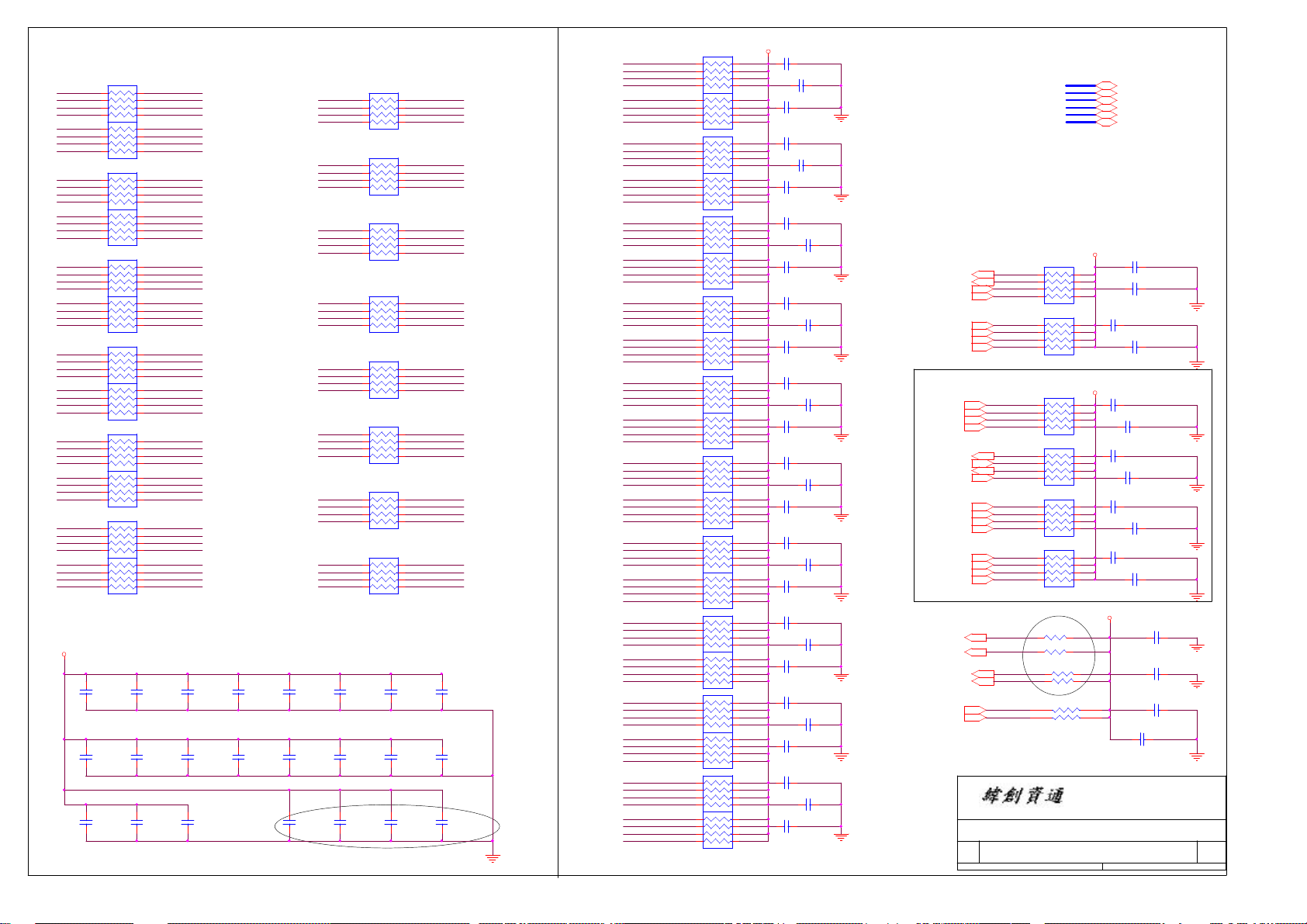

PCI DEVICE RESOURCE ASSIGNMENT

BUS DEV ICE

IDSEL PCI_REQ# PCI_GNT# INT_I RQ#

3D3V_S0

3D3V_S3

3D3V_S5

2D5V_LAN_S5

3D3V_LAN_S5

VCC_RTC_S5

5V_USB1_S0

5V_USB3_S0

5V_CRT_S0

5VA_AUD_S0

5V_S0

5V_S3

5V_S5

+5V_UP_S5

5V_AUX_S5

LCDVDD

DCBATOUT

ICH_VBIAS

RTC_AUX_S5

FAN1_VCC

A_SKT_VCC_S0

A_SKT_VPP_S0

3D3V_S0 3,6,8,9,11,12,13,14,15,16,17,18,19,21,22,24,25,26,27,28,30,31,36,38,39

3D3V_S3 11,22,25,36,39

3D3V_S5 3,4,13,14,15,18,22,33,36,37,39

2D5V_LAN_S5 19

3D3V_LAN_S5 18,19,20,36

VCC_RTC_S5 14

5V_USB1_S0 18

5V_USB3_S0 18

5V_CRT_S0 12

5VA_AUD_S0 22,23,38

5V_S0 11,12,14,15,16,17,18,21,22,23,24,25,27,28,29,31,32,34,36,39

5V_S3 30,33,36,38

5V_S5 15,33

+5V_UP_S5 11,25,34,35,37,39

5V_AUX_S5 16,35,37,38,39

LCDVDD 11

AD+

AD+ 34,35,39

DCBATOUT 11,30,32,33,34,36,37,39

ICH_VBIAS 14

RTC_AUX_S5 14

FAN1_VCC 16

A_SKT_VCC_S0 26,27

A_SKT_VPP_S0 27

LAN

CardBus

MiniPCI

1

1

1

5

9

6

PCI_AD26

PCI_AD20

PCI_AD21

REQ#4

REQ#1

REQ#2

GNT#4

GNT#1

GNT#2

IRQD#

IRQB#/IR QA#

IRQE#

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Title

Table of Content / HISTORY

Size Document Number Rev

A3

Date: Sheet of

Taipei Hsien 221, Taiwan, R.O.C.

YUHINA

2 39Thursday, May 29, 2003

SC

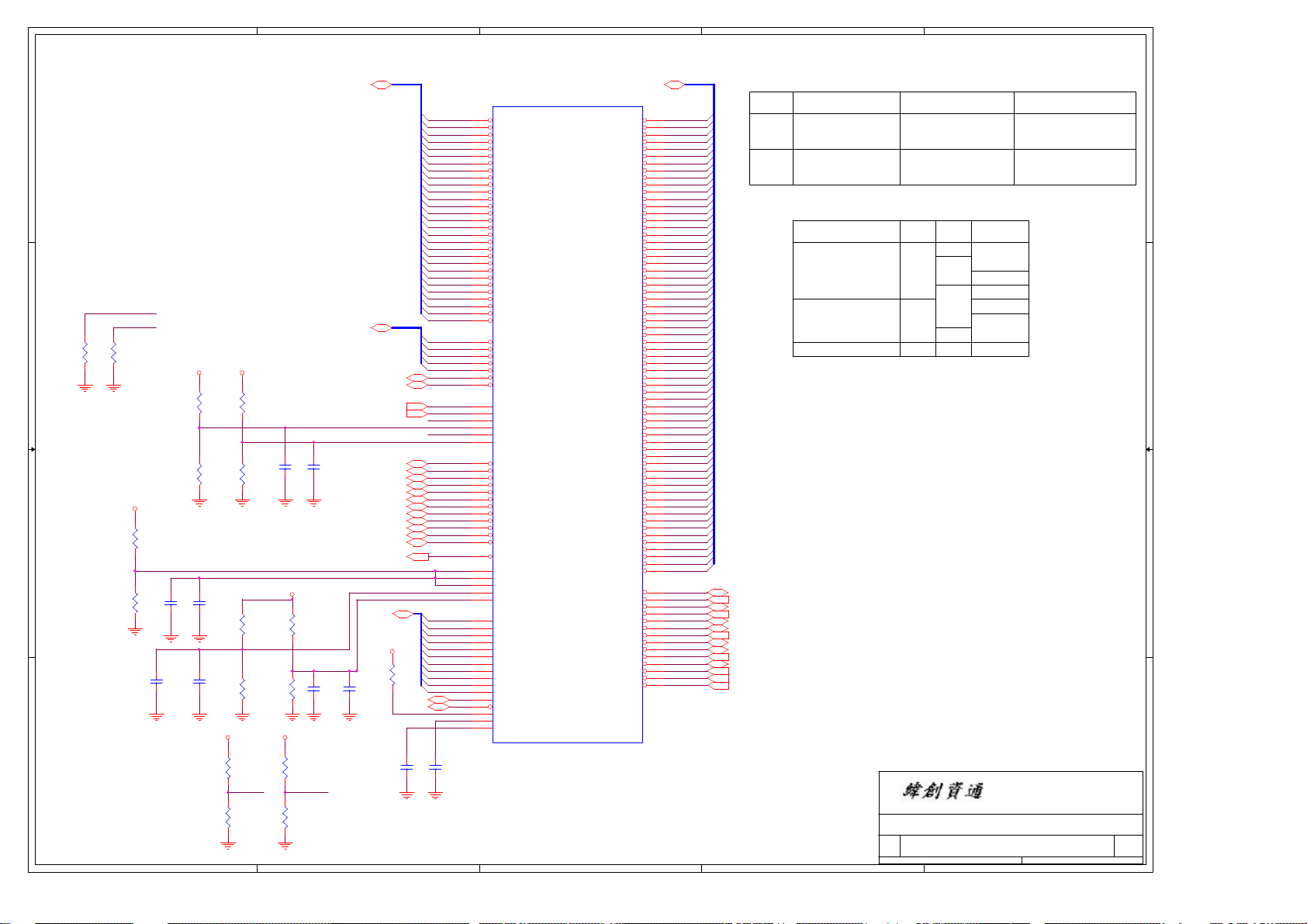

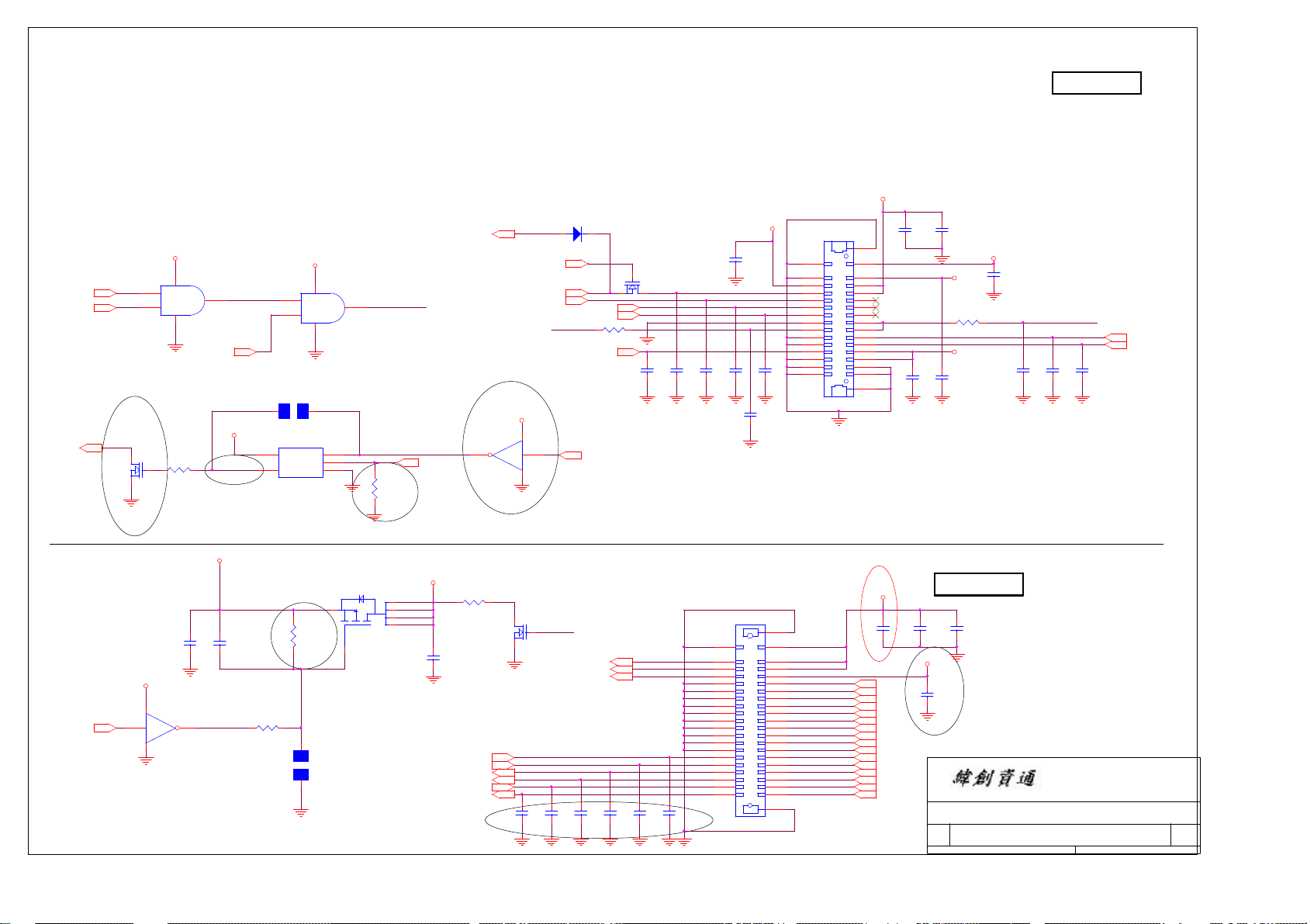

CLKPCIF_ICH13

PCLK_PCM26

PCLK_LAN19

PCLK_KBC25

PCLK_SIO28

PCLK_FWH24

PCLK_MINI21

PCLK_DEBUGBD24

CLK66_MCH6

CLK66_ICH13

CLK66_LVDS6

TP10 TPAD30

3D3V_S0

SMBD_ICH9,14

SMBC_ICH9,14

SB

SMBD_ICH

SMBC_ICH

CKG_CLKEN#14

CLK66_AGP

CPU & MEMORY Freq . Selection

3D3V_S0

CPU BSEL1 BSEL0

400MHz

12

R135

1KR3

12

R129

1KR3

CKG_FS1_1

CKG_FS0

12

R126

DUMMY-R3

533MHz00

R125 0R3-0-U

1 2

1 2

R618 DUMMY-R3

CKG FS1 FS0

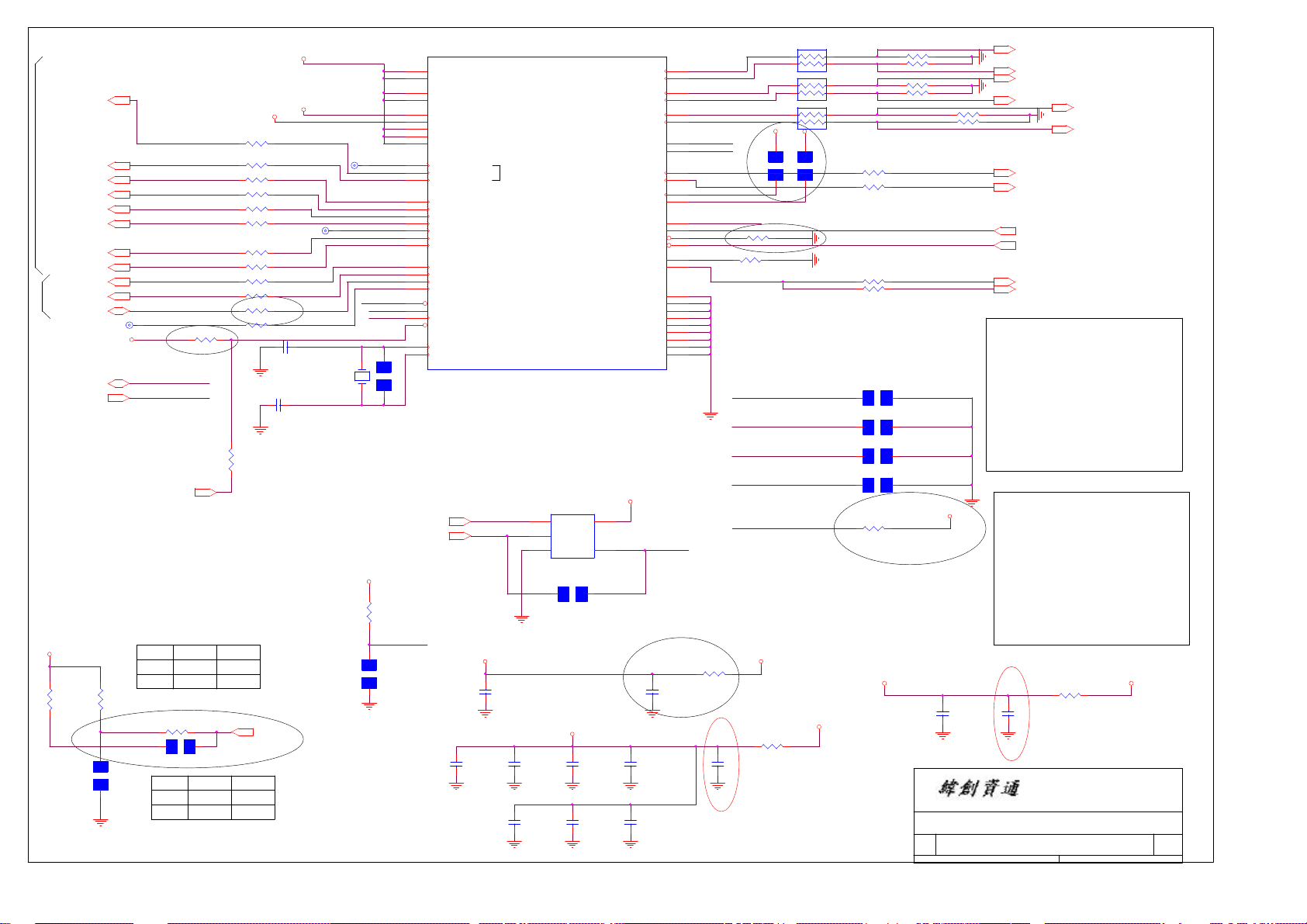

CY28346

100MHz

133MHz

SB

R168

1 2

10KR3

0

1

VCCA_CKG48

R155

R156

1 2

R157

1 2

R158

1 2

R159

1 2

R160 33R2

1 2

R161

1 2

R162

1 2

R163

1 2

R164

1 2

R165

1 2

R166

1 2

CKG_CLKEN#_1

1 2

R167

0R2-0

1 2

0

1

BSEL0 4,6

1

1

VCCD_CKG

VCCA_CKG

33R21 2

33R2

33R2

33R2

33R2

TP71TPAD30

33R2

33R2

33R2

33R2

22R2

33R2

BC39

1 2

CK-408_GEN_X1

SC10P50V2JN-1

X-14D31818M-1

BC38

CK-408_GEN_X2

SC10P50V2JN-1

No stuf f:

caps a re

internal to

CK-TITA N.

SB

TP70TPAD30

PCICLK_F0

CLKPCIF_ICH_1

PCLK_CBUS_1

PCLK_LAN_1

PCLK_KBC_1

PCLK_SIO_1

PCLK_FWH_1

PCICLK4

PCLK_MINI_1

LPC_DB_PCICLK_1

CLK66_DREF_GMCH_1

CLK66_ICH_1

CLK66_LVDS_1

CLK66_AGP_1

CKG-PD#

SMBD_ICH

SMBC_ICH

X1

1 2

Placed within 500

mils of CK-408

3D3V_S0

12

12

12

R144

DUMMY-R3

PM_SLP_S3#14,15,22,25,30,33,36

PM_SLP_S1#14

R448

10KR3

CK-408_MULT0

R447

DUMMY-R3

U19

8

VDDPCI

14

VDDPCI

50

VDDCPU

46

VDDCPU

26

VDDA

37

VDD48

32

VDD3V66

19

VDD3V66

1

VDDREF

5

PCICLK_F0

6

PCICLK_F1

7

ASEL/PCICLK_F2

10

PCICLK0

11

E_PCICLK1/PCICLK1

12

PCICLK2

13

E_PCICLK3/PCICLK3

16

PCICLK4

17

PCICLK5

18

PCICLK6

21

3V66_2

22

3V66_3

23

3V66_4

24

3V66_5

*

25

PD#

29

SDATA

30

SCLK

28

VTT_PWRGD#

2

X1

3

X2

CY28346-2ZCT

CK-408

V1.1

Free running

*

** *

CPUCLKT0

CPUCLKC0

CPUCLKT1

CPUCLKC1

CPUCLKT2

CPUCLKC2

**

48MHZ_USB/FS2

48MHZ_DOT

**

3V66_1/VCH_CLK/FS3

3V66_0/FS4

****

MULTSEL

*

CPU_STOP#

*

PWRSAVE#

*

PCI_STOP#

* These inputs have 120K internal pull-u p resistor to VDD

** Internal pull-down resi stors to ground

Primary Source: ICS950813 TSSOP

Secondary Source: CY28346-2 TSSOP

If S1 doesn't support power down

mode, this AND gate can be dummy

1

2

VCCA_CKG

C518

SCD1U16V

C514

SCD1U16V

C503

SCD1U16V

C515

SCD1U16V

U18

A

VCC

B

GND3Y

DUMMY-NC7SZ08-U

R465 DUMMY-R3

1 2

VCCD_CKG

5

4

C502

SCD1U16V

C516

SCD1U16V

3D3V_S5

CKG-PD#

FS1

FS0

IREF

REF

GND

GND

GND

GND

GND

GND

GND

GND

GND

SB

12

C505

SCD1U16V

C517

SCD1U16V

52

CLK_CPU_1

51

CLK_CPU#_1

49

CLK_MCH_1

48

CLK_MCH#_1

45

CLK_ITP_R_1

44

CLK_ITP#_R_1

CKG_FS1_1

55

54

CKG_FS0

CLK48_ICH_1

39

38

CLK48_DREF_GMCH_1

35

33

43

53

40

34

42

IREF_1

56

4

9

15

20

27

47

41

36

31

R146

1 2

2D2R5

C128

SC10U6D3V5MX

RN5 SRN33-2-U2

RN6 SRN33-2-U2

RN7 SRN33-2-U2

3D3V_S0 3D3V_S0

R628

DUMMY-R3

FS3

FS4

CK-408_MULT0

1 2

FS2

R614 10KR2

R127 475R3F12

CLK14_ICH_1

CLK66_DREF_GMCH_1

CLK66_ICH_1

CLK66_LVDS

CLK66_AGP

CLK48_ICH_1

Save two 4.7u F capacitor

3D3V_S0

300 ohm@100MHz

600mA

R133

1 2

0R5

C492

DUMMY-SC4D7U10V5ZY

1

2 3

1

2 3

1

2 3

12

4

4 R443 49D9R3F1 2

4

12

R629

DUMMY-R3

ICS950813(PIN40->TESTPAD,R450->10K)

CY28346-2(PIN40->PL 10K TO GND,R450->DUMMY)

SB

R442 49D9R3F1 2

R441 49D9R3F

1 2

R444 49D9R3F

1 2

CLKH_ITP

CLKH_ITP#

SB

R449

33R21 2

R132

33R21 2

R130 10R2

1 2

R131 10R21 2

R445 49D9R3F1 2

R446 49D9R3F

1 2

CLKH_CPU 4

CLKH_CPU# 4

CLKH_MCH 7

CLKH_MCH# 7

CLK48_ICH 13

CLK48_DAC 6

PM_STPCPU# 14,31

PM_STPPCI# 14

CLK14_ICH 14

CLK14_SIO 28

ICS950 813

Frequency Setting

CPU AGP PCI

FS1/0 = 00 100.00MHz 66.67MHz 33.33MHz

FS1/0 = 01 133.33MHz 66.67MHz 33.33MHz

FS1/0 = 10 200.00MHz 66.67MHz 33.33MHz

FS1/0 = 11 166.66MHz 66.67MHz 33.33MHz

FS2 = 0 unbuffer mode (disable 66MHz-IN)

FS2 = 1 buffer mode

Mult0 = 0 Rr=221,Iref=5mA

=>Vswing=1.0V@50ohm

Mult0 = 1 Rr=475,Iref=2.32mA

=>Vswing=0.7V@50ohm

Frequency Setting

CPU AGP PCI

FS1/0 = 00 66.00MHz 66.67MHz 33.33MHz

FS1/0 = 01 100.00MHz 66.67MHz 33.33MHz

FS1/0 = 10 200.00MHz 66.67MHz 33.33MHz

FS1/0 = 11 133.33MHz 66.67MHz 33.33MHz

FS2 = 0 unbuffer mode (disable 66MHz-IN)

FS2 = 1 buffer mode

Mult0 = 0 Rr=221,Iref=5mA

=>Vswing=1.0V@50ohm

Mult0 = 1 Rr=475,Iref=2.32mA

=>Vswing=0.7V@50ohm

R128 0R5

1 2

C504

SCD1U16V

C115

DUMMY-SC4D7U10V5ZY

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

Clock Generator - ICS950813YGT

YUHINA

SB

3D3V_S0

300 ohm@100MHz

600mA

PACKAGE 0 805

1 2

C523 DUMMY-C3

1 2

C524 DUMMY-C3

1 2

C525 DUMMY-C3

1 2

C526 DUMMY-C3

1 2

R450 DUMMY-10KR3

Title

Size Document Number Rev

A3

Date: Sheet of

3D3V_S0

CLKH_ITP 4,5

CLKH_ITP# 4,5

CY28346-2

3 39Thursday, June 12, 2003

3D3V_S0VCCA_CKG48

SC

U12D

H25

M21

G25

D25

D23

C26

H21

G22

B25

C24

C23

B24

D22

C21

A25

A23

B22

B21

E21

E22

F21

K23

L22

H24

G26

L21

D26

F26

E25

F24

F23

G23

E24

H22

K22

U12B

T23

D#15

J21

D#14

D#13

D#12

D#11

D#10

D#9

D#8

D#7

D#6

D#5

D#4

D#3

D#2

D#1

D#0

DBI#0

DSTBN#0

DSTBP#0

D#31

D#30

J24

D#29

D#28

D#27

D#26

D#25

D#24

D#23

D#22

D#21

D#20

D#19

D#18

D#17

D#16

DBI#1

DSTBN#1

J23

DSTBP#1

D#47

D#46

D#45

D#44

D#43

D#42

D#41

D#40

D#39

D#38

D#37

D#36

D#35

DATA GR P0

D#34

DATA GR P2DATA GR P3

D#33

D#32

DBI#2

DSTBN#2

DSTBP#2

D#63

D#62

D#61

D#60

D#59

D#58

D#57

D#56

D#55

D#54

D#53

D#52

D#51

D#50

DATA GR P1

D#49

D#48

DBI#3

DSTBN#3

DSTBP#3

T22

T25

T26

R24

R25

P24

R21

N25

N26

M26

N23

M24

P21

N22

M23

P26

R22

P23

AA24

AA22

AA25

Y21

Y24

Y23

W25

Y26

W26

V24

V22

U21

V25

U23

U24

U26

V21

W22

W23

GTL_D#47

GTL_D#46

GTL_D#45

GTL_D#44

GTL_D#43

GTL_D#42

GTL_D#41

GTL_D#40

GTL_D#39

GTL_D#38

GTL_D#37

GTL_D#36

GTL_D#35

GTL_D#34

GTL_D#33

GTL_D#32

GTL_D#63

GTL_D#62

GTL_D#61

GTL_D#60

GTL_D#59

GTL_D#58

GTL_D#57

GTL_D#56

GTL_D#55

GTL_D#54

GTL_D#53

GTL_D#52

GTL_D#51

GTL_D#50

GTL_D#49

GTL_D#48

GTL_D#[47:32] 7

GTL_DINV#2 7

GTL_DSTBN#2 7

GTL_DSTBP#2 7

GTL_D#[63:48] 7

GTL_DINV#3 7

GTL_DSTBN#3 7

GTL_DSTBP#3 7

GTL_A#[16:3]7

GTL_ADSTB#07

GTL_REQ#[4:0]7

TP44 TPAD30

TP43 TPAD30

TP41 TPAD30

GTL_A#[31:17]7

TP39 TPAD30

GTL_ADSTB#17

N5

GTL_A#16

GTL_A#15

GTL_A#14 AP#1

GTL_A#13

GTL_A#12

GTL_A#11

GTL_A#10

GTL_A#9

GTL_A#8

GTL_A#7

GTL_A#6

GTL_A#5

GTL_A#4

GTL_A#3

GTL_REQ#4

GTL_REQ#3 TESTHI8

GTL_REQ#2

GTL_REQ#1

GTL_REQ#0

GTL_A#35

GTL_A#34

GTL_A#33

GTL_A#32

GTL_A#31

GTL_A#30

GTL_A#29

GTL_A#28

GTL_A#27

GTL_A#26

GTL_A#25

GTL_A#24

GTL_A#23

GTL_A#22

GTL_A#21

GTL_A#20

GTL_A#19

GTL_A#18

GTL_A#17

N4

N2

M1

N1

M4

M3

L2

M6

L3

K1

L6

K4

K2

L5

H3

J3

J4

K5

J1

AB1

Y1

W2

V3

U4

T5

W1

R6

V2

T4

U3

P6

U1

T2

R3

P4

P3

R2

T1

R5

A#16

A#15

A#14

A#13

A#12

A#11

A#10

A#9

A#8

A#7

A#6

A#5

A#4

A#3

ADSTB#0

REQ#4

REQ#3

REQ#2

REQ#1

REQ#0

A#35

A#34

A#33

A#32

A#31

A#30

A#29

A#28

A#27

A#26

A#25

A#24

A#23

A#22

A#21

A#20

A#19

A#18

A#17

ADSTB#1

P4M-NW-U1

ADDR GROUP 0ADDR GROUP 1

CONTROL

ADS#

AP#0

AP#1

BINIT#

BNR#

BPRI#

DP#3

DP#2

DP#1

DP#0

DEFER#

DRDY#

DBSY#

TESTHI8

TESTHI9

TESTHI10

BR#0

IERR#

INIT#

LOCK#

MCERR#

RESET#

RS#2

RS#1

RS#0

RSP#

TRDY#

HIT#

HITM#

G1

AC1

V5

AA3

G2

D2

L25

K26

K25

J26

E2

H2

H5

U6

W4

Y3

H6

AC3

W5

G4

V6

AB25

F4

G5

F1

AB2

J6

F3

E3

AP#0

BINIT#

DP#3

DP#2

DP#1

DP#0

TESTHI9

TESTHI10

IERR

MCERR#

RSP#

GTL_ADS# 7

GTL_BNR# 7

GTL_BPRI# 7

GTL_DEFER# 7

GTL_DRDY# 7

GTL_DBSY# 7

R423 56R31 2

R424 56R3

1 2

R425 56R31 2

R434 56R31 2

CC_INIT# 14,24

GTL_LOCK# 7

TP37TPAD30

GTL_RS#2 7

GTL_RS#1 7

GTL_RS#0 7

TP42TPAD30

GTL_TRDY# 7

GTL_HIT# 7

GTL_HITM# 7

TP45TPAD30

TP38TPAD30

TP40TPAD30

TP4TPAD30

TP2TPAD30

TP3TPAD30

TP1TPAD30

R417

220R3F

1 2

R49

1 2

51R3F

GTL_CPURST# 5,7

VCC_CORE

VCC_CORE

GTL_BR0# 7

VCC_CORE

GTL_D#[15:0]7

GTL_DINV#07

GTL_DSTBN#07

GTL_DSTBP#07

GTL_D#[31:16]7

GTL_DINV#17

GTL_DSTBN#17

GTL_DSTBP#17

GTL_D#15

GTL_D#14

GTL_D#13

GTL_D#12

GTL_D#11

GTL_D#10

GTL_D#9

GTL_D#8

GTL_D#7

GTL_D#6

GTL_D#5

GTL_D#4

GTL_D#3

GTL_D#2

GTL_D#1

GTL_D#0

GTL_D#31

GTL_D#30

GTL_D#29

GTL_D#28

GTL_D#27

GTL_D#26

GTL_D#25

GTL_D#24

GTL_D#23

GTL_D#22

GTL_D#21

GTL_D#20

GTL_D#19

GTL_D#18

GTL_D#17

GTL_D#16

THERMDP16

THERMDN16

CC_THRMTRIP_S#14

P4:R433->DUMMY

Prescott:R433->0ohm

C448

SC1000P50V

VCC_CORE

PWRGD_VID31,33

H_VID531

Note:Host Clock

terminations are at the

source(CK408)

CLKH_CPU3

CLKH_CPU#3

CLKH_ITP3,5

CLKH_ITP#3,5

CC_A20M#14

CC_FERR#14

CC_IGNNE#14

CC_INTR14

CC_NMI14

CC_SMI#14

CC_STPCLK#14

R52 56R31 2

R50 56R3

1 2

R359 56R31 2

R358 56R3

1 2

R426 56R31 2

R51 56R3

1 2

1 2

1D2V_VID

R433 DUMMY-R3

PWRGD_VID_CPU

R399

R396

C456

DUMMY-SCD1U16V

CC_PROCHOT_S#

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

1 2

1 2

DUMMY-R3

DUMMY-R3

AF22

AF23

AC26

AD26

AC23

AC24

AC20

AC21

AA2

AD24

AD2

AD3

AE21

AF3

AF24

AF25

A22

C6

B6

B2

D1

E5

B5

Y4

B3

C4

A2

C3

A7

U12C

BCLK0

BCLK1

ITP_CLK0

ITP_CLK1

A20M#

FERR#

IGNNE#

/INTR

LINT0

/NMI

LINT1

SMI#

STPCLK#

THERMDA

THERMDC

THERMTRIP#

PROCHOT#

TESTHI5

TESTHI4

TESTHI3

TESTHI2

TESTHI1

TESTHI0

NC

NC

NC

NC

NC

NC

NC

NC

P4M-NW-U1

HOST CLKLEGACY CPUTHERM

BSEL0

FSBSE1

GHI#

DPSLP#

SLP#

COMP0

COMP1

GTLREF3

GTLREF2

GTLREF1

GTLREF0

BPM#5

BPM#4

BPM#3

BPM#2

BPM#1

BPM#0

ITPCLKOUT0

ITPCLKOUT1

DBR#

TCK

TDI

TDO

TAP/ITP REF&COMP

TMS

TRST#

SKTOCC#

VCC_CORE

12

R91

300R3

SB

AD6

AD5

BSEL1

A6

AD25

AB26

Trace 25 mi ls Mini.

L24

COMP0

P1

COMP1

GTLREF_3

GTLREF_1

GTLREF_0

ITPCLK0

ITPCLK1

SKTOCC#

1 2

12

AA21

AA6

F20

F6

AB4

AA5

Y6

AC4

AB5

AC6

AA20

AB22

AE25

D4

C1

D5

F7

E6

AF26

TP87TPAD30

CC_DPSLP# 6,14

CC_CPUSLP# 14

R354 61D9R3F1 2

R422 61D9R3F

1 2

R377

0R2-0

TP26TPAD30

TP36TPAD30

Near

processor

C380

SC220P50V2JN

H_BPM5_PREQ# 5

H_BPM4_PRDY# 5

H_BPM3_ITP# 5

H_BPM2_ITP# 5

H_BPM1_ITP# 5

H_BPM0_ITP# 5

R355 56R3

1 2

R357 56R31 2

H_TCK 5

H_TDI 5

H_TDO 5

H_TMS 5

12

TP5TPAD30

GTLREF_2

R412

680R3

BSEL0 3,6

PM_CPUPERF# 14

12

C442

SC220P50V2JN

VCC_CORE

H_TRST# 5

Trace length:Less

than 1.5 inch

Near

resistor

C420

SC1U10V3ZY

3D3V_S5

12

VCC_CORE

12

R379

51D1R3F

12

R380

86D6R3

R360

150R3

DBRESET#_ITP 5,14

P4M-NW-U1

VCC_CORE

12

H_BPM5_PREQ#

H_BPM4_PRDY#

H_BPM3_ITP#

H_BPM2_ITP#

H_BPM1_ITP#

H_BPM0_ITP#

H_TDI

CC_PROCHOT_S#

12

12

12

12

R427

R428

R429

51R3F

51R3F

Title

Size Document Number Rev

Date: Sheet of

R430

51R3F

51R3F

A3

12

R431

R432

51R3F

51R3F

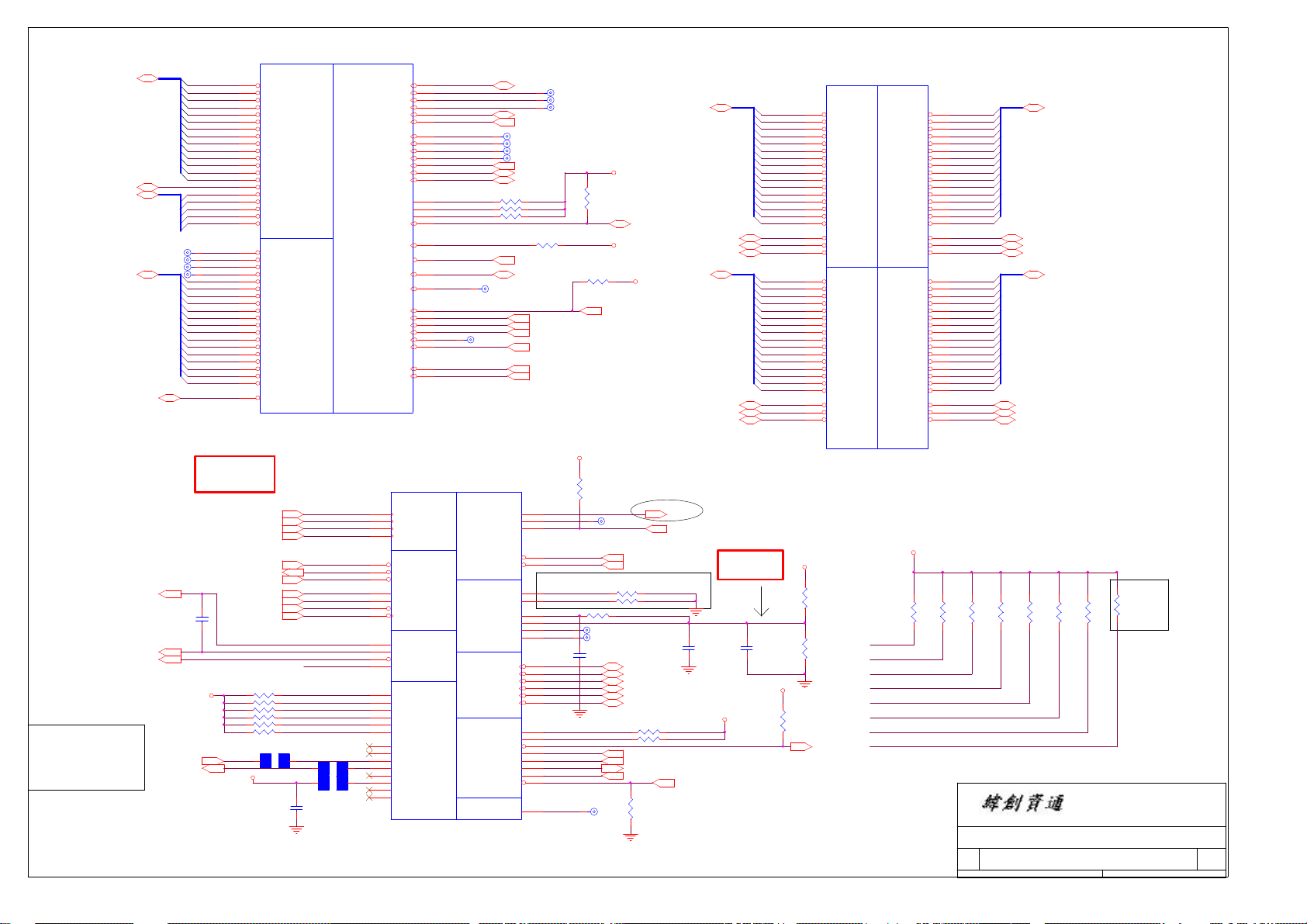

P4-M Northwood-MT 1/2

YUHINA

12

12

R410

150R3

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

R405

100KR2

4 39Thursday, June 12, 2003

SC

VCC_CORE

A10

A12

VCC

VSS

A11

A13

VCC_CORE

12

TC1 ST33U10VBM

1 2

C379 SC1U10V3ZY

H_VCCA

AE3

AE4

AE5

AD20

A5

VID3

VID2

VID1

VID0

VCCA

VSSC2VSS

VSS

VSSC5VSSC7VSSC9VSS

C22

C25

D10

D12

12

H_VCCIOPLL

AE23

VCCSENSE

VSS

D14

Layout Note:

C3D7 should be placed within 600 mils of the

VCCA and VSSA pins

VCCA should be routed in parallel and next to

VSSA

R398 0R3-U

1 2

A14

A16

A18

A20

AA10

AA12

AA14

AA16

AA18

AA8

AB11

AB13

AB15

AB17

AB19

AB7

AB9

AC10

AC12

AC14

AC16

AC18

AC8

AD11

AD13

AD15

AD17

AD19

AD7

AD9

AE10

AE12

AE14

VCC

VCC

VCC

VCC

VCC

VCCA8VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSSA3VSSA9VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

A15

A17

A19

A21

A24

A26

AA1

AA11

AA13

AA15

AA17

AA19

AA23

AA26

AA4

AA7

AA9

AB10

AB12

AB14

AB16

AB18

AB20

AB21

AB24

AB3

AB6

AB8

AC11

AC13

AC15

AC17

VCC_CORE_L

AE16

AE18

AE20

AE6

AE8

AF11

AF13

E14

E16

E18

E20

F11

F13

F15

F17

F19

AF15

AF17

AF19

AF2

AF21

AF5

AF7

AF9

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCE8VCC

VCC

VCC

VCC

VCC

VCCF9VCC

VCC

VCC

VCC

VCC

VCC

VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AC19

AC2

AC5

AC7

AC9

AC22

AC25

AD1

BOOTSELECT

AD10

AD12

AD14

AD16

AD18

AD21

AD23

AD4

AD8

AE11

AE13

AE15

AE17

AE19

AE22

AE24

AE26

AE7

H_VID[4:0]31

B11

B13

B15

B17

B19

C10

C12

C14

C16

C18

C20

D11

VCC

VCC

VCC

VCC

VCC

VCC

VCCB7VCCB9VCC

VCC

VCC

VCC

VCC

VCC

VCCC8VCC

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

AF1

AF6

AF8

B10

B12

B14

B16

AE9

AF10

AF12

AF14

AF16

AF18

B18

AF20

L4

IND-10UH-3

H_VID0

H_VID1

H_VID2

H_VID3

H_VID4

D13

D15

D17

D19

E10

E12

AE1

AE2

VCC

VCC

VCC

VCC

VCCD7VCCD9VCC

VCC

VID4

VSS

VSS

VSS

VSS

VSSB4VSSB8VSS

VSS

VSS

VSS

VSS

B20

B23

B26

C11

C13

C15

C17

C19

L5

IND-10UH-3

H_VSSA

AD22

A4

AF4

VSSA

VCCIOPLL

VSSSENSE

VSS

VSS

VSS

D16

D18

D20

VCCVID

VSS

VSS

D21

AB23

PWRGOOD

VSS

VSSD3VSSD6VSSD8VSSE1VSS

D24

SC

C368

SC1U10V3ZY

VCCSENSE 31

VSSSENSE 31

VSS

E11

E13

CC_CPUPWRGD 14

VCC_CORE

SB

1D2V_VID

VSS

VSS

VSS

VSS

VSS

E15

E17

E19

E23

E26

VSSE4VSSE7VSSE9VSS

F10

12

R356

300R3

U12A

P4M-NW-U1

T6

VSS

K3

VSS

Y5

VSS

Y25

VSS

Y22

VSS

Y2

VSS

W6

VSS

W3

VSS

W24

VSS

W21

VSS

V4

VSS

V26

VSS

V23

VSS

V1

VSS

U5

VSS

U25

VSS

U22

VSS

U2

P25

VSS

VSSP5VSSR1VSS

R23

VSS

VSS

VSS

R4

R26

VSS

VSS

VSS

VSS

VSSF2VSS

VSS

VSSF5VSSF8VSS

VSS

VSSG3VSSG6VSSH1VSS

VSS

VSSH4VSSJ2VSS

VSS

VSSJ5VSS

VSS

VSS

VSS

VSS

VSSK6VSSL1VSS

VSS

VSSL4VSSM2VSS

VSS

VSSM5VSS

VSS

T3

J22

F12

F14

F16

F18

F22

F25

G21

G24

J25

T21

T24

L23

K21

H23

H26

L26

K24

VSSN3VSSN6VSSP2VSS

P22

N21

N24

M22

M25

10U/X5R 1206 DECOUPLING CAPS

8X IN SOCKET CAVITY

10X IN CRB

0.1U/X5R 0603 DECOUPLING CAPS

20X AROUND SOCKET

VCC_CORE

12

VCC_CORE

12

VCC_CORE

12

C391

C389

SC10U6D3V5MX

C433

SC10U6D3V5MX

12

C392

SCD1U10V2MX-1

SCD1U10V2MX-1

12

C402

SC10U6D3V5MX

12

C426

SC10U6D3V5MX

12

C393

12

12

C394

SCD1U10V2MX-1

12

C403

SC10U6D3V5MX

C483

SC10U6D3V5MX

12

C390

SCD1U10V2MX-1

12

C416

SC10U6D3V5MX

12

C441

SCD1U10V2MX-1

12

12

C395

SC10U6D3V5MX

12

C440

SCD1U10V2MX-1

R421

0R2-0

12

C423

SC10U6D3V5MX

12

C439

SCD1U10V2MX-1

12

C430

SC10U6D3V5MX

12

C438

SCD1U10V2MX-1

GDN: 50 ohm platform

NC: 60 ohm platform

TP_PSC_50_60_BUFFER

R53

1 2

0R2-0

12

C436

SC10U6D3V5MX

12

C383

SC10U6D3V5MX

12

C437

SCD1U10V2MX-1

SCD1U10V2MX-1

12

C401

SC10U6D3V5MX

VCC_CORE

12

C409

12

12

C415

SCD1U10V2MX-1

C376

SC10U6D3V5MX

12

C408

SC10U6D3V5MX

12

C417

SCD1U10V2MX-1

SCD1U10V2MX-1

12

C372

SC10U6D3V5MX

12

12

C419

SCD1U10V2MX-1

C425

SC10U6D3V5MX

12

C399

SCD1U10V2MX-1

12

C421

ITP Debug Pad

12

C382

SC10U6D3V5MX

12

C443

SCD1U10V2MX-1

SCD1U10V2MX-1

12

C384

12

C418

SCD1U10V2MX-1

Should place near conn.

SCD1U10V2MX-1

12

C432

H_TRST#4

CLKH_ITP#3,4

CLKH_ITP3,4

GTL_CPURST#4,7

SCD1U10V2MX-1

VCC_CORE

VCC_CORE

12

12

R419

R411

75R3F

39D2R3F

R406 0R2-0

H_TDI4

H_TMS4

H_TCK4

H_TDO4

12

R418

27D4R3F

1 2

R407 0R2-01 2

R413 0R2-01 2

R414 0R2-0

1 2

GTL_CPURST#

H_BPM5_PREQ#4

H_BPM4_PRDY#4

H_BPM3_ITP#4

H_BPM2_ITP#4

H_BPM1_ITP#4

H_BPM0_ITP#4

DBRESET#_ITP4,14

Title

Size Document Number Rev

Custom

Date: Sheet of

TDI_FLEX

TMS_FLEX

TRST_FLEX

TCK_FLEX

H_TDO

CLKH_ITP#

CLKH_ITP

H_TCK

VCC_CORE

12

C352

SCD1U10V2MX-1

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

P4-M Northwood-MT 2/2

YUHINA

TP46TPAD30

TP47TPAD30

TP48TPAD30

TP49TPAD30

TP50TPAD30

TP51TPAD30

TP53TPAD30

TP52TPAD30

TP54TPAD30

TP55TPAD30

TP56TPAD30

TP57TPAD30

TP58TPAD30

TP59TPAD30

TP60TPAD30

TP61TPAD30

TP62TPAD30

TP63TPAD30

TP64TPAD30

TP65TPAD30

5 39Thursday, June 12, 2003

SC

A

4 4

M_DATA[0..63]10 M_DQS[7..0] 10

3 3

2 2

1 1

M_DATA0

M_DATA1

M_DATA2

M_DATA3

M_DATA4

M_DATA5

M_DATA6

M_DATA7

M_DATA8

M_DATA9

M_DATA10

M_DATA11

M_DATA12

M_DATA13

M_DATA14

M_DATA15

M_DATA16

M_DATA17

M_DATA18

M_DATA19

M_DATA20

M_DATA21

M_DATA22

M_DATA23

M_DATA24

M_DATA25

M_DATA26

M_DATA27

M_DATA28

M_DATA29

M_DATA30

M_DATA31

M_DATA32

M_DATA33

M_DATA34

M_DATA35

M_DATA36

M_DATA37

M_DATA38

M_DATA39

M_DATA40

M_DATA41

M_DATA42

M_DATA43

M_DATA44

M_DATA45

M_DATA46

M_DATA47

M_DATA48

M_DATA49

M_DATA50

M_DATA51

M_DATA52

M_DATA53

M_DATA54

M_DATA55

M_DATA56

M_DATA57

M_DATA58

M_DATA59

M_DATA60

M_DATA61

M_DATA62

M_DATA63

DDR_VREF_S3

12

C500

SCD1U10V2MX-1

A

AG10

AF10

AE11

AH10

AH11

AG13

AF14

AG11

AD12

AF13

AH13

AH16

AG17

AF19

AE20

AD18

AE18

AH18

AG19

AH20

AG20

AF22

AH22

AF20

AH19

AH21

AG22

AE23

AH23

AE24

AH25

AG23

AF23

AF25

AG25

AH26

AE26

AG28

AF28

AG26

AF26

AE27

AD27

AG14

AE14

AE17

AG16

AH14

AE15

AF16

AF17

AJ24

AF2

AE3

AF4

AH2

AD3

AE2

AG4

AH3

AD6

AG5

AG7

AE8

AF5

AH4

AF7

AH6

AF8

AG8

AH9

AH7

AD9

U15A

SDQ[0]

SDQ[1]

SDQ[2]

SDQ[3]

SDQ[4]

SDQ[5]

SDQ[6]

SDQ[7]

SDQ[8]

SDQ[9]

SDQ[10]

SDQ[11]

SDQ[12]

SDQ[13]

SDQ[14]

SDQ[15]

SDQ[16]

SDQ[17]

SDQ[18]

SDQ[19]

SDQ[20]

SDQ[21]

SDQ[22]

SDQ[23]

SDQ[24]

SDQ[25]

SDQ[26]

SDQ[27]

SDQ[28]

SDQ[29]

SDQ[30]

SDQ[31]

SDQ[32]

SDQ[33]

SDQ[34]

SDQ[35]

SDQ[36]

SDQ[37]

SDQ[38]

SDQ[39]

SDQ[40]

SDQ[41]

SDQ[42]

SDQ[43]

SDQ[44]

SDQ[45]

SDQ[46]

SDQ[47]

SDQ[48]

SDQ[49]

SDQ[50]

SDQ[51]

SDQ[52]

SDQ[53]

SDQ[54]

SDQ[55]

SDQ[56]

SDQ[57]

SDQ[58]

SDQ[59]

SDQ[60]

SDQ[61]

SDQ[62]

SDQ[63]

SDQ[64]

SDQ[65]

SDQ[66]

SDQ[67]

SDQ[68]

SDQ[69]

SDQ[70]

SDQ[71]

SMVREF

MONTARA-GT-U1

DDR SYSTEM M EMORY

12

C98

SCD1U10V2MX-1

SDQS[0]

SDQS[1]

SDQS[2]

SDQS[3]

SDQS[4]

SDQS[5]

SDQS[6]

SDQS[7]

SDQS[8]

SMA[0]

SMA[1]

SMA[2]

SMA[3]

SMA[4]

SMA[5]

SMA[6]

SMA[7]

SMA[8]

SMA[9]

SMA[10]

SMA[11]

SMA[12]

SMAB[1]

SMAB[2]

SMAB[4]

SMAB[5]

SCKE[0]

SCKE[1]

SCKE[2]

SCKE[3]

SCS[0]#

SCS[1]#

SCS[2]#

SCS[3]#

SBA[0]

SBA[1]

SRAS#

SCAS#

SWE#

SCK[0]

SCK[0]#

SCK[1]

SCK[1]#

SCK[2]

SCK[2]#

SCK[3]

SCK[3]#

SCK[4]

SCK[4]#

SCK[5]

SCK[5]#

SDM[0]

SDM[1]

SDM[2]

SDM[3]

SDM[4]

SDM[5]

SDM[6]

SDM[7]

SDM[8]

RCVENOUT#

RCVENIN#

SMRCOMP

SMVSWINGL

SMVSWINGH

2D5V_S3

12

MX_RCOMP

12

R123

68D1R3F

R122

60D4R3F

B

RP9

1

2

3

4

5 6

SRP2K2

66.22236.100

PM_SUSCLK14,15

M_A[12..0] 9,10

M_SDM_[7..0] 10

2D5V_S3

TP66TPAD30

12

TP67TPAD30

R141

604R3F

12

R142

150R3F

12

12

R140

150R3F

R139

604R3F

R386

1KR3

AG2

AH5

AH8

AE12

AH17

AE21

AH24

AH27

AD15

AC18

AD14

AD13

AD17

AD11

AC13

AD8

AD7

AC6

AC5

AC19

AD5

AB5

AD16

AC12

AF11

AD10

AC7

AB7

AC9

AC10

AD23

AD26

AC22

AC25

AD22

AD20

AC21

AC24

AD25

AB2

AA2

AC26

AB25

AC3

AD4

AC2

AD2

AB23

AB24

AA3

AB4

AE5

AE6

AE9

AH12

AD19

AD21

AD24

AH28

AH15

AC15

AC16

AB1

AJ22

AJ19

MI2CCLK

MI2CDATA DVICLK

GADSTB0

GADSTB1

M_DQS0

M_DQS1

M_DQS2

M_DQS3

M_DQS4

M_DQS5

M_DQS6

M_DQS7

M_A0

M_A1

M_A2

M_A3

M_A4

M_A5

M_A6

M_A7

M_A8

M_A9

M_A10

M_A11

M_A12

M_B1 9,10

M_B2 9,10

M_B4 9,10

M_B5 9,10

M_CKE0_R# 9,10

M_CKE1_R# 9,10

M_CKE2_R# 9,10

M_CKE3_R# 9,10

M_CS0_R# 9,10

M_CS1_R# 9,10

M_CS2_R# 9,10

M_CS3_R# 9,10

M_BS0_FR# 9

M_BS1_FR# 9

M_RAS# 9

M_CAS# 9

M_WE# 9

CLK_DDR0 9

CLK_DDR0# 9

CLK_DDR1 9

CLK_DDR1# 9

CLK_DDR2 9

CLK_DDR2# 9

CLK_DDR3 9

CLK_DDR3# 9

CLK_DDR4 9

CLK_DDR4# 9

CLK_DDR5 9

CLK_DDR5# 9

M_SDM_0

M_SDM_1

M_SDM_2

M_SDM_3

M_SDM_4

M_SDM_5

M_SDM_6

M_SDM_7

RCVENOUT#

RCVENIN#

MX_RCOMP

SMVSWING_L

SMVSWING_H

12

12

C495

C494

SCD1U10V2M X-1

SCD1U10V2M X-1

SB

2KR2F

B

R397

10

9

8

7

1

G

DVIDATA

MDDCCLK

MDDCDATA

1D5V_S0

12

12

1D5V_S0

12

DPMS

D

S

2 3

1D5V_S0

12

1KR3

C

R390

1KR3

63.10234.151

Q41

2N7002

100KR3

1D5V_S0

R92

1KR3F

R94

1KR3F

SC

12

R387

1KR3

12

R102

2KR2F

C

1D5V_S0

R401

12

12

R389

AGP_ST2

AGP_ST1

AGP_ST0

GADSTB#0

GADSTB#1

GSBSTB#

12

R383

2KR2F

1 2

C428

1D5V_S0

12

1D5V_S0

1 2

12

R97

2KR2F

64.20015.6D1

GSBSTB

RN62

1

2

3

4 5

SRN2K2

66.22236.080

R100100KR3

R104

100KR3

12

SCD1U10V2M X-1

SC

1 2

D

S

2 3

AGP_BUSY#14

CLK66_MCH3

R76

40D2R3F

D48

BAT54

Q57

2N7002

D

DDCP_DATA

U15B

R3

12

12

R5

R6

R4

P6

P5

N5

P2

N2

N3

M1

M5

P3

P4

T6

T5

L2

M2

G2

M3

K5

K1

K3

K2

J6

J5

H2

H1

H3

H4

H6

G3

J3

J2

K6

L5

L3

H5

K7

N6

N7

M6

P7

T7

E5

F5

E3

E2

G5

F4

G6

F6

L7

D5

F1

F7

D1

Y3

AA5

F2

F3

B2

B3

C2

C3

C4

D2

D3

D7

L4

R121

DUMMY-R2

C97

DUMMY-C2

GAD3/DVOBD0

GAD2/DVOBD1

GAD5/DVOBD2

GAD4/DVOBD3

GAD7/DVOBD4

GAD6/DVOBD5

GAD8/DVOBD6

GCBE#0/DVOBD7

GAD10/DVOBD8

GAD9/DVOBD9

GAD12/DVOBD10

GAD11/DVOBD11

GADSTB0/DVOBCLK

GADSTB#0/DVOBCLK#

GAD0/DVOBHSYNC

GAD1/DVOBVSYNC

GCBE#1/DVOBBLANK#

GAD14/DVOBFLDSTL

GAD30/DVOBCINTR#

GAD13/DVOBCCLKINT

GAD19/DVOCD0

GAD20/DVOCD1

GAD21/DVOCD2

GAD22/DVOCD3

GAD23/DVOCD4

GCBE#3/DVOCD5

GAD25/DVOCD6

GAD24/DVOCD7

GAD27/DVOCD8

GAD26DVOCD9

GAD29/DVOCD10

GAD28/DVOCD11

GADSTB1/DVOCCLK

GADSTB#1/DVOCCLK#

GAD17/DVOCHSYNC

GAD16/DVOCVSYNC

GAD18/DVOCBLANK#

GAD31/DVOCFLDSTL

GIRDY#/MI2CCLK

GDEVSEL#/MI2CDATA

GTRDY#/MDVICLK

GFRAME#/MDVIDATA

GSTOP#/MDDCCLK

GAD15/MDDCDATA

GSBA0/ADDID0

GSBA1/ADDID1

GSBA2/ADDID2

GSBA3/ADDID3

GSBA4/ADDID4

GSBA5/ADDID5

GSBA6/ADDID6

GSBA7/ADDID7

GPAR/DVODETECT

GPIPE#/DPMS

GVREF

AGPBUSY#

DVO_GRCOMP

GCLKIN

RSVD0

GSBSTB

GSBSTB#

GGNT#

GREQ#

GST[2]

GST[1]

GST[0]

GWBF#

GRBF#

RSVD4

GCBE#[2]

MONTARA-GT-U1

D

AGP_REQ#

8

AGP_GNT#

7

AGP_WBF#

6

AGP_RBF#

GADSTB0

GADSTB#0

R108

1D5V_S0

12

1 2

GADSTB1

GADSTB#1

MI2CCLK

MI2CDATA

DVICLK

DVIDATA

MDDCCLK

MDDCDATA

R402

1KR3

DVODETECT

DVO_GCOMP

GSBSTB

GSBSTB#

AGP_GNT#

AGP_REQ#

AGP_ST2

AGP_ST1

AGP_ST0

AGP_WBF#

AGP_RBF#

BSEL0 3,4

AGP_AD30

AGP_AD13

DPMS

GVREF

12

100KR3

1

G

DDCP_CLK

3D3V_S0

12

12

R375

2K2R3

DVO

R77

2K2R3

BLUE

BLUE#

GREEN

GREEN#

RED

RED#

HSYNC

VSYNC

REFSET

DDCA_CLK

DDCA_DATA

IYAM0

IYAM1

IYAM2

IYAM3

IYAP0

IYAP1

IYAP2

IYAP3

IYBM0

IYBM1

IYBM2

IYBM[3

IYBP0

IYBP1

IYBP2

IYBP3

LVDS DACMISCNC CLKS

ICLKAM

ICLKAP

ICLKBM

ICLKBP

DDCPCLK

DDCPDATA

PANELBKLTCTL

PANELBKLTEN

PANELVDDEN

RSVD1

RSVD2

RSVD3

LIBG

DREFCLK

DREFSSCLK

LCLKCTLA

LCLKCTLB

DPWR#

DPSLP#

RSTIN#

PWROK

EXTTS0

VSS182

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

Title

MONTARA GT (1/3)

Size Document Number Rev

Custom

Date: Sheet of

YUHINA

E

C9

D9

C8

D8

A7

A8

H10

J9

REFSET_MCH

E8

B6

G9

G14

E15

C15

C13

F14

E14

C14

B13

H12

E12

C12

G11

G12

E11

C11

G10

D14

E13

E10

F10

DDCP_CLK

B4

DDCP_DATA

C5

R400DUMMY-R2

G8

1 2

F8

A5

RSVD1

D12

RSVD2

F12

RSVD3

B12

LIBG

A10

B7

B17

LCLKCTLA

H9

LCLKCTLB

C6

AA22

Y23

AD28

J11

EX_THRM

D6

AJ1

B1

AH1

A2

AJ2

A28

AJ28

A29

B29

AH29

AJ29

AA9

AJ4

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

1 2

R79 1K5R3F

12

R391

DUMMY-R2

10KR3F

1 2

R395

R378

1 2

DUMMY-R2

R376

1 2

DUMMY-R2

6 39Thursday, June 12, 2003

E

DAC_BLUE 12

DAC_GREEN 12

DAC_RED 12

DAC_HSYNC 12

DAC_VSYNC 12

1 2

R371 127R3F

CLKDDC3_3 12

DATDDC3_3 12

TXAOUT0- 11

TXAOUT1- 11

TXAOUT2- 11

TXAOUT0+ 11

TXAOUT1+ 11

TXAOUT2+ 11

TXBOUT0- 11

TXBOUT1- 11

TXBOUT2- 11

TXBOUT0+ 11

TXBOUT1+ 11

TXBOUT2+ 11

TXACLK- 11

TXACLK+ 11

TXBCLK- 11

TXBCLK+ 11

BRIGHTNESS 11,25

BL_ON 11

LCDVDD_ON 11

CLK48_DAC 3

CLK66_LVDS 3

TP35

TPAD30

R385

1 2

10KR3

CC_DPSLP# 4,14

PCIRST1# 11,15,19,26,27

VGATE_PWRGD 14

2D5V_S3

3D3V_S0

1 2

DUMMY-C2

1 2

DUMMY-C2

TP8 TPAD30

TP25 TPAD30

TP28TPAD30

TP29TPAD30

TP27TPAD30

3D3V_S0

C410

C404

SC

A

B

C

D

E

GTL_D#[63:0]4GTL_A#[31:3]4

U15C

GTL_A#3

P23

W25

AA27

W24

W23

W27

AA28

W28

AB27

AB28

AA26

AD29

AE29

T25

T28

R27

U23

U24

R24

U28

V28

U27

T27

V27

U25

V26

Y24

V25

V23

Y25

Y27

Y26

R28

P25

R23

R25

T23

T26

H28

K28

B20

B18

J28

C27

E22

D18

K27

D26

E21

E18

J25

E25

B25

G19

F15

K21

J21

J17

Y28

Y22

U7

U4

U3

V3

W2

W6

V6

W7

T3

V5

V4

W3

V2

T2

U2

W1

HA[3]#

HA[4]#

HA[5]#

HA[6]#

HA[7]#

HA[8]#

HA[9]#

HA[10]#

HA[11]#

HA[12]#

HA[13]#

HA[14]#

HA[15]#

HA[16]#

HA[17]#

HA[18]#

HA[19]#

HA[20]#

HA[21]#

HA[22]#

HA[23]#

HA[24]#

HA[25]#

HA[26]#

HA[27]#

HA[28]#

HA[29]#

HA[30]#

HA[31]#

HREQ[0]#

HREQ[1]#

HREQ[2]#

HREQ[3]#

HREQ[4]#

HADSTB[0]#

HADSTB[1]#

BCLK#

BCLK

HYRCOMP

HYSWING

HXRCOMP

HXSWING

HDSTBN[0]#

HDSTBN[1]#

HDSTBN[2]#

HDSTBN[3]#

HDSTBP[0]#

HDSTBP[1]#

HDSTBP[2]#

HDSTBP[3]#

DINV[0]#

DINV[1]#

DINV[2]#

DINV[3]#

CPURST#

HDVREF[0]

HDVREF[1]

HDVREF[2]

HCCVREF

HAVREF

HL[0]

HL[1]

HL[2]

HL[3]

HL[4]

HL[5]

HL[6]

HL[7]

HL[8]

HL[9]

HL[10]

HLSTB

HLSTB#

HLRCOMP

PSWING

HLVREF

MONTARA-GT-U1

HOST

GTL_A#4

GTL_A#5

12

R111

48D7R3F

C471

GTL_A#6

GTL_A#7

GTL_A#8

GTL_A#9

GTL_A#10

GTL_A#11

GTL_A#12

GTL_A#13

GTL_A#14

GTL_A#15

GTL_A#16

GTL_A#17

GTL_A#18

GTL_A#19

GTL_A#20

GTL_A#21

GTL_A#22

GTL_A#23

GTL_A#24

GTL_A#25

GTL_A#26

GTL_A#27

GTL_A#28

GTL_A#29

GTL_A#30

GTL_A#31

GTL_REQ#0

GTL_REQ#1

GTL_REQ#2

GTL_REQ#3

GTL_REQ#4

HY_COMP

HY_SWING

HX_COMP

HX_SWING

HDVREF

HCCVREF

HAVREF

HL_0

HL_1

HL_2

HL_3

HL_4

HL_5

HL_6

HL_7

HL_8

HL_9

HL_10

HL_STB13

HL_STB#13

HLZCOMP

PSWING

HLVREF

12

12

C466

SCD1U10V2M X-1

SCD1U10V2MX-1

4 4

HY_COMP

HX_COMP

12

12

R93

3 3

27D4R3F

2 2

1 1

R84

27D4R3F

VCC_CORE

12

R392

49D9R3F

12

R393

100R3F

A

C449

12

C476

VCC_CORE VCC_CORE

12

R96

301R3F

12

R98

150R3F

12

12

C450

SC1U16V 3KX

12

C474

SC1U16V3KX

SCD1U10V2M X-1

12

R83

301R3F

12

R82

150R3F

12

R415

SCD1U10V2M X-1

49D9R3F

12

R416

100R3F

12

R114

86D6R3

PSWING HLVREF

12

R112

100R3F

12

C451

VCC_CORE

R404

1D5V_S01D5V_S0

12

12

100R3F

12

12

R119

GTL_REQ#[4:0]4

C412

SCD1U10V2M X-1

R409

49D9R3F

C475

100R3F

R118

324R3F

GTL_ADSTB#04

GTL_ADSTB#14

CLKH_MCH#3

CLKH_MCH3

12

GTL_DSTBN#04

GTL_DSTBN#14

GTL_DSTBN#24

GTL_DSTBN#34

GTL_DSTBP#04

SCD1U10V2M X-1

GTL_DSTBP#14

GTL_DSTBP#24

GTL_DSTBP#34

GTL_DINV#04

GTL_DINV#14

GTL_DINV#24

GTL_DINV#34

GTL_CPURST#4,5

HL_[10:0]13

1D5V_S0

12

12

C467

SC1U16V3KX

SCD1U10V2M X-1

B

HUB LI NK

HD[0]#

HD[1]#

HD[2]#

HD[3]#

HD[4]#

HD[5]#

HD[6]#

HD[7]#

HD[8]#

HD[9]#

HD[10]#

HD[11]#

HD[12]#

HD[13]#

HD[14]#

HD[15]#

HD[16]#

HD[17]#

HD[18]#

HD[19]#

HD[20]#

HD[21]#

HD[22]#

HD[23]#

HD[24]#

HD[25]#

HD[26]#

HD[27]#

HD[28]#

HD[29]#

HD[30]#

HD[31]#

HD[32]#

HD[33]#

HD[34]#

HD[35]#

HD[36]#

HD[37]#

HD[38]#

HD[39]#

HD[40]#

HD[41]#

HD[42]#

HD[43]#

HD[44]#

HD[45]#

HD[46]#

HD[47]#

HD[48]#

HD[49]#

HD[50]#

HD[51]#

HD[52]#

HD[53]#

HD[54]#

HD[55]#

HD[56]#

HD[57]#

HD[58]#

HD[59]#

HD[60]#

HD[61]#

HD[62]#

HD[63]#

ADS#

HTRDY#

DRDY#

DEFER#

HITM#

HLOCK#

BREQ0#

BNR#

BPRI#

DBSY#

RS[0]#

RS[1]#

RS[2]#

C

GTL_D#0

K22

GTL_D#1

H27

GTL_D#2

K25

GTL_D#3

L24

GTL_D#4

J27

GTL_D#5

G28

GTL_D#6

L27

GTL_D#7

L23

GTL_D#8

L25

GTL_D#9

J24

GTL_D#10

H25

GTL_D#11

K23

GTL_D#12

G27

GTL_D#13

K26

GTL_D#14

J23

GTL_D#15

H26

GTL_D#16

F25

GTL_D#17

F26

GTL_D#18

B27

GTL_D#19

H23

GTL_D#20

E27

GTL_D#21

G25

GTL_D#22

F28

GTL_D#23

D27

GTL_D#24

G24

GTL_D#25

C28

GTL_D#26

B26

GTL_D#27

G22

GTL_D#28

C26

GTL_D#29

E26

GTL_D#30

G23

GTL_D#31

B28

GTL_D#32

B21

GTL_D#33

G21

GTL_D#34

C24

GTL_D#35

C23

GTL_D#36

D22

GTL_D#37

C25

GTL_D#38

E24

GTL_D#39

D24

GTL_D#40

G20

GTL_D#41

E23

GTL_D#42

B22

GTL_D#43

B23

GTL_D#44

F23

GTL_D#45

F21

GTL_D#46

C20

GTL_D#47

C21

GTL_D#48

G18

GTL_D#49

E19

GTL_D#50

E20

GTL_D#51

G17

GTL_D#52

D20

GTL_D#53

F19

GTL_D#54

C19

GTL_D#55

C17

GTL_D#56

F17

GTL_D#57

B19

GTL_D#58

G16

GTL_D#59

E16

GTL_D#60

C16

GTL_D#61

E17

GTL_D#62

D16

GTL_D#63

C18

L28

M25

N24

M28

N28

N27

HIT#

P27

M23

N25

P28

M26

N23

P26

M27

AGPDETCT

GTL_ADS# 4

GTL_TRDY# 4

GTL_DRDY# 4

GTL_DEFER# 4

GTL_HITM# 4

GTL_HIT# 4

GTL_LOCK# 4

GTL_BR0# 4

GTL_BNR# 4

GTL_BPRI# 4

GTL_DBSY# 4

GTL_RS#0 4

GTL_RS#1 4

GTL_RS#2 4

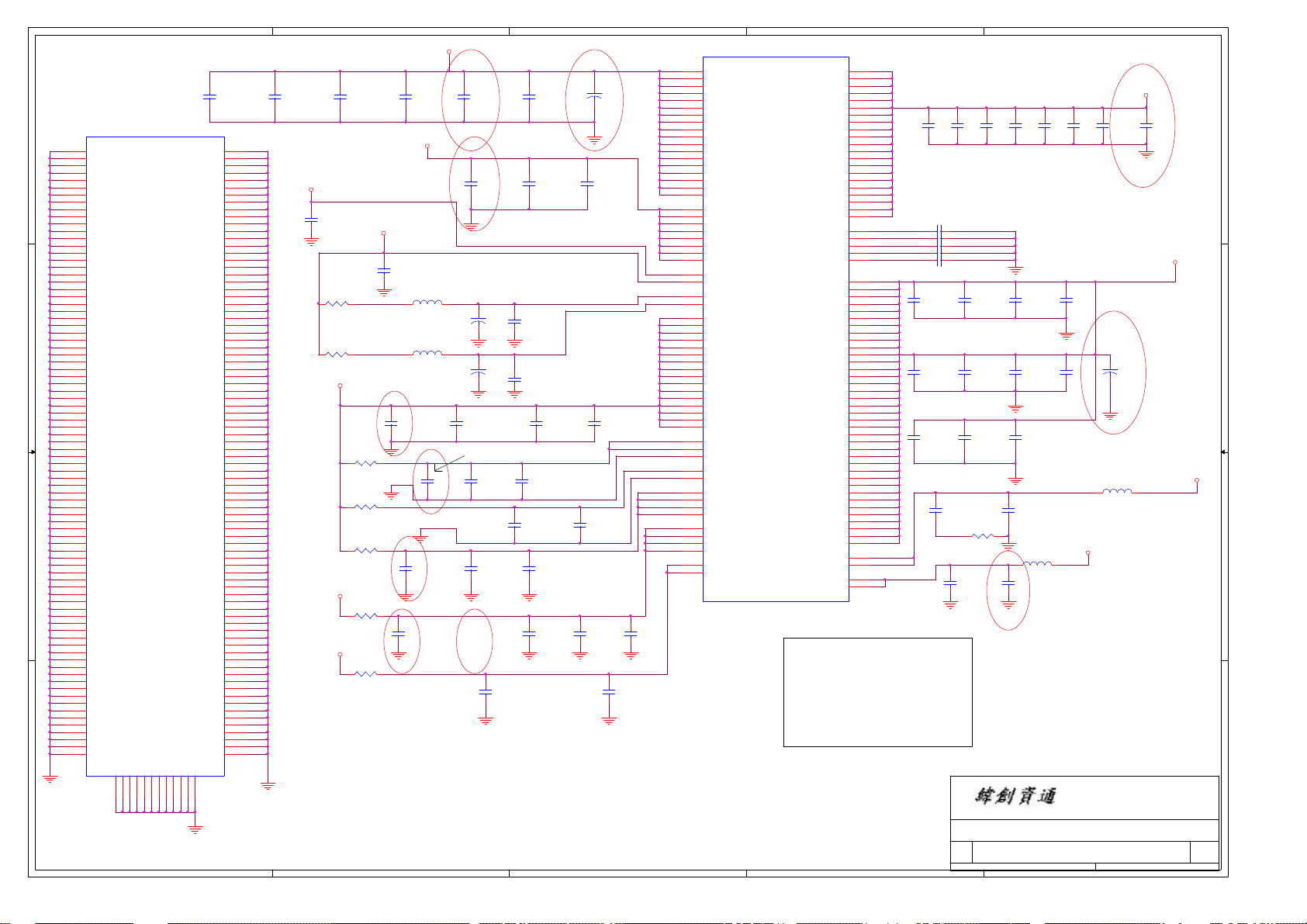

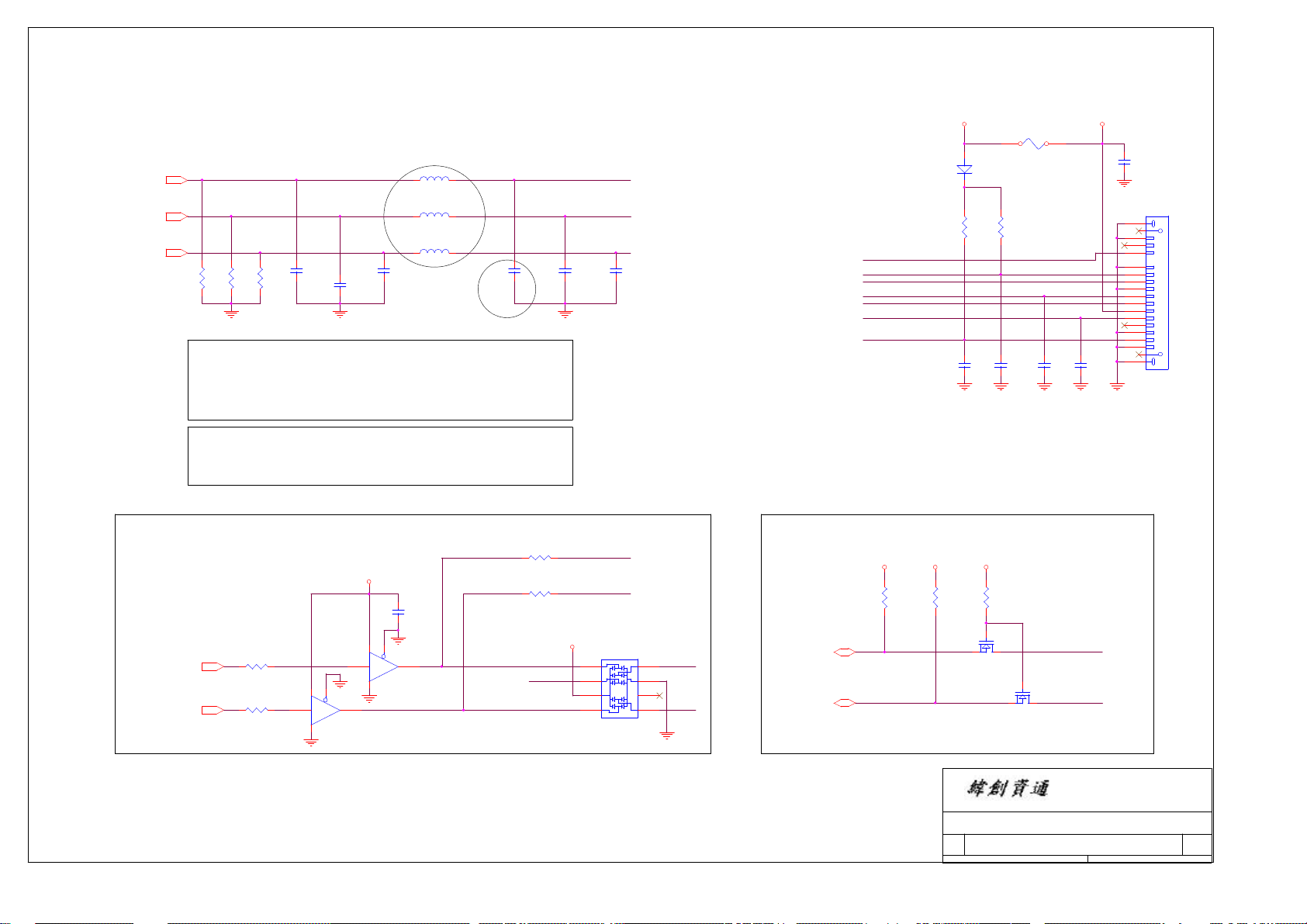

GMCH Strapping Options

Function Board Default Optional Override

PSB Voltage Select Shunt for 1.2V No shunt for 1.05VLCLKCTB

DVO/AGP Strap No shunt for DVO Shunt for AGP

GMCH Frequency Starpping

0 0 0

ST0ST1ST2

0 0 1

0 1 0

0 1 1

1 0 0

1* 0* 1*

1 1 0

1 1 1

D

PSB

FreqSMFreq

400 267 133-200

400

400

400

533

533

533

400

Title

MONTARA GT (2/3)

Size Document Number Rev

Custom

Date: Sheet of

200

200

267

267

267

333

333

GFX Freq

Range

100-200

100-133

133-267

0 = No Shunt

1 = Shunt

* Default

133-200

133-267

167-267

167-250

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

YUHINA

E

7 39Thursday, June 12, 2003

SC

A

C463

SCD1U16V

4 4

3 3

2 2

1 1

U15E

AA29

VSS

W29

VSS

U29

VSS

N29

VSS

L29

VSS

J29

VSS

G29

VSS

E29

VSS

C29

VSS

AE28

VSS

AC28

VSS

E28

VSS

D28

VSS

AJ27

VSS

AG27

VSS

AC27

VSS

F27

VSS

A27

VSS

AJ26

VSS

AB26

VSS

W26

VSS

U26

VSS

R26

VSS

N26

VSS

L26

VSS

J26

VSS

G26

VSS

AE25

VSS

AA25

VSS

D25

VSS

A25

VSS

AG24

VSS

AA24

VSS

V24

VSS

T24

VSS

P24

VSS

M24

VSS

K24

VSS

H24

VSS

F24

VSS

B24

VSS

AJ23

VSS

AC23

VSS

AA23

VSS

D23

VSS

A23

VSS

AE22

VSS

W22

VSS

U22

VSS

R22

VSS

N22

VSS

L22

VSS

J22

VSS

F22

VSS

C22

VSS

AG21

VSS

AB21

VSS

AA21

VSS

Y21

VSS

V21

VSS

T21

VSS

P21

VSS

M21

VSS

H21

VSS

D21

VSS

A21

VSS

AJ20

VSS

AC20

VSS

AA20

VSS

J20

VSS

F20

VSS

AE19

VSS

AB19

VSS

H19

VSS

D19

VSS

A19

VSS

AJ18

VSS

AG18

VSS

AA18

VSS

J18

VSS

F18

VSS

AC17

VSS

AB17

VSS

U17

VSS

MONTARA-GT-U1

VSS

R17

VSS

VSS

N17

H17

GND

VSS

VSS

VSS

VSS

A17

D17

AE16

AA16

A

AE13

VSS

AB13

VSS

U13

VSS

R13

VSS

N13

VSS

H13

VSS

F13

VSS

D13

VSS

A13

VSS

AJ12

VSS

AG12

VSS

AA12

VSS

J12

VSS

AJ11

VSS

AC11

VSS

AB11

VSS

H11

VSS

F11

VSS

D11

VSS

AJ10

VSS

AE10

VSS

AA10

VSS

J10

VSS

C10

VSS

AG9

VSS

AB9

VSS

W9

VSS

U9

VSS

T9

VSS

R9

VSS

N9

VSS

L9

VSS

E9

VSS

AC8

VSS

Y8

VSS

V8

VSS

T8

VSS

P8

VSS

K8

VSS

H8

VSS

AJ7

VSS

AE7

VSS

AA7

VSS

R7

VSS

M7

VSS

J7

VSS

G7

VSS

E7

VSS

C7

VSS

AG6

VSS

Y6

VSS

L6

VSS

Y5

VSS

U5

VSS

B5

VSS

AE4

VSS

AC4

VSS

AA4

VSS

W4

VSS

T4

VSS

N4

VSS

K4

VSS

G4

VSS

D4

VSS

AJ3

VSS

AG3

VSS

R2

VSS

AE1

VSS

AA1

VSS

U1

VSS

L1

VSS

G1

VSS

C1

VSS

F16

VSS

AG15

VSS

AB15

VSS

U15

VSS

R15

VSS

N15

VSS

H15

VSS

D15

VSS

AC14

VSS

AA14

VSS

T14

VSS

VSS

VSS

VSS

VSS

VSS

J16

J14

T16

P16

P14

C462

SCD1U16V

1D5V_S0

C473

SCD1U16V

R69

1 2

1R5

R81

1 2

1R5

1D5V_S0

Orignal us e 220uF6V

Orignal us e 47uF4V

2D5V_S0

Orignal us e 47uF4V

3D3V_S0

Orignal u se 22uF

B

1D5V_S0

C459

SCD1U16V

1D5V_S0

VCCADPLLB

C455

SCD1U16V

1D5V_S0

C81

SCD1U16V

L9

1 2

IND-D1UH

68.R1020.1F1

L10

1 2

IND-D1UH

68.R1020.1F1

ST100U4VBM

Orignal use 150uF6.3V

R78

1 2

0R3-0-U

R80

1 2

0R3-0-U

R368

1 2

0R3-0-U

R372

1 2

0R3-0-U

R382

1 2

0R3-0-U

12

TC26

SC10U10V5ZY

12

12

B

12

TC20

SC10U10V5ZY

TC21

SC10U10V5ZY

TC19

SC10U10V5ZY

12

C470

TC18

TC15

12

C68

SCD1U16V

C73

SCD1U16V

12

C479

DUMMY-SC10U6D3V5MX

12

DUMMY-SC10U6D3V5MX

12

12

ST100U4VBM

C92

DUMMY-SC10U10V5ZY

For VGA noise issue

12

C69

SCD1U16V

12

C71

SCD01U16V2KX

12

C371

DUMMY-SC10U10V5ZY

12

TC24

SC10U10V5ZY

C435

SC10U6D3V5MX

C468

SCD1U16V

VCC_ADPLLAVCCADPLLA

VCC_ADPLLB

C454

SCD1U16V

C70

SCD01U16V2KX

C406

SCD1U16V

C411

SCD1U16V

C

12

TC5

DUMMY-ST150U6D3VM-U

C469

SCD1U16V

C460

SCD1U16V

VCC_ADAC

VCCALVDS

VCCDLVDS

C72

SCD1U16V

C398

SCD1U16V

VCCGPIO

C427

SCD1U16V

C

VCCTXLVDS

C407

SCD1U16V

W21

AA19

AA17

T17

P17

U16

R16

N16

AA15

T15

P15

J15

U14

R14

N14

H14

T13

P13

V9

W8

U8

V7

U6

W5

Y1

V1

Y2

D29

A6

B16

P9

M9

K9

R8

N8

M8

L8

J8

H7

E6

M4

J4

E4

N1

J1

E1

B9

A9

B8

A11

B11

B15

B14

J13

G13

A12

D10

B10

F9

A3

A4

MONTARA-GT-U1

U15D

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

2540mA

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCC

VCCHL

VCCHL

VCCHL

VCCHL

VCCHL

VCCHL

VCCHL

VCCHL

VCCAGPLL

VCCAHPLL

VCCADPLLA

VCCADPLLB

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCDVO

VCCADAC

VCCADAC

VSSADAC

VCCALVDS

VSSALVDS

VCCDLVDS

VCCDLVDS

VCCDLVDS

VCCDLVDS

VCCTXLVDS

VCCTXLVDS

VCCTXLVDS

VCCTXLVDS

VCCGPIO

VCCGPIO

90mA

90mA

90mA

70mA

70mA

40mA

50mA

20mA

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

940mA

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTLF

VTTHF

VTTHF

VTTHF

VTTHF

VTTHF

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

POWER

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

2000mA

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCSM

VCCQSM

VCCQSM

VCCASM

240mA

VCCASM

Power Con sumption

VCC-COR E_S0:

1D5V_S0: 3140mA

2D5V_S3: 2050mA

3D3V_S0: 20mA

AB29

Y29

K29

F29

A26

V22

T22

P22

M22

H22

U21

R21

N21

L21

H20

A20

J19

H18

A18

H16

G15

V29

M29

H29

A24

A22

AG29

AF29

AC29

AF27

AJ25

AF24

AB22

AJ21

AF21

AB20

AF18

AB18

AJ17

AB16

AF15

AB14

AJ13

AA13

AF12

AB12

AA11

AB10

AJ9

AF9

Y9

AB8

AA8

Y7

AF6

AB6

AA6

AJ5

Y4

AF3

AB3

AG1

AC1

AJ8

AJ6

AF1

AD1

D

VTTHF1

VTTHF2

VTTHF3

VTTHF4

VTTHF5

D

C457

C96 SCD1U16V

C89 SCD1U16V

C83 SCD1U16V

C414 SCD1U16V

C413 SCD1U16V

12

C478

12

C498

12

C501

VCC_ASM

940mA

E

VCC_CORE

12

SCD1U10V2MX-1

12

C461

12

C445

SCD1U10V2MX-1

SCD1U10V2MX-1

12

C464

12

C452

SCD1U10V2MX-1

12

C446

SC10U6D3V5MX

SCD1U10V2MX-1

SCD1U10V2MX-1

12

C67

Orignal u se 220uF

12

C121

SCD1U10V2MX-1

12

C477

SCD1U10V2MX-1

12

C487

SCD1U10V2MX-1

VCC_QSM

12

C125

SC10U10V5ZY

1 2

VCCQSM_1

C116

SCD1U16V

Title

Size Document Number Rev

A3

Date: Sheet of

12

C481

R143

SCD1U10V2M X-1

SCD1U10V2M X-1

SCD1U10V2M X-1

1R5

SCD1U10V2MX-1

12

C497

SCD1U10V2MX-1

12

C482

SCD1U10V2MX-1

12

C122

SCD1U10V2M X-1

L14

1 2

IND-1UH-5

12

TC6

SC10U10V5ZY

Origna l use

100uF 6.3V

MONTARA GT (3/3)

12

C499

SCD1U10V2M X-1

12

12

C472

SCD1U10V2M X-1

Origna l use

150uFX 2 6.3V

L15

1 2

IND-D68UH-2

68.R6830.101

1D5V_S0

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

YUHINA

E

TC7

ST100U4VBM

8 39Thursday, June 12, 2003

12

TC16

SC10U10V5ZY

78.10693.411

2D5V_S3

2D5V_S3

SC

M_A[12..0]6,10

R235 10R3

M_A0 M_R_A0

1 2

R217 10R3

M_A3 M_R_A3

1 2

R234 10R3

1 2

R216 10R3

M_A7 M_R_A7

1 2

R233 10R3

M_A8 M_R_A8

1 2

R215 10R3

1 2

R218 10R3

M_A10 M_R_A10

1 2

R232 10R3

1 2

R214 10R3

M_A12 M_R_A12

1 2

M_R_A6M_A6

M_R_A9M_A9

M_R_A11M_A11

DDR_VREF_S3 DDR_VREF_S3

M_A0

M_A1

M_A2

M_A3

M_A4

M_A5

M_A6

M_A7

M_A8

M_A9

M_A10

M_A11

M_A12

M_BS0_FR#

M_BS1_FR#

M_DATA_R_0

M_DATA_R_1

M_DATA_R_2

M_DATA_R_3

M_DATA_R_4

M_DATA_R_5

M_DATA_R_6

M_DATA_R_7

M_DATA_R_8

M_DATA_R_9

M_DATA_R_10

M_DATA_R_11

M_DATA_R_12

M_DATA_R_13

M_DATA_R_14

M_DATA_R_15

M_DATA_R_16

M_DATA_R_17

M_DATA_R_18

M_DATA_R_19

M_DATA_R_20

M_DATA_R_21

M_DATA_R_22

M_DATA_R_23

M_DATA_R_24

M_DATA_R_25

M_DATA_R_26

M_DATA_R_27

M_DATA_R_28

M_DATA_R_29

M_DATA_R_30

M_DATA_R_31

M_DATA_R_32

M_DATA_R_33

M_DATA_R_34

M_DATA_R_35

M_DATA_R_36

M_DATA_R_37

M_DATA_R_38

M_DATA_R_39

M_DATA_R_40

M_DATA_R_41

M_DATA_R_42

M_DATA_R_43

M_DATA_R_44

M_DATA_R_45

M_DATA_R_46

M_DATA_R_47

M_DATA_R_48

M_DATA_R_49

M_DATA_R_50

M_DATA_R_51

M_DATA_R_52

M_DATA_R_53

M_DATA_R_54

M_DATA_R_55

M_DATA_R_56

M_DATA_R_57

M_DATA_R_58

M_DATA_R_59

M_DATA_R_60

M_DATA_R_61

M_DATA_R_62

M_DATA_R_63

M_RAS#

M_CAS#

M_WE#

3D3V_S0

12

C193

SCD1U10V2M X-1

DM1

112

A0

111

A1

110

A2

109

A3

108

A4

107

A5

106

A6

105

A7

102

A8

101

A9

115

A10 / AP

100

A11

99

A12

117

BA0

116

BA1

5

DQ0

7

DQ1

13

DQ2

17

DQ3

6

DQ4

8

DQ5

14

DQ6

18

DQ7

19

DQ8

23

DQ9

29

DQ10

31

DQ11

20

DQ12

24

DQ13

30

DQ14

32

DQ15

41

DQ16

43

DQ17

49

DQ18

53

DQ19

42

DQ20

44

DQ21

50

DQ22

54

DQ23

55

DQ24

59

DQ25

65

DQ26

67

DQ27

56

DQ28

60

DQ29

66

DQ30

68

DQ31

127

DQ32

129

DQ33

135

DQ34

139

DQ35

128

DQ36

130

DQ37

136

DQ38

140

DQ39

141

DQ40

145

DQ41

151

DQ42

153

DQ43

142

DQ44

146

DQ45

152

DQ46

154

DQ47

163

DQ48

165

DQ49

171

DQ50

175

DQ51

164

DQ52

166

DQ53

172

DQ54

176

DQ55

177

DQ56

181

DQ57

187

DQ58

189

DQ59

178

DQ60

182

DQ61

188

DQ62

190

DQ63

71

CB0

73

CB1

79

CB2

83

CB3

72

CB4

74

CB5

80

CB6

84

CB7

85

NC

86

NC/(RESET#)

97

NC/A13

98

NC/BA2

123

NC

124

NC

200

NC

118

/RAS

120

/CAS

119

/WE

1

VREF

2

VREF

197

VDDSPD

199

VDDID

202

GND

DDR-SODIMM-R-U1

M_DATA_R_[63..0]10

121

/CS0

122

/CS1

96

CKE0

95

CKE1

11

DQS0

25

DQS1

47

DQS2

61

DQS3

133

DQS4

147

DQS5

169

DQS6

183

DQS7

77

DQS8

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DM8

CK0

/CK0

CK1

/CK1

CK2

/CK2

SCL

SDA

SA0

SA1

SA2

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VDD

VSS

REVERSE TYPE

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

GND

M_SDM_R0

12

M_SDM_R1

26

M_SDM_R2

48

M_SDM_R3

62

M_SDM_R4

134

M_SDM_R5

148

M_SDM_R6

170

M_SDM_R7

184

78

35

37

160

158

89

91

SMBC_ICH

195

SMBD_ICH

193

DM1_SA0

194

196

198

9

10

21

22

33

34

36

45

46

57

58

69

70

81

82

92

93

94

113

114

131

132

143

144

155

156

157

167

168

179

180

191

192

3

4

15

16

27

28

38

39

40

51

52

63

64

75

76

87

88

90

103

104

125

126

137

138

149

150

159

161

162

173

174

185

186

201

M_DQS_R0

M_DQS_R1

M_DQS_R2

M_DQS_R3

M_DQS_R4

M_DQS_R5

M_DQS_R6

M_DQS_R7

M_CS0_R# 6,10

M_CS1_R# 6,10

M_CKE0_R# 6,10

M_CKE1_R# 6,10

CLK_DDR0 6

CLK_DDR0# 6

CLK_DDR1 6

CLK_DDR1# 6

CLK_DDR2 6

CLK_DDR2# 6

M_BS0_FR#6

M_BS1_FR#6

2D5V_S3

M_RAS#6

M_CAS#6

M_WE#6

R228

0R3-U

10R3

R229

1 2

12

DUMMY-R3

R219

10R3

1 2

1 2

R236

10R3

R23710R3

1 2

R23810R3

1 2

1 2

R220

M_R_RAS#

M_R_CAS#

M_R_WE#

M_R_A010

M_B16,10

M_B26,10

M_R_A310

M_B46,10

M_B56,10

M_R_A610

M_R_A710

M_R_A810

M_R_A910

M_R_A1010

M_R_A1110

M_R_A1210

M_BS_FR#_0 10

M_BS_FR#_1 10

M_R_RAS#10

M_R_CAS#10

M_R_WE#10

M_R_A0

M_R_A3

M_R_A6

M_R_A7

M_R_A8

M_R_A9

M_R_A10

M_R_A11

M_R_A12

M_BS_FR#_0

M_BS_FR#_1

M_DATA_R_0

M_DATA_R_1

M_DATA_R_2

M_DATA_R_3

M_DATA_R_4

M_DATA_R_5

M_DATA_R_6

M_DATA_R_7

M_DATA_R_8

M_DATA_R_9

M_DATA_R_10

M_DATA_R_11

M_DATA_R_12

M_DATA_R_13

M_DATA_R_14

M_DATA_R_15

M_DATA_R_16

M_DATA_R_17

M_DATA_R_18

M_DATA_R_19

M_DATA_R_20

M_DATA_R_21

M_DATA_R_22

M_DATA_R_23

M_DATA_R_24

M_DATA_R_25

M_DATA_R_26

M_DATA_R_27

M_DATA_R_28

M_DATA_R_29

M_DATA_R_30

M_DATA_R_31

M_DATA_R_32

M_DATA_R_33

M_DATA_R_34

M_DATA_R_35

M_DATA_R_36

M_DATA_R_37

M_DATA_R_38

M_DATA_R_39

M_DATA_R_40

M_DATA_R_41

M_DATA_R_42

M_DATA_R_43

M_DATA_R_44

M_DATA_R_45

M_DATA_R_46

M_DATA_R_47

M_DATA_R_48

M_DATA_R_49

M_DATA_R_50

M_DATA_R_51

M_DATA_R_52

M_DATA_R_53

M_DATA_R_54

M_DATA_R_55

M_DATA_R_56

M_DATA_R_57

M_DATA_R_58

M_DATA_R_59

M_DATA_R_60

M_DATA_R_61

M_DATA_R_62

M_DATA_R_63

M_R_RAS#

M_R_CAS#

M_R_WE#

3D3V_S0

12

C161

SCD1U10V2M X-1

DM2

112

A0

111

A1

110

A2

109

A3

108

A4

107

A5

106

A6

105

A7

102

A8

101

A9

115

A10 / AP

100

A11

99

A12

117

BA0

116

BA1

5

DQ0

7

DQ1

13

DQ2

17

DQ3

6

DQ4

8

DQ5

14

DQ6

18

DQ7

19

DQ8

23

DQ9

29

DQ10

31

DQ11

20

DQ12

24

DQ13

30

DQ14

32

DQ15

41

DQ16

43

DQ17

49

DQ18

53

DQ19

42

DQ20

44

DQ21

50

DQ22

54

DQ23

55

DQ24

59

DQ25

65

DQ26

67

DQ27

56

DQ28

60

DQ29

66

DQ30

68

DQ31

127

DQ32

129

DQ33

135

DQ34

139

DQ35

128

DQ36

130

DQ37

136

DQ38

140

DQ39

141

DQ40

145

DQ41

151

DQ42

153

DQ43

142

DQ44

146

DQ45

152

DQ46

154

DQ47

163

DQ48

165

DQ49

171

DQ50

175

DQ51

164

DQ52

166

DQ53

172

DQ54

176

DQ55

177

DQ56

181

DQ57

187

DQ58

189

DQ59

178

DQ60

182

DQ61

188

DQ62

190

DQ63

71

CB0

73

CB1

79

CB2

83

CB3

72

CB4

74

CB5

80

CB6

84

CB7

85

NC

86

NC/(RESET#)

97

NC/A13

98

NC/BA2

123

NC

124

NC

200

NC

118

/RAS

120

/CAS

119

/WE

1

VREF

2

VREF

197

VDDSPD

199

VDDID

201

GND

DDR-SODIMM-N-U1

121

/CS0

122

/CS1

96

CKE0

95

CKE1

11

DQS0

25

DQS1

47

DQS2

61

DQS3

133

DQS4

147

DQS5

169

DQS6

183

DQS7

77

DQS8

12

DM0

26

DM1

48

DM2

62

DM3

134

DM4

148

DM5

170

DM6

184

DM7

78

DM8

35

CK0

37

/CK0

160

CK1

158

/CK1

89

CK2

91

/CK2

195

SCL

193

SDA

DM2_SA0

194

SA0

196

SA1

198

SA2

9

VDD

10

VDD

21

VDD

22

VDD

33

VDD

34

VDD

36

VDD

45

VDD

46

VDD

57

VDD

58

VDD

69

VDD

70

VDD

81

VDD

82

VDD

92

VDD

93

VDD

94

VDD

113

VDD

114

VDD

131

VDD

132

VDD

143

VDD

144

VDD

155

VDD

156

VDD

157

VDD

167

VDD

168

VDD

179

VDD

180

VDD

191

VDD

192

VDD

NORMAL TYPE

3

VSS

4

VSS

15

VSS

16

VSS

27

VSS

28

VSS

38

VSS

39

VSS

40

VSS

51

VSS

52

VSS

63

VSS

64

VSS

75

VSS

76

VSS

87

VSS

88

VSS

90

VSS

103

VSS

104

VSS

125

VSS

126

VSS

137

VSS

138

VSS

149

VSS

150

VSS

159

VSS

161

VSS

162

VSS

173

VSS

174

VSS

185

VSS

186

VSS

202

GND

M_CS2_R# 6,10

M_CS3_R# 6,10

M_CKE2_R# 6,10

M_CKE3_R# 6,10

M_DQS_R0

M_DQS_R1

M_DQS_R2

M_DQS_R3

M_DQS_R4

M_DQS_R5

M_DQS_R6

M_DQS_R7

M_SDM_R0

M_SDM_R1

M_SDM_R2

M_SDM_R3

M_SDM_R4

M_SDM_R5

M_SDM_R6

M_SDM_R7

CLK_DDR3 6

CLK_DDR3# 6

CLK_DDR4 6

CLK_DDR4# 6

CLK_DDR5 6

CLK_DDR5# 6

SMBC_ICH 3,14

SMBD_ICH 3,14

2D5V_S3

Title

DDR Socket

Size Document Number Rev

Custom

Date: Sheet of

M_DQS_R[7..0] 10

M_SDM_R[7..0] 10

R285

1 2

12

0R3-U

R284

DUMMY-R3

Wistron Corporation

21F, 88, Sec.1, Hsin Tai Wu Rd., Hsichih,

Taipei Hsien 221, Taiwan, R.O.C.

YUHINA