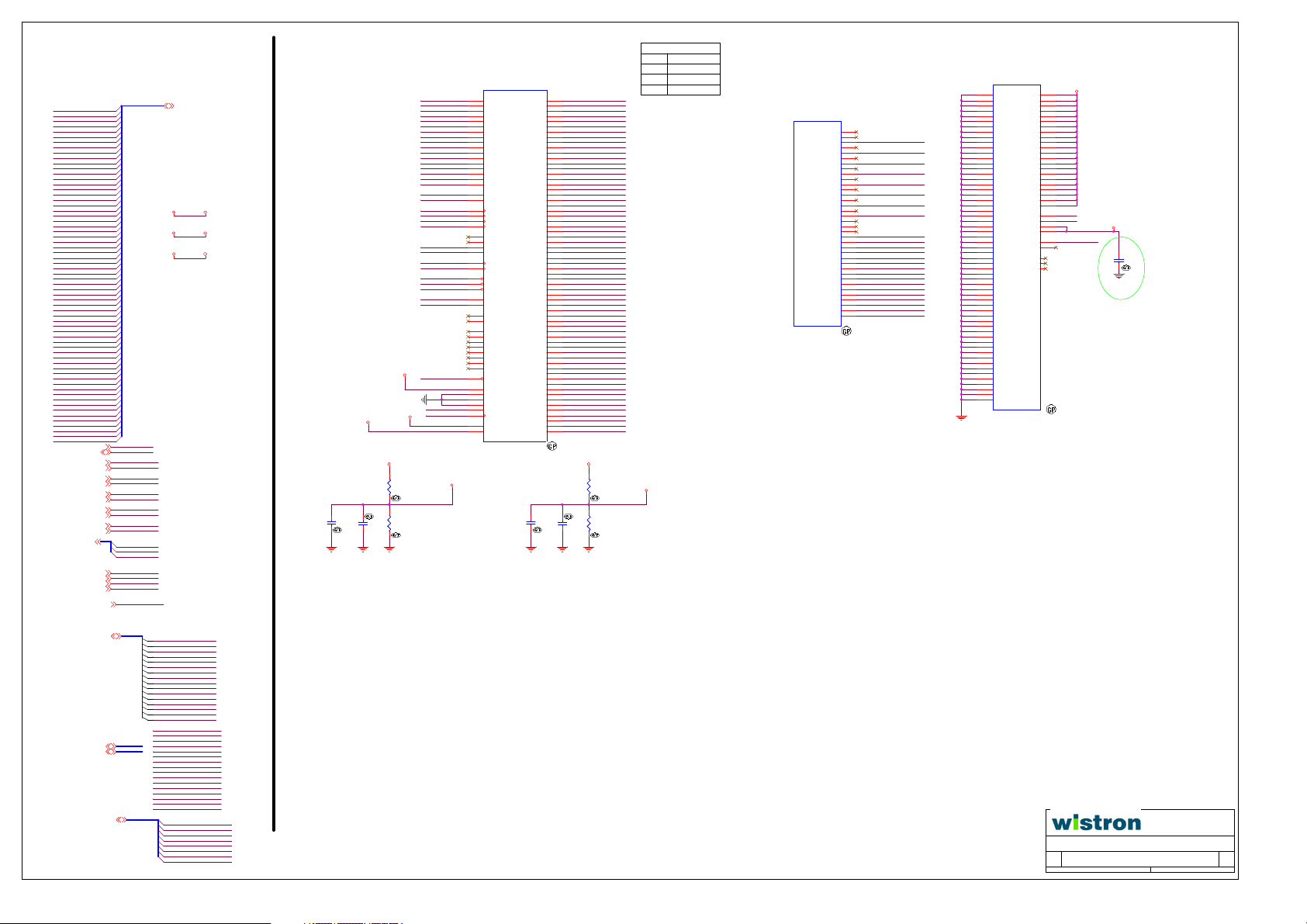

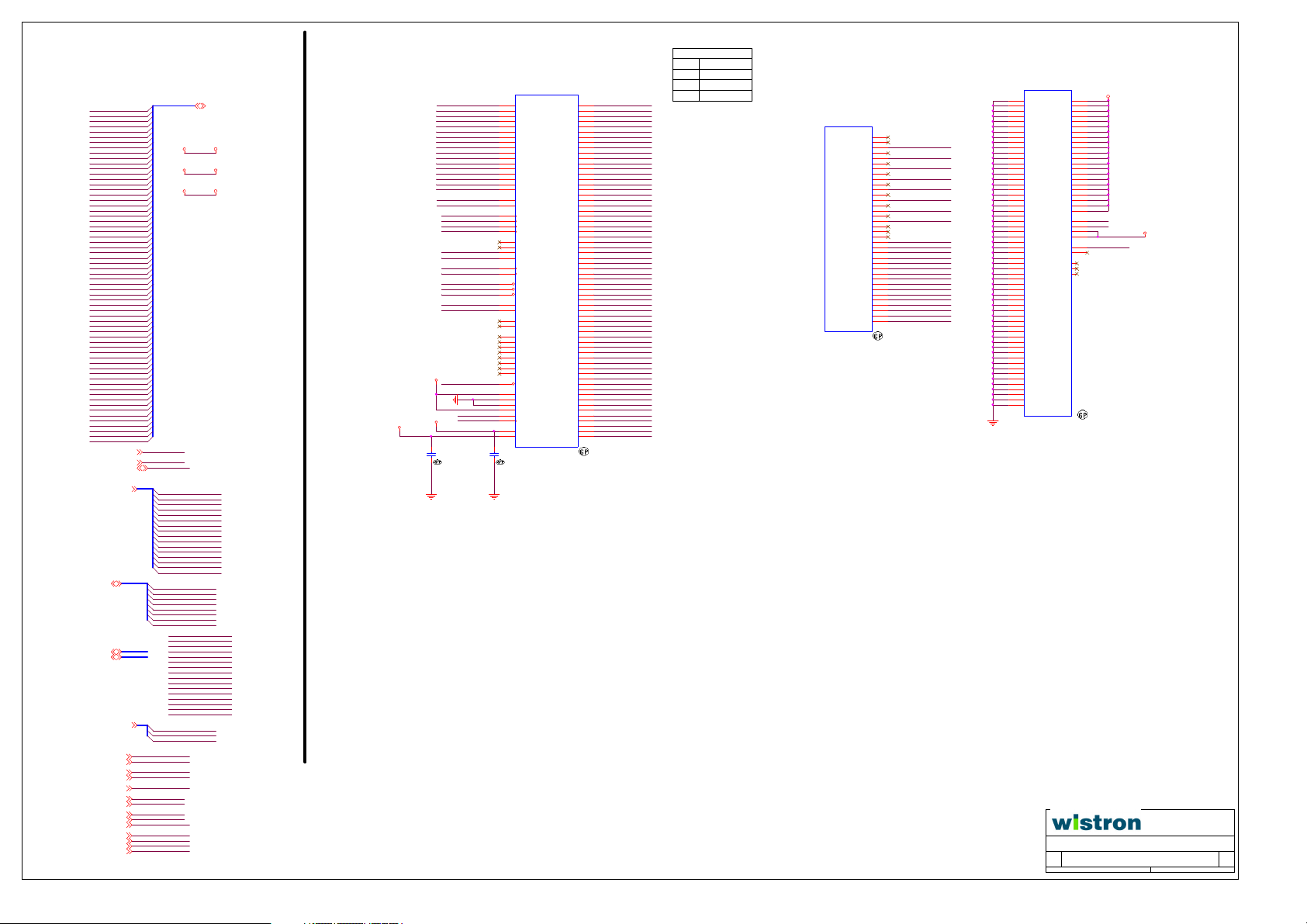

Acer Aspire x1400, Aspire X1420 Schematics

09178-1A(11/03/2009)

Sheet

COVER PAGESheet 1

Sheet 2

Sheet 3

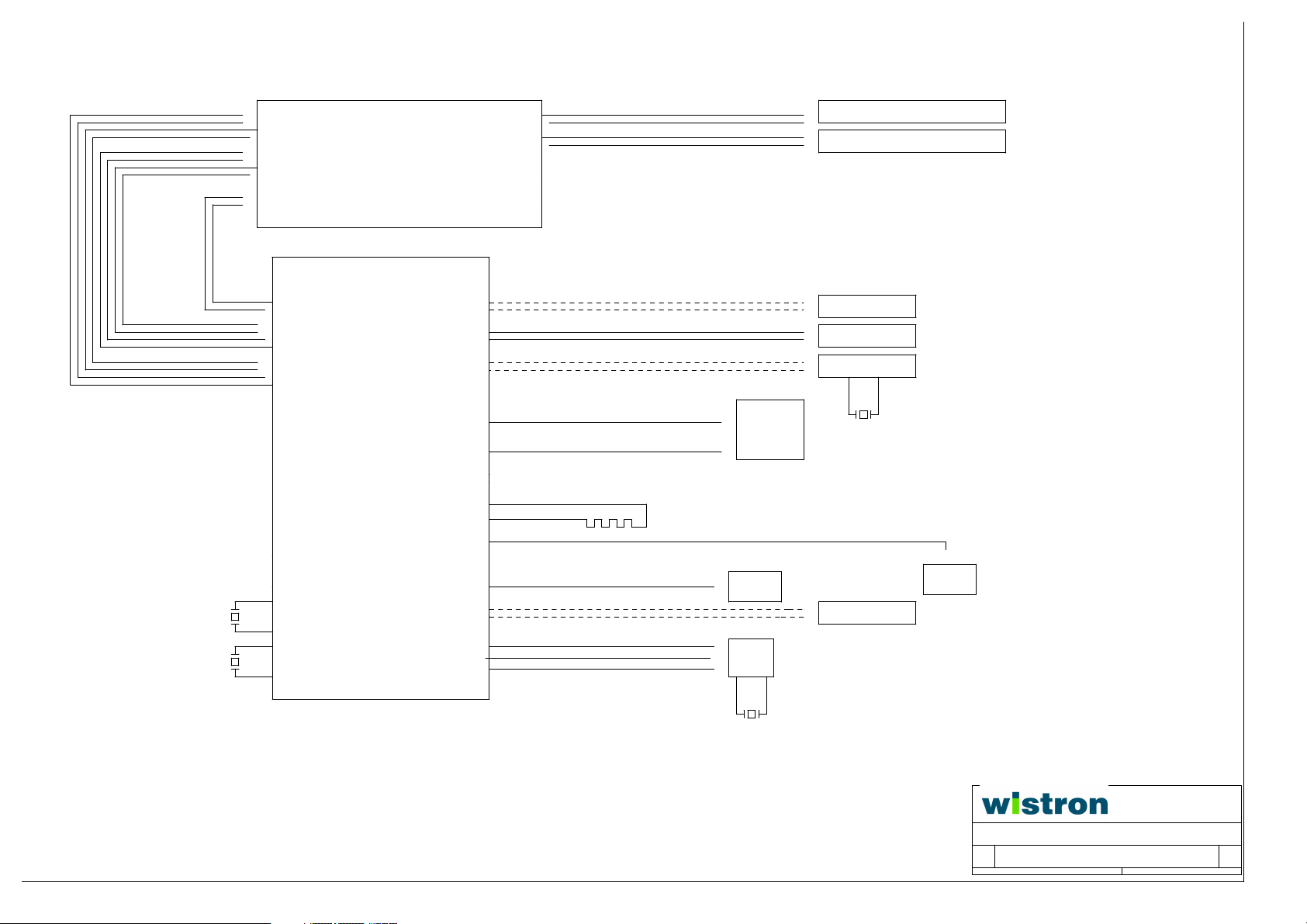

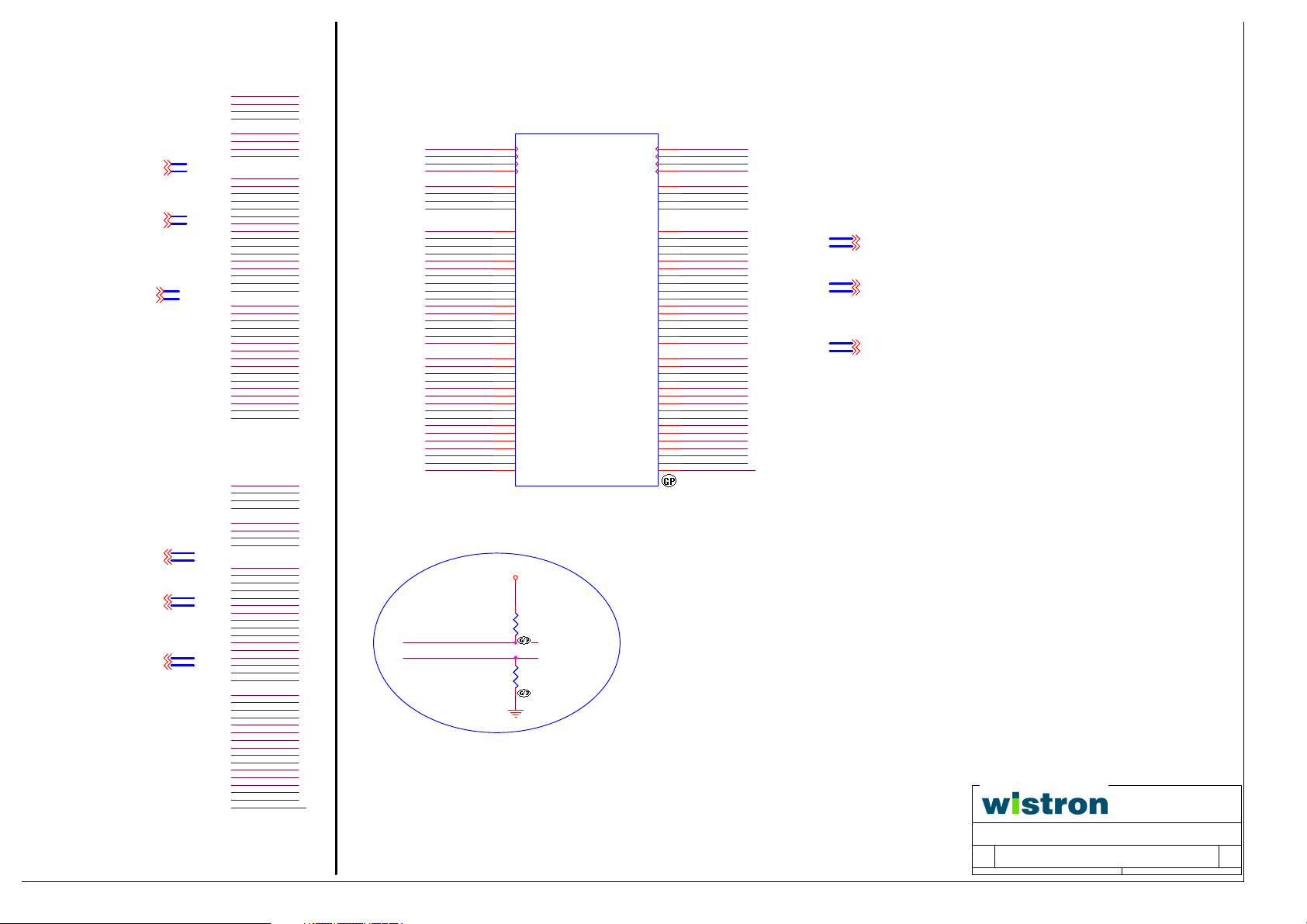

Sheet 4 CLOCK DIAGRAM

Sheet 5

Sheet 6

Sheet 9

Sheet 10

Sheet 11

Sheet 12

Sheet 13

Sheet 14

Sheet 15

Sheet 17 MCP61 PEX X1/RGMII/HDMI/DAC

Sheet 18

Sheet 19

Sheet 21 MCP61 PWR/GND

Sheet 22

Sheet 23

Sheet 24

Sheet 25

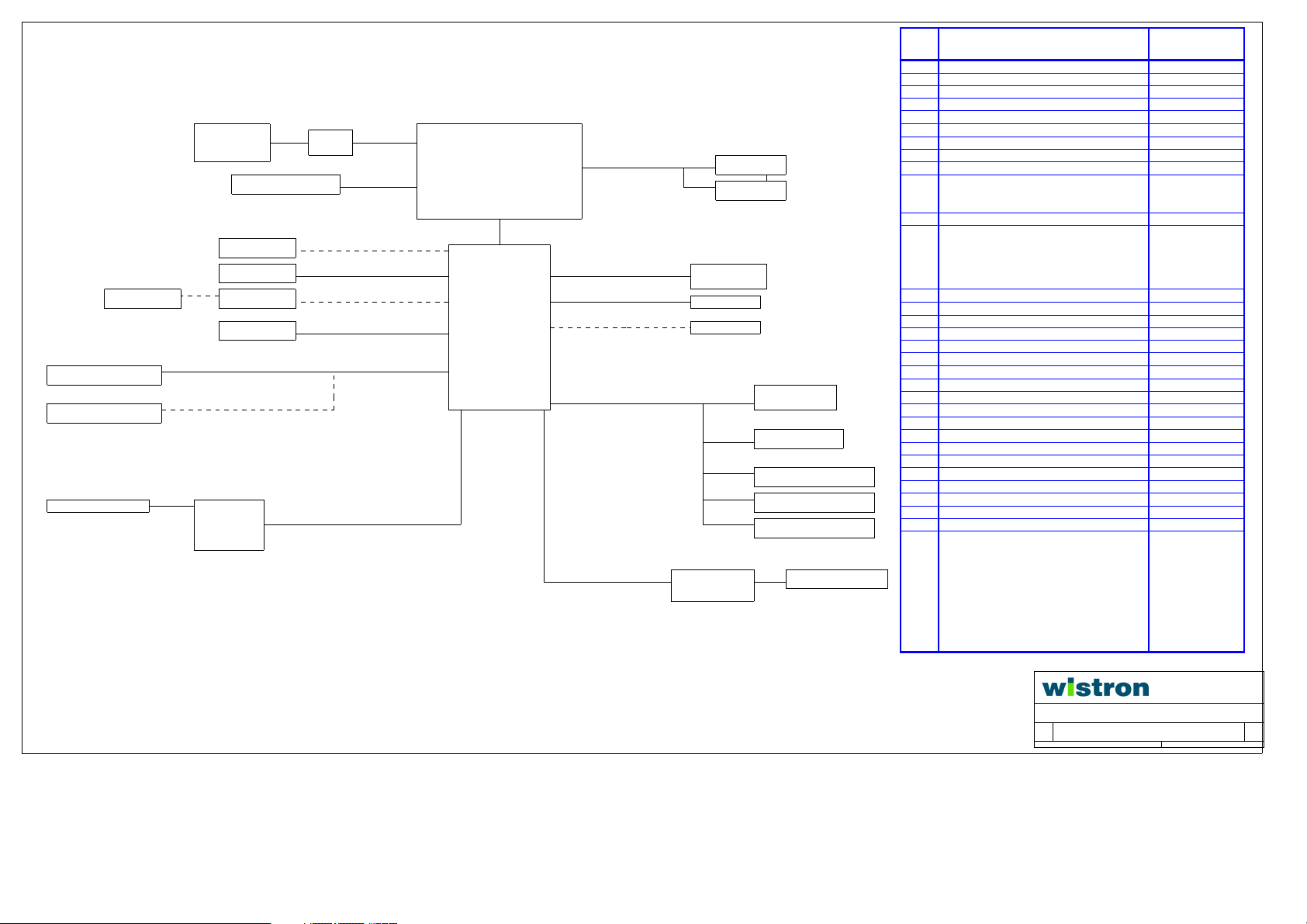

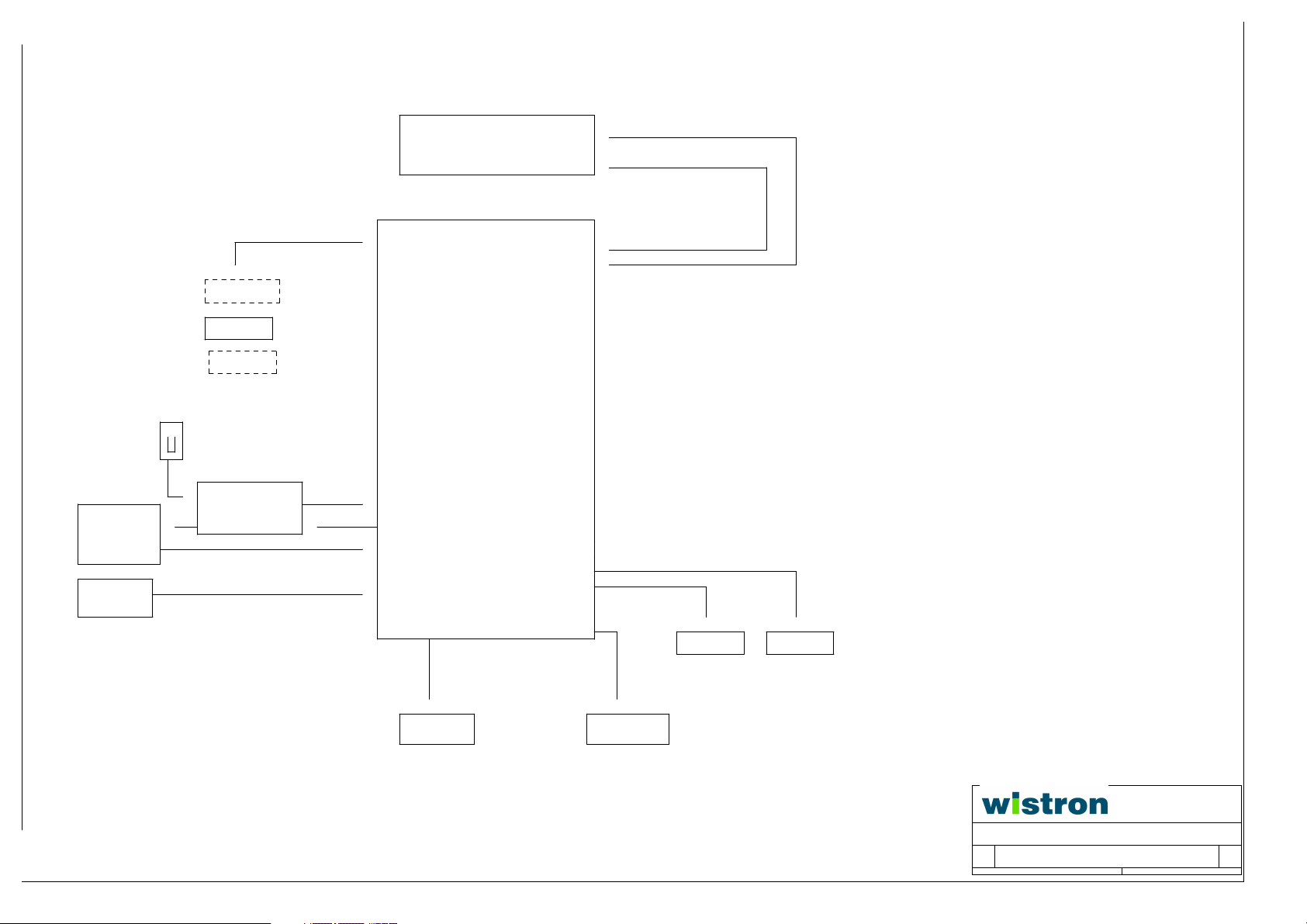

BlOCK DIAGRAM

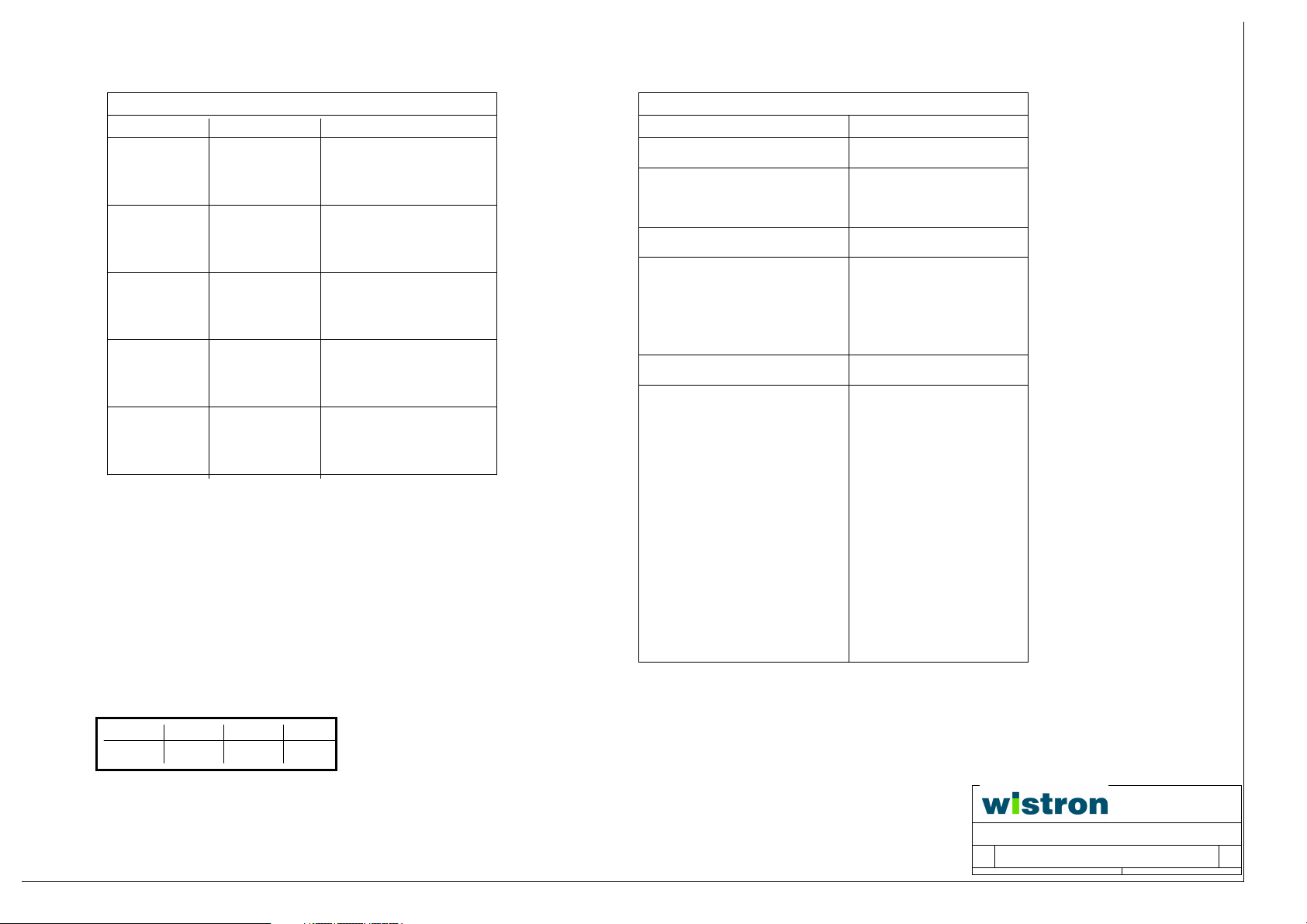

POWER DISTRIBUTION

RESET MAP

GPIO TABLE

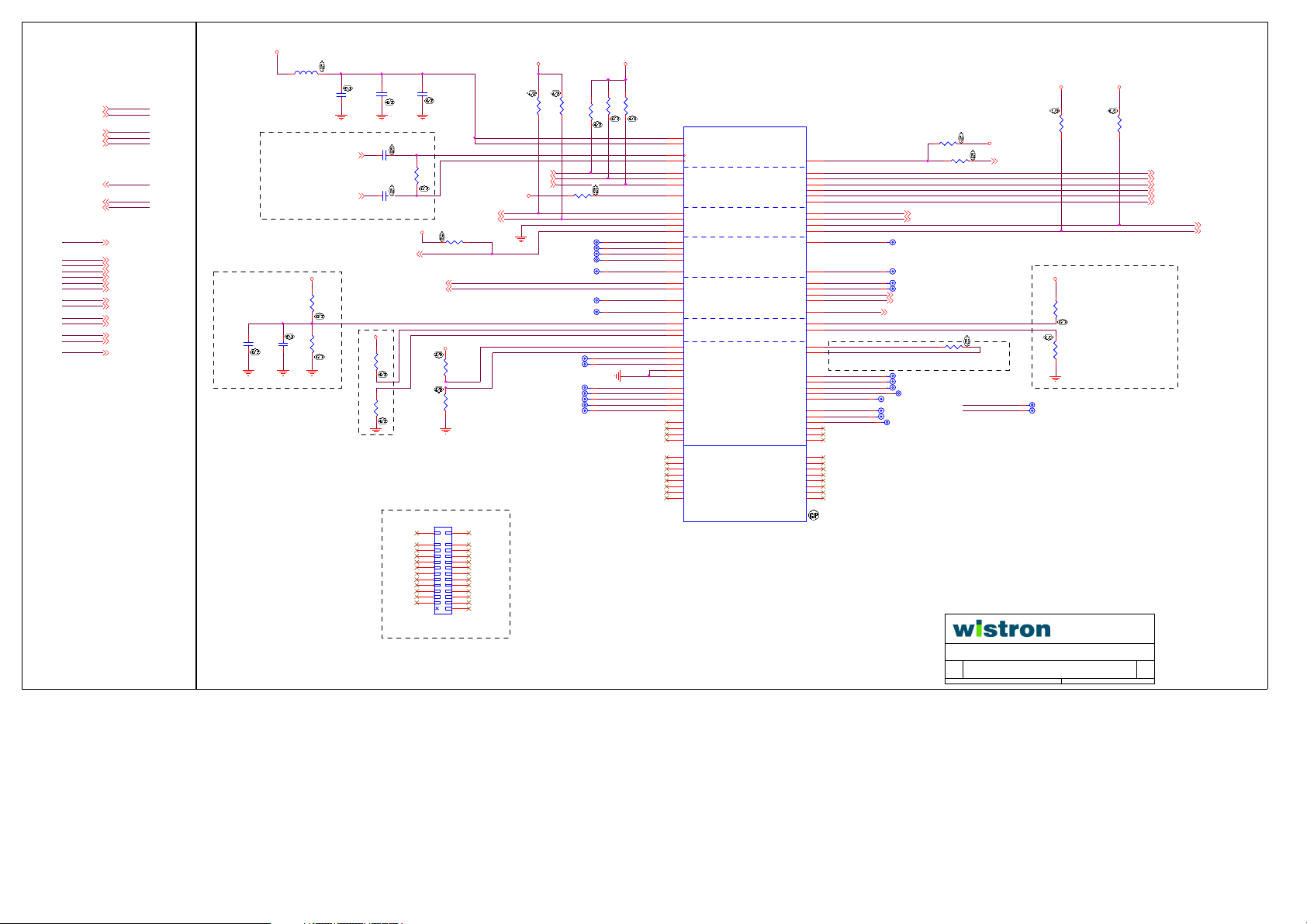

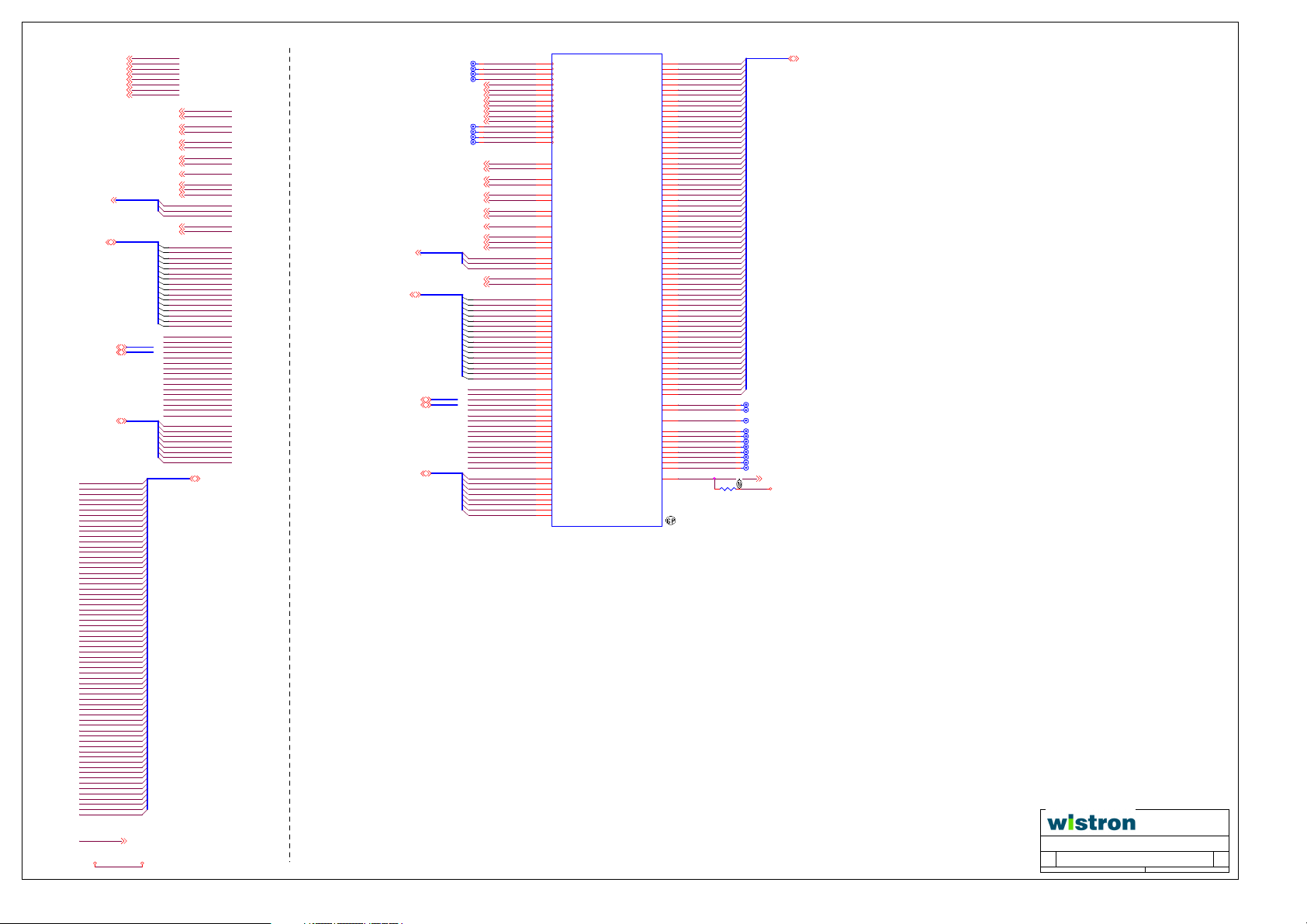

CPU HT INTERFACESheet 7

CPU CNTL/STRAPSSheet 8

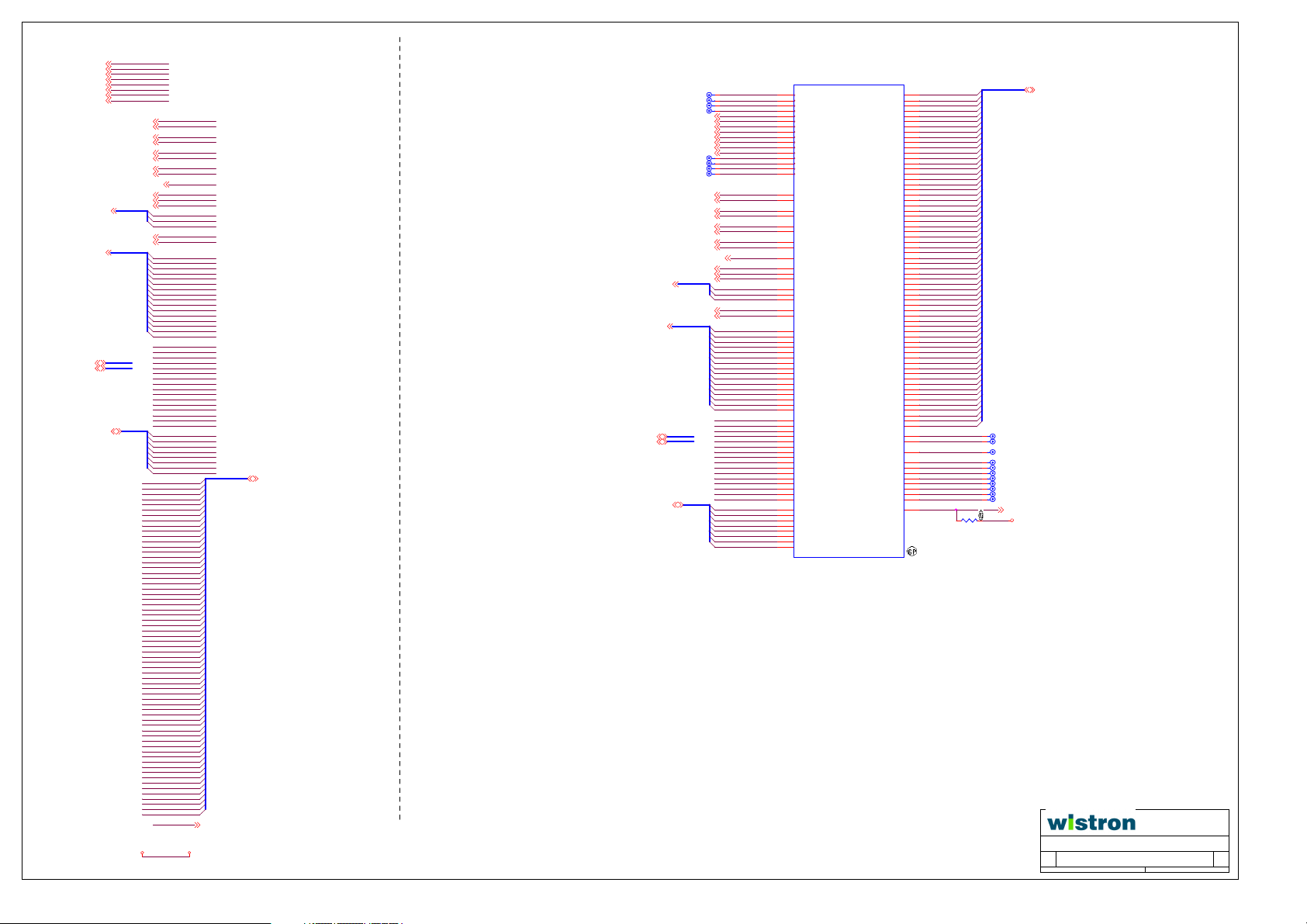

CPU MEM_A

CPU MEM_B

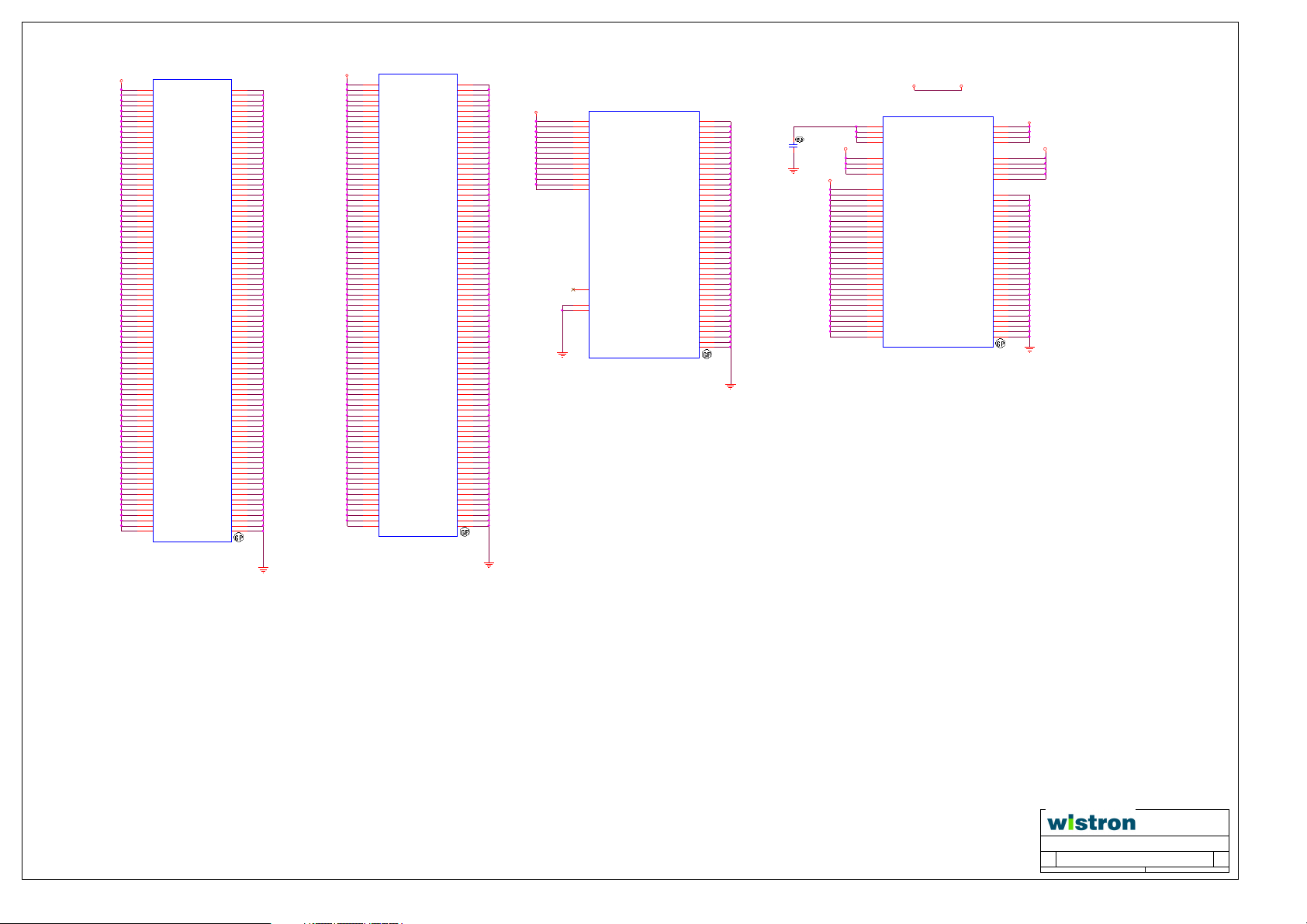

CPU POWER/GND

CPU DECOUPLING

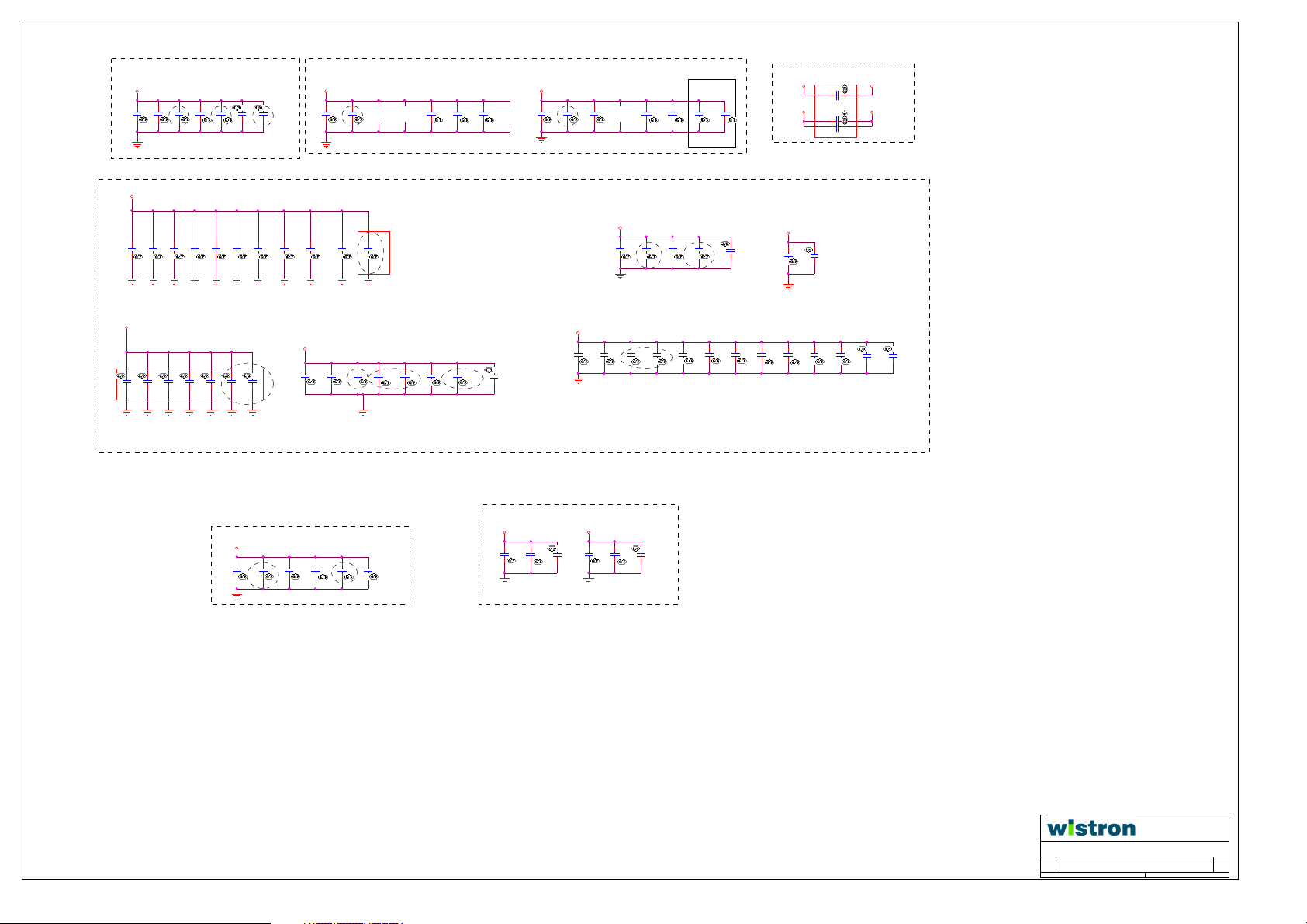

MEM_DIMM_A0

MEM_DIMM_B0

MCP61 HT/CLKS

MCP61 PEX X16Sheet 16

MCP61 PCI/LPC

MCP61 SATA/IDE

MCP61 AUDIO/USB/MISCSheet 20

MCP61 DECOUPLING/SPI

HDMI CONNECTOR

VGA CONNECTOR

PCIEX16 CONNECTOR

Sheet

Sheet 26

Sheet 27

Sheet 28

Sheet 29

Sheet 30

Sheet 31

Sheet 34

Sheet 35

Sheet 36

Sheet 37

Sheet 38

Sheet 39

Sheet 40

Sheet 41

Sheet 42

Sheet 43

Sheet 44

Sheet 45

PCIEX1 CONNECTOR

VT6315N 1394 CONTROLLER

USB+E-SATA CONNECTOR/FRONT

USB+RJ45 CONNECOTR/FRONT

LAN RTL8211CL/8201EL

SIO IT8755E/ITE8757/DEBUG

SERIAL PORT & KB, MSSheet 32

PARALLEL PORT/HEADERSheet 33

POWER SEQUENCING

PWR/FNT PNL/SPKR/VBAT

FAN CIRCUITS/HOLE

AUDIO CODEC

AUDIO CODEC JACKS

DUAL RAIL VREG/1.1VSB

NCP5393 CONTROL

NCP5393 PHASE 1, 2, 3

APW7120 1.1V

APW7120 1.8V

LDO FOR 2.5V/1.2V/0.9V

EuP (Energy-using Products)

<Variant Name>

<Variant Name>

<Variant Name>

Wistron Incorpo rated

Wistron Incorpo rated

Wistron Incorpo rated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Title

Title

Title

Cover page

Cover page

Cover page

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

EBOXER

A3

EBOXER

A3

EBOXER

A3

Date: Sheet of

Date: Sheet

Date: Sheet

Hsichih, Taipei

SA

SA

1 45Monday, January 04, 2010

1 45Monday, January 04, 2010

1 45Monday, January 04, 2010

SA

of

of

1394 HEADER

INTERNAL CONN

X2 - SATA

BACK PANEL CONN

X1 - ESATA

PS2/KBRD CONN

POWER

SUPPLY

CONNECTOR

SIO THERM MON.

PEX X16

PEX X1

VT6315N

SPI FLASH

INTEGRATED SATA CONTROLLERS

SIO

ITE8758

VREG

PCI EXPRESSX16

PCI EXPRESSX1

PCI EXPRESSX1

LPC BUS 33MHZ

BLOCK DIAGRAM

AM3 SOCKET 941

HT1/HT3 16X16

NFORCE

MCP61/MCP78

692 BGA

128-BIT 667/800/1066/1333MHZ

HDA

RGB

HDMI

X10 USB2.0

5.1 or 3/2 AUDIO

ALC888S/662

DDR3 DIMM0

DDR3 DIMM1

RGB

HDMI

BACK PANEL CONN

USB PORTS 0-1

BACK PANEL CONN

USB PORTS 2-3

FRONT PANEL HDR

USB PORTS 4-5

USB PORTS 6-7

USB PORTS 8-9

USBF1

USBF2

USBF3

PAGE

TITLE

01

COVER PAGE

BlOCK DIAGRAM

02

POWER DISTRIBUTION

03

04

CLOCK DIAGRAM

05

RESET MAP

06

GPIO TABLE

07

CPU HT INTERFACE

08

CPU CNTL/STRAPS

09

CPU MEM_A

CPU MEM_B

10

CPU POWER/GND

11

CPU DECOUPLING

12

MEM_DIMM_A0

13

MEM_DIMM_B0

14

MCP61 HT/CLKS

15

16

MCP61 PEX X16

17

MCP61 PEX X1/RGMII/HDMI/DAC

18

MCP61 PCI/LPC

MCP61 SATA/IDE

19

20

MCP61 AUDIO/USB/MISC

21

22

23

24

25

26

27

28

29

USB+RJ45 CONNECOTR/FRONT

LAN RTL8211CL/8201EL

30

31

SIO IT8755E/ITE8757/DEBUG

SERIAL PORT & KB, MS

32

PARALLEL PORT/HEADER

33

34

PWR/FNT PNL/SPKR/VBAT

35

FAN CIRCUITS/HOLE

36

AUDIO CODEC

37

AUDIO CODEC JACKS

38

Quantity

(TOTAL/EMPTY)

30(31/1)

MII/RGMII

Realtek

8211CL/8201EL

GIGA and 10/100 LAN

EBOXER

EBOXER

EBOXER

Total: 932

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

2 45Monday, Ja nuary 04, 2010

2 45Monday, Ja nuary 04, 2010

2 45Monday, Ja nuary 04, 2010

<Variant Na me>

<Variant Na me>

<Variant Na me>

Title

Title

Title

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Size Docu ment Number Rev

Size Docu ment Number Rev

Size Docu ment Number Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

SA

SA

SA

5

4

3

2

1

MCP61 Power Delivery Architecture

CPU(AM3)

D D

5VSB

+/-5%

5V

+/-5%

ATX P SU

3.3V

+/-5%

12V

+/-5%

-12V

+/-5%

CPU

PWR

12V

+/-5%

VRD 11 Switching

REGUALTOR

ON5939+4*ON5359

APW7120

VCC_MEM

REGULATOR

VCORE (S0, S1)

V_1P5(S0, S1,S3)

APL5531KAC MEM_VTT

V_1P5

C C

V_3P3_DUAL

APL5912 CPU_HT

REGULATOR

APL5312 CPU_VDDA

REGULATOR

APW7120 MCP78_CORE

REGULATOR

APL5315 V_1P1_DUAL

REGULATOR

V_1P2 (S0, S1)

V_2P5 (S0, S1)

V_1P2 (S0,S1)

V_1P2_DUAL (S0,S1,S3,S4,S5)

VCC3_3

V_3P3_DUAL

VCC3_3

3.3VSB REGULATOR

APL1085

V_3SB

RTC

TDP 89W

CPU VORE 80A

CPU NB 20A

CPU HT 1.4A

CPU VDDA 250mAV_5_DIMM

1.5V

VDD/VDDQ 8.6A

1.2V

VTT 1.75A

Nvdia MCP61

1.2V

Core 7.7A

1.2V

HT 2.3A

1.2V

PEA 1.7A

1.2V

OTHER 1.4A

3.3V

Vcc3_3 372mA

3.3V

VccSus3_3 51mA

3.3V

OTHER TBD

VCCRTC 6uA

3.3VDUAL NPMOS

CEM2939A

5VDUAL NMOS.PM OS

B B

PCIE x1

A A

12V

3.3VSB

5

5VDUAL NPMOS

CEM2939A

5VDUAL NPMOS

CEM2939A

3.0A

0.5A

0.375A

X16 PC IE

3.3V3.3V

12V

3.3VSB

3.0A

5.5A

0.375A

4

V_5_USB_R

V_5_USB_F

VT6315N 1394

3.3V 0.3A

V_3P3DUAL

5VAA LDO

REGULATOR

MC78M05

V_5_CODEC

HD AUDI O CODEC

+3.3V 40mA

+5V 52mA

V_5

SUPER I/O

V_5SBVCC5_DIMM

VCC5_USB_R

USB X 4 REAR

VDD

5VDual

2.0A

2XPS/ 2

5VDual

0.6A

VCC5_USB_F

USB X 6 FRONT

VDD

5VDual

3.0A

ETHERNET

3.3V TBD

1.8V TBD

1.5V TBD

3

2

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

POWER DISTRIBUTION

POWER DISTRIBUTION

POWER DISTRIBUTION

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

EBOXER

Custom

EBOXER

Custom

EBOXER

Custom

Date: Sheet

Date: Sheet of

Date: Sheet of

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

3 45Monday, January 04, 2010

3 45Monday, January 04, 2010

3 45Monday, January 04, 2010

1

of

SA

SA

SA

AM2R2 SOCKET 940

HT_CPU_TXCLK0

HT_CPU_TXCLK0*

HT_CPU_RXCLK0

HT_CPU_RXCLK0*

HT_CPU_TXCLK1

HT_CPU_TXCLK1*

HT_CPU_RXCLK1

HT_CPU_RXCLK1*

CPUCLK_IN*

CPUCLK_IN

MEMORY_A0_CLK[2:0]

MEMORY_A0_CLK[2:0]*

MEMORY_B0_CLK[2:0]

MEMORY_B0_CLK[2:0]*

MEMORY_A1_CLK[2:0]

MEMORY_A1_CLK[2:0]*

MEMORY_B1_CLK[2:0]

MEMORY_B1_CLK[2:0]*

CHANNEL A0 0-63

CHANNEL B0 64-127

DIMM 0

DIMM 1

25 MHZ

CLKOUT_200MHZ

CLKOUT_200MHZ*

HT_CPU_RXCLK1*

HT_CPU_RXCLK1

HT_CPU_TXCLK1*

HT_CPU_TXCLK1

HT_CPU_RXCLK0*

HT_CPU_RXCLK0

HT_CPU_TXCLK0*

HT_CPU_TXCLK0

TV_XTAL

RTC_XTAL32.0 KHZ

XTAL_IN

XTAL_OUT

MCP61

PE_REFCLK

PE_REFCLK*

PEB_REFCLK

PEB_REFCLK*

PEC_REFCLK

PEC_REFCLK*

BUF_SIO

LPC_CLK0

PCI_CLK0

PCI_CLK1

PCI_CLK2

PCI_CLK3

PCI_CLK4

PCI_CLKIN

LPC_CLK1

HDA_BITCLK

HDMI/DVI_CLK

HDMI/DVI_CLK*

RGMII_TXCLK

RGMII_RXCLK

BUF_25MHZ

24MHZ

HDA

CODEC

LAN

PHY

SIO

25 MHZ

PE0 X16

PE1 X1

VT6315N

HDMI

24.576 MHZ

DEBUG

HEADER

<Variant Name>

<Variant Name>

<Variant Name>

Wistron Incorpo rated

Wistron Incorpo rated

Wistron Incorpo rated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Title

Title

Title

CLOCK DIAGRAM

CLOCK DIAGRAM

CLOCK DIAGRAM

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

EBOXER

A3

EBOXER

A3

EBOXER

A3

Date: Sheet of

Date: Sheet

Date: Sheet

Hsichih, Taipei

4 45Monday, January 04, 2010

4 45Monday, January 04, 2010

4 45Monday, January 04, 2010

of

of

SA

SA

SA

RESET MAP

AM2R2 SOCKET 940

CPU PWRGD

CPU RST*

PWR CONN

PWR GOOD

PWRGD SB

CIRCUIT

PWR SWTCH

PS ON

PEX0 X16

PEX1 X1

VT6315N

PSIN*

PSON*

SIO

PSOUT*

SUSB*

PWRBTN*

SLP_S3*

POWER_GOOD

PWRGD_SB

PE_RESET*

PWR BUTTON

SLP S3*

PWRGD

PWRGD_SB

MIIRESET*

MCP61

HT MCP RST*

HT MCP PWRGD

PCI RST0*

PCI RST1*

PCI RST2*

PCI RST3*

LPC_RST*

HDA_RESET*

HT_MCP_RST*

HT_MCP_PWRGD

LPCRST_DEBUG

LPCRST_SIO*

SIO

DEBUG HDR

LAN_PHY

RESET*

AUDIO_PHY

RESET*

<Variant Name>

<Variant Name>

<Variant Name>

Wistron Incorpo rated

Wistron Incorpo rated

Wistron Incorpo rated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Title

Title

Title

RESET MAP

RESET MAP

RESET MAP

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

EBOXER

A3

EBOXER

A3

EBOXER

A3

Date: Sheet of

Date: Sheet

Date: Sheet

Hsichih, Taipei

5 45Monday, January 04, 2010

5 45Monday, January 04, 2010

5 45Monday, January 04, 2010

of

of

SA

SA

SA

SIO GPIO TABLE

ATTRIBUTE

PIN NAME

FAN_TAC2/ GP52 5

6 FAN_CTL2/ GP51

11 PECI_RQT/ GP14

12 PWROK1/ GP13

PCIRST1#/ GP12

13

PCIRST2#/ GP11

14

KRST#/ GP62

24

PWRON#/ GP44

33

34

PME#/ GP54

35

PANSWH#/ GP43

36

PSON#/ GP42

37

SUSC#/ GP53

38

3VSBSW#/ GP40

39

KDAT/ GP61

40

KCLK/ GP60

41

MDAT/ GP57

MCLK/ GP56

42

PCIRST3#/ GP10

43

RSMRST#/ GP55

44

POWER

DI/ DIOD8 VCC

DOD8/ DIOD8 VCC

PECI/ DIOD8 VCC

DOD8/ DIOD8 VCC

DOD8/ DIOD8 VCC

DOD8/ DIOD8 VCC

DO16/ DIOD16 VCC

DOD8/ DIOD8 VCCH

DOD8/ DIOD8 VCCH

DI/ DIOD8 VCCH

DOD8/ DIOD8 VCCH

DI/ DIOD8 VCCH

DO8/ DIOD8 VCCH

DIOD24/ DIOD24 VCCH

DIOD24/ DIOD24 VCCH

MDAT/ GP57 VCCH

FAN_TAC2/ GP52

FAN_TAC2/ GP52

FAN_TAC2/ GP52

JUMPER SETTING

FUNCTION

BOARD_ID1

MCP61 GPIO TABLE

PIN NAME

THERMTRIP*/GPIO58

PROCHOT*/GPIO20

MII0_RXER/GPIO36

MII_COL/GPIO13/MI2C_DATA

MII_CRS/GPIO14/MI2C_CLK

RGMII/MII0_INTR/GPIO35

RGMII/MII0_PWRDWN/GPIO37

MII_RESET*

DDC_CLK0/3

DDC_DATA0/3

PCI_REQ2*/GPIO40.RS232_DSR*

PCI_REQ3*/GPIO38/RS232_CTS*

PCI_REQ4*/GPIO52/RS232_SIN*

PCI_GNT2*/GPIO41/RS232_DTR*

PCI_GNT3*/GPIO39/RS232_RTS*

PCI_GNT4*/GPIO53/RS232_SOUT*

PCI_PERR*/GPIO43/RS232_DCD*

PCI_PME*/GPIO30

LPC_PWRDWN*/GPIO54/EXT_NMI*

LPC_DRQ0*/GPIO50

LPC_DRQ1*/GPIO15/FANRPM1

CABLE_DET_P/GPIO63

SATE_LED*/GPIO57

HDA_SDATA_OUT0/GPIO45

HDA_SDATA_IN0/GPIO22

HDA_SDATA_IN1/GPIO23/MGPIO0

HDA_SDATA_IN2/GPIO24

HDA_SYNC/GPIO44

GPIO_1/PWRDN_OK/SPI_CS1

GPIO_2/NMI*/PS2_CLK0*

GPIO_3/SMI*/PS2_DATA0*

GPIO_4/SCI_INTR/PS2_CLK1*

GPIO_5/INIT*/PS2_DATA1*

GPIO_6/FERR*/SYS_FERR*/IGPU_GPIO_6*

GPIO_7/NFERR*/SYS_PERR*/IGPU_GPIO_7*

GPIO_8/SPI_DI

GPIO_9/SPI_DO

GPIO_10/SPI_CS

GPIO_11/SPI_CLK

USB_OC0*/GPIO25

USB_OC1*/GPIO26

USB_OC2*/GPIO27

USB_OC3*/GPIO28/MGPIO_1

USB_OC4*/GPIO29

A20GATE/FANCTL3/GPIO55

EXT_SMI*/GPIO32

RI*/GPIO33

SIO_PME*/GPIO31/SPI_CS2

KBRDRSTIN*/FANRPM3/GPIO56

SUS_CLK/GPIO34

THERM*/GPIO59

FANRPM0/GPIO60

FANCTL0/GPIO61

FANCTL1/GPIO62

THERM_SIC/GPIO48

THERM_SID0/GPIO49

THERM_ALERT*/PWR_LED/GPIO47

PE_WAKE*/GPIO21

FUNCTION

CPU_THERMTRIP*

CPU_PROCHOT*

--

--

-RGMII_INTR*

RGMII_PWRDWN

RGMII_RESET*

VGA/HDMI DDC_CLK

VGA/HDMI DDC_DATA

--

--

--

--

--

--

--

--

-LPC_DRQ0*

--

-SATA_LED*

HDA_SDATA_OUT

HDA_SDATA_IN0

--

-HDA_SYNC

--

--

-DEBUG_INTR

--

--

-SPI_DI

SPI_DO

SPI_CS

SPI_CLK

USB_OC_10*

USB_OC_32*

USB_OC_54*

USB_OC_76*

USB_OC_98*

A20GATE

EXT_SMI*

SER_RI*

IO_PME*

SIO_KBRST*

-CPU_THERM*

--

--

-THERM_SIC

THERM_SID

CPU_THERM_ALERT*

PE_WAKE*

Location

JBIOS1

* DEFAULT SETTING

CMOS

NORMAL*

2-3FUNCTION 1-2

CLEAR

B:For MCP78

E:For MCP61

L: without spdif

G:GIGA LAN

M:10/100 LAN

U:EuP

N:Non-EuP

<Variant Name>

<Variant Name>

<Variant Name>

Wistron Incorpo rated

Wistron Incorpo rated

Wistron Incorpo rated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Title

Title

Title

GPIO TABLE

GPIO TABLE

GPIO TABLE

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

EBOXER

A3

EBOXER

A3

EBOXER

A3

Date: Sheet of

Date: Sheet

Date: Sheet

Hsichih, Taipei

6 45Monday, January 04, 2010

6 45Monday, January 04, 2010

6 45Monday, January 04, 2010

of

of

SA

SA

SA

HT BUS

HT_CPU_UPCLK_P1

HT_CPU_UPCLK_N1

HT_CPU_UPCLK_P0

HT_CPU_UPCLK_N0

HT_CPU_UPCNTL_P1

HT_CPU_UPCNTL_N1

HT_CPU_UPCNTL_P0

HT_CPU_UPCLK_P[1..0]15

HT_CPU_UPCLK_N[1..0]15

HT_CPU_UPCNTL_P[1..0]15

HT_CPU_UPCNTL_N[1..0]15

HT_CPU_UP_P[15..0]15

HT_CPU_UP_N[15..0]15

HT_CPU_DWNCLK_P[1..0]15

HT_CPU_DWNCLK_N[1..0]15

HT_CPU_DWNCNTL_P[1..0]15

HT_CPU_DWNCNTL_N[1..0]15

HT_CPU_DWN_P[15..0]15

HT_CPU_DWN_N[15..0]15

HT_CPU_UPCNTL_N0

HT_CPU_UP_P15

HT_CPU_UP_N15

HT_CPU_UP_P14

HT_CPU_UP_N14

HT_CPU_UP_P13

HT_CPU_UP_N13

HT_CPU_UP_P12

HT_CPU_UP_N12

HT_CPU_UP_P11

HT_CPU_UP_N11

HT_CPU_UP_P10

HT_CPU_UP_N10

HT_CPU_UP_P9

HT_CPU_UP_N9

HT_CPU_UP_P8

HT_CPU_UP_N8

HT_CPU_UP_P7

HT_CPU_UP_N7

HT_CPU_UP_P6

HT_CPU_UP_N6

HT_CPU_UP_P5

HT_CPU_UP_N5

HT_CPU_UP_P4

HT_CPU_UP_N4

HT_CPU_UP_P3

HT_CPU_UP_N3

HT_CPU_UP_P2

HT_CPU_UP_N2

HT_CPU_UP_P1

HT_CPU_UP_N1

HT_CPU_UP_P0

HT_CPU_UP_N0

HT_CPU_DWNCLK_P1

HT_CPU_DWNCLK_N1

HT_CPU_DWNCLK_P0

HT_CPU_DWNCLK_N0

HT_CPU_DWNCNTL_P1

HT_CPU_DWNCNTL_N1

HT_CPU_DWNCNTL_P0

HT_CPU_DWNCNTL_N0

HT_CPU_DWN_P15

HT_CPU_DWN_N15

HT_CPU_DWN_P14

HT_CPU_DWN_N14

HT_CPU_DWN_P13

HT_CPU_DWN_N13

HT_CPU_DWN_P12

HT_CPU_DWN_N12

HT_CPU_DWN_P11

HT_CPU_DWN_N11

HT_CPU_DWN_P10

HT_CPU_DWN_N10

HT_CPU_DWN_P9

HT_CPU_DWN_N9

HT_CPU_DWN_P8

HT_CPU_DWN_N8

HT_CPU_DWN_P7

HT_CPU_DWN_N7

HT_CPU_DWN_P6

HT_CPU_DWN_N6

HT_CPU_DWN_P5

HT_CPU_DWN_N5

HT_CPU_DWN_P4

HT_CPU_DWN_N4

HT_CPU_DWN_P3

HT_CPU_DWN_N3

HT_CPU_DWN_P2

HT_CPU_DWN_N2

HT_CPU_DWN_P1

HT_CPU_DWN_N1

HT_CPU_DWN_P0

HT_CPU_DWN_N0

HT_CPU_UPCLK_P1

HT_CPU_UPCLK_N1

HT_CPU_UPCLK_P0

HT_CPU_UPCLK_N0

HT_CPU_UPCNTL_P1

HT_CPU_UPCNTL_N1

HT_CPU_UPCNTL_P0

HT_CPU_UPCNTL_N0

HT_CPU_UP_P15

HT_CPU_UP_N15

HT_CPU_UP_P14

HT_CPU_UP_N14

HT_CPU_UP_P13

HT_CPU_UP_N13

HT_CPU_UP_P12

HT_CPU_UP_N12

HT_CPU_UP_P11

HT_CPU_UP_N11

HT_CPU_UP_P10

HT_CPU_UP_N10

HT_CPU_UP_P9

HT_CPU_UP_N9

HT_CPU_UP_P8

HT_CPU_UP_N8

HT_CPU_UP_P7

HT_CPU_UP_N7

HT_CPU_UP_P6

HT_CPU_UP_N6

HT_CPU_UP_P5

HT_CPU_UP_N5

HT_CPU_UP_P4

HT_CPU_UP_N4

HT_CPU_UP_P3

HT_CPU_UP_N3

HT_CPU_UP_P2

HT_CPU_UP_N2

HT_CPU_UP_P1

HT_CPU_UP_N1

HT_CPU_UP_P0

HT_CPU_UP_N0

NEAR CPU

HT_CPU_UPCNTL_P1

HT_CPU_UPCNTL_N1

R556

R556

51R2F-2-GP

51R2F-2-GP

R557

R557

51R2F-2-GP

51R2F-2-GP

N6

P6

N3

N2

V4

V5

U1

V1

U6

V6

T4

T5

R6

T6

P4

P5

M4

M5

L6

M6

K4

K5

J6

K6

U3

U2

R1

T1

R3

R2

N1

P1

L1

M1

L3

L2

J1

K1

J3

J2

V_1P2

U1A

U1A

OPTER

OPTER

(62.10055.281)

(62.10055.281)

12

12

L0_CLKIN_H1

L0_CLKIN_L1

L0_CLKIN_H0

L0_CLKIN_L0

L0_CTLIN_H1

L0_CTLIN_L1

L0_CTLIN_H0

L0_CTLIN_L0

L0_CADIN_H15

L0_CADIN_L15

L0_CADIN_H14

L0_CADIN_L14

L0_CADIN_H13

L0_CADIN_L13

L0_CADIN_H12

L0_CADIN_L12

L0_CADIN_H11

L0_CADIN_L11

L0_CADIN_H10

L0_CADIN_L10

L0_CADIN_H9

L0_CADIN_L9

L0_CADIN_H8

L0_CADIN_L8

L0_CADIN_H7

L0_CADIN_L7

L0_CADIN_H6

L0_CADIN_L6

L0_CADIN_H5

L0_CADIN_L5

L0_CADIN_H4

L0_CADIN_L4

L0_CADIN_H3

L0_CADIN_L3

L0_CADIN_H2

L0_CADIN_L2

L0_CADIN_H1

L0_CADIN_L1

L0_CADIN_H0

L0_CADIN_L0

(E)

(E)

(E)

(E)

L0_CLKOUT_H1

L0_CLKOUT_L1

L0_CLKOUT_H0

L0_CLKOUT_L0

L0_CTLOUT_H1

L0_CTLOUT_L1

L0_CTLOUT_H0

L0_CTLOUT_L0

OPTERON

OPTERON

L0_CADOUT_H15

L0_CADOUT_L15

L0_CADOUT_H14

L0_CADOUT_L14

L0_CADOUT_H13

L0_CADOUT_L13

L0_CADOUT_H12

L0_CADOUT_L12

L0_CADOUT_H11

L0_CADOUT_L11

L0_CADOUT_H10

L0_CADOUT_L10

L0_CADOUT_H9

L0_CADOUT_L9

L0_CADOUT_H8

L0_CADOUT_L8

L0_CADOUT_H7

L0_CADOUT_L7

L0_CADOUT_H6

L0_CADOUT_L6

L0_CADOUT_H5

L0_CADOUT_L5

L0_CADOUT_H4

L0_CADOUT_L4

L0_CADOUT_H3

L0_CADOUT_L3

HT LINK

HT LINK

L0_CADOUT_H2

L0_CADOUT_L2

L0_CADOUT_H1

L0_CADOUT_L1

L0_CADOUT_H0

L0_CADOUT_L0

1 OF 8

1 OF 8

AD5

AD4

AD1

AC1

Y6

W6

W2

W3

Y5

Y4

AB6

AA6

AB5

AB4

AD6

AC6

AF6

AE6

AF5

AF4

AH6

AG6

AH5

AH4

Y1

W1

AA2

AA3

AB1

AA1

AC2

AC3

AE2

AE3

AF1

AE1

AG2

AG3

AH1

AG1

E for MCP61 05/07

B for MCP78 05/07

NEAR CPU

HT_CPU_DWNCLK_P1

HT_CPU_DWNCLK_N1

HT_CPU_DWNCLK_P0

HT_CPU_DWNCLK_N0

HT_CPU_DWNCNTL_P1

HT_CPU_DWNCNTL_N1

HT_CPU_DWNCNTL_P0

HT_CPU_DWNCNTL_N0

HT_CPU_DWN_P15

HT_CPU_DWN_N15

HT_CPU_DWN_P14

HT_CPU_DWN_N14

HT_CPU_DWN_P13

HT_CPU_DWN_N13

HT_CPU_DWN_P12

HT_CPU_DWN_N12

HT_CPU_DWN_P11

HT_CPU_DWN_N11

HT_CPU_DWN_P10

HT_CPU_DWN_N10

HT_CPU_DWN_P9

HT_CPU_DWN_N9

HT_CPU_DWN_P8

HT_CPU_DWN_N8

HT_CPU_DWN_P7

HT_CPU_DWN_N7

HT_CPU_DWN_P6

HT_CPU_DWN_N6

HT_CPU_DWN_P5

HT_CPU_DWN_N5

HT_CPU_DWN_P4

HT_CPU_DWN_N4

HT_CPU_DWN_P3

HT_CPU_DWN_N3

HT_CPU_DWN_P2

HT_CPU_DWN_N2

HT_CPU_DWN_P1

HT_CPU_DWN_N1

HT_CPU_DWN_P0

HT_CPU_DWN_N0

HT_CPU_DWNCLK_P[1..0] 15

HT_CPU_DWNCLK_N[1..0] 15

HT_CPU_DWNCNTL_P[1..0] 15

HT_CPU_DWNCNTL_N[1..0] 15

HT_CPU_DWN_P[15..0] 15

HT_CPU_DWN_N[15..0] 15

<Variant Name>

<Variant Name>

<Variant Name>

Wistron Incorpo rated

Wistron Incorpo rated

Wistron Incorpo rated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Title

Title

Title

CPU HT INTERFACE

CPU HT INTERFACE

CPU HT INTERFACE

Size Document Number Rev

Size Document Number Rev

Size Document Number Rev

EBOXER

A3

EBOXER

A3

EBOXER

A3

Date: Sheet of

Date: Sheet

Date: Sheet

Hsichih, Taipei

7 45Monday, January 04, 2010

7 45Monday, January 04, 2010

7 45Monday, January 04, 2010

of

of

SA

SA

SA

CPU control signals

CPU_CLK_P15

CPU_CLK_N15

HT_CPU_PWRGD15,40

HT_CPU_STOP*15

HT_CPU_RST*15

CPU_THERM_ALERT*15

CPU_CORE_FB40

CPU_CORE_FB*40

CPU_VID1/SEL

CPU_VID5

CPU_VID4

CPU_VID3/SVC

CPU_VID2/SVD

CPU_VID1/SEL

CPU_VID0

CPU_THERMDC

CPU_THERMDA

CPU_THERMTRIP*

CPU_PROCHOT*

CPU_NB_FB_P

CPU_NB_FB_N

CPU_PSI*

CPU_CLK_P

CPU_CLK_N

HT_CPU_PWRGD

HT_CPU_STOP*

HT_CPU_RST*

CPU_THERM_ALERT*

CPU_CORE_FB

CPU_CORE_FB*

CPU_VID1/SEL 40

CPU_VID5 40

CPU_VID4 40

CPU_VID3/SVC 40

CPU_VID2/SVD 40

CPU_VID1/SEL 40

CPU_VID0 40

CPU_THERMDC 31

CPU_THERMDA 31

CPU_THERMTRIP* 15

CPU_PROCHOT* 15

CPU_NB_FB_P 40

CPU_NB_FB_N 40

CPU_PSI* 40

ROUTE AS A 15MIL TRACE

C165

C165

SCD1U16V2ZY-2GP

SCD1U16V2ZY-2GP

V_2P5

0.5A,0.25ohm,300ohm

L53

L53

1 2

FCM1608KF G-301T05 -GP

FCM1608KF G-301T05 -GP

LAYOUT: PLACE 169 OHM WITHIN 0.5INCH OF CPU

ROUTE AS 100 ohm DIFF

V_1P5

12

12

12

C540

C540

1 2

SC1KP50V2KX-1GP

SC1KP50V2KX-1GP

LAYOUT: 5MIL TRACE 10 MIL SPACE

LAYOUT: PLACE WITHIN 1 INCH OF CPU

C377

C377

1 2

SC4D7U10V5ZY-3GP

SC4D7U10V5ZY-3GP

CPU_CLK_P15

CPU_CLK_N15

R201

R201

15R2F-2 -GP

15R2F-2 -GP

R202

R202

15R2F-2 -GP

15R2F-2 -GP

+2.5V_CPU_VDDA

12

C374

C374

SCD22U16V2ZY-1GP

SCD22U16V2ZY-1GP

1 2

169R2F- GP

169R2F- GP

1 2

CPU_THERM_ALERT*15

V_1P5

12

R464

R464

39D2R2F -L-GP

39D2R2F -L-GP

12

R180

R180

39D2R2F -L-GP

39D2R2F -L-GP

C365

C365

SC3900P50 V2KX-2GP

SC3900P50 V2KX-2GP

R192

R192

C168

C168

SC3900P50 V2KX-2GP

SC3900P50 V2KX-2GP

CPU_CORE_FB40

CPU_CORE_FB*40

12

C539

C539

SC3300P50 V2KX-1GP

SC3300P50 V2KX-1GP

12

V_1P5

1KR2J-1-GP

1KR2J-1-GP

ROUTE AS DIFF PAIR

10/5/10 10

V_1P5

R162

R162

510R2J-1-G P

510R2J-1-G P

1 2

R164

R164

510R2J-1-G P

510R2J-1-G P

1 2

HDT1

HDT1

1

3

5

7

9

11

13

15

17

19

21

23

SMC-CONN26A-FP

SMC-CONN26A-FP

(R)

(R)

CLKIN

CLKIN*

THERM_SIC

THERM_SID

R461

R461

12

CPU_TEST25

CPU_TEST25*

2

4

6

8

10

12

14

16

18

20

22

24

26

HT_CPU_PWRGD15,40

HT_CPU_STOP*15

HT_CPU_RST*15

V_1P5

V_1P5

300R2J-4-G P

300R2J-4-G P

1 2

R468

R468

R469

R469

300R2J-4-G P

300R2J-4-G P

1 2

1 2

TP99TP-2 TP9 9TP-2

TP29TP-2 TP2 9TP-2

TP25TP-2 TP2 5TP-2

TP27TP-2 TP2 7TP-2

TP26TP-2 TP2 6TP-2

TP23TP-2 TP2 3TP-2

TP35TP-2 TP3 5TP-2

TP95TP-2 TP9 5TP-2

TP93TP-2 TP9 3TP-2

TP92TP-2 TP9 2TP-2

TP94TP-2 TP9 4TP-2

TP22TP-2 TP2 2TP-2

TP21TP-2 TP2 1TP-2

TP100TP- 2 TP100TP- 2

12

12

R179

R179

300R2J-4-G P

300R2J-4-G P

CPU_PRSNT*

R465

R465

10KR2J-3-GP

10KR2J-3-GP

1

1

1

1

1

1

1

1

1

TP_TEST1 7

1

TP_TEST1 6

1

TP_TEST1 5

1

TP_TEST1 4

1

TP_TEST1 2

1

V_1P5

12

R187

R187

R184

R184

300R2J-4-G P

300R2J-4-G P

300R2J-4-G P

300R2J-4-G P

TP_CPU_TDI

TP_CPU_TRST*

TP_CPU_TCK

TP_CPU_TMS

TP_CPU_DBREQ*

TP_M_VDDIO_PWRGD

TP_MEM_VTT_SENSE

MEM_CPU_VREF

CPU_MEMZN

CPU_MEMZP

TEST19

TEST18

AL10

AJ10

AH10

AH11

AJ11

C10

D10

A8

B8

C9

D8

C7

AL3

AL6

AK6

AK4

AL4

AL9

A5

G2

G1

F3

E12

F12

A10

B10

F10

E9

AJ7

F6

D6

E7

F8

C5

AH9

E5

AJ5

AH7

AJ6

C18

C20

F2

G24

G25

H25

L25

L26

U1D

U1D

VDDA

VDDA

CLKIN_H

CLKIN_L

PWROK

LDTSTOP_ L

RESET_L

CPU_PRESENT_L

SIC

SID

SA0

ALERT_L

TDI

TRST_L

TCK

TMS

DBREQ_L

VDD_FB_H

VDD_FB_L

M_VDDIO_PWRGD

VDDR_SENSE

M_VREF

M_ZN

M_ZP

TEST25_H

TEST25_L

TEST19

TEST18

TEST13

TEST9

TEST17

TEST16

TEST15

TEST14

TEST12

TEST7

TEST6

TEST3

TEST2

RSVD#C18

RSVD#C20

RSVD#F2

RSVD#G24

RSVD#G25

RSVD#H25

RSVD#L25

RSVD#L26

OPTER

OPTER

(62.10055.281)

(62.10055.281)

MISC.

MISC.

OPTERON

OPTERON

INT. MISC.

INT. MISC.

4 OF 8

4 OF 8

CORE_TYPE

SVC/VID3

SVD/VID2

PVIEN/VID1

THERMDC

THERMDA

THERMTRIP_L

PROCHOT_L

DBRDY

VDDIO_FB_H

VDDIO_FB_L

VDDNB_FB_H

VDDNB_FB_L

PSI_L

HTREF1

HTREF0

TEST29_H

TEST29_L

TEST24

TEST23

TEST22

TEST21

TEST20

TEST28_H

TEST28_L

TEST27

TEST26

TEST10

TEST8

RSVD#L30

RSVD#L31

RSVD#AD25

RSVD#AE24

RSVD#AE25

RSVD#AJ18

RSVD#AJ20

RSVD#AK3

CORE_TYPE

G5

D2

VID5

D1

VID4

C1

E3

E2

E1

VID0

AG9

AG8

AK7

AL7

TP_CPU_TDO

AK10

TDO

TP_CPU_DBRDY

B6

TP_CPU_VDDIOFB

AK11

TP_CPU_VDDIOFB*

AL11

G4

G3

F1

HT_REF1

V8

HT_REF0

V7

C11

D11

AK8

AH8

AJ9

AL8

AJ8

J10

H9

AK9

AK5

G7

D4

L30

L31

AD25

AE24

AE25

AJ18

AJ20

AK3

FBCLKOUT

FBCLKOUT*

Layout: Route as 80 ohms diff impedance.

Keep trace to resistor < 1" from CPU pins

TP_TEST2 4

TP_TEST2 3

TP_TEST2 2

CPU_TEST21

TP_TEST2 0

1

1

TP_TEST2 8_N

1

TP_TEST2 7

1

1

1

1

1

1

1

1

1

TP32 TP- 2TP32 TP-2

TP34 TP- 2TP34 TP-2

TP33 TP- 2TP33 TP-2

CPU_THERMDC 31

CPU_THERMDA 31

TP98 T P-2TP98 T P-2

TP24 TP- 2TP24 TP-2

TP-2

TP-2

TP97

TP97

TP96 TP- 2TP96 TP-2

CPU_NB_FB_P 40

CPU_NB_FB_N 40

CPU_PSI* 40

TP28 TP- 2TP28 TP-2

TP31 TP- 2TP31 TP-2

TP36 TP- 2TP36 TP-2

TP30 TP- 2TP30 TP-2

TP37 TP- 2TP37 TP-2

V_1P5

R462

R462

300R2J-4-G P

300R2J-4-G P

R167

R167

1 2

1 2

1 2

V_1P5

1KR2J-1-GP

1KR2J-1-GP

R191

R191

300R2J-4-G P

300R2J-4-G P

R173

R173

80D6R2F -L-GP

80D6R2F -L-GP

<Variant Name>

<Variant Name>

<Variant Name>

Title

Title

Title

Size Docu ment Number Rev

Size Docu ment Number Rev

Size Docu ment Number Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet of

CPU_VID1/SEL 40

FBCLKOUT

FBCLKOUT*TP_TEST2 8_P

CPU CNTL/STRAPS

CPU CNTL/STRAPS

CPU CNTL/STRAPS

EBOXER

EBOXER

EBOXER

1 2

V_1P2

12

R466

R466

44D2R2F -GP

44D2R2F -GP

PLACE WITHIN 1 INCH

5MIL TRACE 10MIL SPACE

R467

R467

44D2R2F -GP

44D2R2F -GP

1 2

1

TP17 TP- 2TP17 TP-2

1

TP16 TP- 2TP16 TP-2

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

8 45Monday, Janua ry 04, 201 0

8 45Monday, Janua ry 04, 201 0

8 45Monday, Janua ry 04, 201 0

of

of

V_1P5

1 2

R463

R463

300R2J-4-G P

300R2J-4-G P

SA

SA

SA

CPU_VID5 40

CPU_VID4 40

CPU_VID3/SVC 40

CPU_VID2/SVD 40

CPU_VID1/SEL 40

CPU_VID0 40

CPU_THERMTRIP* 15

CPU_PROCHOT* 15

Memory CHA

MEM_A_CLK5

MEM_A_CLK5 *

MEM_A_CLK413

MEM_A_CLK4 *13

MEM_A_CLK3

MEM_A_CLK3 *

MEM_A_CLK213

MEM_A_CLK2 *13

MEM_A_BA[2..0]13

MEM_A_ADD[15 ..0]13

MEM_A_DQS[7..0 ]13

MEM_A_DQS*[7 ..0]13

MEM_A_DM[7..0]13

MEM_A_DATA63

MEM_A_DATA62

MEM_A_DATA61

MEM_A_DATA60

MEM_A_DATA59

MEM_A_DATA58

MEM_A_DATA57

MEM_A_DATA56

MEM_A_DATA55

MEM_A_DATA54

MEM_A_DATA53

MEM_A_DATA52

MEM_A_DATA51

MEM_A_DATA50

MEM_A_DATA49

MEM_A_DATA48

MEM_A_DATA47

MEM_A_DATA46

MEM_A_DATA45

MEM_A_DATA44

MEM_A_DATA43

MEM_A_DATA42

MEM_A_DATA41

MEM_A_DATA40

MEM_A_DATA39

MEM_A_DATA38

MEM_A_DATA37

MEM_A_DATA36

MEM_A_DATA35

MEM_A_DATA34

MEM_A_DATA33

MEM_A_DATA32

MEM_A_DATA31

MEM_A_DATA30

MEM_A_DATA29

MEM_A_DATA28

MEM_A_DATA27

MEM_A_DATA26

MEM_A_DATA25

MEM_A_DATA24

MEM_A_DATA23

MEM_A_DATA22

MEM_A_DATA21

MEM_A_DATA20

MEM_A_DATA19

MEM_A_DATA18

MEM_A_DATA17

MEM_A_DATA16

MEM_A_DATA15

MEM_A_DATA14

MEM_A_DATA13

MEM_A_DATA12

MEM_A_DATA11

MEM_A_DATA10

MEM_A_DATA9

MEM_A_DATA8

MEM_A_DATA7

MEM_A_DATA6

MEM_A_DATA5

MEM_A_DATA4

MEM_A_DATA3

MEM_A_DATA2

MEM_A_DATA1

MEM_A_DATA0

V_1P5 V_1P5

MEM_A0_CS1 *13

MEM_A0_CS0 *13

MEM_A0_ODT113

MEM_A0_ODT013

MEM_A1_CS1 *

MEM_A1_CS0 *

MEM_A1_ODT1

MEM_A1_ODT0

MEM_A_RESET _L13

MEM_A_CAS*13

MEM_A_WE*13

MEM_A_RAS*13

MEM_A1_CKE13

MEM_A0_CKE13

MEM_A_EVNT_L 1 3

MEM_A_BA2

MEM_A_BA1

MEM_A_BA0

MEM_A_ADD15

MEM_A_ADD14

MEM_A_ADD13

MEM_A_ADD12

MEM_A_ADD11

MEM_A_ADD10

MEM_A_ADD9

MEM_A_ADD8

MEM_A_ADD7

MEM_A_ADD6

MEM_A_ADD5

MEM_A_ADD4

MEM_A_ADD3

MEM_A_ADD2

MEM_A_ADD1

MEM_A_ADD0

MEM_A_DQS7

MEM_A_DQS*7

MEM_A_DQS6

MEM_A_DQS*6

MEM_A_DQS5

MEM_A_DQS*5

MEM_A_DQS4

MEM_A_DQS*4

MEM_A_DQS3

MEM_A_DQS*3

MEM_A_DQS2

MEM_A_DQS*2

MEM_A_DQS1

MEM_A_DQS*1

MEM_A_DQS0

MEM_A_DQS*0

MEM_A_DM7

MEM_A_DM6

MEM_A_DM5

MEM_A_DM4

MEM_A_DM3

MEM_A_DM2

MEM_A_DM1

MEM_A_DM0

MEM_A_DATA[63..0] 13

U1B

AG21

AG20

AE20

AE19

AC25

AA24

AE28

AC28

AD27

AA25

AE27

AC27

AB25

AB27

AA26

AA27

AC26

AD15

AE15

AG18

AG19

AG24

AG25

AG27

AG28

AF15

AF19

AH29

U27

U26

V27

W27

W26

W25

U24

V24

G19

H19

G20

G21

E20

N25

Y27

M25

M27

N24

N26

P25

Y25

N27

R24

P27

R25

R26

R27

U25

W24

D29

C29

C25

D25

E19

F19

F15

G15

AJ25

B29

E24

E18

H15

L27

T25

T27

U1B

MA_CLK_H7

MA_CLK_L7

MA_CLK_H6

MA_CLK_L6

MA_CLK_H5

MA_CLK_L5

MA_CLK_H4

MA_CLK_L4

MA_CLK_H3

MA_CLK_L3

MA_CLK_H2

MA_CLK_L2

MA_CLK_H1

MA_CLK_L1

MA_CLK_H0

MA_CLK_L0

MA0_CS_L1

MA0_CS_L0

MA0_ODT1

MA0_ODT0

MA1_CS_L1

MA1_CS_L0

MA1_ODT1

MA1_ODT0

MA_RESET_L

MA_CAS_L

MA_WE_L

MA_RAS_L

MA_BANK2

MA_BANK1

MA_BANK0

MA_CKE1

MA_CKE0

MA_ADD15

MA_ADD14

MA_ADD13

MA_ADD12

MA_ADD11

MA_ADD10

MA_ADD9

MA_ADD8

MA_ADD7

MA_ADD6

MA_ADD5

MA_ADD4

MA_ADD3

MA_ADD2

MA_ADD1

MA_ADD0

MA_DQS_H7

MA_DQS_L7

MA_DQS_H6

MA_DQS_L6

MA_DQS_H5

MA_DQS_L5

MA_DQS_H4

MA_DQS_L4

MA_DQS_H3

MA_DQS_L3

MA_DQS_H2

MA_DQS_L2

MA_DQS_H1

MA_DQS_L1

MA_DQS_H0

MA_DQS_L0

MA_DM7

MA_DM6

MA_DM5

MA_DM4

MA_DM3

MA_DM2

MA_DM1

MA_DM0

OPTER

OPTER

(62.10055.281)

(62.10055.281)

TP_MEM_A_CL K7_P

1

TP68TP-2 TP6 8TP-2

TP_MEM_A_CL K7_N

1

TP64TP-2 TP6 4TP-2

TP_MEM_A_CL K6_P

1

TP56TP-2 TP5 6TP-2

TP_MEM_A_CL K6_N

1

TP52TP-2 TP5 2TP-2

MEM_A_CLK5

MEM_A_CLK5 *

MEM_A_CLK413

MEM_A_CLK4 *13

MEM_A_CLK3

MEM_A_CLK3 *

MEM_A_CLK213

MEM_A_CLK2 *13

MEM_A0_CS1 *13

MEM_A0_CS0 *13

MEM_A0_ODT113

MEM_A0_ODT013

MEM_A1_CS1 *

MEM_A1_CS0 *

MEM_A1_ODT1

MEM_A1_ODT0

MEM_A_RESET _L13

MEM_A_CAS*13

MEM_A_WE*13

MEM_A_BA[2..0]13

MEM_A_ADD[15 ..0]13

MEM_A_DQS[7..0 ]13

MEM_A_DQS*[7 ..0]13

MEM_A_DM[7..0]13

MEM_A_RAS*13

MEM_A1_CKE1 3

MEM_A0_CKE1 3

TP_MEM_A_CL K1_P

1

TP60TP-2 TP6 0TP-2

TP_MEM_A_CL K1_N

1

TP49TP-2 TP4 9TP-2

TP_MEM_A_CL K0_P

1

TP58TP-2 TP5 8TP-2

TP_MEM_A_CL K0_N

1

TP62TP-2 TP6 2TP-2

MEM_A_BA2

MEM_A_BA1

MEM_A_BA0

MEM_A_ADD15

MEM_A_ADD14

MEM_A_ADD13

MEM_A_ADD12

MEM_A_ADD11

MEM_A_ADD10

MEM_A_ADD9

MEM_A_ADD8

MEM_A_ADD7

MEM_A_ADD6

MEM_A_ADD5

MEM_A_ADD4

MEM_A_ADD3

MEM_A_ADD2

MEM_A_ADD1

MEM_A_ADD0

MEM_A_DQS7

MEM_A_DQS*7

MEM_A_DQS6

MEM_A_DQS*6

MEM_A_DQS5

MEM_A_DQS*5

MEM_A_DQS4

MEM_A_DQS*4

MEM_A_DQS3

MEM_A_DQS*3

MEM_A_DQS2

MEM_A_DQS*2

MEM_A_DQS1

MEM_A_DQS*1

MEM_A_DQS0

MEM_A_DQS*0

MEM_A_DM7

MEM_A_DM6

MEM_A_DM5

MEM_A_DM4

MEM_A_DM3

MEM_A_DM2

MEM_A_DM1

MEM_A_DM0

2 OF 8

2 OF 8

MEM_A_DATA63

AE14

MA_DATA63

MA_DATA62

MA_DATA61

MA_DATA60

MA_DATA59

MA_DATA58

MA_DATA57

MA_DATA56

MA_DATA55

MA_DATA54

MA_DATA53

OPTERON

OPTERON

MA_DATA52

MA_DATA51

MA_DATA50

MA_DATA49

MA_DATA48

MA_DATA47

MA_DATA46

MA_DATA45

MA_DATA44

MA_DATA43

MA_DATA42

MA_DATA41

MA_DATA40

MA_DATA39

MA_DATA38

MA_DATA37

MA_DATA36

MA_DATA35

MA_DATA34

MA_DATA33

MA_DATA32

MA_DATA31

MA_DATA30

MA_DATA29

MA_DATA28

MA_DATA27

MA_DATA26

MA_DATA25

MA_DATA24

MA_DATA23

MA_DATA22

MA_DATA21

MA_DATA20

MA_DATA19

MA_DATA18

MA_DATA17

MA_DATA16

MA_DATA15

MA_DATA14

MA_DATA13

MA_DATA12

MA_DATA11

MA_DATA10

MEM CHA

MEM CHA

MA_DATA9

MA_DATA8

MA_DATA7

MA_DATA6

MA_DATA5

MA_DATA4

MA_DATA3

MA_DATA2

MA_DATA1

MA_DATA0

MA_DQS_H8

MA_DQS_L8

MA_DM8

MA_CHECK7

MA_CHECK6

MA_CHECK5

MA_CHECK4

MA_CHECK3

MA_CHECK2

MA_CHECK1

MA_CHECK0

MA_EVENT_L

AG14

AG16

AD17

AD13

AE13

AG15

AE16

AG17

AE18

AD21

AG22

AE17

AF17

AF21

AE21

AF23

AE23

AJ26

AG26

AE22

AG23

AH25

AF25

AJ28

AJ29

AF29

AE26

AJ27

AH27

AG29

AF27

E29

E28

D27

C27

G26

F27

C28

E27

F25

E25

E23

D23

E26

C26

G23

F23

E22

E21

F17

G17

G22

F21

G18

E17

G16

E15

G13

H13

H17

E16

E14

G14

J28

J27

J25

K25

J26

G28

G27

L24

K27

H29

H27

W30

MEM_A_DATA62

MEM_A_DATA61

MEM_A_DATA60

MEM_A_DATA59

MEM_A_DATA58

MEM_A_DATA57

MEM_A_DATA56

MEM_A_DATA55

MEM_A_DATA54

MEM_A_DATA53

MEM_A_DATA52

MEM_A_DATA51

MEM_A_DATA50

MEM_A_DATA49

MEM_A_DATA48

MEM_A_DATA47

MEM_A_DATA46

MEM_A_DATA45

MEM_A_DATA44

MEM_A_DATA43

MEM_A_DATA42

MEM_A_DATA41

MEM_A_DATA40

MEM_A_DATA39

MEM_A_DATA38

MEM_A_DATA37

MEM_A_DATA36

MEM_A_DATA35

MEM_A_DATA34

MEM_A_DATA33

MEM_A_DATA32

MEM_A_DATA31

MEM_A_DATA30

MEM_A_DATA29

MEM_A_DATA28

MEM_A_DATA27

MEM_A_DATA26

MEM_A_DATA25

MEM_A_DATA24

MEM_A_DATA23

MEM_A_DATA22

MEM_A_DATA21

MEM_A_DATA20

MEM_A_DATA19

MEM_A_DATA18

MEM_A_DATA17

MEM_A_DATA16

MEM_A_DATA15

MEM_A_DATA14

MEM_A_DATA13

MEM_A_DATA12

MEM_A_DATA11

MEM_A_DATA10

MEM_A_DATA9

MEM_A_DATA8

MEM_A_DATA7

MEM_A_DATA6

MEM_A_DATA5

MEM_A_DATA4

MEM_A_DATA3

MEM_A_DATA2

MEM_A_DATA1

MEM_A_DATA0

TP_MEM_A_DQS8

TP_MEM_A_DQS*8

TP_MEM_A_DM8

TP_MEM_A_EC C7

TP_MEM_A_EC C6

TP_MEM_A_EC C5

TP_MEM_A_EC C4

TP_MEM_A_EC C3

TP_MEM_A_EC C2

TP_MEM_A_EC C1

TP_MEM_A_EC C0

1 2

1

TP108 TP-2TP108 TP-2

1

TP109 TP-2TP109 TP-2

1

TP67 TP-2TP67 TP-2

1

TP101 TP-2TP101 TP-2

1

TP70 TP-2TP70 TP-2

1

TP103 TP-2TP103 TP-2

1

TP102 TP-2TP102 TP-2

1

TP104 TP-2TP104 TP-2

1

TP105 TP-2TP105 TP-2

1

TP106 TP-2TP106 TP-2

1

TP107 TP-2TP107 TP-2

R471

R471

1KR2 J-1-GP

1KR2 J-1-GP

MEM_A_DATA[63..0] 13

MEM_A_EVNT_L 1 3

V_1P5

<Varian t Name >

<Varian t Name >

<Varian t Name >

Title

Title

Title

CPU MEM_A

CPU MEM_A

CPU MEM_A

Size Doc ume nt Num ber Rev

Size Doc ume nt Num ber Rev

Size Doc ume nt Num ber Rev

EBOXER

A2

EBOXER

A2

EBOXER

A2

Date: Sheet of

Date: Sheet of

Date: Sheet

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

of

9 45Monday, Ja nuary 04, 2 010

9 45Monday, Ja nuary 04, 2 010

9 45Monday, Ja nuary 04, 2 010

SA

SA

SA

Memory CHB

MEM_B_CL K5

MEM_B_CL K5*

MEM_B_CL K414

MEM_B_CL K4*14

MEM_B_CL K3

MEM_B_CL K3*

MEM_B_CL K214

MEM_B_CL K2*14

MEM_B_BA[2..0]14

MEM_B_ADD[1 5..0]14

MEM_B_DQS [7..0]14

MEM_B_DQS *[7..0]14

MEM_B_DM[7..0 ]14

MEM_B0_C S1*14

MEM_B0_C S0*14

MEM_B0_OD T114

MEM_B0_OD T014

MEM_B1_C S1*

MEM_B1_C S0*

MEM_B1_OD T1

MEM_B1_OD T0

MEM_B_RE SET_L14

MEM_B_CAS*14

MEM_B_WE*14

MEM_B_RAS*14

MEM_B1_C KE14

MEM_B0_C KE14

MEM_B_BA2

MEM_B_BA1

MEM_B_BA0

MEM_B_ADD1 5

MEM_B_ADD1 4

MEM_B_ADD1 3

MEM_B_ADD1 2

MEM_B_ADD1 1

MEM_B_ADD1 0

MEM_B_ADD9

MEM_B_ADD8

MEM_B_ADD7

MEM_B_ADD6

MEM_B_ADD5

MEM_B_ADD4

MEM_B_ADD3

MEM_B_ADD2

MEM_B_ADD1

MEM_B_ADD0

MEM_B_DQS 7

MEM_B_DQS *7

MEM_B_DQS 6

MEM_B_DQS *6

MEM_B_DQS 5

MEM_B_DQS *5

MEM_B_DQS 4

MEM_B_DQS *4

MEM_B_DQS 3

MEM_B_DQS *3

MEM_B_DQS 2

MEM_B_DQS *2

MEM_B_DQS 1

MEM_B_DQS *1

MEM_B_DQS 0

MEM_B_DQS *0

MEM_B_DM7

MEM_B_DM6

MEM_B_DM5

MEM_B_DM4

MEM_B_DM3

MEM_B_DM2

MEM_B_DM1

MEM_B_DM0

MEM_B_DATA63

MEM_B_DATA62

MEM_B_DATA61

MEM_B_DATA60

MEM_B_DATA59

MEM_B_DATA58

MEM_B_DATA57

MEM_B_DATA56

MEM_B_DATA55

MEM_B_DATA54

MEM_B_DATA53

MEM_B_DATA52

MEM_B_DATA51

MEM_B_DATA50

MEM_B_DATA49

MEM_B_DATA48

MEM_B_DATA47

MEM_B_DATA46

MEM_B_DATA45

MEM_B_DATA44

MEM_B_DATA43

MEM_B_DATA42

MEM_B_DATA41

MEM_B_DATA40

MEM_B_DATA39

MEM_B_DATA38

MEM_B_DATA37

MEM_B_DATA36

MEM_B_DATA35

MEM_B_DATA34

MEM_B_DATA33

MEM_B_DATA32

MEM_B_DATA31

MEM_B_DATA30

MEM_B_DATA29

MEM_B_DATA28

MEM_B_DATA27

MEM_B_DATA26

MEM_B_DATA25

MEM_B_DATA24

MEM_B_DATA23

MEM_B_DATA22

MEM_B_DATA21

MEM_B_DATA20

MEM_B_DATA19

MEM_B_DATA18

MEM_B_DATA17

MEM_B_DATA16

MEM_B_DATA15

MEM_B_DATA14

MEM_B_DATA13

MEM_B_DATA12

MEM_B_DATA11

MEM_B_DATA10

MEM_B_DATA9

MEM_B_DATA8

MEM_B_DATA7

MEM_B_DATA6

MEM_B_DATA5

MEM_B_DATA4

MEM_B_DATA3

MEM_B_DATA2

MEM_B_DATA1

MEM_B_DATA0

V_1P5 V_1P5

MEM_B_EVNT_ L 14

MEM_B_DATA[63..0 ] 14

U1C

TP_MEM_B_ CLK7

1

TP50TP-2 TP5 0TP-2

TP_MEM_B_ CLK7*

1

TP54TP-2 TP5 4TP-2

TP_MEM_B_ CLK6

1

TP55TP-2 TP5 5TP-2

TP_MEM_B_ CLK6*

1

TP51TP-2 TP5 1TP-2

MEM_B_CL K5

MEM_B_CL K5*

MEM_B_CL K414

MEM_B_CL K4*14

MEM_B_CL K3

MEM_B_CL K3*

MEM_B_CL K214

MEM_B_CL K2*14

MEM_B0_C S1*14

MEM_B0_C S0*14

MEM_B0_OD T114

MEM_B0_OD T014

MEM_B1_C S1*

MEM_B1_C S0*

MEM_B1_OD T1

MEM_B1_OD T0

MEM_B_CAS*14

MEM_B_WE*14

MEM_B_RAS*14

MEM_B_BA[2..0]14

MEM_B1_C KE14

MEM_B_ADD[1 5..0]14

MEM_B_DQS [7..0]14

MEM_B_DQS *[7..0]14

MEM_B0_C KE14

MEM_B_DM[7..0 ]14

TP_MEM_B_ CLK1

1

TP57TP-2 TP5 7TP-2

TP_MEM_B_ CLK1*

1

TP59TP-2 TP5 9TP-2

TP_MEM_B_ CLK0

1

TP61TP-2 TP6 1TP-2

TP_MEM_B_ CLK0*

1

TP63TP-2 TP6 3TP-2

MEM_B_RE SET_L14

MEM_B_BA2

MEM_B_BA1

MEM_B_BA0

MEM_B_ADD1 5

MEM_B_ADD1 4

MEM_B_ADD1 3

MEM_B_ADD1 2

MEM_B_ADD1 1

MEM_B_ADD1 0

MEM_B_ADD9

MEM_B_ADD8

MEM_B_ADD7

MEM_B_ADD6

MEM_B_ADD5

MEM_B_ADD4

MEM_B_ADD3

MEM_B_ADD2

MEM_B_ADD1

MEM_B_ADD0

MEM_B_DQS 7

MEM_B_DQS *7

MEM_B_DQS 6

MEM_B_DQS *6

MEM_B_DQS 5

MEM_B_DQS *5

MEM_B_DQS 4

MEM_B_DQS *4

MEM_B_DQS 3

MEM_B_DQS *3

MEM_B_DQS 2

MEM_B_DQS *2

MEM_B_DQS 1

MEM_B_DQS *1

MEM_B_DQS 0

MEM_B_DQS *0

MEM_B_DM7

MEM_B_DM6

MEM_B_DM5

MEM_B_DM4

MEM_B_DM3

MEM_B_DM2

MEM_B_DM1

MEM_B_DM0

U1C

AJ19

MB_CLK_H7

AK19

MB_CLK_L7

AL19

MB_CLK_H6

AL18

MB_CLK_L6

U31

MB_CLK_H5

U30

MB_CLK_L5

W29

MB_CLK_H4

W28

MB_CLK_L4

Y31

MB_CLK_H3

Y30

MB_CLK_L3

V31

MB_CLK_H2

W31

MB_CLK_L2

A18

MB_CLK_H1

A19

MB_CLK_L1

C19

MB_CLK_H0

D19

MB_CLK_L0

AE30

MB0_CS_L1

AC31

MB0_CS_L0

AF31

MB0_ODT1

AD29

MB0_ODT0

AE29

MB1_CS_L1

AB31

MB1_CS_L0

AG31

MB1_ODT1

AD31

MB1_ODT0

B19

MB_RESET_L

AC29

MB_CAS_L

AC30

MB_WE_L

AB29

MB_RAS_L

N31

MB_BANK2

AA31

MB_BANK1

AA28

MB_BANK0

M31

MB_CKE1

M29

MB_CKE0

N28

MB_ADD15

N29

MB_ADD14

AE31

MB_ADD13

N30

MB_ADD12

P29

MB_ADD11

AA29

MB_ADD10

P31

MB_ADD9

R29

MB_ADD8

R28

MB_ADD7

R31

MB_ADD6

R30

MB_ADD5

T31

MB_ADD4

T29

MB_ADD3

U29

MB_ADD2

U28

MB_ADD1

AA30

MB_ADD0

AK13

MB_DQS_H7

AJ13

MB_DQS_L7

AK17

MB_DQS_H6

AJ17

MB_DQS_L6

AK23

MB_DQS_H5

AL23

MB_DQS_L5

AL28

MB_DQS_H4

AL29

MB_DQS_L4

D31

MB_DQS_H3

C31

MB_DQS_L3

C24

MB_DQS_H2

C23

MB_DQS_L2

D17

MB_DQS_H1

C17

MB_DQS_L1

C14

MB_DQS_H0

C13

MB_DQS_L0

AJ14

MB_DM7

AH17

MB_DM6

AJ23

MB_DM5

AK29

MB_DM4

C30

MB_DM3

A23

MB_DM2

B17

MB_DM1

B13

MB_DM0

OPTER

OPTER

(62.10055.281)

(62.10055.281)

3 OF 8

3 OF 8

MEM_B_DATA63

AH13

MB_DATA63

MB_DATA62

MB_DATA61

MB_DATA60

MB_DATA59

MB_DATA58

MB_DATA57

MB_DATA56

MB_DATA55

MB_DATA54

MB_DATA53

MB_DATA52

OPTERON

OPTERON

MB_DATA51

MB_DATA50

MB_DATA49

MB_DATA48

MB_DATA47

MB_DATA46

MB_DATA45

MB_DATA44

MB_DATA43

MB_DATA42

MB_DATA41

MB_DATA40

MB_DATA39

MB_DATA38

MB_DATA37

MB_DATA36

MB_DATA35

MB_DATA34

MB_DATA33

MB_DATA32

MB_DATA31

MB_DATA30

MB_DATA29

MB_DATA28

MB_DATA27

MB_DATA26

MB_DATA25

MB_DATA24

MB_DATA23

MB_DATA22

MB_DATA21

MB_DATA20

MB_DATA19

MB_DATA18

MB_DATA17

MB_DATA16

MB_DATA15

MB_DATA14

MB_DATA13

MB_DATA12

MB_DATA11

MB_DATA10

MB_DATA9

MEM CHB

MEM CHB

MB_DATA8

MB_DATA7

MB_DATA6

MB_DATA5

MB_DATA4

MB_DATA3

MB_DATA2

MB_DATA1

MB_DATA0

MB_DQS_H8

MB_DQS_L8

MB_DM8

MB_CHECK7

MB_CHECK6

MB_CHECK5

MB_CHECK4

MB_CHECK3

MB_CHECK2

MB_CHECK1

MB_CHECK0

MB_EVENT_L

AL13

AL15

AJ15

AF13

AG13

AL14

AK15

AL16

AL17

AK21

AL21

AH15

AJ16

AH19

AL20

AJ22

AL22

AL24

AK25

AJ21

AH21

AH23

AJ24

AL27

AK27

AH31

AG30

AL25

AL26

AJ30

AJ31

E31

E30

B27

A27

F29

F31

A29

A28

A25

A24

C22

D21

A26

B25

B23

A22

B21

A20

C16

D15

C21

A21

A17

A16

B15

A14

E13

F13

C15

A15

A13

D13

J31

J30

J29

K29

K31

G30

G29

L29

L28

H31

G31

V29

MEM_B_DATA62

MEM_B_DATA61

MEM_B_DATA60

MEM_B_DATA59

MEM_B_DATA58

MEM_B_DATA57

MEM_B_DATA56

MEM_B_DATA55

MEM_B_DATA54

MEM_B_DATA53

MEM_B_DATA52

MEM_B_DATA51

MEM_B_DATA50

MEM_B_DATA49

MEM_B_DATA48

MEM_B_DATA47

MEM_B_DATA46

MEM_B_DATA45

MEM_B_DATA44

MEM_B_DATA43

MEM_B_DATA42

MEM_B_DATA41

MEM_B_DATA40

MEM_B_DATA39

MEM_B_DATA38

MEM_B_DATA37

MEM_B_DATA36

MEM_B_DATA35

MEM_B_DATA34

MEM_B_DATA33

MEM_B_DATA32

MEM_B_DATA31

MEM_B_DATA30

MEM_B_DATA29

MEM_B_DATA28

MEM_B_DATA27

MEM_B_DATA26

MEM_B_DATA25

MEM_B_DATA24

MEM_B_DATA23

MEM_B_DATA22

MEM_B_DATA21

MEM_B_DATA20

MEM_B_DATA19

MEM_B_DATA18

MEM_B_DATA17

MEM_B_DATA16

MEM_B_DATA15

MEM_B_DATA14

MEM_B_DATA13

MEM_B_DATA12

MEM_B_DATA11

MEM_B_DATA10

MEM_B_DATA9

MEM_B_DATA8

MEM_B_DATA7

MEM_B_DATA6

MEM_B_DATA5

MEM_B_DATA4

MEM_B_DATA3

MEM_B_DATA2

MEM_B_DATA1

MEM_B_DATA0

TP_MEM_B_DQS8

TP_MEM_B_DQS*8

TP_MEM_B_DM8

TP_MEM_B_ ECC7

TP_MEM_B_ ECC6

TP_MEM_B_ ECC5

TP_MEM_B_ ECC4

TP_MEM_B_ ECC3

TP_MEM_B_ ECC2

TP_MEM_B_ ECC1

TP_MEM_B_ ECC0

1 2

1

1

1

1

1

1

1

1

1

1

1

R470

R470

1KR2 J-1-GP

1KR2 J-1-GP

MEM_B_DATA[63..0 ] 14

TP113 TP-2TP113 TP-2

TP89 TP -2TP89 TP -2

TP86 TP -2TP86 TP -2

TP84 TP -2TP84 TP -2

TP110 TP-2TP110 TP-2

TP87 TP -2TP87 TP -2

TP85 TP -2TP85 TP -2

TP88 TP -2TP88 TP -2

TP78 TP -2TP78 TP -2

TP111 TP-2TP111 TP-2

TP112 TP-2TP112 TP-2

MEM_B_EVNT_ L 14

V_1P5

<Varian t Name >

<Varian t Name >

<Varian t Name >

Title

Title

Title

CPU MEM_B

CPU MEM_B

CPU MEM_B

Size Doc ume nt Num ber Rev

Size Doc ume nt Num ber Rev

Size Doc ume nt Num ber Rev

EBOXER

A2

EBOXER

A2

EBOXER

A2

Date: Sheet of

Date: Sheet of

Date: Sheet

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

of

10 45Monday, Ja nuary 04, 2 010

10 45Monday, Ja nuary 04, 2 010

10 45Monday, Ja nuary 04, 2 010

SA

SA

SA

V_CPU

U1F

U1F

U1E

U1E

B3

VDD

C2

VDD

C4

VDD

D3

VDD

D5

VDD

E4

VDD

E6

VDD

F5

VDD

F7

VDD

G6

VDD

G8

VDD

H7

VDD

H11

VDD

H23

VDD

J8

VDD

J12

VDD

J14

VDD

J16

VDD

J18

VDD

J20

VDD

J22

VDD

J24

VDD

K7

VDD

K9

VDD

K11

VDD

K13

VDD

K15

VDD

K17

VDD

K19

VDD

K21

VDD

K23

VDD

L4

VDD

L5

VDD

L8

VDD

L10

VDD

L12

VDD

L14

VDD

L16

VDD

L18

VDD

L20

VDD

L22

VDD

M2

VDD

M3

VDD

M7

VDD

M9

VDD

M11

VDD

M13

VDD

M15

VDD

M17

VDD

M19

VDD

M21

VDD

M23

VDD

N8

VDD

N10

VDD

N12

VDD

N14

VDD

N16

VDD

N18

VDD

N20

VDD

N22

VDD

P7

VDD

P9

VDD

P11

VDD

P13

VDD

P15

VDD

P17

VDD

P19

VDD

P21

VDD

P23

VDD

R4

VDD

R5

VDD

R8

VDD

R10

VDD

R12

VDD

R14

VDD

R16

VDD

R18

VDD

R20

VDD

R22

VDD

T2

VDD

T3

VDD

T7

VDD

T9

VDD

T11

VDD

T13

VDD

OPTER

OPTER

(62.10055.281)

(62.10055.281)

5 OF 8

5 OF 8

A3

VSS

A7

VSS

A9

VSS

A11

VSS

B4

VSS

B9

VSS

B11

VSS

B14

VSS

B16

VSS

B18

VSS

B20

VSS

B22

VSS

B24

OPTERON

OPTERON

VSS

B26

VSS

B28

VSS

B30

VSS

C3

VSS

D14

VSS

D16

VSS

D18

VSS

D20

VSS

D22

VSS

D24

VSS

D26

VSS

D28

VSS

D30

VSS

E11

VSS

F4

VSS

F14

VSS

F16

VSS

F18

VSS

F20

VSS

F22

VSS

F24

VSS

F26

VSS

F28

VSS

F30

VSS

G9

VSS

G11

VSS

H8

VSS

H10

VSS

H12

VSS

H14

VSS

H16

VSS

H18

VSS

H24

VSS

H26

VSS

H28

VSS

H30

VSS

J4

VSS

J5

VSS

POWER/GND1

POWER/GND1

J7

VSS

J9

VSS

J11

VSS

J13

VSS

J15

VSS

J17

VSS

J19

VSS

J21

VSS

J23

VSS

K2

VSS

K3

VSS

K8

VSS

K10

VSS

K12

VSS

K14

VSS

K16

VSS

K18

VSS

K20

VSS

K22

VSS

K24

VSS

K26

VSS

K28

VSS

K30

VSS

L7

VSS

L9

VSS

L11

VSS

L13

VSS

L15

VSS

L17

VSS

L19

VSS

L21

VSS

L23

VSS

M8

VSS

M10

VSS

V_CPU

T15

VDD

T17

VDD

T19

VDD

T21

VDD

T23

VDD

U8

VDD

U10

VDD

U12

VDD

U14

VDD

U16

VDD

U18

VDD

U20

VDD

U22

VDD

V9

VDD

V11

VDD

V13

VDD

V15

VDD

V17

VDD

V19

VDD

V21

VDD

V23

VDD

W4

VDD

W5

VDD

W8

VDD

W10

VDD

W12

VDD

W14

VDD

W16

VDD

W18

VDD

W20

VDD

W22

VDD

Y2

VDD

Y3

VDD

Y7

VDD

Y9

VDD

Y11

VDD

Y13

VDD

Y15

VDD

Y17

VDD

Y19

VDD

Y21

VDD

Y23

VDD

AA8

VDD

AA10

VDD

AA12

VDD

AA14

VDD

AA16

VDD

AA18

VDD

AA20

VDD

AA22

VDD

AB7

VDD

AB9

VDD

AB11

VDD

AB13

VDD

AB15

VDD

AB17

VDD

AB19

VDD

AB21

VDD

AB23

VDD

AC4

VDD

AC5

VDD

AC8

VDD

AC10

VDD

AC12

VDD

AC14

VDD

AC16

VDD

AC18

VDD

AC20

VDD

AC22

VDD

AD2

VDD

AD3

VDD

AD7

VDD

AD9

VDD

AD11

VDD

AD23

VDD

AE10

VDD

AE12

VDD

AF7

VDD

AF9

VDD

AF11

VDD

AG4

VDD

AG5

VDD

AG7

VDD

AH2

VDD

AH3

VDD

OPTER

OPTER

(62.10055.281)

(62.10055.281)

6 OF 8

6 OF 8

M12

VSS

M14

VSS

M16

VSS

M18

VSS

M20

VSS

M22

VSS

N4

VSS

N5

VSS

N7

VSS

N9

VSS

N11

VSS

N13

VSS

N15

OPTERON

OPTERON

VSS

N17

VSS

N19

VSS

N21

VSS

N23

VSS

P2

VSS

P3

VSS

P8

VSS

P10

VSS

P12

VSS

P14

VSS

P16

VSS

P18

VSS

P20

VSS

P22

VSS

R7

VSS

R9

VSS

R11

VSS

R13

VSS

R15

VSS

R17

VSS

R19

VSS

R21

VSS

R23

VSS

T8

VSS

T10

VSS

T12

VSS

T14

VSS

T16

VSS

T18

VSS

T20

VSS

T22

VSS

U4

VSS

U5

VSS

U7

VSS

U9

VSS

U11

VSS

U13

VSS

POWER/GND2

POWER/GND2

U15

VSS

U17

VSS

U19

VSS

U21

VSS

U23

VSS

V2

VSS

V3

VSS

V10

VSS

V12

VSS

V14

VSS

V16

VSS

V18

VSS

V20

VSS

V22

VSS

W7

VSS

W9

VSS

W11

VSS

W13

VSS

W15

VSS

W17

VSS

W19

VSS

W21

VSS

W23

VSS

Y8

VSS

Y10

VSS

Y12

VSS

Y14

VSS

Y16

VSS

Y18

VSS

Y20

VSS

Y22

VSS

AA4

VSS

AA5

VSS

AA7

VSS

AA9

VSS

V_CPU_ NB

U1G

U1G

A4

VDDNB

A6

VDDNB

B5

VDDNB

B7

VDDNB

C6

VDDNB

C8

VDDNB

D7

VDDNB

D9

VDDNB

E8

VDDNB

E10

VDDNB

F9

VDDNB

F11

VDDNB

G10

VDDNB

G12

VDDNB

B2

NP/RSVD

H20

NP/VSS1

AE7

NP/VSS2

OPTER

OPTER

(62.10055.281)

(62.10055.281)

7 OF 8

7 OF 8

AA11

VSS

AA13

VSS

AA15

VSS

AA17

VSS

AA19

VSS

AA21

VSS

AA23

VSS

AB2

VSS

AB3

VSS

AB8

VSS

OPTERON

OPTERON

POWER/GND3

POWER/GND3

AB10

VSS

AB12

VSS

AB14

VSS

AB16

VSS

AB18

VSS

AB20

VSS

AB22

VSS

AC7

VSS

AC9

VSS

AC11

VSS

AC13

VSS

AC15

VSS

AC17

VSS

AC19

VSS

AC21

VSS

AC23

VSS

AD8

VSS

AD10

VSS

AD12

VSS

AD14

VSS

AD16

VSS

AD20

VSS

AD22

VSS

AD24

VSS

AE4

VSS

AE5

VSS

AE11

VSS

AF2

VSS

AF3

VSS

AF8

VSS

AF10

VSS

AF12

VSS

AF14

VSS

AF16

VSS

SC4D 7U10V5 ZY-3GP

SC4D 7U10V5 ZY-3GP

1 2

CPU_V_HT

C541

C541

V_1P5

U1H

U1H

AJ1

VLDT_A

AJ2

VLDT_A

AJ3

VLDT_A

AJ4

VLDT_A

A12

VDDR

B12

VDDR

C12

VDDR

D12

VDDR

M24

VDDIO

M26

VDDIO

M28

VDDIO

M30

VDDIO

P24

VDDIO

P26

VDDIO

P28

VDDIO

P30

VDDIO

T24

VDDIO

T26

VDDIO

T28

VDDIO

T30

VDDIO

V25

VDDIO

V26

VDDIO

V28

VDDIO

V30

VDDIO

Y24

VDDIO

Y26

VDDIO

Y28

VDDIO

Y29

VDDIO

AB24

VDDIO

AB26

VDDIO

AB28

VDDIO

AB30

VDDIO

AC24

VDDIO

AD26

VDDIO

AD28

VDDIO

AD30

VDDIO

AF30

VDDIO

OPTER

OPTER

(62.10055.281)

(62.10055.281)

VTT_CPUV_1P2

8 OF 8

8 OF 8

V_1P2

H1

VLDT_B

H2

VLDT_B

H5

VLDT_B

H6

VLDT_B

VDDR

VDDR

VDDR

VDDR

OPTERON

OPTERON

VDDR

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

POWER/GND4

POWER/GND4

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VTT_CPUV_1P2

AG12

AH12

AJ12

AK12

AL12

AF18

AF20

AF22

AF24

AF26

AF28

AG10

AG11

AH14

AH16

AH18

AH20

AH22

AH24

AH26

AH28

AH30

AK2

AK14

AK16

AK18

AK20

AK22

AK24

AK26

AK28

AK30

AL5

<Varian t Name >

<Varian t Name >

<Varian t Name >

Title

Title

Title

CPU POWER/GND

CPU POWER/GND

CPU POWER/GND

Size Doc ume nt Num ber Rev

Size Doc ume nt Num ber Rev

Size Doc ume nt Num ber Rev

EBOXER

A2

EBOXER

A2

EBOXER

A2

Date: Sheet of

Date: Sheet of

Date: Sheet

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

of

11 45Monday, Ja nuary 04, 2 010

11 45Monday, Ja nuary 04, 2 010

11 45Monday, Ja nuary 04, 2 010

SA

SA

SA

PLACE AT CPU

V_1P2

12

C247

C247

SC4D 7U10V5 ZY-3GP

SC4D 7U10V5 ZY-3GP

SC4D 7U10V5 ZY-3GP

SC4D 7U10V5 ZY-3GP

SC4D 7U10V5 ZY-3GP

SC4D 7U10V5 ZY-3GP

12

12

C372

C372

12

C371

C371

C123

C123

SCD2 2U16V2 ZY-1GP

SCD2 2U16V2 ZY-1GP

SCD2 2U16V2 ZY-1GP

SCD2 2U16V2 ZY-1GP

12

C133

C133

SC18 0P50V2JN -1GP

SC18 0P50V2JN -1GP

TOP

C370

C370

1 2

SC18 0P50V2JN -1GP

SC18 0P50V2JN -1GP

PLACE NEAR CPU SOCKET SIDES ALONG VDDR (VTT_CPU/V_1P2 COMBINED) POUR

VTT_CPU

12

12

C180

C180

C176

SC4D 7U10V5 ZY-3GP

SC4D 7U10V5 ZY-3GP

SC4D 7U10V5 ZY-3GP

SC4D 7U10V5 ZY-3GP

(78.10610.51L)

(78.10610.51L)

(78.10610.51L)

(78.10610.51L)

C176

C368

C368

1 2

TOP LEFT

12

C235

C235

SCD2 2U16V2 ZY-1GP

SCD2 2U16V2 ZY-1GP

SCD2 2U16V2 ZY-1GP

SCD2 2U16V2 ZY-1GP

12

(78.10590.4FL)

(78.10590.4FL)

C400

C400

12

C380

C380

SCD0 1U50V2 ZY-1GP

SCD0 1U50V2 ZY-1GP

(78.10590.4FL)

(78.10590.4FL)

V_1P2

12

C181

C181

SC4D 7U10V5 ZY-3GP

SC4D 7U10V5 ZY-3GP

SC4D 7U10V5 ZY-3GP

SC4D 7U10V5 ZY-3GP

(78.10610.51L)

(78.10610.51L)

10/24

12

(78.10610.51L)

(78.10610.51L)

C234

C234

12

C140

C140

SC4D 7U10V5 ZY-3GP

SC4D 7U10V5 ZY-3GP

(78.10610.51L)

(78.10610.51L)

TOP RIGHT

12

C379

C379

SCD2 2U16V2 ZY-1GP

SCD2 2U16V2 ZY-1GP

SCD2 2U16V2 ZY-1GP

SCD2 2U16V2 ZY-1GP

(78.10590.4FL)

(78.10590.4FL)

12

(78.10590.4FL)

(78.10590.4FL)

C392

C392

Bottom

12

C389

C389

SCD0 1U50V2 ZY-1GP

SCD0 1U50V2 ZY-1GP

SCD2 2U16V2 ZY-1GP

SCD2 2U16V2 ZY-1GP

(78.10590.4FL)

(78.10590.4FL)

12

(78.10590.4FL)

(78.10590.4FL)

C166

C166

EMI OPTIONS

V_CPU

C145

C145

1

1

(R)

(R)

V_CPU

(R)

(R)

C147 SC2D2 U6D3 V2MX-GP

C147 SC2D2 U6D3 V2MX-GP

1

1

1

1

(R)

(R)

C148 SC2D2 U6D3 V2MX-GP

C148 SC2D2 U6D3 V2MX-GP

V_CPU_ NB

2

2

SC2D 2U6D 3V2MX-GP

SC2D 2U6D 3V2MX-GP

V_1P5

2

2

2

2

V_CPU

SC22 U6D3V5 MX-2GP

SC22 U6D3V5 MX-2GP

SC22 U6D3V5 MX-2GP

SC22 U6D3V5 MX-2GP

(78.10610.51L)

(78.10610.51L)

V_CPU

1 2

SC10 U6D3V5 MX-3GP

SC10 U6D3V5 MX-3GP

SC10 U6D3V5 MX-3GP

SC10 U6D3V5 MX-3GP

12

12

C383

C383

C416

C416

SC22 U6D3V5 MX-2GP

SC22 U6D3V5 MX-2GP

(78.10610.51L)

(78.10610.51L)

Ceramic / 0805/X5R

C382

C382

C415

C415

1 2

(R)

(R)

(R)

(R)

SC10 U6D3V5 MX-3GP

SC10 U6D3V5 MX-3GP

12

12

C460

C460

SC22 U6D3V5 MX-2GP

SC22 U6D3V5 MX-2GP

(78.10610.51L)

(78.10610.51L)

(78.10610.51L)

(78.10610.51L)

C407

C407

1 2

1 2

(R)

(R)

SC10 U6D3V5 MX-3GP

SC10 U6D3V5 MX-3GP

12

C396

C396

C417

C417

SC22 U6D3V5 MX-2GP

SC22 U6D3V5 MX-2GP

SC22 U6D3V5 MX-2GP

SC22 U6D3V5 MX-2GP

(78.10610.51L)

(78.10610.51L)

(78.10610.51L)

(78.10610.51L)

C387

C387

C414

C414

1 2

1 2

(R)

(R)

(R)

(R)

SC10 U6D3V5 MX-3GP

SC10 U6D3V5 MX-3GP

SC10 U6D3V5 MX-3GP

SC10 U6D3V5 MX-3GP

PLACE TOPSIDE CLOSE TO SOCKET

V_CPU_ NB

SC10 U10V5ZY-1GP

SC10 U10V5ZY-1GP

12

12

C397

C397

C431

C431

SC22 U6D3V5 MX-2GP

SC22 U6D3V5 MX-2GP

SC22 U6D3V5 MX-2GP

SC22 U6D3V5 MX-2GP

(78.10610.51L)

(78.10610.51L)

MOUNT 10uF/0805

C406

C406

C376

C376

1 2

(R)

(R)

(R)

(R)

SC10 U6D3V5 MX-3GP

SC10 U6D3V5 MX-3GP

10/25

12

12

C153

C153

C249

C249

SC10 U10V5ZY-1GP

SC10 U10V5ZY-1GP

SC4D 7U10V5 ZY-3GP

SC4D 7U10V5 ZY-3GP

12

C378

C378

SC22 U6D3V5 MX-2GP

SC22 U6D3V5 MX-2GP

(78.10610.51L)

(78.10610.51L)

(78.10610.51L)

(78.10610.51L)

V_CPU

12

SC4D 7U10V5 ZY-3GP

SC4D 7U10V5 ZY-3GP

12

C146

C146

SCD2 2U16V2 ZY-1GP

SCD2 2U16V2 ZY-1GP

12

12

C381

C381

SC22 U6D3V5 MX-2GP

SC22 U6D3V5 MX-2GP

(78.10610.51L)

(78.10610.51L)

12

C118

C118

C125

C125

SC4D 7U10V5 ZY-3GP

SC4D 7U10V5 ZY-3GP

SC4D 7U10V5 ZY-3GP

SC4D 7U10V5 ZY-3GP

10/25

12

12

C143

C143

SCD2 2U16V2 ZY-1GP

SCD2 2U16V2 ZY-1GP

12

C395

C395

SC22 U6D3V5 MX-2GP

SC22 U6D3V5 MX-2GP

(R)(78.10610.51L)

(R)(78.10610.51L)

12

C130

C130

SCD2 2U16V2 ZY-1GP

SCD2 2U16V2 ZY-1GP

12

C137

C137

SCD0 1U50V2 ZY-1GP

SCD0 1U50V2 ZY-1GP

C405

C405

12

C246

C246

12

C411

C411

SCD2 2U16V2 ZY-1GP

SCD2 2U16V2 ZY-1GP

C369

C369

SCD0 1U50V2 ZY-1GP

SCD0 1U50V2 ZY-1GP

12

Under the CPU socket

12

C402

C402

C424

C424

1 2

SC18 0P50V2JN -1GP

SC18 0P50V2JN -1GP

SCD0 1U50V2 ZY-1GP

SCD0 1U50V2 ZY-1GP

PLACE BETWEEN CPU AND DIMM IN MEM_ADD FIELD

V_1P5

SC4D 7U10V5 ZY-3GP

SC4D 7U10V5 ZY-3GP

C444

C444

12

C280

C280

12

C259

C259

SC18 0P50V2JN -1GP

SC18 0P50V2JN -1GP

SCD2 2U16V2 ZY-1GP

SCD2 2U16V2 ZY-1GP

TOP LEFT

V_1P5

12

C434

C434

SC22 U6D3V5 MX-2GP

SC22 U6D3V5 MX-2GP

(78.10693.41L)

(78.10693.41L)

V_1P5

C279

C279

1 2

SC4D 7U10V5 ZY-3GP

SC4D 7U10V5 ZY-3GP

V_CPU_ NB

12

C384

C384

SC22 U6D3V5 MX-2GP

SC22 U6D3V5 MX-2GP

(78.10610.51L)

(78.10610.51L)

MOUNT 10uF/0805

12

C429

C429

C430

C430

SC22 U6D3V5 MX-2GP

SC22 U6D3V5 MX-2GP

SC22 U6D3V5 MX-2GP

SC22 U6D3V5 MX-2GP

(78.10693.41L)

(78.10693.41L)

12

12

C277

C277

C275

C275

SCD2 2U16V2 ZY-1GP

SCD2 2U16V2 ZY-1GP

TOP RIGHT

12

C404

C404

SC22 U6D3V5 MX-2GP

SC22 U6D3V5 MX-2GP

(78.10610.51L)

(78.10610.51L)

12

C443

C443

SC22 U6D3V5 MX-2GP

SC22 U6D3V5 MX-2GP

(78.10693.41L)

(78.10693.41L)

C276

C276

1 2

SC18 0P50V2JN -1GP

SC18 0P50V2JN -1GP

12

C398

C398

SCD0 1U50V2 ZY-1GP

SCD0 1U50V2 ZY-1GP

SCD0 1U50V2 ZY-1GP

SCD0 1U50V2 ZY-1GP

12

12

C461

C461

SC10 U10V5ZY-1GP

SC10 U10V5ZY-1GP

SC4D 7U10V5 ZY-3GP

SC4D 7U10V5 ZY-3GP

(78.10693.41L)

(78.10693.41L)

12

C518

C518

SC18 0P50V2JN -1GP

SC18 0P50V2JN -1GP

12

C447

C447

SC4D 7U10V5 ZY-3GP

SC4D 7U10V5 ZY-3GP

C399

C399

1 2

12

C445

C445

SCD2 2U16V2 ZY-1GP

SCD2 2U16V2 ZY-1GP

12

C452

C452

SCD2 2U16V2 ZY-1GP

SCD2 2U16V2 ZY-1GP

V_1P2

12

C128

C128

SC10 U6D3V5 MX-3GP

SC10 U6D3V5 MX-3GP

SC22 U6D3V5 MX-2GP

SC22 U6D3V5 MX-2GP

(78.10610.51L)

(78.10610.51L)

12

C457

C457

SCD0 1U50V2 ZY-1GP

SCD0 1U50V2 ZY-1GP

C172

C172

1 2

12

C446

C446

12

C459

C459

SCD0 1U50V2 ZY-1GP

SCD0 1U50V2 ZY-1GP

SC18 0P50V2JN -1GP

SC18 0P50V2JN -1GP

C458

C458

1 2

C465

C465

1 2

SC18 0P50V2JN -1GP

SC18 0P50V2JN -1GP

<Varian t Name >

<Varian t Name >

<Varian t Name >

Title

Title

Title

CPU DECOUPLING

CPU DECOUPLING

CPU DECOUPLING

Size Doc ume nt Num ber Rev

Size Doc ume nt Num ber Rev

Size Doc ume nt Num ber Rev

EBOXER

A2

EBOXER

A2

EBOXER

A2

Date: Sheet

Date: Sheet

Date: Sheet

Wistron Incorporated

Wistron Incorporated

Wistron Incorporated

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

21F, 88, Hsin Tai Wu Rd

Hsichih, Taipei

Hsichih, Taipei

Hsichih, Taipei

of

12 45Monday, Ja nuary 04, 2 010

of

12 45Monday, Ja nuary 04, 2 010

of

12 45Monday, Ja nuary 04, 2 010

SA

SA

SA

SMB_CL K_MAIN14,20

SMB_DATA_MAIN14,20

MEM_A_BA[2..0]9

Memory CHA

MEM_A_DATA63

MEM_A_DATA62

MEM_A_DATA61

MEM_A_DATA60

MEM_A_DATA59

MEM_A_DATA58

MEM_A_DATA57

MEM_A_DATA56

MEM_A_DATA55

MEM_A_DATA54

MEM_A_DATA53

MEM_A_DATA52

MEM_A_DATA51

MEM_A_DATA50

MEM_A_DATA49

MEM_A_DATA48

MEM_A_DATA47

MEM_A_DATA46

MEM_A_DATA45

MEM_A_DATA44

MEM_A_DATA43

MEM_A_DATA42

MEM_A_DATA41

MEM_A_DATA40

MEM_A_DATA39

MEM_A_DATA38

MEM_A_DATA37

MEM_A_DATA36

MEM_A_DATA35

MEM_A_DATA34

MEM_A_DATA33

MEM_A_DATA32

MEM_A_DATA31

MEM_A_DATA30

MEM_A_DATA29

MEM_A_DATA28

MEM_A_DATA27

MEM_A_DATA26

MEM_A_DATA25

MEM_A_DATA24

MEM_A_DATA23

MEM_A_DATA22

MEM_A_DATA21

MEM_A_DATA20

MEM_A_DATA19

MEM_A_DATA18