ZILOG Z89313 Datasheet

FEATURES

PRELIMINARY

P

RELIMINARY

C

USTOMER PROCUREMENT SPECIFICATION

Z89313

DIGITAL TELEVISION CONTROLLER

Z89313

CPS5TEL0700

■ Part ROM RAM Speed

Number (Word) (Word) (MHz)

Z89313 32K x 16 1K x 16 12

■ 52-Pin Shrink DIP Package

■ 4.5- to 5.5-Volt Operating Range

■ Z89C00 RISC Processor Core

■ 0°C to +70°C Temperature Range

GENERAL DESCRIPTION

The Z89313 is a member of Zilog's family of Digital

Television Controllers designed to provide complete audio

and video control of television receivers, video recorders,

and advanced on-screen display facilities.

The Z89313 features a powerful Z89C00 RISC processor

core that controls on-board peripheral functions and

registers using the standard processor instruction set.

In closed caption mode, text can be decoded directly from

the composite video signal and displayed on the screen

with assistance from the processor's digital signal

processing capabilities. The character representation in

this mode allows for a simple attribute control through the

insertion of control characters.

■ Direct Closed Caption Decoding

■ TV Tuner Serial Interface

■ Customized Character Set

■ Character Control Mode

■ Directly Controlled Receiver Functions

Serial interfacing with the television tuner is provided

through the tuner serial port. Digital channel tuning

adjustments may be accessed through the industrystandard I2C port.

Additional hardware provides the capability to display two

to three times normal size characters. The smoothing logic

contained in the on-screen display circuit improves the

appearance of larger fonts. Special circuitry can be

activated to improve the visibiity of text by adding a rightsided shadow effect to the characters.

Receiver functions such as color and volume can be

directly controlled by six 8-bit pulse width modulated

ports.

The character control mode provides access to the full set

of attribute controls. The modification of attributes is allowed

on a character-by-character basis. The insertion of control

characters permits direction of other character attributes.

Display attributes, including underlining, italics, blinking,

eight foreground/background colors, character position

offset delay, and background transparency, are made

possible through a fully customized 512 character set,

formatted in two 256 character banks.

CP95TEL0700 (6/95)

Notes:

All Signals with a preceding front slash, "/", are active Low, e.g.:

B//W (WORD is active Low); /B/W (BYTE is active Low, only).

Power connections follow conventional descriptions below:

Connection Circuit Device

Power V

Ground GND V

CC

V

DD

SS

1

PRELIMINARY

GENERAL DESCRIPTION (Continued)

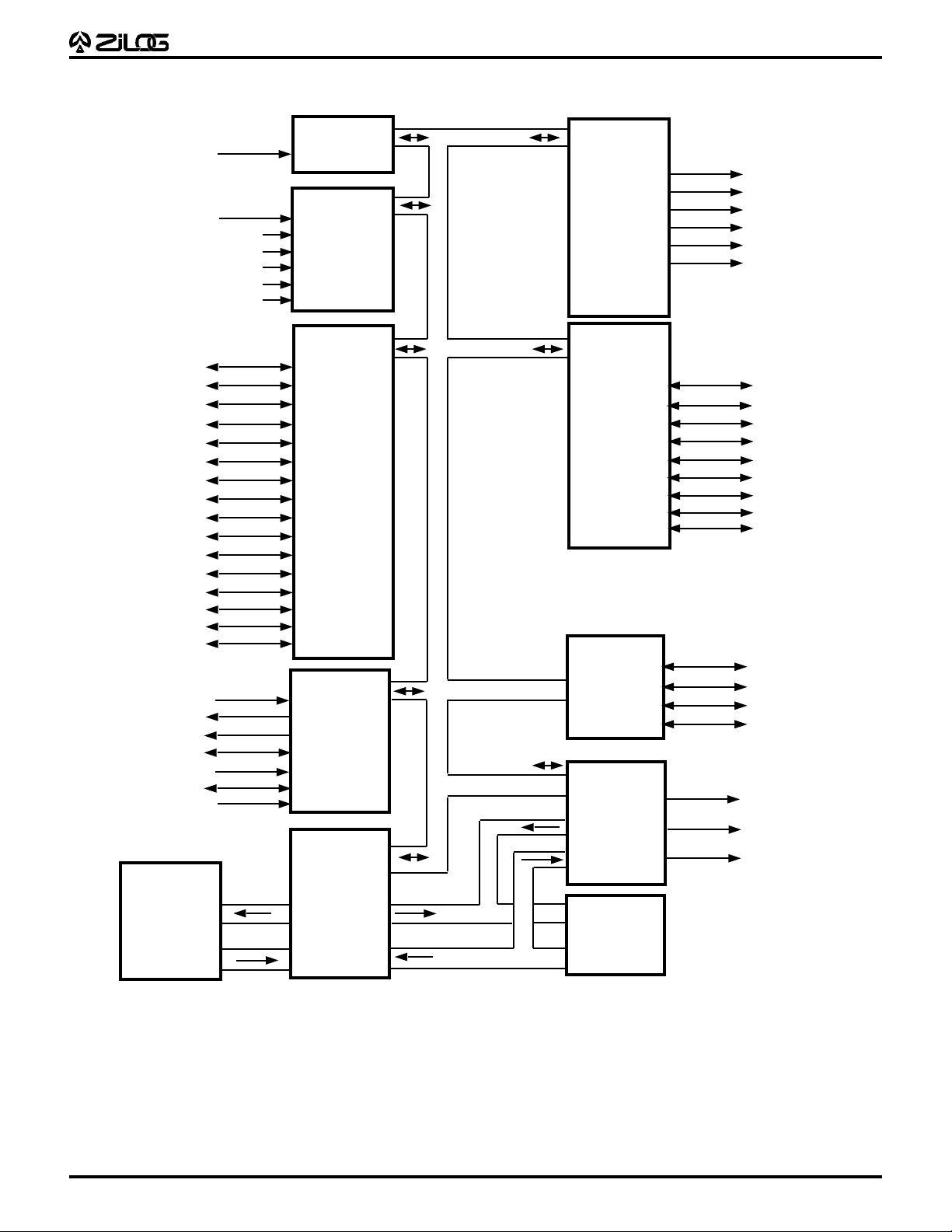

Z89313

CP95TEL0700

CVI

PWM6

Port 17

Port 00

Port 05

Port 04

Capture

IRIN

ADC

ADC0

ADC1

ADC2

ADC3

ADC4

ADC5

Port 0

Port 00

Port 01

Port 02

Port 03

Port 04

Port 05

Port 06

Port 07

Port 08

Port 09

Port 0A

Port 0B

Port 0C

Port 0D

Port 0E

Port 0F

Control

XTAL1

XTAL2

LPF

HSYNC

HSYNC2

VSYNC

/Reset

Register Addr/Data

PWM

PWM1

PWM2

PWM3

PWM4

PWM5

PWM6

Port1

Port 10

Port 11

Port 12

Port 13

Port 14

Port 15

Port 16

Port 17

Port 18

I2C

SCL/MSCL2

SCD/MSCD2

MSCL1

MSCD1

OSD

V1(R)

Port 01/11

Port 02/12

CPU

V2(G)

V3(B)

RAM

1K x 16

Address

Data

ROM Addr

ROM

32K x 16

ROM Data

Functional Block Diagram

2

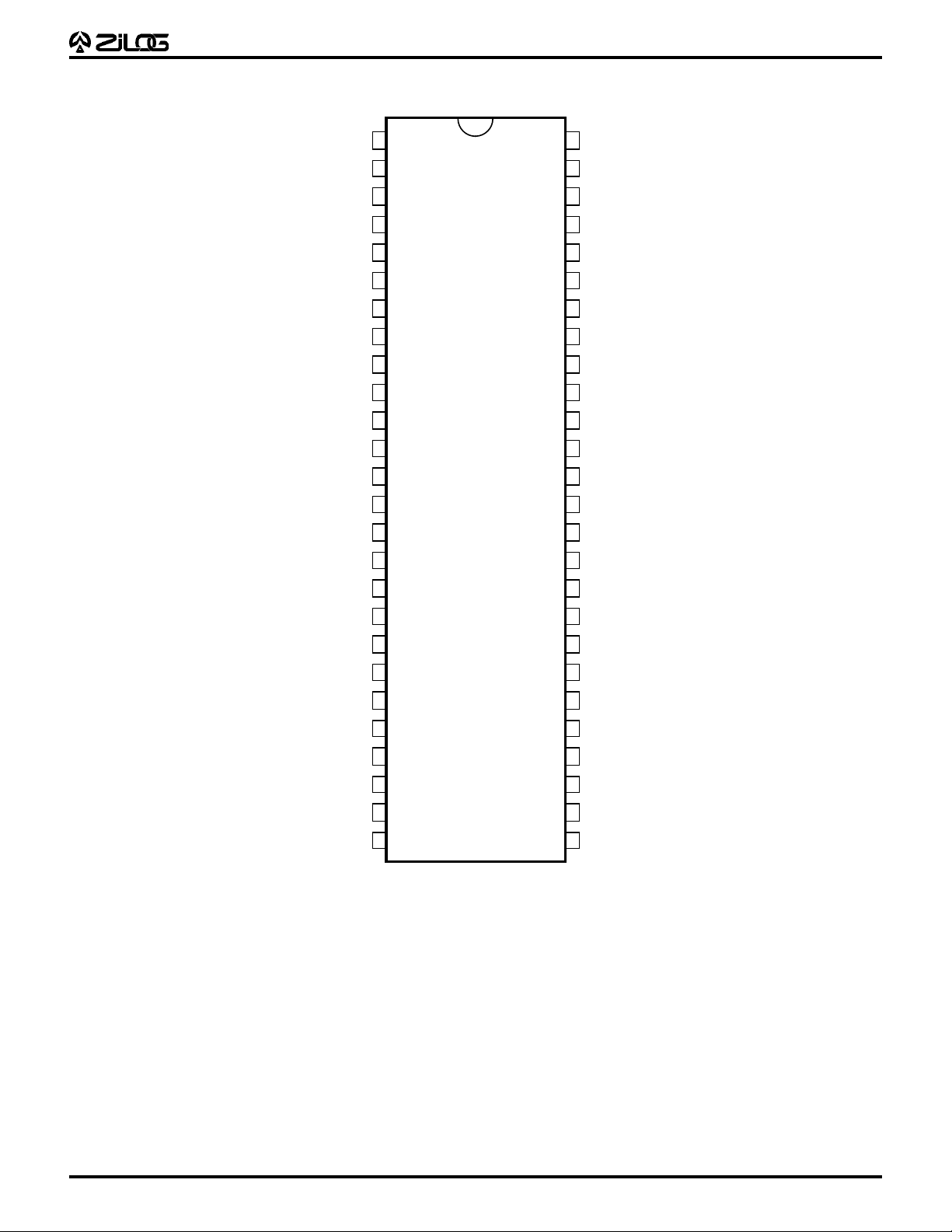

PIN DESCRIPTION

PRELIMINARY

Z89313

CPS5TEL0700

Port 16/SCLK

IRIN

Port 0C

Port 0B

Port 0A

Port 09

Port 0D

Port 07/CSync

Port 06/Counter

Port 03

Port 01/I2SSC

Port 02/I2SSD

CVI/ADC0

LPF

ANGNDF

ADC5

Port 04/ADC4

Port 05/ADC3

Port 00/ADC2

Port 17/ADC1

ANGND

ANVCC

Port0F/HalfBlank

V3 (B)

V2 (G)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

Z89313

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

Port15/B<1>

Port14/B<0>

Port13/G<1>

Port18/G<0>

Port08/R<1>

Port10/R<0>

PWM6/Hsync2

PWM5

PWM4

PWM3

PWM2

PWM1

ANGNDX

VCC

GND

XTAL2

XTAL1

/Reset

I2MSC1

I2MSD1

Port 0E

Port11/I2MSC2

Port11/I2MSD2

VSync

HSync

V1 (R)

26

52-Pin Shrink DIP Configuration

27

Blank

3

Loading...

Loading...