1

查询Z86733供应商

P

RELIMINARY

C

USTOMER

P

ROCUREMENT

S

PECIFICATION

Z86E33/733/E34

FEATURES

ROM

Device

Z86E33 4 237 24 16

Z86733 8 237 24 16

Z86E34 16 237 24 16

Z86E43 4 236 32 16

Z86743 8 236 32 16

Z86E44 16 236 32 16

Note: *General-Purpose

Standard Temperature (V

■

■

Extended Temperature (V

■

28-Pin DIP/SOIC/PLCC Packages (E33/733/E34)

40-Pin DIP Package (E43/743/E44)

44-Pin PLCC/QFP Packages (E43/743/E44)

■

Software Enabled Watch-Dog Timer (WDT)

■

Push-Pull/Open-Drain Programmable on

Port 0, Port 1, and Port 2

(KBytes)

RAM*

(Bytes)

= 3.5V to 5.5V)

CC

= 4.5V to 5.5V)

CC

I/O

Lines

Speed

(MHz)

Z86E43/743/E44

CMOS Z8

■

■

■

■

■

■

■

■

■

■

■

®

OTP M

Programmable Crystal Oscillator, EPROM Protect,

RAM Protect, Auto Latch Disable, Permanent WDT,

32 KHz Oscillator, and EPROM /Test Mode Disable

Fast Instruction Pointer: 0.6 µ s

Two Standby Modes: STOP and HALT

24/32 Input and Output Lines

Digital Inputs CMOS Levels, Schmitt-Triggered

Software Programmable Low EMI Mode

Two Programmable 8-Bit Counter/Timers Each with a 6-

Bit Programmable Prescaler

Six Vectored, Priority Interrupts from Six Different

Sources

Auto Latches

Auto Power-On Reset (POR)

Two Comparators

ICROCONTROLLERS

1

■

Low-Power Consumption: 60 mW

GENERAL DESCRIPTION

The Z86E33/733/E34/E43/743/E44 8-bit CMOS One-Time

Programmable (OTP) microcontrollers are members of

Zilog's Z8

hanced wake-up circuitry, programmable Watch-Dog Timers, Low Noise EMI options, and easy hardware/software

system expansion capability.

Four basic address spaces support a wide range of memory configurations. The designer has easy access to register mapped peripheral and I/O circuits.

CP97DZ83300

®

single-chip microcontroller family featuring en-

P R E L I M I N A R Y

■

On-Chip Oscillator that Accepts a Crystal, Ceramic

Resonator, LC, RC, or External Clock Drive

For applications demanding powerful I/O capabilities, the

Z86E33/733/E34 have 24 pins and the Z86E43/743/E44

have 32 pins of dedicated input and output. These lines are

grouped into four ports, eight lines per port, and are configurable under software control to provide timing, status signals, and parallel I/O with or without handshake, and address/data bus for interfacing external memory.

Notes: All Signals with a preceding front slash, "/", are

active Low, e.g., B//W (WORD is active Low); /B/W (BYTE

is active Low, only).

1

2

Z86E33/733/E34/E43/743/E44

CMOS Z8® OTP Microcontrollers Zilog

Power connections follow conventional descriptions below:

Connection Circuit Device

Power V

CC

Ground GND V

V

DD

SS

(E43/743/E44)

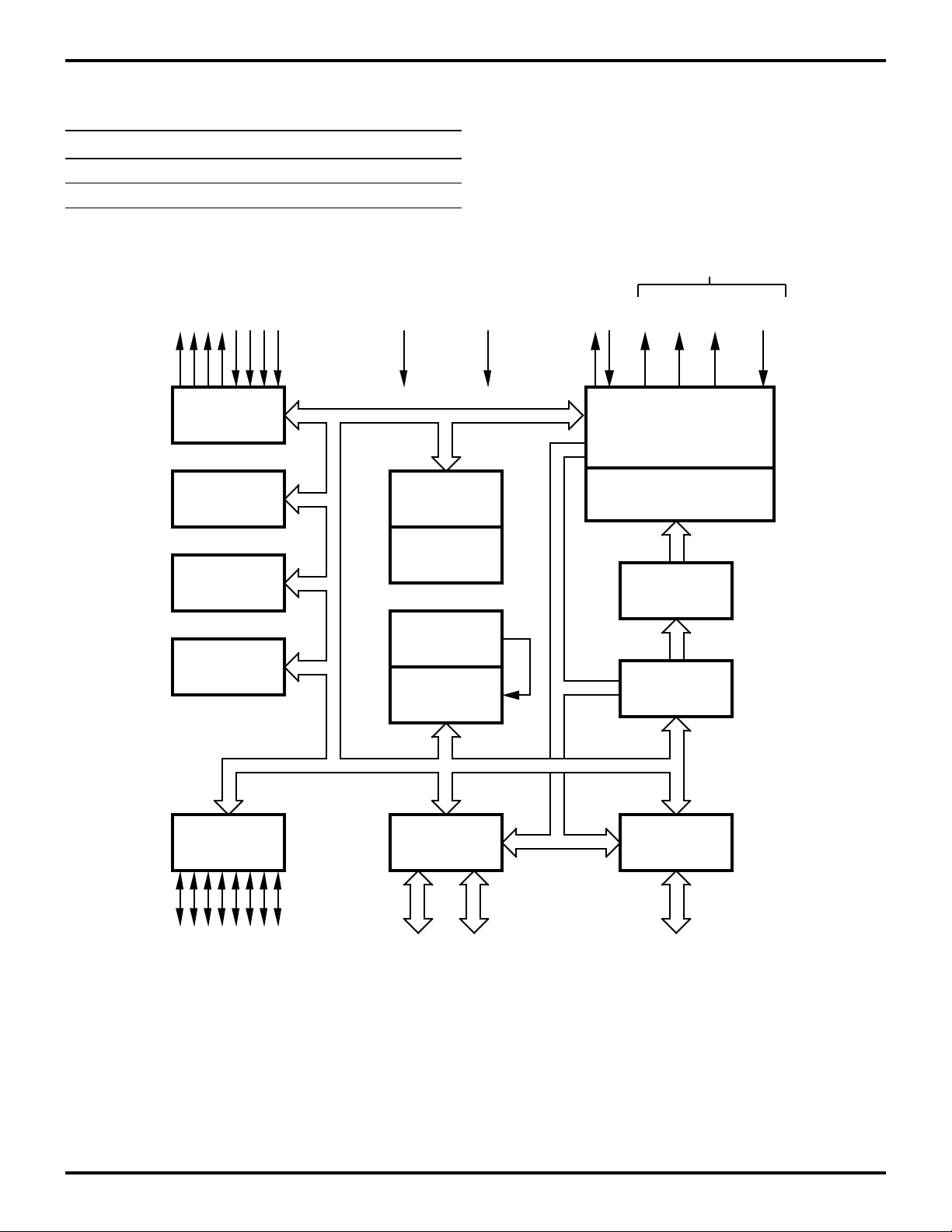

Output Input

Port 3

Counter/

Timers (2)

Interrupt

Control

T wo Analog

Comparators

VCC

ALU

FLAGS

Register

Pointer

Register File

GND

XTAL

/AS /DS R//W /RESET

Machine T iming

Instruction Control

RESET

WDT, POR

OTP

Program

Counter

&

Port 2

I/O

(Bit Programmable)

Port 0

44

Address or I/O

(Nibble Programmable)

Figure 1. Functional Block Diagram

P R E L I M I N A R Y

Port 1

8

Address/Data or I/O

(Byte Programmable)

(E43/743/E44 Only)

CP97DZ83300

1

Z86E33/733/E34/E43/743/E44

Zilog CMOS Z8® OTP Microcontrollers

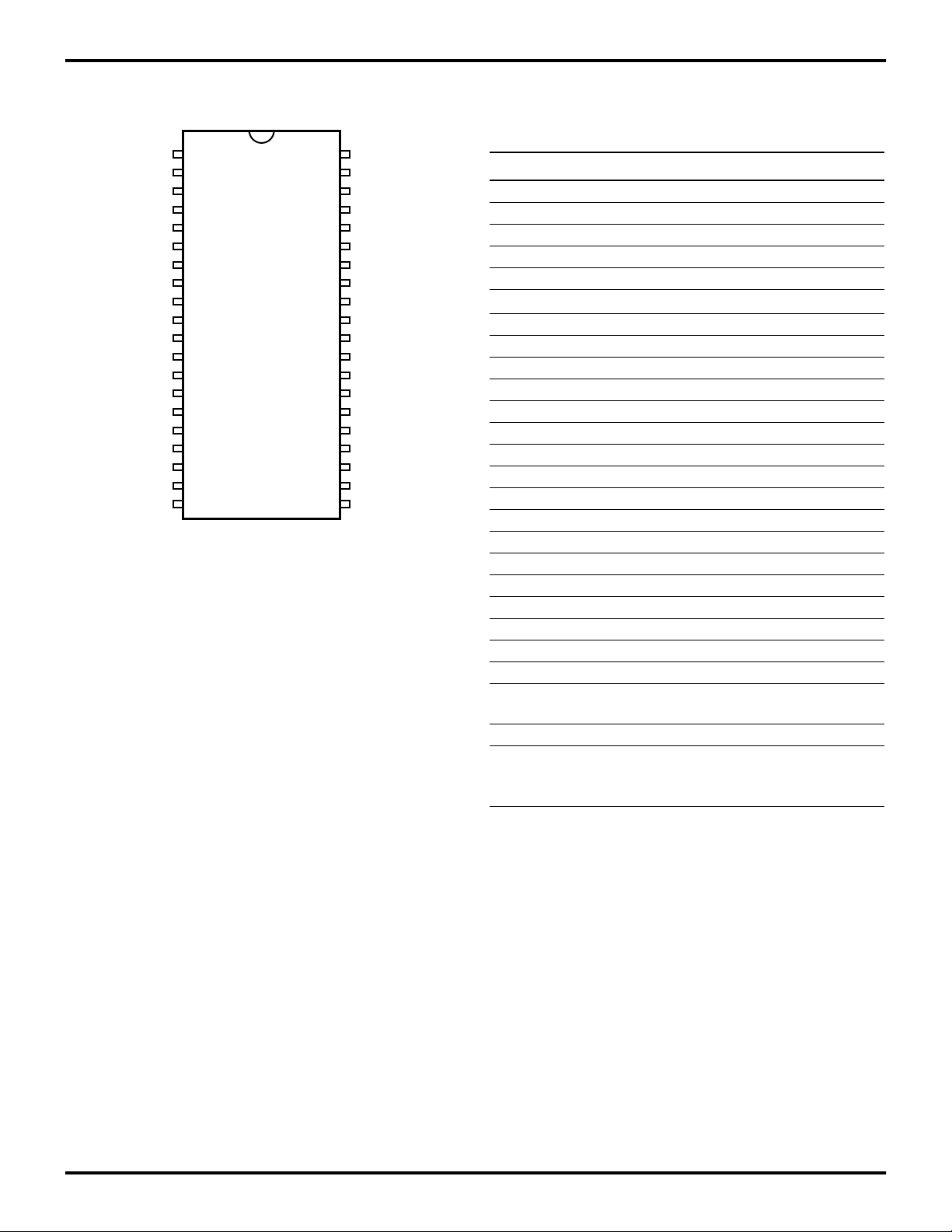

PIN IDENTIFICATION

Table 1. 40-Pin DIP Pin Identification

Standard Mode

R//W

P25

P26

P27

P04

P05

P06

P14

P15

P07

VCC

P16

P17

XTAL2

XTAL1

P31

P32

P33

P34

/AS

1

DIP

20 21

Figure 2. 40-Pin DIP Pin Configuration

Standard Mode

40

/DS

P24

P23

P22

P21

P20

P03

P13

P12

GND

P02

P11

P10

P01

P00

P30

P36

P37

P35

/RESET

Pin # Symbol Function Direction

1 R//W Read/Write Output

2-4 P25-P27 Port 2, Pins 5,6,7 In/Output

5-7 P04-P06 Port 0, Pins 4,5,6 In/Output

8-9 P14-P15 Port 1, Pins 4,5 In/Output

10 P07 Port 0, Pin 7 In/Output

11 V

CC

Power Supply

12-13 P16-P17 Port 1, Pins 6,7 In/Output

14 XTAL2 Crystal Oscillator Output

15 XTAL1 Crystal Oscillator Input

16-18 P31-P33 Port 3, Pins 1,2,3 Input

19 P34 Port 3, Pin 4 Output

20 /AS Address Strobe Output

21 /RESET Reset Input

22 P35 Port 3, Pin 5 Output

23 P37 Port 3, Pin 7 Output

24 P36 Port 3, Pin 6 Output

25 P30 Port 3, Pin 0 Input

26-27 P00-P01 Port 0, Pins 0,1 In/Output

28-29 P10-P11 Port 1, Pins 0,1 In/Output

30 P02 Port 0, Pin 2 In/Output

31 GND Ground

32-33 P12-P13 Port 1, Pins 2,3 In/Output

34 P03 Port 0, Pin 3 In/Output

35-39 P20-P24 Port 2, Pins

In/Output

0,1,2,3,4

40 DS Data Strobe Output

Notes:

Pin Configuration and Identification identical on DIP

and Cerdip Window Lid style packages.

CP97DZ83300

P R E L I M I N A R Y

3

Loading...

Loading...