Page 1

AFC1

ACTIVE FIELD CONTROLLER

SERVICE MANUAL

CONTENTS

SPECIFICATIONS .............................................. 3/4

PANEL LAYOUT ..................................... 5

CIRCUIT BOARD LAYOUT ................. 6

DIMENSIONS ............................................................ 7

DISASSEMBLY PROCEDURE .............................. 8

LSI PIN DESCRIPTION .............................. 12

IC BLOCK DIAGRAM ................................... 18

CIRCUIT BOARDS ....................................... 20

TEST PROGRAM AND INSPECTION

(テストプログラムと検査)

FIRMWARE PROGRAM UPDATE

(ファームウェアプログラムのバージョンアップ)

SOUND CHECK FILE FOR SERVICE

(サービス用音声チェックファイル)

ERROR MESSAGES ............................. 42

MIDI IMPLEMENTATION CHART......................................... 43

MIDI DATA FORMAT............................................................. 44

PARTS LIST

POWER SUPPLY UNIT RERAIR MANUAL

(電源ユニットリペアマニュアル)

BLOCK DIAGRAM

WIRING

CIRCUIT DIAGRAM

(総コネクタ接続回路図)

(目次)

(総合仕様)

(パネルレイアウト)

(ユニットレイアウト)

(

寸法図

)

(分解手順)

(LSI端子機能表)

(ICブロック図)

(シート基板図)

(エラーメッセージ)

(ブロックダイアグラム)

(回路図)

................................. 28/32

...... 37

....................... 38/40

011691

PA

200306-オープンプライス

HAMAMATSU, JAPAN

Copyright (c) Yamaha Corporation. All rights reserved. PDF-K8841 ’03.07

1

Page 2

AFC1

IMPORTANT NOTICE

This manual has been provided for the use of authorized Yamaha Retailers and their service personnel. It has been assumed

that basic service procedures inherent to the industry, and more specifically Yamaha Products, are already known and understood by the users, and have therefore not been restated.

WARNING : Failure to follow appropriate service and safety procedures when servicing this product may result in per-

IMPORTANT : This presentation or sale of this manual to any individual or firm does not constitute authorization certifi-

The data provided is belived to be accurate and applicable to the unit(s) indicated on the cover. The research engineering, and

service departments of Yamaha are continually striving to improve Yamaha products. Modifications are, therefore, inevitable

and changes in specification are subject to change without notice or obligation to retrofit. Should any discrepancy appear to

exist, please contact the distributor’s Service Division.

WARNING : Static discharges can destroy expensive components. Discharge any static electricity your body may have

IMPORTANT : Turn the unit OFF during disassembly and parts replacement. Recheck all work before you apply power

sonal injury, destruction of expensive components and failure of the product to perform as specified. For

these reasons, we advise all Yamaha product owners that all service required should be performed by an

authorized Yamaha Retailer or the appointed service representative.

cation, recognition of any applicable technical capabilities, or establish a principal-agent relationship of

any form.

accumulated by grounding yourself to the ground bus in the unit (heavy gauge black wires connect to

this bus.)

to the unit.

LITHIUM BATTER Y HANDLING

This product uses a lithium battery for memory back-up.

WARNING : Lithium batteries are dangerous because they can be exploded by improper handling. Observe the following pre-

Leave lithium battery replacement to qualified service personnel.

Always replace with batteries of the same type.

When installing on the PC board by soldering, solder using the connection terminals provided on the battery cells.

Never solder directly to the cells. Perform the soldering as quickly as possible.

Never reverse the battery polarities when installing.

Do not short the batteries.

Do not attempt to recharge these batteries.

Do not disasemble the batteries.

Never heat batteries or throw them into fire.

ADVARSEL!

Lithiumbatteri-Eksplosionsfare ved fejlagtig handtering. Udskiftning ma kun ske med batteri af samme fabrikat og type. lever det brugte

batteri tilbage til leverandren.

VARNING

Explosionsfara vid felaktigt batteribyte.

Anvand samma batterityp eller en ekvivalent typ som rekommenderas av apparattillverkaren.

Kassera anvant batteri enligt fabrikantens instruktion.

VAROITUS

Paristo voi rajahtaa, jos se on virheellisesti asennettu.

Vaihda paristo ainoastaan laitevalmistajan suosittelemaan tyyppiiin.

Havita kaytetty paristo valmistajan ohjeiden mukaisesti.

The following information complies with Dutch official Gazette 1995. 45; ESSENTIALS OF ORDER ON THE COLLECTION OF BATTERIES.

• Please refer to the diassembly procedure for the removal of Back-up Battery.

• Leest u voor het verwijderen van de backup batterij deze beschrijving.

cautions when handling or replacing lithium batteries.

リチウム電池の取り扱い

<注意>

リチウム電池を誤って交換すると爆発する危険があります。交換する場合は、サービスマニュアルで指定された部品を

使用してください。

WARNING: CHEMICAL CONTENT NOTICE!

The solder used in the production of this product contains LEAD. In addition, other electrical/electronic and/or plastic (Where

applicable) components may also contain traces of chemicals found by the California Health and Welfare Agency (and possibly

other entities) to cause cancer and/or birth defects or other reproductive harm.

DO NOT PLACE SOLDER, ELECTRICAL/ELECTRONIC OR PLASTIC COMPONENTS IN YOUR MOUTH FOR ANY REASON WHAT

SO EVER!

Avoid prolonged, unprotected contact between solder and your skin! When soldering, do not inhale solder fumes or expose

eyes to solder/flux vapor!

If you come in contact with solder or components located inside the enclosure of this product, wash your hands before handling

food.

2

Page 3

AFC1

• General

Sampling

frequency

Internal 48 kHz

External 39.69 to 50.88 kHz

Signal delay

0.21 ms (direct cable routed from Input

1 to output 1, fs = 48 kHz)

Memory

Configuration 2 (AA, SURROUND)

PATTERN 6 (for each configuration)

Indicators 7-segment LED x 2

Power source 120 V, 60 Hz

Power consumption 40 W

Max. dimensions (W x H x D)

480 x 141.5 x 373 mm

Weight 9.5 kg

Operating temperature 5 ˚C to 35 ˚C

Storing temperature –20 ˚C to 60 ˚C

Power cord length 2.5 m

Accessories

Power cord, removal-proof fixing clamp

16-pin Euro-block connectors x 4

Owner’s Manual

Options

Digital audio cable CAS003

Digital audio cable CAS015

I/Os Format Level

Connector

specifications

WORD CLOCK

INPUT

— TTL BNC

WORD CLOCK

OUTPUT

— TTL BNC

MIDI IN MIDI — DIN 5-pin

MIDI OUT MIDI — DIN 5-pin

CASCADE IN ——

Half-pitch

50-pin

CASCADE OUT ——

Half-pitch

50-pin

PC CONTROL —

RS232C/

RS422

9-pin D-sub

FOR SERVICE USE

— RS422 9-pin D-sub

GPI IN (x16) — 0 to 5 V Euro-block

GPI OUT (x16) — 0 to 5 V Euro-block

GPI +V (x16) — 6 mA max Euro-block

SLOT (x4) mini YGDAI — —

Card name Format Inputs Outputs

MY8-AT ADAT 8 8

MY8-TD TASCAM 8 8

MY8-AE AES/EBU 8 8

MY4-AD Analog input 4

MY8-AD Analog input 8

—

—

MY8-AD24 Analog input 8—

• Control I/Os

• SLOT 1 through 4

The following digital interface cards can be installed in Slots 1-4 on the rear panel.

Slot 1 is a serial interface.

Card name Format Inputs Outputs

MY4-DA Analog output — 4

MY8-AD96 Analog input 8—

MY8-DA96 Analog output — 8

MY8-mLAN mLAN 8 8

• The following cards are not supported for the AFC1:

MY8-AE96, MY8-AE96S, MY16-AT, MY16-TD, MY16-AE, Y56K

• MY8-mLAN is recognized as MY8-AE.

IMPORTANT NOTICE FOR THE UNITED KINGDOM

Connecting the Plug and Cord

WARNING: THIS APPARATUS MUST BE EARTHED

IMPORTANT. The wires in this mains lead are coloured in

accordance with the following code:

GREEN-AND-YELLOW : EARTH

BLUE : NEUTRAL

BROWN : LIVE

As the colours of the wires in the mains lead of this apparatus

may not correspond with the coloured markings identifying the

terminals in your plug proceed as follows:

The wire which is coloured GREEN-and-YELLOW must be connected to the terminal in the plug which is marked by the letter

E or by the safety earth symbol or colored GREEN or

GREEN-and-YELLOW.

The wire which is coloured BLUE must be connected to the terminal which is marked with the letter N or coloured BLACK.

The wire which is coloured BROWN must be connected to the

terminal which is marked with the letter L or coloured RED.

• This applies only to products distributed by Yamaha-Kemble Music (U.K.) Ltd.(3

wires)

SPECIFICATIONS

WARNING

Components having special characteristics are marked and

must be replaced with parts having specification equal to those

originally installed.

印の部品は、安全を維持するために重要な部品です。交換する

場合は、安全のために必ず指定の部品をご使用ください。

3

Page 4

AFC1

総合仕様

• 一般仕様

サンプリング

周波数

シグナルディレイ

メモリー

インジケーター 7 セグメントLED x 2

電源 100 V、50/60 Hz

消費電力 40 W

最大外形寸法 (W x H x D) 480 x 141.5 x 373 mm

質量 9.5 kg

動作保証温度 5 ˚C 〜 35 ˚C

保管温度 –20 ˚C 〜 60 ˚C

電源コード長 2.5 m

付属品

オプション品

内部 48 kHz

外部 39.69 〜 50.88 kHz

0.21 ms (インプット1からアウトプット1

へダイレクトケーブル、fs = 48 kHz)

コンフ ィグレーション

PATTERN コンフィグレーション1つに付き、6個

2 (AA, SURROUND)

電源ケーブル、誤脱防止クランプ

ユーロブロックコネクター16ピン x 4

取扱説明書、保証書

デジタルオーディオケーブル CAS003

デジタルオーディオケーブル CAS015

• SLOT 1 〜 4

リアパネルのSLOT1〜4には、以下のデジタルインターフェー

スカードが使用できます。

SLOT1はシリアルインターフェースです。

カード名 フォーマット 入力 出力

MY8-AT ADAT

MY8-TD TASCAM

MY8-AE AES/EBU

MY4-AD アナログ入力

MY8-AD アナログ入力 8

MY8-AD24 アナログ入力 8

MY4-DA アナログ入力 — 4

MY8-AD96 アナログ入力

MY8-DA96 アナログ出力 — 8

MY8-mLAN mLAN

• 次のカードは使用できません:MY8-AE96、MY8-AE96S、

MY16-AT、MY16-TD、MY16-AE、Y56K

• MY8-mLANは、MY8-AEとして認識されます。

8 8

8 8

8 8

4

8

8 8

—

—

—

—

• コントロールI/O

入出力端子 フォーマット レベル 仕様コネクター

WORD CLOCK

INPUT

WORD CLOCK

OUTPUT

MIDI IN MIDI — DIN 5ピン

MIDI OUT MIDI — DIN 5ピン

CASCADE IN ——

CASCADE OUT ——

PC CONTROL —

FOR SERVICE USE

GPI IN (x16) —0 〜 5 V ユーロブロック

GPI OUT (x16) —0 〜 5 V ユーロブロック

GPI +V (x16) — 6 mA max ユーロブロック

SLOT (x4) mini YGDAI — —

— TTL BNC

— TTL BNC

ハーフピッチ

50ピン

ハーフピッチ

50ピン

RS232C/

RS422

— RS422 9ピン D-sub

9ピン D-sub

4

Page 5

AFC1

PANEL LAYOUT

Front panel

1

2

Rear panel

(フロントパネル)

PATTERN/LIVENESS indicator

POWER switch

(リアパネル)

(パネルレイアウト)

1

1

PATTERN/LIVENESS インジケーター

2

POWER スイッチ

2

3

5 6 7 8 9 10 11 12 13

4 14 15

3

AC IN connector

4

Grounding screw

5

WORD CLOCK OUT connector

6

WORD CLOCK 75Ω ON/OFF switch

7

WORD CLOCK IN connector

8

MIDI IN/OUT connectors

9

PC CONTROL RS232C/RS422 switch

10

PC CONTROL port

11

FOR SERVICE USE port

12

CASCADE OUT port

13

CASCADE IN port

14

GPI connectors

15

SLOTs 1–4

3

AC INソケット

4

アース用ネジ

5

WORD CLOCK OUT 端子

6

WORD CLOCK 75Ω ON/OFF スイッチ

7

WORD CLOCK IN 端子

8

MIDI IN/OUT 端子

9

PC CONTROL RS232C/RS422 スイッチ

10

PC CONTROL 端子

11

FOR SERVICE USE 端子

12

CASCADE OUT 端子

13

CASCADE IN 端子

14

GPI 端子

15

SLOT(スロット)1–4

5

Page 6

AFC1

CIRCUIT BOARD LAYOUT

< Rear view>

MAIN PNR (GPI)

< Top view>

(ユニットレイアウト)

PNR

(MYMB)

SUB

< Front view>

CN005

CN016

Power supply unit

(電源ユニット)

CN012

CN010

CN014

CN013

CN011

CN502

CN501

PNF (LED) PNF (PSW)

6

Page 7

AFC1

DIMENSIONS

(寸法図)

430

355

D: 373

30

30

(34) 18

43.5 277.5

W: 480

81 81318

132

H: 141.5

Units: mm

(単位)

9.5

7

Page 8

AFC1

DISASSEMBLY PROCEDURE

1. Top Cover (Time required: About 2 minutes)

1-1 Remove the fourteen (14) screws marked [470]. The

top cover can then be removed. (Fig. 1)

2. Front Panel Assembly (Time required: About 5 minutes)

2-1 Remove the top cover. (See procedure 1.)

2-2 Remove the eight (8) screws marked [345A] and

the two (2) screws marked [350]. The left and right

mount brackets can then be removed. (Fig. 1)

(分解手順)

1. トップカバー(所要時間:約2 分)

1-1 [470]のネジ14本を外して、トップカバーを外しま

す。(図 1)

2. フロントパネルAss'y(所要時間:約 5分)

2-1 トップカバーを外します。(1 項参照)

2-2 [345A]のネジ 8 本と[350]のネジ 2 本を外して、左

右のマウントブラケットを外します。(図 1)

2-3 [70]のネジ1本と[320]のネジ4本を外して、フロン

トパネルAss'y を外します。(図 1)

2-3 Remove the screw marked [70] and the four (4)

screws marked [320]. The front panel assemb ly can

then be removed. (Fig. 1)

[470]

< Top view >

Top cover(トップカバー)

[470]

< Left side view > < Right side view >

[470]

[345A] Mount bracket

(マウントブラケット)

[70]: Bind Head Tapping Screw-B(+バインドBタイト)A4.0X8 MFZN2BL (VC688800)

[320]: Bind Head Tapping Screw-B(+バインドBタイト)A4.0X8 MFZN2BL (VC688800)

[345A]: Oval Head Screw(+丸皿小ネジ)4.0X8 MFZN2BL (VS153600)

[350]: Oval Head Screw(歯付座金付+丸皿小ネジ)B4.0X10 MFZN2BL (V6221000)

[470]: Bind Head Tapping Screw-B(+バインドBタイト)A4.0X8 MFZN2BL (VC688800)

3. MAIN+SUB Circuit Boards (Time required: About 5 minutes)

3-1 Remove the top cover. (See procedure 1.)

3-2 Remove the four (4) screws marked [A], the four

(4) screws marked [B], the two (2) screws marked

[420], the two (2) screws marked [430] and the five

(5) screws marked [440]. The MAIN+SUB circuit

boards can then be removed. (Fig. 2, 3)

Fig .1 (図1)

[350][350]

[470]

[70]

Mount bracket

(マウントブラケット)

[345A] [320] x 4

3. MAIN+ SUBシート(所要時間:約 5分)

3-1 トップカバーを外します。(1 項参照)

3-2 [A]のネジ 4本と[B]のネジ 4 本、[420]のネジ2 本、

[430]のネジ2本、[440]のネジ 5 本を外して、MAIN

+SUB シートを外します。(図 2,3)

8

Page 9

AFC1

4. Replacement of the Lithium Battery

(Time required: About 2 minutes)

4-1 Remove the top cover. (See procedure 1.)

4-2 The lithium battery can be replacement on the MAIN

circuit board. (Fig. 3)

The lithium battery is not a part of the MAIN circuit

board. Therefore, always save the data before

exchanging the MAIN circuit board. Once the data

has been saved, the lithium battery can be

removed from the circuit boar d f or the Main body

and mounted to the new circuit board.

< Rear view >

[170A] [420] [430] [A]

[40c] [290] [290]

PNR (GPI)

[B]

4. リチウム電池の交換(所要時間:約2 分)

4-1 トップカバーを外します。(1 項参照)

4-2 MAINシート上より、リチウム電池を交換するこ

とが出来ます。(図 3)

※ リチウム電池は、MAINシートの構成部品ではあり

ません。MAINシートを交換する際には、まず交換

前にデータを保存し、その後本体のシートからリ

チウム電池を取り外して新しいシートに取り付け

てください。

[40c]: Support(サポート)(V5600300)

[170A]: Bind Head Tapping Screw-B(+バインドB タイト)

A4.0X8 MFZN2BL (VC688800)

[290]: Pan Head Screw(+ナベ小ネジ)2.6X6 MFZN2BL (VC990500)

[420]: Bonding Screw(+ボンディング小ネジ)3.0X6 MFZN2BL (VS863000)

[430]: Bonding Tapping Screw-B(+ボンディングBタイト)

3.0X8 MFZN2BL (VN413300)

Fig .2 (図2)

• Lithium Battery(リチウム電池)

Battery VN103500

VN103600(Battery holder for VN103500)

Notice for back-up battery removal

Push the battery as shown in figure,

then the battery will pop up.

Druk de batterij naar beneden zoals

aangeven in de tekening de batterij

springt dan naar voren.

[440]: Bind Head Tapping Screw-B(+バインド B タイト)

3.0X6 MFZN2BL (EP600230)

Battery

Battery holder

< Top view >

[440]

MAIN

+

SUB

[440]

Fig .3 (図3)

9

Page 10

AFC1

5. Power Supply Unit (Time required: About 3 minutes)

5-1 Remove the top cover. (See procedure 1.)

5-2 Remove the two (2) screws marked [150]. The

power supply unit can then be removed. (Fig. 4)

6. AC Inlet (Time required: About 4 minutes)

6-1 Remove the top cover. (See procedure 1.)

6-2 Remove the two (2) screws marked [170A], the four

(4) screws marked [170B] and the two (2) screws

marked [345B]. The side panel R and the mount

bracket can then be removed. (Fig. 2, 4)

6-3 Remove the two (2) supports marked [40c] and the

screw marked [80]. The AC inlet can then be

removed. (Fig. 2, 4)

7. PNR(MYMB) and PNR(GPI) Circuit Boards (Time required: About 6 minutes each)

7-1 Remove the top cover. (See procedure 1.)

7-2 Remove the MAIN+SUB circuit boards.

(See procedure 3.)

7-3 PNR(MYMB) Circuit Board:

Remove the four (4) screws marked [240]. The

PNR(MYMB) circuit board can then be removed.

(Fig. 4)

7-4 PNR(GPI) Circuit Board:

Remove the eight (8) screws marked [290]. The

PNR(GPI) circuit board can then be removed.

(Fig. 2, 4)

5. 電源ユニット(所要時間:約3 分)

5-1 トップカバーを外します。(1 項参照)

5-2 [150]のネジ 2 本を外して、電源ユニットを外しま

す。(図 4)

6. ACインレット(所要時間:約 4分)

6-1 トップカバーを外します。(1 項参照)

6-2 [170A]のネジ 2 本と[170B]のネジ4本、[345B]のネ

ジ2 本を外して、サイドパネルR とマウントブラ

ケットを外します。(図 2,4)

6-3 [40c]のサポート2本と[80]のネジ1本を外して、AC

インレットを外します。(図 2,4)

7. PNR(MYMB),PNR(GPI)シート

(所要時間:各約6 分)

7-1 トップカバーを外します。(1 項参照)

7-2 MAIN + SUB シートを外します。(3 項参照)

7-3 PNR(MYMB)シート:

[240]のネジ4 本を外して、PNR(MYMB)シートを

外します。(図 4)

7-4 PNR(GPI)シート:

[290]のネジ8本を外して、PNR(GPI)シートを外し

ます。(図 2,4)

8. PNF(LED) and PNF(PSW) Circuit Boards (Time required: About 6 minutes each)

8-1 Remove the top cover. (See procedure 1.)

8-2 Remove the front panel assembly.

(See procedure 2.)

8-3 Remove the six (6) screws marked [90]. The front

panel can then be removed. (Fig. 5)

8-4 PNF(LED) Circuit Board:

Remove the screw marked [30]. The PNF(LED)

circuit board can then be removed. (Fig. 6)

8-5 PNF(PSW) Circuit Board:

Pull out the power switch knob. Remove the two (2)

screws marked [60]. The PNF(PSW) circuit board

can then be removed. (Fig. 5, 6)

8. PNF(LED),PNF(PSW)シート(所要時間:各約6分)

8-1 トップカバーを外します。(1 項参照)

8-2 フロントパネル Ass'y を外します。(2 項参照)

8-3 [90]のネジ6本を外して、フロントパネルを外しま

す。(図 5)

8-4 PNF(LED)シート:

[30]のネジ1本を外して、PNF(LED)シートを外し

ます。(図 6)

8-5 PNF(PSW)シート:

PSW ノブを抜き取ります。[60]のネジ2本を外し

て、PNF(PSW)シートを外します。(図 5,6)

10

Page 11

AFC1

)

< Front view > < Front view >

[90]

[90]

[30]

[60]

[60]

Front panel

(フロントパネル)

Power switch knob

(PSWノブ)

PNF (LED)

PNF (PSW)

< Top view > < Right side view >

[240]

[240]

PNR (MYMB)

[80]: Bind Head Screw(+バインド小ネジ)4.0X8 MFZN2BL (EG340360)

[150]: Bind Head Tapping Screw-B(+バインドBタイト)A4.0X8 MFZN2BL (VC688800)

[170B]: Bind Head Tapping Screw-B(+バインドBタイト)A4.0X8 MFZN2BL (VC688800)

[240]: Bind Head Screw(+バインド小ネジ)4.0X8 MFZN2BL (EG340360)

[345B]: Oval Head Screw(+丸皿小ネジ)4.0X8 MFZN2BL (VS153600)

PNR (GPI)

[150]

Power supply unit

(電源ユニット)

Side panel R

(サイドパネルR)

[150]

Fig .4 (図4)

[345B]

[170B]

[80]

[170B]

Mount bracket

(マウントブラケット

[90]: Oval Head Screw(+丸皿小ネジ)4.0X8 MFZN2BL (VS153600)

Fig .5 (図5)

[30]: Bind Head Tapping Screw-B(+バインドBタイト)

3.0X6 MFZN2BL (EP600230)

[60]: Bonding Screw(+ボンディング小ネジ)

3.0X6 MFZN2BL (VS863000)

Fig .6 (図6)

11

Page 12

AFC1

LSI PIN DESCRIPTION

(LSI端子機能表)

HD6437042AF62F (XY885B00) CPU ................................................................................................ 12

YSS904-F (XV989A00) DSP5 (Digital Signal Processor) .................................................................. 13

YSS910-S (XV988A00) DSP6 (Digital Signal Processor) .................................................................. 14

EPM7128SQC100-7 (XY976C00) FPGA (Field Programmable Gate Array) .................................... 15

YM3436DK (XG948E00) DIR2 (Digital Format Interface Receiver) .................................................. 16

ST16C554DCQ64 (XW934A00) UART (Universal asynchronous receiver and transmitter)............. 16

SGH609080F-47F (XU235A00) ATSC ............................................................................................... 17

HD6437042AF62F (XY885B00) CPU

PIN

NO.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

RDWR / PB5

29

30

31

32

PB9 /A21

33

34

35

/WDTOVF

36

37

38

39

40

41

42

PA9 / TCLKD

43

/IRQ2 / TCLKC

44

45

46

47

48

49

50

PA1 / TXD0

51

PA0 / RXD0

52

53

54

55

56

PE14

PE15

VSS

VCC

VSS

/RAS

/CASL

/CASH

VSS

VSS

/WRH

VCC

/WRL

VSS

/CS1

/CS0

/CS3

/CS2

/IRQ1

TXD

RXD

/IRQ0

VSS

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

/RD

D15

D14

D13

D12

I/O FUNCTIONNAME

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

I/O

I/O

I/O

I/O

Port E

I

I

I

I

I

I

I

I

I

I

I

I

Port E

Ground

Address bus

Power supply

Address bus

Ground

Row address strobe

Column address strobe (low)

Column address strobe (high)

Ground

DRAM read/write / Port B

Address bus

Port B / Address bus

Ground

Read

Watch dog timer overflow

High write

Power supply

Low write

Ground

Chip select

Chip select

Port A / Timer clock

Interrupt request / Timer clock

Chip select

Chip select

Interrupt request

Data transmission

Data reception

Interrupt request

Port A / Data transmission

Port A / Data reception

Data bus

Ground

Data bus

PIN

NO.

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

D11

D10

D9

D8

VSS

D7

D6

D5

VCC

D4

D3

D2

D1

D0

VSS

XTAL

MD3

EXTAL

MD2

NMI

VCC

MD1

MD0

PLLVCC

PLLCAP

PLLVSS

PA15 / CK

/RES

PE0

PE1

PE2

PE3

PE4

VSS

AN0 / PF0

AN1 / PF1

AN2 / PF2

AN3 / PF3

AN4 / PF4

AN5 / PF5

AVSS

AN6 / PF6

AN7 / PF7

AVCC

VSS

PE5

VCC

PE6

PE7

PE8

PE9

PE10

VSS

PE11

PE12

PE13

I/O FUNCTIONNAME

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

O

O

O

O

O

O

O

O

O

Data bus

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

Ground

Data bus

Power supply

Data bus

Ground

Crystal oscillator

Mode control

Crystal oscillator

Mode control

Non-maskable interrupt request

Power supply

Mode control

Mode control

PLL Power supply

PLL capacitor

PLL Ground

Port A / Clock

Reset

Port E

Ground

Analog input / Port F

Analog ground

Analog input / Port F

Analog input / Port F

Power supply

Ground

Port E

Power supply

Port E

Ground

Port E

MAIN: IC004

12

Page 13

AFC1

YSS904-F (XV989A00) DSP5 (Digital Signal Processor)

PIN

NO.

100

101

102

103

104

I/O

NC

1

NC

2

NC

3

NC

4

Vdd

5

Vss

6

XI

7

XO

8

Vdd

9

/SYNCI

10

/SYNCO

11

Vdd

12

CKI

13

CKO

14

CKSEL

15

Vss

16

MCKD

17

/SSYNC

18

/IC

19

/TEST

20

NC

21

NC

22

NC

23

Vdd

24

Vss

25

/CS

26

/WR

27

/RD

28

CA7

29

CA6

30

CA5

31

CA4

32

CA3

33

CA2

34

CA1

35

Vss

36

Vdd

37

CD15

38

CD14

39

CD13

40

CD12

41

CD11

42

CD10

43

CD09

44

CD08

45

CD07

46

CD06

47

Vss

48

NC

49

NC

50

NC

51

NC

52

NC

53

NC

54

NC

55

NC

56

Vdd

57

Vdd

58

CD05

59

CD04

60

CD03

61

CD02

62

CD01

63

CD00

64

/WAIT

65

Vss

66

SIO00

67

SIO01

68

SIO02

69

SIO03

70

SIO04

71

SIO05

72

SIO06

73

SIO07

74

Vss

75

Vdd

76

SIO08

77

SIO09

78

SIO10

79

SIO11

80

SIO12

81

SIO13

82

SIO14

83

SIO15

84

Vss

85

Vdd

86

SIO16

87

SIO17

88

SIO18

89

SIO19

90

SIO20

91

SIO21

92

SIO22

93

SIO23

94

Vss

95

Vdd

96

SIO24

97

SIO25

98

SIO26

99

SIO27

NC

NC

NC

NC

I

O

O

I

O

I

O

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

Not used

Ground

Power supply

System master clock input (60 MHz or 30 MHz)

System master clock output (High or 30 MHz)

Ground

Sync. signal input

Sync. signal output

Ground

System clock input (30 MHz)

System clock output (30 MHz)

System master clock select

Power supply

Serial clock input (256 fs)

Serial. signal input

Initial clear

Test mode setting (0: TEST, 1: Normal)

Not used

Ground

Power supply

Chip select

Write enable input

Read enable input

CPU address bus

Power supply

Ground

CPU data bus

Power supply

Not used

Ground

CPU data bus

Wait output

Power supply

Serial data bus

Power supply

Ground

Serial data bus

Power supply

Ground

Serial data bus

Power supply

Ground

Serial data bus

Not used

FUNCTIONNAME

PIN

NO.

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

180

181

182

183

184

185

186

187

188

189

190

191

192

193

194

195

196

197

198

199

200

201

202

203

204

205

206

207

208

NC

NC

NC

NC

SIO28

SIO29

SIO30

SIO31

Vss

Vdd

SIO32

SIO33

SIO34

SIO35

SIO36

SIO37

SIO38

SIO39

Vss

Vdd

SIO40

SIO41

SIO42

SIO43

SIO44

SIO45

SIO46

SIO47

Vss

SIO48

SIO49

SIO50

SIO51

SIO52

SIO53

SIO54

SIO55

Vss

Vdd

Vdd

SIO56

SIO57

SIO58

SIO59

SIO60

SIO61

SIO62

SIO63

NC

NC

NC

NC

NC

NC

NC

NC

Vss

/POE

Vss

PIO00

PIO01

PIO02

PIO03

PIO04

PIO05

PIO06

PIO07

Vss

Vdd

Vdd

PIO08

PIO09

PIO10

PIO11

PIO12

PIO13

PIO14

PIO15

Vss

NC

PIO16

PIO17

PIO18

PIO19

PIO20

PIO21

PIO22

PIO23

Vss

Vdd

Vdd

PIO24

PIO25

PIO26

PIO27

PIO28

PIO29

PIO30

PIO31

Vss

NC

NC

NC

NC

MAIN: IC106, 107, 110

I/O

Not used

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

Serial data bus

Power supply

Ground

Serial data bus

Power supply

Ground

Serial data bus

Power supply

Serial data bus

Power supply

Ground

Serial data bus

Not used

Power supply

Parallel data bus controll signal

Power supply

Parallel data bus

Power supply

Ground

Parallel data bus

Power supply

Not used

Parallel data bus

Power supply

Ground

Parallel data bus

Power supply

Not used

FUNCTIONNAME

13

Page 14

AFC1

YSS910-S (XV988A00) DSP6 (Digital Signal Processor)

14

PIN

NO.

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

1

2

3

4

5

6

7

8

9

/SYNCI

/SYNCO

CKO

CKSEL

MCKS

/SSYNC

/TEST

BTYP

TRIG

CD15

CD14

CD13

CD12

CD11

CD10

CD09

CD08

CD07

CD06

CD05

CD04

CD03

CD02

CD01

CD00

/WAIT

DB00

DB01

DB02

DB03

DB04

DB05

DB06

DB07

DB08

DB09

DB10

DB11

DB12

Vdd

Vss

XI

XO

Vdd

Vdd

CKI

Vss

/IC

/IRQ

Vdd

Vss

/CS

/WR

/RD

CA7

CA6

CA5

CA4

CA3

CA2

CA1

Vss

Vdd

Vss

Vdd

Vdd

Vss

SI0

SI1

SI2

SI3

SI4

SI5

SI6

SI7

Vss

Vdd

SO0

SO1

SO2

SO3

SO4

SO5

SO6

SO7

Vss

Vdd

Vdd

I/O FUNCTIONNAME

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

Power supply (3.3 V)

Ground

I

O

I

O

I

O

I

I

I

I

I

I

O

I

I

I

O

I

I

I

I

I

I

I

I

O

O

O

O

O

O

O

O

System master clock input (60 MHz or 30 MHz)

System master clock output (High or 30 MHz)

Power supply (5 V)

Sync. signal input

Sync. signal output

Power supply (5 V)

System clock input (30 MHz)

System clock output (30 MHz)

System master clock select (0: 60 MHz, 1: 30 MHz)

Ground

Serial I/O master clock input (128 x Fs)

Serial I/O Sync. signal output

Initial clear

Test mode setting (0: Test, 1: Normal)

Data bus type select (0: 8 bit, 1: 16 bit)

IRQ output

Trigger signal input/output

Power supply (5 V)

Ground

chip select signal input

Write signal input

Read signal input

Address bus of internal register

Ground

Power supply (3.3 V)

Data bus of internal register

Ground

Power supply (3.3 V)

Power supply (5 V)

Data bus of internal register

WAIT output

Ground

Serial data input

Ground

Power supply (5 V)

Serial data output

Ground

Parallel data bus

Power supply (5 V)

Power supply (3.3 V)

PIN

NO.

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

89

90

91

92

93

94

95

96

97

98

99

Vss

DB13

DB14

DB15

DB16

DB17

DB18

DB19

DB20

DB21

DB22

Vss

Vdd

DB23

DB24

DB25

DB26

DB27

DB28

DB29

DB30

DB31

TIMO/DBOB

Vss

Vdd

DA00

DA01

DA02

DA03

DA04

DA05

DA06

DA07

Vss

DA08

DA09

DA10

DA11

DA12

DA13

DA14

DA15

Vss

Vdd

(n.c)

Vdd

DA16

DA17

DA18

DA19

DA20

DA21

DA22

DA23

Vss

DA24

DA25

DA26

DA27

DA28

DA29

DA30

DA31

Vdd

Vss

A00

A01

A02

A03

A04

A05

A06

A07

A08

A09

Vss

Vdd

A10

A11

A12

A13

A14

A15/RAS

A16/CAS

A17/CE

/WE

/OE

Vdd

I/O FUNCTIONNAME

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

MAIN: IC077, 080, 083, 086, 089,

092, 095, 098, 101, 104

Ground

Parallel data bus

Ground

Power supply (3.3 V)

Parallel data bus

Timing signal output/ Parallel data bus output/ input

Ground

Power supply (5 V)

Memory data bus

Ground

Memory data bus

Ground

Power supply (3.3 V)

Not used

Power supply (5 V)

Memory data bus

Ground

Memory data bus

Power supply (5 V)

Ground

Memory address (SRAM, PSRAM, DRAM)

Ground

Power supply (3.3 V)

Memory address (SRAM, PSRAM, DRAM)

Memory address (SRAM, PSRAM)

Memory address (SRAM, PSRAM), /RAS (DRAM)

Memory address (SRAM, PSRAM), /CAS (DRAM)

Memory address (SRAM), /CE (PSRAM)

Memory write enable signal

Memory output enable signal

Power supply (5 V)

Page 15

AFC1

EPM7128SQC100-7 (XY976C00) FPGA (Field Programmable Gate Array)

PIN

NO.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

A1

A2

A3

A4

VCCIO

TDI

A5

A6

A7

A12

A13

A14

GND

A15

A18

A19

TMS

A21

D0

VCCIO

D1

D2

D3

SIOSEL

/BS

WDTOVF

/PCMINT

GND

/PCMWAIT

/DSPWAIT1

/DSPWAIT2

/MYINT

/WAIT

/DSPRST

/DSPEN2

VCCIO

/DSPEN1

/DSPCS

/MYCS4

GND

VCCINT

/MYCS3

/MYCS2

/MYCS1

GND

/MYCS

/IREQ3

/IREQ2

/IREQ1

/IREQ0

I/O FUNCTIONNAME

I/O

I/O

I/O

I/O

I/O

I/O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

Address bus

Power supply (5.0 V)

Unrestricted user-programmable Input/Output pin. Open for normal use.

Address bus

Ground

Address bus

Unrestricted user-programmable Input/Output pin. Open for normal use.

Address bus

Data bus

Power supply (5.0 V)

Data bus

Select

Bus cycle start signal

Watch dog timer overflow

Interrupt

Ground

LSI wait

Wait

Interrupt

Bus wait

DSP reset

Data bus enable

Power supply (5.0 V)

Data bus enable

Chip select decord enable

Chip select

Ground

Power supply (5.0 V)

Chip select

Ground

Data bus enable

Interrupt request

PIN

NO.

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

/GPIWR

/CASLOCK

VCCIO

/SWRD

/LCDGATE

LCD_E

/LEDSET

/SCSET

WCKIN

CASINTX

GND

CASINRX

RPTX

TCK

RPRX

MYSINT

/MY_SCS

VCCIO

HASINT

/HASCS

/USBINT

/USBCS

CASSINT

/CASSCS

TDO

GND

CNTSTX

/CNTSCS

CNTSINT

CNTSRX

/PCMCS

SCS4

SCS3

VCCIO

/SCNCS2

/SCNCS1

/FMCS

GND

CPUCLK

/RD

/RESET1

/WR

VCCINT

/CS1

/CS2

/CS3

GND

/DREQ1

DACK1

CKIO

I/O FUNCTIONNAME

O

O

O

O

O

O

O

O

I/O

O

O

O

O

I/O

O

O

O

O

O

O

O

O

O

O

O

Data latch clock

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

Cascade clock input lock

Power supply (5.0 V)

Switch read strobe

Data bus enable

Access enable

Data latch clock

Strobe latch clock

Word clock

Serial transmit data

Ground

Serial receive data

Serial transmit data

Unrestricted user-programmable Input/Output pin. Open for normal use.

Serial receive data

Interrupt

Chip select

Power supply (5.0 V)

Interrupt

Chip select

Interrupt

Chip select

Interrupt

Chip select

Unrestricted user-programmable Input/Output pin. Open for normal use.

Ground

Serial transmit data

Chip select

Interrupt

Serial receive data

Data bus enable

Chip select

Power supply (5.0 V)

Chip select

Chip select

Ground

System clock supply

Read strobe

System reset

Write strobe

Power supply (5.0 V)

Chip select

Ground

DMA request

DMA acknowledge

Clock supply

MAIN: IC015

15

Page 16

AFC1

YM3436DK (XG948E00) DIR2 (Digital Format Interface Receiver)

PIN

NO.

10

11

12

13

14

15

16

17

18

19

20

21

22

1

2

3

4

5

6

7

8

9

DAUX

HDLT

DOUT

VFL

OPT

SYNC

MCC

WC

MCB

MCA

SKSY

XI

XO

P256

LOCK

Vss

TC

DIM1

DIM0

DOM1

DOM0

KM1

I/O FUNCTIONNAME

I

O

O

O

O

O

O

O

O

O

I

I

O

O

O

O

I

I

I

I

I

Auxiliary input for audio data

Asynchronous buffer operation flag

Audio data output

Parity flag output

Fs x 1 Synchronous output signal for DAC

Fs x 1 Synchronous output signal for DSP

Fs x 64 Bit clock output

Fs x 1 Word clock output

Fs x 128 Bit clock output

Fs x 256 Bit clock output

Clock synchronization control input

Crystal oscillator connection or external

clock input

Crystal oscillator connection

VCO oscillating clock connection

PLL lock flag

Logic section power (GND)

PLL time constant switching output

Data input mode selection

Data input mode selection

Data output mode selection

Data output mode selection

Clock mode switching input 1

PIN

NO.

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

RSTN

Vdda

CTLN

PCO

(NC)

CTLP

Vssa

TSTN

KM2

KM0

FS1

FS0

CSM

EXTW

DDIN

LR

Vdd

ERR

EMP

CD0

CCK

CLD

I/O FUNCTIONNAME

I

I

O

I

I

I

I

O

O

I

I

I

O

O

O

O

I

I

MAIN: IC028, 040

System reset input

VCO section power (+5 V)

VCO control input N

PLL phase comparison output

VCO control input P

VCO section power (GND)

Test terminal. Open for normal use

Clock mode switching input 2

Clock mode switching input 0

Channel status sampling frequency

display output 1

Channel status sampling frequency

display output 0

Channel status output method selection

External synchronous auxiliary input

word clock

EIAJ (AES/EBU) data input

PLL word clock output

Logic section power (+5 V)

Data error flag output

Channel status emphasis control code

output

3-wire type microcomputer interface data

output

3-wire type microcomputer interface clock

input

3-wire type microcomputer interface load

input

ST16C554DCQ64 (XW934A00) UART

(Universal asynchronous receiver and transmitter)

PIN

NO.

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

1

2

3

4

5

6

7

8

9

/DSRA

/CTSA

/DTRA

VCC

/RTSA

INTA

/CSA

TXA

/LOW

TXB

/CSB

INTB

/RTSB

GND

/DTRB

/CTSB

/DSRB

/CDB

/RIB

RXB

VCC

XTAL1

XTAL2

RESET

GND

RXC

/RIC

/CDC

/DSRC

A2

A1

A0

I/O FUNCTIONNAME

I

I

O

I

O

O

I

O

I

O

I

O

O

O

I

I

I

I

I

I

I

I

I

I

O

I

I

I

I

I

Data set ready (active low)

Clear to send (active low)

Data terminal ready (active low)

Power supply inputs

Request to send (active low)

Interrupt A (active high)

Chip select

Transmit data

Write strobe

Transmit data

Chip select

Interrupt B (active high)

Request to send (active low)

Signal and power ground

Data terminal ready (active low)

Clear to send (active low)

Data set ready (active low)

Carrier detect (active low)

Ring indicator (active low)

Receive data input RX B

Power supply inputs

Address bus

Crystal or External clock input

Output of the crystal oscillator or buffered clock

Reset

Signal and power ground

Receive data input RX C

Ring indicator (active low)

Carrier detect (active low)

Data set ready (active low)

PIN

NO.

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

/CTSC

/DTRC

VCC

/RTSC

INTC

/CSC

TXC

/IOR

TXD

/CSD

INTD

/RTSD

GND

/DTRD

/CTSD

/DSRD

/CDD

/RID

RXD

VCC

D0

D1

D2

D3

D4

D5

D6

D7

GND

RXA

/RIA

/CDA

I/O FUNCTIONNAME

O

O

O

O

O

O

O

O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

MAIN: IC018

I

I

I

I

I

I

I

I

I

I

I

I

I

I

Clear to send (active low)

Data terminal ready (active low)

Power supply inputs

Request to send (active low)

Interrupt C (active high)

Chip select

Transmit data

Read strobe

Transmit data

Chip select

Interrupt D (active high)

Request to send (active low)

Signal and power ground

Data terminal ready (active low)

Clear to send (active low)

Data set ready (active low)

Carrier detect (active low)

Ring indicator (active low)

Receive data input RX D

Power supply inputs

Data bus

Signal and power ground

Receive data input RX A

Ring indicator (active low)

Carrier detect (active low)

16

Page 17

AFC1

SGH609080F-47F (XU235A00) ATSC

PIN

NO.

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

syncati

1

mccti

2

mcbti

3

4

5

mcati

6

7

8

9

soat3

soat2

soat1

soat0

mcato

mcbto

mccto

syncato

clksel

ato-sel0

ato-sel1

bitsel2

bitsel1

bitsel0

ext-sync2

si-sel0

si-sel1

VCC

GND

GND

siat0

siat1

siat2

siat3

GND

VCC

GND

GND

VCC

GND

ati

ato

ui0

ui1

ui2

ui3

I/O FUNCTIONNAME

I

Synch. word input terminal for ati,

siat3-0 input

I

64 fs clock input terminal for ati,

siat3-0 input

I

128 fs clock input terminal for ati,

siat3-0 input

Power supply (+5 V)

Ground

I

256 fs clock input terminal for ati,

siat3-0 input

Ground

I

I

I

Serial data input terminal

I

I

Optical input terminal

Ground

O

Optical output terminal

O

O

O

Serial data output terminal

O

Power supply (+5 V)

Ground

I

256 fs clock input terminal for ato,

soat3-0 output

Ground

I

128 fs clock input terminal for ato,

soat3-0 output

I

64 fs clock input terminal for ato,

soat3-0 output

I

Synch. word input terminal for ato,

soat3-0 output

I

Clock select terminal for ato,

soat 3-0 output

0: mcato,mcbto,mccto,syncato

1: mcai,mcbi,mcci,synci

I

Format select terminal for ato,

soat3-0 output

I

Format select terminal for ato,

soat3-0 output

0: mcato,mcbto,mccto,syncato

1: mcai,mcbi,mcci,synci

ato sel0

ato sel1

1

1

0

0

1

0

1

0

output format

ato

soat0

soat2, 0

soat3-0

Bit shift select terminal for the ato output

Power supply (+5 V)

Ground

Synch. detect output terminal 2

U-bit input terminal for optical output

input format select terminal for si3-0

input format select terminal for si3-0i

si sel1

si sel0

1

0

1

0

input format

not enable to set

si0

si2, 0

si3-0

1

1

0

0

(8ch/line)

(4ch/line)

(2ch/line)

(8ch/line)

(4ch/line)

(2ch/line)

PIN

NO.

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

synci

mcci

mcbi

VCC

GND

mcai

GND

si0

si1

si2

si3

GND

so3

so2

so1

so0

VCC

GND

mcao

GND

mcbo

mcco

synco

so-sel1

so-sel0

uo3

uo2

uo1

uo0

ext-sync1

VCC

GND

clk

GND

/res

GND

wc-at

mute

ati-sel1

ati-sel0

MAIN: IC038, 042

I/O FUNCTIONNAME

I

I

I

Synch. word input terminal for si3-0 input

64 fs clock input terminal for si3-0 input

128 fs clock input terminal for si3-0 input

Power supply (+5 V)

Ground

I

256 fs clock input terminal for si3-0 input

Ground

I

I

I

Serial data input terminal

I

Ground

O

O

O

Serial data output terminal

O

Power supply (+5 V)

Ground

I

256 fs clock input terminal for so3-0 output

Ground

I

I

I

I

I

O

128 fs clock input terminal for so3-0 output

64 fs clock input terminal for so3-0 output

Synch. word input terminal for so3-0 output

Format select terminal for soat3-0 output

Format select terminal for soat3-0 output

so sel1

so sel0

1

0

1

0

input format

not enable to set

so0

so2, 0

so3-0

(8ch/line)

(4ch/line)

(2ch/line)

1

1

0

0

O

U-bit output terminal for optical output

O

O

O

Synch. detect output terminal 1

Power supply (+5 V)

Ground

I

Clock input terminal for word clock extract

Ground

I

System reset input terminal

Ground

O

I

I

I

Word clock output terminal

Data mute input terminal

Input format select terminal for ati, siat3-0.

input format select terminal for ati, siat3-0.

ati sel1

ati sel0

1

0

1

0

input format

ati

ati0

ati2, 0

ati3-0

(8ch/line)

(4ch/line)

(2ch/line)

1

1

0

0

17

Page 18

AFC1

IC BLOCK DIAGRAM

MM74HCU04SJX (XY070A00)

IC016

MAIN:

TC74HC04AF (XS993A00)

IC025

MAIN:

Hex Inverter

1

1A

2

1Y

3

2A

4

2Y

5

3A

6

3Y

7

Vss

MM74HC74ASJX (XY153A00)

MAIN: IC017, 022

Dual D-Type Flip-Flop

14

VDD

13

6A

12

6Y

11

5A

10

5Y

9

4A

8

4Y

(IC ブロック図)

MM74HC14SJX (XW104A00)

MAIN: IC019

Hex Inverter

1

1A

2

1Y

3

2A

4

2Y

5

3A

6

3Y

7

GND

TC74HC123AF (XN242A00)

MAIN: IC041

Dual Retriggerable Single Shot

14

VDD

13

6A

12

6Y

11

5A

10

5Y

9

4A

8

4Y

74VHC32SJX (XY306A00)

MAIN: IC003, 005

Quad 2 Input OR

1

GND

1A

1B

2

1Y

3

4

2A

5

2B

6

2Y

7

14

Vcc

4B

13

4A

12

11

4Y

10

3B

9

3A

8

3Y

TC74VHC138F (XT015A00)

MAIN: IC064, 065

3 to 8 Demultiplexer

1

1CLR

2

D

1D

3

1CK

1PR

GND

PR CLR CLK D Q Q

L

H

L

H

H

H

CK

4

PR

5

Q

1Q

6

Q

1Q

7

INPUTS OUTPUTS

X

H

X

L

X

L

f

H

f

H

L

H

14

VCC

13

CLR

X

X

X

H

L

X

2CLR

D

12

CLR

2D

11

CK

2CK

10

2PR

PR

9

Q

2Q

8

Q

2Q

H

L

L

H

H

H

H

L

L

H

O

O

Q

Q

MM74HC151SJX (XY308A00)

MAIN: IC026, 062, 063

8 to 1 Data Selector

Data

Inputs

Outputs

Strobe

GND

1

3

2

2

D2

3

1

D1

4

0

D0

5

Y

Y

6

W

W

7

S

8

16

D3

C

Vcc

15

4

D4

14

5

D5

D6

D7

A

B

Data

Inputs

13

6

12

7

11

A

Data

10

B

Select

9

C

1A

2 Cext

2 Rext / Cext

GND

1 16

2 15

1B

3 14

1

CLR

4 13

1Q

Q

5 12

2Q

Q

6 11

7 10

8 9

CLR

Vcc

1 Rext / Cext

Cext

Q

1Q

2Q

Q

CLR

2B

2A

TC74HC153AFEL (XY309A00)

MAIN: IC027

Dual 4 to 1 Data Selectors

1G SELECT

STROBE B

DATA

INPUTS

OUTPUT 1Y

GND

1

2

1G

3

IC3

4

IC2

5

IC1

B

IC0

6

B

A

7

1Y

A

8

16

Vcc

15

SELECT 2G

14

STROBE A

2G

13

2C3

12

2C2

B

2C1

B

A

2C0

A

2Y

11

10

9

OUTPUT 2Y

DATA

INPUTS

Enable

Output

Select

G2A

G2B

GND

1

A

2

B

3

C

4

5

6

G1

7

Y7

8

A

B

C

G2A

G2B

G1

Y7 Y5

Y6

16

Vcc

15

Y0

YO

14

Y1

Y1

13

Y2

Y2

12

Y3

11

Y4

10

9

Output

Y3

Y4

Y5

Y6

MM74HC157SJX (XY310A00)

MAIN: IC108, 109

Quad 2 to 1 Multiplexer

SELECT

GND

1

2

1A

1A

3

1B

1B

4

1Y

1Y

5

2A

2A

6

2B

2B

7

2Y

2Y

8

16

S3Y

Vcc

G

15

STROBE

4A

14

4A

4B

13

4B

4Y

12

4Y

3A

11

3A

3B

10

3B

9

3Y

18

Page 19

AFC1

MM74HC175SJX (XY307A00)

MAIN: IC024, 046-049

Quad D-Type Flip-Flop

Vss

1

CL

2

QCL

1Q

CK

QD

3

1Q

4

1D

5

2D

6

QD

2Q

CK

QCL

7

2Q

8

16

VDD

15

QCL

4Q

CK

QD

14

4Q

13

4D

12

3D

11

QD

3Q

CK

QCL

10

3Q

9

CK

TC74HC4052AF (XS790A00)

MAIN: IC044, 045

Differential 4-Channel

Multiplexer/Demultiplexer

Y-COM

INH

VEE

VSS

1

0Y

2

2Y

2Y

3

Y-COM

4

3Y

3Y

5

1Y

1Y

6

INH

7

8

0Y

X-COM

B

16

VDD

15

2X

2X

14

1X

1X

13

X-COM

12

0X

0X

11

3X

3X

10

A

A

B

9

TC74VHC245F (XT487A00)

IC029, 066, 067, 074, 075

MAIN:

MM74HC245ASJX (XW107A00)

IC030, 031, 052-061, 068-073

MAIN:

SN74ABT245BNSR (XU009A00)

IC050, 051

MAIN:

Octal 3-State Bus Transceiver

D1R

GND

1

2

A1

3

A2

4

A3

5

A4

6

A5

7

A6

8

A7

A8

9

10

20

Vcc

19

G

18

B1

17

B2

16

B3

15

B4

14

B5

13

B6

12

B7

11

B8

TC74LVX4245FS (XU229A00)

MAIN: IC111-117

Dual Supply Octal Bus Transceiver

1

VCCA

DIR

GND

GND

2

1

3

A1

2

4

A2

3

A3

5

4

6

A4

5

A5

7

6

8

7

A6

9

A7

8

10

9

A8

11

10 12

12

24

0

11

VCCB

23

VCCB

A

/G

22

B

B1

21

D

20

D

B2

19

G2

B3

18

G1

B4

15

17

B5

16

14

B6

15

13

B7

14

B8

13

GND

MM74HC273SJX (XY198A00)

MAIN: IC023

Octal D-Type Flir Flop

1 20

CLEAR

2 19

Q

1Q

3 18

DCK

1D

4 17

D

2D

5 16

Q

2Q

6 15

3Q

Q

7 14

DCK

3D

8 13

4D

D

9 12

Q

4Q

10 11

GND

CL

CL

CK

CL

CL

CL

CL

CK

CL

CL

VCC

8Q

Q

DCK

8D

7D

D

CK

Q

7Q

6Q

Q

DCK

6D

5D

D

CK

Q

5Q

CLOCK

SN75121NSR (XU816A00)

MAIN: IC036, 043

Dual Line Driver

16

Vcc

15

2F

14

2E

13

2D

12

2C

11

2B

10

2A

9

2Y

GND

1

1A

2

1B

3

1C

4

1D

5

1E

6

1F

7

1Y

8

SN75124NSR (XV930A00)

MAIN: IC039

Triple Line Receiver

1A

1 16

1B

2 15

2R

3 14

2S

4 13

2A

5 12

2B

6 11

2Y

7 10

GND

8 9

Vcc

1S

1R

1Y

3A

3S

3R

3Y

SN75C1168NSR (XU073A00)

MAIN: IC021, 037, 122

Line Driver / Receiver

1DE

GND

1

1B

2

1A

3

1R

4

5

2R

6

2A

7

2B

8

16

Vcc

15

1D

14

1Y

13

1Z

12

2DE

11

2Z

10

2Y

9

2D

AM26LS31CNSR (XU996A00)

MAIN: IC034, 035, 118, 119

Quad Line Driver

1A

1Y

1Z

ENABLE G

2Z

2Y

2A

GND

ENABLESINPUT

A

GGYZ

H

H

H

L

X

H

X

L

L

X

1

2

3

4

5

6

7

8

OUTPUTS

X

H

X

L

L

H

L

L

H

Z

16

Vcc

15

4A

14

4Y

13

4Z

12

ENABLE G

11

3Z

10

3Y

3A

9

L

H= high level

H

L= low level

L

X= irrelevant

H

Z= high impedance (off)

Z

19

Page 20

AFC1

DS26C32ATMX (XU815A00)

MAIN: IC032, 033, 120, 121

Quad Differential Line Receiver

INPUT A

INPUT A

OUTPUT A

ENABLE

OUTPUT C

INPUT C

INPUT C

GND

1

-

+

2

3

4

5

6

+

-

7

8

+

+

-

16

15

14

13

12

11

10

9

Vcc

INPUT B

INPUT B

OUTPUT B

ENABLE

OUTPUT D

INPUT D

INPUT D

NJM2082M(T1) (XN797A00)

MAIN: IC001

Dual Operational Amplifier

+-

+V

+DC Voltage

8

Supply

Output B

7

Inverting

6

Input B

Non-Inverting

5

Input B

Output A

Inverting

Input A

Non-Inverting

Input A

-DC Voltage Supply

1

2

3

4-V

+-

TC7S00F (XG150A00)

SUB: IC3

2 Input NAND

IN B

1 5

2

IN A

VSS

3

4

VDD

OUT Y

TC7S08F (XM616A00)

SUB: IC2

2 Input AND Gate

IN B

1 5

2

IN A

3

VSS

VDD

4

OUT

20

CIRCUIT BOARDS

CONTENTS

(目次)

(シート基板図)

MAIN Circuit Board (XW953D0)............................................... 22/24

SUB Circuit Board (X3791A0) ....................................................... 25

PNF (LED) Circuit Board (XY041B0)........................................ 26/27

PNF (PSW) Circuit Board (XY041B0) ............................................ 21

PNR (GPI) Circuit Board (XY231B0) ............................................. 21

PNR (MYMB) Circuit Board (XY231B0) ........................................ 26

Note: See parts list for details of circuit board component parts.

注:シートの部品詳細はパーツリストをご参照ください。

Page 21

PNR (GPI) Circuit Board

OUT/GND 1-8

IN/+V 1-8

OUT/GND 9-16

AFC1

to MAIN-CN010

IN/+V 9-16

Component side

to Power supply unit-CN3

(部品側)

PNF (PSW) Circuit Board

to AC inlet

Component side Pattern side

PNR (GPI): 2NAP-WB28680-2

PNF (PSW): 2NAP-WB28670-2

Pattern side

to Power supply unit-CN1

POWER

ON/ OFF

(パターン側)

(部品側) (パターン側)

21

Page 22

AFC1

E

• Lithium Battery(リチウム電池)

Battery VN103500

VN103600(Battery holder for VN103500)

Notice for back-up battery removal

Push the battery as shown in figure,

then the battery will pop up.

Druk de batterij naar beneden zoals

aangeven in de tekening de batterij

springt dan naar voren.

Battery

Battery holder

MAIN Circuit Board

CASCADE IN CASCADE OUT

A

S

OPEN

22

OPENOPENto PNF (LED)-CN401

A'

2NAP-WB41600-2

Page 23

A

SERVICE

FOR

USE

PC CONTROL

RS

422RS232C

MIDI

IN OUT

AFC1

WORD CLOCK

IN OUT

75

OFF • • ON

to Power supply unit-CN5

A'

2NAP-WB41600-2

to PNR (GPI)-CN701OPENOPENOPENOPEN

Component side(部品側)

to PNR (MYMB)-CN606

to PNR (MYMB)-CN608

to PNR (MYMB)-CN607

to PNR (MYMB)-CN605

23

Page 24

AFC1

MAIN Circuit Board

B

24

B'

2NAP-WB41600-3

Page 25

AFC1

B

B'

MAIN: 2NAP-WB41600-3

SUB: 2NAP-WA50300

Pattern side

(パターン側)

SUB Circuit Board

Component side

(部品側)

25

Page 26

AFC1

PNR (MYMB) Circuit Board

C

SLOT 1

SLOT 3

PNF (LED) Circuit Board

to MAIN-CN005

to Power supply unit-CN2

C'

D

D'

26

PATTERN LIVENESS

AA

Component side

AA ON

(部品側)

PNR (MYMB): 2NAP-WB28680-2

PNF (LED): 2NAP-WB28670-2

Page 27

AFC1

C

SLOT 2

to MAIN -CN011

to MAIN -CN013

to MAIN -CN014

C'

D

SLOT 4

C601

Component side

to MAIN -CN012

(部品側)

D'

PNR (MYMB): 2NAP-WB28680-2

PNF (LED): 2NAP-WB28670-2

PNF (LED) Circuit Board

Pattern side

(パターン側)

Pattern side

(パターン側)

27

Page 28

AFC1

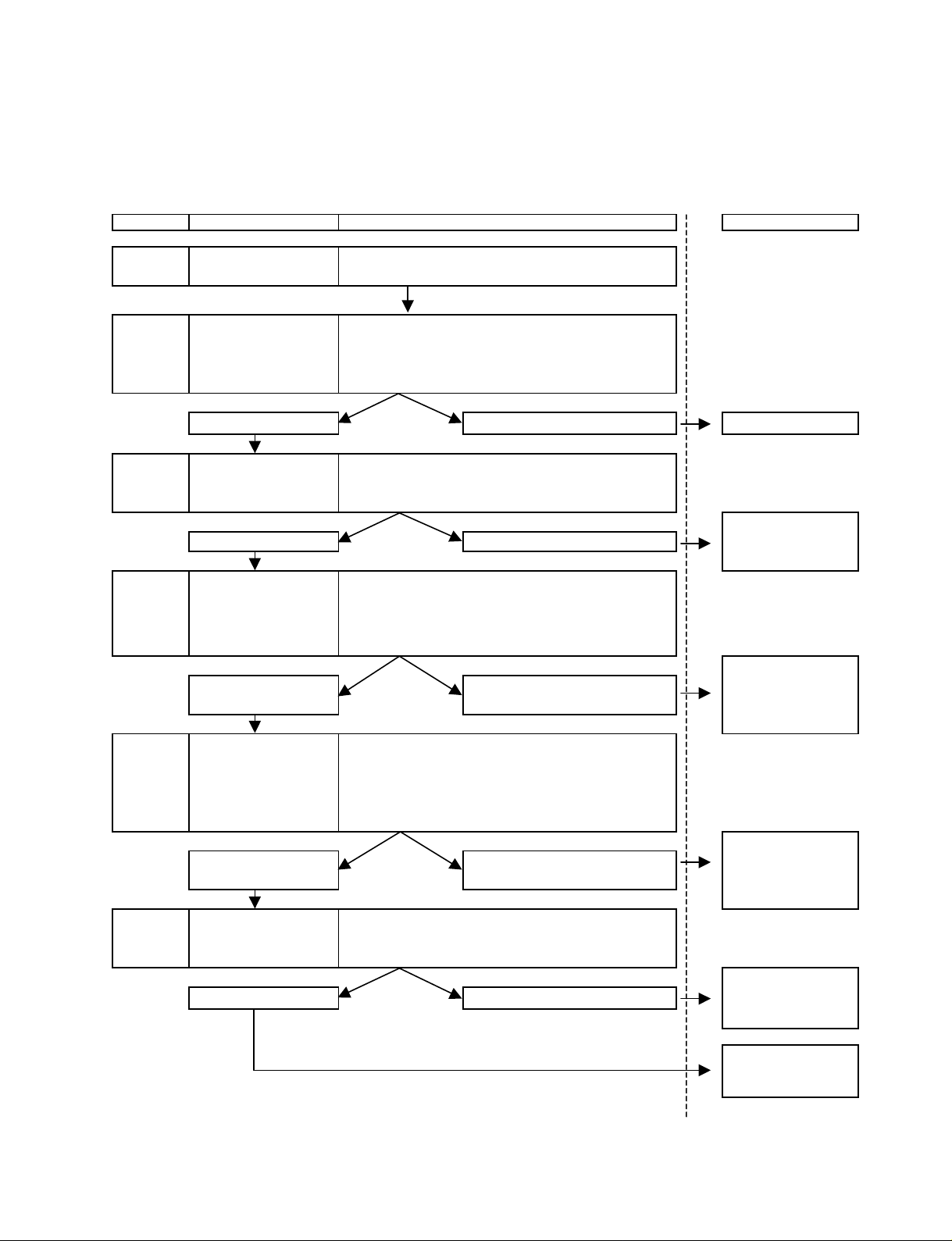

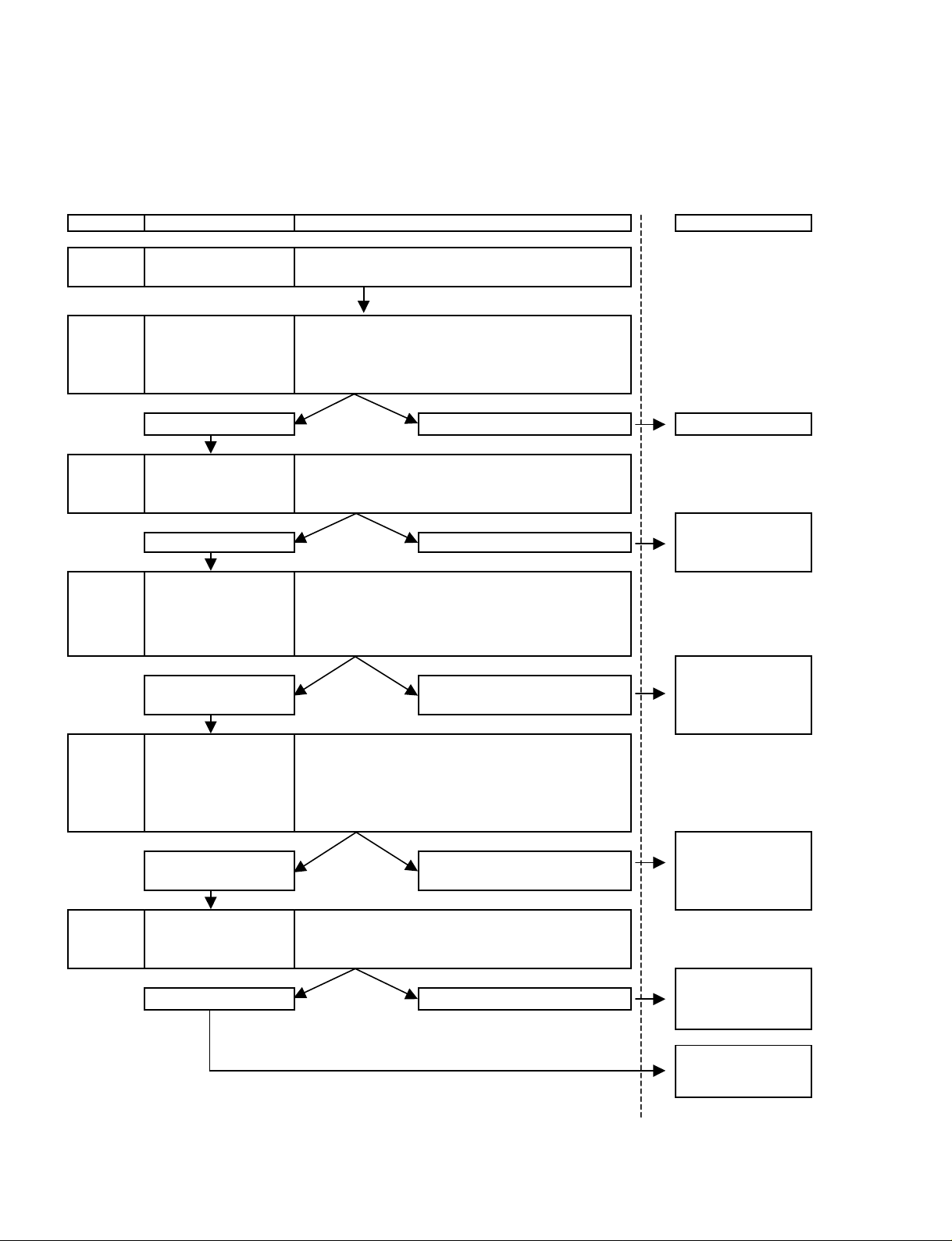

TEST PROGRAM AND INSPECTION

1. Preparation

1-1. Initial settings

• Connect the [CASCADE IN] ter minal and [CASCADE

OUT] terminal with a SCSI 50p cable.

• Connect the [PC CONTROL] terminal and PC (Windows

machine) serial terminal with a D-sub 9b cross cable.

• Connect the [MIDI IN] terminal and [MIDI OUT] terminal

with a MIDI cable.

• Connect the [WORD CLOCK IN] terminal and transmitter

output terminal with a BNC cable.

The transmitter source can be switched between 44.1

kHz and 48 kHz with a jitter of approximately 1nSec.

• Connect the [WORD CLOCK OUT] terminal and

frequency counter input terminal with BNC cable.

• Insert the slot inspection jig card (TX800810) in [SLOT 1

to 4].

(Connect a voltmeter to CN2 of the jig.)

• At 1 to 16 channels of the GPI ter minal, connect the

circuit GPI connect jig shown in the figure below.

Circuit diagram for GPI inspection jig

CH1(CH9):+V CH1(CH9):GND

CH1(CH9):IN

CH2(CH10):+V

CH2(CH10):IN

CH3(CH11):+V

CH3(CH11):IN

CH4(CH12):+V

CH4(CH12):IN

CH5(CH13):+V

CH5(CH13):IN

CH6(CH14):+V

CH6(CH14):IN

CH7(CH15):+V

CH7(CH15):IN

CH8(CH16):+V

V542290: Mini terminal block 16P MC310-50816

CH8(CH16):IN

1P

SW1

2P

SW2

3P

The same as the above

4P

5P

The same as the above

6P

7P

The same as the above

8P

9P

The same as the above

10P

11P

The same as the above

12P

13P

The same as the above

14P

15P

The same as the above

16P

10k

150

1P

2P

3P

4P

5P

6P

7P

8P

9P

10P

11P

12P

13P

14P

15P

16P

CH1(CH9):OUT

CH2(CH10):GND

CH2(CH10):OUT

CH3(CH11):GND

CH3(CH11):OUT

CH4(CH12):GND

CH4(CH12):OUT

CH5(CH13):GND

CH5(CH13):OUT

CH6(CH14):GND

CH6(CH14):OUT

CH7(CH15):GND

CH7(CH15):OUT

CH8(CH16):GND

CH8(CH16):OUT

1-2. Conditions

The following are the conditions unless otherwise specified.

• Each setting is performed by command inputs from the

terminal software in the PC by the (D-sub 9P) cable

connected to the [PC CONTROL] terminal.

• Set the [PC CONTROL] [RS232C/RS422] switch to

RS232C.

• Set [WORD CLOCK IN 75Ω] to on.

1-3. Structure of test program file, version manage-

ment and file structure

File structure

DME32Diag

cont.dll

DIAG.exe

CascadeCheck.dme

Note: Download the data file from YSISS website.

• DME32Diag

• cont.dll

1. Copy the test program to each DME32Diag holder and

PC C:¥Program Files.

2. DME Manager is installed. Copy cont.dll from

C:¥Program Files¥Dme to each of the DME32Diag

holders.

Note: cont.dll version

Make sure that the firmware written in the AFC1

to be detected and cont.dll in the PC are the

same version.

If cont.dll in a different version is used, the test

program will not operate properly.

2. Test program

2-1. Starting the test program

Click “DIA G.ex e” on the PC screen to start the test program.

Double click “DIAG.exe”.

V542290: Mini terminal block 16P MC310-50816

If inspecting the main sheet, click “Board Check”. For a

comprehensive inspection, click “Complete Check”.

2-2. Main Sheet Inspection

2-2-1.Selecting the main sheet inspection items

On the “Board Check” screen, click the check boxes for

the items to be inspected.

UsbDriver

DME32.inf

Xgusb.drv

Ymidusb.sys

28

Click the [START] button and the check box items that have been

selected will be executed in order starting from the top left.

Page 29

AFC1

Use the following buttons as needed.

Click [SELECT ALL] and all check boxes will be set to on.

Click [CLEAR ALL] and all check boxes will be set to off.

Click [EXIT] and program can be ended.

Click [PRINT] and results of the inspection will be printed.

There will be no explanation of these buttons after this.

2-2-2.Initial diagnosis

The results of the diagnosis is shown on the initial screen.

Click [NEXT] and check boxes are set to on and the inspection

goes to the next item.

Use the following buttons as needed.

Click [END] to end the test program. The screen returns

to the one shown in

“2-2-1 Selecting the main sheet

inspection items”.

Click [ABORT] to interrupt the diagnosis. The results of

the diagnosis will be NG (No Good).

There will be no explanation of these buttons after this.

Click [OK] and loop check is performed between [MIDI IN]

and [MIDI OUT]. The results of the diagnosis are displayed

on the MIDI screen.