XICOR X24320V14I, X24320V14-2,5, X24320V14-1,8, X24320V14, X24320S8I-2,5 Datasheet

...

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

32K |

|

|

X24320 |

|

|

|

|

|

|

|

4K x 8 Bit |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

400KHz 2-Wire Serial E2PROM with Block LockTM |

|

||||||||||||||||

|

FEATURES |

|

|

|

|

DESCRIPTION |

||||||||||||

|

• Save Critical Data with Programmable |

The X24320 is a CMOS Serial E2PROM, internally |

||||||||||||||||

|

Block Lock Protection |

|

|

|

|

organized 4K x 8. The device features a serial inter- |

||||||||||||

|

—Block Lock (0, 1/4, 1/2, or all of E2PROM Array) |

face and software protocol allowing operation on a |

||||||||||||||||

|

—Software Write Protection |

|

|

|

|

simple two wire bus. The bus operates at 400 KHz all |

||||||||||||

|

—Programmable Hardware Write Protect |

the way down to 1.8V. |

||||||||||||||||

|

• In Circuit Programmable ROM Mode |

Three device select inputs (S0–S2) allow up to eight |

||||||||||||||||

|

• 400KHz 2-Wire Serial Interface |

|||||||||||||||||

|

—Schmitt Trigger Input Noise Suppression |

devices to share a common two wire bus. |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

—Output Slope Control for Ground Bounce |

A Write Protect Register at the highest address loca- |

||||||||||||||||

|

Noise Elimination |

|

|

|

|

|||||||||||||

|

|

|

|

|

tion, FFFFh, provides three write protection features: |

|||||||||||||

|

• Longer Battery Life With Lower Power |

|||||||||||||||||

|

Software |

Write Protect, Block Lock Protect, and |

||||||||||||||||

|

—Active Read Current Less Than 1mA |

Programmable Hardware Write Protect. The Software |

||||||||||||||||

|

—Active Write Current Less Than 3mA |

|||||||||||||||||

|

Write Protect feature prevents any nonvolatile writes to |

|||||||||||||||||

|

—Standby Current Less Than 1 A |

|||||||||||||||||

|

the device until the WEL bit in the Write Protect |

|||||||||||||||||

|

• 1.8V to 3.6V, 2.5V to 5.5V and 4.5V to 5.5V |

|||||||||||||||||

|

Register |

is set. The Block Lock Protection feature |

||||||||||||||||

|

Power Supply Versions |

|

|

|

|

gives the user four array block protect options, set by |

||||||||||||

|

• 32 Word Page Write Mode |

|||||||||||||||||

|

programming two bits in the Write Protect Register. |

|||||||||||||||||

|

—Minimizes Total Write Time Per Word |

The Programmable Hardware Write Protect feature |

||||||||||||||||

|

• Internally Organized 4K x 8 |

|||||||||||||||||

|

allows the user to install the device with WP tied to |

|||||||||||||||||

|

• Bidirectional Data Transfer Protocol |

VCC, write to and Block Lock the desired portions of |

||||||||||||||||

|

• Self-Timed Write Cycle |

|

|

|

|

|||||||||||||

|

|

|

|

|

the memory array in circuit, and then enable the In |

|||||||||||||

|

—Typical Write Cycle Time of 5ms |

Circuit Programmable ROM Mode by programming the |

||||||||||||||||

|

• High Reliability |

|

|

|

|

|||||||||||||

|

|

|

|

|

WPEN bit HIGH in the Write Protect Register. After |

|||||||||||||

|

—Endurance: 100,000 Cycles |

this, the Block Locked portions of the array, including |

||||||||||||||||

|

—Data Retention: 100 Years |

|

|

|

|

|||||||||||||

|

|

|

|

|

the Write Protect Register itself, are permanently |

|||||||||||||

|

• 8-Lead SOIC |

|

|

|

|

|||||||||||||

|

|

|

|

|

protected from being erased. |

|||||||||||||

|

• 14-Lead TSSOP |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

• 8-Lead PDIP |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

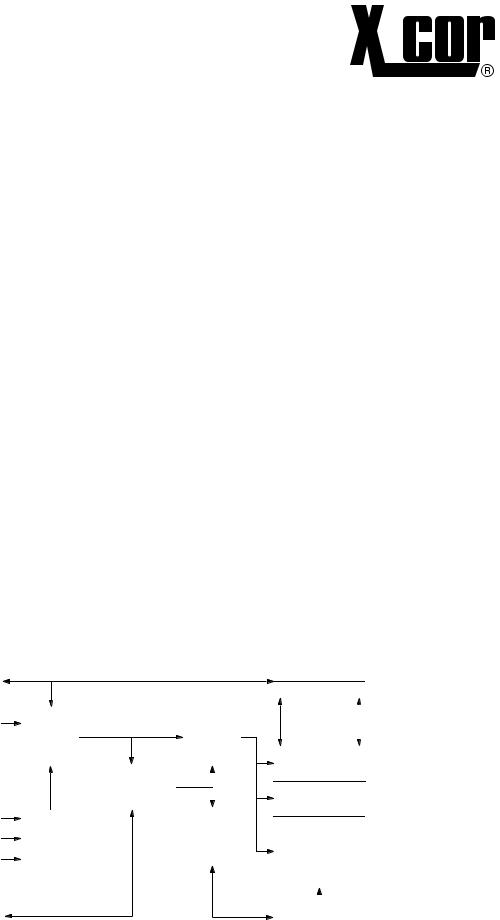

FUNCTIONAL DIAGRAM |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

SERIAL E2PROM DATA |

|

|

|

|

|

|

|

DATA REGISTER |

|

|

|

|

|

||||

|

AND ADDRESS (SDA) |

|

|

|

|

|

|

|

Y DECODE LOGIC |

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

SERIAL E2PROM |

|

|

|

|

|

|

|

|

|

SCL |

|

COMMAND |

|

|

|

|

|

|

|

|

|

||||||

|

|

DECODE |

|

|

|

PAGE |

|

ARRAY |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

AND |

|

|

|

DECODE |

|

4K x 8 |

|

|

|

||||||

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

CONTROL |

|

|

|

LOGIC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LOGIC |

|

|

|

|

|

|

1K x 8 |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

BLOCK LOCK AND |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

WRITE PROTECT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CONTROL LOGIC |

|

|

|

|

1K x 8 |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

S2 |

|

DEVICE |

|

|

|

WRITE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

S1 |

|

SELECT |

|

|

|

PROTECT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LOGIC |

|

|

|

REGISTER |

|

2K x 8 |

|

|

|||||||

|

S0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

WP |

|

|

|

|

|

|

|

WRITE VOLTAGE |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

CONTROL |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

7035 FM 01 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Xicor, 1995, 1996 Patents Pending |

1 |

|

|

|

|

|

Characteristics subject to change without notice |

||||||||||

|

7035-1.2 4/25/97 T0/C2/D0 SH |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

X24320

Xicor E2PROMs are designed and tested for applications requiring extended endurance. Inherent data retention is greater than 100 years.

PIN DESCRIPTIONS

Serial Clock (SCL)

The SCL input is used to clock all data into and out of the device.

Serial Data (SDA)

SDA is a bidirectional pin used to transfer data into and out of the device. It is an open drain output and may be wire-ORed with any number of open drain or open collector outputs.

An open drain output requires the use of a pull-up resistor. For selecting typical values, refer to the Pullup resistor selection graph at the end of this data sheet.

Device Select (S0, S1, S2)

The device select inputs (S0, S1, S2) are used to set the first three bits of the 8-bit slave address. This allows up to eight devices to share a common bus. These inputs can be static or actively driven. If used statically they must be tied to VSS or VCC as appropriate. If actively driven, they must be driven with CMOS levels (driven to VCC or VSS).

Write Protect (WP)

The Write Protect input controls the Hardware Write Protect feature. When held LOW, Hardware Write Protection is disabled. When this input is held HIGH, and the WPEN bit in the Write Protect Register is set HIGH, the Write Protect Register is protected, preventing changes to the Block Lock Protection and WPEN bits.

PIN NAMES

|

Symbol |

|

|

|

|

|

|

|

Description |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

S0, S1, S2 |

|

|

|

Device Select Inputs |

||||||||||||

|

SDA |

|

|

|

|

|

|

|

Serial Data |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SCL |

|

|

|

|

|

|

|

Serial Clock |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

WP |

|

|

|

|

|

|

|

Write Protect |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VSS |

|

|

|

|

|

|

|

Ground |

||||||||

|

VCC |

|

|

|

|

|

|

|

Supply Voltage |

||||||||

|

NC |

|

|

|

|

|

|

|

No Connect |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

7035 FM T01 |

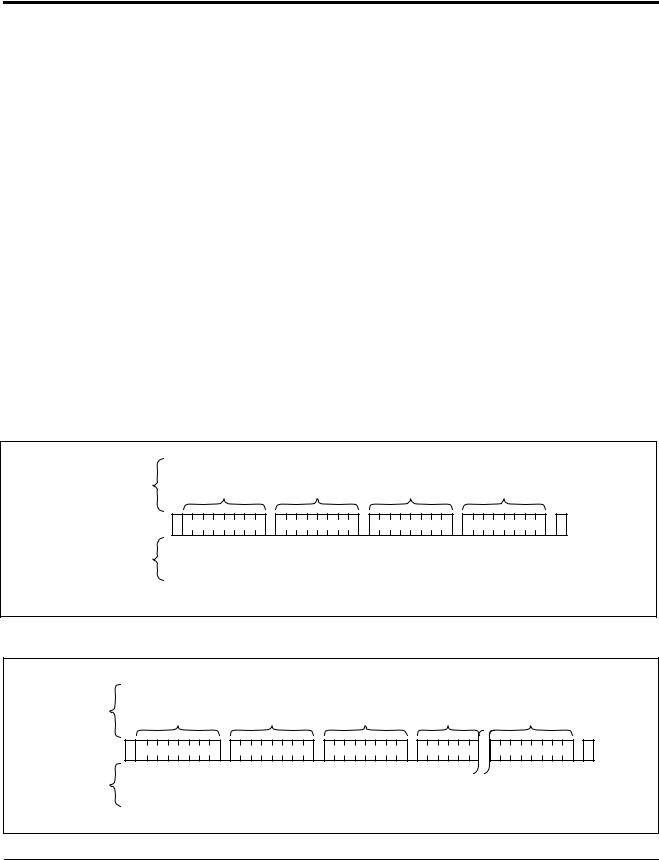

PIN CONFIGURATION |

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Not to scale |

|

|

|

|

|

|

|

|

8-Lead DIP/SOIC |

|

|

|

||||||

|

|

|

|

S0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

8 |

|

|

|

V |

|||||

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

S1 |

|

|

|

|

|

|

|

|

|

|

|

CC |

|

|

|

|

|

|

|

2 |

|

7 |

|

|

|

WP |

|||||

* .197” |

S2 |

|

|

|

|

X24320 |

|

|

|

|

|||||||

|

|

|

|

|

|

3 |

|

6 |

|

|

|

SCL |

|||||

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

VSS |

|

|

4 |

|

5 |

|

|

|

SDA |

||||

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

* .244” |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

14-Lead TSSOP |

|

|

|

||||||

|

|

|

|

S0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

14 |

|

|

|

V |

||||

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

S1 |

|

|

|

|

|

13 |

|

|

|

CC |

|||

|

|

|

|

|

|

|

2 |

|

|

|

|

WP |

|||||

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

NC |

|

|

|

3 |

|

12 |

|

|

|

NC |

|||

|

|

|

|

|

|

|

|

|

|

|

|||||||

.200” NC |

|

|

|

4 |

|

X24320 11 |

|

|

|

NC |

|||||||

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

NC |

5 |

|

10 |

|

|

|

NC |

||||||

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

S2 |

6 |

|

9 |

|

|

|

SCL |

||||||

|

|

|

|

VSS |

7 |

|

8 |

|

|

|

SDA |

||||||

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

.252” |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

* SOIC Measurement |

|

|

|

|

|

|

|

|

|

7035 FM 02 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2

X24320

DEVICE OPERATION

The device supports a bidirectional bus oriented protocol. The protocol defines any device that sends data onto the bus as a transmitter, and the receiving device as the receiver. The device controlling the transfer is a master and the device being controlled is the slave. The master will always initiate data transfers, and provide the clock for both transmit and receive operations. Therefore, the device will be considered a slave in all applications.

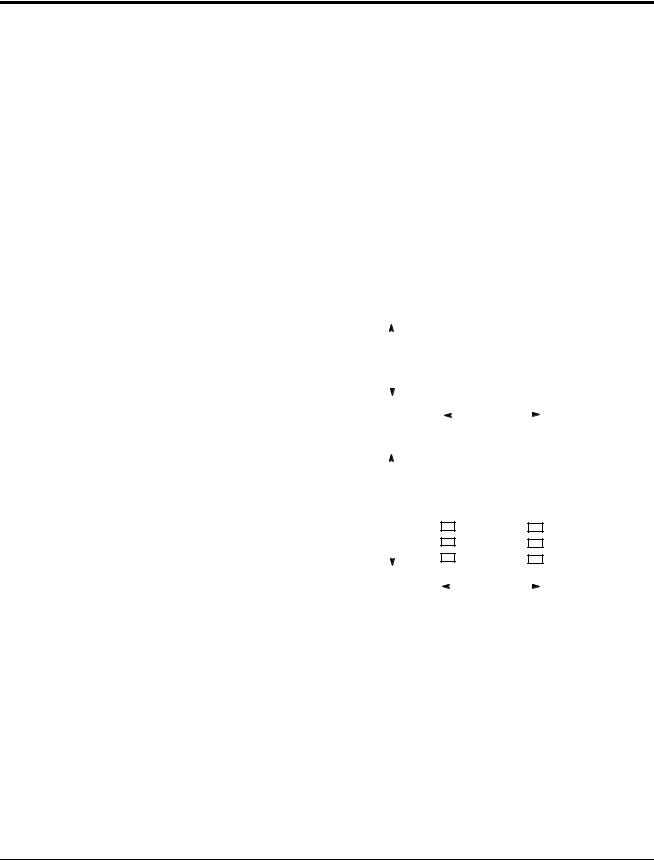

Figure 1. Data Validity

Clock and Data Conventions

Data states on the SDA line can change only during SCL LOW. SDA state changes during SCL HIGH are reserved for indicating start and stop conditions. Refer to Figures 1 and 2.

Start Condition

All commands are preceded by the start condition, which is a HIGH to LOW transition of SDA when SCL is HIGH. The device continuously monitors the SDA and SCL lines for the start condition and will not respond to any command until this condition has been met.

SCL

SDA

DATA STABLE DATA

CHANGE |

7035 FM 03 |

Figure 2. Definition of Start and Stop

SCL

SDA

START BIT |

STOP BIT |

7035 FM 04 |

3

X24320

Stop Condition

All communications must be terminated by a stop condition, which is a LOW to HIGH transition of SDA when SCL is HIGH. The stop condition is also used to place the device into the standby power mode after a read sequence. A stop condition can only be issued after the transmitting device has released the bus.

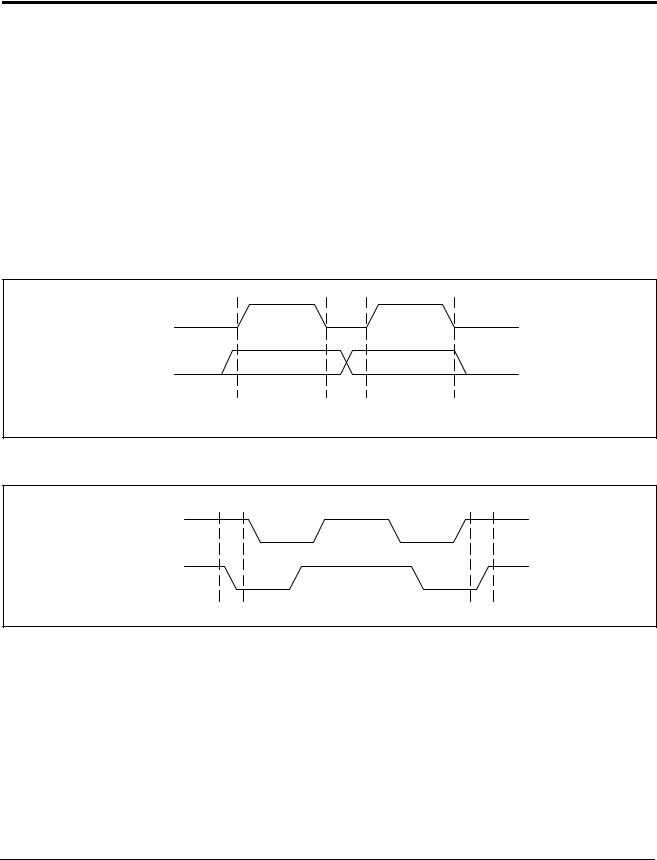

Acknowledge

Acknowledge is a software convention used to indicate successful data transfer. The transmitting device, either master or slave, will release the bus after transmitting eight bits. During the ninth clock cycle the receiver will pull the SDA line LOW to acknowledge that it received the eight bits of data. Refer to Figure 3.

Figure 3. Acknowledge Response From Receiver

The device will respond with an acknowledge after recognition of a start condition and its slave address. If both the device and a write operation have been selected, the device will respond with an acknowledge after the receipt of each subsequent 8-bit word.

In the read mode the device will transmit eight bits of data, release the SDA line and monitor the line for an acknowledge. If an acknowledge is detected and no stop condition is generated by the master, the device will continue to transmit data. If an acknowledge is not detected, the device will terminate further data transmissions. The master must then issue a stop condition to return the device to the standby power mode and place the device into a known state.

SCL FROM |

|

|

|

MASTER |

1 |

8 |

9 |

DATA OUTPUT

FROM

TRANSMITTER

DATA

OUTPUT

FROM

RECEIVER

START |

ACKNOWLEDGE |

7035 FM 05

4

X24320

DEVICE ADDRESSING

Following a start condition, the master must output the address of the slave it is accessing. The first four bits of the Slave Address Byte are the device type identifier bits. These must equal “1010”The. next 3 bits are the device select bits S0, S1, and S2. This allows up to 8 devices to share a single bus. These bits are compared to the S0, S1, and S2 device select input pins. The last bit of the Slave Address Byte defines the operation to be performed. When the R/W bit is a one, then a read operation is selected. When it is zero then a write operation is selected. Refer to figure 4. After loading the Slave Address Byte from the SDA bus, the device compares the device type bits with the value “1010”and the device select bits with the status of the

Figure 4. Device Addressing

device select input pins. If the compare is not successful, no acknowledge is output during the ninth clock cycle and the device returns to the standby mode.

The word address is either supplied by the master or obtained from an internal counter, depending on the operation. The master must supply the two Word Address Bytes as shown in figure 4.

The internal organization of the E2 array is 128 pages by 32 bytes per page. The page address is partially contained in the Word Address Byte 1 and partially in bits 7 through 5 of the Word Address Byte 0. The byte address is contained in bits 4 through 0 of the Word Address Byte 0. See figure 4.

|

|

DEVICE TYPE |

|

|

|

|

|

|

|

|

|

DEVICE |

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

|

|

IDENTIFIER |

|

|

|

|

|

|

|

|

|

SELECT |

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

0 |

|

|

|

|

|

1 |

|

|

|

0 |

|

|

|

|

|

S2 |

|

|

S1 |

|

|

|

|

|

S0 |

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||

R/W |

|

|

||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

SLAVE ADDRESS BYTE |

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

HIGH ORDER WORD ADDRESS |

|||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

0 |

|

|

|

0 |

|

|

|

0 |

|

|

|

|

A11 |

|

|

A10 |

|

|

|

A9 |

|

|

A8 |

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X24320 WORD ADDRESS BYTE 1 |

|

|

|

|

|

|||||||||||||||||||||||||||||||||

|

|

|

|

|

|

LOW ORDER WORD ADDRESS |

|

|

|

|

|

|||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A4 |

|

|

|

|

A3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

A7 |

|

|

|

|

A6 |

|

|

|

|

|

A5 |

|

|

|

|

|

|

|

A2 |

A1 |

A0 |

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

WORD ADDRESS BYTE 0 |

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||

D7 |

|

D6 |

D5 |

|

D4 |

|

D3 |

|

D2 |

|

D1 |

|

D0 |

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DATA BYTE

7035 FM 06

5

X24320

WRITE OPERATIONS

Byte Write

For a write operation, the device requires the Slave Address Byte, the Word Address Byte 1, and the Word Address Byte 0, which gives the master access to any one of the words in the array. Upon receipt of the Word Address Byte 0, the device responds with an acknowledge, and waits for the first eight bits of data. After receiving the 8 bits of the data byte, the device again responds with an acknowledge. The master then terminates the transfer by generating a stop condition, at which time the device begins the internal write cycle to the nonvolatile memory. While the internal write cycle is in progress the device inputs are disabled and the device will not respond to any requests from the master. The SDA pin is at high impedance. See figure 5.

Page Write

The device is capable of a thirty-two byte page write operation. It is initiated in the same manner as the byte write operation; but instead of terminating the write operation after the first data word is transferred, the

master can transmit up to thirty-one more words. The device will respond with an acknowledge after the receipt of each word, and then the byte address is internally incremented by one. The page address remains constant. When the counter reaches the end of the page, it “rolls ver”o and goes back to the first byte of the current page. This means that the master can write 32 words to the page beginning at any byte. If the master begins writing at byte 16, and loads 32 words, then the first 16 words are written to bytes 16 through 31, and the last 16 words are written to bytes 0 through 15. Afterwards, the address counter would point to byte 16. If the master writes more than 32 words, then the previously loaded data is overwritten by the new data, one byte at a time.

The master terminates the data byte loading by issuing a stop condition, which causes the device to begin the nonvolatile write cycle. As with the byte write operation, all inputs are disabled until completion of the internal write cycle. Refer to figure 6 for the address, acknowledge, and data transfer sequence.

Figure 5. Byte Write Sequence

SIGNALS |

S |

|

|

|

|

|

S |

T |

SLAVE |

WORD ADDRESS |

|

WORD ADDRESS |

|

||

FROM THE |

A |

|

|

T |

|||

ADDRESS |

BYTE 1 |

|

BYTE 0 |

DATA |

|||

MASTER |

R |

|

O |

||||

|

|

|

|

|

|||

|

T |

|

|

|

|

|

P |

SDA BUS |

S 1 0 1 0 |

0 |

|

|

|

P |

|

SIGNALS |

|

|

A |

A |

A |

|

A |

|

|

C |

C |

C |

|

C |

|

FROM THE |

|

|

|

||||

|

|

K |

K |

K |

|

K |

|

SLAVE |

|

|

|

||||

|

|

|

|

|

|

|

|

7035 FM 07

Figure 6. Page Write Sequence

|

|

|

|

|

|

|

(0≤n≤31) |

|

SIGNALS |

S |

|

|

|

|

|

|

|

T |

SLAVE |

|

WORD ADDRESS |

WORD ADDRESS |

DATA |

DATA |

S |

|

FROM THE |

A |

ADDRESS |

|

BYTE 1 |

BYTE 0 |

(0) |

(n) |

T |

MASTER |

R |

|

|

|

|

|

|

O |

|

T |

|

|

|

|

|

|

P |

SDA BUS |

S 1 0 1 0 |

0 |

|

|

|

|

P |

|

SIGNALS |

|

|

A |

A |

A |

A |

|

A |

|

|

C |

C |

C |

C |

|

C |

|

FROM THE |

|

|

|

|||||

|

|

K |

K |

K |

K |

|

K |

|

SLAVE |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

7035 FM 08

6

Loading...

Loading...