White Electronic Designs WEDPN16M64VR-66BM, WEDPN16M64VR-66BC, WEDPN16M64VR-133BM, WEDPN16M64VR-133BI, WEDPN16M64VR-133BC Datasheet

...

White Electronic Designs Corporation (602) 437-1520 www.whiteedc.com

HI-RELIABILITY PRODUCT

WEDPN16M64VR-XBX

Sept. 2001 Rev. 1

GENERAL DESCRIPTION

The 128MByte (1Gb) SDRAM is a high-speed CMOS, dynamic

random-access, memory using 4 chips containing 268,435,456

bits. Each chip is internally configured as a quad-bank DRAM with

a synchronous interface. Each of the chips 67,108,864-bit banks

is organized as 8,192 rows by 512 columns by 16 bits. The MCP

also incorporates two 16-bit universal bus drivers for input control

signals and addresses.

Read and write accesses to the SDRAM are burst oriented;

accesses start at a selected location and continue for a programmed number of locations in a programmed sequence.

Accesses begin with the registration of an ACTIVE command,

which is then followed by a READ or WRITE command. The

address bits registered coincident with the ACTIVE command are

used to select the bank and row to be accessed (BA

0, BA1 select

the bank; A0-12 select the row). The address bits registered

coincident with the READ or WRITE command are used to select

the starting column location for the burst access.

The SDRAM provides for programmable READ or WRITE burst

lengths of 1, 2, 4 or 8 locations, or the full page, with a burst terminate

option. An AUTO PRECHARGE function may be enabled to provide

a self-timed row precharge that is initiated at the end of the burst

sequence.

The 1Gb SDRAM uses an internal pipelined architecture to achieve

high-speed operation. This architecture is compatible with the 2n rule

of prefetch architectures, but it also allows the column address to be

changed on every clock cycle to achieve a high-speed, fully random

access. Precharging one bank while accessing one of the other three

banks will hide the precharge cycles and provide seamless, highspeed, random-access operation.

The 1Gb SDRAM is designed to operate in 3.3V, low-power memory

systems. An auto refresh mode is provided, along with a powersaving, power-down mode.

All inputs and outputs are LVTTL compatible. SDRAMs offer substantial advances in DRAM operating performance, including the ability to

synchronously burst data at a high data rate with automatic columnaddress generation, the ability to interleave between internal banks

in order to hide precharge time and the capability to randomly change

column addresses on each clock cycle during a burst access.

16Mx64 Registered Synchronous DRAM *ADVANCED

FEATURES

n Registered for enhanced performace of bus speeds

66 MHz - 133 MHz Commercial, Industrial Temperature Only

66 MHz - 125 MHz Military Temperature Only

n Package:

219 Plastic Ball Grid Array (PBGA), 32 x 25mm

n Single 3.3V ±0.3V power supply

n Fully Synchronous; all signals registered on positive edge of

system clock cycle

n Internal pipelined operation; column address can be changed

every clock cycle

n Internal banks for hiding row access/precharge

n Programmable Burst length 1,2,4,8 or full page

n 8192 refresh cycles

n Commercial, Industrial and Military Temperature Ranges

n Organized as 16M x 64

n Weight: WEDPN16M64VR-XBX - 2.5 grams typical

BENEFITS

n 37% SPACE SAVINGS

n 17% I/O Reduction

n Reduced part count

n Reduced trace lengths for lower parasitic capacitance

n Glue-less connection to memory controller/PCI Bridge

n Suitable for hi-reliability applications

n Laminate interposer for optimum TCE match

n Upgradeable to 32M x 64 density (contact factory for information)

*This data sheet describes a product under development, non-qualified, not fully

characterized, and is subject to change without notice.

2

White Electronic Designs Corporation (602) 437-1520 www.whiteedc.com

WEDPN16M64VR-XBX

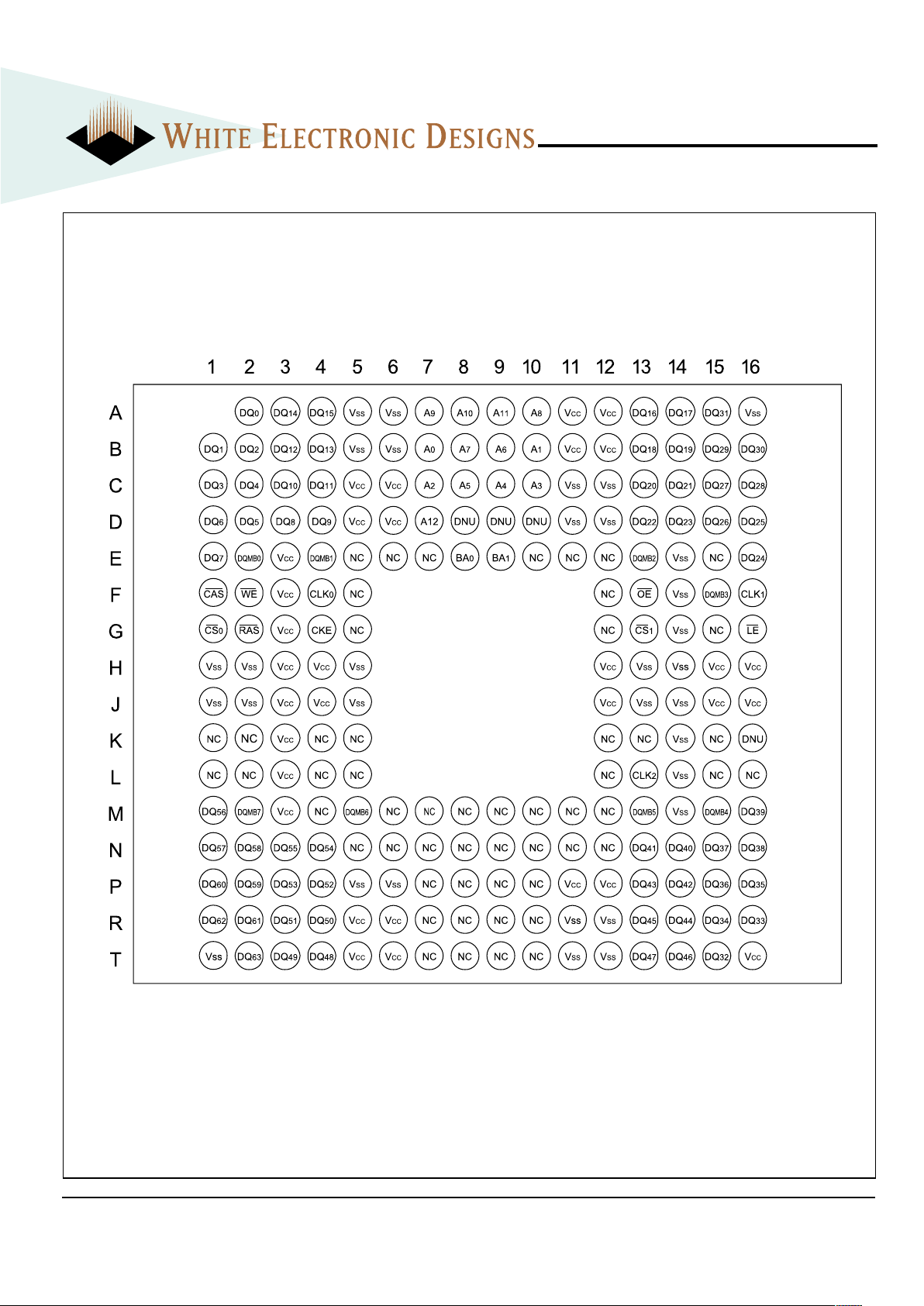

FIG. 1 PIN CONFIGURATION

NOTE: DNU = Do Not Use; to be left unconnected for future upgrades.

NC = Not Connected Internally.

TOP VIEW

3

White Electronic Designs Corporation (602) 437-1520 www.whiteedc.com

WEDPN16M64VR-XBX

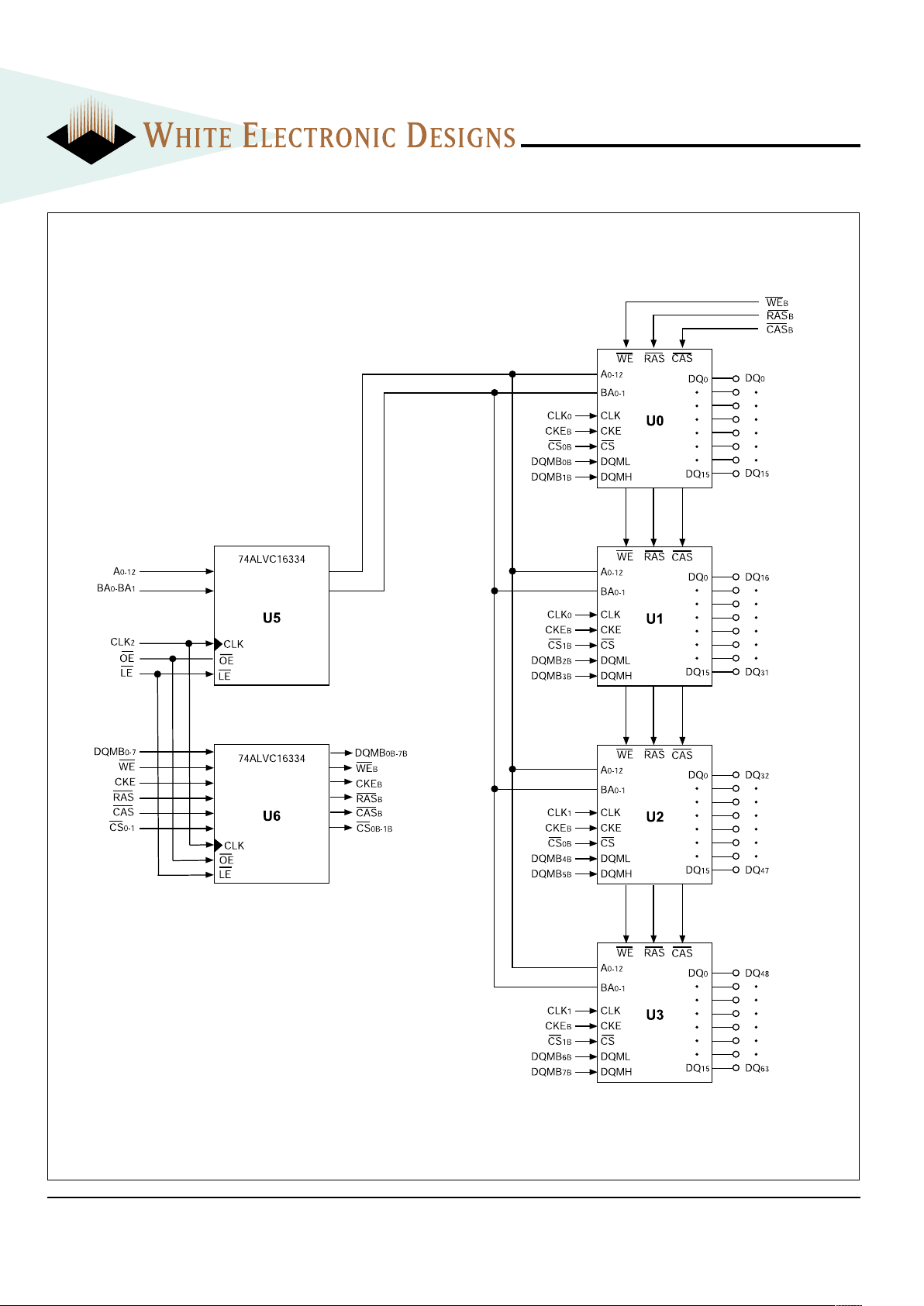

FIG. 2 FUNCTIONAL BLOCK DIAGRAM

4

White Electronic Designs Corporation (602) 437-1520 www.whiteedc.com

WEDPN16M64VR-XBX

FUNCTIONAL DESCRIPTION

Read and write accesses to the SDRAM are burst oriented;

accesses start at a selected location and continue for a programmed number of locations in a programmed sequence. Accesses begin with the registration of an ACTIVE command which

is then followed by a READ or WRITE command. The address bits

registered coincident with the ACTIVE command are used to

select the bank and row to be accessed (BA

0 and BA1 select the

bank, A

0-12 select the row). The address bits (A0-8) registered

coincident with the READ or WRITE command are used to select

the starting column location for the burst access.

Prior to normal operation, the SDRAM must be initialized. The

following sections provide detailed information covering device

initialization, register definition, command descriptions and device operation.

INITIALIZATION

SDRAMs must be powered up and initialized in a predefined

manner. Operational procedures other than those specified may

result in undefined operation. Once power is applied to V

DD and

V

DDQ (simultaneously) and the clock is stable (stable clock is

defined as a signal cycling within timing constraints specified for

the clock pin), the SDRAM requires a 100µs delay prior to issuing

any command other than a COMMAND INHIBIT or a NOP. Starting

at some point during this 100µs period and continuing at least

through the end of this period, COMMAND INHIBIT or NOP

commands should be applied.

Once the 100µs delay has been satisfied with at least one COMMAND INHIBIT or NOP command having been applied, a PRECHARGE

command should be applied. All banks must be precharged,

thereby placing the device in the all banks idle state.

Once in the idle state, two AUTO REFRESH cycles must be performed. After the AUTO REFRESH cycles are complete, the SDRAM

is ready for Mode Register programming. Because the Mode

Register will power up in an unknown state, it should be loaded

prior to applying any operational command.

REGISTER DEFINITION

MODE REGISTER

The Mode Register is used to define the specific mode of operation of the SDRAM. This definition includes the selec-tion of a

burst length, a burst type, a CAS latency, an operating mode and

a write burst mode, as shown in Figure 3. The Mode Register is

programmed via the LOAD MODE REGISTER command and will

retain the stored information until it is programmed again or the

device loses power.

Mode register bits M0-M2 specify the burst length, M3 specifies

the type of burst (sequential or interleaved), M4-M6 specify the

CAS latency, M7 and M8 specify the operating mode, M9 specifies the WRITE burst mode, and M10 and M11 are reserved for

future use. Address A12 (M12) is undefined but should be driven

LOW during loading of the mode register.

The Mode Register must be loaded when all banks are idle, and the

controller must wait the specified time before initiating the subsequent

operation. Violating either of these requirements will result in unspecified operation.

Burst Length

Read and write accesses to the SDRAM are burst oriented, with the

burst length being programmable, as shown in Figure 3. The burst

length determines the maximum number of column locations that can

be accessed for a given READ or WRITE command. Burst lengths

of 1, 2, 4 or 8 locations are available for both the sequential and the

interleaved burst types, and a full-page burst is available for the

sequential type. The full-page burst is used in conjunction with the

BURST TERMINATE command to generate arbitrary burst lengths.

Reserved states should not be used, as unknown operation or

incompatibility with future versions may result.

When a READ or WRITE command is issued, a block of columns

equal to the burst length is effectively selected. All accesses for

that burst take place within this block, meaning that the burst will

wrap within the block if a boundary is reached. The block is

uniquely selected by A

1-8 when the burst length is set to two; by

A

2-8 when the burst length is set to four; and by A3-8 when the

burst length is set to eight. The remaining (least significant)

address bit(s) is (are) used to select the starting location within

the block. Full-page bursts wrap within the page if the boundary

is reached.

Burst Type

Accesses within a given burst may be programmed to be either

sequential or interleaved; this is referred to as the burst type and

is selected via bit M3.

The ordering of accesses within a burst is determined by the burst

length, the burst type and the starting column address, as shown

in Table 1.

Loading...

Loading...