Page 1

TMS320DM643x DMP

Ethernet Media Access Controller (EMAC)/

Management Data Input/Output (MDIO)

Module

User's Guide

Literature Number: SPRU941A

April 2007

Page 2

2 SPRU941A – April 2007

Submit Documentation Feedback

Page 3

Contents

Preface .............................................................................................................................. 10

1 Introduction .............................................................................................................. 11

1.1 Purpose of the Peripheral ..................................................................................... 11

1.2 Features ......................................................................................................... 11

1.3 Functional Block Diagram ..................................................................................... 12

1.4 Industry Standard(s) Compliance Statement ............................................................... 13

2 Peripheral Architecture .............................................................................................. 13

2.1 Clock Control .................................................................................................... 13

2.2 Memory Map .................................................................................................... 13

2.3 Signal Descriptions ............................................................................................. 13

2.4 Ethernet Protocol Overview ................................................................................... 15

2.5 Programming Interface ......................................................................................... 16

2.6 EMAC Control Module ......................................................................................... 27

2.7 MDIO Module ................................................................................................... 28

2.8 EMAC Module ................................................................................................... 33

2.9 Media Independent Interface (MII) ........................................................................... 35

2.10 Packet Receive Operation ..................................................................................... 39

2.11 Packet Transmit Operation .................................................................................... 44

2.12 Receive and Transmit Latency ............................................................................... 44

2.13 Transfer Node Priority .......................................................................................... 45

2.14 Reset Considerations .......................................................................................... 45

2.15 Initialization ...................................................................................................... 46

2.16 Interrupt Support ................................................................................................ 49

2.17 Power Management ............................................................................................ 52

2.18 Emulation Considerations ..................................................................................... 52

3 EMAC Control Module Registers ................................................................................. 53

3.1 EMAC Control Module Interrupt Control Register (EWCTL) .............................................. 53

3.2 EMAC Control Module Interrupt Timer Count Register (EWINTTCNT) ................................. 54

4 MDIO Registers ......................................................................................................... 55

4.1 MDIO Version Register (VERSION) ......................................................................... 55

4.2 MDIO Control Register (CONTROL) ......................................................................... 56

4.3 PHY Acknowledge Status Register (ALIVE) ................................................................ 57

4.4 PHY Link Status Register (LINK) ............................................................................. 57

4.5 MDIO Link Status Change Interrupt (Unmasked) Register (LINKINTRAW) ............................ 58

4.6 MDIO Link Status Change Interrupt (Masked) Register (LINKINTMASKED) .......................... 59

4.7 MDIO User Command Complete Interrupt (Unmasked) Register (USERINTRAW) ................... 60

4.8 MDIO User Command Complete Interrupt (Masked) Register (USERINTMASKED) ................. 61

4.9 MDIO User Command Complete Interrupt Mask Set Register (USERINTMASKSET) ................ 62

4.10 MDIO User Command Complete Interrupt Mask Clear Register (USERINTMASKCLEAR) .......... 63

4.11 MDIO User Access Register 0 (USERACCESS0) ......................................................... 64

4.12 MDIO User PHY Select Register 0 (USERPHYSEL0) .................................................... 65

4.13 MDIO User Access Register 1 (USERACCESS1) ......................................................... 66

4.14 MDIO User PHY Select Register 1 (USERPHYSEL1) .................................................... 67

5 Ethernet Media Access Controller (EMAC) Registers ..................................................... 68

SPRU941A – April 2007 Table of Contents 3

Submit Documentation Feedback

Page 4

5.1 Transmit Identification and Version Register (TXIDVER) ................................................. 71

5.2 Transmit Control Register (TXCONTROL) .................................................................. 71

5.3 Transmit Teardown Register (TXTEARDOWN) ............................................................ 72

5.4 Receive Identification and Version Register (RXIDVER) .................................................. 73

5.5 Receive Control Register (RXCONTROL) .................................................................. 73

5.6 Receive Teardown Register (RXTEARDOWN) ............................................................. 74

5.7 Transmit Interrupt Status (Unmasked) Register (TXINTSTATRAW) .................................... 75

5.8 Transmit Interrupt Status (Masked) Register (TXINTSTATMASKED) ................................... 76

5.9 Transmit Interrupt Mask Set Register (TXINTMASKSET) ................................................ 77

5.10 Transmit Interrupt Mask Clear Register (TXINTMASKCLEAR) .......................................... 78

5.11 MAC Input Vector Register (MACINVECTOR) ............................................................. 79

5.12 Receive Interrupt Status (Unmasked) Register (RXINTSTATRAW) ..................................... 80

5.13 Receive Interrupt Status (Masked) Register (RXINTSTATMASKED) ................................... 81

5.14 Receive Interrupt Mask Set Register (RXINTMASKSET) ................................................. 82

5.15 Receive Interrupt Mask Clear Register (RXINTMASKCLEAR) ........................................... 83

5.16 MAC Interrupt Status (Unmasked) Register (MACINTSTATRAW) ...................................... 84

5.17 MAC Interrupt Status (Masked) Register (MACINTSTATMASKED) ..................................... 84

5.18 MAC Interrupt Mask Set Register (MACINTMASKSET) .................................................. 85

5.19 MAC Interrupt Mask Clear Register (MACINTMASKCLEAR) ............................................ 85

5.20 Receive Multicast/Broadcast/Promiscuous Channel Enable Register (RXMBPENABLE) ............ 86

5.21 Receive Unicast Enable Set Register (RXUNICASTSET) ................................................ 89

5.22 Receive Unicast Clear Register (RXUNICASTCLEAR) ................................................... 90

5.23 Receive Maximum Length Register (RXMAXLEN) ........................................................ 91

5.24 Receive Buffer Offset Register (RXBUFFEROFFSET) .................................................... 91

5.25 Receive Filter Low Priority Frame Threshold Register (RXFILTERLOWTHRESH) ................... 92

5.26 Receive Channel 0-7 Flow Control Threshold Register (RX nFLOWTHRESH) ........................ 92

5.27 Receive Channel 0-7 Free Buffer Count Register (RX nFREEBUFFER) ................................ 93

5.28 MAC Control Register (MACCONTROL) .................................................................... 94

5.29 MAC Status Register (MACSTATUS)........................................................................ 96

5.30 Emulation Control Register (EMCONTROL) ................................................................ 98

5.31 FIFO Control Register (FIFOCONTROL) .................................................................... 98

5.32 MAC Configuration Register (MACCONFIG) ............................................................... 99

5.33 Soft Reset Register (SOFTRESET) .......................................................................... 99

5.34 MAC Source Address Low Bytes Register (MACSRCADDRLO) ....................................... 100

5.35 MAC Source Address High Bytes Register (MACSRCADDRHI) ....................................... 100

5.36 MAC Hash Address Register 1 (MACHASH1) ............................................................ 101

5.37 MAC Hash Address Register 2 (MACHASH2) ............................................................ 101

5.38 Back Off Test Register (BOFFTEST) ....................................................................... 102

5.39 Transmit Pacing Algorithm Test Register (TPACETEST) ............................................... 102

5.40 Receive Pause Timer Register (RXPAUSE) .............................................................. 103

5.41 Transmit Pause Timer Register (TXPAUSE) .............................................................. 103

5.42 MAC Address Low Bytes Register (MACADDRLO) ...................................................... 104

5.43 MAC Address High Bytes Register (MACADDRHI) ...................................................... 104

5.44 MAC Index Register (MACINDEX) ......................................................................... 105

5.45 Transmit Channel 0-7 DMA Head Descriptor Pointer Register (TX nHDP) ............................ 106

5.46 Receive Channel 0-7 DMA Head Descriptor Pointer Register (RX nHDP) ............................ 106

5.47 Transmit Channel 0-7 Completion Pointer Register (TX nCP) ........................................... 107

5.48 Receive Channel 0-7 Completion Pointer Register (RX nCP) ........................................... 107

5.49 Network Statistics Registers ................................................................................. 108

4 Contents SPRU941A – April 2007

Submit Documentation Feedback

Page 5

Appendix A Glossary ...................................................................................................... 117

Appendix B Revision History ............................................................................................ 119

SPRU941A – April 2007 Contents 5

Submit Documentation Feedback

Page 6

List of Figures

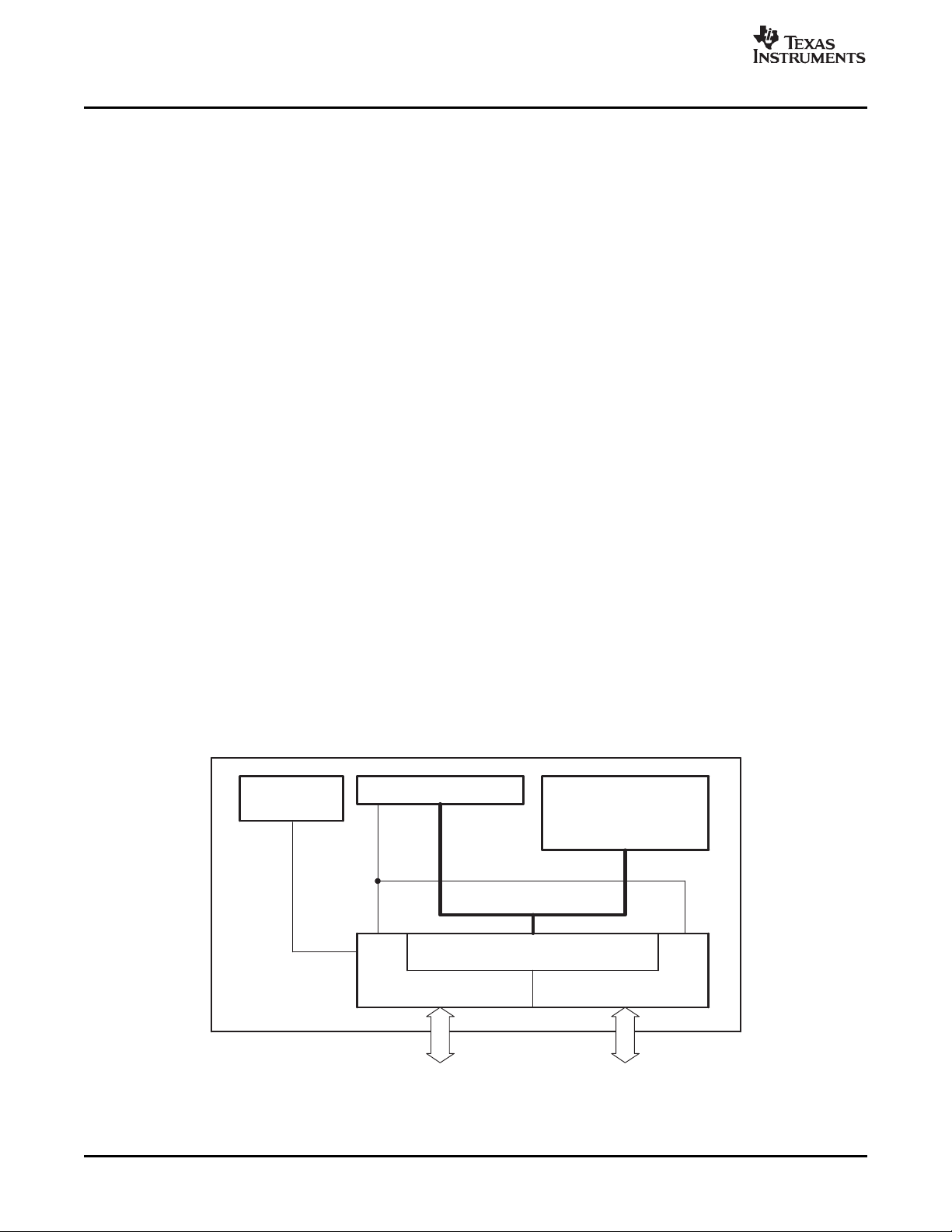

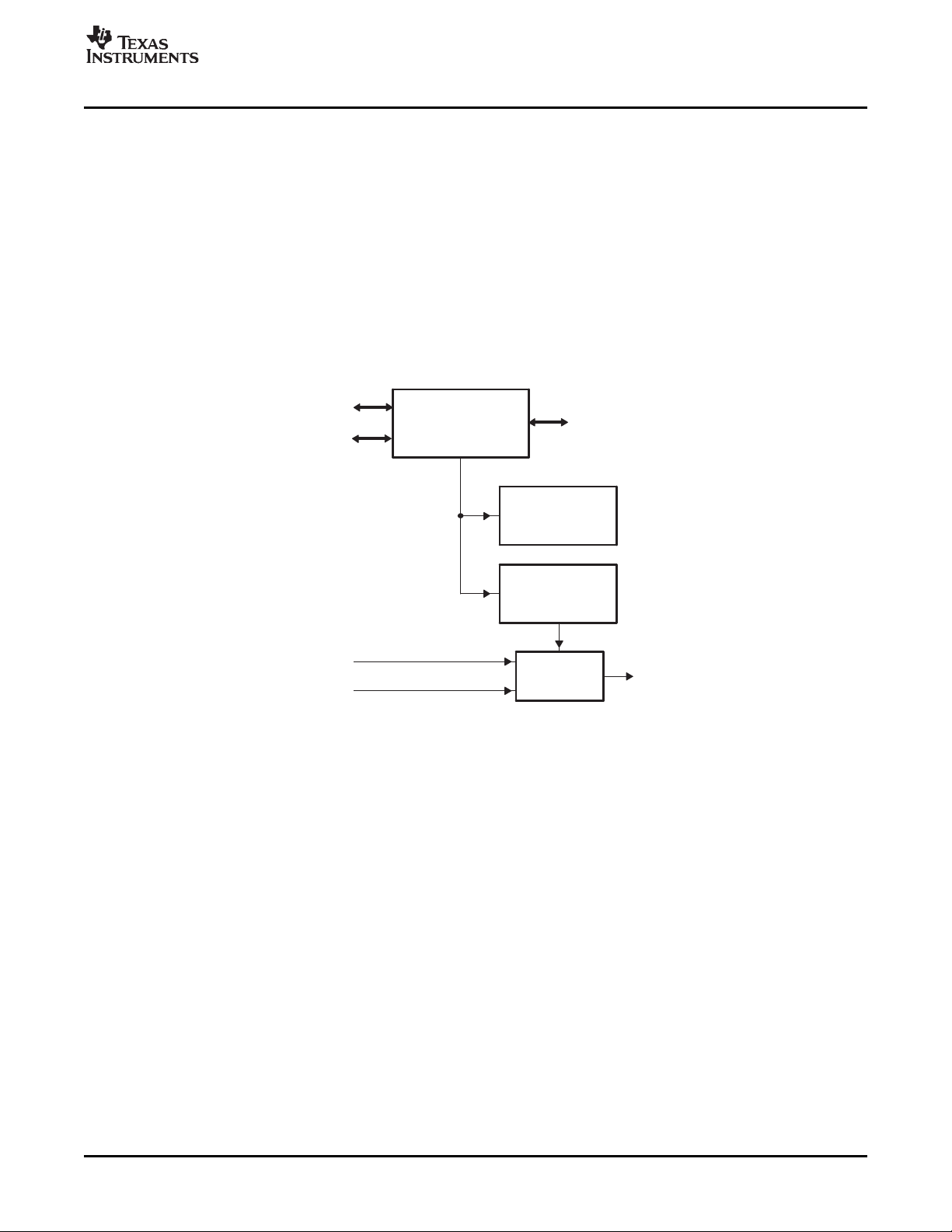

1 EMAC and MDIO Block Diagram ........................................................................................ 12

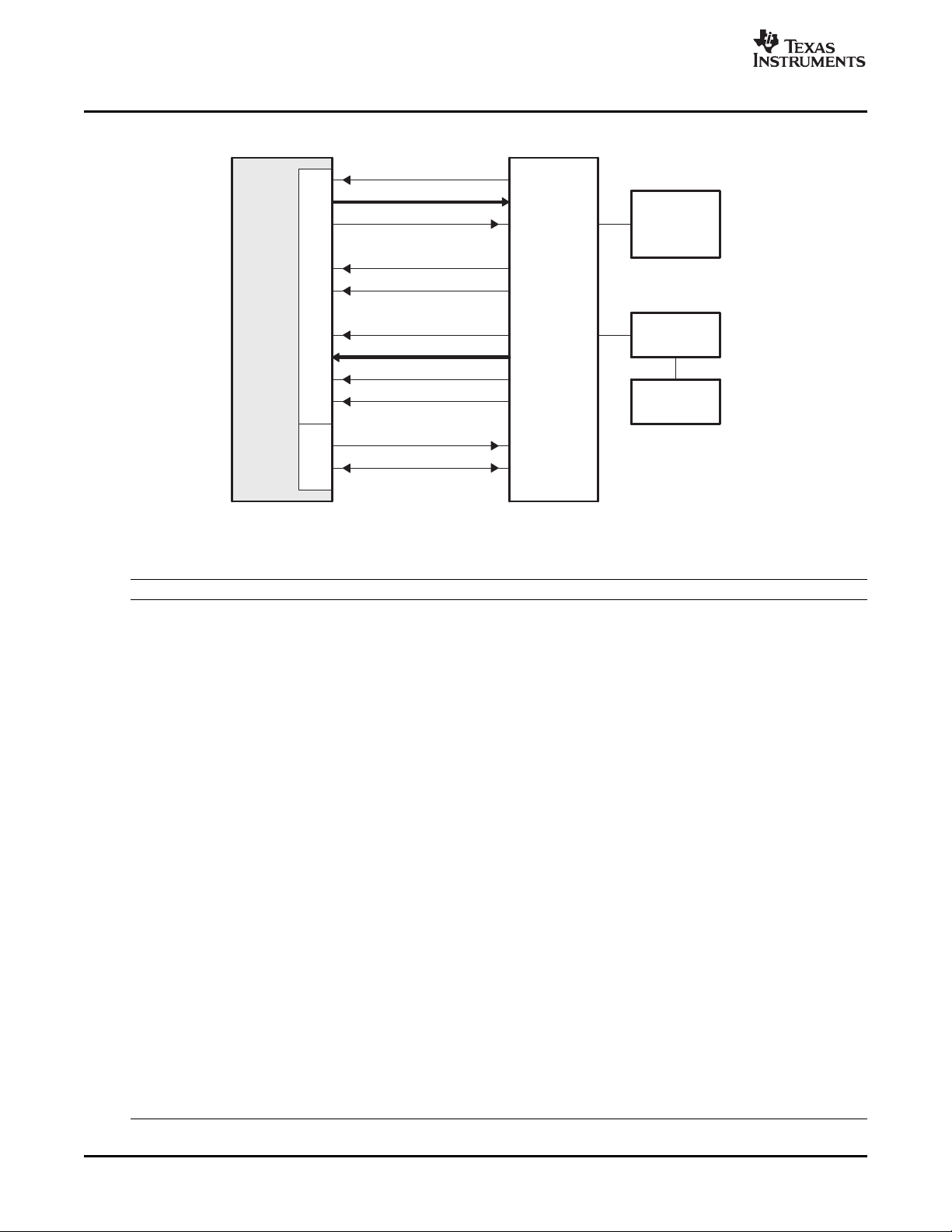

2 Typical Ethernet Configuration ........................................................................................... 14

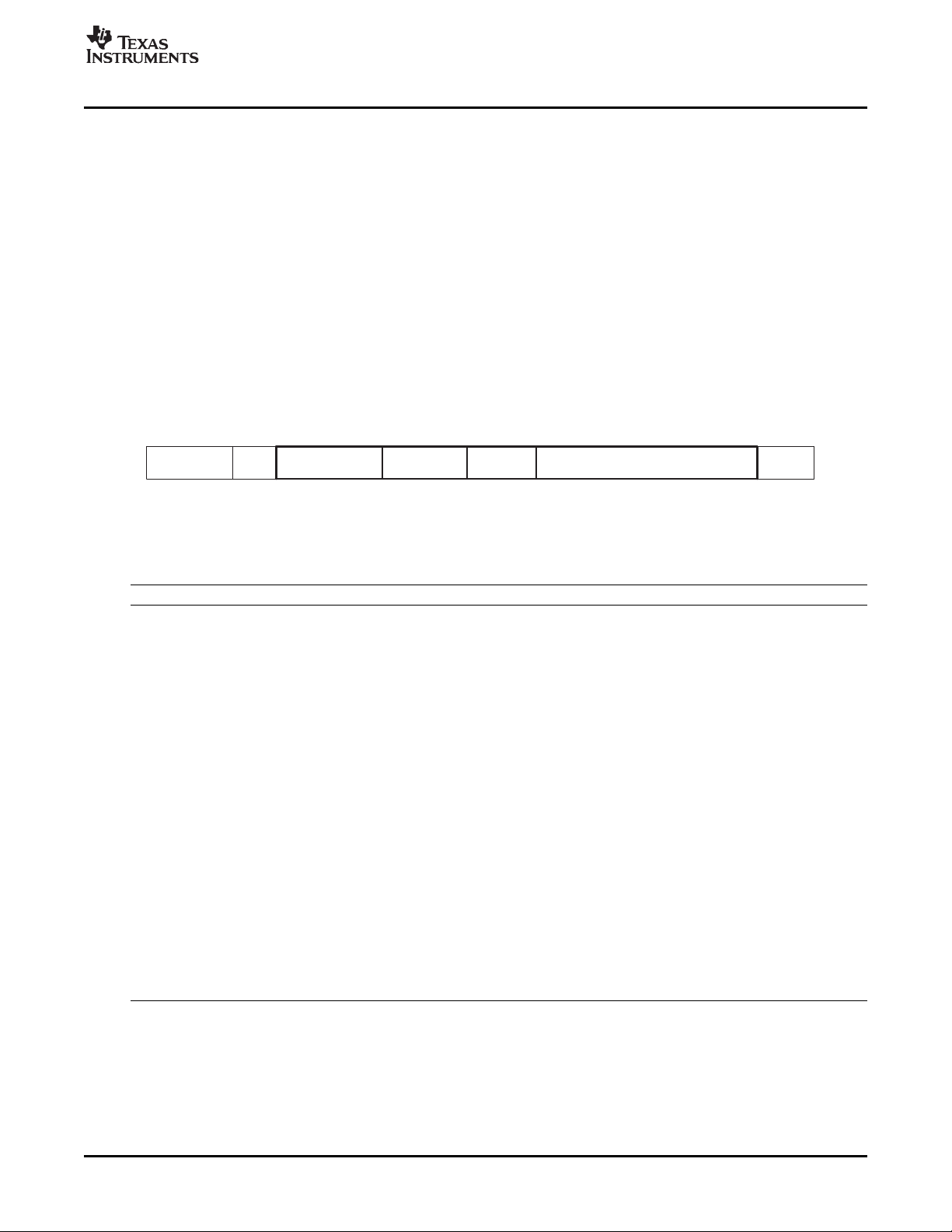

3 Ethernet Frame Format .................................................................................................... 15

4 Basic Descriptor Format ................................................................................................... 16

5 Typical Descriptor Linked List ............................................................................................ 17

6 Transmit Buffer Descriptor Format ....................................................................................... 20

7 Receive Buffer Descriptor Format ........................................................................................ 23

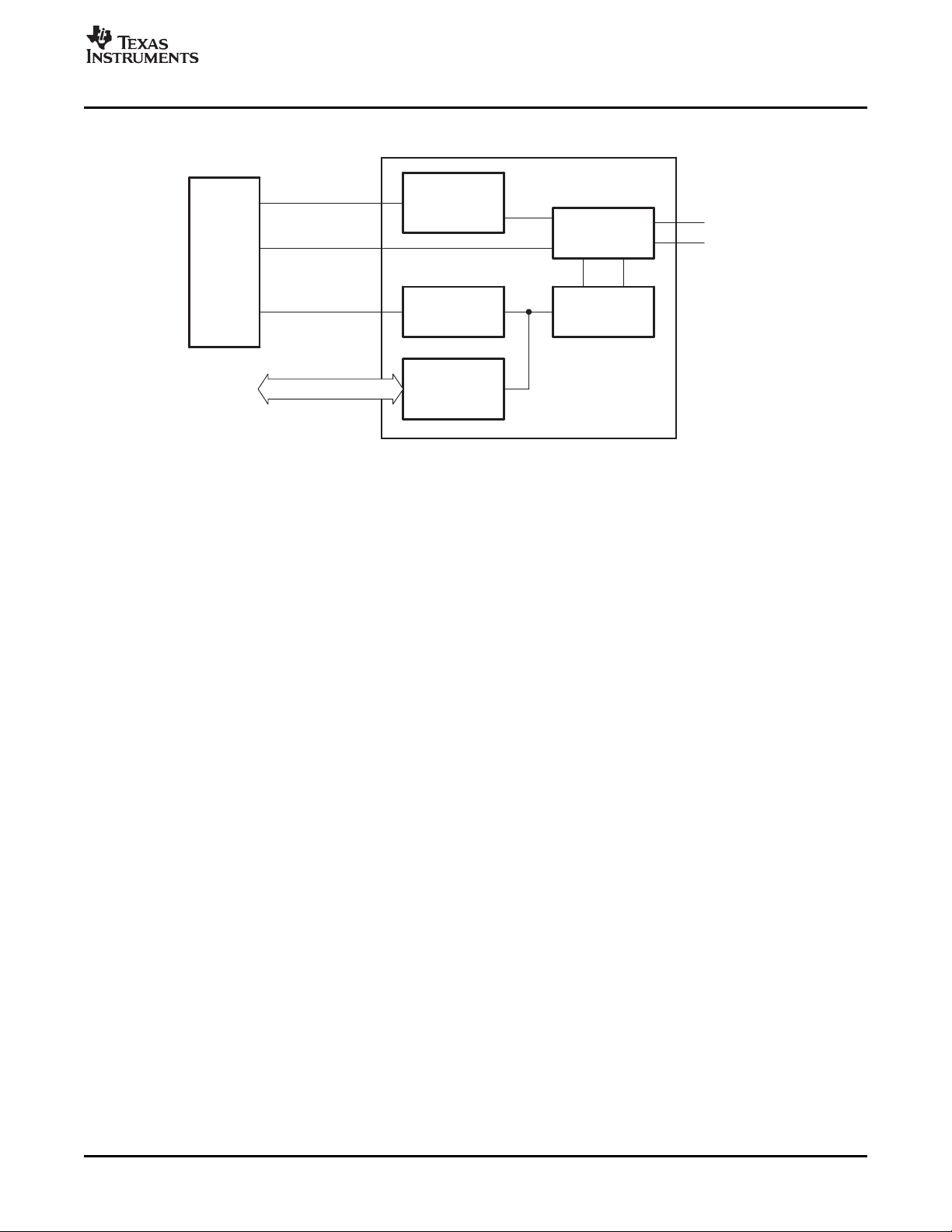

8 EMAC Control Module Block Diagram .................................................................................. 27

9 MDIO Module Block Diagram ............................................................................................. 29

10 EMAC Module Block Diagram ............................................................................................ 33

11 EMAC Control Module Interrupt Control Register (EWCTL) .......................................................... 53

12 EMAC Control Module Interrupt Timer Count Register (EWINTTCNT) ............................................. 54

13 MDIO Version Register (VERSION) ..................................................................................... 55

14 MDIO Control Register (CONTROL) ..................................................................................... 56

15 PHY Acknowledge Status Register (ALIVE) ............................................................................ 57

16 PHY Link Status Register (LINK) ......................................................................................... 57

17 MDIO Link Status Change Interrupt (Unmasked) Register (LINKINTRAW) ........................................ 58

18 MDIO Link Status Change Interrupt (Masked) Register (LINKINTMASKED) ...................................... 59

19 MDIO User Command Complete Interrupt (Unmasked) Register (USERINTRAW) ............................... 60

20 MDIO User Command Complete Interrupt (Masked) Register (USERINTMASKED) ............................. 61

21 MDIO User Command Complete Interrupt Mask Set Register (USERINTMASKSET) ........................... 62

22 MDIO User Command Complete Interrupt Mask Clear Register (USERINTMASKCLEAR) ..................... 63

23 MDIO User Access Register 0 (USERACCESS0) ..................................................................... 64

24 MDIO User PHY Select Register 0 (USERPHYSEL0) ................................................................ 65

25 MDIO User Access Register 1 (USERACCESS1) ..................................................................... 66

26 MDIO User PHY Select Register 1 (USERPHYSEL1) ................................................................ 67

27 Transmit Identification and Version Register (TXIDVER) ............................................................. 71

28 Transmit Control Register (TXCONTROL) .............................................................................. 71

29 Transmit Teardown Register (TXTEARDOWN) ........................................................................ 72

30 Receive Identification and Version Register (RXIDVER) ............................................................. 73

31 Receive Control Register (RXCONTROL) .............................................................................. 73

32 Receive Teardown Register (RXTEARDOWN) ........................................................................ 74

33 Transmit Interrupt Status (Unmasked) Register (TXINTSTATRAW) ................................................ 75

34 Transmit Interrupt Status (Masked) Register (TXINTSTATMASKED) .............................................. 76

35 Transmit Interrupt Mask Set Register (TXINTMASKSET) ............................................................ 77

36 Transmit Interrupt Mask Clear Register (TXINTMASKCLEAR) ...................................................... 78

37 MAC Input Vector Register (MACINVECTOR) ......................................................................... 79

38 Receive Interrupt Status (Unmasked) Register (RXINTSTATRAW) ................................................ 80

39 Receive Interrupt Status (Masked) Register (RXINTSTATMASKED) ............................................... 81

40 Receive Interrupt Mask Set Register (RXINTMASKSET) ............................................................. 82

41 Receive Interrupt Mask Clear Register (RXINTMASKCLEAR) ...................................................... 83

42 MAC Interrupt Status (Unmasked) Register (MACINTSTATRAW) .................................................. 84

43 MAC Interrupt Status (Masked) Register (MACINTSTATMASKED) ................................................ 84

44 MAC Interrupt Mask Set Register (MACINTMASKSET) .............................................................. 85

45 MAC Interrupt Mask Clear Register (MACINTMASKCLEAR) ........................................................ 85

46 Receive Multicast/Broadcast/Promiscuous Channel Enable Register (RXMBPENABLE) ........................ 86

47 Receive Unicast Enable Set Register (RXUNICASTSET) ............................................................ 89

48 Receive Unicast Clear Register (RXUNICASTCLEAR) ............................................................... 90

49 Receive Maximum Length Register (RXMAXLEN) .................................................................... 91

50 Receive Buffer Offset Register (RXBUFFEROFFSET) ............................................................... 91

51 Receive Filter Low Priority Frame Threshold Register (RXFILTERLOWTHRESH) ............................... 92

52 Receive Channel n Flow Control Threshold Register (RX nFLOWTHRESH) ...................................... 92

6 List of Figures SPRU941A – April 2007

Submit Documentation Feedback

Page 7

53 Receive Channel n Free Buffer Count Register (RX nFREEBUFFER) .............................................. 93

54 MAC Control Register (MACCONTROL) ................................................................................ 94

55 MAC Status Register (MACSTATUS) ................................................................................... 96

56 Emulation Control Register (EMCONTROL) ............................................................................ 98

57 FIFO Control Register (FIFOCONTROL) ............................................................................... 98

58 MAC Configuration Register (MACCONFIG) ........................................................................... 99

59 Soft Reset Register (SOFTRESET) ..................................................................................... 99

60 MAC Source Address Low Bytes Register (MACSRCADDRLO)................................................... 100

61 MAC Source Address High Bytes Register (MACSRCADDRHI) ................................................... 100

62 MAC Hash Address Register 1 (MACHASH1) ........................................................................ 101

63 MAC Hash Address Register 2 (MACHASH2) ........................................................................ 101

64 Back Off Random Number Generator Test Register (BOFFTEST) ................................................ 102

65 Transmit Pacing Algorithm Test Register (TPACETEST) ........................................................... 102

66 Receive Pause Timer Register (RXPAUSE) .......................................................................... 103

67 Transmit Pause Timer Register (TXPAUSE) .......................................................................... 103

68 MAC Address Low Bytes Register (MACADDRLO) .................................................................. 104

69 MAC Address High Bytes Register (MACADDRHI) .................................................................. 104

70 MAC Index Register (MACINDEX) ..................................................................................... 105

71 Transmit Channel n DMA Head Descriptor Pointer Register (TX nHDP) .......................................... 106

72 Receive Channel n DMA Head Descriptor Pointer Register (RX nHDP) .......................................... 106

73 Transmit Channel n Completion Pointer Register (TX nCP) ......................................................... 107

74 Receive Channel n Completion Pointer Register (RX nCP) ......................................................... 107

75 Statistics Register ......................................................................................................... 108

SPRU941A – April 2007 List of Figures 7

Submit Documentation Feedback

Page 8

List of Tables

1 EMAC and MDIO Signals ................................................................................................. 14

2 Ethernet Frame Description ............................................................................................... 15

3 Basic Descriptor Description .............................................................................................. 17

4 Receive Frame Treatment Summary .................................................................................... 42

5 Middle of Frame Overrun Treatment .................................................................................... 43

6 Emulation Control .......................................................................................................... 52

7 EMAC Control Module Registers ......................................................................................... 53

8 EMAC Control Module Interrupt Control Register (EWCTL) Field Descriptions ................................... 53

9 EMAC Control Module Interrupt Timer Count Register (EWINTTCNT) Field Descriptions ....................... 54

10 Management Data Input/Output (MDIO) Registers .................................................................... 55

11 MDIO Version Register (VERSION) Field Descriptions ............................................................... 55

12 MDIO Control Register (CONTROL) Field Descriptions .............................................................. 56

13 PHY Acknowledge Status Register (ALIVE) Field Descriptions ..................................................... 57

14 PHY Link Status Register (LINK) Field Descriptions .................................................................. 57

15 MDIO Link Status Change Interrupt (Unmasked) Register (LINKINTRAW) Field Descriptions ................. 58

16 MDIO Link Status Change Interrupt (Masked) Register (LINKINTMASKED) Field Descriptions ................ 59

17 MDIO User Command Complete Interrupt (Unmasked) Register (USERINTRAW) Field Descriptions ........ 60

18 MDIO User Command Complete Interrupt (Masked) Register (USERINTMASKED) Field Descriptions ....... 61

19 MDIO User Command Complete Interrupt Mask Set Register (USERINTMASKSET) Field Descriptions ..... 62

20 MDIO User Command Complete Interrupt Mask Clear Register (USERINTMASKCLEAR) Field

Descriptions ................................................................................................................. 63

21 MDIO User Access Register 0 (USERACCESS0) Field Descriptions ............................................... 64

22 MDIO User PHY Select Register 0 (USERPHYSEL0) Field Descriptions .......................................... 65

23 MDIO User Access Register 1 (USERACCESS1) Field Descriptions ............................................... 66

24 MDIO User PHY Select Register 1 (USERPHYSEL1) Field Descriptions .......................................... 67

25 Ethernet Media Access Controller (EMAC) Registers ................................................................. 68

26 Transmit Identification and Version Register (TXIDVER) Field Descriptions ....................................... 71

27 Transmit Control Register (TXCONTROL) Field Descriptions ....................................................... 71

28 Transmit Teardown Register (TXTEARDOWN) Field Descriptions.................................................. 72

29 Receive Identification and Version Register (RXIDVER) Field Descriptions ....................................... 73

30 Receive Control Register (RXCONTROL) Field Descriptions ........................................................ 73

31 Receive Teardown Register (RXTEARDOWN) Field Descriptions .................................................. 74

32 Transmit Interrupt Status (Unmasked) Register (TXINTSTATRAW) Field Descriptions .......................... 75

33 Transmit Interrupt Status (Masked) Register (TXINTSTATMASKED) Field Descriptions ........................ 76

34 Transmit Interrupt Mask Set Register (TXINTMASKSET) Field Descriptions ...................................... 77

35 Transmit Interrupt Mask Clear Register (TXINTMASKCLEAR) Field Descriptions ................................ 78

36 MAC Input Vector Register (MACINVECTOR) Field Descriptions ................................................... 79

37 Receive Interrupt Status (Unmasked) Register (RXINTSTATRAW) Field Descriptions .......................... 80

38 Receive Interrupt Status (Masked) Register (RXINTSTATMASKED) Field Descriptions......................... 81

39 Receive Interrupt Mask Set Register (RXINTMASKSET) Field Descriptions ...................................... 82

40 Receive Interrupt Mask Clear Register (RXINTMASKCLEAR) Field Descriptions ................................ 83

41 MAC Interrupt Status (Unmasked) Register (MACINTSTATRAW) Field Descriptions ............................ 84

42 MAC Interrupt Status (Masked) Register (MACINTSTATMASKED) Field Descriptions .......................... 84

43 MAC Interrupt Mask Set Register (MACINTMASKSET) Field Descriptions ........................................ 85

44 MAC Interrupt Mask Clear Register (MACINTMASKCLEAR) Field Descriptions .................................. 85

45 Receive Multicast/Broadcast/Promiscuous Channel Enable Register (RXMBPENABLE) Field Descriptions . 86

46 Receive Unicast Enable Set Register (RXUNICASTSET) Field Descriptions ...................................... 89

47 Receive Unicast Clear Register (RXUNICASTCLEAR) Field Descriptions ......................................... 90

48 Receive Maximum Length Register (RXMAXLEN) Field Descriptions .............................................. 91

49 Receive Buffer Offset Register (RXBUFFEROFFSET) Field Descriptions ......................................... 91

8 List of Tables SPRU941A – April 2007

Submit Documentation Feedback

Page 9

50 Receive Filter Low Priority Frame Threshold Register (RXFILTERLOWTHRESH) Field Descriptions ......... 92

51 Receive Channel n Flow Control Threshold Register (RX nFLOWTHRESH) Field Descriptions ................ 92

52 Receive Channel n Free Buffer Count Register (RX nFREEBUFFER) Field Descriptions ....................... 93

53 MAC Control Register (MACCONTROL) Field Descriptions ......................................................... 94

54 MAC Status Register (MACSTATUS) Field Descriptions ............................................................. 96

55 Emulation Control Register (EMCONTROL) Field Descriptions ..................................................... 98

56 FIFO Control Register (FIFOCONTROL) Field Descriptions ......................................................... 98

57 MAC Configuration Register (MACCONFIG) Field Descriptions ..................................................... 99

58 Soft Reset Register (SOFTRESET) Field Descriptions ............................................................... 99

59 MAC Source Address Low Bytes Register (MACSRCADDRLO) Field Descriptions ............................ 100

60 MAC Source Address High Bytes Register (MACSRCADDRHI) Field Descriptions............................. 100

61 MAC Hash Address Register 1 (MACHASH1) Field Descriptions ................................................. 101

62 MAC Hash Address Register 2 (MACHASH2) Field Descriptions ................................................. 101

63 Back Off Test Register (BOFFTEST) Field Descriptions ............................................................ 102

64 Transmit Pacing Algorithm Test Register (TPACETEST) Field Descriptions ..................................... 102

65 Receive Pause Timer Register (RXPAUSE) Field Descriptions .................................................... 103

66 Transmit Pause Timer Register (TXPAUSE) Field Descriptions ................................................... 103

67 MAC Address Low Bytes Register (MACADDRLO) Field Descriptions ........................................... 104

68 MAC Address High Bytes Register (MACADDRHI) Field Descriptions ............................................ 104

69 MAC Index Register (MACINDEX) Field Descriptions ............................................................... 105

70 Transmit Channel n DMA Head Descriptor Pointer Register (TX nHDP) Field Descriptions .................... 106

71 Receive Channel n DMA Head Descriptor Pointer Register (RX nHDP) Field Descriptions .................... 106

72 Transmit Channel n Completion Pointer Register (TX nCP) Field Descriptions .................................. 107

73 Receive Channel n Completion Pointer Register (RX nCP) Field Descriptions ................................... 107

A-1 Physical Layer Definitions ............................................................................................... 118

B-1 Document Revision History .............................................................................................. 119

SPRU941A – April 2007 List of Tables 9

Submit Documentation Feedback

Page 10

About This Manual

Notational Conventions

Preface

SPRU941A – April 2007

Read This First

This document provides a functional description of the Ethernet Media Access Controller (EMAC) and

physical layer (PHY) device Management Data Input/Output (MDIO) module integrated in the

TMS320DM643x Digital Media Processor (DMP). Included are the features of the EMAC and MDIO

modules, a discussion of their architecture and operation, how these modules connect to the outside

world, and the registers description for each module.

This document uses the following conventions.

• Hexadecimal numbers are shown with the suffix h. For example, the following number is 40

hexadecimal (decimal 64): 40h.

• Registers in this document are shown in figures and described in tables.

– Each register figure shows a rectangle divided into fields that represent the fields of the register.

Each field is labeled with its bit name, its beginning and ending bit numbers above, and its

read/write properties below. A legend explains the notation used for the properties.

– Reserved bits in a register figure designate a bit that is used for future device expansion.

Related Documentation From Texas Instruments

The following documents describe the TMS320DM643x Digital Media Processor (DMP). Copies of these

documents are available on the Internet at www.ti.com . Tip: Enter the literature number in the search box

provided at www.ti.com.

The current documentation that describes the DM643x DMP, related peripherals, and other technical

collateral, is available in the C6000 DSP product folder at: www.ti.com/c6000 .

SPRU978 — TMS320DM643x DMP DSP Subsystem Reference Guide. Describes the digital signal

processor (DSP) subsystem in the TMS320DM643x Digital Media Processor (DMP).

SPRU983 — TMS320DM643x DMP Peripherals Overview Reference Guide. Provides an overview and

briefly describes the peripherals available on the TMS320DM643x Digital Media Processor (DMP).

SPRAA84 — TMS320C64x to TMS320C64x+ CPU Migration Guide. Describes migrating from the

Texas Instruments TMS320C64x digital signal processor (DSP) to the TMS320C64x+ DSP. The

objective of this document is to indicate differences between the two cores. Functionality in the

devices that is identical is not included.

SPRU732 — TMS320C64x/C64x+ DSP CPU and Instruction Set Reference Guide. Describes the CPU

architecture, pipeline, instruction set, and interrupts for the TMS320C64x and TMS320C64x+ digital

signal processors (DSPs) of the TMS320C6000 DSP family. The C64x/C64x+ DSP generation

comprises fixed-point devices in the C6000 DSP platform. The C64x+ DSP is an enhancement of

the C64x DSP with added functionality and an expanded instruction set.

SPRU871 — TMS320C64x+ DSP Megamodule Reference Guide. Describes the TMS320C64x+ digital

signal processor (DSP) megamodule. Included is a discussion on the internal direct memory access

(IDMA) controller, the interrupt controller, the power-down controller, memory protection, bandwidth

management, and the memory and cache.

10 Preface SPRU941A – April 2007

Submit Documentation Feedback

Page 11

1 Introduction

This document provides a functional description of the Ethernet Media Access Controller (EMAC) and

physical layer (PHY) device Management Data Input/Output (MDIO) module integrated in the

TMS320DM643x Digital Media Processor (DMP). Included are the features of the EMAC and MDIO

modules, a discussion of their architecture and operation, how these modules connect to the outside

world, and a description of the registers for each module.

The EMAC controls the flow of packet data from the system to the PHY. The MDIO module controls PHY

configuration and status monitoring.

Both the EMAC and the MDIO modules interface to the system core through a custom interface that

allows efficient data transmission and reception. This custom interface is referred to as the EMAC control

module and is considered integral to the EMAC/MDIO peripheral.

1.1 Purpose of the Peripheral

The EMAC module is used to move data between the DM643x device and another host connected to the

same network, in compliance with the Ethernet protocol.

User's Guide

SPRU941A – April 2007

Ethernet Media Access Controller (EMAC)/

Management Data Input/Output (MDIO)

1.2 Features

The EMAC/MDIO has the following features:

• Synchronous 10/100 Mbps operation.

• Standard Media Independent Interface (MII) to physical layer device (PHY).

• EMAC acts as DMA master to either internal or external device memory space.

• Eight receive channels with VLAN tag discrimination for receive quality-of-service (QOS) support.

• Eight transmit channels with round-robin or fixed priority for transmit quality-of-service (QOS) support.

• Ether-Stats and 802.3-Stats statistics gathering.

• Transmit CRC generation selectable on a per channel basis.

• Broadcast frames selection for reception on a single channel.

• Multicast frames selection for reception on a single channel.

• Promiscuous receive mode frames selection for reception on a single channel (all frames, all good

frames, short frames, error frames).

• Hardware flow control.

• 8K-byte local EMAC descriptor memory that allows the peripheral to operate on descriptors without

affecting the CPU. The descriptor memory holds enough information to transfer up to 512 Ethernet

packets without CPU intervention.

• Programmable interrupt logic permits the software driver to restrict the generation of back-to-back

interrupts, which allows more work to be performed in a single call to the interrupt service routine.

SPRU941A – April 2007 Ethernet Media Access Controller (EMAC)/ 11

Submit Documentation Feedback

Management Data Input/Output (MDIO)

Page 12

www.ti.com

Configuration bus

DMA memory

transfer controller

Peripheral bus

EMAC control module

EMAC module MDIO module

MII bus MDIO bus

EMAC/MDIO

interrupt

DSP interrupt

controller

Introduction

1.3 Functional Block Diagram

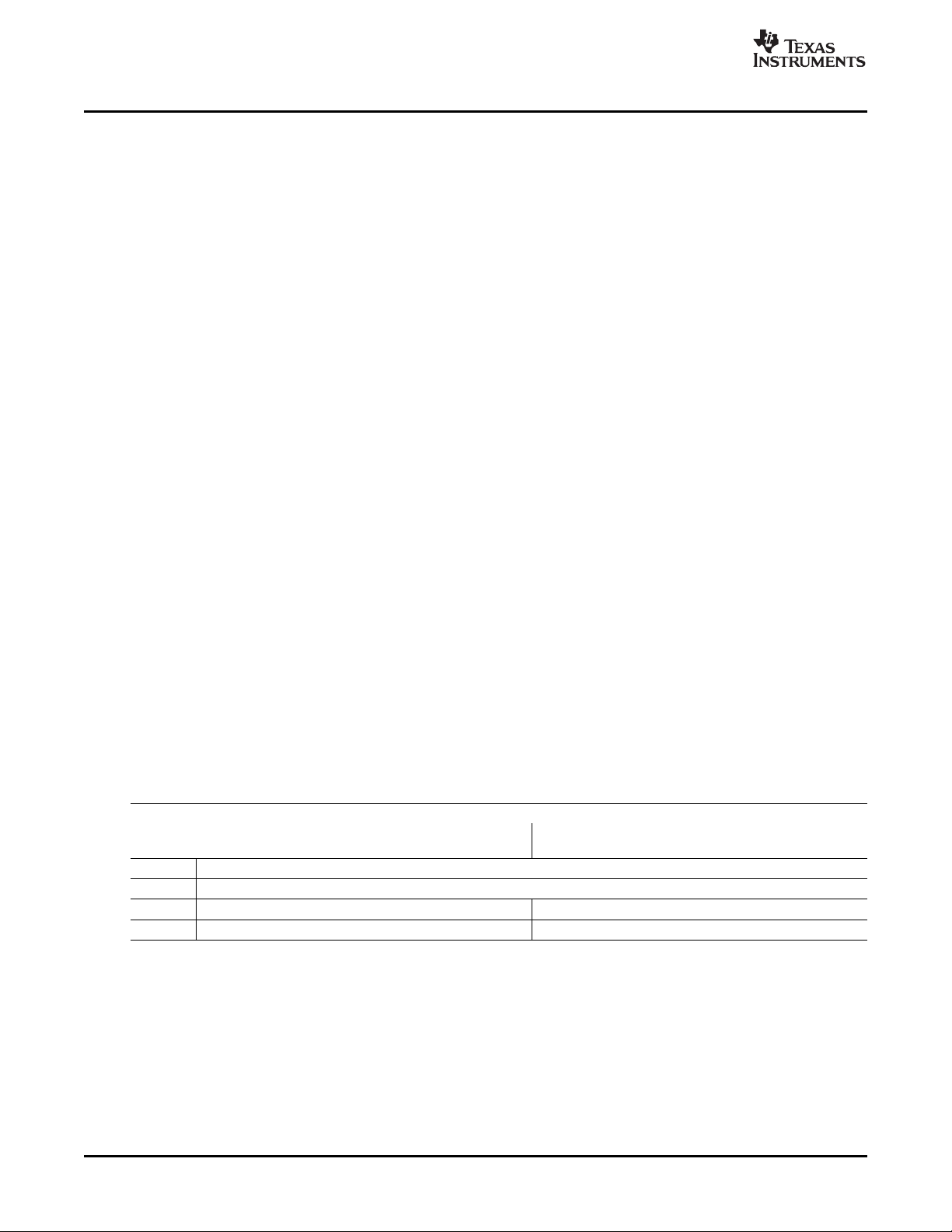

Figure 1 shows the three main functional modules of the EMAC/MDIO peripheral:

• EMAC control module

• EMAC module

• MDIO module

The EMAC control module is the main interface between the device core processor and the EMAC

module and MDIO module. The EMAC control module contains the necessary components to allow the

EMAC to make efficient use of device memory, plus it controls device interrupts. The EMAC control

module incorporates 8K-byte internal RAM to hold EMAC buffer descriptors.

The MDIO module implements the 802.3 serial management interface to interrogate and control up to 32

Ethernet PHYs connected to the device, using a shared two-wire bus. Host software uses the MDIO

module to configure the autonegotiation parameters of each PHY attached to the EMAC, retrieve the

negotiation results, and configure required parameters in the EMAC module for correct operation. The

module is designed to allow almost transparent operation of the MDIO interface, with very little

maintenance from the core processor.

The EMAC module provides an efficient interface between the processor and the networked community.

The EMAC on this device supports both 10Base-T (10 Mbits/sec), and 100BaseTX (100 Mbits/sec), in

either half-duplex or full-duplex mode, with hardware flow control and quality-of-service (QOS) support.

Figure 1 also shows the main interface between the EMAC control module and the CPU. The following

connections are made to the device core:

• The peripheral bus connection from the EMAC control module allows the EMAC module to read and

write both internal and external memory through the DMA memory transfer controller.

• The EMAC control module, EMAC, and MDIO all have control registers. These registers are

memory-mapped into device memory space via the device configuration bus. Along with these

registers, the control module’s internal RAM is mapped into this same range.

• The EMAC and MDIO interrupts are combined into a single interrupt within the control module. The

interrupt from the control module then goes to the DSP interrupt controller.

The EMAC and MDIO interrupts are combined within the control module, so only the control module

interrupt needs to be monitored by the application software or device driver. The combined EMAC/MDIO

interrupt is connected to the DSP interrupt INT43, through the DSP interrupt controller.

12 Ethernet Media Access Controller (EMAC)/ SPRU941A – April 2007

Figure 1. EMAC and MDIO Block Diagram

Management Data Input/Output (MDIO)

Submit Documentation Feedback

Page 13

www.ti.com

1.4 Industry Standard(s) Compliance Statement

The EMAC peripheral conforms to the IEEE 802.3 standard, describing the Carrier Sense Multiple Access

with Collision Detection (CSMA/CD) Access Method and Physical Layer specifications. The IEEE 802.3

standard has also been adopted by ISO/IEC and re-designated as ISO/IEC 8802-3:2000(E).

In difference from this standard, the EMAC peripheral does not use the Transmit Coding Error signal

MTXER. Instead of driving the error pin when an underflow condition occurs on a transmitted frame, the

EMAC intentionally generates an incorrect checksum by inverting the frame CRC, so that the transmitted

frame is detected as an error by the network.

2 Peripheral Architecture

This section discusses the architecture and basic function of the EMAC peripheral.

2.1 Clock Control

The frequencies for the transmit and receive clocks are fixed by the IEEE 802.3 specification as:

• 2.5 MHZ at 10 Mbps

• 25 MHZ at 100 Mbps

All EMAC logic is clocked synchronously with the PLL1/6 peripheral clock, except for the Ethernet MII

synchronization logic.

The transmit and receive clock sources are provided from the external PHY via the MTCLK and MRCLK

pins. These clocks are inputs to the EMAC module and operate at 2.5 MHZ in 10-Mbps mode, and at 25

MHZ in 100-Mbps mode. For timing purposes, data is transmitted and received with respect to MTCLK

and MRCLK, respectively.

The MDIO clock is based on a divide-down of the peripheral clock (PLL1/6) specified to run up to 2.5

MHZ, although typical operation would be 1.0 MHZ. Since the peripheral clock frequency is variable

(PLL1/6), the application software or driver controls the divide-down amount.

Peripheral Architecture

2.2 Memory Map

The EMAC peripheral includes internal memory that is used to hold information about the Ethernet

packets received and transmitted. This internal RAM is 2K × 32 bits in size. Data can be written to and

read from the EMAC internal memory by either the EMAC or the CPU. It is used to store buffer descriptors

that are 4-words (16-bytes) deep. This 8K local memory holds enough information to transfer up to 512

Ethernet packets without CPU intervention.

The packet buffer descriptors can also be placed in the internal processor memory (L2), or in EMIF

memory (DDR). There are some tradeoffs in terms of cache performance and throughput when

descriptors are placed in the system memory, versus when they are placed in the EMAC’s internal

memory. Cache performance is improved when the buffer descriptors are placed in internal memory.

However, the EMAC throughput is better when the descriptors are placed in the local EMAC RAM.

2.3 Signal Descriptions

Figure 2 shows a device with integrated EMAC and MDIO interfaced via a MII connection in a typical

system. The EMAC module does not include a transmit error (MTXER) pin. In the case of transmit error,

CRC inversion is used to negate the validity of the transmitted frame.

The individual EMAC and MDIO signals for the MII interface are summarized in Table 1 . For more

information, refer to either the IEEE 802.3 standard or ISO/IEC 8802-3:2000(E).

SPRU941A – April 2007 Ethernet Media Access Controller (EMAC)/ 13

Submit Documentation Feedback

Management Data Input/Output (MDIO)

Page 14

www.ti.com

MTCLK

MTXD(3−0)

MTXEN

MCOL

MCRS

MRCLK

MRXD(3−0)

MRXDV

MRXER

MDCLK

MDIO

Physical

layer

device

(PHY)

System

core

Transformer

2.5 MHz

or

25 MHz

RJ−45

EMACMDIO

Peripheral Architecture

Figure 2. Typical Ethernet Configuration

Table 1. EMAC and MDIO Signals

Signal Type Description

MTCLK I Transmit clock (MTCLK). The transmit clock is a continuous clock that provides the timing reference

MTXD[3-0] O Transmit data (MTXD). The transmit data pins are a collection of 4 data signals comprising 4 bits of

MTXEN O Transmit enable (MTXEN). The transmit enable signal indicates that the MTXD pins are generating

MCOL I Collision detected (MCOL). The MCOL pin is asserted by the PHY when it detects a collision on the

MCRS I Carrier sense (MCRS). The MCRS pin is asserted by the PHY when the network is not idle in either

MRCLK I Receive clock (MRCLK). The receive clock is a continuous clock that provides the timing reference

MRXD[3-0] I Receive data (MRXD). The receive data pins are a collection of 4 data signals comprising 4 bits of

MRXDV I Receive data valid (MRXDV). The receive data valid signal indicates that the MRXD pins are

MRXER I Receive error (MRXER). The receive error signal is asserted for one or more MRCLK periods to

MDCLK O Management data clock (MDCLK). The MDIO data clock is sourced by the MDIO module on the

MDIO I/O Management data input output (MDIO). The MDIO pin drives PHY management data into and out of

for transmit operations. The MTXD and MTXEN signals are tied to this clock. The clock is generated

by the PHY and is 2.5 MHz at 10 Mbps operation and 25 MHz at 100 Mbps operation.

data. MTDX0 is the least-significant bit (LSB). The signals are synchronized by MTCLK and valid

only when MTXEN is asserted.

nibble data for use by the PHY. It is driven synchronously to MTCLK.

network. It remains asserted while the collision condition persists. This signal is not necessarily

synchronous to MTCLK nor MRCLK. This pin is used in half-duplex operation only.

transmit or receive. The pin is deasserted when both transmit and receive are idle. This signal is not

necessarily synchronous to MTCLK nor MRCLK. This pin is used in half-duplex operation only.

for receive operations. The MRXD, MRXDV, and MRXER signals are tied to this clock. The clock is

generated by the PHY and is 2.5 MHz at 10 Mbps operation and 25 MHz at 100 Mbps operation.

data. MRDX0 is the least-significant bit (LSB). The signals are synchronized by MRCLK and valid

only when MRXDV is asserted.

generating nibble data for use by the EMAC. It is driven synchronously to MRCLK.

indicate that an error was detected in the received frame. This is meaningful only during data

reception when MRXDV is active.

system. It is used to synchronize MDIO data access operations done on the MDIO pin. The

frequency of this clock is controlled by the CLKDIV bits in the MDIO control register (CONTROL).

the PHY by way of an access frame consisting of start of frame, read/write indication, PHY address,

register address, and data bit cycles. The MDIO pin acts as an output for all but the data bit cycles

at which time it is an input for read operations.

Ethernet Media Access Controller (EMAC)/14 SPRU941A – April 2007

Management Data Input/Output (MDIO)

Submit Documentation Feedback

Page 15

www.ti.com

2.4 Ethernet Protocol Overview

Preamble SFD Destination Source Len Data

7 1 6 6 2 46−1500 4

FCS

Number of bytes

Legend: SFD=Start Frame Delimeter; FCS=Frame Check Sequence (CRC)

A brief overview of the Ethernet protocol is given in the following subsections. For in-depth information on

the Carrier Sense Multiple Access with Collision Detection (CSMA/CD) Access Method, which is the

Ethernet’s multiple access protocol, see the IEEE 802.3 standard document.

2.4.1 Ethernet Frame Format

All the Ethernet technologies use the same frame structure. The format of an Ethernet frame is shown in

Figure 3 and described in Table 2 . The Ethernet packet, which is the collection of bytes representing the

data portion of a single Ethernet frame on the wire, is shown outlined in bold. The Ethernet frames are of

variable lengths, with no frame smaller than 64 bytes or larger than RXMAXLEN bytes (header, data, and

CRC).

Peripheral Architecture

Figure 3. Ethernet Frame Format

Table 2. Ethernet Frame Description

Field Bytes Description

Preamble 7 Preamble. These 7 bytes have a fixed value of 55h and serve to wake up the receiving

SFD 1 Start of Frame Delimiter. This field with a value of 5Dh immediately follows the preamble

Destination 6 Destination address. This field contains the Ethernet MAC address of the EMAC port for

Source 6 Source address. This field contains the MAC address of the Ethernet port that transmits the

Len 2 Length/Type field. The length field indicates the number of EMAC client data bytes

Data 46 to Data field. This field carries the datagram containing the upper layer protocol frame, that is,

(RXMAXLEN - 18) IP layer datagram. The maximum transfer unit (MTU) of Ethernet is (RXMAXLEN - 18)

FCS 4 Frame Check Sequence. A cyclic redundancy check (CRC) is used by the transmit and

EMAC ports and to synchronize their clocks to that of the sender’s clock.

pattern and indicates the start of important data.

which the frame is intended. It may be an individual or multicast (including broadcast)

address. When the destination EMAC port receives an Ethernet frame with a destination

address that does not match any of its MAC physical addresses, and no promiscuous,

multicast or broadcast channel is enabled, it discards the frame.

frame to the Local Area Network.

contained in the subsequent data field of the frame. This field can also be used to identify

the type of data the frame is carrying.

bytes. This means that if the upper layer protocol datagram exceeds (RXMAXLEN - 18)

bytes, then the host has to fragment the datagram and send it in multiple Ethernet packets.

The minimum size of the data field is 46 bytes. This means that if the upper layer datagram

is less then 46 bytes, the data field has to be extended to 46 bytes by appending extra bits

after the data field, but prior to calculating and appending the FCS.

receive algorithms to generate a CRC value for the FCS field. The frame check sequence

covers the 60 to 1514 bytes of the packet data. Note that this 4-byte field may or may not

be included as part of the packet data, depending on how the EMAC is configured.

SPRU941A – April 2007 Ethernet Media Access Controller (EMAC)/ 15

Submit Documentation Feedback

Management Data Input/Output (MDIO)

Page 16

www.ti.com

Peripheral Architecture

2.4.2 Ethernet’s Multiple Access Protocol

Nodes in an Ethernet Local Area Network are interconnected by a broadcast channel, as a result, when

an EMAC port transmits a frame, all the adapters on the local network receive the frame. Carrier Sense

Multiple Access with Collision Detection (CSMA/CD) algorithms are used when the EMAC operates in

half-duplex mode. When operating in full-duplex mode, there is no contention for use of a shared medium,

since there are exactly two ports on the local network.

Each port runs the CSMA/CD protocol without explicit coordination with the other ports on the Ethernet

network. Within a specific port, the CSMA/CD protocol works as follows:

1. The port obtains data from upper layers protocols at its node, prepares an Ethernet frame, and puts

the frame in a buffer.

2. If the port senses that the medium is idle it starts to transmit the frame. If the port senses that the

transmission medium is busy, it waits until it senses no signal energy (plus an Inter-Packet Gap time)

and then starts to transmit the frame.

3. While transmitting, the port monitors for the presence of signal energy coming from other ports. If the

port transmits the entire frame without detecting signal energy from other Ethernet devices, the port is

done with the frame.

4. If the port detects signal energy from other ports while transmitting, it stops transmitting its frame and

instead transmits a 48-bit jam signal.

5. After transmitting the jam signal the port enters an exponential backoff phase. Specifically, when

transmitting a given frame, after experiencing a number of collisions in a row for the frame, the port

chooses a random value that is dependent on the number of collisions. The port then waits an amount

of time that is multiple of this random value, and returns to step 2.

2.5 Programming Interface

2.5.1 Packet Buffer Descriptors

The buffer descriptor is a central part of the EMAC module and is how the application software describes

Ethernet packets to be sent and empty buffers to be filled with incoming packet data. The basic descriptor

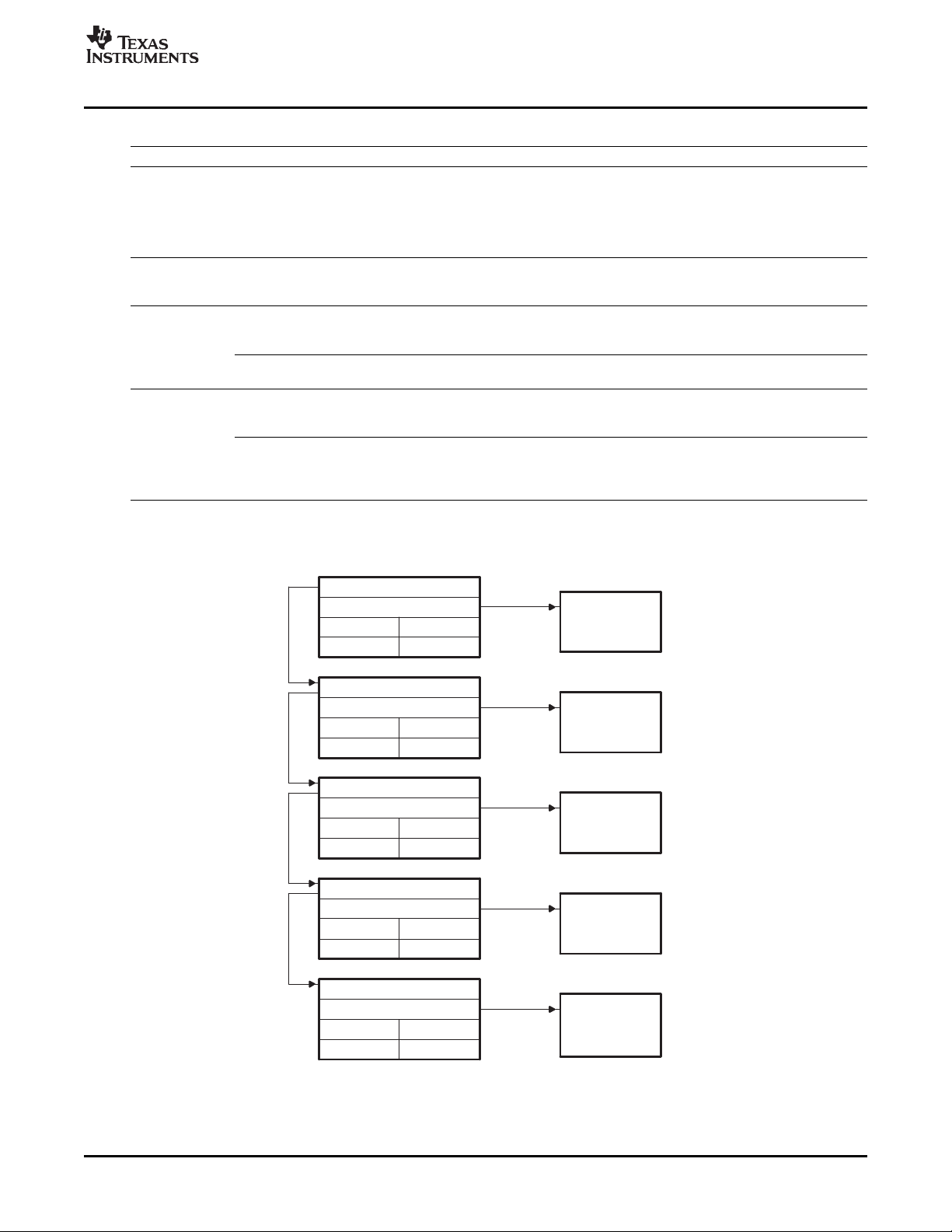

format is shown in Figure 4 and described in Table 3 .

For example, consider three packets to be transmitted, Packet A is a single fragment (60 bytes), Packet B

is fragmented over three buffers (1514 bytes total), and Packet C is a single fragment (1514 bytes). The

linked list of descriptors to describe these three packets is shown in Figure 5 .

Word

Offset 31 16 15 0

0 Next Descriptor Pointer

1 Buffer Pointer

2 Buffer Offset Buffer Length

3 Flags Packet Length

Figure 4. Basic Descriptor Format

Bit Fields

16 Ethernet Media Access Controller (EMAC)/ SPRU941A – April 2007

Management Data Input/Output (MDIO)

Submit Documentation Feedback

Page 17

www.ti.com

SOP | EOP 60

0 60

pBuffer

pNext

Packet A

60 bytes

0

SOP

Fragment 1

Packet B

512

1514

pBuffer

pNext

512 bytes

EOP

0

0

−−−

Packet B

Fragment 3

500 bytes

502

pBuffer

−−−

500

pNext

−−−

pBuffer

pNext

Packet B

Fragment 2

502 bytes

SOP | EOP

0

1514 bytes

Packet C

1514

pBuffer

pNext (NULL)

1514

Peripheral Architecture

Table 3. Basic Descriptor Description

Word Offset Field Field Description

0 Next Descriptor The next descriptor pointer is used to create a single linked list of descriptors. Each descriptor

1 Buffer Pointer The buffer pointer refers to the actual memory buffer that contains packet data during

2 Buffer Offset The buffer offset is the offset from the start of the packet buffer to the first byte of valid data.

3 Flags The flags field contains more information about the buffer, such as, is it the first fragment in a

Pointer describes a packet or a packet fragment. When a descriptor points to a single buffer packet

or the first fragment of a packet, the start of packet (SOP) flag is set in the flags field. When a

descriptor points to a single buffer packet or the last fragment of a packet, the end of packet

(EOP) flag is set. When a packet is fragmented, each fragment must have its own descriptor

and appear sequentially in the descriptor linked list.

transmit operations, or is an empty buffer ready to receive packet data during receive

operations.

This field only has meaning when the buffer descriptor points to a buffer that actually contains

data.

Buffer Length The buffer length is the actual number of valid packet data bytes stored in the buffer. If the

buffer is empty and waiting to receive data, this field represents the size of the empty buffer.

packet (SOP), the last fragment in a packet (EOP), or contains an entire contiguous Ethernet

packet (both SOP and EOP). The flags are described in Section 2.5.4 and Section 2.5.5 .

Packet Length The packet length only has meaning for buffers that both contain data and are the start of a

new packet (SOP). In the case of SOP descriptors, the packet length field contains the length

of the entire Ethernet packet, regardless if it is contained in a single buffer or fragmented over

several buffers.

Figure 5. Typical Descriptor Linked List

SPRU941A – April 2007 Ethernet Media Access Controller (EMAC)/ 17

Submit Documentation Feedback

Management Data Input/Output (MDIO)

Page 18

www.ti.com

Peripheral Architecture

2.5.2 Transmit and Receive Descriptor Queues

The EMAC module processes descriptors in linked list chains as discussed in Section 2.5.1 . The lists

controlled by the EMAC are maintained by the application software through the use of the head descriptor

pointer registers (HDP). Since the EMAC supports eight channels for both transmit and receive, there are

eight head descriptor pointer registers for both. They are:

• TX nHDP - Transmit Channel n DMA Head Descriptor Pointer Register

• RX nHDP - Receive Channel n DMA Head Descriptor Pointer Register

After an EMAC reset and before enabling the EMAC for send or receive, all 16 head descriptor pointer

registers must be initialized to 0.

The EMAC uses a simple system to determine if a descriptor is currently owned by the EMAC or by the

application software. There is a flag in the buffer descriptor flags called OWNER. When this flag is set, the

packet that is referenced by the descriptor is considered to be owned by the EMAC. Note that ownership

is done on a packet based granularity, not on descriptor granularity, so only SOP descriptors make use of

the OWNER flag. As packets are processed, the EMAC patches the SOP descriptor of the corresponding

packet and clears the OWNER flag. This is an indication that the EMAC has finished processing all

descriptors up to and including the first with the EOP flag set, indicating the end of the packet (note this

may only be one descriptor with both the SOP and EOP flags set).

To add a descriptor or a linked list of descriptors to an EMAC descriptor queue for the first time, the

software application simply writes the pointer to the descriptor or first descriptor of a list to the

corresponding HDP register. Note that the last descriptor in the list must have its “next” pointer cleared to

0. This is the only way the EMAC has of detecting the end of the list. So in the case where only a single

descriptor is added, its “next descriptor” pointer must be initialized to 0.

The HDP must never be written to a second time while a previous list is active. To add additional

descriptors to a descriptor list already owned by the EMAC, the NULL “next” pointer of the last descriptor

of the previous list is patched with a pointer to the first descriptor in the new list. The list of new

descriptors to be appended to the existing list must itself be NULL terminated before the pointer patch is

performed.

There is a potential race condition where the EMAC may read the “next” pointer of a descriptor as NULL in

the instant before an application appends additional descriptors to the list by patching the pointer. This

case is handled by the software application always examining the buffer descriptor flags of all EOP

packets, looking for a special flag called end of queue (EOQ). The EOQ flag is set by the EMAC on the

last descriptor of a packet when the descriptor’s “next” pointer is NULL. This is the way the EMAC

indicates to the software application that it believes it has reached the end of the list. When the software

application sees the EOQ flag set, and there are more descriptors to process, the application may at that

time submit the new list, or the portion of the appended list that was missed, by writing the new list pointer

to the same HDP that started the process.

This process applies when adding packets to a transmit list, and empty buffers to a receive list.

18 Ethernet Media Access Controller (EMAC)/ SPRU941A – April 2007

Management Data Input/Output (MDIO)

Submit Documentation Feedback

Page 19

www.ti.com

2.5.3 Transmit and Receive EMAC Interrupts

The EMAC processes descriptors in linked list chains as discussed in Section 2.5.1 , using the linked list

queue mechanism discussed in Section 2.5.2 .

The EMAC synchronizes descriptor list processing through the use of interrupts to the software

application. The interrupts are controlled by the application using the interrupt masks, global interrupt

enable, and the completion pointer register (CP). The CP is also called the interrupt acknowledge register.

As the EMAC supports eight channels for both transmit and receive, there are eight completion pointer

registers for both. They are:

• TX nCP - Transmit Channel n Completion Pointer (Interrupt Acknowledge) Register

• RX nCP - Receive Channel n Completion Pointer (Interrupt Acknowledge) Register

These registers serve two purposes. When read, they return the pointer to the last descriptor that the

EMAC has processed. When written by the software application, the value represents the last descriptor

processed by the software application. When these two values do not match, the interrupt is active.

The system configuration determines whether or not an active interrupt actually interrupts the CPU. In

general, the global interrupt for EMAC and MDIO must be enabled in the EMAC control module, and it

also must be mapped in the DSP interrupt controller and enabled as a CPU interrupt. If the system is

configured properly, the interrupt for a specific receive or transmit channel executes under the previously

described conditions when the corresponding interrupt is enabled in the EMAC using the receive interrupt

mask set register (RXINTMASKSET) or the transmit interrupt mask set register (TXINTMASKSET).

Whether or not the interrupt is enabled, the current state of the receive or transmit channel interrupt can

be examined directly by the software application reading the receive interrupt status (unmasked) register

(RXINTSTATRAW) and transmit interrupt status (unmasked) register (TXINTSTATRAW).

Interrupts are acknowledged when the application software updates the value of TX nCP or RX nCP with a

value that matches the internal value kept by the EMAC. This mechanism ensures that the application

software never misses an EMAC interrupt, since the interrupt and its acknowledgment are tied directly to

the actual buffer descriptors processing.

Peripheral Architecture

SPRU941A – April 2007 Ethernet Media Access Controller (EMAC)/ 19

Submit Documentation Feedback

Management Data Input/Output (MDIO)

Page 20

www.ti.com

Peripheral Architecture

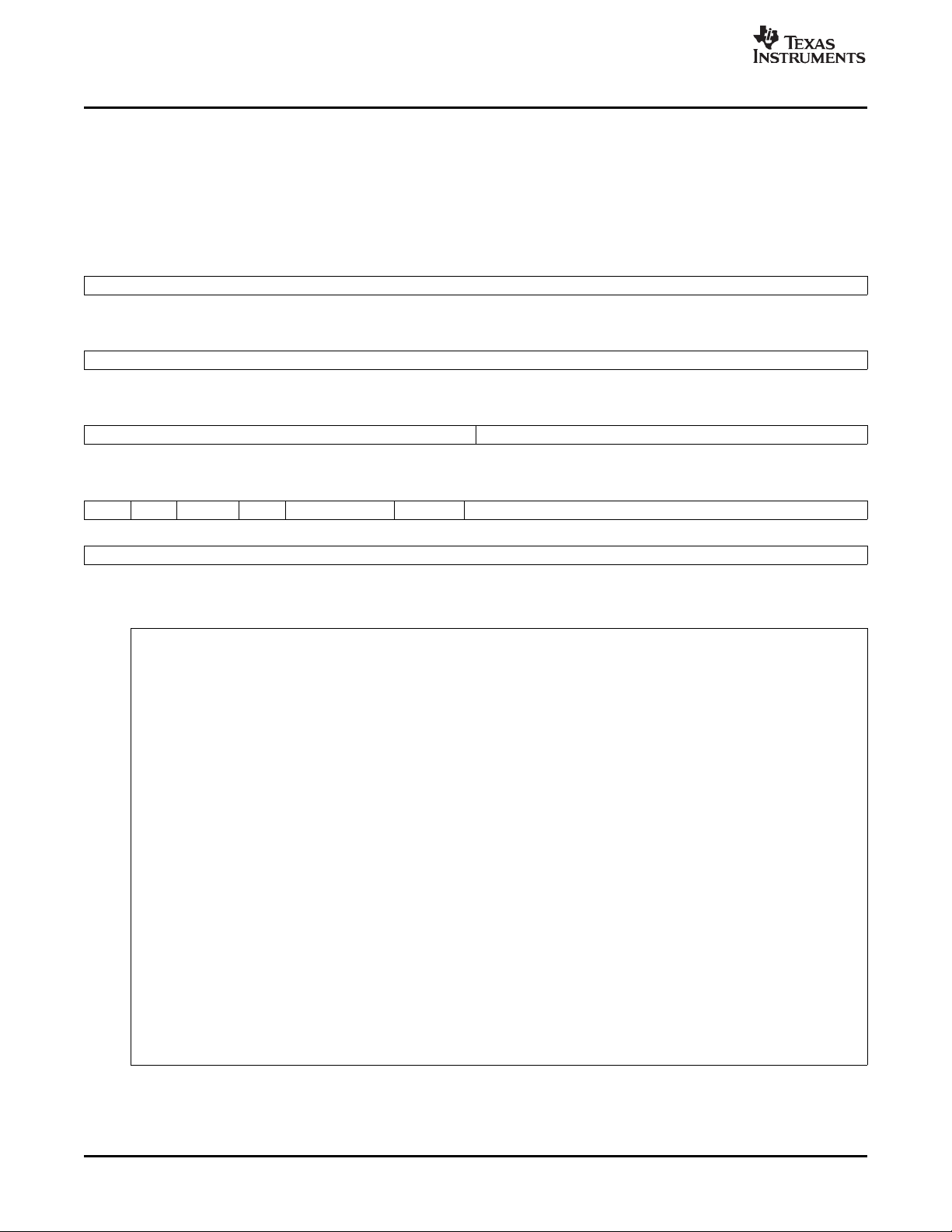

2.5.4 Transmit Buffer Descriptor Format

A transmit (TX) buffer descriptor (Figure 6 ) is a contiguous block of four 32-bit data words aligned on a

32-bit boundary that describes a packet or a packet fragment. Example 1 shows the transmit buffer

descriptor described by a C structure.

Figure 6. Transmit Buffer Descriptor Format

Word 0

31 0

Next Descriptor Pointer

Word 1

31 0

Buffer Pointer

Word 2

31 16 15 0

Buffer Offset Buffer Length

Word 3

31 30 29 28 27 26 25 16

SOP EOP OWNER EOQ TDOWNCMPLT PASSCRC Reserved

15 0

Packet Length

Example 1. Transmit Buffer Descriptor in C Structure Format

/*

// EMAC Descriptor

//

// The following is the format of a single buffer descriptor

// on the EM

AC.

*/

typedef struct _EMAC_Desc {

struct _EMAC_Desc *pNext; /* Pointer to next descriptor in chain */

Uint8 *pBuffer; /* Pointer to data buffer */

Uint32 BufOffLen; /* Buffer Offset(MSW) and Length(LSW) */

Uint32 PktFlgLen; /* Packet Flags(MSW) and Length(LSW) */

} EMAC_Desc;

/* Packet Flags */

#define EMAC_DSC_FLAG_SOP 0x80000000u

#define EMAC_DSC_FLAG_EOP 0x40000000u

#define EMAC_DSC_FLAG_OWNER 0x20000000u

#define EMAC_DSC_FLAG_EOQ 0x10000000u

#define EMAC_DSC_FLAG_TDOWNCMPLT 0x08000000u

#define EMAC_DSC_FLAG_PASSCRC 0x04000000u

Ethernet Media Access Controller (EMAC)/20 SPRU941A – April 2007

Management Data Input/Output (MDIO)

Submit Documentation Feedback

Page 21

www.ti.com

2.5.4.1 Next Descriptor Pointer

The next descriptor pointer points to the 32-bit word aligned memory address of the next buffer descriptor

in the transmit queue. This pointer is used to create a linked list of buffer descriptors. If the value of this

pointer is zero, then the current buffer is the last buffer in the queue. The software application must set

this value prior to adding the descriptor to the active transmit list. This pointer is not altered by the EMAC.

The value of pNext should never be altered once the descriptor is in an active transmit queue, unless its

current value is NULL. If the pNext pointer is initially NULL, and more packets need to be queued for

transmit, the software application may alter this pointer to point to a newly appended descriptor. The

EMAC will use the new pointer value and proceed to the next descriptor unless the pNext value has

already been read. In this latter case, the transmitter will halt on the transmit channel in question, and the

software application may restart it at that time. The software can detect this case by checking for an end

of queue (EOQ) condition flag on the updated packet descriptor when it is returned by the EMAC.

2.5.4.2 Buffer Pointer

The buffer pointer is the byte-aligned memory address of the memory buffer associated with the buffer

descriptor. The software application must set this value prior to adding the descriptor to the active transmit

list. This pointer is not altered by the EMAC.

2.5.4.3 Buffer Offset

This 16-bit field indicates how many unused bytes are at the start of the buffer. For example, a value of

0000h indicates that no unused bytes are at the start of the buffer and that valid data begins on the first

byte of the buffer, while a value of 000Fh indicates that the first 15 bytes of the buffer are to be ignored by

the EMAC and that valid buffer data starts on byte 16 of the buffer. The software application must set this

value prior to adding the descriptor to the active transmit list. This field is not altered by the EMAC.

Note that this value is only checked on the first descriptor of a given packet (where the start of packet

(SOP) flag is set). It can not be used to specify the offset of subsequent packet fragments. Also, since the

buffer pointer may point to any byte–aligned address, this field may be entirely superfluous, depending on

the device driver architecture.

The range of legal values for this field is 0 to (Buffer Length – 1).

Peripheral Architecture

2.5.4.4 Buffer Length

This 16-bit field indicates how many valid data bytes are in the buffer. On single fragment packets, this

value is also the total length of the packet data to be transmitted. If the buffer offset field is used, the offset

bytes are not counted as part of this length. This length counts only valid data bytes. The software

application must set this value prior to adding the descriptor to the active transmit list. This field is not

altered by the EMAC.

2.5.4.5 Packet Length

This 16-bit field specifies the number of data bytes in the entire packet. Any leading buffer offset bytes are

not included. The sum of the buffer length fields of each of the packet’s fragments (if more than one) must

be equal to the packet length. The software application must set this value prior to adding the descriptor to

the active transmit list. This field is not altered by the EMAC. This value is only checked on the first

descriptor of a given packet (where the start of packet (SOP) flag is set).

2.5.4.6 Start of Packet (SOP) Flag

When set, this flag indicates that the descriptor points to a packet buffer that is the start of a new packet.

In the case of a single fragment packet, both the SOP and end of packet (EOP) flags are set. Otherwise,

the descriptor pointing to the last packet buffer for the packet sets the EOP flag. This bit is set by the

software application and is not altered by the EMAC.

SPRU941A – April 2007 Ethernet Media Access Controller (EMAC)/ 21

Submit Documentation Feedback

Management Data Input/Output (MDIO)

Page 22

www.ti.com

Peripheral Architecture

2.5.4.7 End of Packet (EOP) Flag

When set, this flag indicates that the descriptor points to a packet buffer that is last for a given packet. In

the case of a single fragment packet, both the start of packet (SOP) and EOP flags are set. Otherwise, the

descriptor pointing to the last packet buffer for the packet sets the EOP flag. This bit is set by the software

application and is not altered by the EMAC.

2.5.4.8 Ownership (OWNER) Flag

When set, this flag indicates that all the descriptors for the given packet (from SOP to EOP) are currently

owned by the EMAC. This flag is set by the software application on the SOP packet descriptor before

adding the descriptor to the transmit descriptor queue. For a single fragment packet, the SOP, EOP, and

OWNER flags are all set. The OWNER flag is cleared by the EMAC once it is finished with all the

descriptors for the given packet. Note that this flag is valid on SOP descriptors only.

2.5.4.9 End of Queue (EOQ) Flag

When set, this flag indicates that the descriptor in question was the last descriptor in the transmit queue

for a given transmit channel, and that the transmitter has halted. This flag is initially cleared by the

software application prior to adding the descriptor to the transmit queue. This bit is set by the EMAC when

the EMAC identifies that a descriptor is the last for a given packet (the EOP flag is set), and there are no

more descriptors in the transmit list (next descriptor pointer is NULL).

The software application can use this bit to detect when the EMAC transmitter for the corresponding

channel has halted. This is useful when the application appends additional packet descriptors to a transmit

queue list that is already owned by the EMAC. Note that this flag is valid on EOP descriptors only.

2.5.4.10 Teardown Complete (TDOWNCMPLT) Flag

This flag is used when a transmit queue is being torn down, or aborted, instead of allowing it to be

transmitted. This would happen under device driver reset or shutdown conditions. The EMAC sets this bit

in the SOP descriptor of each packet as it is aborted from transmission.

Note that this flag is valid on SOP descriptors only. Also note that only the first packet in an unsent list has

the TDOWNCMPLT flag set. Subsequent descriptors are not even processed by the EMAC.

2.5.4.11 Pass CRC (PASSCRC) Flag

This flag is set by the software application in the SOP packet descriptor before it adds the descriptor to the

transmit queue. Setting this bit indicates to the EMAC that the 4 byte Ethernet CRC is already present in

the packet data, and that the EMAC should not generate its own version of the CRC.

When the CRC flag is cleared, the EMAC generates and appends the 4-byte CRC. The buffer length and

packet length fields do not include the CRC bytes. When the CRC flag is set, the 4-byte CRC is supplied

by the software application and is already appended to the end of the packet data. The buffer length and

packet length fields include the CRC bytes, as they are part of the valid packet data. Note that this flag is

valid on SOP descriptors only.

22 Ethernet Media Access Controller (EMAC)/ SPRU941A – April 2007

Management Data Input/Output (MDIO)

Submit Documentation Feedback

Page 23

www.ti.com

2.5.5 Receive Buffer Descriptor Format

A receive (RX) buffer descriptor (Figure 7 ) is a contiguous block of four 32-bit data words aligned on a

32-bit boundary that describes a packet or a packet fragment. Example 2 shows the receive buffer

descriptor described by a C structure.

2.5.5.1 Next Descriptor Pointer

This pointer points to the 32–bit word aligned memory address of the next buffer descriptor in the receive

queue. This pointer is used to create a linked list of buffer descriptors. If the value of this pointer is zero,

then the current buffer is the last buffer in the queue. The software application must set this value prior to

adding the descriptor to the active receive list. This pointer is not altered by the EMAC.

The value of pNext should never be altered once the descriptor is in an active receive queue, unless its

current value is NULL. If the pNext pointer is initially NULL, and more empty buffers can be added to the

pool, the software application may alter this pointer to point to a newly appended descriptor. The EMAC

will use the new pointer value and proceed to the next descriptor unless the pNext value has already been

read. In this latter case, the receiver will halt the receive channel in question, and the software application

may restart it at that time. The software can detect this case by checking for an end of queue (EOQ)

condition flag on the updated packet descriptor when it is returned by the EMAC.

2.5.5.2 Buffer Pointer

The buffer pointer is the byte-aligned memory address of the memory buffer associated with the buffer

descriptor. The software application must set this value prior to adding the descriptor to the active receive

list. This pointer is not altered by the EMAC.

Peripheral Architecture

Figure 7. Receive Buffer Descriptor Format

Word 0

31 0

Next Descriptor Pointer

Word 1

31 0

Buffer Pointer

Word 2

31 16 15 0

Buffer Offset Buffer Length

Word 3

31 30 29 28 27 26 25 24

SOP EOP OWNER EOQ TDOWNCMPLT PASSCRC JABBER OVERSIZE

23 22 21 20 19 18 17 16

FRAGMENT UNDERSIZED CONTROL OVERRUN CODEERROR ALIGNERROR CRCERROR NOMATCH

15 0

Packet Length

SPRU941A – April 2007 Ethernet Media Access Controller (EMAC)/ 23

Submit Documentation Feedback

Management Data Input/Output (MDIO)

Page 24

www.ti.com

Peripheral Architecture

Example 2. Receive Buffer Descriptor in C Structure Format

/*

// EMAC Descriptor

//

// The following is the format of a single buffer descriptor

// on the EMAC.

*/

typedef struct _EMAC_Desc {

struct _EMAC_Desc *pNext; /* Pointer to next descriptor in chain */

Uint8 *pBuffer; /* Pointer to data buffer */

Uint32 BufOffLen; /* Buffer Offset(MSW) and Length(LSW) */

Uint32

PktFlgLen; /* Packet Flags(MSW) and Length(LSW) */

} EMAC_Desc;

/* Packet Flags */

#define EMAC_DSC_FLAG_SOP 0x80000000u

#define EMAC_DSC_FLAG_EOP 0x40000000u

#define EMAC_DSC_FLAG_OWNER 0x20000000u

#define EMAC_DSC_FLAG_EOQ 0x10000000u

#define EMAC_DSC_FLAG_TDOWNCMPLT 0x08000000u

#define EMAC_DSC_FLAG_PASSCRC 0x04000000u

#define EMAC_DSC_FLAG_JABBER 0x02000000u

#define EMAC_DSC_FLAG_OVERSIZE 0x01000000u

#define EMAC_DSC_FLAG_FRAGMENT 0x00800000u

#define EMAC_DSC_FLAG_UNDERSIZED 0x00400000u

#define EMAC_DSC_FLAG_CONTROL 0x00200000u

#define EMAC_DSC_FLAG_OVERRUN 0x00100000u

#define EMAC_DSC_FLAG_CODEERROR 0x00080000u

#define EMAC_DSC_FLAG_ALIGNERROR 0x00040000u

#define EMAC_DSC_FLAG_CRCERROR 0x00020000u

#define EMAC_DSC_FLAG_NOMATCH 0x00010000u

2.5.5.3 Buffer Offset

This 16-bit field must be initialized to zero by the software application before adding the descriptor to a

receive queue.

Whether or not this field is updated depends on the setting of the RXBUFFEROFFSET register. When the

offset register is set to a non-zero value, the received packet is written to the packet buffer at an offset

given by the value of the register, and this value is also written to the buffer offset field of the descriptor.

When a packet is fragmented over multiple buffers because it does not fit in the first buffer supplied, the

buffer offset only applies to the first buffer in the list, which is where the start of packet (SOP) flag is set in

the corresponding buffer descriptor. In other words, the buffer offset field is only updated by the EMAC on

SOP descriptors.

The range of legal values for the BUFFEROFFSET register is 0 to (Buffer Length – 1) for the smallest

value of buffer length for all descriptors in the list.

24 Ethernet Media Access Controller (EMAC)/ SPRU941A – April 2007

Management Data Input/Output (MDIO)

Submit Documentation Feedback

Page 25

www.ti.com

2.5.5.4 Buffer Length

This 16-bit field is used for two purposes:

• Before the descriptor is first placed on the receive queue by the application software, the buffer length

field is first initialized by the software to have the physical size of the empty data buffer pointed to by

the buffer pointer field.

• After the empty buffer has been processed by the EMAC and filled with received data bytes, the buffer

length field is updated by the EMAC to reflect the actual number of valid data bytes written to the

buffer.

2.5.5.5 Packet Length

This 16-bit field specifies the number of data bytes in the entire packet. This value is initialized to zero by

the software application for empty packet buffers. The value is filled in by the EMAC on the first buffer

used for a given packet. This is signified by the EMAC setting a start of packet (SOP) flag. The packet

length is set by the EMAC on all SOP buffer descriptors.

2.5.5.6 Start of Packet (SOP) Flag

When set, this flag indicates that the descriptor points to a packet buffer that is the start of a new packet.

In the case of a single fragment packet, both the SOP and end of packet (EOP) flags are set. Otherwise,

the descriptor pointing to the last packet buffer for the packet has the EOP flag set. This flag is initially

cleared by the software application before adding the descriptor to the receive queue. This bit is set by the

EMAC on SOP descriptors.

Peripheral Architecture

2.5.5.7 End of Packet (EOP) Flag

When set, this flag indicates that the descriptor points to a packet buffer that is last for a given packet. In

the case of a single fragment packet, both the start of packet (SOP) and EOP flags are set. Otherwise, the

descriptor pointing to the last packet buffer for the packet has the EOP flag set. This flag is initially cleared

by the software application before adding the descriptor to the receive queue. This bit is set by the EMAC

on EOP descriptors.

2.5.5.8 Ownership (OWNER) Flag

When set, this flag indicates that the descriptor is currently owned by the EMAC. This flag is set by the