www.ti.com

1 TMS320DM6431 Digital Media Processor

1.1 Features

TMS320DM6431

Digital Media Processor

SPRS342A – NOVEMBER 2006 – REVISED MARCH 2007

• High-Performance Digital Media Processor • C64x+ L1/L2 Memory Architecture

(DM6431)

– 256K-Bit (32K-Byte) L1P Program

– 3.33-ns Instruction Cycle Time RAM/Cache [Flexible Allocation]

– 300-MHz C64x+™ Clock Rate – 256K-Bit (32K-Byte) L1D Data RAM/Cache

[Flexible Allocation]

– Eight 32-Bit C64x+ Instructions/Cycle

– 512K-Bit (64K-Byte) L2 Unified Mapped

– 2400 MIPS

RAM/Cache [Flexible Allocation]

– Fully Software-Compatible With C64x

• Supports Little Endian Mode Only

– Commercial and Extended Temperature

Ranges

• Video Processing Subsystem (VPSS), VPFE

Only

• VelociTI.2™ Extensions to VelociTI™

– Front End Provides:

Advanced Very-Long-Instruction-Word (VLIW)

TMS320C64x+™ DSP Core

• CCD and CMOS Imager Interface

– Eight Highly Independent Functional Units

• BT.601/BT.656 Digital YCbCr 4:2:2

With VelociTI.2 Extensions:

(10-Bit) Interface

• Six ALUs (32-/40-Bit), Each Supports

• Glueless Interface to Common Video

Single 32-Bit, Dual 16-Bit, or Quad 8-Bit

Decoders

Arithmetic per Clock Cycle

• External Memory Interfaces (EMIFs)

• Two Multipliers Support Four 16 x 16-Bit

– 16-Bit DDR2 SDRAM Memory Controller

Multiplies (32-Bit Results) per Clock

With 128M-Byte Address Space (1.8-V I/O)

Cycle or Eight 8 x 8-Bit Multiplies (16-Bit

– Asynchronous 8-Bit Wide EMIF (EMIFA)

Results) per Clock Cycle

With up to 64M-Byte Address Reach

– Load-Store Architecture With Non-Aligned

• Flash Memory Interfaces

Support

• NOR (8-Bit-Wide Data)

– 64 32-Bit General-Purpose Registers

• NAND (8-Bit-Wide Data)

– Instruction Packing Reduces Code Size

• Enhanced Direct-Memory-Access (EDMA)

– All Instructions Conditional

Controller (64 Independent Channels)

– Additional C64x+™ Enhancements

• Two 64-Bit General-Purpose Timers (Each

• Protected Mode Operation

Configurable as Two 32-Bit Timers)

• Exceptions Support for Error Detection

• One 64-Bit Watch Dog Timer

and Program Redirection

• Hardware Support for Modulo Loop

• One UART With RTS and CTS Flow Control

Auto-Focus Module Operation

• Master/Slave Inter-Integrated Circuit (I2C

• C64x+ Instruction Set Features

Bus™)

– Byte-Addressable (8-/16-/32-/64-Bit Data)

• One Multichannel Buffered Serial Port

– 8-Bit Overflow Protection

(McBSP0)

– Bit-Field Extract, Set, Clear

– I2S and TDM

– Normalization, Saturation, Bit-Counting

– AC97 Audio Codec Interface

– VelociTI.2 Increased Orthogonality

– SPI

– C64x+ Extensions

– Standard Voice Codec Interface (AIC12)

• Compact 16-bit Instructions

– Telecom Interfaces – ST-Bus, H-100

• Additional Instructions to Support

– 128 Channel Mode

Complex Multiplies

• Multichannel Audio Serial Port (McASP0)

– Four Serializers and SPDIF (DIT) Mode

• High-End CAN Controller (HECC)

• 10/100 Mb/s Ethernet MAC (EMAC)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this document.

All trademarks are the property of their respective owners.

PRODUCT PREVIEW information concerns products in the

Copyright © 2006–2007, Texas Instruments Incorporated

formative or design phase of development. Characteristic data and

other specifications are design goals. Texas Instruments reserves

the right to change or discontinue these products without notice.

www.ti.com

PRODUCT PREVIEW

1.2 Description

TMS320DM6431

Digital Media Processor

SPRS342A – NOVEMBER 2006 – REVISED MARCH 2007

– IEEE 802.3 Compliant

• Packages:

– Supports Media Independent Interface (MII)

– 361-Pin Pb-Free PBGA Package

(ZWT Suffix), 0.8-mm Ball Pitch

– Management Data I/O (MDIO) Module

– 376-Pin Plastic BGA Package

• Three Pulse Width Modulator (PWM) Outputs

(ZDU Suffix), 1.0-mm Ball Pitch

• On-Chip ROM Bootloader

• 0.09- µ m/6-Level Cu Metal Process (CMOS)

• Individual Power-Savings Modes

• 3.3-V and 1.8-V I/O, 1.2-V Internal (-300)

• Flexible PLL Clock Generators

• Applications:

• IEEE-1149.1 (JTAG™)

– Digital Media

Boundary-Scan-Compatible

– Networked Media Encode

• Up to 111 General-Purpose I/O (GPIO) Pins

– Video Imaging

(Multiplexed With Other Device Functions)

The TMS320C64x+™ DSPs (including the TMS320DM6431 device) are the highest-performance

fixed-point DSP generation in the TMS320C6000™ DSP platform. The DM6431 device is based on the

third-generation high-performance, advanced VelociTI™ very-long-instruction-word (VLIW) architecture

developed by Texas Instruments (TI), making these DSPs an excellent choice for digital media

applications. The C64x+™ devices are upward code-compatible from previous devices that are part of the

C6000™ DSP platform. The C64x™ DSPs support added functionality and have an expanded instruction

set from previous devices.

Any reference to the C64x DSP or C64x CPU also applies, unless otherwise noted, to the C64x+ DSP and

C64x+ CPU, respectively.

With performance of up to 2400 million instructions per second (MIPS) at a clock rate of 300 MHz, the

C64x+ core offers solutions to high-performance DSP programming challenges. The DSP core possesses

the operational flexibility of high-speed controllers and the numerical capability of array processors. The

C64x+ DSP core processor has 64 general-purpose registers of 32-bit word length and eight highly

independent functional units—two multipliers for a 32-bit result and six arithmetic logic units (ALUs). The

eight functional units include instructions to accelerate the performance in video and imaging applications.

The DSP core can produce four 16-bit multiply-accumulates (MACs) per cycle for a total of 1200 million

MACs per second (MMACS), or eight 8-bit MACs per cycle for a total of 2400 MMACS. For more details

on the C64x+ DSP, see the TMS320C64x/C64x+ DSP CPU and Instruction Set Reference Guide

(literature number SPRU732 ).

The DM6431 also has application-specific hardware logic, on-chip memory, and additional on-chip

peripherals similar to the other C6000 DSP platform devices. The DM6431 core uses a two-level

cache-based architecture. The Level 1 program memory/cache (L1P) consists of 32K-byte (KB) memory

space that can be configured as mapped memory or direct mapped cache. The Level 1 data/memory

memory/cache (L1D) of 32KB memory space that can be configured as mapped memory or 2-way

set-associative cache. The Level 2 memory/cache (L2) consists of a 64KB memory space that is shared

between program and data space. L2 memory can be configured as mapped memory, cache, or a

combination of both.

The peripheral set includes: 1 configurable video port; a 10/100 Mb/s Ethernet MAC (EMAC) with a

management data input/output (MDIO) module; an inter-integrated circuit (I2C) Bus interface; a

multichannel buffered serial port (McBSP0); a multichannel audio serial port (McASP0) with 4 serializers; 2

64-bit general-purpose timers each configurable as 2 independent 32-bit timers; 1 64-bit watchdog timer;

up to 111-pins of general-purpose input/output (GPIO) with programmable interrupt/event generation

modes, multiplexed with other peripherals; 1 UART with hardware handshaking support; 3 pulse width

modulator (PWM) peripherals; 1 high-end controller area network (CAN) controller [HECC]; and 2 glueless

external memory interfaces: an asynchronous external memory interface (EMIFA) for slower

memories/peripherals, and a higher speed synchronous memory interface for DDR2.

TMS320DM6431 Digital Media Processor2 Submit Documentation Feedback

www.ti.com

TMS320DM6431

Digital Media Processor

SPRS342A – NOVEMBER 2006 – REVISED MARCH 2007

The DM6431 device includes a Video Processing Subsystem (VPSS) with a Video Processing Front-End

(VPFE) input used for video capture.

The Video Processing Front-End (VPFE) is comprised of a CCD Controller (CCDC). The CCDC is capable

of interfacing to common video decoders, CMOS sensors, and Charge Coupled Devices (CCDs).

The Ethernet Media Access Controller (EMAC) provides an efficient interface between the DM6431 and

the network. The DM6431 EMAC support both 10Base-T and 100Base-TX, or 10 Mbits/second (Mbps)

and 100 Mbps in either half- or full-duplex mode, with hardware flow control and quality of service (QOS)

support.

The Management Data Input/Output (MDIO) module continuously polls all 32 MDIO addresses in order to

enumerate all PHY devices in the system.

The I2C port allows DM6431 to easily control peripheral devices and/or communicate with host

processors.

The high-end controller area network (CAN) controller [HECC] module provides a network protocol in a

harsh environment to communicate serially with other controllers, typically in automotive applications.

The rich peripheral set provides the ability to control external peripheral devices and communicate with

external processors. For details on each of the peripherals, see the related sections later in this document

and the associated peripheral reference guides.

The DM6431 has a complete set of development tools. These include C compilers, a DSP assembly

optimizer to simplify programming and scheduling, and a Windows™ debugger interface for visibility into

source code execution.

Submit Documentation Feedback TMS320DM6431 Digital Media Processor 3

www.ti.com

PRODUCT PREVIEW

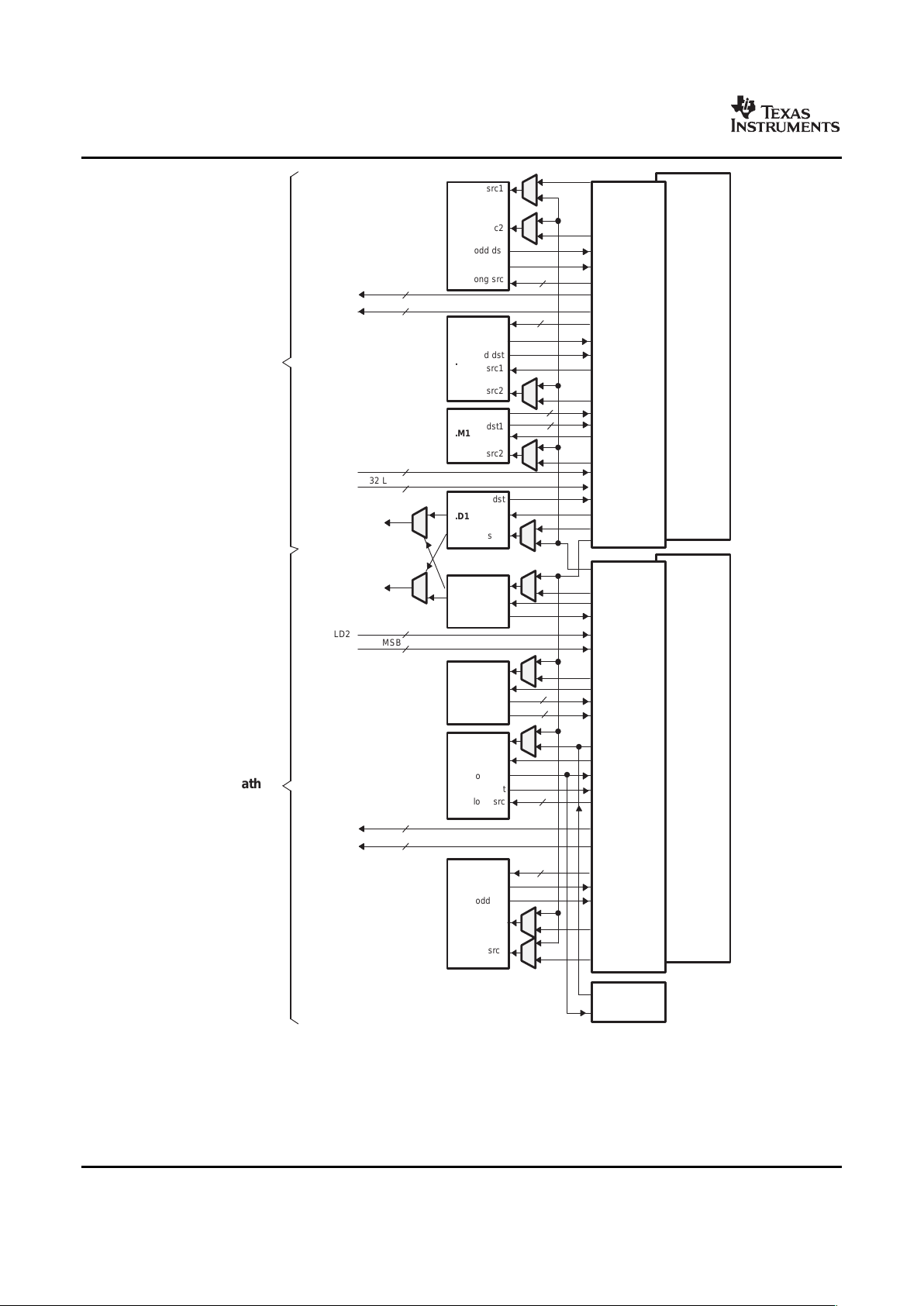

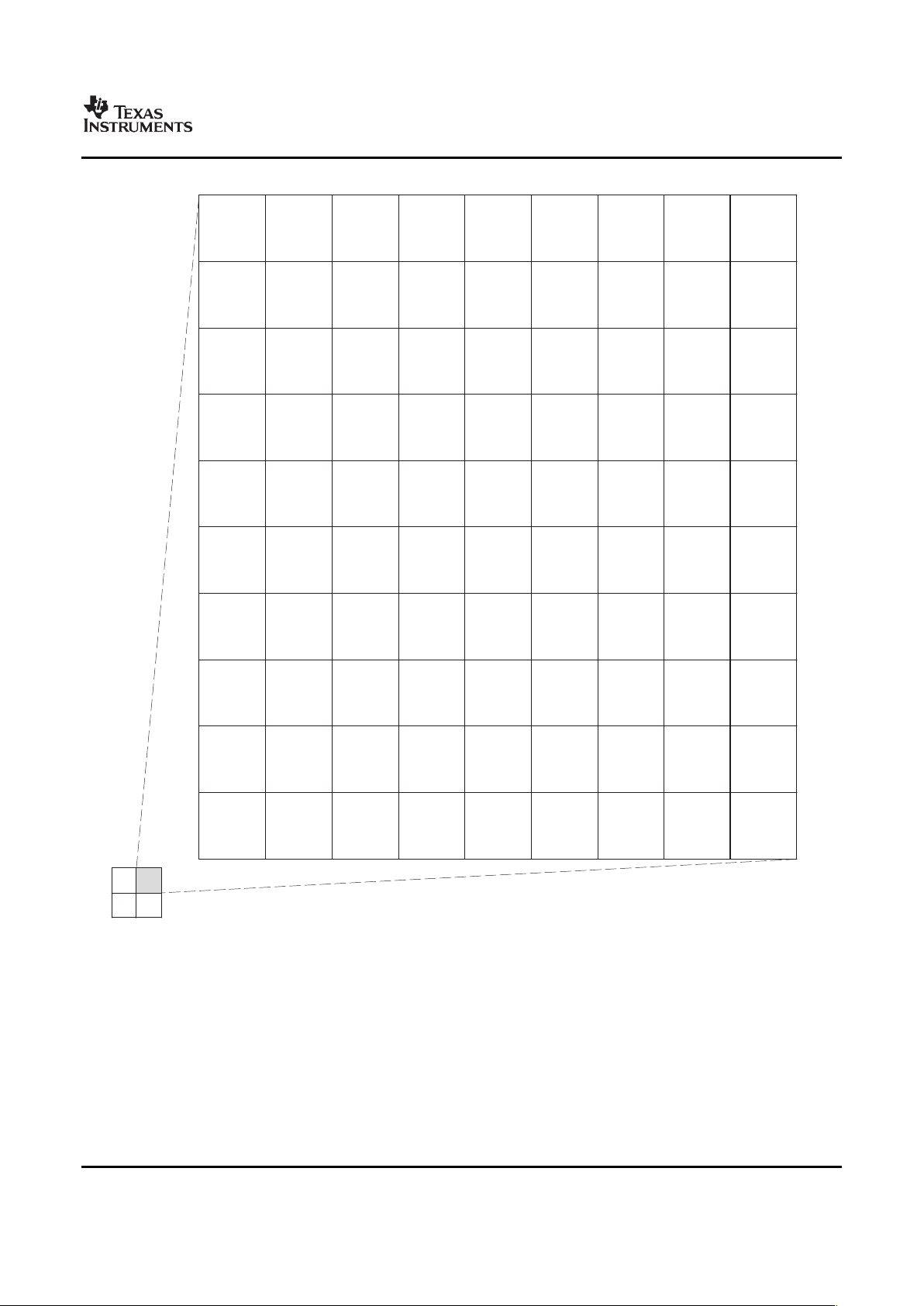

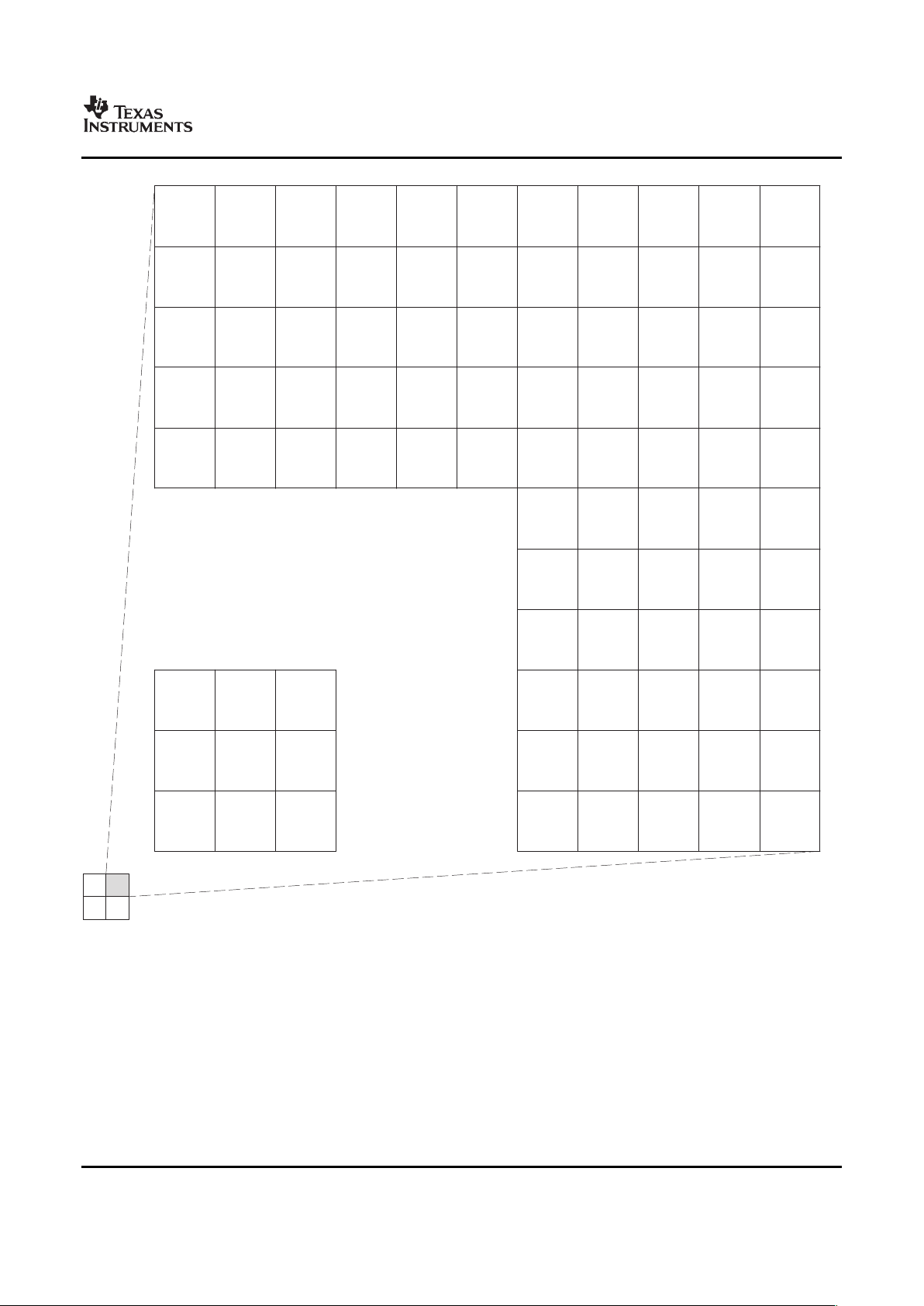

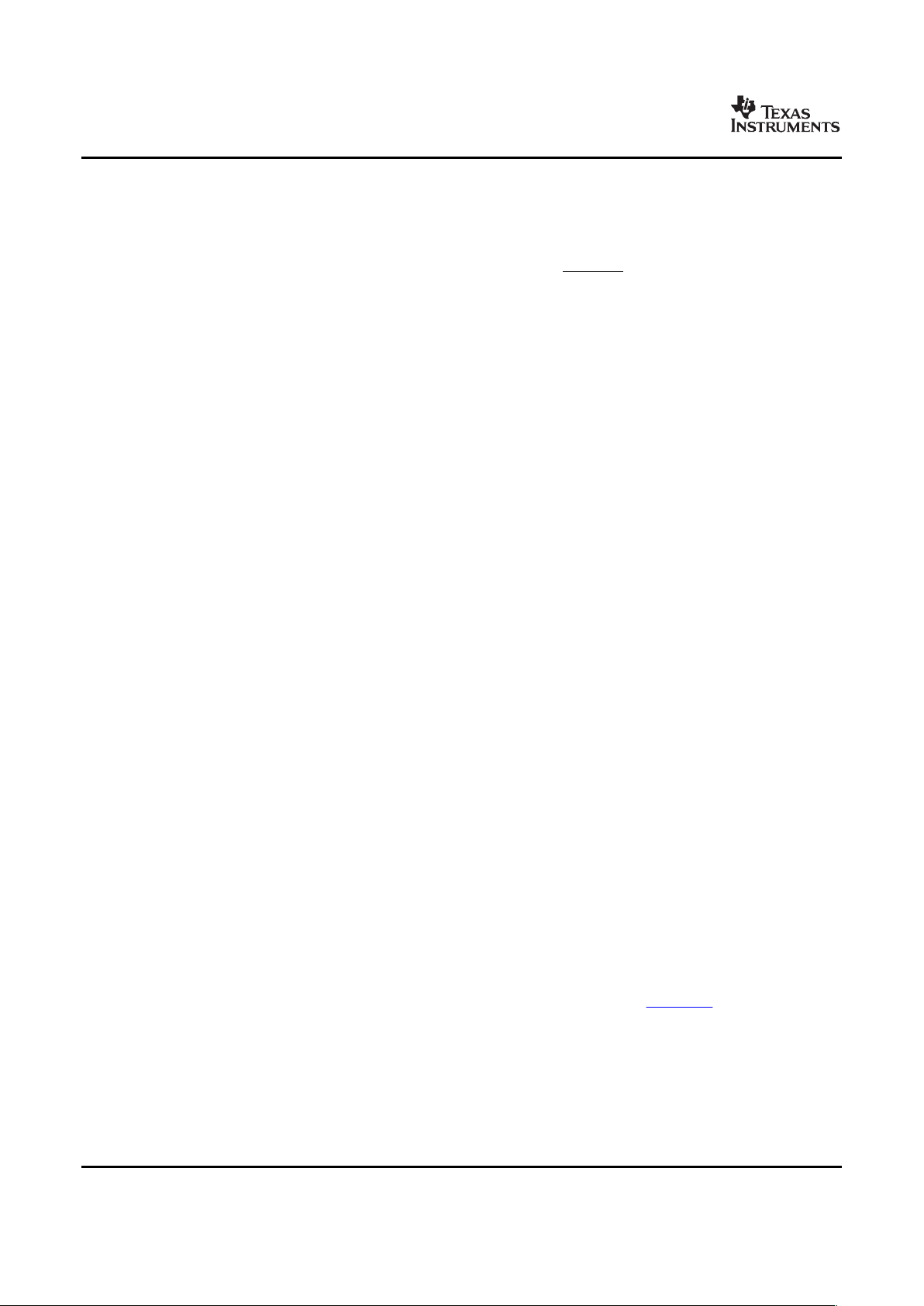

1.3 Functional Block Diagram

JTAG Interface

System Control

PLLs/Clock Generator

Input

Clock(s)

Power/Sleep Controller

Pin Multiplexing

DSP Subsystem

C64x+t DSP CPU

32 KB

L1 Pgm

64 KB L2 RAM

32 KB

L1 Data

BT.656,

Y/C,

Raw (Bayer)

Video Processing Subsystem (VPSS)

CCD

Controller

Video

Interface

Front End

Switched Central Resource (SCR)

Peripherals

EDMA

I2C HECC UART

Serial Interfaces

DDR2

Mem Ctlr

(16b)

Async EMIF/

NAND/

(8b)

Program/Data Storage

Watchdog

Timer

PWM

System

GeneralPurpose

Timer

EMAC

With

MDIO

Connectivity

McASP

McBSP

OSC

Boot ROM

10b

GPIO

TMS320DM6431

Digital Media Processor

SPRS342A – NOVEMBER 2006 – REVISED MARCH 2007

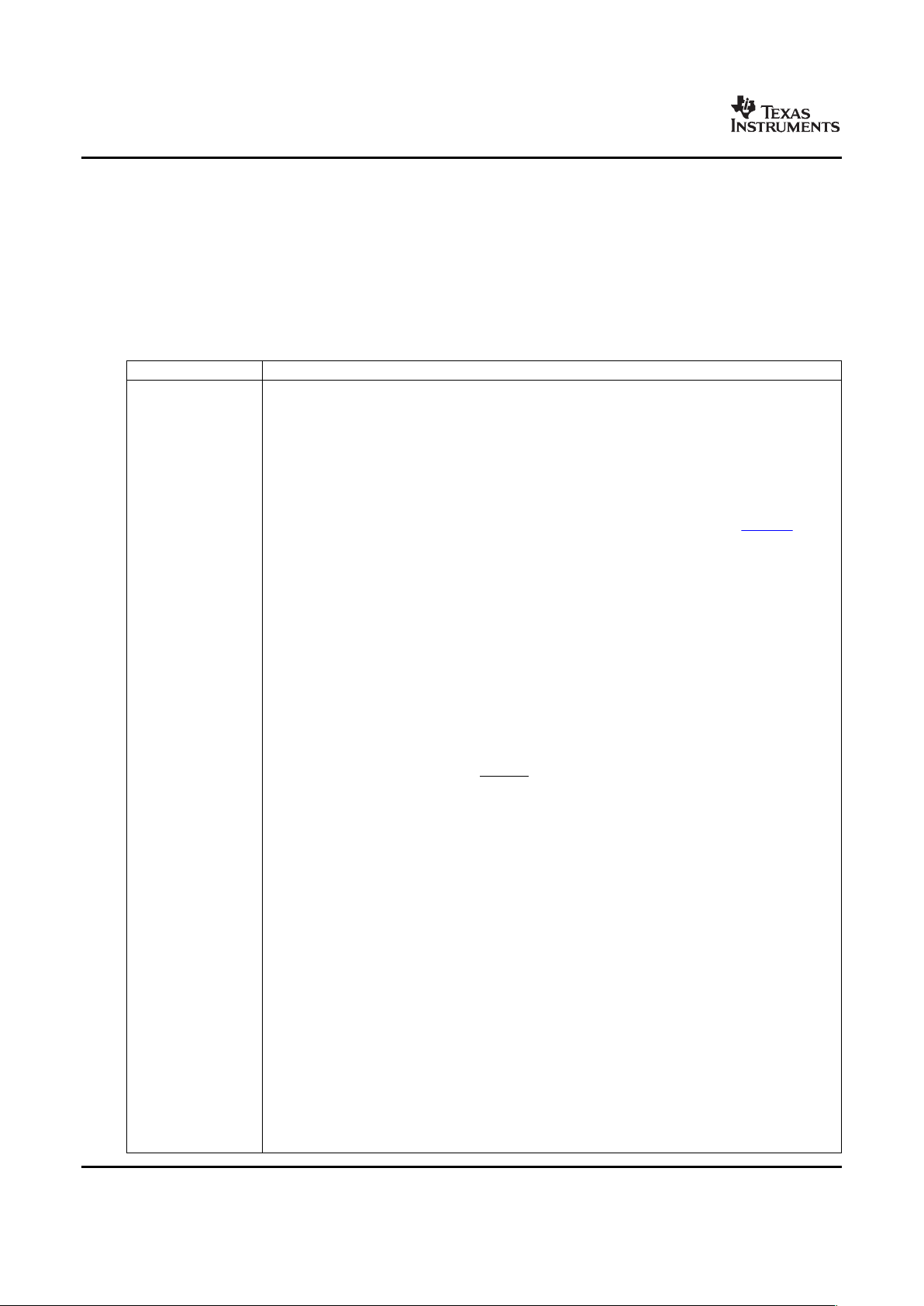

Figure 1-1 shows the functional block diagram of the DM6431 device.

Figure 1-1. TMS320DM6431 Functional Block Diagram

TMS320DM6431 Digital Media Processor4 Submit Documentation Feedback

www.ti.com

Contents

TMS320DM6431

Digital Media Processor

SPRS342A – NOVEMBER 2006 – REVISED MARCH 2007

5.3 Electrical Characteristics Over Recommended

1 TMS320DM6431 Digital Media Processor ........... 1

Ranges of Supply Voltage and Operating

1.1 Features .............................................. 1

Temperature (Unless Otherwise Noted) ........... 119

1.2 Description ............................................ 2

6 Peripheral Information and Electrical

1.3 Functional Block Diagram ............................ 4

Specifications ......................................... 120

Revision History ............................................... 6

6.1 Parameter Information ............................. 120

2 Device Overview ......................................... 7

6.2 Recommended Clock and Control Signal Transition

Behavior ............................................ 121

2.1 Device Characteristics ................................ 7

6.3 Power Supplies .................................... 122

2.2 CPU (DSP Core) Description ......................... 8

6.4 Enhanced Direct Memory Access (EDMA3)

2.3 C64x+ CPU .......................................... 11

Controller ........................................... 129

2.4 Memory Map Summary ............................. 12

6.5 Reset ............................................... 141

2.5 Pin Assignments .................................... 16

6.6 External Clock Input From MXI/CLKIN Pin ........ 150

2.6 Terminal Functions .................................. 24

6.7 Clock PLLs ......................................... 152

2.7 Device Support ...................................... 56

6.8 Interrupts ........................................... 157

2.8 Device and Development-Support Tool

6.9 External Memory Interface (EMIF) ................. 160

Nomenclature ....................................... 56

6.10 Video Processing Sub-System (VPSS) Overview . 169

2.9 Documentation Support ............................. 58

6.11 Universal Asynchronous Receiver/Transmitter

3 Device Configurations ................................. 59

(UART) ............................................. 174

3.1 System Module Registers ........................... 59

6.12 Inter-Integrated Circuit (I2C) ....................... 176

3.2 Power Considerations ............................... 60

6.13 Multichannel Buffered Serial Port (McBSP) ........ 180

3.3 Clock Considerations ................................ 62

6.14 Multichannel Audio Serial Port (McASP0)

3.4 Boot Sequence ...................................... 64

Peripheral .......................................... 188

3.5 Configurations At Reset ............................. 74

6.15 High-End Controller Area Network Controller

3.6 Configurations After Reset .......................... 75

(HECC) ............................................. 196

3.7 Multiplexed Pin Configurations ...................... 79

6.16 Ethernet Media Access Controller (EMAC) ........ 202

3.8 Device Initialization Sequence After Reset ........ 112

6.17 Management Data Input/Output (MDIO) .......... 209

3.9 Debugging Considerations ......................... 114

6.18 Timers .............................................. 211

4 System Interconnect ................................. 115

6.19 Pulse Width Modulator (PWM) ..................... 213

4.1 System Interconnect Block Diagram ............... 115

6.20 General-Purpose Input/Output (GPIO) ............. 215

5 Device Operating Conditions ....................... 117

6.21 IEEE 1149.1 JTAG ................................. 219

5.1 Absolute Maximum Ratings Over Operating

7 Mechanical Data ....................................... 221

Temperature Range (Unless Otherwise Noted) ... 117

7.1 Thermal Data for ZWT ............................. 221

5.2 Recommended Operating Conditions ............. 118

7.1.1 Thermal Data for ZDU ............................. 222

7.1.2 Packaging Information ............................. 222

Submit Documentation Feedback Contents 5

www.ti.com

PRODUCT PREVIEW

Revision History

TMS320DM6431

Digital Media Processor

SPRS342A – NOVEMBER 2006 – REVISED MARCH 2007

This data manual revision history highlights the technical changes made to the SPRS342 device-specific

data manual to make it an SPRS342A revision.

Scope: Applicable updates to the device family, specifically relating to the device, have been

incorporated.

• The RSV1 pin (E5, D4) must be left unconnected. Do not connect to power or ground.

• Upon exit from the bootloader code, all C64x+ memories are configured as all RAM, Cache is disabled.

• This is now a complete document. New sections and subsections have been added.

SEE ADDITIONS/MODIFICATIONS/DELETIONS

Global Added section cross-references throughout the entire document

Section 1.1 Section 1.1 , Features:

Deleted "/Debug" from the "Fully Software-Compatible With C64x" feature

Section 2.1 Section 2.1 , Device Characteristics:

Table 2-1 , Characteristics of the DM6431 Processor:

Added "MegaMdodule Rev ID"

Updated/Changed the "CPU ID + CPU Rev ID" row to reference the " TMS320DM6437/35/33/31 Digital

Media Processor (DMP) [Silicon Revisions 1.1 and 1.0] Silicon Errata (literature number SPRZ250 )."

Updated/Changed PLL Options " CLKIN1 frequency multiplier (27 MHz reference)" to " MXI/CLKIN

frequency multiplier (27 MHz reference)"

Section 2.4 Section 2.4 , Memory Map Summary:

Section 2.4 , Memory Map Summary:

Added "For all boot modes that default to ..." footnote

Table 2-4 , Configuration Memory Map Summary:

Deleted 0x01BC 0000 — 0x01BC 00FF AET Registers; now "Reserved"

Section 2.6 Section 2.6 , Terminal Functions:

Table 2-5 , Boot Terminal Functions:

Updated/Changed Bootmode[3:0] Descriptions to reference Section 3.4.1 , Boot Modes

Updated/Changed EM_BA[1:0]/(AEM0:1) DSECRIPTION from "...pinout type" to ..."pinout mode"

Table 2-10 , EMIFA Terminal Functions (EMIFA Pinout Mode 1, AEM[2:0] = 001):

Updated/Changed the DESCRIPTION for EM_A[12:0]

Table 2-11 , EMIFA Terminal Functions (EMIFA Pinout Mode 5, AEM[2:0] = 101):

Updated/Changed DESPCRIPTION for EM_CS2/GP[12]

Table 2-12 , DDR2 Memory Controller Terminal Functions:

Added "Output" pin direction to the DESCRIPTION for all address bus and control signals

Added "bi-directional" to the DESCRIPTION for the DDR2 data bus

Table 2-13 , EMAC and MDIO Terminal Functions:

Updated/Changed the "MTXCLK/GP[73]" DESCRIPTION from "output" to "input"

Updated/Changed the "MTXD0/GP[72]" DESCRIPTION from "TXD0" to " MTXD0"

Updated/Changed the "MRXD3/GP[82]" DESCRIPTION from "RXD3" to " MRXD3"

Added " (I/O/Z)" to the MDIO/GP[83] DESCRIPTION

Table 2-14 , VPFE Terminal Functions:

Updated/Changed the DESCRIPTION for the following signals: CCDC9 through CCDC0 from "CCD AFE

mode" to "CCD Raw mode"

Added "In 8-bit YCbCr mode, this pin should not be used." to the DESCRIPTION for CCD8 and CCD9

Table 2-23 , Standalone GPIO 3.3 V Terminal Functions:

Updated/Changed the DESCRIPTION for GP[28] to "... pulled down via an external resistor"

Table 2-24 , Reserved Terminal Functions:

Deleted TYPE for the following signals: RSV4 through RSV15

Section 2.8 Section 2.8 , Device and Development-Support Tool Nomenclature:

Updated/Changed Figure 2-10 , Device Nomenclature

Section 5.3 Section 5.3 , Electrical Characteristics Over Recommended Ranges of Supply Voltage and Operating

Temperature (Unless Otherwise Noted):

Updated/Changed CIand COMAX values from "10 pF" to "5 pF"

Updated/Changed the "Measured under the following conditions: ..." footnote

6 Revision History Submit Documentation Feedback

www.ti.com

2 Device Overview

2.1 Device Characteristics

TMS320DM6431

Digital Media Processor

SPRS342A – NOVEMBER 2006 – REVISED MARCH 2007

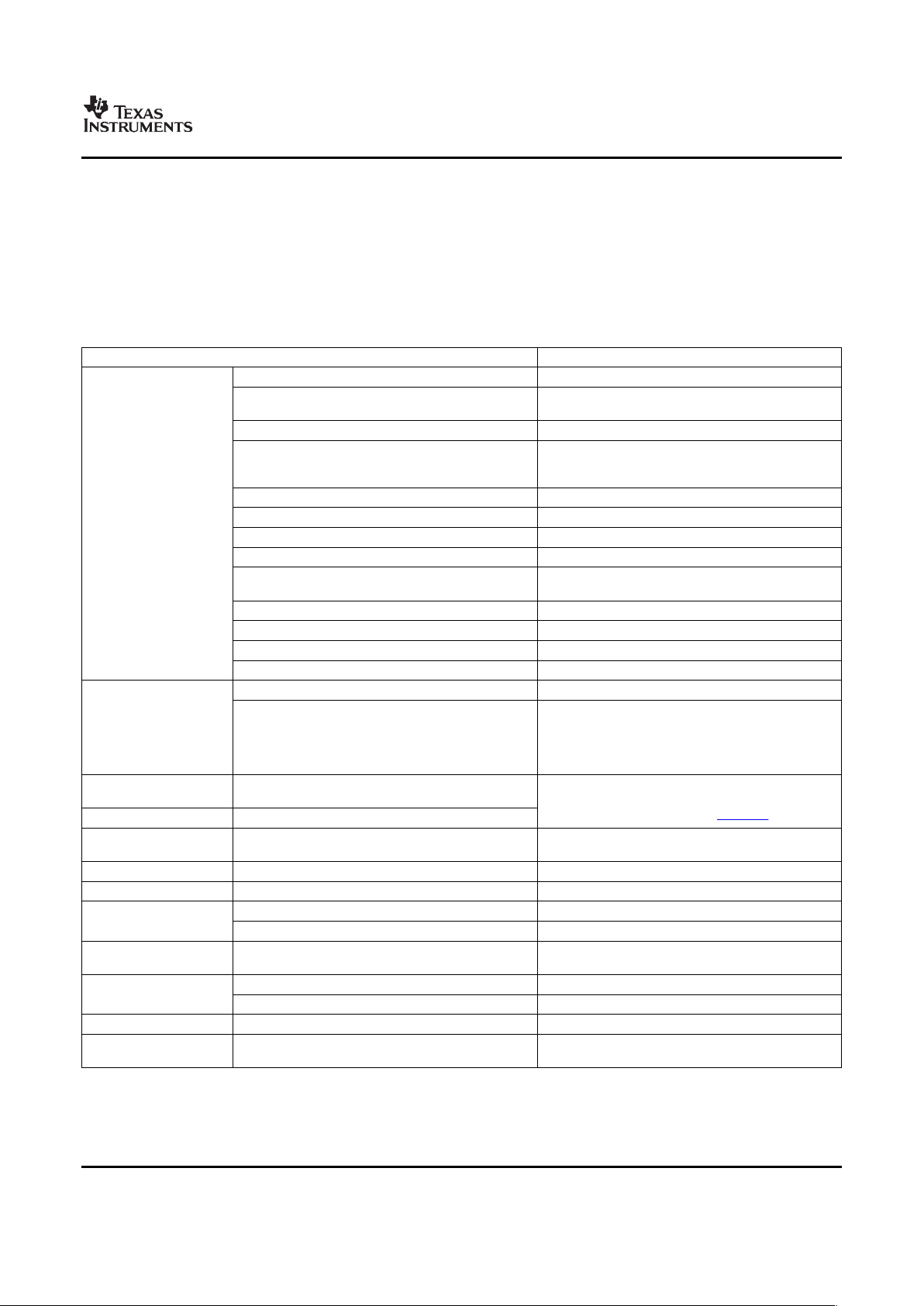

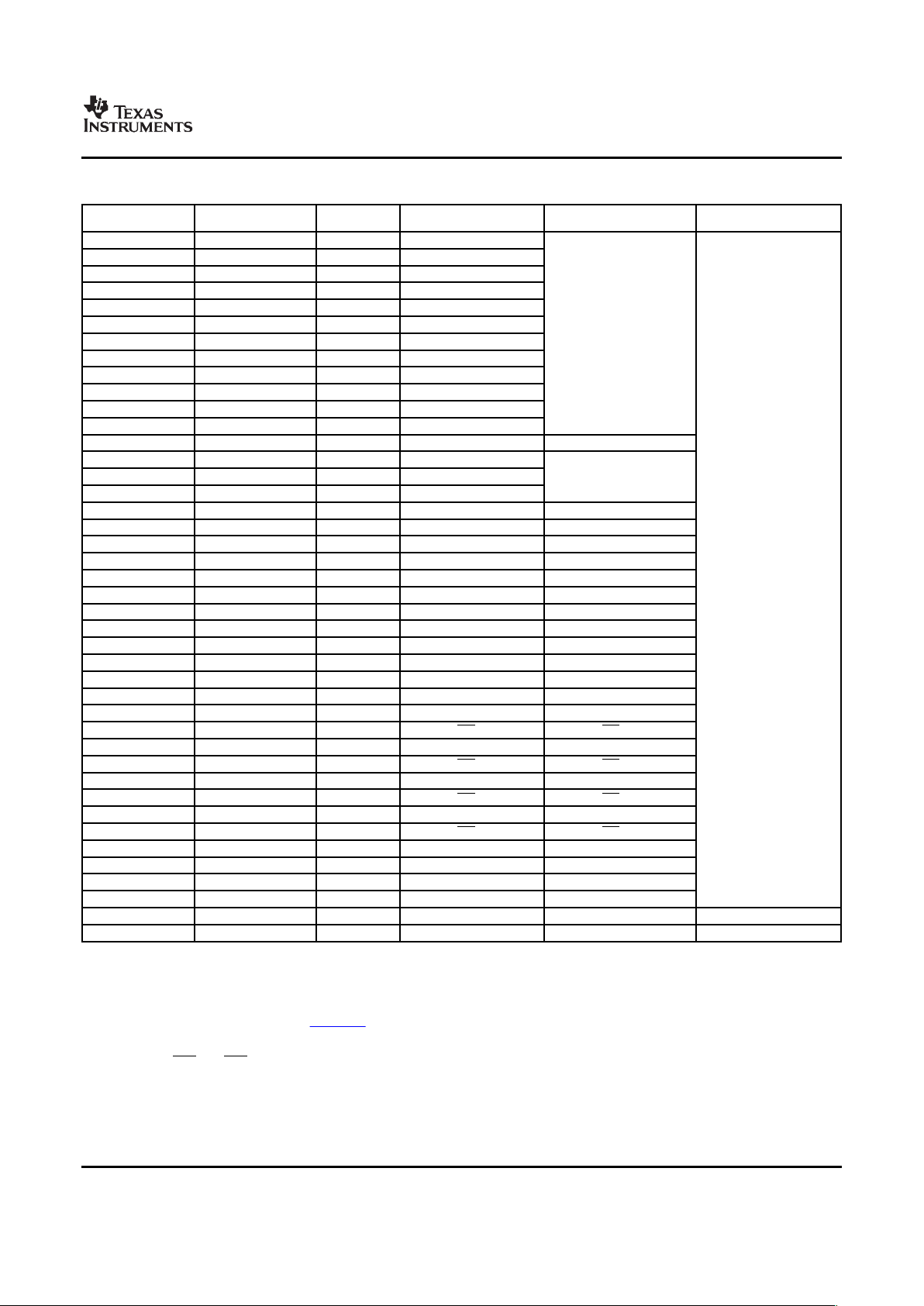

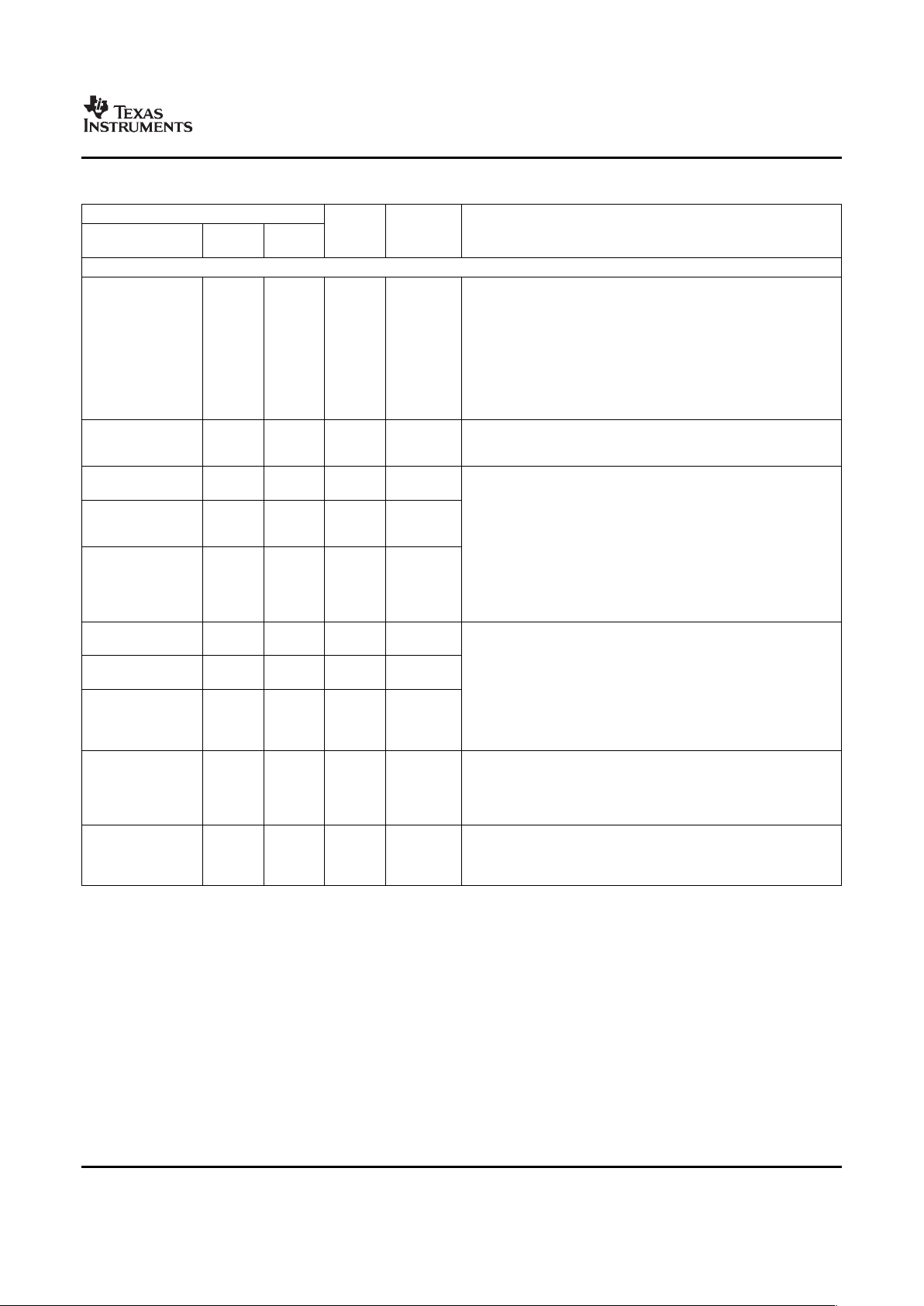

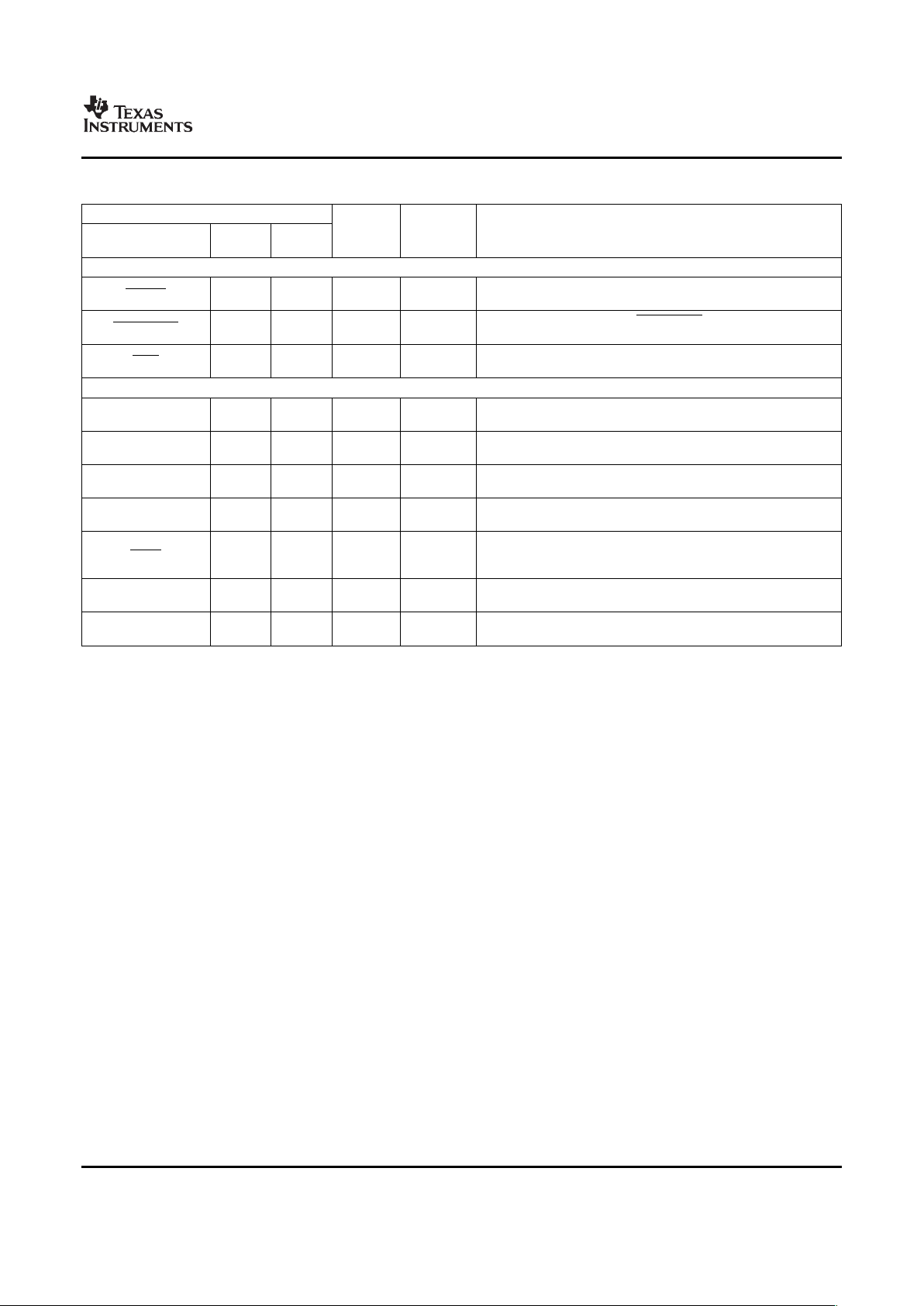

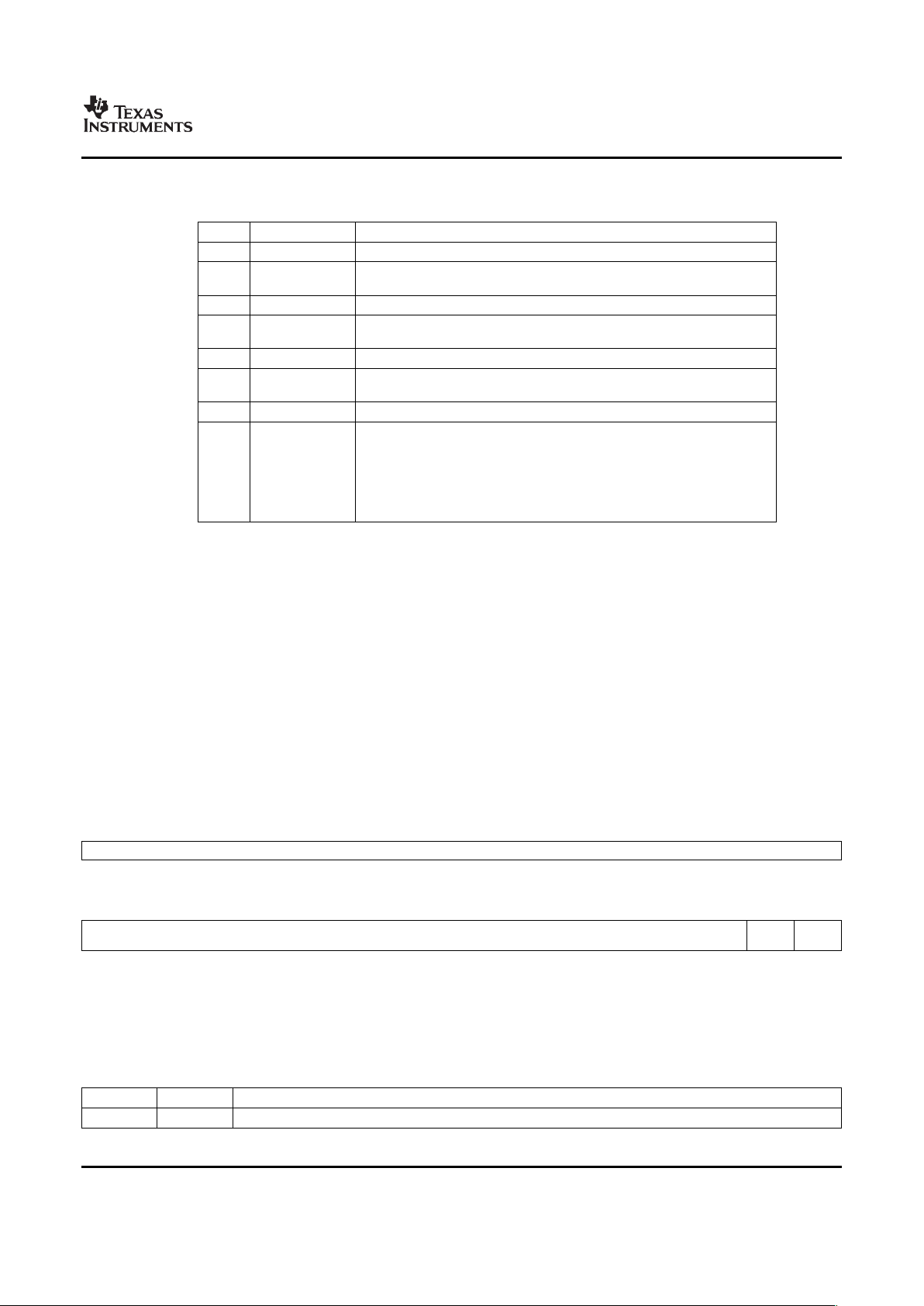

Table 2-1 , provides an overview of the TMS320DM6431 DSP. The tables show significant features of the

DM6431 device, including the capacity of on-chip RAM, the peripherals, the CPU frequency, and the

package type with pin count.

Table 2-1. Characteristics of the DM6431 Processor

HARDWARE FEATURES DM6431

DDR2 Memory Controller (16-bit bus width) [1.8 V I/O]

Asynchronous (8-bit bus width),

Asynchronous EMIF [EMIFA]

RAM, Flash, (8-bit NOR or 8-bit NAND)

EDMA3 1 (64 independent channels, 8 QDMA channels)

2 64-bit General Purpose

Timers (configurable as 2 64-bit or 4 32-bit)

1 64-bit Watch Dog

Peripherals

UART 1 (with RTS and CTS flow control)

Not all peripherals pins

I2C 1 (Master/Slave)

are available at the same

time (For more detail, see

McBSP 1

the Device Configuration

McASP 1 (4 serailizers)

section).

10/100 Ethernet MAC (EMAC) with

1

Management Data Input/Output (MDIO)

General-Purpose Input/Output Port (GPIO) Up to 111 pins

PWM 3 outputs

Configurable Video Port 1 Input (VPFE)

HECC 1

Size (Bytes) 128KB RAM, 64KB ROM

32K-Byte (32KB) L1 Program (L1P) RAM/Cache

(Cache up to 32KB)

On-Chip Memory

Organization 32KB L1 Data (L1D) RAM/Cache (Cache up to 32KB)

64KB Unified Mapped RAM/Cache (L2)

64KB Boot ROM

Revision ID Register (MM_REVID.[15:0])

See the TMS320DM6437/35/33/31 Digital Media

MegaModule Rev ID

(address location: 0x0181 2000)

Processor (DMP) [Silicon Revisions 1.1 and 1.0]

Silicon Errata (literature number SPRZ250 ).

CPU ID + CPU Rev ID Control Status Register (CSR.[31:16])

JTAGID register See Section 6.21.1 , JTAG ID (JTAGID) Register

JTAG BSDL_ID

(address location: 0x01C4 0028) Description(s)

CPU Frequency MHz 300

Cycle Time ns 3.33 ns (-300)

Core (V) 1.2 V (-300)

Voltage

I/O (V) 1.8 V, 3.3 V

MXI/CLKIN frequency multiplier

PLL Options x1 (Bypass), x14 to x30

(27 MHz reference)

16 x 16 mm, 0.8 mm pitch 361-Pin BGA (ZWT)

BGA Package(s)

23 x 23 mm, 1.0 mm pitch 376-Pin BGA (ZDU)

Process Technology µm 0.09 µm

Product Preview (PP), Advance Information (AI),

Product Status

(1)

PP

or Production Data (PD)

(1) PRODUCT PREVIEW information concerns experimental products (designated as TMX) that are in the formative or design phase of

development. Characteristic data and other specifications are design goals. Texas Instruments reserves the right to change or

discontinue these products without notice.

Submit Documentation Feedback Device Overview 7

www.ti.com

PRODUCT PREVIEW

2.2 CPU (DSP Core) Description

TMS320DM6431

Digital Media Processor

SPRS342A – NOVEMBER 2006 – REVISED MARCH 2007

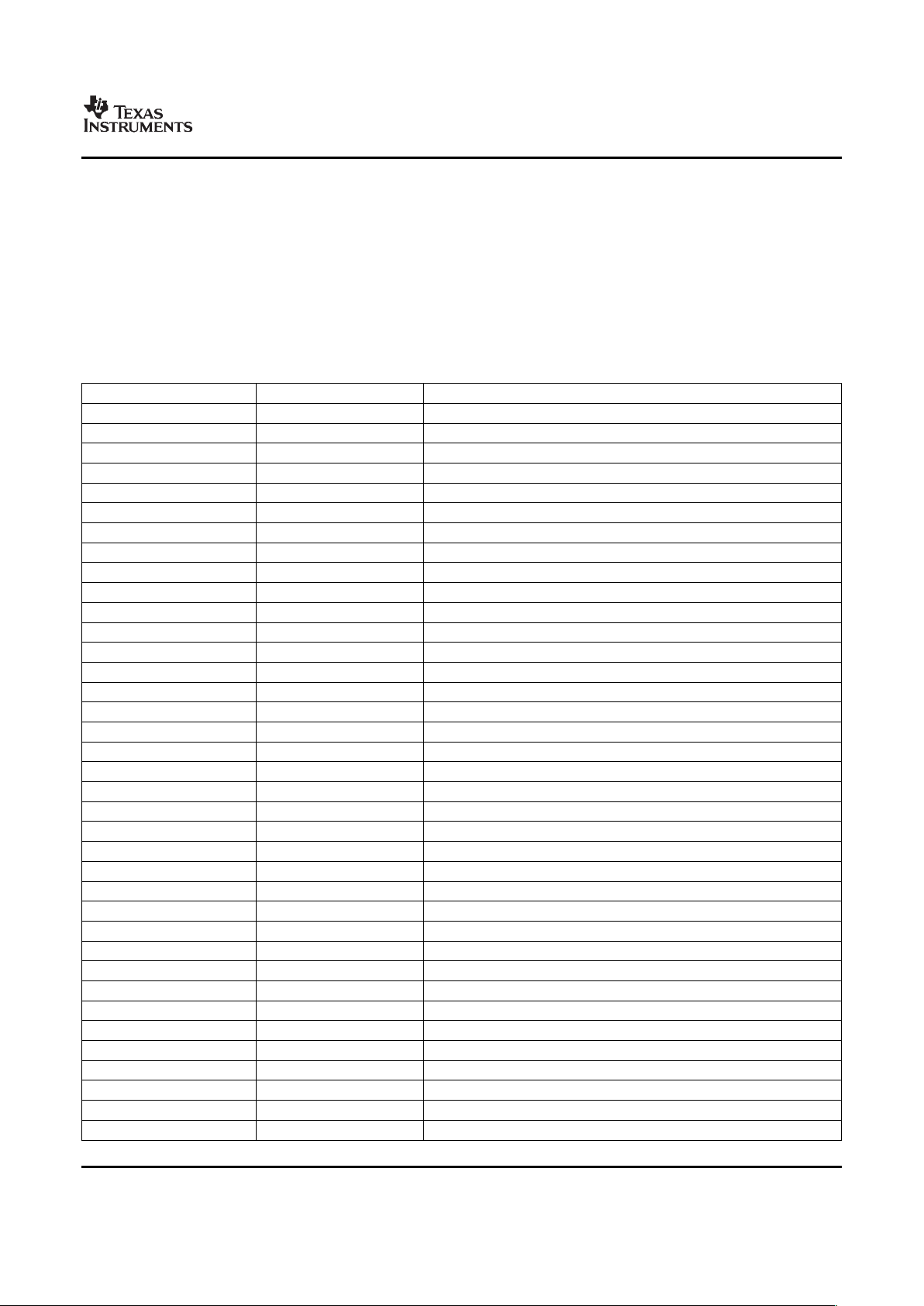

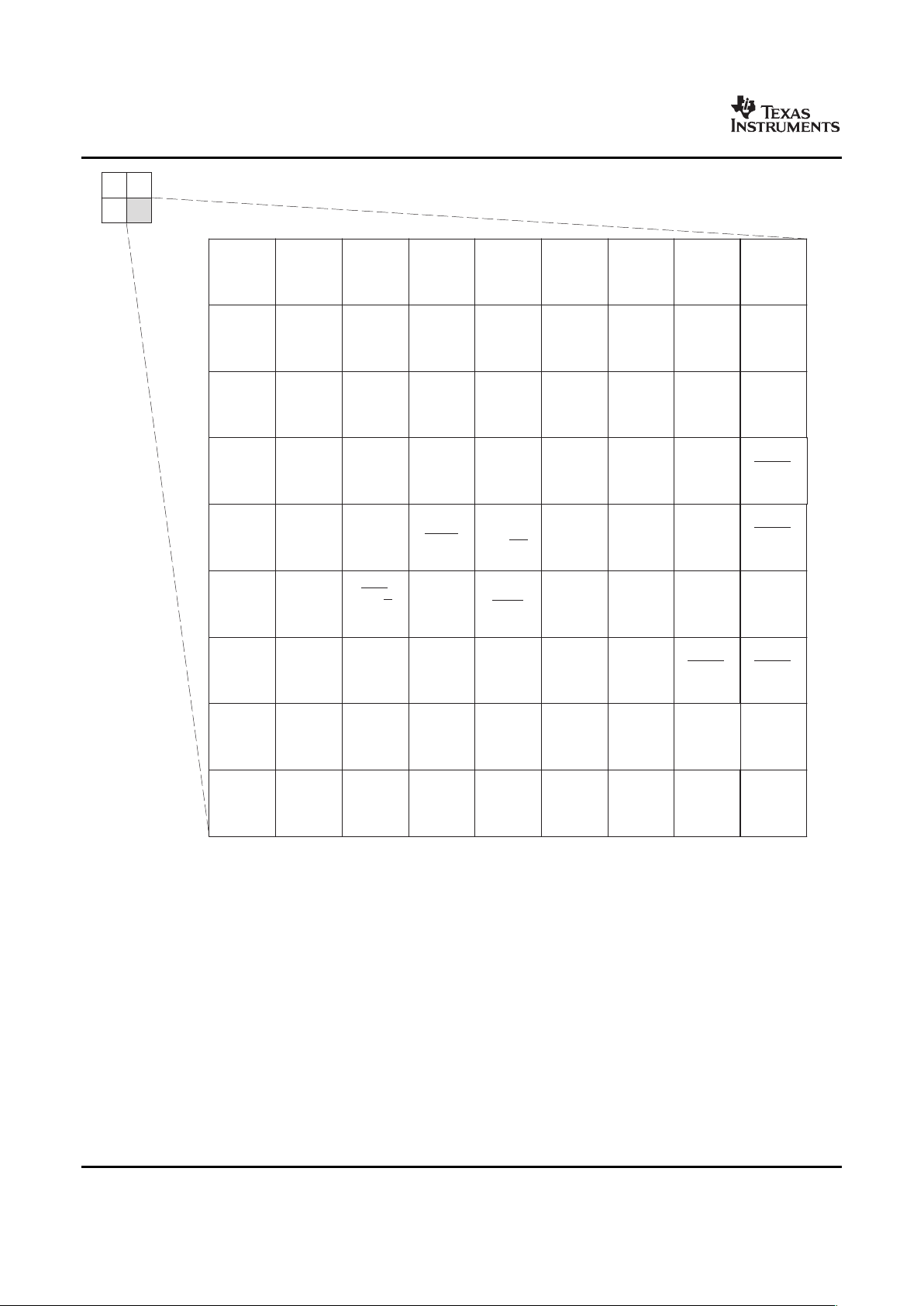

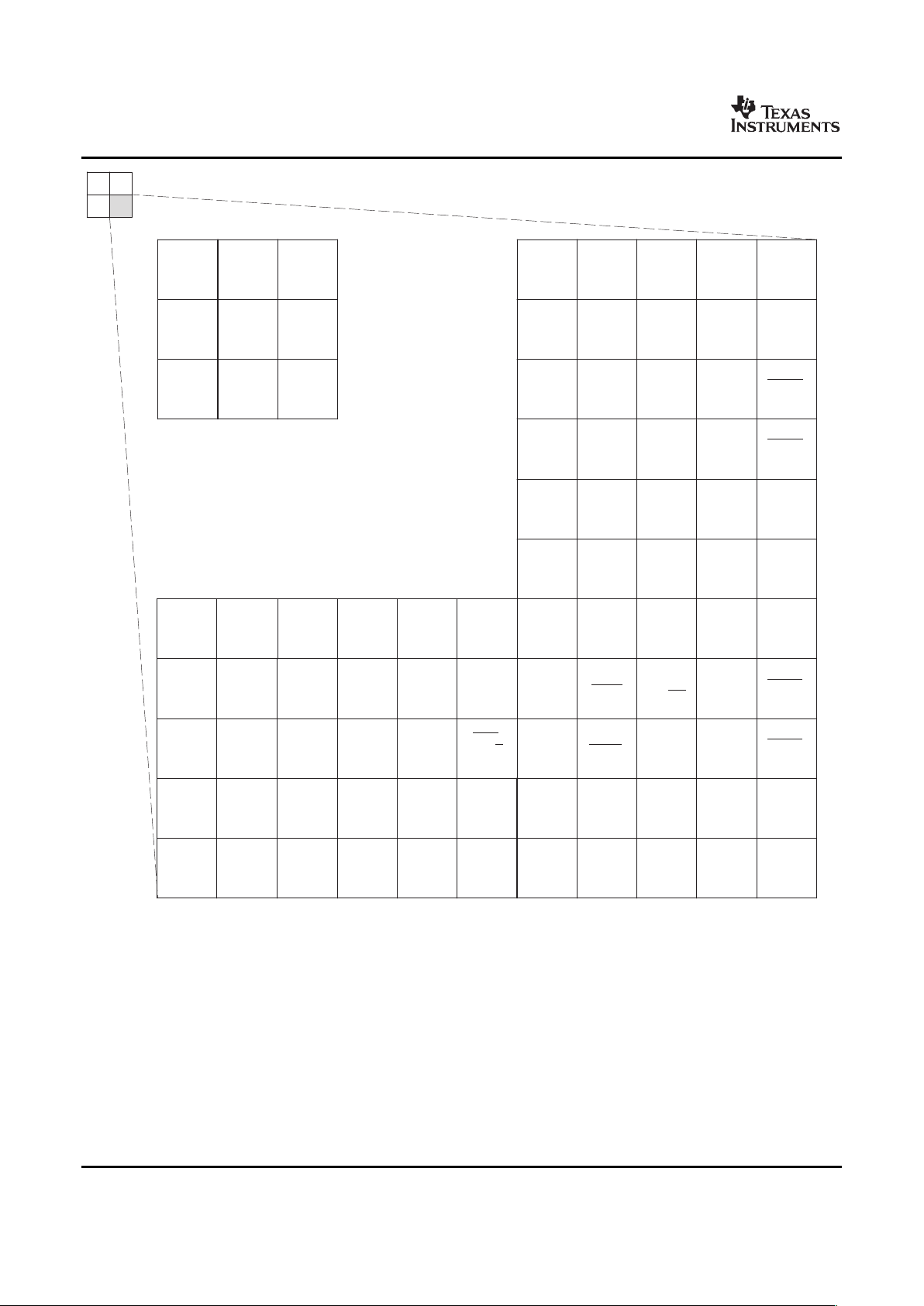

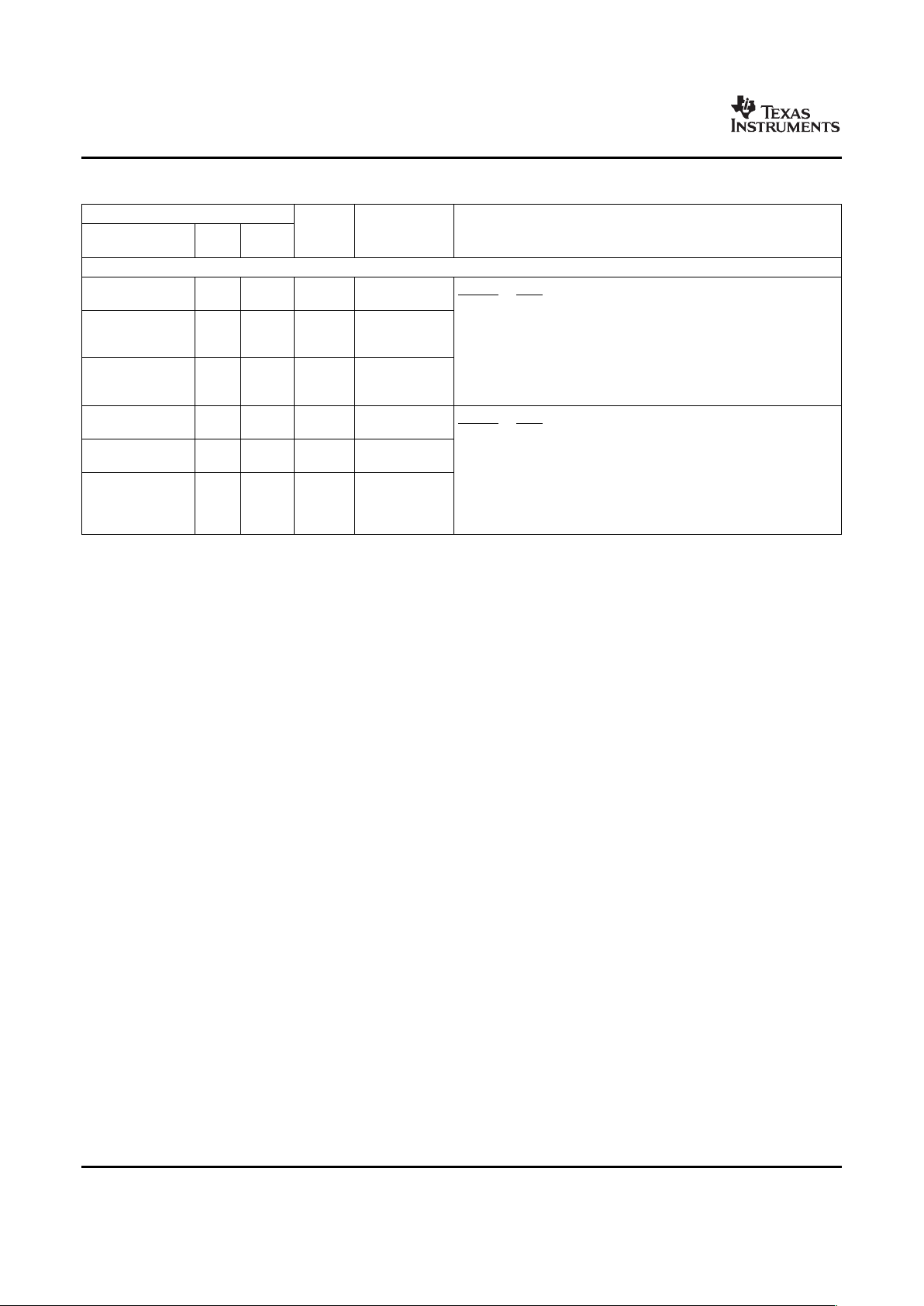

The C64x+ Central Processing Unit (CPU) consists of eight functional units, two register files, and two

data paths as shown in Figure 2-1 . The two general-purpose register files (A and B) each contain

32 32-bit registers for a total of 64 registers. The general-purpose registers can be used for data or can be

data address pointers. The data types supported include packed 8-bit data, packed 16-bit data, 32-bit

data, 40-bit data, and 64-bit data. Values larger than 32 bits, such as 40-bit-long or 64-bit-long values are

stored in register pairs, with the 32 LSBs of data placed in an even register and the remaining 8 or

32 MSBs in the next upper register (which is always an odd-numbered register).

The eight functional units (.M1, .L1, .D1, .S1, .M2, .L2, .D2, and .S2) are each capable of executing one

instruction every clock cycle. The .M functional units perform all multiply operations. The .S and .L units

perform a general set of arithmetic, logical, and branch functions. The .D units primarily load data from

memory to the register file and store results from the register file into memory.

The C64x+ CPU extends the performance of the C64x core through enhancements and new features.

Each C64x+ .M unit can perform one of the following each clock cycle: one 32 x 32 bit multiply, one 16 x

32 bit multiply, two 16 x 16 bit multiplies, two 16 x 32 bit multiplies, two 16 x 16 bit multiplies with

add/subtract capabilities, four 8 x 8 bit multiplies, four 8 x 8 bit multiplies with add operations, and four

16 x 16 multiplies with add/subtract capabilities (including a complex multiply). There is also support for

Galois field multiplication for 8-bit and 32-bit data. Many communications algorithms such as FFTs and

modems require complex multiplication. The complex multiply (CMPY) instruction takes for 16-bit inputs

and produces a 32-bit real and a 32-bit imaginary output. There are also complex multiplies with rounding

capability that produces one 32-bit packed output that contain 16-bit real and 16-bit imaginary values. The

32 x 32 bit multiply instructions provide the extended precision necessary for audio and other

high-precision algorithms on a variety of signed and unsigned 32-bit data types.

The .L or (Arithmetic Logic Unit) now incorporates the ability to do parallel add/subtract operations on a

pair of common inputs. Versions of this instruction exist to work on 32-bit data or on pairs of 16-bit data

performing dual 16-bit add and subtracts in parallel. There are also saturated forms of these instructions.

The C64x+ core enhances the .S unit in several ways. In the C64x core, dual 16-bit MIN2 and MAX2

comparisons were only available on the .L units. On the C64x+ core they are also available on the .S unit

which increases the performance of algorithms that do searching and sorting. Finally, to increase data

packing and unpacking throughput, the .S unit allows sustained high performance for the quad 8-bit/16-bit

and dual 16-bit instructions. Unpack instructions prepare 8-bit data for parallel 16-bit operations. Pack

instructions return parallel results to output precision including saturation support.

Other new features include:

• SPLOOP - A small instruction buffer in the CPU that aids in creation of software pipelining loops where

multiple iterations of a loop are executed in parallel. The SPLOOP buffer reduces the code size

associated with software pipelining. Furthermore, loops in the SPLOOP buffer are fully interruptible.

• Compact Instructions - The native instruction size for the C6000 devices is 32 bits. Many common

instructions such as MPY, AND, OR, ADD, and SUB can be expressed as 16 bits if the C64x+

compiler can restrict the code to use certain registers in the register file. This compression is

performed by the code generation tools.

Device Overview8 Submit Documentation Feedback

www.ti.com

TMS320DM6431

Digital Media Processor

SPRS342A – NOVEMBER 2006 – REVISED MARCH 2007

• Instruction Set Enhancement - As noted above, there are new instructions such as 32-bit

multiplications, complex multiplications, packing, sorting, bit manipulation, and 32-bit Galois field

multiplication.

• Exceptions Handling - Intended to aid the programmer in isolating bugs. The C64x+ CPU is able to

detect and respond to exceptions, both from internally detected sources (such as illegal op-codes) and

from system events (such as a watchdog time expiration).

• Privilege - Defines user and supervisor modes of operation, allowing the operating system to give a

basic level of protection to sensitive resources. Local memory is divided into multiple pages, each with

read, write, and execute permissions.

• Time-Stamp Counter - Primarily targeted for Real-Time Operating System (RTOS) robustness, a

free-running time-stamp counter is implemented in the CPU which is not sensitive to system stalls.

For more details on the C64x+ CPU and its enhancements over the C64x architecture, see the following

documents:

• TMS320C64x/C64x+ DSP CPU and Instruction Set Reference Guide (literature number SPRU732 )

• TMS320C64x+ DSP Megamodule Reference Guide (literature number SPRU871 )

• TMS320C64x to TMS320C64x+ CPU Migration Guide Application Report (literature number SPRAA84 )

• TMS320C64x+ DSP Cache User's Guide (literature number SPRU862 )

Submit Documentation Feedback Device Overview 9

www.ti.com

PRODUCT PREVIEW

src2

src2

.D1

.M1

.S1

.L1

long src

odd dst

src2

src1

src1

src1

src1

even dst

even dst

odd dst

dst1

dst

src2

src2

src2

long src

DA1

ST1b

LD1b

LD1a

ST1a

Data path A

Odd

register

file A

(A1, A3,

A5...A31)

Odd

register

file B

(B1, B3,

B5...B31)

.D2

src1

dst

src2

DA2

LD2a

LD2b

src2

.M2

src1

dst1

.S2

src1

even dst

long src

odd dst

ST2a

ST2b

long src

.L2

even dst

odd dst

src1

Data path B

Control Register

32 MSB

32 LSB

dst2

(A)

32 MSB

32 LSB

2x

1x

32 LSB

32 MSB

32 LSB

32 MSB

dst2

(B)

(B)

(A)

8

8

8

8

32

32

32

32

(C)

(C)

Even

register

file A

(A0, A2,

A4...A30)

Even

register

file B

(B0, B2,

B4...B30)

(D)

(D)

(D)

(D)

A. On .M unit, dst2 is 32 MSB.

B. On .M unit, dst1 is 32 LSB.

C. On C64x CPU .M unit, src2 is 32 bits; on C64x+ CPU .M unit, src2 is 64 bits.

D. On .L and .S units, odd dst connects to odd register files and even dst connects to even register files.

TMS320DM6431

Digital Media Processor

SPRS342A – NOVEMBER 2006 – REVISED MARCH 2007

Figure 2-1. TMS320C64x+™ CPU (DSP Core) Data Paths

10 Device Overview Submit Documentation Feedback

www.ti.com

2.3 C64x+ CPU

TMS320DM6431

Digital Media Processor

SPRS342A – NOVEMBER 2006 – REVISED MARCH 2007

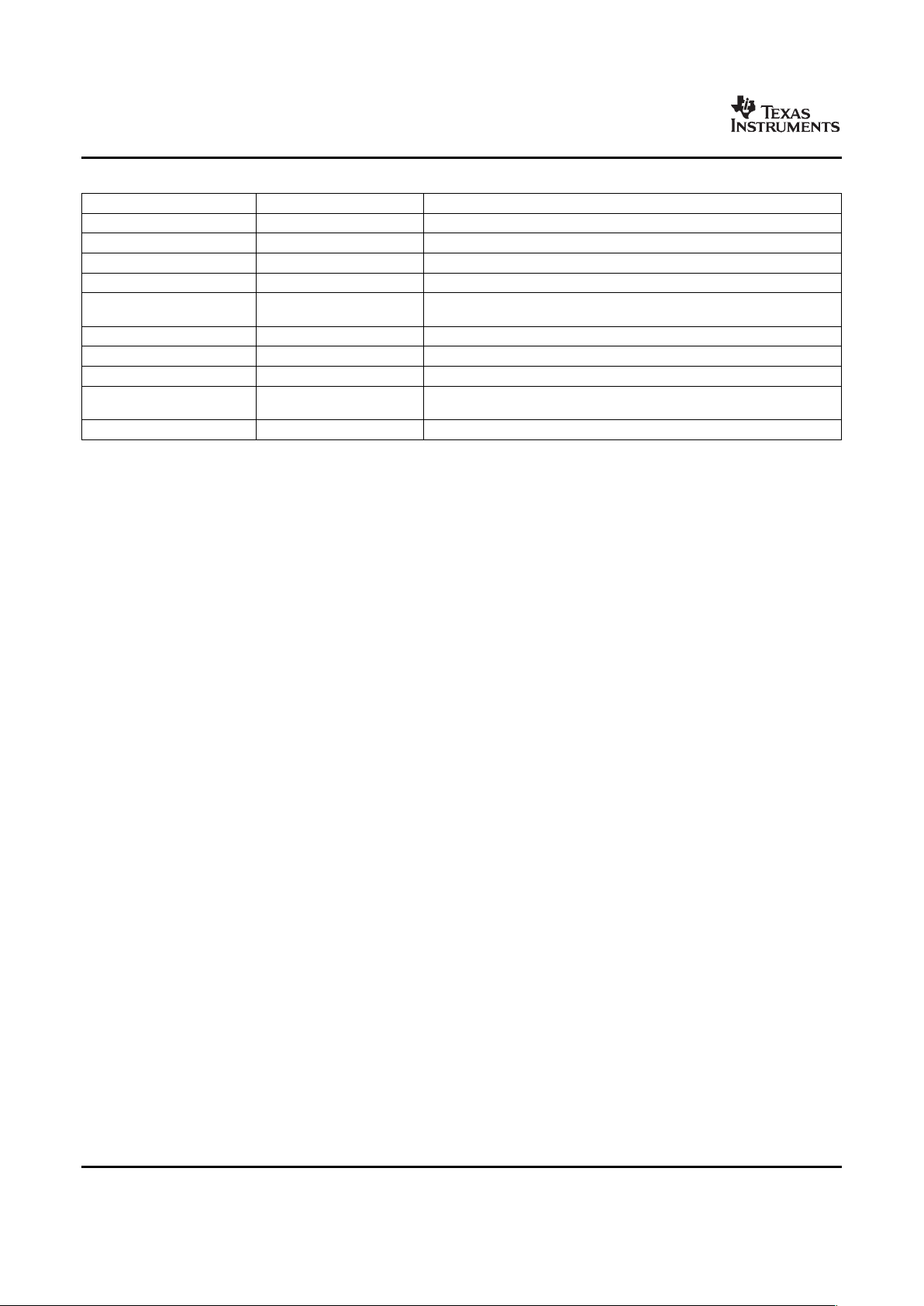

The C64x+ core uses a two-level cache-based architecture. The Level 1 Program memory/cache (L1P)

consists of 32 KB memory space that can be configured as mapped memory or direct mapped cache. The

Level 1 Data memory/cache (L1D) consists of 32 KB memory space that can be configured as mapped

memory or 2-way set associated cache. The Level 2 memory/cache (L2) consists of a 64 KB memory

space that is shared between program and data space. L2 memory can be configured as mapped

memory, cache, or a combination of both.

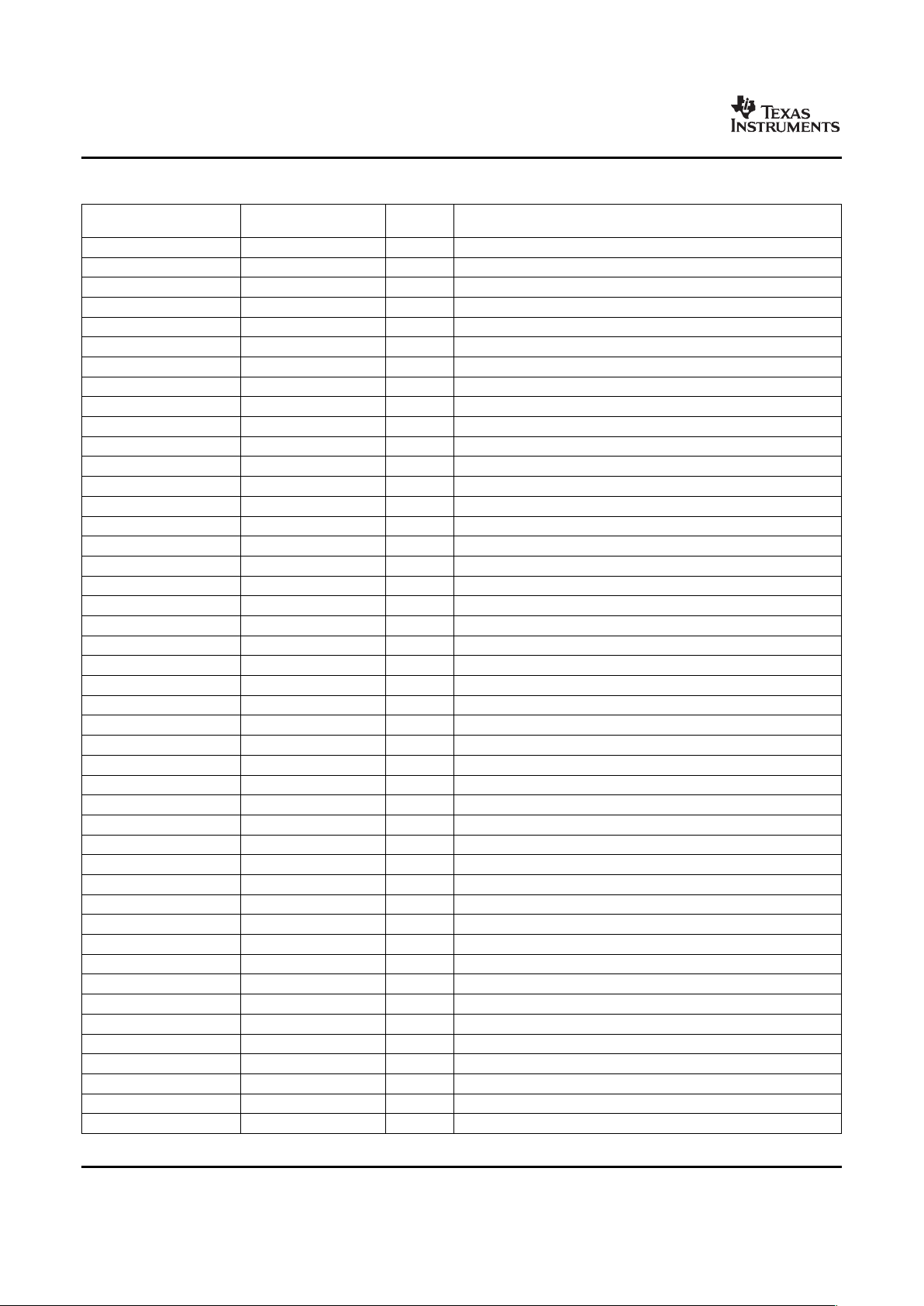

Table 2-2 shows a memory map of the C64x+ CPU cache registers for the device.

Table 2-2. C64x+ Cache Registers

HEX ADDRESS RANGE REGISTER ACRONYM DESCRIPTION

0x0184 0000 L2CFG L2 Cache configuration register

0x0184 0020 L1PCFG L1P Size Cache configuration register

0x0184 0024 L1PCC L1P Freeze Mode Cache configuration register

0x0184 0040 L1DCFG L1D Size Cache configuration register

0x0184 0044 L1DCC L1D Freeze Mode Cache configuration register

0x0184 0048 - 0x0184 0FFC - Reserved

0x0184 1000 EDMAWEIGHT L2 EDMA access control register

0x0184 1004 - 0x0184 1FFC - Reserved

0x0184 2000 L2ALLOC0 L2 allocation register 0

0x0184 2004 L2ALLOC1 L2 allocation register 1

0x0184 2008 L2ALLOC2 L2 allocation register 2

0x0184 200C L2ALLOC3 L2 allocation register 3

0x0184 2010 - 0x0184 3FFF - Reserved

0x0184 4000 L2WBAR L2 writeback base address register

0x0184 4004 L2WWC L2 writeback word count register

0x0184 4010 L2WIBAR L2 writeback invalidate base address register

0x0184 4014 L2WIWC L2 writeback invalidate word count register

0x0184 4018 L2IBAR L2 invalidate base address register

0x0184 401C L2IWC L2 invalidate word count register

0x0184 4020 L1PIBAR L1P invalidate base address register

0x0184 4024 L1PIWC L1P invalidate word count register

0x0184 4030 L1DWIBAR L1D writeback invalidate base address register

0x0184 4034 L1DWIWC L1D writeback invalidate word count register

0x0184 4038 - Reserved

0x0184 4040 L1DWBAR L1D Block Writeback

0x0184 4044 L1DWWC L1D Block Writeback

0x0184 4048 L1DIBAR L1D invalidate base address register

0x0184 404C L1DIWC L1D invalidate word count register

0x0184 4050 - 0x0184 4FFF - Reserved

0x0184 5000 L2WB L2 writeback all register

0x0184 5004 L2WBINV L2 writeback invalidate all register

0x0184 5008 L2INV L2 Global Invalidate without writeback

0x0184 500C - 0x0184 5027 - Reserved

0x0184 5028 L1PINV L1P Global Invalidate

0x0184 502C - 0x0184 5039 - Reserved

0x0184 5040 L1DWB L1D Global Writeback

0x0184 5044 L1DWBINV L1D Global Writeback with Invalidate

Submit Documentation Feedback Device Overview 11

www.ti.com

PRODUCT PREVIEW

2.4 Memory Map Summary

TMS320DM6431

Digital Media Processor

SPRS342A – NOVEMBER 2006 – REVISED MARCH 2007

Table 2-2. C64x+ Cache Registers (continued)

HEX ADDRESS RANGE REGISTER ACRONYM DESCRIPTION

0x0184 5048 L1DINV L1D Global Invalidate without writeback

0x0184 8000 - 0x0184 80BC MAR0 - MAR47 Reserved (corresponds to byte address 0x0000 0000 - 0x2FFF FFFF)

0x0184 80C0 - 0x0184 80FC MAR48 - MAR63 Reserved (corresponds to byte address 0x3000 0000 - 0x3FFF FFFF)

0x0184 8100 - 0x0184 8104 MAR64 - MAR65 Reserved (corresponds to byte address 0x4000 0000 - 0x41FF FFFF)

Memory Attribute Registers for EMIFA

0x0184 8108 - 0x0184 8124 MAR66 - MAR73

(corresponds to byte address 0x4200 0000 - 0x49FF FFFF)

0x0184 8128 - 0x0184 812C MAR74 - MAR75 Reserved (corresponds to byte address 0x4A00 0000 - 0x4BFF FFFF)

0x0184 8130 - 0x0184 813C MAR76 - MAR79 Reserved (corresponds to byte address 0x4C00 0000 - 0x4FFF FFFF)

0x0184 8140- 0x0184 81FC MAR80 - MAR127 Reserved (corresponds to byte address 0x5000 0000 - 0x7FFF FFFF)

Memory Attribute Registers for DDR2

0x0184 8200 - 0x0184 823C MAR128 - MAR143

(corresponds to byte address 0x8000 0000 - 0x8FFF FFFF)

0x0184 8240 - 0x0184 83FC MAR144 - MAR255 Reserved (corresponds to byte address 0x9000 0000 - 0xFFFF FFFF)

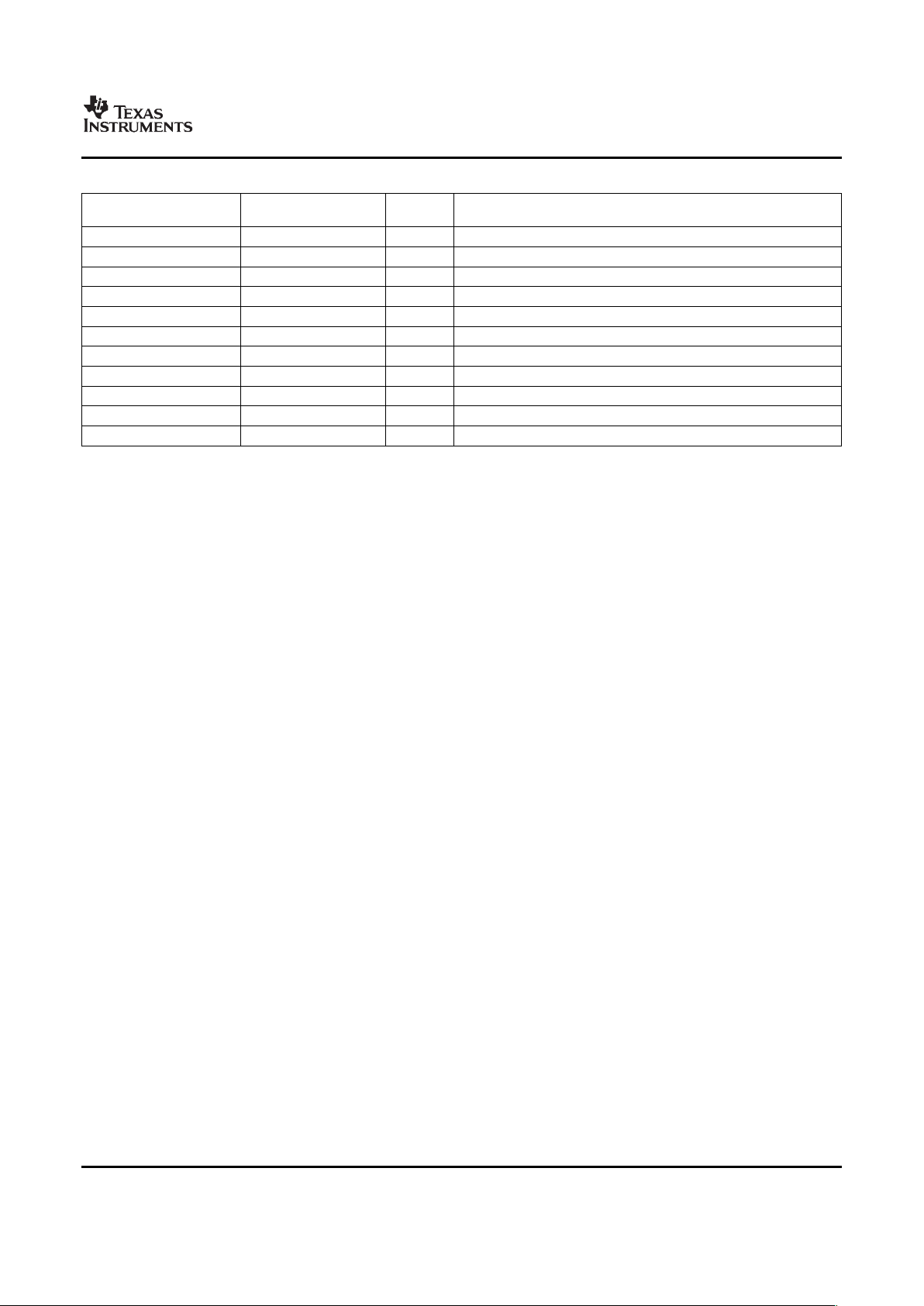

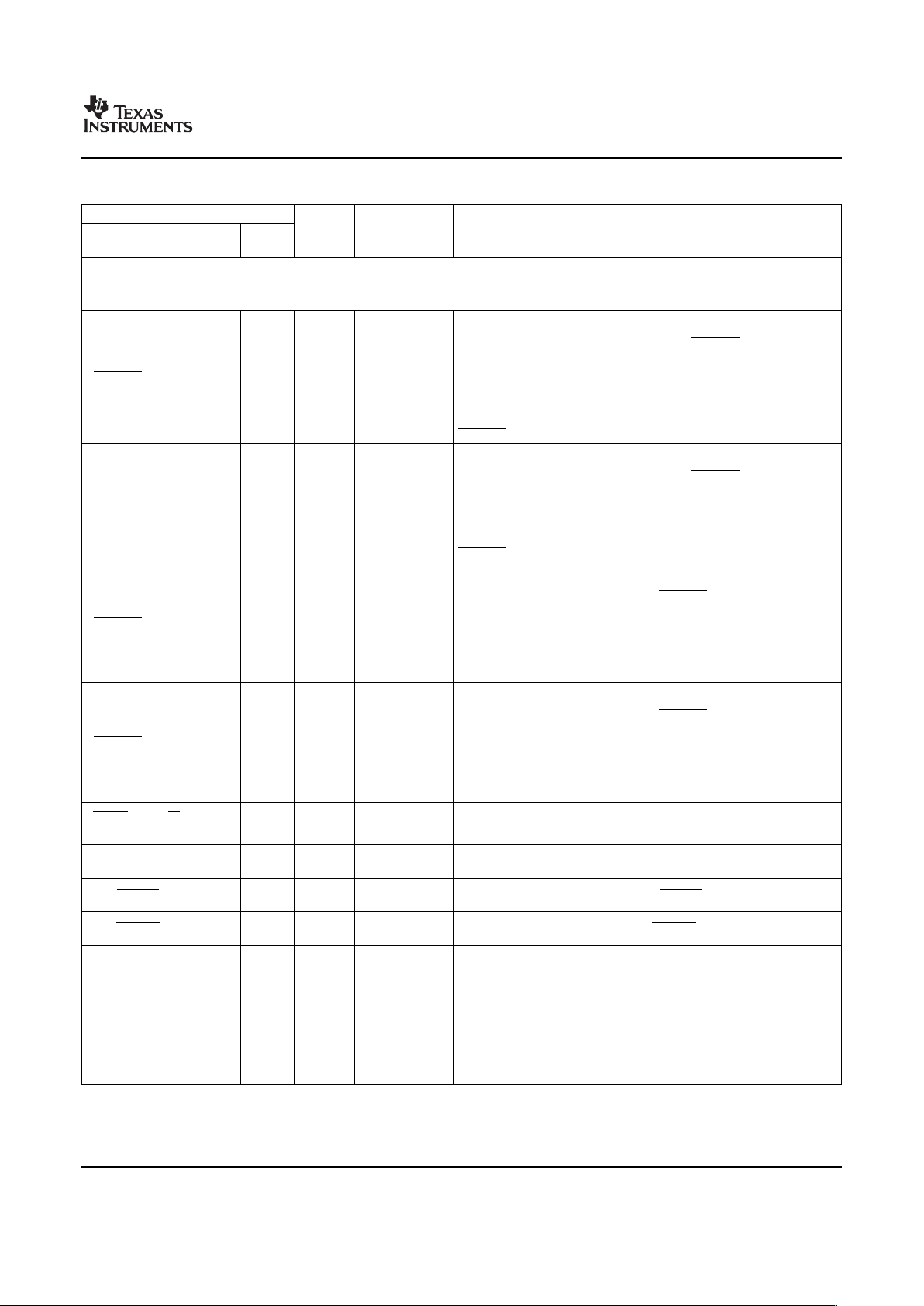

Table 2-3 shows the memory map address ranges of the device. Table 2-4 depicts the expanded map of

the Configuration Space (0x0180 0000 through 0x0FFF FFFF). The device has multiple on-chip memories

associated with its two processors and various subsystems. To help simplify software development a

unified memory map is used where possible to maintain a consistent view of device resources across all

bus masters.

Device Overview12 Submit Documentation Feedback

www.ti.com

TMS320DM6431

Digital Media Processor

SPRS342A – NOVEMBER 2006 – REVISED MARCH 2007

Table 2-3. Memory Map Summary

START END SIZE C64x+ EDMA PERIPHERAL VPSS

ADDRESS ADDRESS (Bytes) MEMORY MAP MEMORY MAP MEMORY MAP

0x0000 0000 0x000F FFFF 1M Reserved

0x0010 0000 0x0010 FFFF 64K Boot ROM

0x0011 0000 0x007F FFFF 7M-64K Reserved

0x0080 0000 0x0080 FFFF 64K Reserved

0x0081 0000 0x0081 FFFF 64K L2 RAM/Cache

(1)

0x0082 0000 0x00E0 7FFF 6048K Reserved

Reserved

0x00E0 8000 0x00E0 FFFF 32K L1P RAM/Cache

(1)

0x00E1 0000 0x00F0 3FFF 976K Reserved

0x00F0 4000 0x00F0 FFFF 48K Reserved

0x00F1 0000 0x00F1 7FFF 32K L1D RAM/Cache

(1)

0x00F1 8000 0x017F FFFF 9120K Reserved

0x0180 0000 0x01BF FFFF 4M CFG Space

0x01C0 0000 0x01FF FFFF 4M CFG Bus Peripherals CFG Bus Peripherals

0x0200 0000 0x100F FFFF 225M Reserved

0x1010 0000 0x1010 FFFF 64K Boot ROM Reserved

0x1011 0000 0x107F FFFF 7M-48K Reserved

0x1080 0000 0x1080 FFFF 64K Reserved Reserved

0x1081 0000 0x1081 FFFF 64K L2 RAM/Cache

(1)

L2 RAM/Cache

(1)

0x1082 0000 0x10E0 7FFF 6048K Reserved Reserved

0x10E0 8000 0x10E0 FFFF 32K L1P RAM/Cache

(1)

L1P RAM/Cache

(1)

Reserved

0x10E1 0000 0x10F0 3FFF 976K Reserved Reserved

0x10F0 4000 0x10F0 FFFF 48K Reserved Reserved

0x10F1 0000 0x10F1 7FFF 32K L1D RAM/Cache

(1)

L1D RAM/Cache

(1)

0x10F1 8000 0x10FF FFFF 1M-96K Reserved Reserved

0x1100 0000 0x1FFF FFFF 240M Reserved Reserved

0x2000 0000 0x2000 7FFF 32K DDR2 Control Regs DDR2 Control Regs

0x2000 8000 0x2FFF FFFF 256M-32K Reserved Reserved

0x3000 0000 0x3FFF FFFF 256M Reserved Reserved

0x4000 0000 0x41FF FFFF 32M Reserved Reserved

0x4200 0000 0x42FF FFFF 16M EMIFA Data ( CS2)

(2)

EMIFA Data ( CS2)

(2)

0x4300 0000 0x43FF FFFF 16M Reserved Reserved

0x4400 0000 0x44FF FFFF 16M EMIFA Data ( CS3)

(2)

EMIFA Data ( CS3)

(2)

0x4500 0000 0x45FF FFFF 16M Reserved Reserved

0x4600 0000 0x46FF FFFF 16M EMIFA Data ( CS4)

(2)

EMIFA Data ( CS4)

(2)

0x4700 0000 0x47FF FFFF 16M Reserved Reserved

0x4800 0000 0x48FF FFFF 16M EMIFA Data ( CS5)

(2)

EMIFA Data ( CS5)

(2)

0x4900 0000 0x49FF FFFF 16M Reserved Reserved

0x4A00 0000 0x4BFF FFFF 32M Reserved Reserved

0x4C00 0000 0x4FFF FFFF 64M Reserved Reserved

0x5000 0000 0x7FFF FFFF 768M Reserved Reserved

0x8000 0000 0x8FFF FFFF 256M DDR2 Memory Controller DDR2 Memory Controller DDR2 Memory Controller

0x9000 0000 0xFFFF FFFF 1792M Reserved Reserved Reserved

(1) For all bootmodes that default to DSPBOOTADDR = 0x0010 0000 (i.e., all boot modes except the EMIFA ROM Direct Boot,

BOOTMODE[3:0] = 0100, FASTBOOT = 0), the bootloader code disables all C64x+ cache (L2, L1P, and L1D) so that upon exit from the

bootloader code, all C64x+ memories are configured as all RAM (L2CFG.L2MODE = 0h, L1PCFG.L1PMODE = 0h, and

L1DCFG.L1DMODE = 0h). If cache use is required, the application code must explicitly enable the cache. For more information on boot

modes, see Section 3.4.1 , Boot Modes. For more information on the bootloader, see the Using the TMS320DM643x Bootloader

Application Report (literature number SPRAAG0 ). For the EMIFA ROM Direct Boot (BOOTMODE[3:0] = 0100, FASTBOOT = 0), the

bootloader is not executed—that is, L2 RAM/Cache defaults to all RAM (L2CFG.L2MODE = 0h); L1P RAM/Cache defaults to all cache

(L1PCFG.L1PMODE = 7h); and L1D RAM/Cache defaults to all cache (L1DCFG.L1DMODE = 7h).

(2) The EMIFA CS0 and CS1 are not functionally supported on the DM6431 device, and therefore, are not pinned out.

Submit Documentation Feedback Device Overview 13

www.ti.com

PRODUCT PREVIEW

TMS320DM6431

Digital Media Processor

SPRS342A – NOVEMBER 2006 – REVISED MARCH 2007

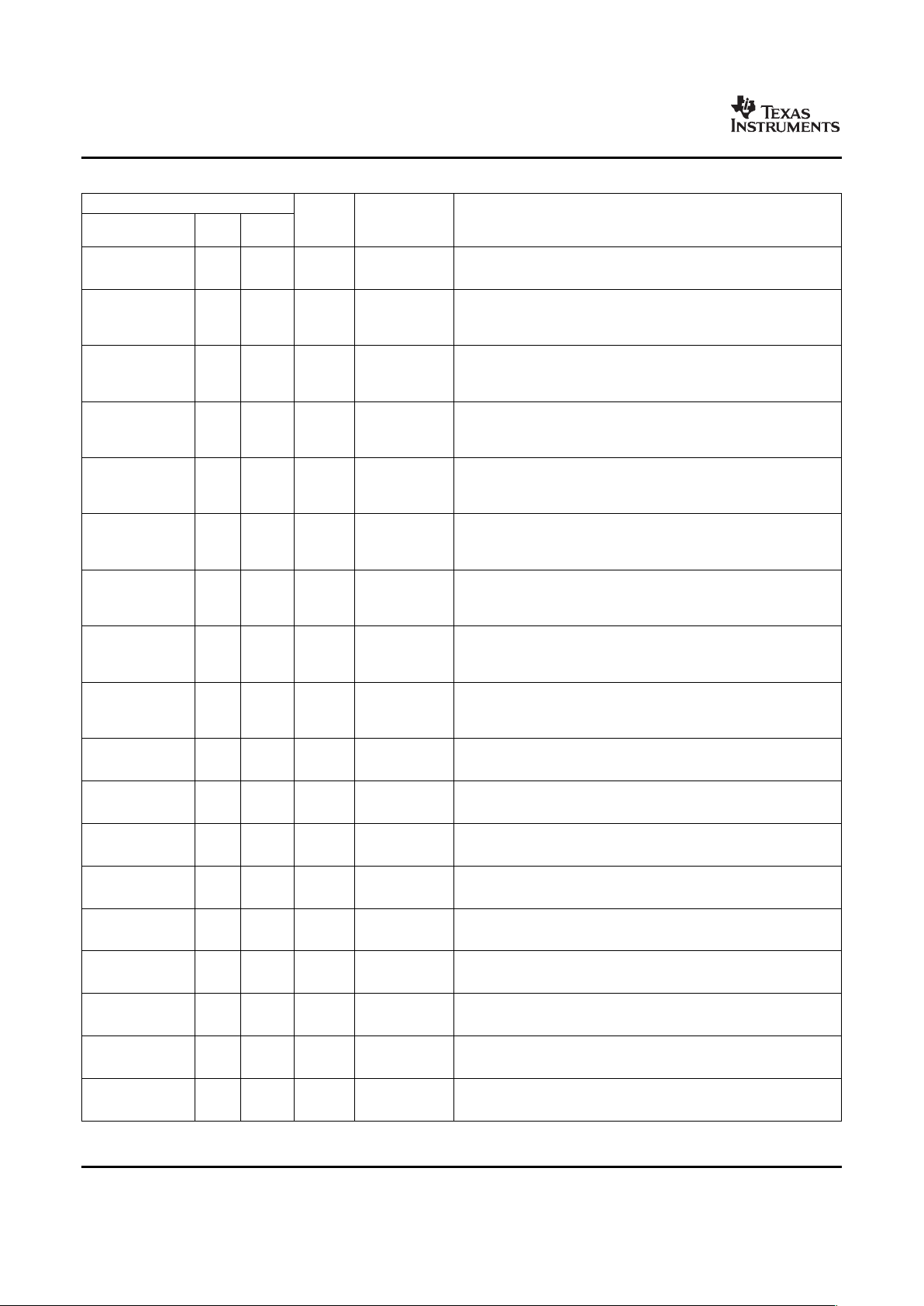

Table 2-4. Configuration Memory Map Summary

START END SIZE C64x+

ADDRESS ADDRESS (Bytes)

0x0180 0000 0x0180 FFFF 64K C64x+ Interrupt Controller

0x0181 0000 0x0181 0FFF 4K C64x+ Powerdown Controller

0x0181 1000 0x0181 1FFF 4K C64x+ Security ID

0x0181 2000 0x0181 2FFF 4K C64x+ Revision ID

0x0182 0000 0x0182 FFFF 64K C64x+ EMC

0x0183 0000 0x0183 FFFF 64K Reserved

0x0184 0000 0x0184 FFFF 64K C64x+ Memory System

0x0185 0000 0x0187 FFFF 192K Reserved

0x0188 0000 0x01BB FFFF 3328K Reserved

0x01BC 0000 0x01BC 00FF 256 Reserved

0x01BC 0100 0x01BC 01FF 256 Pin Manager and Trace

0x01BC 0400 0x01BF FFFF 255K Reserved

0x01C0 0000 0x01C0 FFFF 64K EDMA CC

0x01C1 0000 0x01C1 03FF 1K EDMA TC0

0x01C1 0400 0x01C1 07FF 1K EDMA TC1

0x01C1 0800 0x01C1 0BFF 1K EDMA TC2

0x01C1 0C00 0x01C1 9FFF 5K Reserved

0x01C1 A000 0x01C1 A7FF 2K Reserved

0x01C1 A800 0x01C1 FFFF 22K Reserved

0x01C2 0000 0x01C2 03FF 1K UART0

0x01C2 0400 0x01C2 07FF 1K Reserved

0x01C2 0800 0x01C2 0FFF 2K Reserved

0x01C2 1000 0x01C2 13FF 1K I2C

0x01C2 1400 0x01C2 17FF 1K Timer0

0x01C2 1800 0x01C2 1BFF 1K Timer1

0x01C2 1C00 0x01C2 1FFF 1K Timer2 (Watchdog)

0x01C2 2000 0x01C2 23FF 1K PWM0

0x01C2 2400 0x01C2 27FF 1K PWM1

0x01C2 2800 0x01C2 2BFF 1K PWM2

0x01C2 2C00 0x01C2 2FFF 1K Reserved

0x01C2 3000 0x01C2 3FFF 4K HECC Control

(1)

0x01C2 4000 0x01C2 53FF 5K HECC RAM

0x01C2 5400 0x01C3 FFFF 107K Reserved

0x01C4 0000 0x01C4 07FF 2K System Module

0x01C4 0800 0x01C4 0BFF 1K PLL Controller 1

0x01C4 0C00 0x01C4 0FFF 1K PLL Controller 2

0x01C4 1000 0x01C4 1FFF 4K Power and Sleep Controller

0x01C4 2000 0x01C6 6FFF 148K Reserved

0x01C6 7000 0x01C6 77FF 2K GPIO

0x01C6 7800 0x01C6 7FFF 2K Reserved

0x01C6 8000 0x01C6 FFFF 32K Reserved

0x01C7 0000 0x01C7 3FFF 16K VPSS Registers

0x01C7 4000 0x01C7 FFFF 48K Reserved

0x01C8 0000 0x01C8 0FFF 4K EMAC Control Registers

0x01C8 1000 0x01C8 1FFF 4K EMAC Control Module Registers

(1) Software must not access "Reserved" locations of the HECC. Access to HECC "Reserved" locations may hang the device.

Device Overview14 Submit Documentation Feedback

www.ti.com

TMS320DM6431

Digital Media Processor

SPRS342A – NOVEMBER 2006 – REVISED MARCH 2007

Table 2-4. Configuration Memory Map Summary (continued)

START END SIZE C64x+

ADDRESS ADDRESS (Bytes)

0x01C8 2000 0x01C8 3FFF 8K EMAC Control Module RAM

0x01C8 4000 0x01C8 47FF 2K MDIO Control Registers

0x01C8 4800 0x01CF FFFF 494K Reserved

0x01D0 0000 0x01D0 07FF 2K McBSP0

0x01D0 0800 0x01D0 0FFF 2K Reserved

0x01D0 1000 0x01D0 13FF 1K McASP0 Control

0x01D0 1400 0x01D0 17FF 1K McASP0 Data

0x01D0 1800 0x01DF FFFF 1018K Reserved

0x01E0 0000 0x01E0 0FFF 4K EMIFA Control

0x01E0 1000 0x01E0 1FFF 4K Reserved

0x01E0 2000 0x0FFF FFFF 226M-8K Reserved

Submit Documentation Feedback Device Overview 15

www.ti.com

PRODUCT PREVIEW

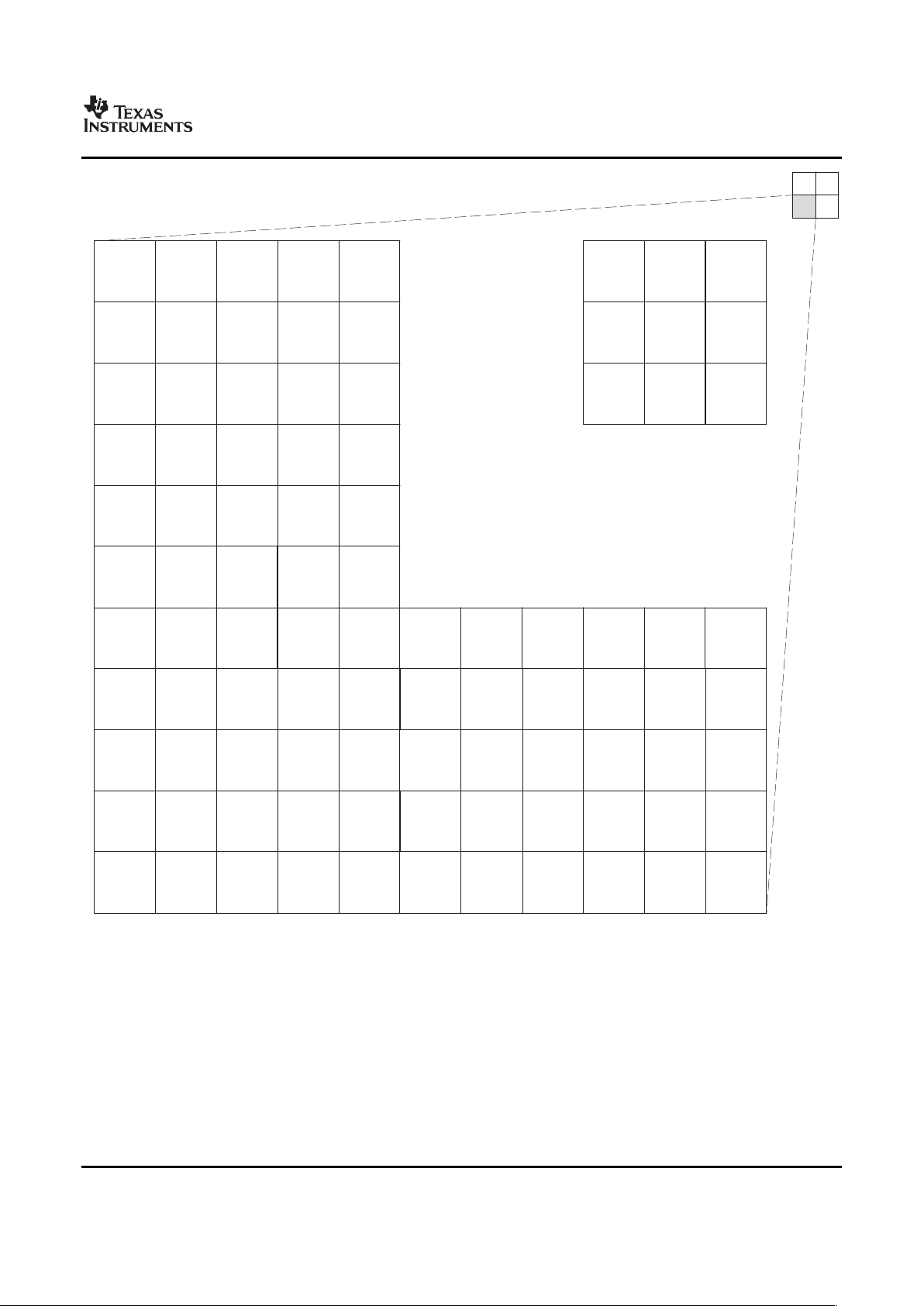

2.5 Pin Assignments

2.5.1 Pin Map (Bottom View)

W

V

U

T

R

P

N

M

L

K

10987654321

10987654321

DDR_D[3]

V

SS

HECC_TX/

TOUT1L/

GP[55]

V

SS

UCTS0/

GP[87]

UTXD0/

GP[86]

URXD0/

GP[85]

SCL SDA

TCK RESETOUTEMU1 POR

DV

DD33

TDOEMU0

TRST

DV

DDR2

TMS

DDR_D[1] DDR_DQM[0]

DDR_D[2]

RSV16

TDI

RESET

RSV3

HECC_RX/

TINP1L/

GP[56]

RSV2

CV

DD

V

SS

V

SS

V

SS

CV

DD

DV

DDR2

DDR_A[11]DDR_A[12]DDR_CLK0DDR_CLK0DDR_D[14]

V

SS

DV

DD33

V

SS

DDR_D[5]

DDR_D[6]

DDR_D[9]

V

SS

V

SS

DV

DDR2

DDR_BS[2]

V

SS

DDR_D[11] DDR_D[15] DDR_CKE

CV

DD

V

SS

CV

DD

CV

DD

V

SS

DDR_DQM[1] DDR_CAS DDR_WE DDR_ZN

V

SS

V

SS

DDR_DQS[1] DDR_RAS DDR_A[10]

CV

DD

CV

DD

DV

DDR2

DDR_D[4] DDR_D[8] DDR_D[13] DDR_BS[1]

DDR_D[12]

DV

DDR2

TINP0L/

GP[98]

V

SS

V

SS

V

SS

DV

DDR2

CLKOUT0/

PWM2/

GP[84]

DV

DD33

V

SS

DV

DD33

DV

DDR2

DV

DDR2

V

SS

DV

DDR2

DDR_CS

CV

DD

DDR_DQS[0] DDR_D[10] DDR_BS[0]

DDR_D[0]

URTS0/

PWM0/

GP[88]

DDR_D[7]

W

V

U

T

R

P

N

M

L

K

V

SS

V

SS

DDR_A[8]DDR_A[8]

TMS320DM6431

Digital Media Processor

SPRS342A – NOVEMBER 2006 – REVISED MARCH 2007

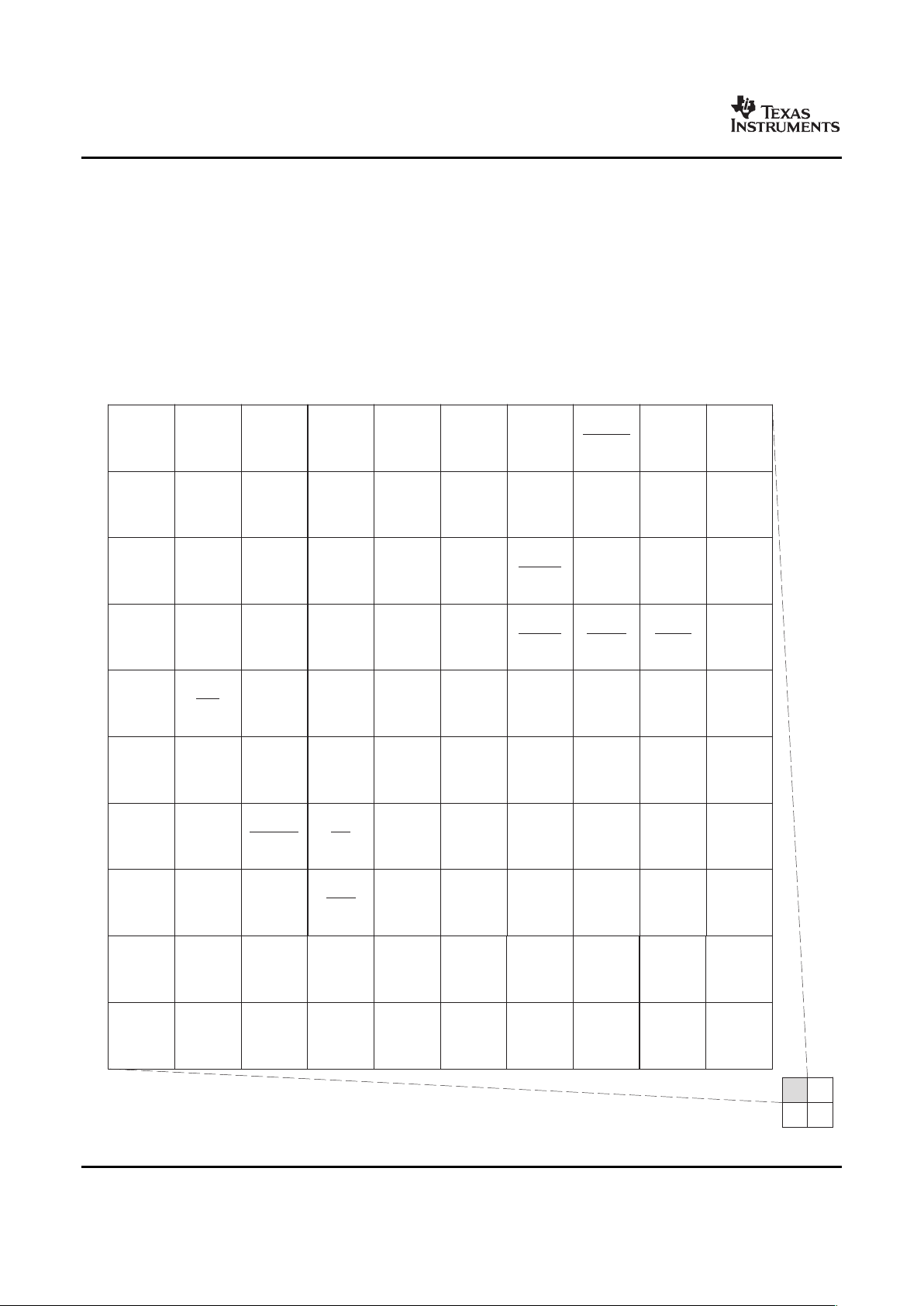

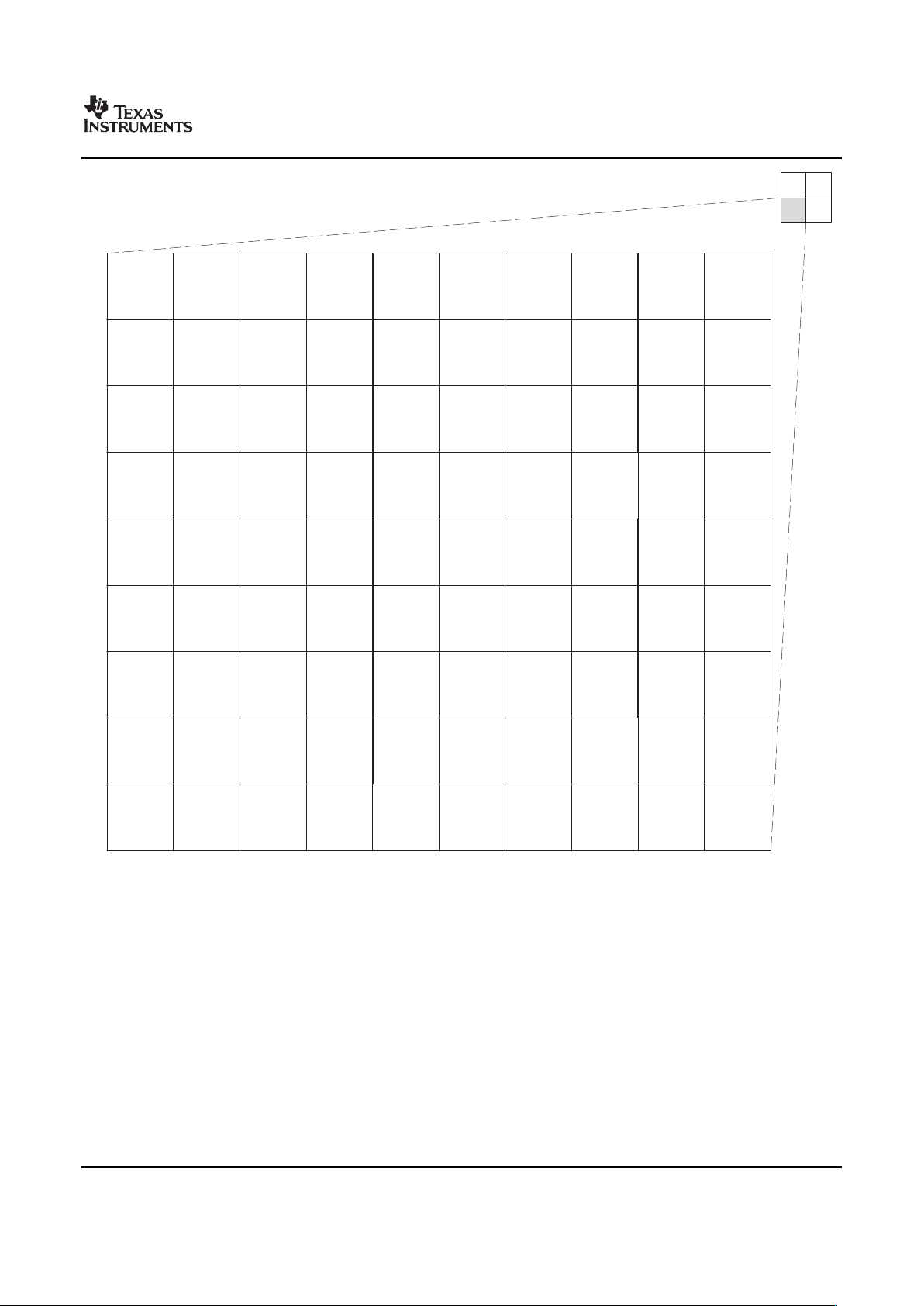

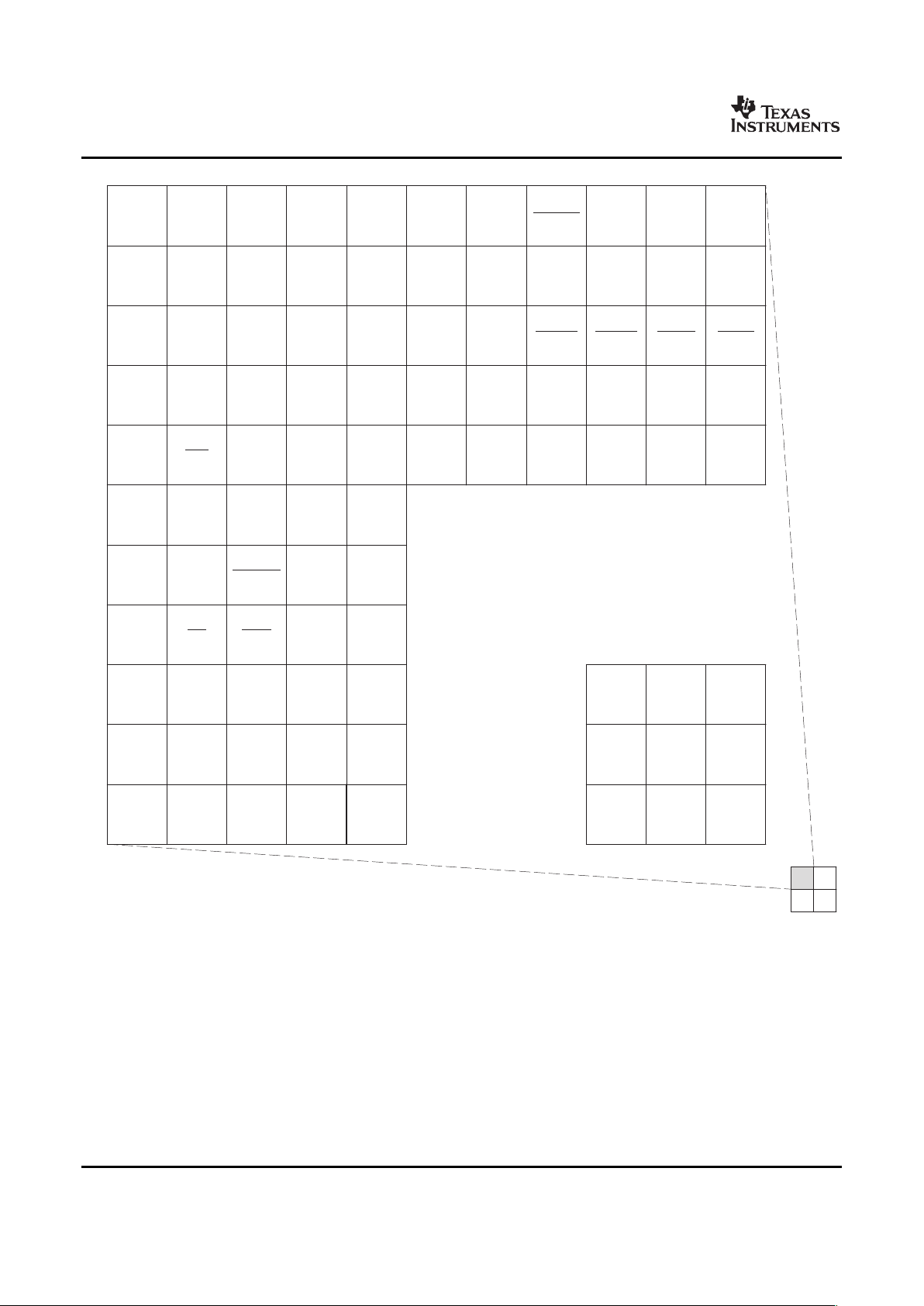

Extensive use of pin multiplexing is used to accommodate the largest number of peripheral functions in

the smallest possible package. Pin multiplexing is controlled using a combination of hardware

configuration at device reset and software programmable register settings. For more information on pin

muxing, see Section 3.7 , Multiplexed Pin Configurations of this document.

Figure 2-2 through Figure 2-5 show the bottom view of the ZWT package pin assignments in four

quadrants (A, B, C, and D). Figure 2-6 through Figure 2-9 show the bottom view of the ZDU package pin

assignments in four quadrants (A, B, C, and D).

Figure 2-2. ZWT Pin Map [Quadrant A]

Device Overview16 Submit Documentation Feedback

www.ti.com

W

V

U

T

R

P

N

M

L

K

191817161514131211

191817161514131211

RSV14

CV

DD

V

SS

V

SS

CV

DD

V

SS

CV

DD

V

SS

V

SS

V

SS

DV

DDR2

V

SS

RSV5DV

DDR2

DDR_ZP DDR_VSSDLLDDR_VDDDLL

DV

DDR2

CV

DD

DV

DDR2

V

SS

V

SS

V

SS

V

SS

V

SS

RSV9 RSV6

RSV8

DV

DDR2

DV

DDR2

RSV35RSV29RSV26

RSV7

RSV4

DV

DDR2

V

SS

DV

DDR2

RSV22 RSV36

MXV

DD

RSV25 RSV30 RSV32 V

SS

V

SS

RSV12

RSV10

V

SS

RSV15

DDR_VREF RSV21 RSV31 RSV39

DV

DD33

MXI/

CLKIN

RSV28 RSV23 RSV38

V

SS

V

SS

RSV27 RSV37

RSV24

V

SS

CV

DD

DV

DD33

V

SS

PLL

PWR18

V

SS

V

SS

DV

DD33

RSV13

V

SS

RSV11

V

SS

RSV34

MXV

SS

RSV20

RSV33

CV

DD

W

V

U

T

R

P

N

M

L

K

DDR_A[0]

DDR_A[1]

DDR_A[2]

DDR_A[5]

DDR_A[3]

DDR_A[4]

DDR_A[6]

DDR_A[9]

DDR_A[7]

TMS320DM6431

Digital Media Processor

SPRS342A – NOVEMBER 2006 – REVISED MARCH 2007

Figure 2-3. ZWT Pin Map [Quadrant B]

Submit Documentation Feedback Device Overview 17

www.ti.com

PRODUCT PREVIEW

H

G

F

E

D

C

B

A

191817161514131211

191817161514131211

CV

DD

EM_WAIT/

(RDY/BSY)

VD/

GP[53]

YI7(CCD7)/

GP[43]

EM_A[15]/

GP[49]

EM_A[16]/

GP[48]

CI0(CCD8)/

EM_A[20]/

GP[44]

C_FIELD/

EM_A[21]/

GP[34]

EM_A[18]/

GP[46]

C_WE/

EM_R/W/

GP[35]

RSV19RSV18

DV

DD33

DV

DD33

V

SS

V

SS

V

SS

DV

DD33

V

SS

YI5(CCD5)/

GP[41]

YI3(CCD3)/

GP[39]

YI6(CCD6)/

GP[42]

PCLK/

GP[54]

EM_CS3/

GP[13]

EM_CS2/

GP[12]

GP[22]/

(BOOTMODE0)

EM_D[1]/

GP[15]

GP[31]

EM_D[4]/

GP[18]

EM_CS4/

GP[32]

YI1(CCD1)/

GP[37]

EM_D[6]/

GP[20]

V

SS

YI4(CCD4)/

GP[40]

V

SS

DV

DD33

DV

DD33

EM_A[3]/

GP[11]

EM_A[1]/

(ALE)/GP[9]/

(AEAW1/

PLLMS1)

EM_D[5]/

GP[19]

EM_D[2]/

GP[16]

EM_BA[1]/

GP[5]/

(AEM0)

EM_D[0]/

GP[14]

GP[24]/

(BOOTMODE2)

GP[25]/

(BOOTMODE3)

GP[26]/

(FASTBOOT)

GP[30]

EM_A[4]/

GP[10]/

(AEAW2/

PLLMS2)

V

SS

GP[29] GP[28] V

SS

EM_A[0]/

GP[7]/

(AEM2)

V

SS

EM_A[17]/

GP[47]

HD/

GP[52]

EM_BA[0]/

GP[6]/

(AEM1)

EM_A[2]/

(CLE)/GP[8]/

(AEAW0/

PLLMS0)

EM_D[7]/

GP[21]

YI2(CCD2)/

GP[38]

YI0(CCD0)/

GP[36]

EM_OE

EM_WE

EM_D[3]/

GP[17]

GP[23]/

(BOOTMODE1)

V

SS

DV

DD33

CV

DD

V

SS

GP[27]

CI1(CCD9)/

EM_A[19]/

GP[45]

H

G

F

E

D

C

B

A

J

V

SS

CV

DD

V

SS

V

SS

DV

DD33

MXO

V

SS

DV

DD33

V

SS

J

EM_CS5/

GP[33]

TMS320DM6431

Digital Media Processor

SPRS342A – NOVEMBER 2006 – REVISED MARCH 2007

Figure 2-4. ZWT Pin Map [Quadrant C]

Device Overview18 Submit Documentation Feedback

www.ti.com

J

H

G

F

E

D

C

B

A

10987654321

10987654321

AXR0[0]/

GP[105]

DV

DD33

MTXCLK/

GP[73]

DV

DD33

V

SS

MRXCLK/

GP[77]

MRXD1/

GP[79]

MRXD3/

GP[82]

MRXD0/

GP[78]

MDIO/

GP[83]

MTXEN/

GP[75]

MRXD2/

GP[80]

MTXD0/

GP[72]

GP[0] GP[2]GP[1]

AMUTEIN0/

GP[109]

V

SS

GP[4]/

PWM1

AFSX0/

GP[107]

AXR0[3]/

FSR0/

GP[102]

ACLKR0/

CLKX0/

GP[99]

AMUTE0/

GP[110]

GP[3]

MRXDV/

GP[74]

MCRS/

GP[68]

MTXD1/

GP[71]

GP[66]

EM_A[7]/

GP[94]

EM_A[11]/

GP[90]

EM_A[9]/

GP[92]

EM_A[12]/

GP[89]

V

SS

RSV17

GP[65]

DV

DD33

AXR0[2]/

FSX0/

GP[103]

AXR0[1]/

DX0/

GP[104]

MTXD2/

GP[70]

DV

DD33

V

SS

CV

DD

EM_A[8]/

GP[93]

V

SS

V

SS

CV

DD

CV

DD

GP[57]

DV

DD33

EM_A[6]/

GP[95]

GP[62]

GP[59]

DV

DD33

V

SS

DV

DD33

DV

DD33

GP[60]

EM_A[14]/

GP[50]

V

SS

CV

DD

V

SS

EM_A[5]/

GP[96]

EM_A[13]/

GP[51]

DV

DD33

AHCLKR0/

CLKR0/

GP[101]

CLKS0/

TOUT0L/

GP[97]

DV

DD33

V

SS

V

SS

DV

DD33

GP[63]

GP[58]

GP[61]

V

SS

MDCLK/

GP[81]

MTXD3/

GP[69]

MCOL/

GP[67]

GP[64]

RSV1 V

SS

ACLKX0/

GP[106]

V

SS

V

SS

AFSR0/

DR0/

GP[100]

DV

DD33

V

SS

AHCLKX0/

GP[108]

MRXER/

GP[76]

J

H

G

F

E

D

C

B

A

DV

DD33

EM_A[10]/

GP[91]

TMS320DM6431

Digital Media Processor

SPRS342A – NOVEMBER 2006 – REVISED MARCH 2007

Figure 2-5. ZWT Pin Map [Quadrant D]

Submit Documentation Feedback Device Overview 19

www.ti.com

PRODUCT PREVIEW

M

N

P

R

T

U

V

11109

43

11109876543

M

N

V

W

W

Y Y

21

21

AA AA

AB AB

M

N

P

R

T

U

P

11

5

109

8

76

CLKOUT0/

PWM2/

GP[84]

RESET

RESETOUT

POR

TMS

TDO TDITCK

TRST

EMU1EMU0

RSV16

DV

DD33

DV

DD33

DV

DD33

DV

DD33

DV

DDR2

DV

DDR2

DV

DDR2

DV

DDR2

DV

DDR2

DV

DDR2

DV

DDR2

DV

DDR2 DV

DDR2

DV

DDR2

URTS0/

PWM0/

GP[88]

HECC_RX/

TINP1L/

GP[56]

HECC_TX/

TOUT1L/

GP[55]

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

CV

DD

V

SS

V

SS

V

SS

V

SS

V

SS

RSV3

UCTS0/

GP[87]

UTXD0/

GP[86]

URXD0/

GP[85]

SDA

SCL

DDR_D[0] DDR_D[1]

DDR_D[2]

DDR_D[3] DDR_D[4]

DDR_D[5]

DDR_D[6]

DDR_D[7]

DDR_D[8]

DDR_D[9]

DDR_D[10]

DDR_D[11]

DDR_D[12]

DDR_D[13]

DDR_D[14]

DDR_D[15]

DDR_A[11]

DDR_A[10]

DDR_A[12]

DDR_BS[2]DDR_BS[1]

DDR_BS[0]

DDR_DQS[1]DDR_DQS[0]

DDR_CAS

DDR_RAS

DDR_DQM[0] DDR_DQM[1]

DDR_CSDDR_WE

DDR_CKE

DDR_CLK0DDR_CLK0

CV

DD

CV

DD

V

SS

CV

DD

V

SS

V

SS

CV

DD

TMS320DM6431

Digital Media Processor

SPRS342A – NOVEMBER 2006 – REVISED MARCH 2007

Figure 2-6. ZDU Pin Map [Quadrant A]

Device Overview20 Submit Documentation Feedback

www.ti.com

M

N

P

R

T

U

V

12 13 14

19 20

12 13 14 15 16 17 18 19 20

M

N

V

W

W

YY

21 22

21 22

AAAA

ABAB

M

N

P

R

T

U

P

12

18

13 14

15

16 17

MXI/

CLKIN

MXOMXV

SS

PLL

PWR18

RSV6RSV7

RSV8

RSV9 RSV10

RSV12

RSV11

RSV13RSV14

RSV15

DV

DD33

DV

DD33

DV

DD33

DV

DD33

DV

DD33

DV

DD33

MXV

DD

DV

DDR2

DV

DDR2

DV

DDR2

DV

DDR2

DV

DDR2

DV

DDR2

DV

DDR2

DV

DDR2

CV

DD

CV

DD

CV

DD

CV

DD

V

SS

V

SS

V

SS

RSV32RSV28RSV20DDR_A[5]

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

RSV4

V

SS

V

SS

V

SS

V

SS

RSV5DDR_ZPDDR_ZN

DDR_VDDDLL DDR_VSSDLL

DDR_VREF

RSV24

RSV25

RSV26

RSV27

RSV29 RSV30

RSV31

RSV33

RSV34

RSV35

RSV36

RSV37

RSV38

RSV39

DDR_A[0]DDR_A[1]

DDR_A[2]

DDR_A[3]

DDR_A[4]

DDR_A[6]

DDR_A[7]

DDR_A[8]

DDR_A[9] RSV23RSV22

RSV21

V

SS

TMS320DM6431

Digital Media Processor

SPRS342A – NOVEMBER 2006 – REVISED MARCH 2007

Figure 2-7. ZDU Pin Map [Quadrant B]

Submit Documentation Feedback Device Overview 21

www.ti.com

PRODUCT PREVIEW

L

K

J

H

G

F

E

12 13 14

19 20

12 13 14 15 16 17 18 19 20

L

K

E

D

V

SS

EM_BA[0]/

GP[6]/

(AEM1)

DV

DD33

DV

DD33

RSV19RSV18 EM_OEV

SS

RSV17

D

C

C_WE/

EM_R/W/

GP[35]

EM_BA[1]/

GP[5[/

(AEM0)

C_FIELD/

EM_A[21]/

GP[34]

CI1(CCD9)/

EM_A[19]/

GP[45]

EM_A[15]/

GP[49]

EM_WE

CI0(CCD8)/

EM_A[20]/

GP[44]

EM_A[11]/

GP[90]

C

21 22

21 22

EM_D[2]/

GP[16]

EM_D[5]/

GP[19]

EM_D[6]/

GP[20]

EM_D[4]/

GP[18]

EM_CS4

/

GP[32]

EM_CS5/

GP[33]

GP[29]

DV

DD33

EM_D[0]/

GP[14]

GP[31]

GP[30]

V

SS

EM_CS3/

GP[13]

EM_A[3]/

GP[11]

EM_CS2/

GP[12]

B

YI2(CCD2)

GP[38]

YI4(CCD4)/

GP[40]

YI1(CCD1)/

GP[37]

EM_A[17]/

GP[47]

EM_A[16]/

GP[48]

YI0(CCD0)/

GP[36]

YI6(CCD6)/

GP[42]

EM_A[12]/

GP[89]

B

A

YI7(CCD7)/

GP[43]

PCLK/

GP[54]

YI3(CCD3)/

GP[39]

EM_A[18]/

GP[46]

EM_A[14]/

GP[50]

HD/

GP[52]

VD/

GP[53]

EM_A[13]/

GP[51]

A

V

SS

V

SS

DV

DD33

13 14 15 16 17

L

K

J

H

G

F

J

12

18

GP[27]

GP[25]/

(BOOTMODE3)

GP[24]/

(BOOTMODE2)

GP[23]/

(BOOTMODE1)

GP[28]

GP[26]/

(FASTBOOT)

EM_A[4]/

GP[10]/

(AEAW2/

PLLMS2)

EM_A[1]/

(ALE)/GP[9]/

(AEAW1/

PLLMS1)

EM_A[2]/

(CLE)/GP[8]/

(AEAW0/

PLLMS0)

EM_A[0]/

GP[7]/

(AEM2)

EM_WAIT/

(RDY/BSY)

GP[22]/

(BOOTMODE0)

DV

DD33

DV

DD33

DV

DD33

V

SS

V

SS

V

SS

V

SS

DV

DD33

V

SS

V

SS

DV

DD33

DV

DD33

V

SS

DV

DD33

DV

DD33

DV

DD33

CV

DD

CV

DD

CV

DD

V

SS

CV

DD

CV

DD

V

SS

V

SS

V

SS

V

SS

V

SS

EM_D[7]/

GP[21]

EM_D[3]/

GP[17]

EM_D[1]/

GP[15]

YI5(CCD5)/

GP[41]

TMS320DM6431

Digital Media Processor

SPRS342A – NOVEMBER 2006 – REVISED MARCH 2007

Figure 2-8. ZDU Pin Map [Quadrant C]

Device Overview22 Submit Documentation Feedback

www.ti.com

L

K

J

H

G

F

E

1110943

1110987

6

543

L

K

E

D

DV

DD33

MRXDV/

GP[74]

V

SS

DV

DD33

RSV1 DV

DD33

V

SS

D

C

MCOL/

GP[67]

MRXD2/

GP[80]

MTXD2/

GP[70]

GP[64] GP[59]

EM_A[7]/

GP[94]

MTXEN/

GP[75]

GP[62]

EM_A[9]/

GP[92]

C

21

21

GP[0]

GP[2] GP[3]

AFSX0/

GP[107]

AHCLKX0/

GP[108]

AXR0[0]/

GP[105]

ACLKR0/

CLKX0/

GP[99]

AXR0[2]/

FSX0/

GP[103]

AXR0[1]/

DX0/

GP[104]

TINP0L/

GP[98]

GP[1]

ACLKX0/

GP[106]

AHCLKR0/

CLKR0/

GP[101]

DV

DD33

MDIO/

GP[83]

MRXD3/

GP[82]

MDCLK/

GP[81]

MRXD0/

GP[78]

B

MCRS/

GP[68]

MRXD1/

GP[79]

MTXD0/

GP[72]

GP[65] GP[58]

EM_A[6]/

GP[95]

MTXD1/

GP[71]

GP[61]

EM_A[10]/

GP[91]

B

A

GP[66]

MRXCLK/

GP[77]

MTXD3/

GP[69]

GP[63] GP[60]

EM_A[5]/

GP[96]

MTXCLK/

GP[73]

GP[57]

EM_A[8]/

GP[93]

A

DV

DD33

MRXER/

GP[76]

V

SS

DV

DD33

11109876

L

K

J

H

G

F

J

5

DV

DD33

DV

DD33

DV

DD33

DV

DD33

V

SS

DV

DD33

DV

DD33

DV

DD33

DV

DD33

DV

DD33

DV

DD33

DV

DD33

GP[4]/

PWM1

TOUT0L/

GP[97]

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

RSV2

AMUTE0/

GP[110]

AMUTEIN0/

GP[109]

AFSR0/

DR0/

GP[100]

AXR0[3]/

FSR0/

GP[102]

CV

DD

CV

DD

CV

DD

CV

DD

2.5.2 Signal Groups Description

TMS320DM6431

Digital Media Processor

SPRS342A – NOVEMBER 2006 – REVISED MARCH 2007

Figure 2-9. ZDU Pin Map [Quadrant D]

TBD

Submit Documentation Feedback Device Overview 23

www.ti.com

PRODUCT PREVIEW

2.6 Terminal Functions

TMS320DM6431

Digital Media Processor

SPRS342A – NOVEMBER 2006 – REVISED MARCH 2007

The terminal functions tables (Table 2-5 through Table 2-26 ) identify the external signal names, the

associated pin (ball) numbers along with the mechanical package designator, the pin type, whether the pin

has any internal pullup or pulldown resistors, and a functional pin description. For more detailed

information on device configuration, peripheral selection, multiplexed/shared pin, and debugging

considerations, see the Device Configurations section of this data manual.

All device boot and configuration pins are multiplexed configuration pins— meaning they are multiplexed

with functional pins. These pins function as device boot and configuration pins only during device reset.

The input states of these pins are sampled and latched into the BOOTCFG register when device reset is

deasserted (see Note below). After device reset is deasserted, the values on these multiplexed pins no

longer have to hold the configuration.

For proper device operation, external pullup/pulldown resistors may be required on these device boot and

configuration pins. Section 3.9.1 , Pullup/Pulldown Resistors discusses situations where external

pullup/pulldown resistors are required.

Note: Internal to the chip, the two device reset pins RESET and POR are logically AND’d together for the

purpose of latching device boot and configuration pins. The values on all device boot and configuration

pins are latched into the BOOTCFG register when the logical AND of RESET and POR transitions from

low-to-high.

Device Overview24 Submit Documentation Feedback

www.ti.com

TMS320DM6431

Digital Media Processor

SPRS342A – NOVEMBER 2006 – REVISED MARCH 2007

Table 2-5. BOOT Terminal Functions

SIGNAL

TYPE

(1)

OTHER

(2) (3)

DESCRIPTION

ZWT ZDU

NAME

NO. NO.

BOOT

GP[25]/

(BOOTMODE3)

G16 H21 Bootmode configuration bits. These bootmode functions along with

GP[24]/

the FASTBOOT function determine what device bootmode

(BOOTMODE2) G15 L20

IPD configuration is selected.

I/O/Z

DV

DD33

The DM6431 device supports several types of bootmodes along with

GP[23]/ F15 K20

a FASTBOOT option; for more details on the types/options, see

(BOOTMODE1)

F18 J20 Section 3.4.1 , Boot Modes.

GP[22]/

(BOOTMODE0)

Fast Boot

GP[26]/ IPD

G17 K19 I/O/Z 0 = Not Fast Boot

(FASTBOOT) DV

DD33

1 = Fast Boot

EM_A[4]/GP[10]/ IPD EMIFA Address Bus Width (AEAW) and Fast Boot PLL Multiplier

A17 B21 I/O/Z

(AEAW2/PLLMS2) DV

DD33

Select (PLLMS).

These configuration pins serve two purposes which are based on

EM_A[1]/(ALE)/

IPD

AEM[2:0] settings.

GP[9]/ A16 B20 I/O/Z

DV

DD33

For AEM[2:0] = 001 [8-bit EMIFA (Async) Pinout Mode 1], the

(AEAW1/PLLMS1)

AEAW/PLLMS pins serve as the AEAW function to select EMIFA

Address Bus Width.

EM_A[2]/(CLE)/

For all other AEM modes, the AEAW/PLLMS pins select the PLL

IPD

GP[8]/ B16 A20 I/O/Z

multiplier for fast boot.

DV

DD33

(AEAW0/PLLMS0)

For more details, see Section 3.5.1.2 , EMIFA Address Width Select

(AEAW) and Fast Boot PLL Multipler Select (PLLMS).

EM_A[0]/ IPD Selects EMIFA Pinout Mode

B17 C21 I/O/Z

GP[7]/(AEM2) DV

DD33

The DM6431 supports the following EMIFA Pinout Modes:

EM_BA[0]/ IPD

C17 E20 I/O/Z

AEM[2:0] = 000, No EMIFA

GP[6]/(AEM1) DV

DD33

AEM[2:0] = 001, 8-bit EMIFA (Async) Pinout Mode 1

AEM[2:0] = 101, 8-bit EMIFA (NAND) Pinout Mode 5

EM_BA[1]/ IPD

C16 C20 I/O/Z

GP[5]/(AEM0) DV

DD33

This signal doesn't actually affect the EMIFA module. It only affects

how the EMIFA is pinned out.

For proper DM6431 device operation, if this pin is both routed and

3-stated (not driven) during device reset, it must be pulled down via

IPD

GP[28] H16 J21 I/O/Z an external resistor. For more detailed information on

DV

DD33

pullup/pulldown resistors, see Section 3.9.1 , Pullup/Pulldown

Resistors.

For proper DM6431 device operation, if this pin is both routed and

IPU 3-stated (not driven) during device reset, it must be pulled up via an

GP[27] H17 L19 I/O/Z

DV

DD33

external resistor. For more detailed information on pullup/pulldown

resistors, see Section 3.9.1 , Pullup/Pulldown Resistors.

(1) I = Input, O = Output, Z = High impedance, S = Supply voltage, GND = Ground, A = Analog signal

(2) IPD = Internal pulldown, IPU = Internal pullup. For more detailed information on pullup/pulldown resistors and situations where external

pullup/pulldown resistors are required, see Section 3.9.1 , Pullup/Pulldown Resistors.

(3) Specifies the operating I/O supply voltage for each signal

Submit Documentation Feedback Device Overview 25

www.ti.com

PRODUCT PREVIEW

TMS320DM6431

Digital Media Processor

SPRS342A – NOVEMBER 2006 – REVISED MARCH 2007

Table 2-6. Oscillator/PLL Terminal Functions

SIGNAL

TYPE

(1)

OTHER

(2)

DESCRIPTION

ZWT ZDU

NAME

NO. NO.

OSCILLATOR, PLL

Crystal input MXI for MX oscillator (system oscillator, typically 27 MHz).

MXI/

K19 N22 I MXV

DD

If the internal oscillator is bypassed, this is the external oscillator clock

CLKIN

input.

(3)

MXO J19 M22 O MXV

DD

Crystal output for MX oscillator

1.8 V power supply for MX oscillator. On the board, this pin can be

MXV

DD

L18 N21 S

(4)

connected to the same 1.8 V power supply as DV

DDR2

.

MXV

SS

K18 M21 GND

(4)

Ground for MX oscillator

PLL

PWR18

L16 N20 S

(4)

1.8 V power supply for PLLs

(1) I = Input, O = Output, Z = High impedance, S = Supply voltage, GND = Ground, A = Analog signal

(2) Specifies the operating I/O supply voltage for each signal

(3) For more information on external board connections, see Section 6.6 , External Clock Input From MXI/CLKIN Pin.

(4) For more information, see the Recommended Operating Conditions table

Table 2-7. Clock Generator Terminal Functions

SIGNAL

TYPE

(1)

OTHER

(2) (3)

DESCRIPTION

ZWT ZDU

NAME

NO. NO.

CLOCK GENERATOR

This pin is multiplexed between the System Clock generator (PLL1), PWM2,

and GPIO.

CLKOUT0/ IPD

M1 R1 I/O/Z For the System Clock generator (PLL1), it is clock output CLKOUT0. This is

PWM2/GP[84] DV

DD33

configurable for 27 MHz or other 27 MHz-divided-down (/1 to /32) clock

outputs.

(1) I = Input, O = Output, Z = High impedance, S = Supply voltage, GND = Ground, A = Analog signal

(2) IPD = Internal pulldown, IPU = Internal pullup. For more detailed information on pullup/pulldown resistors and situations where external

pullup/pulldown resistors are required, see Section 3.9.1 , Pullup/Pulldown Resistors.

(3) Specifies the operating I/O supply voltage for each signal

Device Overview26 Submit Documentation Feedback

www.ti.com

TMS320DM6431

Digital Media Processor

SPRS342A – NOVEMBER 2006 – REVISED MARCH 2007

Table 2-8. RESET and JTAG Terminal Functions

SIGNAL

TYPE

(1)

OTHER

(2) (3)

DESCRIPTION

ZWT ZDU

NAME

NO. NO.

RESET

IPU

RESET M4 R3 I Device reset

DV

DD33

– Reset output status pin. The RESETOUT pin indicates when the

RESETOUT N3 T3 O/Z

DV

DD33

device is in reset.

IPU

POR N4 R2 I Power-on reset.

DV

DD33

JTAG

IPU

TMS R3 V3 I JTAG test-port mode select input

DV

DD33

–

TDO P3 U2 O/Z JTAG test-port data output

DV

DD33

IPU

TDI P4 U3 I JTAG test-port data input

DV

DD33

IPU

TCK N1 U1 I JTAG test-port clock input

DV

DD33

JTAG test-port reset. For IEEE 1149.1 JTAG compatibility, see

IPD

TRST R2 V2 I the IEEE 1149.1 JTAG compatibility statement portion of this data

DV

DD33

sheet

IPU

EMU1 N2 T2 I/O/Z Emulation pin 1

DV

DD33

IPU

EMU0 P2 T1 I/O/Z Emulation pin 0

DV

DD33

(1) I = Input, O = Output, Z = High impedance, S = Supply voltage, GND = Ground, A = Analog signal

(2) IPD = Internal pulldown, IPU = Internal pullup. For more detailed information on pullup/pulldown resistors and situations where external

pullup/pulldown resistors are required, see Section 3.9.1 , Pullup/Pulldown Resistors.

(3) Specifies the operating I/O supply voltage for each signal

Submit Documentation Feedback Device Overview 27

www.ti.com

PRODUCT PREVIEW

TMS320DM6431

Digital Media Processor

SPRS342A – NOVEMBER 2006 – REVISED MARCH 2007

Table 2-9. EMIFA Terminal Functions (Boot Configuration)

SIGNAL

TYPE

(1)

OTHER

(2) (3)

DESCRIPTION

ZWT ZDU

NAME

NO. NO.

EMIFA: BOOT CONFIGURATION

EM_A[4]/GP[10]/ IPD These pins are multiplexed between the EMIFA and GPIO. When

A17 B21 I/O/Z

(AEAW2/PLLMS2) DV

DD33

RESET or POR is asserted, these pins function as EMIFA

configuration pins. At reset if AEM[2:0] = 001 (EMIFA in 8-bit Async

EM_A[1]/(ALE)/GP[

IPD

mode), then the input states of AEAW[2:0] are sampled to set the

9]/ A16 B20 I/O/Z

DV

DD33

EMIFA Address Bus Width. After reset, these pins function as EMIFA

(AEAW1/PLLMS1)

or GPIO pin functions based on pin mux selection.

EM_A[2]/(CLE)/GP

For more details on the AEAW/PLLMS functions, see Section 3.5.1.2 ,

IPD

[8]/ B16 A20 I/O/Z

EMIFA Address Bus Width (AEAW) and Fast Boot PLL Multiplier

DV

DD33

(AEAW0/PLLMS0)

Select (PLLMS).

EM_BA[1]/ IPD These pins are multiplexed between the EMIFA and GPIO. When

C16 C20 I/O/Z

GP[5]/(AEM0) DV

DD33

RESET or POR is asserted, these pins function as EMIFA

configuration pins. At reset, the input states of AEM[2:0] are sampled

EM_BA[0]/ IPD

C17 E20 I/O/Z

to set the EMIFA Pinout Mode.

GP[6]/(AEM1) DV

DD33

For more details, see Section 3.5.1 , Configurations at Reset. After

reset, these pins function as EMIFA or GPIO pin functions based on

EM_A[0]/ IPD

pin mux selection.

B17 C21 I/O/Z

GP[7]/(AEM2) DV

DD33

For more details on the AEM functions, see Section 3.5.1.1 , EMIFA

Pinout Mode (AEM[2:0]).

(1) I = Input, O = Output, Z = High impedance, S = Supply voltage, GND = Ground, A = Analog signal

(2) IPD = Internal pulldown, IPU = Internal pullup. For more detailed information on pullup/pulldown resistors and situations where external

pullup/pulldown resistors are required, see Section 3.9.1 , Pullup/Pulldown Resistors.

(3) Specifies the operating I/O supply voltage for each signal

Device Overview28 Submit Documentation Feedback

www.ti.com

TMS320DM6431

Digital Media Processor

SPRS342A – NOVEMBER 2006 – REVISED MARCH 2007

Table 2-10. EMIFA Terminal Functions (EMIFA Pinout Mode 1, AEM[2:0] = 001)

SIGNAL

TYPE

(1)

OTHER

(2) (3)

DESCRIPTION

ZWT ZDU

NAME

NO. NO.

EMIFA FUNCTIONAL PINS: 8-Bit ASYNC/NOR (EMIFA Pinout Mode 1, AEM[2:0] = 001)

Actual pin functions are determined by the PINMUX0 and PINMUX1 register bit settings (e.g., AEAW[2:0], AEM[2:0], etc.). For more details,

see Section 3.7 , Multiplexed Pin Configurations

This pin is multiplexed between EMIFA and GPIO.

For EMIFA, this pin is Chip Select 2 output EM_CS2 for use with

asynchronous memories (i.e., NOR flash).

IPD This is the chip select for the default boot and ROM boot modes.

EM_CS2/GP[12] C19 C22 I/O/Z

DV

DD33

Note: This pin features an internal pulldown (IPD). If this pin is

connected and used as an EMIFA chip select signal, for proper device

operation, an external pullup resistor must be used to ensure the

EM_CSx function defaults to an inactive (high) state.

This pin is multiplexed between EMIFA and GPIO.

For EMIFA, this pin is Chip Select 3 output EM_CS3 for use with

asynchronous memories (i.e., NOR flash).

IPD

EM_CS3/GP[13] C18 D22 I/O/Z

DV

DD33

Note: This pin features an internal pulldown (IPD). If this pin is

connected and used as an EMIFA chip select signal, for proper device

operation, an external pullup resistor must be used to ensure the

EM_CSx function defaults to an inactive (high) state.

This pin is multiplexed between EMIFA and GPIO.

For EMIFA, it is Chip Select 4 output EM_CS4 for use with

asynchronous memories (i.e., NOR flash).

IPD

EM_CS4/GP[32] E19 H22 I/O/Z

DV

DD33

Note: This pin features an internal pulldown (IPD). If this pin is

connected and used as an EMIFA chip select signal, for proper device

operation, an external pullup resistor must be used to ensure the

EM_CSx function defaults to an inactive (high) state.

This pin is multiplexed between EMIFA and GPIO.

For EMIFA, it is Chip Select 5 output EM_CS5 for use with

asynchronous memories (i.e., NOR flash).

IPD

EM_CS5/GP[33] F19 J22 I/O/Z

DV

DD33

Note: This pin features an internal pulldown (IPD). If this pin is

connected and used as an EMIFA chip select signal, for proper device

operation, an external pullup resistor must be used to ensure the

EM_CSx function defaults to an inactive (high) state.

This pin is multiplexed between VPFE (CCDC), EMIFA, and GPIO.

C_WE/EM_R/ W/ IPD

D13 C17 I/O/Z

GP[35] DV

DD33

For EMIFA, it is read/write output EM_R/ W.

EM_WAIT/ IPU For EMIFA (ASYNC/NOR), this pin is wait state extension input

E15 D20 I/O/Z

(RDY/ BSY) DV

DD33

EM_WAIT.

IPU

EM_OE D15 D19 I/O/Z For EMIFA, it is output enable output EM_OE.

DV

DD33

IPU

EM_WE E14 C19 I/O/Z For EMIFA, it is write enable output EM_WE.

DV

DD33

This pin is multiplexed between EMIFA and GPIO.

EM_BA[0]/ IPD

For EMIFA, this is the Bank Address 0 output (EM_BA[0]). When

C17 E20 I/O/Z

GP[6]/(AEM1) DV

DD33

connected to an 8-bit asynchronous memory, this pin is the lowest

order bit of the byte address.

This pin is multiplexed between EMIFA and GPIO.

EM_BA[1]/ IPD

For EMIFA, this is the Bank Address 1 output EM_BA[1]. When

C16 C20 I/O/Z

GP[5]/(AEM0) DV

DD33

connected to an 8-bit asynchronous memory, this pin is the 2nd bit of

the address.

(1) I = Input, O = Output, Z = High impedance, S = Supply voltage, GND = Ground, A = Analog signal

(2) IPD = Internal pulldown, IPU = Internal pullup. For more detailed information on pullup/pulldown resistors and situations where external

pullup/pulldown resistors are required, see Section 3.9.1 , Pullup/Pulldown Resistors.

(3) Specifies the operating I/O supply voltage for each signal

Submit Documentation Feedback Device Overview 29

www.ti.com

PRODUCT PREVIEW

TMS320DM6431

Digital Media Processor

SPRS342A – NOVEMBER 2006 – REVISED MARCH 2007

Table 2-10. EMIFA Terminal Functions (EMIFA Pinout Mode 1, AEM[2:0] = 001) (continued)

SIGNAL

TYPE

(1)

OTHER

(2) (3)

DESCRIPTION

ZWT ZDU

NAME

NO. NO.

This pin is multiplexed between VPFE (CCDC), EMIFA, and GPIO.

C_FIELD/ IPD

D12 C16 I/O/Z

EM_A[21]/GP[34] DV

DD33

For EMIFA, it is address bit 21 output EM_A[21].

This pin is multiplexed between VPFE (CCDC), EMIFA, and GPIO.

CI0(CCD8)/ IPD

C12 C15 I/O/Z

For EMIFA (AEM[2:0] = 001), this pin is address bit 20 output

EM_A[20]/GP[44] DV

DD33