Texas Instruments TLV1548MJ, TLV1548MJB, TLV1548MFKB, TLV1548IDBR, TLV1548IDB Datasheet

...

TLV1544C, TLV1544I, TLV1548C, TLV1548I, TLV1548M

LOW-VOLTAGE 10-BIT ANALOG-TO-DIGITAL CONVERTERS

WITH SERIAL CONTROL AND 4/8 ANALOG INPUTS

SLAS139C – DECEMBER 1996 – REVISED JANUARY 1999

1

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

D

Conversion Time ≤ 10 µs

D

10-Bit-Resolution ADC

D

Programmable Power-Down

Mode ...1 µA

D

Wide Range Single-Supply Operation of

2.7 V dc to 5.5 V dc

D

Analog Input Range of 0 V to V

CC

D

Built-in Analog Multiplexer with 8 Analog

Input Channels

D

TMS320 DSP and Microprocessor SPI and

QSPI Compatible Serial Interfaces

D

End-of-Conversion (EOC) Flag

D

Inherent Sample-and-Hold Function

D

Built-In Self-Test Modes

D

Programmable Power and Conversion Rate

D

Asynchronous Start of Conversion for

Extended Sampling

D

Hardware I/O Clock Phase Adjust Input

description

The TLV1544 and TLV1548 are CMOS 10-bit

switched-capacitor successive-approximation (SAR)

analog-to-digital (A/D) converters. Each device

has a chip select (CS

), input-output clock (I/O

CLK), data input (DA T A IN) and serial data output

(DATA OUT) that provide a direct 4-wire

synchronous serial peripheral interface (SPI,

QSPI) port of a host microprocessor. When

interfacing with a TMS320 DSP, an additional

frame sync signal (FS) indicates the start of a

serial data frame. The devices allow high-speed

data transfers from the host. The INV CLK

input

provides further timing flexibility for the serial

interface.

In addition to a high-speed converter and versatile

control capability, the device has an on-chip

1 1-channel multiplexer that can select any one of

eight analog inputs or any one of three internal self-test voltages. The sample-and-hold function is automatic

except for the extended sampling cycle, where the sampling cycle is started by the falling edge of asynchronous

CST ART

. At the end of the A/D conversion, the end-of-conversion (EOC) output goes high to indicate that the

conversion is complete. The TLV1544 and TLV1548 are designed to operate with a wide range of supply

voltages with very low power consumption. The power saving feature is further enhanced with a

software-programmed power-down mode and conversion rate. The converter incorporated in the device

features differential high-impedance reference inputs that facilitate ratiometric conversion, scaling, and

isolation of analog circuitry from logic and supply noise. A switched-capacitor design allows low-error

conversion over the full operating temperature range.

SPI and QSPI are registered trademarks of Motorola, Inc.

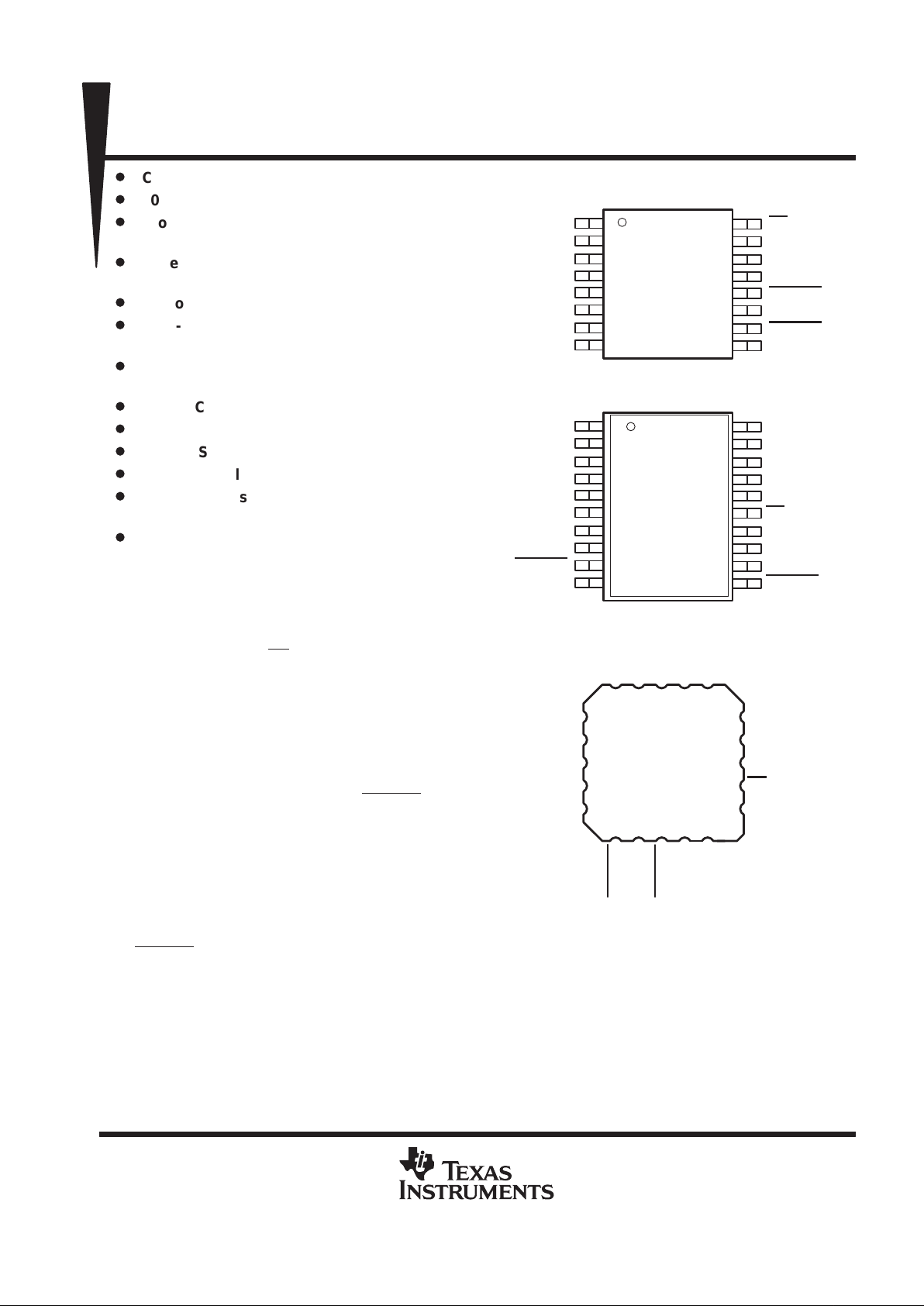

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

A0

A1

A2

A3

A4

A5

A6

A7

CSTART

GND

V

CC

EOC

I/O CLK

DATA IN

DATA OUT

CS

REF+

REF–

FS

INV CLK

DB OR J PACKAGE

(TOP VIEW)

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

DATA OUT

DATA IN

I/O CLK

EOC

V

CC

A0

A1

A2

CS

REF+

REF–

FS

INV CLK

GND

CSTART

A3

D OR PW PACKAGE

(TOP VIEW)

1920132

17

18

16

15

14

1312119 10

5

4

6

7

8

I/O CLK

DATA IN

DATA OUT

CS

REF+

A3

A4

A5

A6

A7

A2A1A0VEOC

GND

INV CLK

FS

REF–

CSTART

FK PACKAGE

(TOP VIEW)

CC

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

Copyright 1999, Texas Instruments Incorporated

TLV1544C, TLV1544I, TLV1548C, TLV1548I, TLV1548M

LOW-VOLTAGE 10-BIT ANALOG-TO-DIGITAL CONVERTERS

WITH SERIAL CONTROL AND 4/8 ANALOG INPUTS

SLAS139C – DECEMBER 1996 – REVISED JANUARY 1999

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

description (continued)

The TLV1544 has four analog input channels while the TLV1548 has eight analog input channels. The

TL V1544C and TLV1548C are characterized for operation from 0°C to 70°C. The TLV1544I and TL V1548I are

characterized for operation over the full industrial temperature range of –40°C to 85°C. The TLV1548M is

characterized for operation over the full military temperature range of –55°C to 125°C.

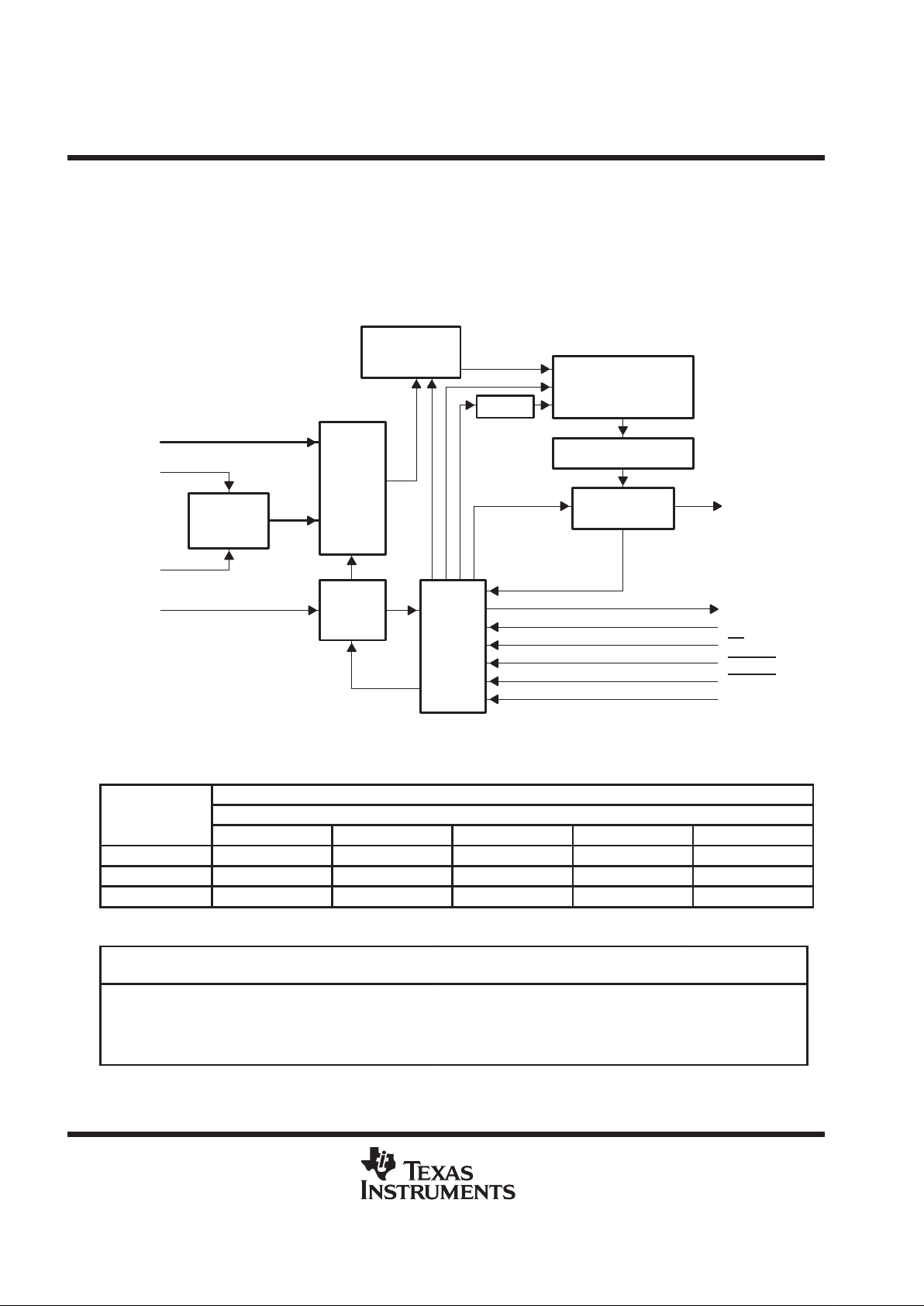

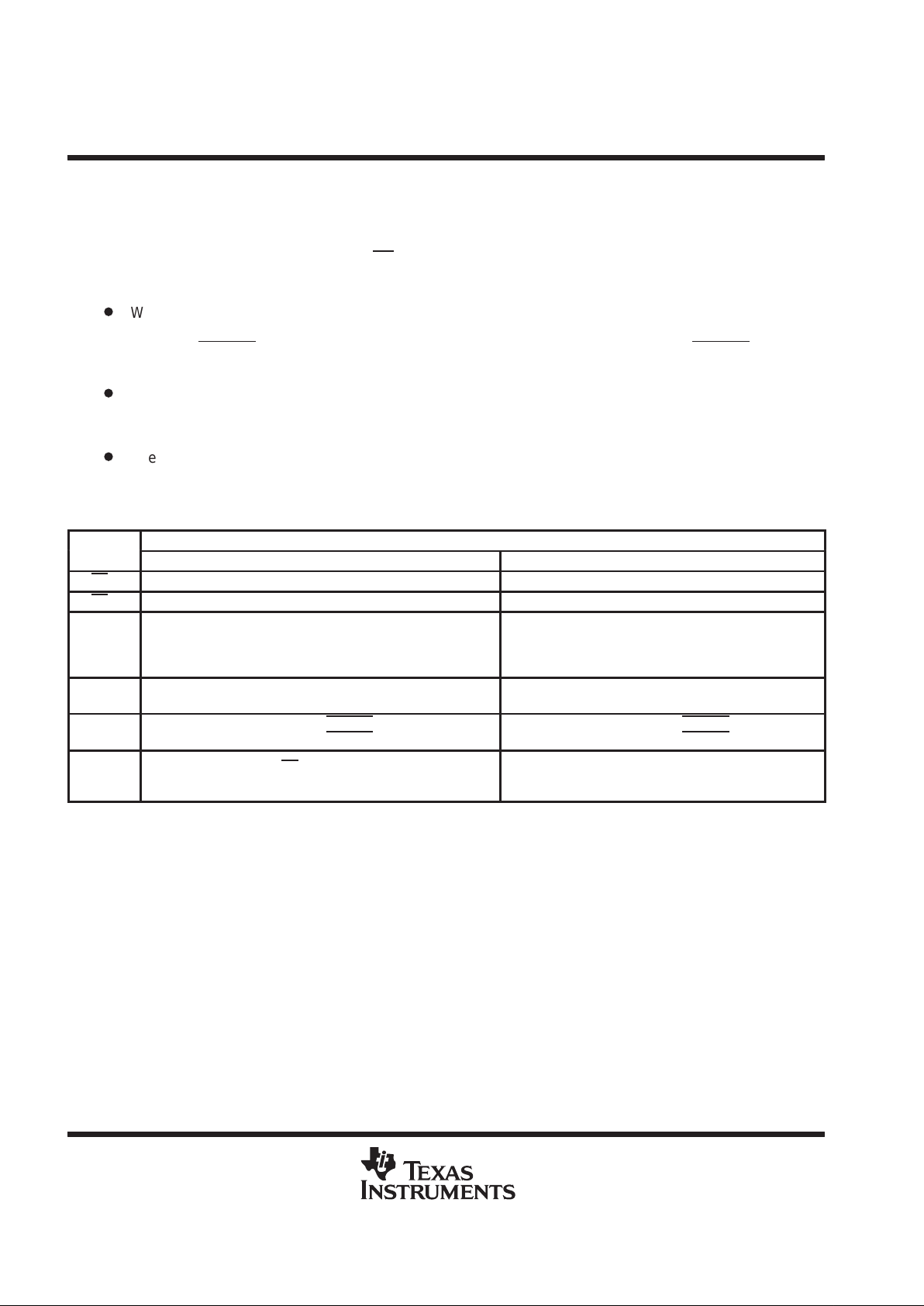

functional block diagram

Analog

MUX

Self-Test

Reference

Input

Data

Register

Control

Logic

and

I/O

Counters

10-Bit ADC

(Switch Capacitors)

Output Data Register

10-to-1

Data Selector

Sample

and

Hold Function

CLOCK

A0–A7

REF+

REF–

DATA IN

DATA OUT

EOC

FS

CS

CSTART

INV CLK

I/O CLK

Terminals shown are for the DB package.

1–8

14

13

17

16

19

12

15

9

11

18

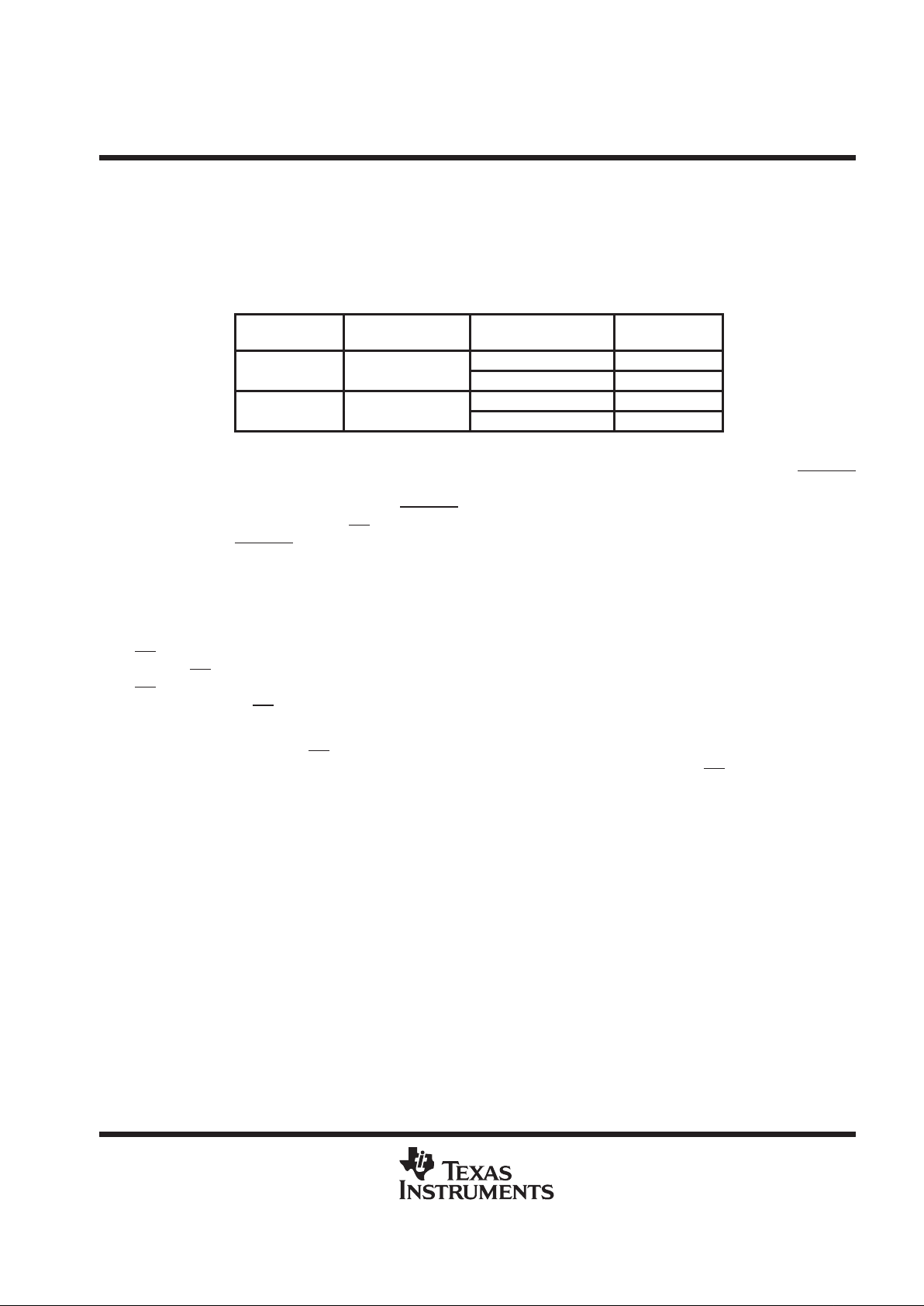

AVAILABLE OPTIONS

PACKAGE

T

A

SMALL OUTLINE

(DB) (D) (PW) (J) (FK)

0°C to 70°C TLV1548CDB TLV1544CD TLV1544CPW

–40°C to 85°C TLV1548IDB TLV1544ID TLV1544IPW

–55°C to 125°C TLV1548MJ TLV1548MFK

DISSIPATION RATING TABLE

T

≤ 25°C DERATING FACTOR

†

T

= 70°C T

= 85°C T

= 125°C

PACKAGE

A

POWER RATING ABOVE TA = 25°CAPOWER RATINGAPOWER RATINGAPOWER RATING

DB

785 mW

8.7 mW/°C

°

393 mW

261 mW

—

DPW799 mW

604 mW

8.9 mW/°C

6.7 mW/°C

399 mW

302 mW

266 mW

201 mW

—

—

JFK1894 mW

1375 mW

15.1 mW/°C

11.0 mW/°C

1212 mW

880 mW

985 mW

715 mW

379 mW

275 mW

†

This is the inverse of the traditional junction-to-ambient thermal resistance (RΘJA). RΘJA values are derived from T exas Instruments

characterization data. Thermal resistance is not production tested and values are given for informational purposes only .

TLV1544C, TLV1544I, TLV1548C, TLV1548I, TLV1548M

LOW-VOLTAGE 10-BIT ANALOG-TO-DIGITAL CONVERTERS

WITH SERIAL CONTROL AND 4/8 ANALOG INPUTS

SLAS139C – DECEMBER 1996 – REVISED JANUARY 1999

3

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

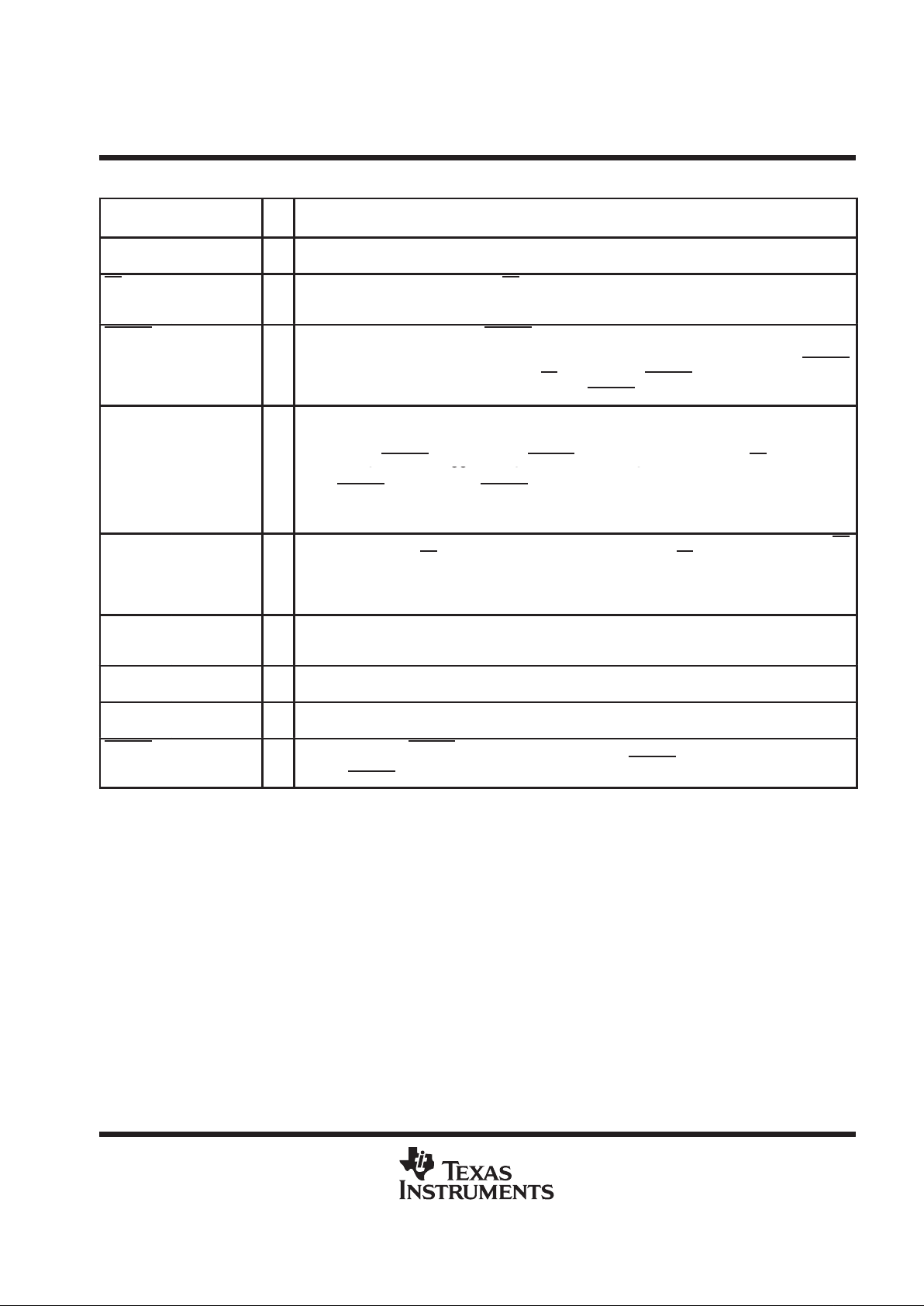

Terminal Functions

TERMINAL

NAME NO.†NO.

‡

I/O

DESCRIPTION

A0–A3

A4–A7

6–9–1–4

5–8

I Analog inputs. The analog inputs are internally multiplexed. (For a source impedance greater than

1 kΩ, the asynchronous start should be used to increase the sampling time.)

CS 16 15 I Chip select. A high-to-low transition on CS resets the internal counters and controls and enables DA T A IN,

DAT A OUT, and I/O CLK within the maximum setup time. A low-to-high transition disables DA TA IN, DA T A

OUT, and I/O CLK within the setup time.

CSTAR T 10 9 I Sampling/conversion start control. CSTART controls the start of the sampling of an analog input from a

selected multiplex channel. A high-to-low transition starts the sampling of the analog input signal. A

low-to-high transition puts the sample-and-hold function in hold mode and starts the conversion. CST ART

is independent from I/O CLK and works when CS is high. The low CSTAR T duration controls the duration

of the sampling cycle for the switched capacitor array. CSTART

is tied to VCC if not used.

DATA IN 2 17 I Serial data input. The 4-bit serial data selects the desired analog input and test voltage to be converted next

in a normal cycle. These bits can also set the conversion rate and enable the power-down mode.

When operating in the microprocessor mode, the input data is presented MSB first and is shifted in on the

first four rising (INV CLK

= VCC) or falling (INV CLK = GND) edges of I/O CLK (after CS↓).

g(

CC

)g( )g ( )

When operating in the DSP mode, the input data is presented MSB first and is shifted in on the first four

falling (INV CLK

= VCC) or rising (INV CLK = GND) edges of I/O CLK (after FS↓).

After the four input data bits have been read into the input data register, DA TA IN is ignored for the remainder

of the current conversion period.

DATA OUT 1 16 O Three-state serial output of the A/D conversion result. DA T A OUT is in the high-impedance state when CS

is high and active when CS is low or after FS↓ (in DSP mode). With a valid CS signal, DAT A OUT is removed

from the high-impedance state and is driven to the logic level corresponding to the MSB or LSB value of

the previous conversion result. DATA OUT changes on the falling (microprocessor mode) or rising (DSP

mode) edge of I/O CLK.

EOC 4 19 O End of conversion. EOC goes from a high to a low logic level on the tenth rising (microprocessor mode)

or tenth falling (DSP mode) edge of I/O CLK and remains low until the conversion is complete and data is

ready for transfer. EOC can also indicate that the converter is busy.

FS 13 12 I DSP frame synchronization input. FS indicates the start of a serial data frame into or out of the device. FS

is tied to VCC when interfacing the device with a microprocessor.

GND 11 10 Ground return for internal circuitry. All voltage measurements are with respect to GND, unless otherwise

noted.

INV CLK 12 11 I Inverted clock input. INV CLK is tied to GND when an inverted I/O CLK is used as the source of the input

clock. This affects both microprocessor and DSP interfaces. INV CLK

is tied to VCC if I/O CLK is not

inverted. INV CLK

can also invoke a built-in test mode.

†

Terminal numbers are for the D package.

‡

Terminal numbers are for the DB, J, and FK packages.

TLV1544C, TLV1544I, TLV1548C, TLV1548I, TLV1548M

LOW-VOLTAGE 10-BIT ANALOG-TO-DIGITAL CONVERTERS

WITH SERIAL CONTROL AND 4/8 ANALOG INPUTS

SLAS139C – DECEMBER 1996 – REVISED JANUARY 1999

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

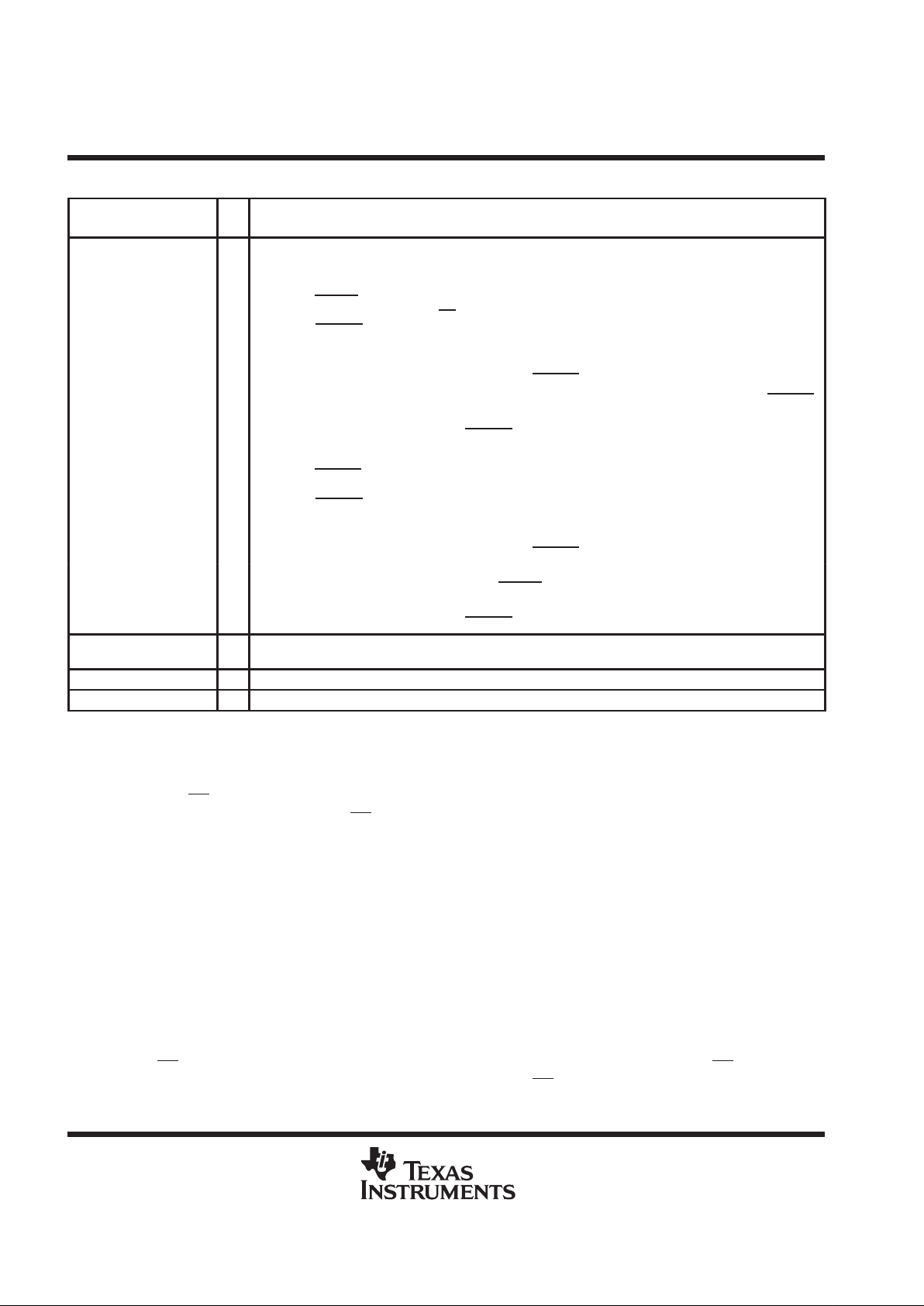

Terminal Functions (Continued)

TERMINAL

NAME NO.†NO.

‡

I/O

DESCRIPTION

I/O CLK 3 18 I

Input/output clock. I/O CLK receives the serial I/O clock input in the two modes and performs the following

four functions in each mode:

Microprocessor mode

• When INVCLK = V

CC

, I/O CLK clocks the four input data bits into the input data register on the first four

rising edges of I/O CLK after CS

↓ with the multiplexer address available after the fourth rising edge.

When INV CLK

= GND, input data bits are clocked in on the first four falling edges instead.

• On the fourth falling edge of I/O CLK, the analog input voltage on the selected multiplex input begins

charging the capacitor array and continues to do so until the tenth rising edge of I/O CLK except in the

extended sampling cycle where the duration of CST ART

determines when to end the sampling cycle.

• Output data bits change on the first ten falling I/O clock edges regardless of the condition of INV CLK.

• I/O CLK transfers control of the conversion to the internal state machine on the tenth rising edge of I/O

CLK regardless of the condition of INV CLK

.

Digital signal processor (DSP) mode

• When INV CLK = V

CC

, I/O CLK clocks the four input data bits into the input data register on the first four

falling edges of I/O CLK after FS↓ with the multiplexer address available after the fourth falling edges.

When INV CLK

= GND, input data bits are clocked in on the first four rising edges instead.

• On the fourth rising edge of I/O CLK, the analog input voltage on the selected multiplex input begins

charging the capacitor array and continues to do so until the tenth falling edge of I/O CLK except in the

extended sampling cycle where the duration of CST ART

determines when to end the sampling cycle.

• Output data MSB shows after FS↓and the rest of the output data bits change on the first ten rising I/O

CLK edges regarless of the condition of INV CLK

.

• I/O CLK transfers control of the conversion to the internal state machine on the tenth falling edge of I/O

CLK regardless of the condition of INV CLK

.

REF+ 15 14 I Upper reference voltage (nominally VCC ). The maximum input voltage range is determined by the difference

between the voltages applied to REF+ and REF–.

REF– 14 13 I Lower reference voltage (nominally ground)

V

CC

5 20 I Positive supply voltage

†

Terminal numbers are for the D package.

‡

Terminal numbers are for the DB, J, and FK packages.

detailed description

Initially, with CS high (inactive), DATA IN and I/O CLK are disabled and DATA OUT is in the high-impedance

state. When the serial interface takes CS

low (active), the conversion sequence begins with the enabling of I/O

CLK and DAT A IN and the removal of DATA OUT from the high-impedance state. The host then provides the

4-bit channel address to DATA IN and the I/O clock sequence to I/O CLK. During this transfer, the host serial

interface also receives the previous conversion result from DA TA OUT . I/O CLK receives an input sequence from

the host that is from 10 to 16 clocks long. The first four valid I/O CLK cycles load the input data register with the

4-bit input data on DA TA IN that selects the desired analog channel. The next six clock cycles provide the control

timing for sampling the analog input. Sampling of the analog input is held after the first valid I/O CLK sequence

of ten clocks. The tenth clock edge also takes EOC low and begins the conversion. The exact locations of the

I/O clock edges depend on the mode of operation.

serial interface

The TL V1548 is compatible with generic microprocessor serial interfaces such as SPI and QSPI, and a TMS320

DSP serial interface. The internal latched flag If_mode is generated by sampling the state of FS at the falling

edge of CS

. If_mode is set to one (for microprocessor) when FS is high at the falling edge of CS, and If_mode

is cleared to zero (for DSP) when FS is low at the falling edge of CS

. This flag controls the multiplexing of I/O

CLK and the state machine reset function. FS is pulled high when interfacing with a microprocessor.

TLV1544C, TLV1544I, TLV1548C, TLV1548I, TLV1548M

LOW-VOLTAGE 10-BIT ANALOG-TO-DIGITAL CONVERTERS

WITH SERIAL CONTROL AND 4/8 ANALOG INPUTS

SLAS139C – DECEMBER 1996 – REVISED JANUARY 1999

5

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

I/O CLK

The I/O CLK can go up to 10 MHz for most of the voltage range when fast I/O is possible. The maximum I/O

CLK is limited to 2.8 MHz for a supply voltage range from 2.7 V . Table 1 lists the maximum I/O CLK frequencies

for all different supply voltage ranges. This also depends on input source impedance. For example, I/O CLK

speed faster than 2.39 MHz is achievable if the input source impedance is less than 1 kΩ.

Table 1. Maximum I/O CLK Frequency

V

CC

MAXIMUM INPUT

RESISTANCE (Max)

SOURCE IMPEDANCE I/O CLK

1 kΩ 2.39 MHz

2.7 V

5 K

100 Ω 2.81 MHz

1 kΩ 7.18 MHz

4.5 V

1 K

100 Ω 10 MHz

microprocessor serial interface

Input data bits from DATA IN are clocked in on the first four rising edges of the I/O CLK sequence if INV CLK

is held high when the device is in microprocessor interface mode. Input data bits are clocked in on the first four

falling edges of the I/O CLK sequence if INV CLK

is held low. The MSB of the previous conversion appears on

DA T A OUT on the falling edge of CS

. The remaining nine bits are shifted out on the next nine edges (depending

on the state of INV CLK

) of I/O CLK. Ten bits of data are transmitted to the host through DATA OUT.

A minimum of 9.5 clock pulses is required for the conversion to begin. On the tenth clock rising edge, the EOC

output goes low and returns to the high logic level when the conversion is complete; then the result can be read

by the host. On the tenth clock falling edge, the internal logic takes DA T A OUT low to ensure that the remaining

bit values are zero if the I/O CLK transfer is more than ten clocks long.

CS

is inactive (high) between serial I/O CLK transfers. Each transfer takes at least ten I/O CLK cycles. The falling

edge of CS

begins the sequence by removing DATA OUT from the high-impedance state. The rising edge of

CS

ends the sequence by returning DA TA OUT to the high-impedance state within the specified delay time. Also,

the rising edge of CS

disables I/O CLK and DA T A IN within a setup time. A conversion does not begin until the

tenth I/O CLK rising edge.

A high-to-low transition on CS

within the specified time during an ongoing cycle aborts the cycle, and the device

returns to the initial state (the output data register holds the previous conversion result). CS

should not be taken

low close to completion of conversion because the output data can be corrupted.

TLV1544C, TLV1544I, TLV1548C, TLV1548I, TLV1548M

LOW-VOLTAGE 10-BIT ANALOG-TO-DIGITAL CONVERTERS

WITH SERIAL CONTROL AND 4/8 ANALOG INPUTS

SLAS139C – DECEMBER 1996 – REVISED JANUARY 1999

6

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

DSP interface

The TL V1544/1548 can also interface with a DSP, from the TMS320 family for example, through a serial port.

The analog-to-digital converter (ADC) serves as a slave device where the DSP supplies FS and the serial I/O

CLK. Transmit and receive operations are concurrent. The falling edge of FS must occur no later than seven

I/O CLK periods after the falling edge of CS

.

DSP I/O cycles differ from microprocessor I/O cycles in the following ways:

D

When interfaced with a DSP , the output data MSB is available after FS↓. The remaining output data changes

on the rising edge of I/O CLK. The input data is sampled on the first four falling edges of I/O CLK after FS↓

and when INV CLK

is high, or the first four rising edges of I/O CLK after FS↓ and when INV CLK is low. This

operation is inverted when interfaced with a microprocessor.

D

A new DSP I/O cycle is started on the rising edge of I/O CLK after the rising edge of FS. The internal state

machine is reset on each falling edge of I/O CLK when FS is high. This operation is opposite when interfaced

with a microprocessor.

D

The TL V1544/1548 supports a 16-clock cycle when interfaced with a DSP. The output data is padded with

six trailing zeros when it is operated in DSP mode.

Table 2. TLV1544/TLV1548 Serial Interface Modes

INTERFACE MODE

I/O

MICROPROCESSOR ACTION DSP ACTION

CS↓ Initializes counter Samples state of FS

CS↑ Resets state machine and disable I/O Disables I/O

FS Connects to V

CC

Connects to DSP FSX output

Initializes the state machine at each CLK↓ after FS↑

Starts a new cycle at each CLK↑ following the initialization

(initializes the counter)

I/O CLK

Starts sampling of the analog input started at fourth I/O CLK↑

Conversion started at tenth I/O CLK↑

Starts sampling of the analog input at fourth I/O CLK↓

Starts sampling of the analog input at tenth I/O CLK↓

DATA IN

Samples input data on I/O CLK↑ (INV CLK high)

Samples input data on I/O CLK↓ (INV CLK

low)

Samples input data at I/O CLK↓ (INV CLK high)

Samples input data at I/O CLK↑ (INV CLK

low)

DATA OUT

Makes MSB available on CS↓

Changes remaining data on I/O CLK↓

Makes MSB available FS↓

Changes remaining data at each following I/O CLK↑ after

FS↓

TLV1544C, TLV1544I, TLV1548C, TLV1548I, TLV1548M

LOW-VOLTAGE 10-BIT ANALOG-TO-DIGITAL CONVERTERS

WITH SERIAL CONTROL AND 4/8 ANALOG INPUTS

SLAS139C – DECEMBER 1996 – REVISED JANUARY 1999

7

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

input data bits

DA TA IN is internally connected to a 4-bit serial input data register. The input data selects a different mode or

selects different analog input channels. The host provides the data word with the MSB first. Each data bit clocks

in on the edge (rising or falling depending on the status of INV CLK

and FS) of the I/O CLK sequence. The input

clock can be inverted by grounding INV CLK

(see Table 3 for the list of software programmed operations set

by the input data).

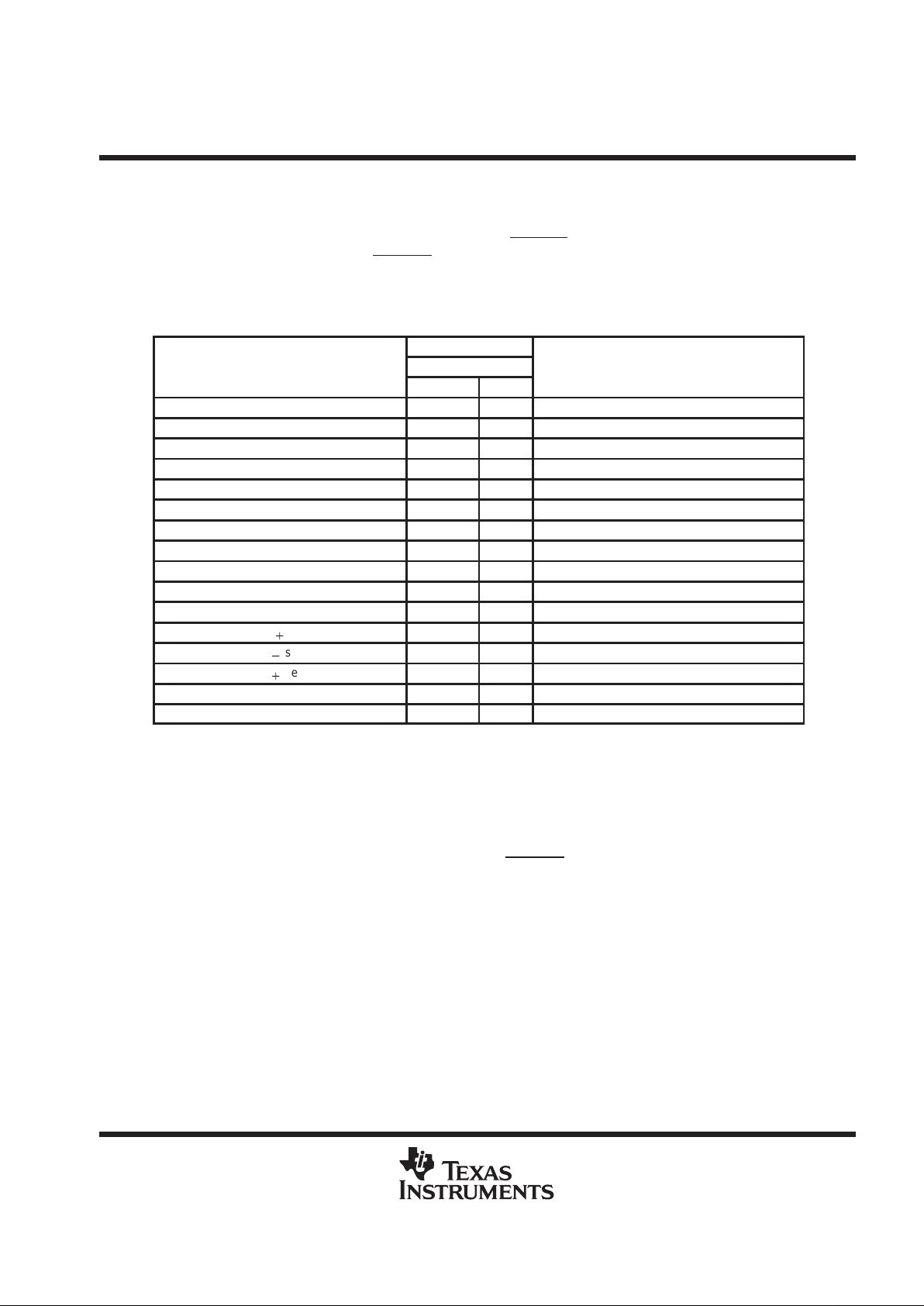

T able 3. TLV1544/1548 Software-Programmed Operation Modes

INPUT DATA BYTE

FUNCTION SELECT

A3 – A0

COMMENT

BINARY HEX

Analog channel A0 for TLV1548 selected 0000b 0h Channel 0 for TLV1544

Analog channel A1 for TLV1548 selected 0001b 1h

Analog channel A2 for TLV1548 selected 0010b 2h Channel 1 for TLV1544

Analog channel A3 for TLV1548 selected 0011b 3h

Analog channel A4 for TLV1548 selected 0100b 4h Channel 2 for TLV1544

Analog channel A5 for TLV1548 selected 0101b 5h

Analog channel A6 for TLV1548 selected 0110b 6h Channel 3 for TLV1544

Analog channel A7 for TLV1548 selected 011 1b 7h

Software power down set 1000b 8h No conversion result (cleared by any access)

Fast conversion rate (10 µs) set 1001b 9h No conversion result (cleared by setting to fast)

Slow conversion rate (40 µs) set 1010b Ah No conversion result (cleared by setting to slow)

Self-test voltage (V

ref

)

– V

ref–

)/2 selected 1011b Bh Output result = 200h

Self-test voltage V

ref

*

selected 1100b Ch Output result = 000h

Self-test voltage V

ref

)

selected 1101b Dh Output result = 3FFh

Reserved 1110b Eh No conversion result

Reserved 1111b Fh No conversion result

analog inputs and internal test voltages

The eight analog inputs and the three internal test inputs are selected by the 1 1-channel multiplexer according

to the input data bit as shown in Table 3. The input multiplexer is a break-before-make type to reduce

input-to-input noise injection resulting from channel switching.

The device can be operated in two distinct sampling modes: normal sampling mode (fixed sampling time) and

extended sampling mode (flexible sampling time). When CST ART

is held high, the device is operated in normal

sampling mode. When operated in normal sampling mode, sampling of the analog input starts on the rising edge

of the fourth I/O CLK pulse in the microprocessor interface mode (and on the fourth falling edge of I/O CLK in

the DSP interface mode). Sampling continues for 6 I/O CLK periods. The sample is held on the falling edge of

the tenth I/O CLK pulse in the microprocessor interface mode. The sample is held on the falling edge of the tenth

I/O CLK pulse in the DSP interface mode.The three test inputs are applied to the multiplexer, then sampled and

converted in the same manner as the external analog inputs.

TLV1544C, TLV1544I, TLV1548C, TLV1548I, TLV1548M

LOW-VOLTAGE 10-BIT ANALOG-TO-DIGITAL CONVERTERS

WITH SERIAL CONTROL AND 4/8 ANALOG INPUTS

SLAS139C – DECEMBER 1996 – REVISED JANUARY 1999

8

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

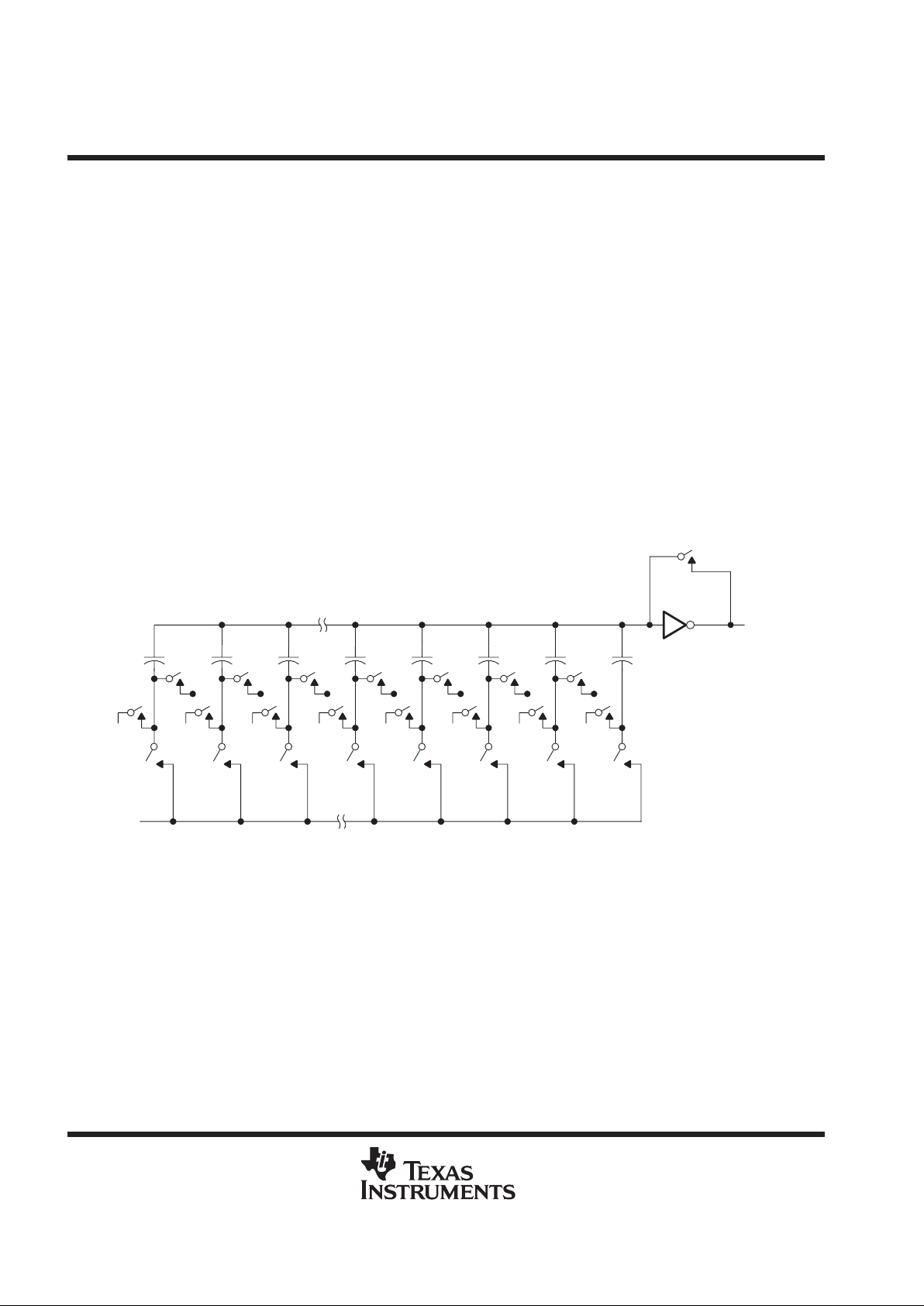

converter

The CMOS threshold detector in the successive-approximation conversion system determines the value of

each bit by examining the charge on a series of binary-weighted capacitors (see Figure 1). In the first phase

of the conversion process, the analog input is sampled by closing the S

C

switch and all ST switches

simultaneously. This action charges all of the capacitors to the input voltage.

In the next phase of the conversion process, all S

T

and SC switches are opened and the threshold detector

begins identifying bits by identifying the charge (voltage) on each capacitor relative to the reference (REF –)

voltage. In the switching sequence, ten capacitors are examined separately until all ten bits are identified and

then the charge-convert sequence is repeated. In the first step of the conversion phase, the threshold detector

looks at the first capacitor (weight = 512). Node 512 of this capacitor is switched to the REF+ voltage, and the

equivalent nodes of all the other capacitors on the ladder are switched to REF –. If the voltage at the summing

node is greater than the trip point of the threshold detector (approximately one-half V

CC

), a bit 0 is placed in the

output register and the 512-weight capacitor is switched to REF –. If the voltage at the summing node is less

than the trip point of the threshold detector, a bit 1 is placed in the register and the 512-weight capacitor remains

connected to REF + through the remainder of the successive-approximation process. The process is repeated

for the 256-weight capacitor, the 128-weight capacitor, and so forth down the line until all bits are counted.

With each step of the successive-approximation process, the initial charge is redistributed among the

capacitors. The conversion process relies on charge redistribution to count and weigh the bits from MSB to LSB.

S

C

Threshold

Detector

Node 512

REF–

REF+

S

T

512

V

I

To Output

Latches

REF–

S

T

REF+

REF–

S

T

REF+

REF–

S

T

REF+

REF–

S

T

REF+

S

T

REF+

REF–

S

T

REF+

REF–

S

T

11248128256

REF–

Figure 1. Simplified Model of the Successive-Approximation System

TLV1544C, TLV1544I, TLV1548C, TLV1548I, TLV1548M

LOW-VOLTAGE 10-BIT ANALOG-TO-DIGITAL CONVERTERS

WITH SERIAL CONTROL AND 4/8 ANALOG INPUTS

SLAS139C – DECEMBER 1996 – REVISED JANUARY 1999

9

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

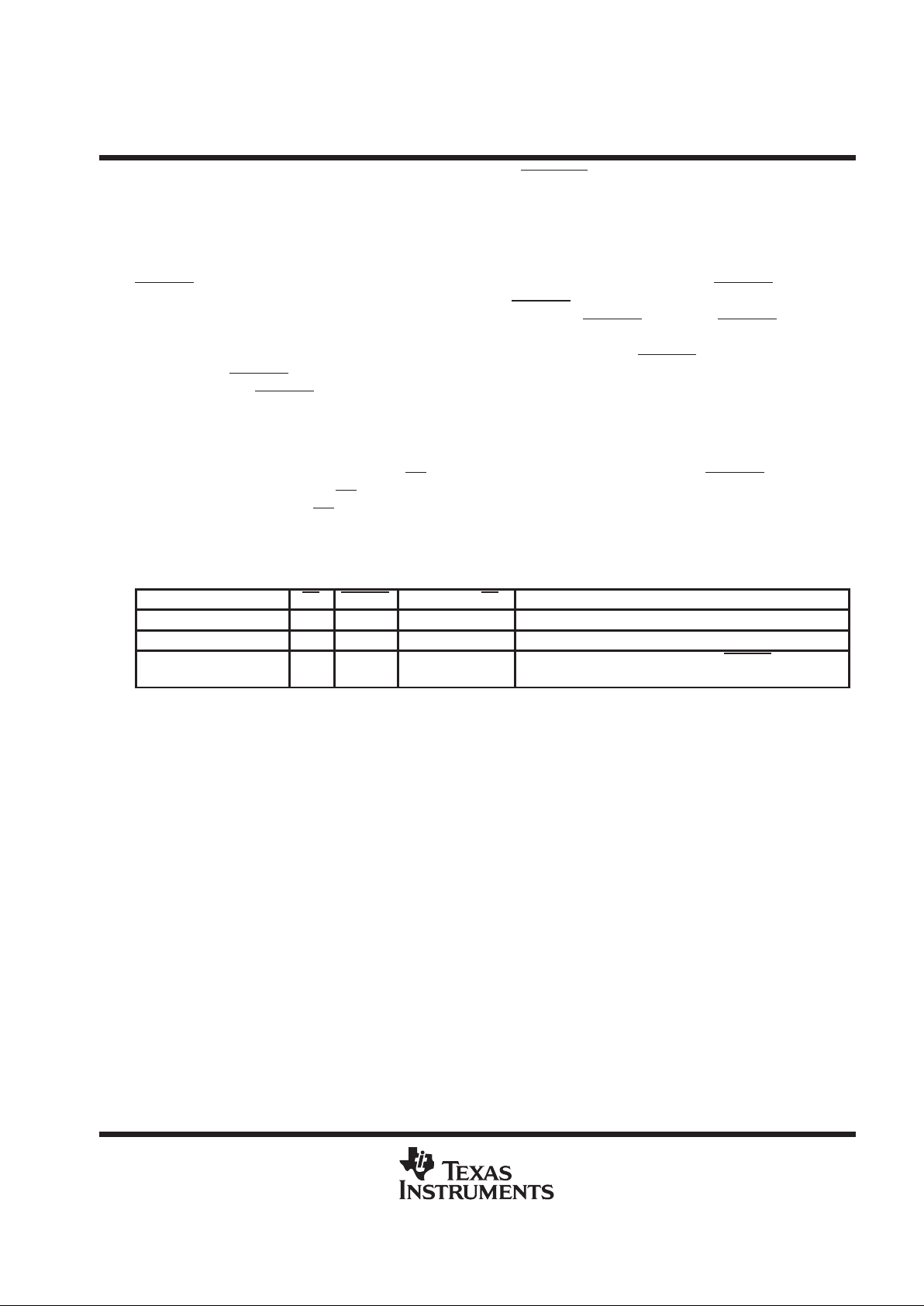

extended sampling, asynchronous start of sampling: CSTART operation

The extended sampling mode of operation programs the acquisition time (t

ACQ

) of the sample-and-hold circuit.

This allows the analog inputs of the device to be directly interfaced to a wide range of input source impedances.

The extended sampling mode consumes higher power depending on the duration of the sampling period

chosen.

CSTART

controls the sampling period and starts the conversion. The falling edge of CSTART initiates the

sampling period of a preset channel. The low time of CSTART

controls the acquisition time of the input

sample-and-hold circuit. The sample is held on the rising edge of CSTART

. Asserting CSTART causes the

converter to perform a new sample of the signal on the preset valid MUX channel (one of the eight) and discard

the current conversion result ready for output. Sampling continues as long as CST ART

is active (negative). The

rising edge of CST ART

ends the sampling cycle. The conversion cycle starts two internal system clocks after

the rising edge of CSTART

.

Once the conversion is complete, the processor can initiate a normal I/O cycle to read the conversion result and

set the MUX address for the next conversion. Since the internal flag AsyncFlag is set high, this flag setting

indicates the cycle is an output cycle, so no conversion is performed during the cycle. The internal state machine

tests the AsyncFlag on the falling edge of CS

. AsyncFlag is set high at the rising edge of CST ART , and it is reset

low at the rising edge of each CS

. A conversion cycle follows a sampling cycle only if AsyncFlag is tested as

low at the falling edge of CS

. As shown in Figure 2, an asynchronous I/O cycle can be removed by two

consecutive normal I/O cycles.

Table 4. TLV1544/1548 Hardware Configuration for Different Operating Modes

OPERATING MODES CS CSTART AsyncFlag at CS↓ ACTION

Normal sampling Low High Low Fixed 6 I/O CLK sampling, synchronous conversion follows

Normal I/O (read out only) Low High High No sampling, no conversion

Extended sampling High Low N/A

Flexible sampling period controlled by CSTAR T,

asynchronous conversion follows

TLV1544C, TLV1544I, TLV1548C, TLV1548I, TLV1548M

LOW-VOLTAGE 10-BIT ANALOG-TO-DIGITAL CONVERTERS

WITH SERIAL CONTROL AND 4/8 ANALOG INPUTS

SLAS139C – DECEMBER 1996 – REVISED JANUARY 1999

10

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

ООООООО

ООООООО

t

ACQ

Aa Ab Ab Ac Ad

XDaDb DbDc

CS

CSTART

DATA IN

EOC

DATA OUT

Async Flag

Read Out

Cycle

Read Out

Cycle

Read Out

Cycle

FS

(DSP Mode)

Complete Extended

Sample Cycle

t

ACQ

NOTES: A. Aa = Address for input channel a.

B. Da = Conversion result from channel a.

Hi–Z Hi–Z Hi–Z Hi–Z Hi–Z Hi–Z

Normal

Cycle

Normal

Cycle

Extended

Sample

Cycle

Extended

Sample

Cycle

Figure 2. Extended Sampling Operation

reference voltage inputs

There are two reference inputs used with the TLV1544/TLV1548, REF+ and REF–. These voltage values

establish the upper and lower limits of the analog inputs to produce a full-scale and zero-scale reading

respectively . The values of REF+, REF–, and the analog input should not exceed the positive supply or be lower

than GND consistent with the specified absolute maximum ratings. The digital output is at full scale when the

input signal is equal to or higher than REF+ and is at zero when the input signal is equal to or lower than REF–.

programmable conversion rate

The TL V1544/TLV1548 offers two conversion rates to maximize battery life when high-speed operation is not

necessary . The conversion rate is programmable. Once the conversion rate has been selected, it takes ef fect

immediately in the same cycle and stays at the same rate until the other rate is chosen. The conversion rate

should be set at power up. Activation and deactivation of the power-down state (digital logic active) has no effect

on the preset conversion rate.

TLV1544C, TLV1544I, TLV1548C, TLV1548I, TLV1548M

LOW-VOLTAGE 10-BIT ANALOG-TO-DIGITAL CONVERTERS

WITH SERIAL CONTROL AND 4/8 ANALOG INPUTS

SLAS139C – DECEMBER 1996 – REVISED JANUARY 1999

11

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

Table 5. Conversion Rate and Power Consumption Selection

TYPICAL SUPPL Y CURRENT, I

CC

CONVERSION RATE

CONVERSION TIME

,

t

conv

AVAILABLE V

CC

RANGE

INPUT DATA

OPERATING

POWER

DOWN

Fast conversion speed 7 µs typ 5.5 V to 3.3 V 9h 0.6 mA typ 1.5 mA max 1 µA typ

Slow conversion speed 15 µs typ 5.5 V to 2.7 V Ah 0.4 mA typ 1 mA max 1 µA typ

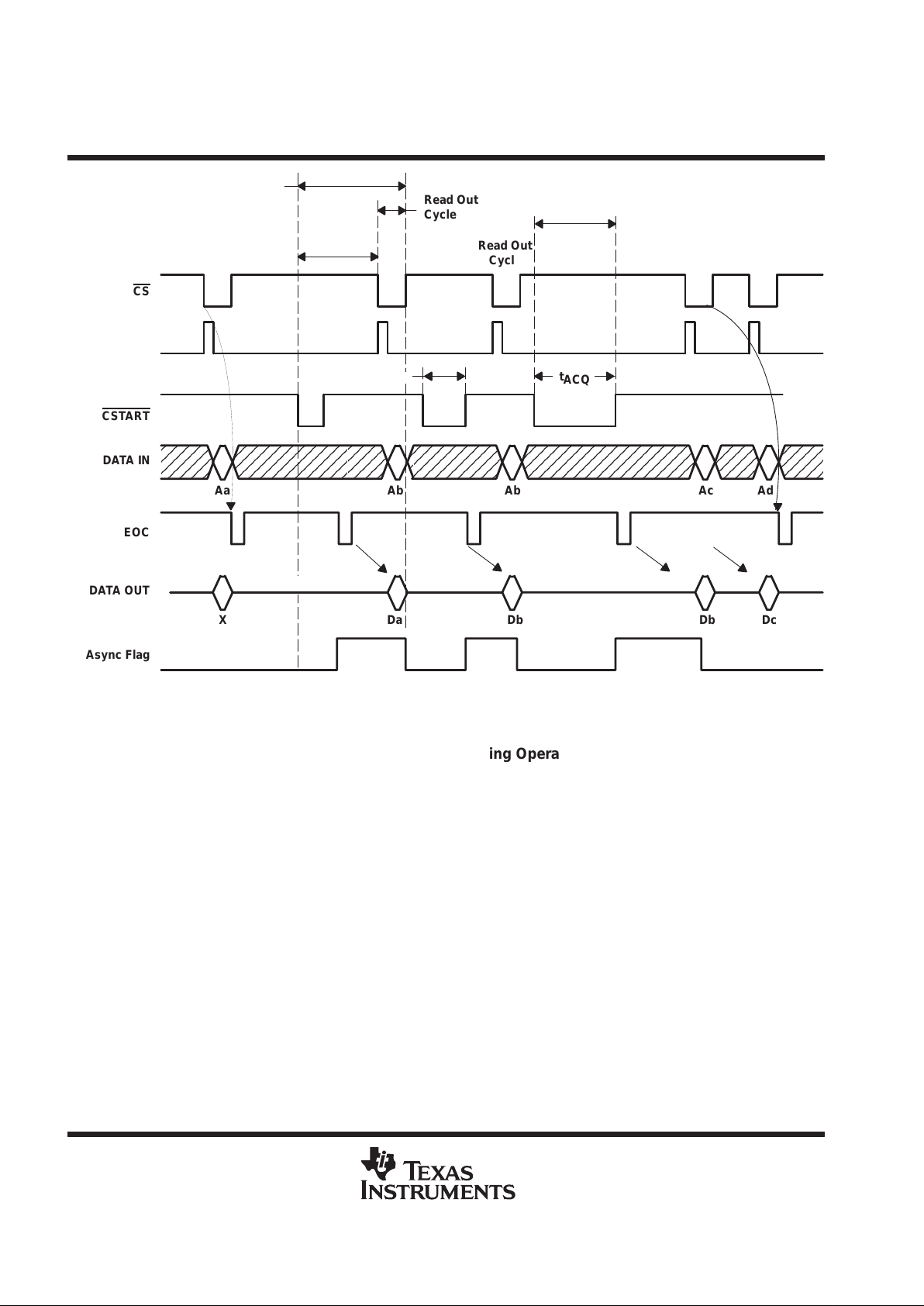

programmable power-down state

The device is put into the power-down state by writing 8h to DATA IN. The power-up state is restored during

the next active access by pulling CS

low. The conversion rate selected before the device is put into the

power-down state is not affected by the power-down mode. Power-down can be used to achieve even lower

power consumption. This is because the sustaining power (when not converting) is only 1.3 mA maximum and

standby power is only 1 µA maximum. (By averaging out the power consumption can be much lower than the

1 mA peak when the conversion throughput is lower.)

Power Down

CS

EOC

I

CC

DATA IN

Hi-Z Hi-Z

0

Supply Current

1 000

1 mA

(Typical Peak Supply)

0.3 mA

(Typical Sustaining)

0.0007 mA

(Typical Power Down

Supply)

Figure 3. Typical Supply Current During Conversion/Power Down

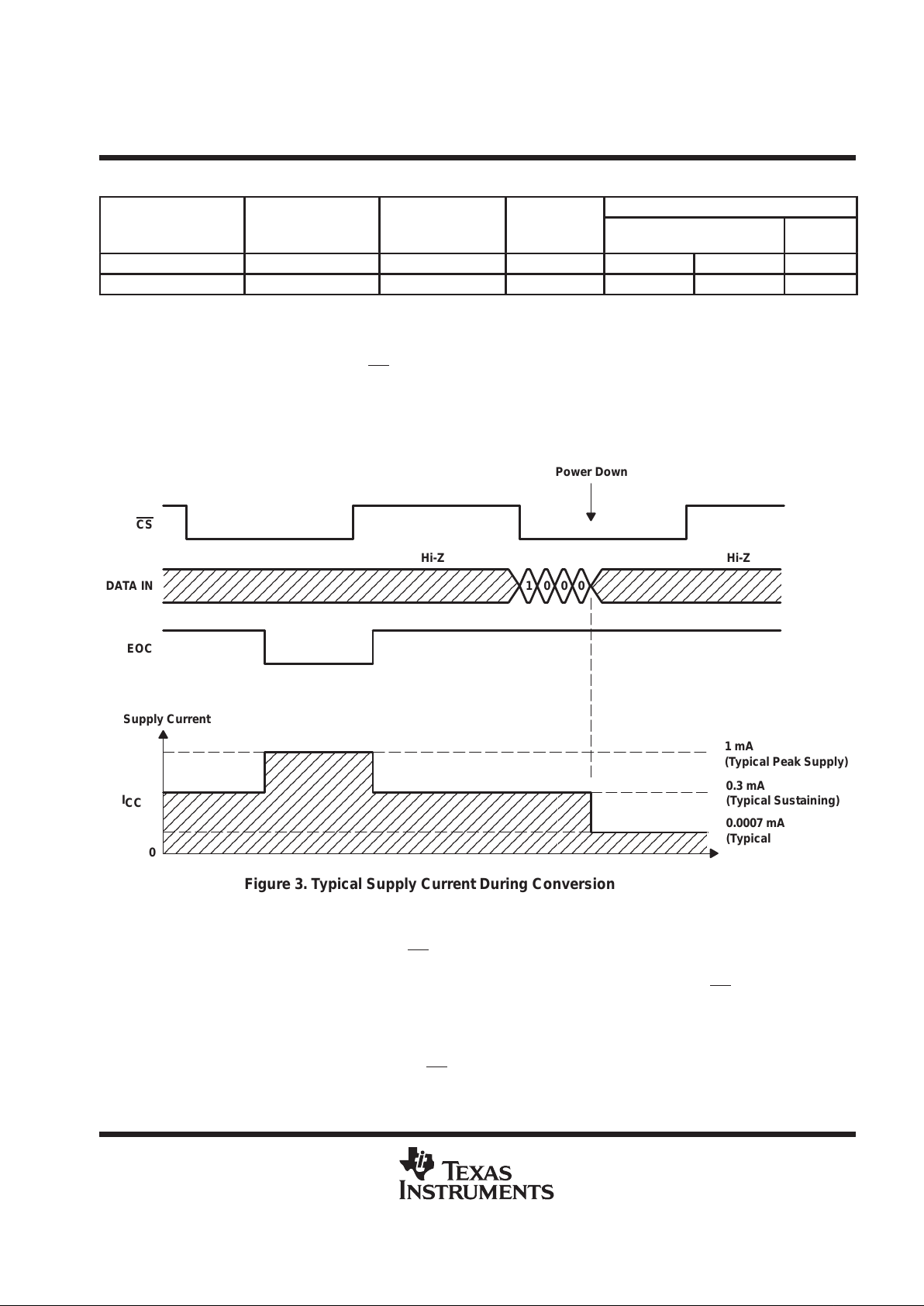

power up and initialization

After power up, if operating in DSP mode, CS and FS must be taken from high to low to begin an I/O cycle. EOC

is initially high, and the input data register is set to all zeroes. The content of the output data register is random,

and the first conversion result should be ignored. For initialization during operation, CS

is taken high and

returned low to begin the next I/O cycle. The first conversion after the device has returned from the power-down

state can be invalid and should be disregarded.

When power is first applied to the device, the conversion rate must be programmed, and the internal Async Flag

must be taken low once. The rising edge of CS

of the same cycle then takes Async Flag low.

TLV1544C, TLV1544I, TLV1548C, TLV1548I, TLV1548M

LOW-VOLTAGE 10-BIT ANALOG-TO-DIGITAL CONVERTERS

WITH SERIAL CONTROL AND 4/8 ANALOG INPUTS

SLAS139C – DECEMBER 1996 – REVISED JANUARY 1999

12

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

9h 0h Ab

X

D0

MUX Address for Channel 0

AsyncFlag Reset LowConversion Rate Set to Fast

Conversion Result From Channel 0

CS

DATA IN

DATA OUT

EOC

Signal Channel 0 Converted

FS

(For DSP Mode)

First Cycle After Powerup

Async Flag

(Internal)

Hi–Z Hi–Z Hi–Z Hi–Z

X

Figure 4. Power Up Initialization

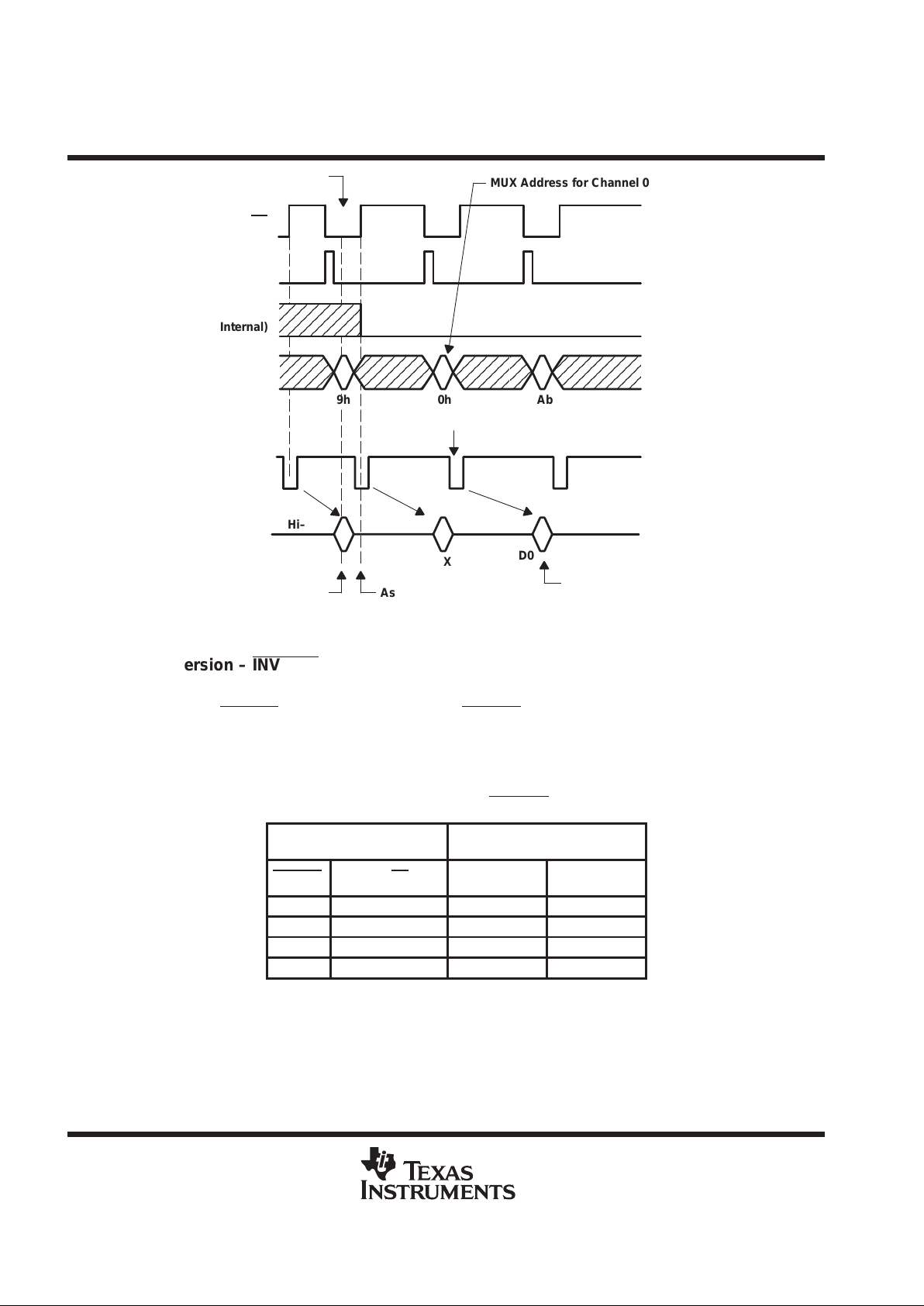

input clock inversion – INV CLK

The input data register uses I/O CLK as the source of the sampling clock. This clock can be inverted to provide

more setup time. INV CLK

can invert the clock. When INV CLK is grounded, the input clock for the input data

register is inverted. This allows an additional one-half I/O CLK period for the input data setup time. This is useful

for some serial interfaces. When the input sampling clock is inverted, the output data changes at the same time

that the input data is sampled.

Table 6. Function of INV CLK

CONDITION

CLOCK

I/O CLK ACTIVE EDGE

INV CLK FS at CS↓

OUTPUT DATA

CHANGES ON

INPUT DATA

SAMPLED ON

High High (MP† mode) ↓ ↑

High Low (DSP‡ mode) ↑ ↓

Low High (MP† mode) ↓ ↓

Low Low (DSP‡ mode) ↑ ↑

†

MP = microprocessor mode

‡

DSP = digital signal processor mode

Loading...

Loading...