TLC32047C, TLC32047I

Data Manual

Wide-Band Analog Interface Circuit

SLAS049A

April 1995

Printed on Recycled Paper

IMPORTANT NOTICE

T exas Instruments (TI) reserves the right to make changes to its products or to discontinue any

semiconductor product or service without notice, and advises its customers to obtain the latest

version of relevant information to verify , before placing orders, that the information being relied

on is current.

TI warrants performance of its semiconductor products and related software to the specifications

applicable at the time of sale in accordance with TI’s standard warranty . T esting and other quality

control techniques are utilized to the extent TI deems necessary to support this warranty.

Specific testing of all parameters of each device is not necessarily performed, except those

mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death,

personal injury , or severe property or environmental damage (“Critical Applications”).

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR

WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES

OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer.

Use of TI products in such applications requires the written approval of an appropriate TI officer .

Questions concerning potential risk applications should be directed to TI through a local SC

sales office.

In order to minimize risks associated with the customer’s applications, adequate design and

operating safeguards should be provided by the customer to minimize inherent or procedural

hazards.

TI assumes no liability for applications assistance, customer product design, software

performance, or infringement of patents or services described herein. Nor does TI warrant or

represent that any license, either express or implied, is granted under any patent right, copyright,

mask work right, or other intellectual property right of TI covering or relating to any combination,

machine, or process in which such semiconductor products or services might be or are used.

Copyright 1995, Texas Instruments Incorporated

Contents

Introduction 1-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Features 1-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Functional Block Diagrams 1-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Terminal Assignments 1-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Terminal Functions 1-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Detailed Description 2-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Internal Timing Configuration 2-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Analog Input 2-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

A/D Band-Pass Filter, Clocking, and Conversion Timing 2-4. . . . . . . . . . . . . . . . . . . . . . . .

A/D Converter 2-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Analog Output 2-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

D/A Low-Pass Filter, Clocking, and Conversion Timing 2-4. . . . . . . . . . . . . . . . . . . . . . . . .

D/A Converter 2-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Serial Port 2-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Synchronous Operation 2-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

One 16-Bit Word 2-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Two 8-Bit Bytes 2-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Synchronous Operating Frequencies 2-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Asynchronous Operation 2-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

One 16-Bit Word 2-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Two 8-Bit Bytes 2-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Asynchronous Operating Frequencies 2-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operation of TLC32047 With Internal Voltage Reference 2-7. . . . . . . . . . . . . . . . . . . . . . .

Operation of TLC32047 With External Voltage Reference 2-7. . . . . . . . . . . . . . . . . . . . . .

Reset 2-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Loopback 2-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Communications Word Sequence 2-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DR Word Bit Pattern 2-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Primary DX Word Bit Pattern 2-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Secondary DX Word Bit Pattern 2-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Page

iii

Reset Function 2-10. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Power-Up Sequence 2-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

AIC Register Constraints 2-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

AIC Responses to Improper Conditions 2-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operation With Conversion Times Too Close Together 2-12. . . . . . . . . . . . . . . . . . . . . . . .

More Than One Receive Frame Sync Occurring Between

Two Transmit Frame Syncs – Asynchronous Operation 2-12. . . . . . . . . . . . . . . . . .

More than One Transmit Frame Sync Occurring Between Two Receive

Frame Syncs – Asynchronous Operation 2-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

More than One Set of Primary and Secondary DX Serial Communications

Occurring Between Two Receive Frame

Syncs – Asynchronous Operation 2-13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

System Frequency Response Correction 2-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

(sin x)/x Correction 2-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

(sin x)/x Roll-Off for a Zero-Order Hold Function 2-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Correction Filter 2-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Correction Results 2-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

TMS320 Software Requirements 2-16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Specifications 3-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Absolute Maximum Ratings Over Operating Free-Air Temperature Range 3-1. . . . . . . . .

Recommended Operating Conditions 3-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Electrical Characteristics 3-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

total device 3-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

power supply rejection and crosstalk attenuation 3-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

serial port 3-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

receive amplifier input 3-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

transmit filter output 3-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

receive and transmit system distortion specifications 3-3. . . . . . . . . . . . . . . . . . . . . . . . .

receive channel signal-to-distortion ratio 3-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

transmit channel signal-to-distortion ratio 3-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

receive and transmit gain and dynamic range 3-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

receive channel band-pass filter transfer function 3-4. . . . . . . . . . . . . . . . . . . . . . . . . . . .

receive and transmit channel low-pass filter transfer function 3-5. . . . . . . . . . . . . . . . . .

Operating Characteristics (Noise) 3-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Timing Requirements 3-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Parameter Measurement Information – Timing Diagrams 4-1. . . . . . . . . . . . . . . . . . . . . . . . . . . .

TMS32047 – Processor Interface 4-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Typical Characteristics 5-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Applications Information 6-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Page

iv

List of Illustrations

Figure Page

1–1 Dual-Word (Telephone Interface) Mode 1-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1–2 Word Mode 1-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1–3 Byte Mode 1-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–1 Asynchronous Internal Timing Configuration 2-3. . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–2 Primary and Secondary Communications Word Sequence 2-8. . . . . . . . . . . . . . .

2–3 Reset on Power-Up Circuit 2-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–4 Conversion Times Too Close Together 2-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–5 More Than One Receive Frame Sync Between Two Transmit Frame Syncs 2-13

2–6 More Than One Transmit Frame Sync Between Two Receive Frame Syncs 2-13

2–7 More Than One Set of Primary and Secondary DX Serial Communications

Between Two Receive Frame Syncs 2-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–8 First-Order Correction Filter 2-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–1 IN+ and IN– Gain Control Circuitry 4-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–2 Dual-Word (Telephone Interface) Mode Timing 4-2. . . . . . . . . . . . . . . . . . . . . . . . . .

4–3 Word Timing 4-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–4 Byte-Mode Timing 4-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–5 Shift-Clock Timing 4-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4–6 TMS32010/TMS320C15–TLC32047 Interface Circuit 4-4. . . . . . . . . . . . . . . . . . . .

4–7 TMS32010/TMS320C15–TLC32047 Interface Timing 4-5. . . . . . . . . . . . . . . . . . . .

5–1 D/A and A/D Low-Pass Filter Response Simulation 5-1. . . . . . . . . . . . . . . . . . . . . .

5–2 D/A and A/D Low-Pass Filter Response 5-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–3 D/A and A/D Low-Pass Group Delay 5-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–4 A/D Band-Pass Response 5-2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–5 A/D Band-Pass Filter Response Simulation 5-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–6 A/D Band-Pass Filter Group Delay 5-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–7 A/D Channel High-Pass Filter 5-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–8 D/A (sin x)/x Correction Filter Response 5-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–9 D/A (sin x)/x Correction Filter Response 5-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–10 D/A (sin x)/x Correction Error 5-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–11 A/D Band-Pass Group Delay 5-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–12 D/A Low-Pass Group Delay 5-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–13 A/D Signal-to-Distortion Ratio vs Input Signal 5-7. . . . . . . . . . . . . . . . . . . . . . . . . . .

5–14 A/D Gain Tracking 5-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5–15 D/A Converter Signal-to-Distortion Ratio vs Input Signal 5-8. . . . . . . . . . . . . . . . .

5–16 D/A Gain Tracking 5-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

v

List of Illustrations (continued)

Figure Page

5–17 A/D Second Harmonic Distortion vs Input Signal 5-9. . . . . . . . . . . . . . . . . . . . . . . .

5–18 D/A Second Harmonic Distortion vs Input Signal 5-9. . . . . . . . . . . . . . . . . . . . . . . .

5–19 A/D Third Harmonic Distortion vs Input Signal 5-10. . . . . . . . . . . . . . . . . . . . . . . . . . .

5–20 D/A Third Harmonic Distortion vs Input Signal 5-10. . . . . . . . . . . . . . . . . . . . . . . . . . .

6–1 AIC Interface to the TMS32020/C25 Showing Decoupling Capacitors

and Schottky Diode 6-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6–2 External Reference Circuit for TLC32047 6-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

vi

List of Tables

Table Page

2–1 Mode-Selection Function Table 2-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–2 Primary DX Serial Communication Protocol 2-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–3 Secondary DX Serial Communication Protocol 2-10. . . . . . . . . . . . . . . . . . . . . . . . . . .

2–4 AIC Responses to Improper Conditions 2-12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–5 (sin x)/x Roll-Off Error 2-15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2–6 (sin x)/x Correction Table for f

4–1 Gain Control Table 4-1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

= 8000 Hz and fs = 9600 Hz 2-16. . . . . . . . . . . . . . . .

s

vii

1 Introduction

The TLC32047 wide-band analog interface circuit (AIC) is a complete analog-to-digital and digital-to-analog

interface system for advanced digital signal processors (DSPs) similar to the TMS32020, TMS320C25, and

TMS320C30. The TLC32047 offers a powerful combination of options under DSP control: three operating

modes [dual-word (telephone interface), word, and byte] combined with two word formats (8 bits and 16 bits)

and synchronous or asynchronous operation. It provides a high level of flexibility in that conversion and

sampling rates, filter bandwidths, input circuitry , receive and transmit gains, and multiplexed analog inputs

are under processor control.

This AIC features a

• band-pass switched-capacitor antialiasing input filter

• 14-bit-resolution A/D converter

• 14-bit-resolution D/A converter

• low-pass switched-capacitor output-reconstruction filter

The antialiasing input filter comprises eighth-order and fourth-order CC-type (Chebyshev/elliptic

transitional) low-pass and high-pass filters, respectively. The input filter is implemented in switchedcapacitor technology and is preceded by a continuous time filter to eliminate any possibility of aliasing

caused by sampled data filtering. When low-pass filtering is desired, the high-pass filter can be switched

out of the signal path. A selectable auxiliary differential analog input is provided for applications where more

than one analog input is required.

The output-reconstruction filter is an eighth-order CC-type (Chebyshev/elliptic transitional low-pass filter)

followed by a second-order (sin x)/x correction filter and is implemented in switched-capacitor technology .

This filter is followed by a continuous-time filter to eliminate images of the sample data signal. The on-board

(sin x)/x correction filter can be switched out of the signal path using digital signal processor control.

The A/D and D/A architectures ensure no missing codes and monotonic operation. An internal voltage

reference is provided to ease the design task and to provide complete control over the performance of the

IC. The internal voltage reference is brought out to REF . Separate analog and digital voltage supplies and

ground are provided to minimize noise and ensure a wide dynamic range. The analog circuit path contains

only differential circuitry to keep noise to a minimum. The exception is the DAC sample-and-hold, which

utilizes pseudo-differential circuitry.

The TLC32047C is characterized for operation from 0

operation from –40

°C to 85°C.

°C to 70°C, and the TLC32047I is characterized for

1–1

1.1 Features

• 14-Bit Dynamic Range ADC and DAC

• 16-Bit Dynamic Range Input With Programmable Gain

• Synchronous or Asynchronous ADC and DAC Sampling Rates Up to 25,000 Samples Per

Second

• Programmable Incremental ADC and DAC Conversion Timing Adjustments

• T ypical Applications

– Speech Encryption for Digital Transmission

– Speech Recognition and Storage Systems

– Speech Synthesis

– Modems at 8-kHz, 9.6-kHz, and 16-kHz Sampling Rates

– Industrial Process Control

– Biomedical Instrumentation

– Acoustical Signal Processing

– Spectral Analysis

– Instrumentation Recorders

– Data Acquisition

• Switched-Capacitor Antialiasing Input Filter and Output-Reconstruction Filter

• Three Fundamental Modes of Operation: Dual-Word (Telephone Interface), Word, and Byte

• 600-mil Wide N Package

• Digital Output in Twos Complement Format

• CMOS Technology

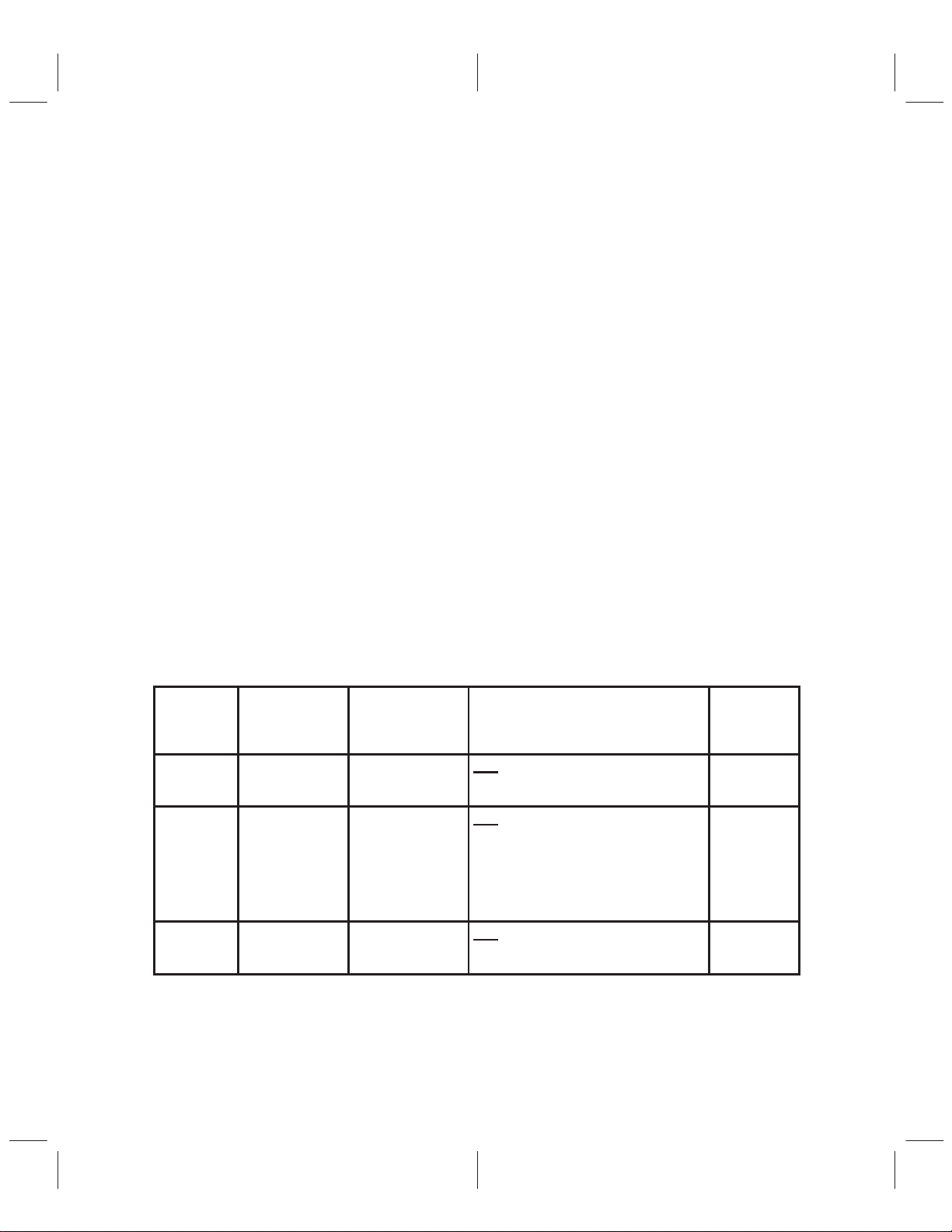

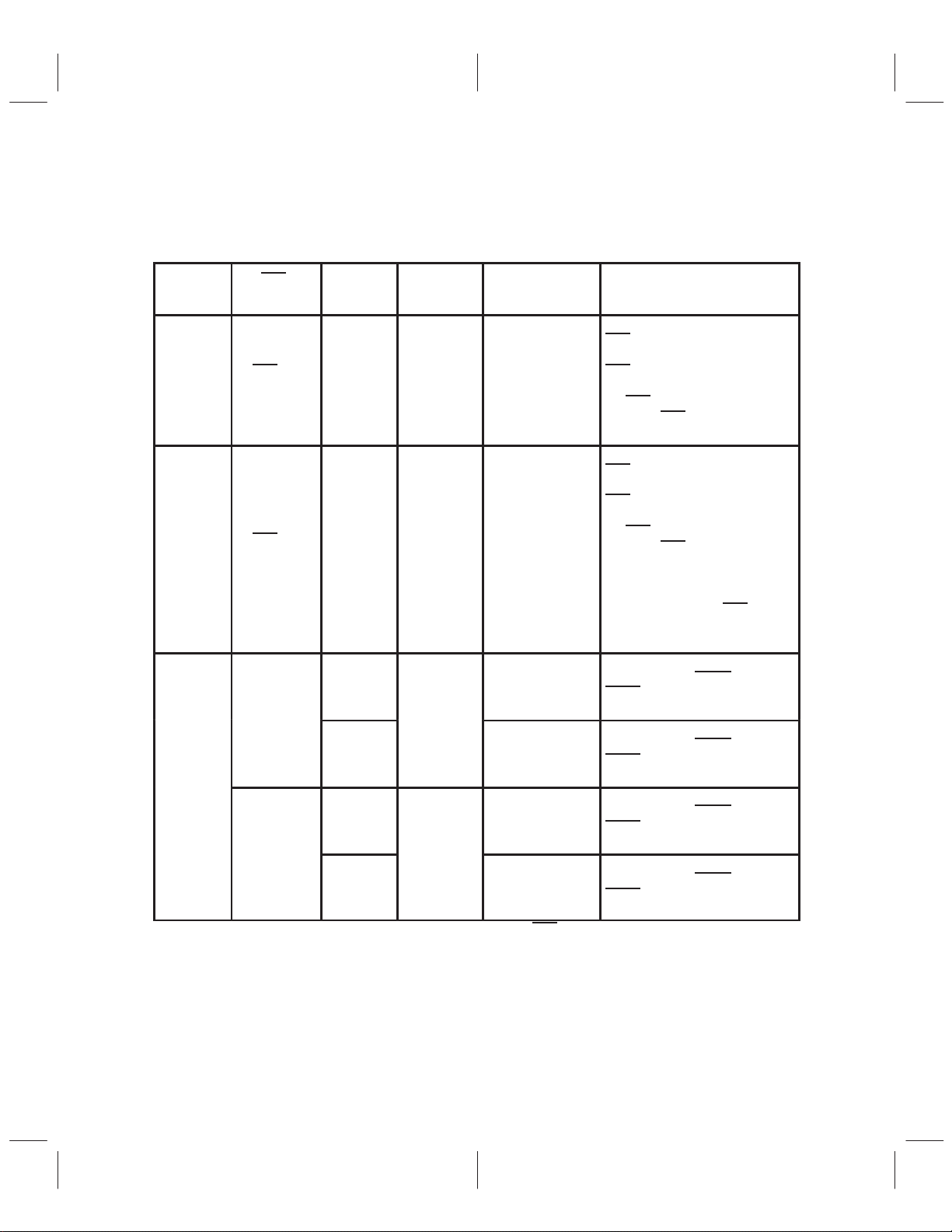

FUNCTION TABLE

DATA

FORMAT

16-bit format Dual-word

16-bit format Word mode Word mode DATA-DR/CONTROL = V

8-bit format

(2 bytes

required)

1–2

SYNCHRONOUS

(CONTROL

REGISTER

BIT D5 = 1)

(telephone

interface) mode

Byte mode Byte mode DATA-DR/CONTROL = V

ASYNCHRONOUS

(CONTROL

REGISTER

BIT D5 = 0)

Dual-word

(telephone

interface) mode

FORCING CONDITION

DATA-DR/CONTROL = 0 to 5 V

FSD

/WORD-BYTE = 0 to 5 V

FSD

/WORD-BYTE = V

FSD

/WORD-BYTE = V

CC–

(5 V nom)

CC+

CC–

(–5 V nom)

CC–

(–5 Vnom)

(–5 Vnom)

DIRECT

INTERFACE

TMS32020,

TMS320C25,

TMS320C30

TMS32020,

TMS320C25,

TMS320C30,

indirect

interface to

TMS320C10

(see Figure 7)

TMS320C17

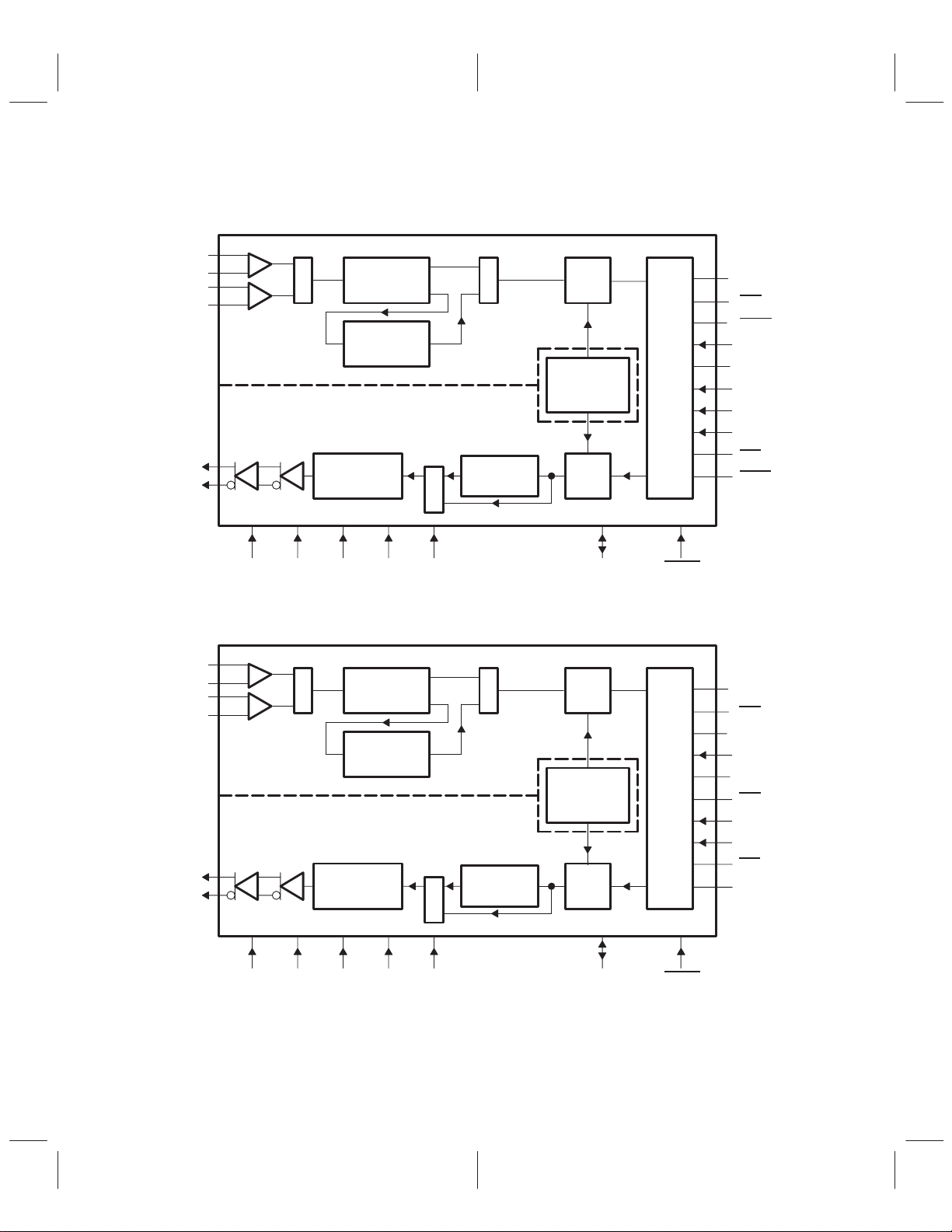

1.2 Functional Block Diagrams

WORD OR BYTE MODE

26

IN +

IN –

AUX IN +

AUX IN –

OUT +

OUT –

25

24

23

Receive Section

Transmit Section

22

21

M

U

X

Low-Pass

High-Pass

Low-Pass

Filter

Filter

Filter

M

U

A/D

X

Serial

Port

Internal

Voltage

Reference

M

U

(sin x)/x

Correction

D/A

5

DR

4

FSR

3

EODR

6

MSTR CLK

10

SHIFT CLK

1

WORDBYTE

13

CONTROL

12

DX

14

FSX

11

EODX

X

IN +

IN –

AUX IN +

AUX IN –

OUT +

OUT –

20 19 17, 18 9 7 8 2

ANLGVCC–VCC+

GND

DGTL

GND

V

DD

(Digital)

DUAL-WORD (TELEPHONE INTERFACE) MODE

26

25

24

23

Receive Section

M

U

Low-Pass

Filter

High-Pass

Filter

Transmit Section

22

21

Low-Pass

Filter

M

U

X

20 19 17, 18 9 7 8 2

ANLGVCC–VCC+

GND

DGTL

GND

V

DD

(Digital)

M

U

XX

(sin x)/x

Correction

A/D

Internal

Voltage

Reference

D/A

RESETREF

Serial

Port

RESETREF

5

DR

4

FSR

3

D11 OUT

6

MSTR CLK

10

SHIFT CLK

1

FSD

13

DATA-DR

12

DX

14

FSX

11

D10 OUT

1–3

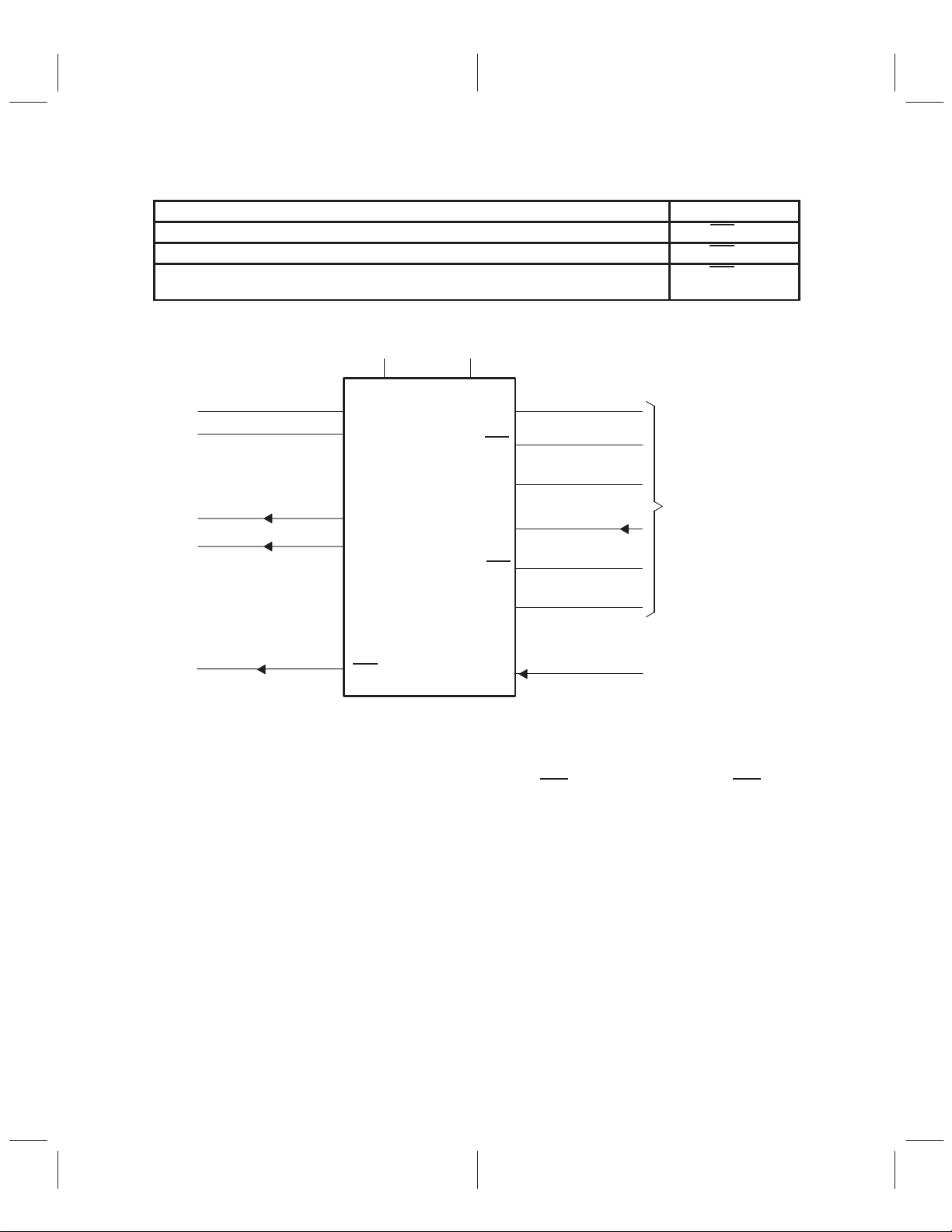

FRAME SYNCHRONIZATION FUNCTIONS

TLC32047 Function

Receiving serial data on DX from processor to internal DAC FSX low

Transmitting serial data on DR from internal ADC to processor , primary communications FSR low

Transmitting serial data on DR from DATA-DR to processor, secondary communications in

dual-word (telephone interface) mode only

–5 V5 V

20 19

Serial Data Out

DR

FSR

5

4

Analog In

26

25

IN+

IN–

V

CC+

TLC32047

V

CC–

Frame Sync Output

FSD low

Analog Out

22

21

1

OUT+

OUT–

FSD

D11OUT

DX

FSX

D10OUT

DATA-DR

3

12

Serial Data In

14

11

Secondary Communication (see Table above)

Serial Data Input

13

16-Bit Format TTL

or CMOS Logic Levels

TMS32020,

TMS320C25,

TMS320C30,

or Equivalent

16-Bit DSP

TTL or CMOS

Logic Levels

Figure 1–1. Dual-Word (Telephone Interface) Mode

When the DATA-DR/CONTROL input is tied to a logic signal source varying between 0 and 5 V, the

TLC32047 is in the dual-word (telephone interface) mode. This logic signal is routed to the DR line for input

to the DSP only when terminal 1, data frame synchronization (FSD

), outputs a low level. The FSD pulse

duration is 16 shift clock pulses. Also, in this mode, the control register data bits D10 and D11 appear on

D10OUT and D1 1OUT, respectively, as outputs.

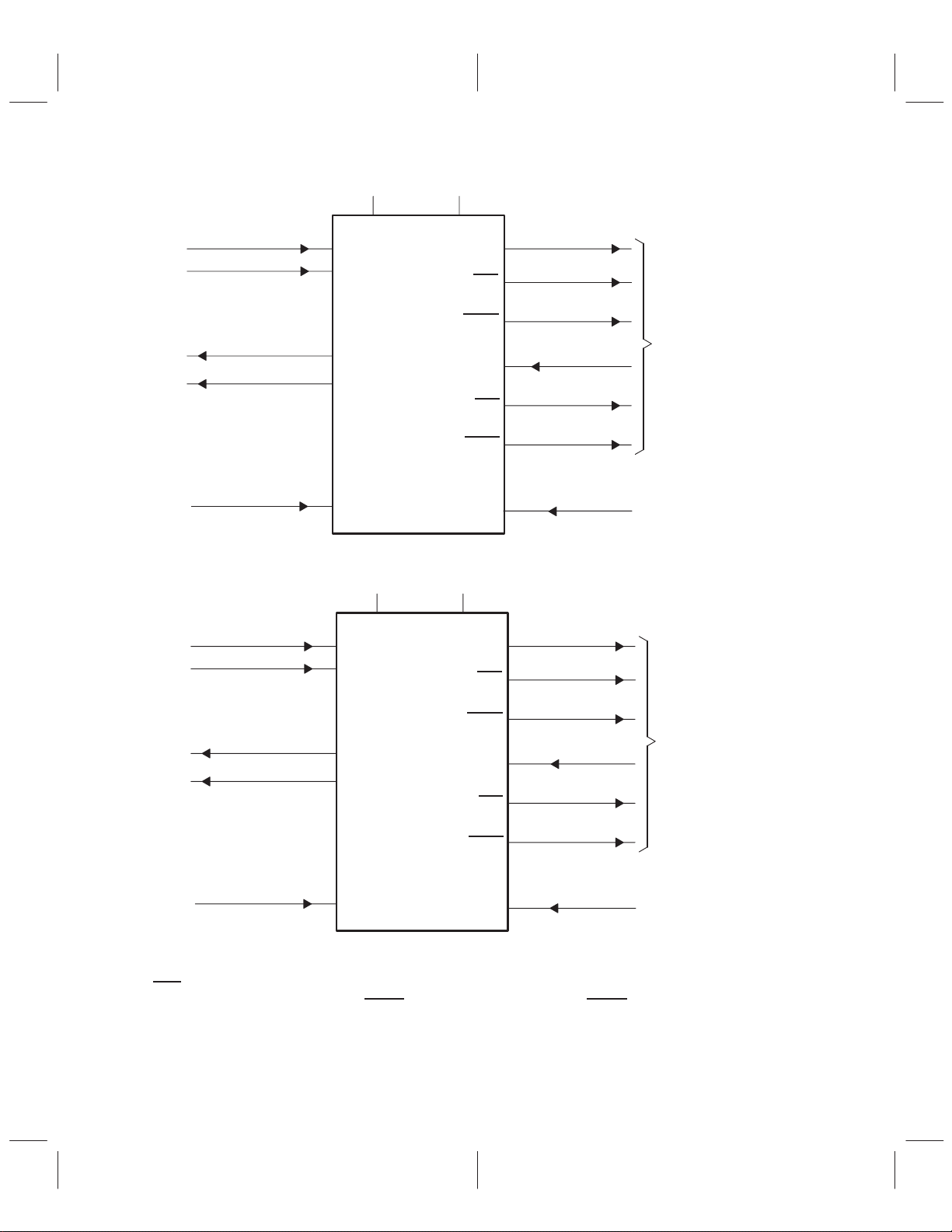

1–4

Analog In

20 19

26

IN+

25

IN–

V

CC+

TLC32047

–5 V5 V

V

CC–

DR

FSR

Serial Data Out

5

4

Analog Out

(5 V nom)

Analog In

Analog Out

V

CC+

22

OUT+

21

OUT–

1

WORD-BYTE

26

IN+

25

IN–

22

OUT+

21

OUT–

CONTROL

Figure 1–2. Word Mode

–5 V5 V

20 19

V

CC+

TLC32047

V

CC–

EODR

DX

FSX

EODX

DR

FSR

EODR

DX

FSX

3

Serial Data In

12

14

11

13

Serial Data Out

5

4

3

Serial Data In

12

14

TMS32020,

TMS320C25,

TMS320C30,

or Equivalent

16-Bit DSP

TTL or CMOS

Logic Levels

V

CC–

(–5 V nom)

TMS320C17

or Equivalent

8-Bit Serial

Interface

(2 Bytes Required)

TTL or CMOS

Logic Levels

11

13

V

CC–

(–5 V nom)

V

CC–

(–5 V nom)

1

WORD-BYTE

EODX

CONTROL

Figure 1–3. Byte Mode

The word or byte mode is selected by first connecting the DATA-DR/CONTROL input to V

FSD

/WORD-BYTE becomes an input and can then be used to select either word or byte transmission

formats. The end-of-data transmit (EODX

) and the end-of-data receive (EODR) signals on terminals 1 1 and

CC–.

3, respectively, are used to signal the end of word or byte communication (see the Terminal Functions

section).

1–5

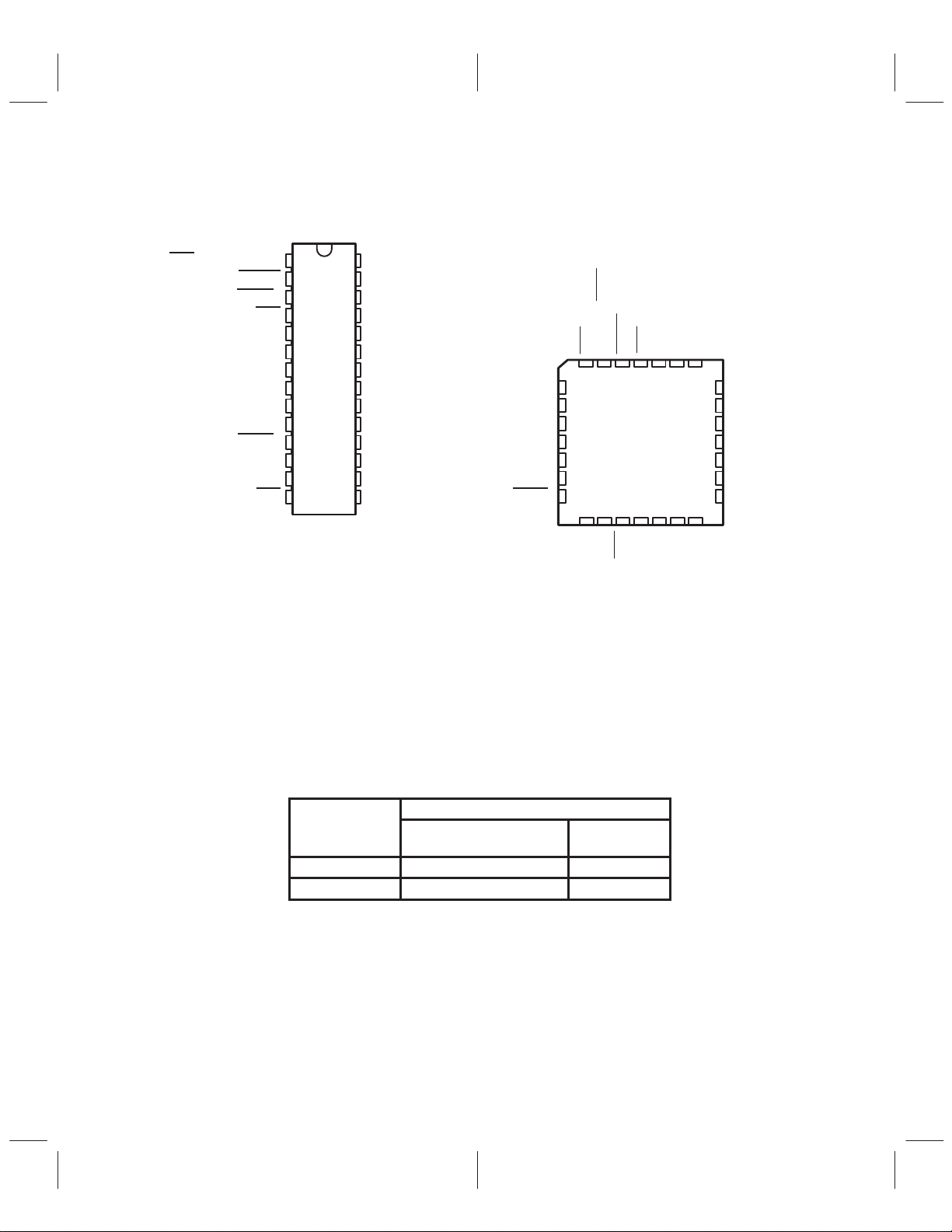

1.3 Terminal Assignments

†

28

27

26

25

24

23

22

21

20

19

18

17

16

15

NU

NU

IN+

IN–

AUX IN+

AUX IN–

OUT+

OUT–

V

V

ANLG GND

ANLG GND

NU

NU

/WORD-BYTE

FSD

RESET

D11OUT/EODR

FSR

MSTR CLK

V

REF

DGTL GND

SHIFT CLK

D10OUT/EODX

DATA-DR/CONTROL

FSX

N PACKAGE

(TOP VIEW)

‡

1

2

‡

3

4

DR

5

6

7

DD

8

9

10

‡

11

DX

12

‡

13

14

CC+

CC–

DR

MSTR CLK

V

DD

REF

DGTL GND

SHIFT CLK

D10OUT/EODX

FN PACKAGE

(TOP VIEW)

‡

‡

FSD/WORD-BYTE

NUNUIN+

RESET

FSR

D11OUT/EODR

321

4

5

6

7

8

9

10

‡

11

12 13

‡

DX

28 27

26

14 15 16 1718

NU

NU

FSX

ANLG GND

25

IN–

24

AUX IN+

23

AUX IN–

22

OUT+

21

OUT–

20

V

CC+

19

V

CC–

ANLG GND

DATA-DR/CONTROL

NU - Nonusable; no external connection should be made to these pins.

†

600-mil wide

‡

The portion of the terminal name to the left of the slash is used for the dual-word (telephone interface) mode.

The portion of the terminal name to the right of the slash is used for word-byte mode.

1.4 Ordering Information

AVAILABLE OPTIONS

PACKAGED DEVICES

1–6

T

A

0°C to 70°C TLC32047CFN TLC32047CN

–40°C to 85°C TLC32047IFN TLC32047IN

PLASTIC CHIP CARRIER

(FN)

PLASTIC DIP

(N)

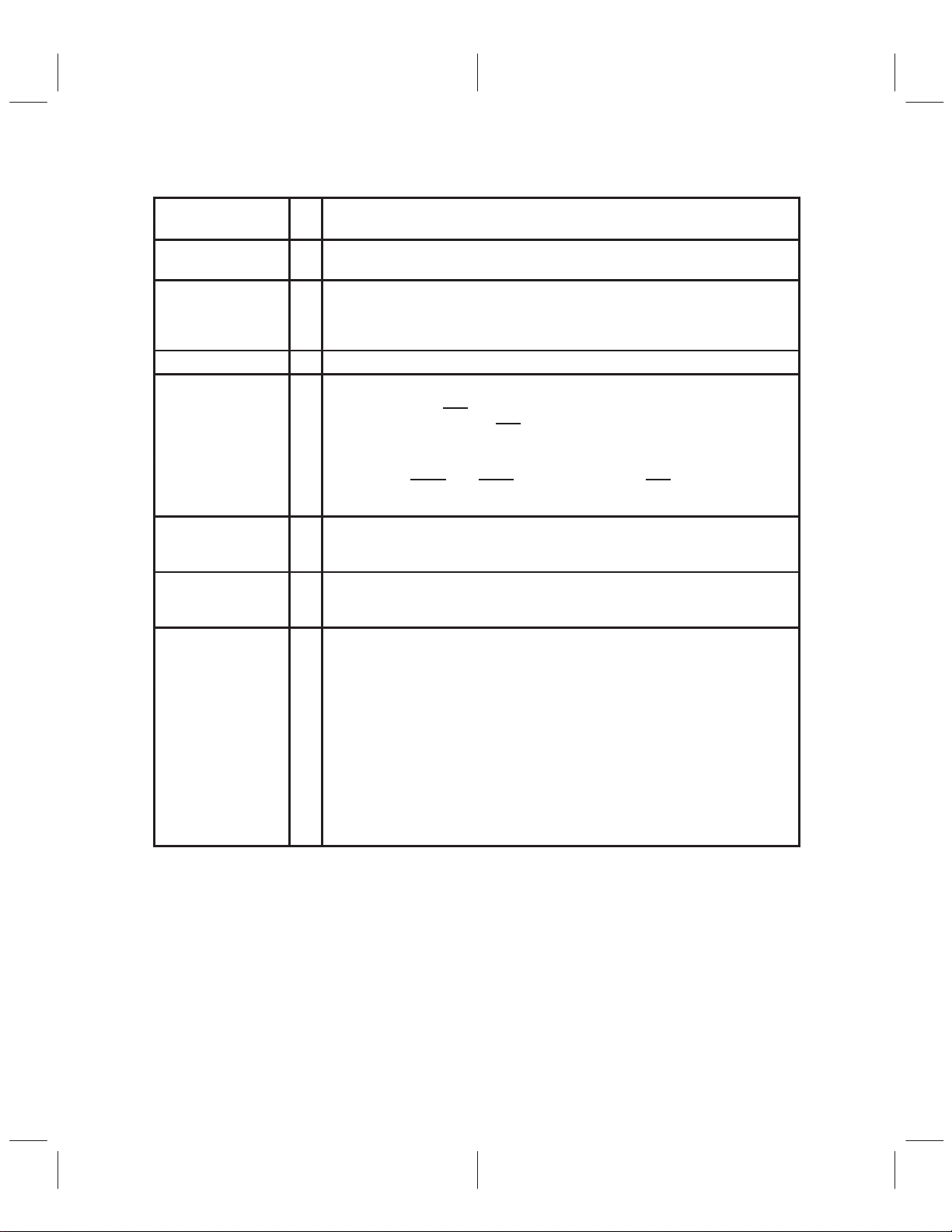

1.5 Terminal Functions

I/O

DESCRIPTION

TERMINAL

NAME NO.

ANLG GND 17,18 Analog ground return for all internal analog circuits. ANLG GND is internally connected

AUX IN+ 24 I Noninverting auxiliary analog input stage. AUX IN+ can be switched into the band-pass

AUX IN– 23 I Inverting auxiliary analog input (see the above AUX IN+ description).

DATA-DR 13 I The dual-word (telephone interface) mode, selected by applying an input logic level

CONTROL When CONTROL is tied to V

DR 5 O DR is used to transmit the ADC output bits from the AIC to the TMS320 serial port. This

DX 12 I DX is used to receive the DAC input bits and timing and control information from the

D10OUT 11 O In the dual-word (telephone interface) mode, bit D10 of the control register is output to

EODX End of data transmit. During the word-mode timing, a low-going pulse occurs on EODX

to DGTL GND.

filter and ADC path via software control. If the appropriate bit in the control register is

a 1, the auxiliary inputs replace the IN+ and IN– inputs. If the bit is a 0, the IN+ and IN–

inputs are used (see the DX Serial Data Word Format).

between 0 and 5 V to DA T A-DR, allows DATA-DR to function as a data input. The data

is then framed by the FSD

communication. The functions FSD

selection (see Table 2–1).

WORD-BYTE, EODR

used to select either the word or byte mode (see Function Table).

transmission of bits from the AIC to the TMS320 serial port is synchronized with the

SHIFT CLK signal.

TMS320. This serial transmission from the TMS320 serial port is synchronized with the

SHIFT CLK signal.

D10OUT . When the device is reset, bit D10 is initialized to 0 (see DX Serial Data W ord

Format). The output update is immediate upon changing bit D10.

immediately after the 16 bits of DAC and control or register information have been

transmitted from the TMS320 serial port to the AIC. EODX can be used to interrupt a

microprocessor upon completion of serial communications. Also, EODX can be used

to strobe and enable external serial-to-parallel shift registers, latches, or external FIFO

RAM and to facilitate parallel data bus communications between the DSP and the

serial-to-parallel shift registers. During the byte-mode timing, EODX goes low after the

first byte has been transmitted from the TMS320 serial port to the AIC and is kept low

until the second byte has been transmitted. The TMS320C17 can use this low-going

signal to differentiate first and second bytes.

signal and transmitted as an output to DR during secondary

, and EODX are valid in this mode. FSD/WORD-BYTE is then

, D11OUT, and D10OUT are valid with this mode

, the device is in the word or byte mode. The functions

CC–

1–7

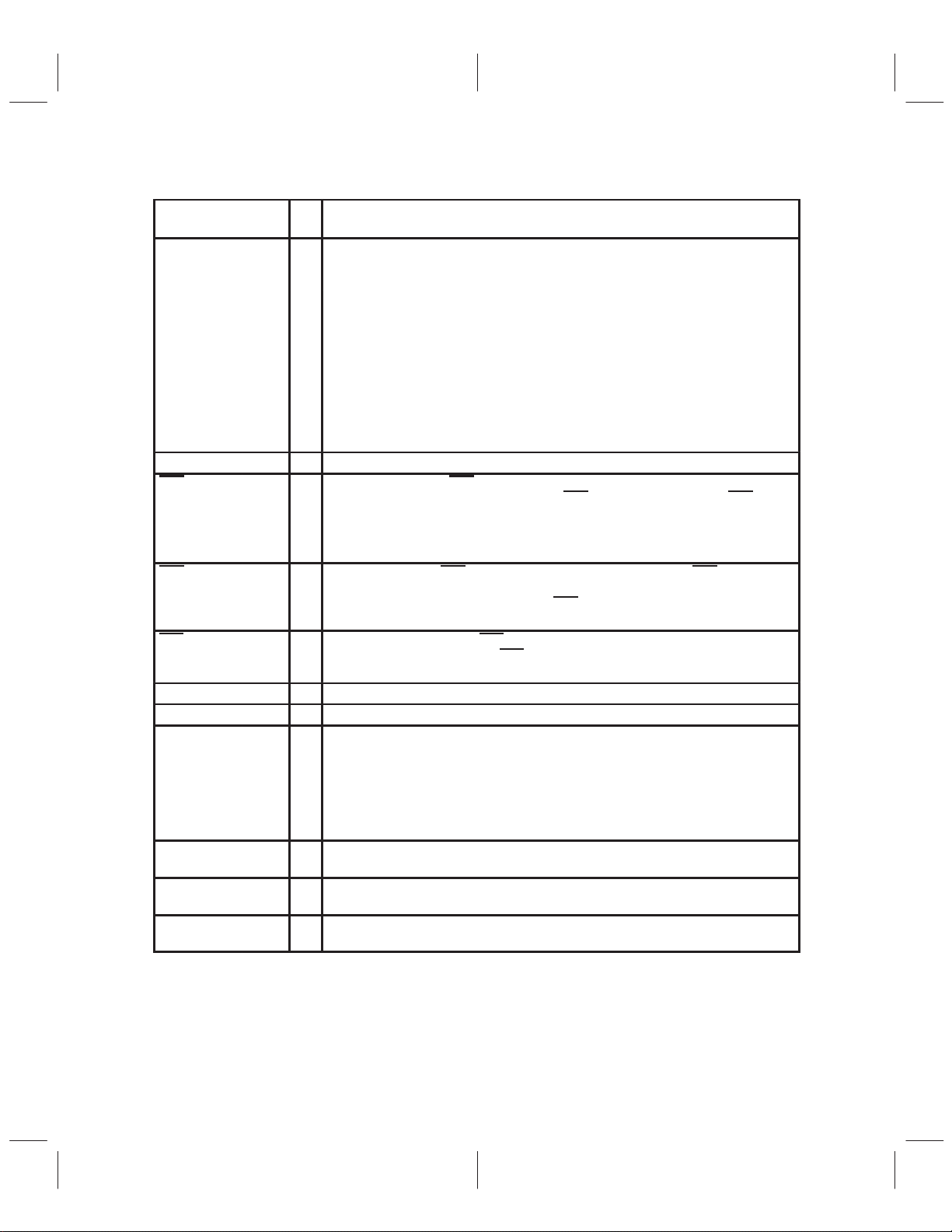

1.5 Terminal Functions (continued)

I/O

DESCRIPTION

TERMINAL

NAME NO.

D11OUT 3 O In the dual-word (telephone interface) mode, bit D11 of the control register is output to

EODR End of data receive. During the word-mode timing, a low-going pulse occurs on EODR

DGTL GND 9 Digital ground for all internal logic circuits. Not internally connected to ANLG GND.

FSD 1 O Frame sync data. The FSD output remains high during primary communication. In the

WORD-BYTE I WORD-BYTE allows differentiation between the word and byte data format (see

FSR 4 O Frame sync receive. FSR is held low during bit transmission. When FSR goes low, the

FSX 14 O Frame sync transmit. When FSX goes low, the TMS320 serial port begins transmitting

IN+ 26 I Noninverting input to analog input amplifier stage

IN– 25 I Inverting input to analog input amplifier stage

MSTR CLK 6 I Master clock. MSTR CLK is used to derive all the key logic signals of the AIC, such as

OUT+ 22 O Noninverting output of analog output power amplifier. OUT+ drives transformer hybrids

OUT– 21 O Inverting output of analog output power amplifier. OUT– is functionally identical with and

REF 8 I/O Internal voltage reference is brought out on REF . An external voltage reference can be

D11OUT. When the device is reset, bit D11 is initialized to 0 (see DX Serial Data W ord

Format). The output update is immediate upon changing bit D1 1.

immediately after the 16 bits of A/D information have been transmitted from the AIC to

the TMS320 serial port. EODR can be used to interrupt a microprocessor upon

completion of serial communications. Also, EODR can be used to strobe and enable

external serial-to-parallel shift registers, latches, or external FIFO RAM, and to facilitate

parallel data bus communications between the DSP and the serial-to-parallel shift

registers. During the byte-mode timing, EODR goes low after the first byte has been

transmitted from the AIC to the TMS320 serial port and is kept low until the second byte

has been transmitted. The TMS320C17 can use this low-going signal to differentiate

between first and second bytes.

dual-word (telephone interface) mode, the FSD

during secondary communication.

DATA-DR/CONTROL and Table 2-1 for details).

TMS320 serial port begins receiving bits from the AIC via DR of the AIC. The most

significant DR bit is present on DR before FSR

Internal Timing Configuration Diagrams).

bits to the AIC via DX of the AIC. FSX

Sections and Internal Timing Configuration Diagrams).

the shift clock, the switched-capacitor filter clocks, and the A/D and D/A timing signals.

The internal timing configuration diagram shows how these key signals are derived. The

frequencies of these signals are synchronous submultiples of the master clock

frequency to eliminate unwanted aliasing when the sampled analog signals are

transferred between the switched-capacitor filters and the ADC and DAC converters

(see the Internal Timing Configuration).

or high-impedance loads directly in a differential or a single-ended configuration.

complementary to OUT+.

applied to REF to override the internal voltage reference.

is held low during bit transmission (see Serial Port

output is identical to the FSX output

goes low (see Serial Port Sections and

1–8

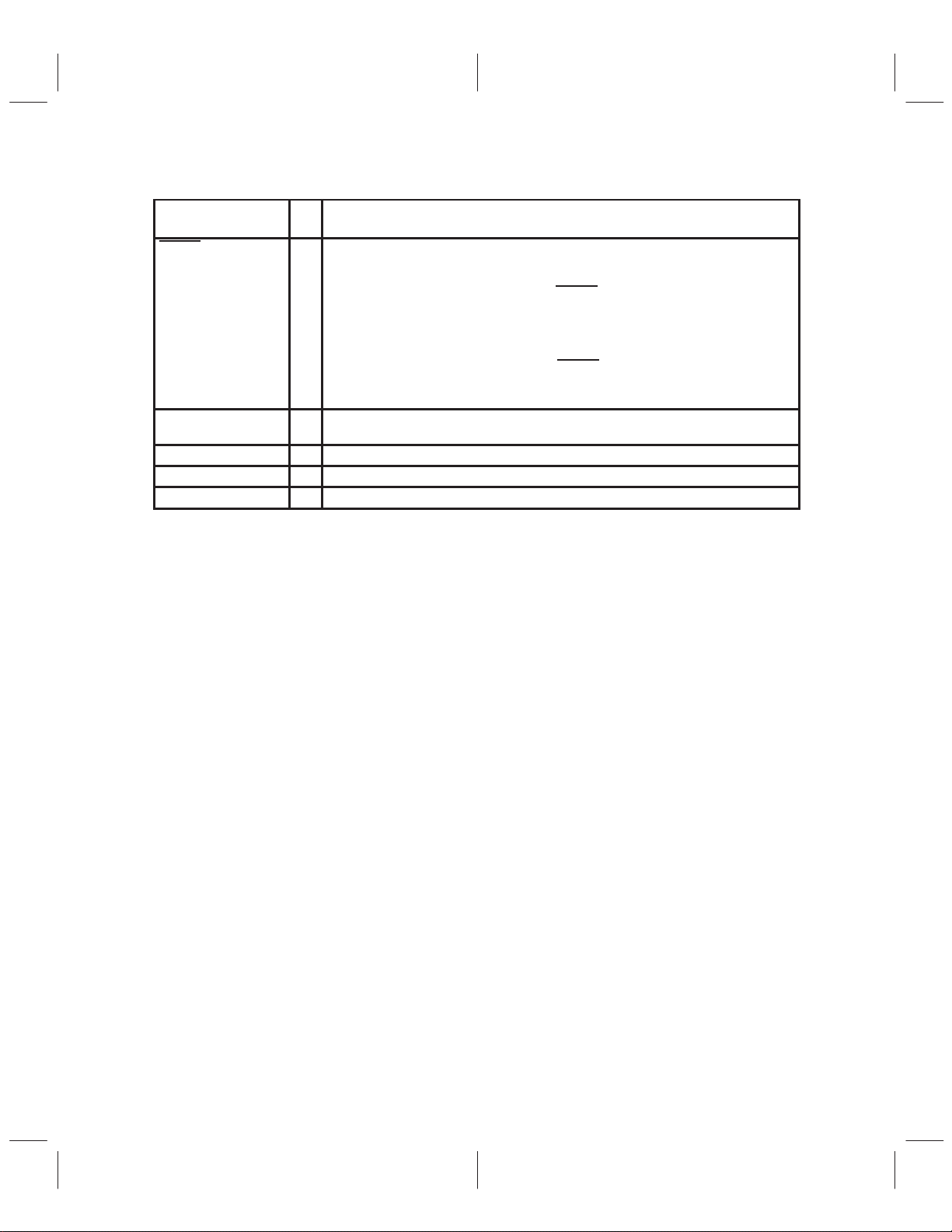

1.5 Terminal Functions (continued)

I/O

DESCRIPTION

TERMINAL

NAME NO.

RESET 2 I Reset. A reset function is provided to initialize T A, TA ’, TB, RA, RA ’, RB (see Figure 2-1),

SHIFT CLK 10 O Shift clock. SHIFT CLK is obtained by dividing the master clock signal frequency by four .

V

V

V

DD

CC+

CC–

7 Digital supply voltage, 5 V ±5%

20 Positive analog supply voltage, 5 V ±5%

19 Negative analog supply voltage, –5 V ±5%

and the control registers. This reset function initiates serial communications between

the AIC and DSP. The reset function initializes all AIC registers, including the control

register. After a negative-going pulse on RESET

provide a 16-kHz data conversion rate for a 10.368-MHz master clock input signal. The

conversion rate adjust registers, TA ’ and RA ’, are reset to 1. The CONTROL register bits

are reset as follows (see AIC DX Data Word Format section):

D11 = 0, D10 = 0, D9 = 1, D7 = 1, D6 = 1, D5 = 1, D4 = 0, D3 = 0, D2 = 1

The shift clock (SCLK) is held high during RESET

This initialization allows normal serial-port communication to occur between the AIC

and the DSP.

SHIFT CLK is used to clock the serial data transfers of the AIC.

, the AIC registers are initialized to

.

1–9

1–10

2 Detailed Description

V

WORD

V

V

BYTE

Table 2–1. Mode-Selection Function Table

DATA-DR/

CONTROL

Data in

(0 to 5 V)

Data in

(0 to 5 V)

CC–

†

DATA-DR/CONTROL has an internal pulldown resistor to –5 V, and FSD/WORD-BYTE has an internal pullup resistor

to 5 V.

FSD/

WORD-BYTE

FSD out

(0 to 5 V)

FSD out

(0 to 5 V)

CC+

CC–

CONTROL

REGISTER

BIT (D5)

1

0

1

0

1

0

OPERATING

MODE

Dual-Word

(Telephone

Interface)

Dual-Word

(Telephone

Interface)

SERIAL

CONFIGURATION

Synchronous,

One 16-Bit Word

Asynchronous,

One 16-bit Word

Synchronous,

One 16-Bit Word

Asynchronous,

One 16-bit Word

Synchronous,

Two 8-Bit Bytes

Asynchronous,

Two 8-Bit Bytes

DESCRIPTION

Terminal functions DATA-DR†,

†

FSD

, D11OUT, and D10OUT are

applicable in this configuration.

FSD

is asserted during

secondary communication, but

the FSR

is not asserted.

However, FSD

during primary communication.

Terminal functions DATA-DR†,

†

FSD

, D11OUT, and D10OUT are

applicable in this configuration.

FSD

is asserted during

secondary communication, but

the FSR

However, FSD

during primary communication. If

secondary communications occur

while the A/D conversion is being

transmitted from DR, FSD

go low, and data from DATA-DR

cannot go onto DR.

Terminal functions CONTROL†,

WORD-BYTE†, EODR

EODX

configuration.

Terminal functions CONTROL†,

WORD-BYTE†, EODR

EODX

configuration.

Terminal functions CONTROL†,

WORD-BYTE†, EODR

EODX

configuration.

Terminal functions CONTROL†,

WORD-BYTE†, EODR

EODX

configuration.

remains high

is not asserted.

remains high

cannot

, and

are applicable in this

, and

are applicable in this

, and

are applicable in this

, and

are applicable in this

2–1

Loading...

Loading...