Texas Instruments THS5641AIPWR, THS5641AIPW, THS5641AIDWR, THS5641AIDW Datasheet

THS5641A

8-BIT, 100 MSPS, CommsDAC

DIGITAL-TO-ANALOG CONVERTER

SLAS277 –MARCH 2000

1

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

D

Member of the Pin-Compatible

CommsDAC Product Family

D

100 MSPS Update Rate

D

8-Bit Resolution

D

Signal-to-Noise and Distortion Ratio

(SINAD) at 5 MHz: 50 dB

D

Integral Nonlinearity INL: 0.25 LSB

D

Differential Nonlinearity DNL: 0.25 LSB

D

1 ns Setup/Hold Time

D

Glitch Energy: 5 pV-s

D

Settling Time to 0.1%: 35 ns

D

Differential Scalable Current Outputs: 2 mA

to 20 mA

D

On-Chip 1.2-V Reference

D

3-V and 5-V Single Supply Operation

D

Straight Binary or Twos Complement Input

D

Power Dissipation: 100 mW at 3.3 V, Sleep

Mode: 17 mW at 3.3 V

D

Package: 28-Pin SOIC and TSSOP

description

The THS5641A is an 8-bit resolution digital-to-analog converter (DAC) optimized for video applications and

digital data transmission in wired and wireless communication systems. The 8-bit DAC is a member of the

CommsDAC series of high-speed, low-power CMOS digital-to-analog converters. The CommsDAC family

consists of pin compatible 14-, 12-, 10-, and 8-bit DACs. All devices offer identical interface options, small outline

package and pinout. The THS5641A offers superior ac and dc performance while supporting update rates up

to 100 MSPS.

The THS5641A operates from an analog and digital supply of 3 V to 5.5 V. Its inherent low power dissipation

of 100 mW ensures that the device is well suited for portable and low power applications. Lowering the full-scale

current output reduces the power dissipation without significantly degrading performance. The device features

a SLEEP mode, which reduces the standby power to approximately 17 mW, thereby optimizing the power

consumption for system needs.

The THS5641A is manufactured in Texas Instruments advanced high-speed mixed-signal CMOS process. A

current-source-array architecture combined with simultaneous switching shows excellent dynamic

performance. On-chip edge-triggered input latches and a 1.2 V temperature compensated bandgap reference

provide a complete monolithic DAC solution. The digital supply range of 3 V to 5.5 V supports 3 V and 5 V CMOS

logic families. Minimum data input setup and hold times allow for easy interfacing with external logic. The

THS5641A supports both a straight binary and twos complement input word format, enabling flexible interfacing

with digital signal processors.

Copyright 2000, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

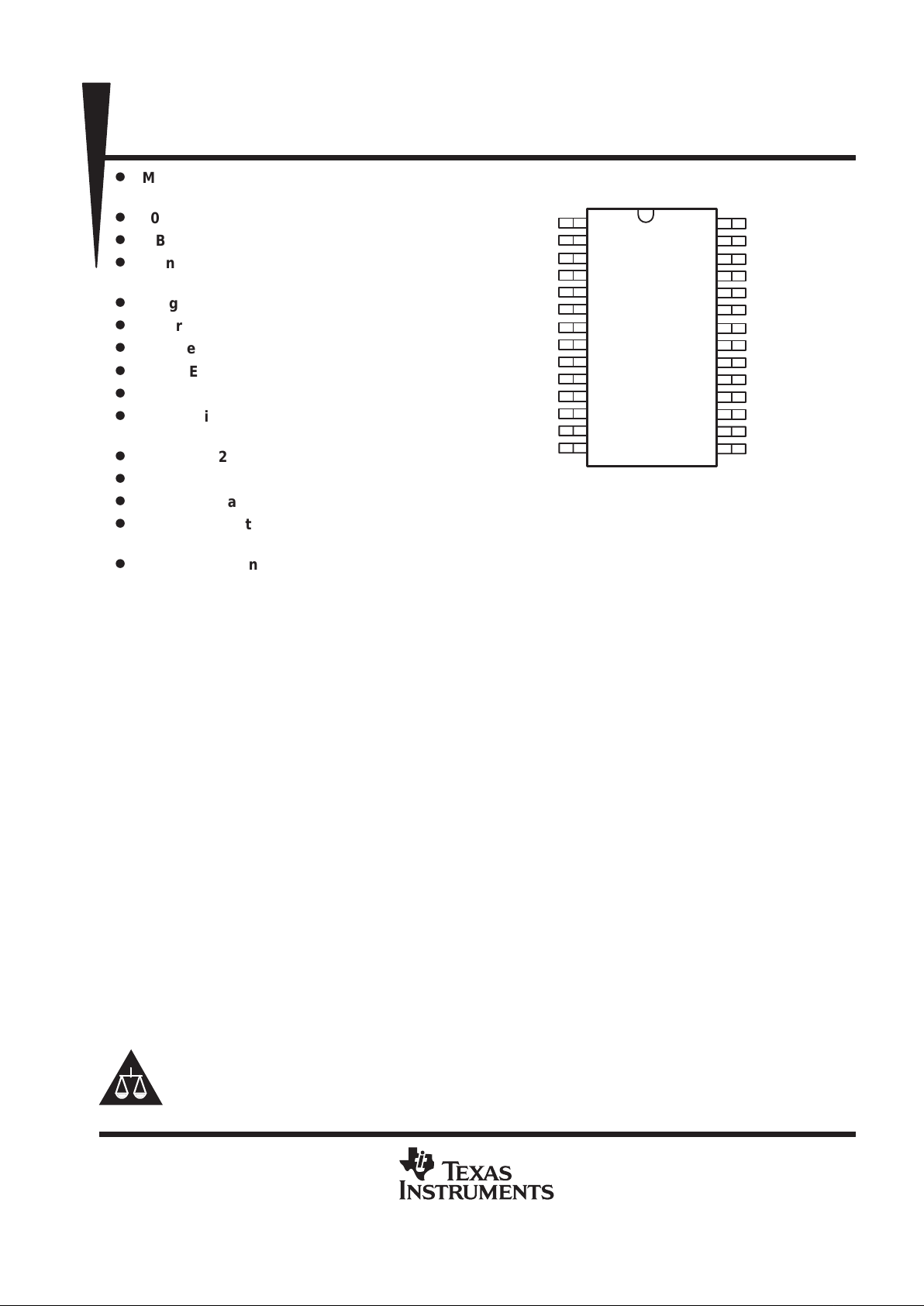

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

D7

D6

D5

D4

D3

D2

D1

D0

NC

NC

NC

NC

NC

NC

CLK

DV

DD

DGND

MODE

AV

DD

COMP2

IOUT1

IOUT2

AGND

COMP1

BIASJ

EXTIO

EXTLO

SLEEP

SOIC (DW) OR TSSOP (PW) PACKAGE

(TOP VIEW)

NC – No internal connection

CommsDAC is a trademark of Texas Instruments.

THS5641A

8-BIT, 100 MSPS, CommsDAC

DIGITAL-TO-ANALOG CONVERTER

SLAS277 –MARCH 2000

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

description (continued)

The THS5641A provides a nominal full-scale differential output current of 20 mA and >300 kΩ output

impedance, supporting both single-ended and differential applications. The output current can be directly fed

to the load (e.g., external resistor load or transformer), with no additional external output buffer required. An

accurate on-chip reference and control amplifier allows the user to adjust this output current from 20 mA down

to 2 mA, with no significant degradation of performance. This reduces power consumption and provides 20 dB

gain range control capabilities. Alternatively , an external reference voltage and control amplifier may be applied

in applications using a multiplying DAC.

The THS5641A is available in both a 28-pin SOIC and TSSOP package. The device is characterized for

operation over the industrial temperature range of –40°C to 85°C.

AVAILABLE OPTIONS

PACKAGE

T

A

28-TSSOP

(PW)

28-SOIC

(DW)

–40°C to 85°C THS5641AIPW THS5641AIDW

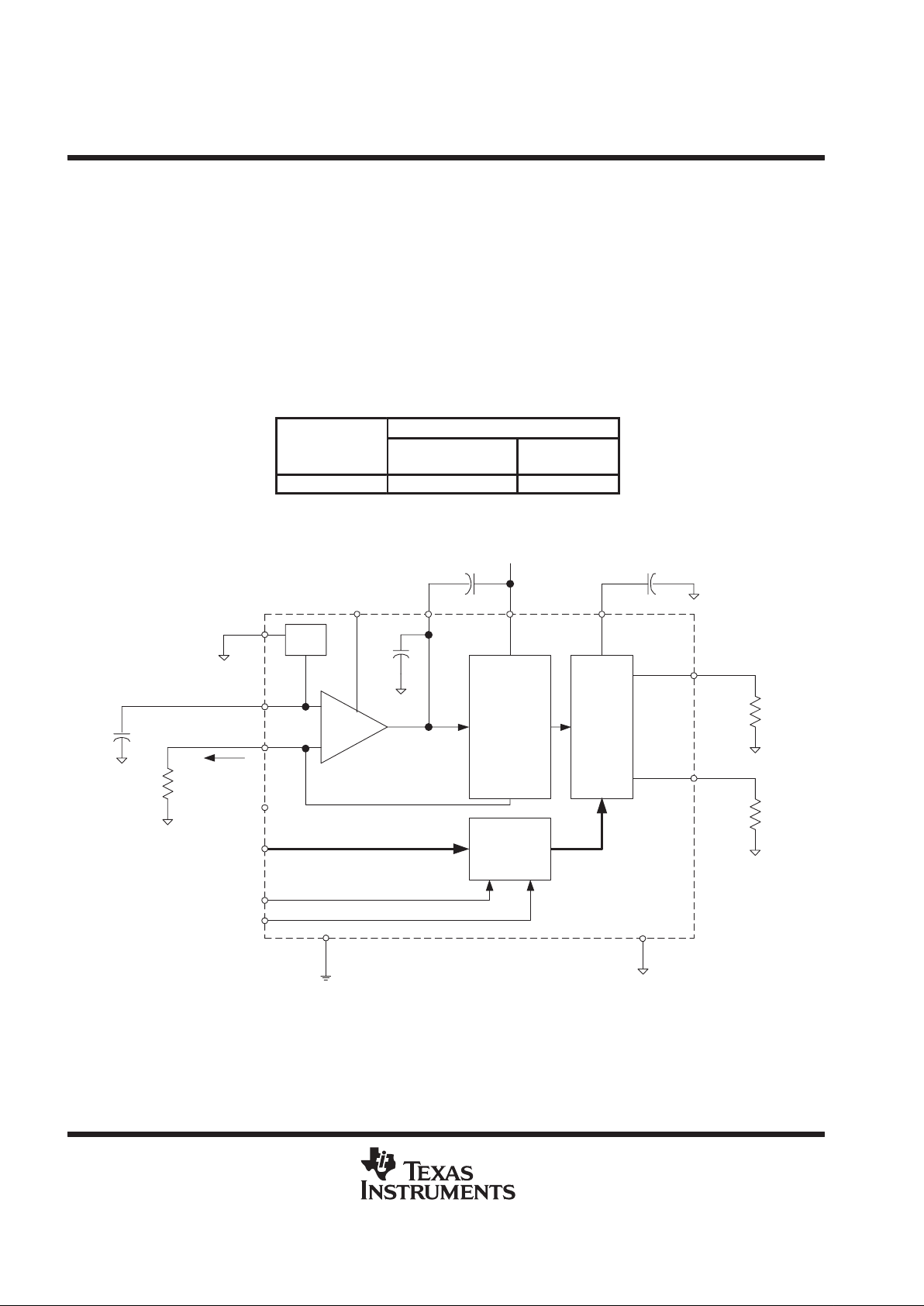

functional block diagram

IOUT1

IOUT2

CLK

D[7:0]

EXTLO

DGND

AV

DD

EXTIO

COMP2

Current

Source

Array

Output

Current

Switches

AGND

1.2 V

REF

BIASJ

–

+

Control

AMP

0.1 µF

2 kΩ

I

BIAS

COMP1

Logic

Control

50 Ω

1 nF

DV

DD

R

BIAS

SLEEP

MODE

R

LOAD

R

LOAD

C

EXT

C

1

0.1 µF 0.1 µF

50 Ω

THS5641A

8-BIT, 100 MSPS, CommsDAC

DIGITAL-TO-ANALOG CONVERTER

SLAS277 –MARCH 2000

3

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

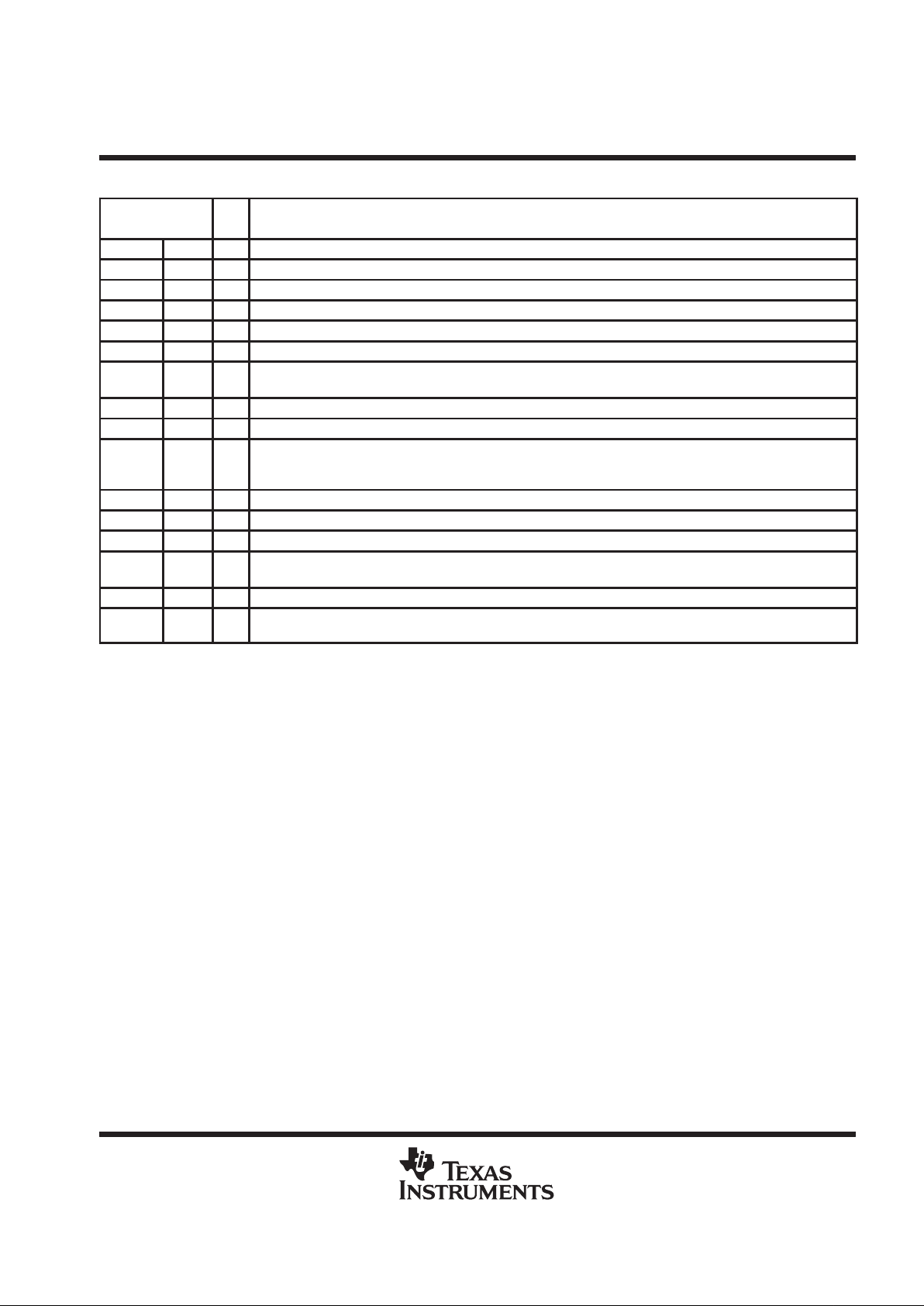

Terminal Functions

TERMINAL

NAME NO.

I/O

DESCRIPTION

AGND 20 I Analog ground return for the internal analog circuitry

AV

DD

24 I Positive analog supply voltage (3 V to 5.5 V)

BIASJ 18 O Full-scale output current bias

CLK 28 I External clock input. Input data latched on rising edge of the clock.

COMP1 19 I Compensation and decoupling node, requires a 0.1 µF capacitor to AVDD.

COMP2 23 I Internal bias node, requires a 0.1 µF decoupling capacitor to AGND.

D[7:0] [1:8] I Data bits 0 through 7.

D7 is most significant data bit (MSB), D0 is least significant data bit (LSB).

DGND 26 I Digital ground return for the internal digital logic circuitry

DV

DD

27 I Positive digital supply voltage (3 V to 5.5 V)

EXTIO 17 I/O Used as external reference input when internal reference is disabled (i.e., EXTLO = AVDD). Used as internal

reference output when EXTLO = AGND, requires a 0.1 µF decoupling capacitor to AGND when used as reference

output

EXTLO 16 O Internal reference ground. Connect to A VDD to disable the internal reference source

IOUT1 22 O DAC current output. Full scale when all input bits are set 1

IOUT2 21 O Complementary DAC current output. Full scale when all input bits are 0

MODE 25 I Mode select. Internal pulldown. Mode 0 is selected if this pin is left floating or connected to DGND. See

timing diagram.

NC [9:14] N No connection

SLEEP 15 I Asynchronous hardware power down input. Active High. Internal pulldown. Requires 5 µs to power down but 3 ms

to power up.

absolute maximum ratings over operating free-air temperature (unless otherwise noted)

†

Supply voltage range, AVDD (see Note 1) –0.3 V to 6.5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

DVDD (see Note 2) –0.3 V to 6.5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Voltage between AGND and DGND –0.3 V to 0.5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Supply voltage range, AVDD to DVDD –6.5 V to 6.5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

CLK, SLEEP, MODE (see Note 2) –0.3 V to DVDD + 0.3 V. . . . . . . . . . . . . . . . . . . . . .

Digital input D7–D0 (see Note 2) –0.3 V to DV

DD

+ 0.3 V. . . . . . . . . . . . . . . . . . . . . .

IOUT1, IOUT2 (see Note 1) –1 V to AVDD + 0.3 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

COMP1, COMP2 (see Note 1) –0.3 V to AVDD + 0.3 V. . . . . . . . . . . . . . . . . . . . . . . . .

EXTIO, BIASJ (see Note 1) –0.3 V to AVDD + 0.3 V. . . . . . . . . . . . . . . . . . . . . . . . . . . .

EXTLO (see Note 1) –0.3 V to 0.3 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Peak input current (any input) 20 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Peak total input current (all inputs) –30 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating free-air temperature range, T

A

: THS5641AI –40°C to 85°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range –65°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Lead temperature 1,6 mm (1/16 inch) from the case for 10 seconds 260°C. . . . . . . . . . . . . . . . . . . . . . . . . . . .

†

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. Measured with respect to AGND.

2. Measured with respect to DGND.

THS5641A

8-BIT, 100 MSPS, CommsDAC

DIGITAL-TO-ANALOG CONVERTER

SLAS277 –MARCH 2000

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

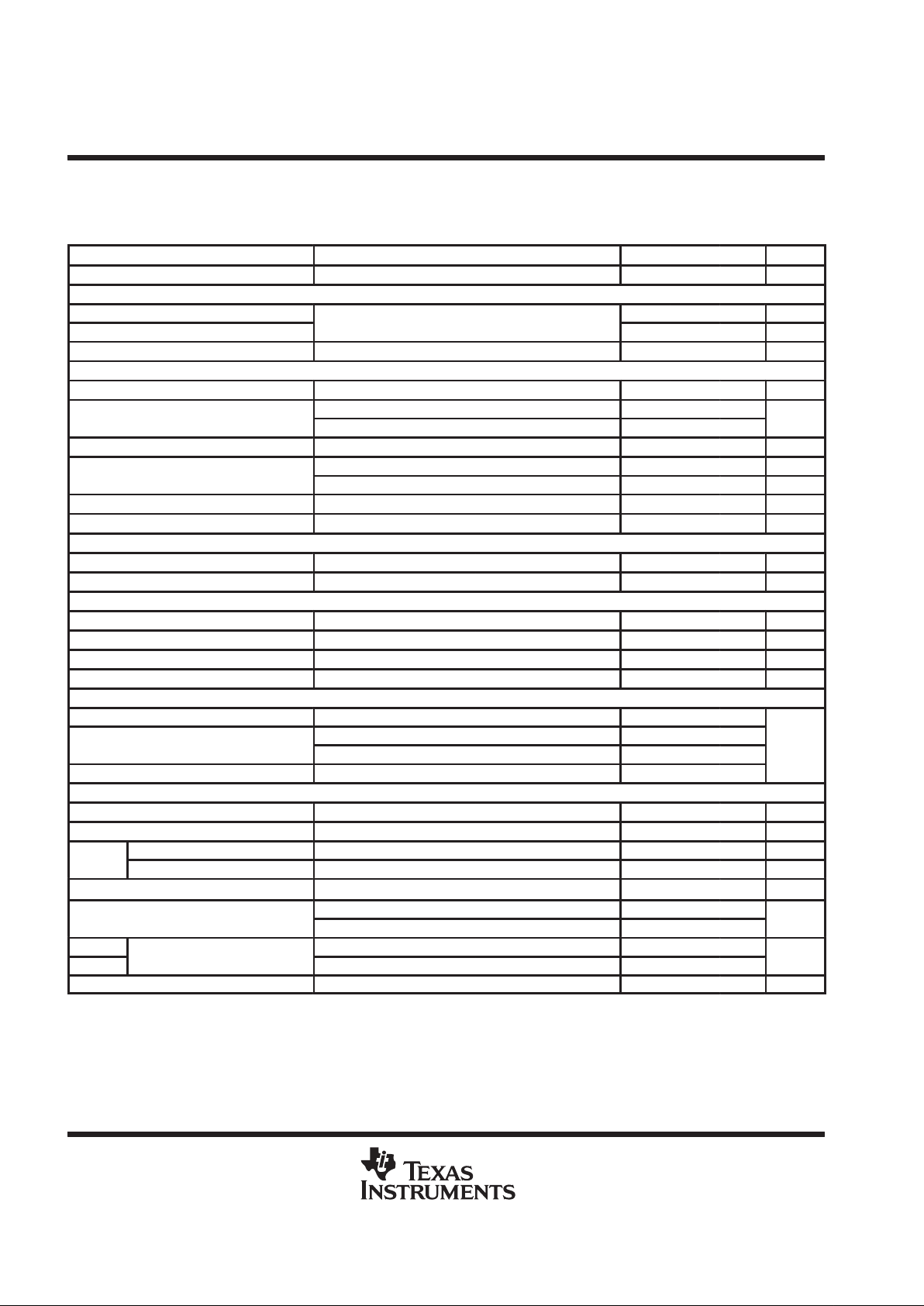

electrical characteristics over recommended operating free-air temperature range, AVDD = 5 V,

DV

DD

= 5 V, IOUTFS = 20 mA (unless otherwise noted)

dc specifications

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

Resolution 8 Bits

DC accuracy

†

INL Integral nonlinearity

°

°

–0.25 ±0.1 0.25 LSB

DNL Differential nonlinearity

T

A

= –

40°C to 85°C

–0.25 ±0.05 0.25 LSB

Monotonicity Monotonic

Analog output

Offset error 0.02 %FSR

Without internal reference 2.3

Gain error

With internal reference 1.3

%FSR

Full scale output current

‡

2 20 mA

p

p

AVDD = 5 V, IOUTFS = 20 mA –1 1.25 V

Output compliance range

AVDD = 3.3 V IOUTFS = 20 mA –1 0.6 V

Output resistance 300 kΩ

Output capacitance 5 pF

Reference output

Reference voltage 1.18 1.22 1.32 V

Reference output current

§

100 nA

Reference input

V

EXTIO

Input voltage range 0.1 1.25 V

Input resistance 1 MΩ

Small signal bandwidth

¶

Without C

COMP1

1.3 MHz

Input capacitance 100 pF

Temperature coefficients

Offset drift 0

Without internal reference ±40

ppm of

Gain drift

With internal reference ±120

FSR/°C

Reference voltage drift ±35

Power supply

AV

DD

Analog supply voltage 3 5.5 V

DV

DD

Digital supply voltage 3 5.5 V

Analog supply current 25 30 mA

I

AVDD

Sleep mode supply current Sleep mode 3 5 mA

I

DVDD

Digital supply current

#

5 6 mA

p

AVDD = 5 V, DVDD = 5 V IOUTFS = 20 mA 175

Power dissipation

||

AVDD = 3.3 V, DVDD = 3.3 V, IOUTFS = 20 mA 100

mW

AV

DD

pp

±0.4

DV

DD

Power supply rejection ratio

±0.025

%FSR/V

Operating range –40 85 °C

†

Measured at IOUT1 in virtual ground configuration.

‡

Nominal full-scale current IOUTFS equals 32X the IBIAS current.

§

Use an external buffer amplifier with high impedance input to drive any external load.

¶

Reference bandwidth is a function of external cap at COMP1 pin and signal level.

#

Measured at f

CLK

= 50 MSPS and f

OUT

= 1 MHz.

||

Measured for 50 Ω R

LOAD

at IOUT1 and IOUT2, f

CLK

= 50 MSPS and f

OUT

= 20 MHz.

Specifications subject to change

THS5641A

8-BIT, 100 MSPS, CommsDAC

DIGITAL-TO-ANALOG CONVERTER

SLAS277 –MARCH 2000

5

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

electrical characteristics over recommended operating free-air temperature range, AVDD = 5 V,

DV

DD

= 5 V, IOUTFS = 20 mA, single-ended output IOUT1, 50 Ω doubly terminated load (unless

otherwise noted)

ac specifications

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

Analog output

p

p

DVDD = 4.5 V to 5.5 V 100

f

CLK

Maximum output update rate

DVDD = 3 V to 3.6 V 67

MSPS

t

s(DAC)

Output settling time to 0.1%

†

35 ns

t

pd

Output propagation delay 1 ns

GE Glitch energy

‡

Worst case LSB transition (code 127 – code 128) 5 pV–s

t

r(IOUT)

Output rise time 10% to 90%

†

1 ns

t

f(IOUT)

Output fall time 90% to 10%

†

1 ns

p

IOUTFS = 20 mA 15

Output noise

IOUTFS = 2 mA 10

pA/√HZ

AC linearity (to Nyquist)

f

CLK

= 5 MSPS, f

OUT

= 1 MHz, TA = 25°C 50

f

CLK

= 25 MSPS, f

OUT

= 1 MHz, TA = 25°C 50

f

CLK

= 25 MSPS, f

OUT

= 5 MHz, TA = 25°C 50

f

CLK

= 25 MSPS, f

OUT

= 10 MHz, TA = 25°C 48

f

CLK

= 50 MSPS, f

OUT

= 1 MHz, TA = 25°C 50

f

CLK

= 50 MSPS, f

OUT

= 5 MHz, TA = 25°C 50

SINAD Signal-to-noise and distortion ratio

f

CLK

= 50 MSPS, f

OUT

= 20 MHz, TA = 25°C

47

dB

f

CLK

= 70 MSPS, f

OUT

= 5 MHz, TA = 25°C 50

f

CLK

= 70 MSPS, f

OUT

= 10 MHz, TA = 25°C 50

f

CLK

= 70 MSPS, f

OUT

= 20 MHz, TA = 25°C 46

f

CLK

= 100 MSPS, f

OUT

= 10 MHz, TA = 25°C 47

f

CLK

= 100 MSPS, f

OUT

= 22 MHz, TA = 25°C 47

f

CLK

= 100 MSPS, f

OUT

= 40 MHz, TA = 25°C 45

f

CLK

= 5 MSPS, f

OUT

= 1 MHz, TA = 25°C –69

f

CLK

= 25 MSPS, f

OUT

= 1 MHz, TA = 25°C –67

f

CLK

= 25 MSPS, f

OUT

= 5 MHz, TA = 25°C –69

f

CLK

= 25 MSPS, f

OUT

= 10 MHz, TA = 25°C –57

f

CLK

= 50 MSPS, f

OUT

= 1 MHz, TA = 25°C –67

f

CLK

= 50 MSPS, f

OUT

= 1 MHz, TA = –40°C to 85°C –64

f

CLK

= 50 MSPS, f

OUT

= 5 MHz, TA = 25°C –66

THD

Total harmonic distortion

f

CLK

= 50 MSPS, f

OUT

= 20 MHz, TA = 25°C –52

dBc

f

CLK

= 70 MSPS, f

OUT

= 5 MHz, TA = 25°C –64

f

CLK

= 70 MSPS, f

OUT

= 10 MHz, TA = 25°C –60

f

CLK

= 70 MSPS, f

OUT

= 20 MHz, TA = 25°C –48

f

CLK

= 100 MSPS, f

OUT

= 10 MHz, TA = 25°C –53

f

CLK

= 100 MSPS, f

OUT

= 22 MHz, TA = 25°C –53

f

CLK

= 100 MSPS, f

OUT

= 40 MHz, TA = 25°C –47

†

Measured single ended into 50 Ω load at IOUT1.

‡

Single-ended output IOUT1, 50 Ω doubly terminated load.

THS5641A

8-BIT, 100 MSPS, CommsDAC

DIGITAL-TO-ANALOG CONVERTER

SLAS277 –MARCH 2000

6

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

electrical characteristics over recommended operating free-air temperature range, AVDD = 5 V,

DV

DD

= 5 V, IOUTFS = 20 mA, single-ended output IOUT1, 50 Ω doubly terminated load (unless

otherwise noted) (continued)

ac specifications

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

AC linearity (to Nyquist)

f

CLK

= 5 MSPS, f

OUT

= 1 MHz, TA = 25°C 68

f

CLK

= 25 MSPS, f

OUT

= 1 MHz, TA = 25°C 69

f

CLK

= 25 MSPS, f

OUT

= 5 MHz, TA = 25°C 68

f

CLK

= 25 MSPS, f

OUT

= 10 MHz, TA = 25°C 56

f

CLK

= 50 MSPS, f

OUT

= 1 MHz, TA = 25°C 67

f

CLK

= 50 MSPS, f

OUT

= 5 MHz, TA = 25°C 67

SFDR Spurious free dynamic range

f

CLK

= 50 MSPS, f

OUT

= 20 MHz, TA = 25°C

53

dBc

f

CLK

= 70 MSPS, f

OUT

= 5 MHz, TA = 25°C 65

f

CLK

= 70 MSPS, f

OUT

= 10 MHz, TA = 25°C 63

f

CLK

= 70 MSPS, f

OUT

= 20 MHz, TA = 25°C 48

f

CLK

= 100 MSPS, f

OUT

= 10 MHz, TA = 25°C 55

f

CLK

= 100 MSPS, f

OUT

= 22 MHz, TA = 25°C 55

f

CLK

= 100 MSPS, f

OUT

= 40 MHz, TA = 25°C 48

digital specifications

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

Interface

p

DVDD = 5 V 3.5 5

VIHHigh-level input voltage

DVDD = 3.3 V 2.1 3.3

V

p

DVDD = 5 V 0 1.3

VILLow-level input voltage

DVDD = 3.3 V 0 0.9

V

I

IH

High-level input current DVDD = 3 V to 5.5 V –10 10 µA

I

IL

Low-level input current DVDD = 3 V to 5.5 V –10 10 µA

Input capacitance 1 5 pF

Timing

t

su(D)

Input setup time 1 ns

t

h(D)

Input hold time 1 ns

t

w(LPH)

Input latch pulse high time 4 ns

t

d(D)

Digital delay time

1 clk

Specifications subject to change

THS5641A

8-BIT, 100 MSPS, CommsDAC

DIGITAL-TO-ANALOG CONVERTER

SLAS277 –MARCH 2000

7

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TYPICAL CHARACTERISTICS

†

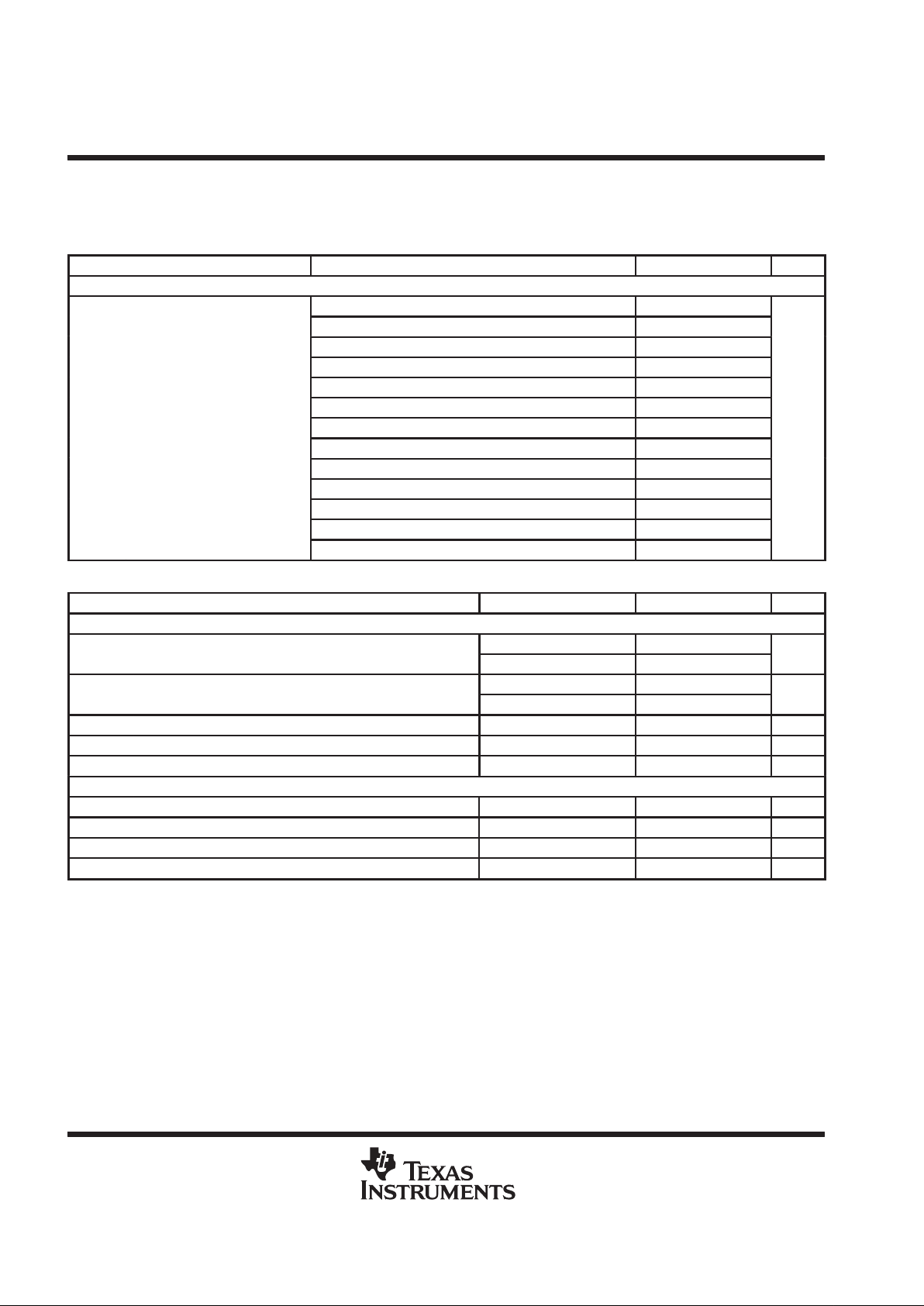

Figure 1

42

48

54

60

66

72

78

0 1020304050

SPURIOUS FREE DYNAMIC RANGE

vs

OUTPUT FREQUENCY

Fout – MHz

Fclock = 5 MSPS

SFDR – dBc

Fclock = 25 MSPS

Fclock = 50 MSPS

Fclock = 70 MSPS

Fclock = 100 MSPS

AVDD = 5 V

DVDD = 5 V

Figure 2

–78

–72

–66

–60

–54

–48

–42

0 1020304050

TOTAL HARMONIC DISTORTION

vs

OUTPUT FREQUENCY

Fout – MHz

THD – dBc

AVDD = 5 V

DVDD = 5 V

70 MSPS

100 MSPS

50 MSPS

5 MSPS

25 MSPS

Figure 3

42

45

48

51

54

0 1020304050

SIGNAL-TO-NOISE AND DISTORTION RATIO

vs

OUTPUT FREQUENCY

Fout – MHz

SINAD – dB

AVDD = 5 V

DVDD = 5 V

5 MSPS

25 MSPS

50 MSPS

70 MSPS

100 MSPS

48

54

60

66

72

78

0 5 10 15 20 25 30 35

Figure 4

SPURIOUS FREE DYNAMIC RANGE

vs

OUTPUT FREQUENCY

Fout – MHz

SFDR – dBc

5 MSPS

67 MSPS

AVDD = 3.3 V

DVDD = 3.3 V

25 MSPS

50 MSPS

†

AVDD and DVDD specified for each chart seperately, IOUTFS = 20 mA, single-ended output IOUT1, 50 Ω doubly terminated load, TA = 25°C

(unless otherwise noted.)

THS5641A

8-BIT, 100 MSPS, CommsDAC

DIGITAL-TO-ANALOG CONVERTER

SLAS277 –MARCH 2000

8

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TYPICAL CHARACTERISTICS

†

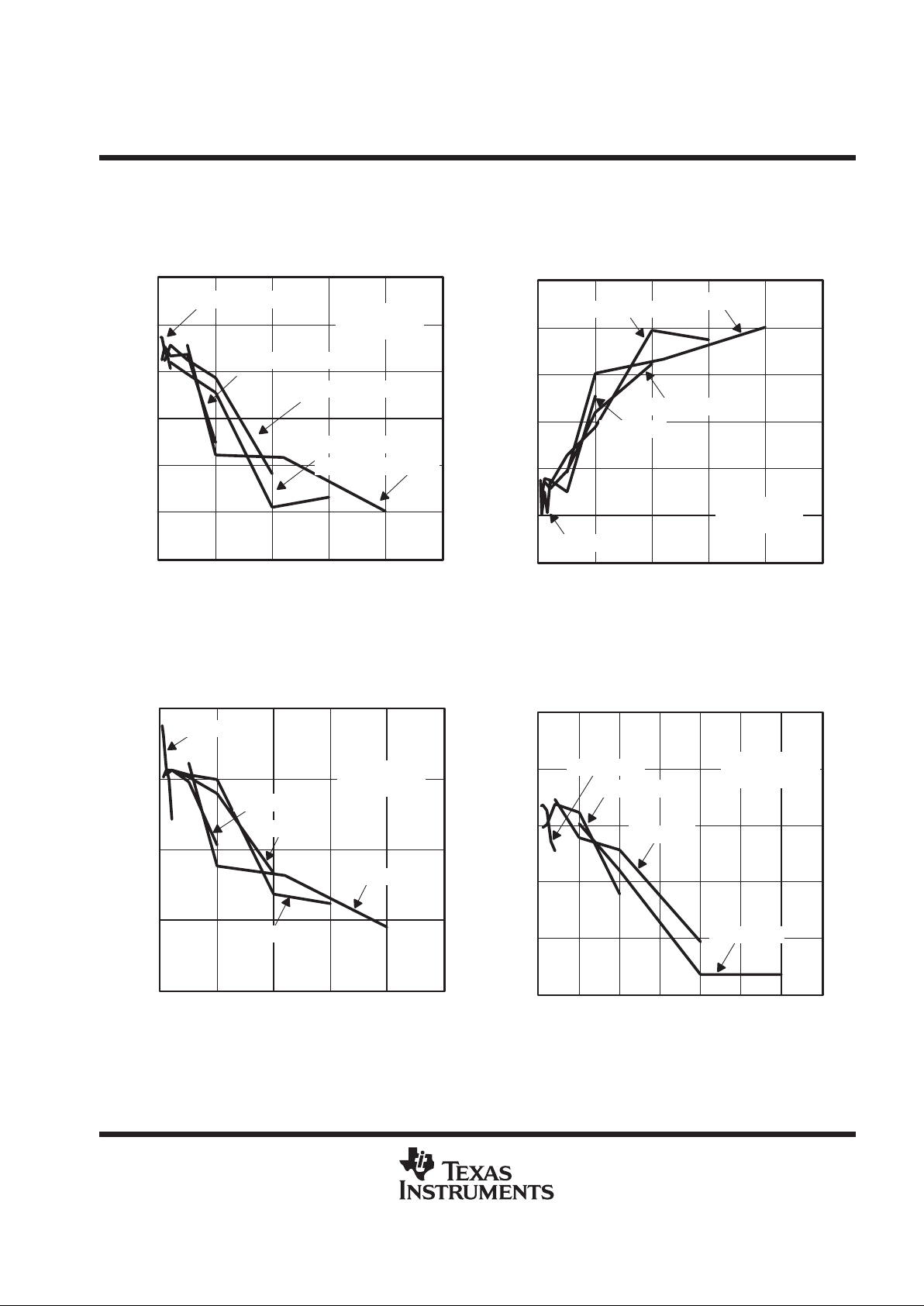

–78

–72

–66

–60

–54

–48

0 5 10 15 20 25 30 35

Figure 5

TOTAL HARMONIC DISTORTION

vs

OUTPUT FREQUENCY

Fout – MHz

THD – dBc

25 MSPS

50 MSPS

AVDD = 3.3 V

DVDD = 3.3 V

5 MSPS

67 MSPS

Figure 6

42

45

48

51

54

0 5 10 15 20 25 30 35

SIGNAL-TO-NOISE AND DISTORTION RATIO

vs

OUTPUT FREQUENCY

Fout – MHz

SINAD – dB

25 MSPS

AVDD = 3.3 V

DVDD = 3.3 V

50 MSPS

5 MSPS

67 MSPS

Figure 7

42

45

48

51

54

–40 –20 0 20 40 60 80

Fout = 2 MHZ

SIGNAL-TO-NOISE AND DISTORTION RATIO

vs

TEMPERATURE AT 70 MSPS

Ambient Temperature – °C

SINAD – dB

Fout = 10 MHZ

Fout = 25 MHZ

AVDD = 5 V

DVDD = 5 V

Figure 8

42

45

48

51

54

–40 –20 0 20 40 60 80

Fout = 2 MHz

SIGNAL-TO-NOISE AND DISTORTION RATIO

vs

TEMPERATURE AT 70 MSPS

Ambient Temperature – °C

SINAD – dB

Fout = 10 MHz

Fout = 25 MHz

AVDD = 3.3 V

DVDD = 3.3 V

†

AVDD and DVDD specified for each chart seperately, IOUTFS = 20 mA, single-ended output IOUT1, 50 Ω doubly terminated load, TA = 25°C

(unless otherwise noted.)

THS5641A

8-BIT, 100 MSPS, CommsDAC

DIGITAL-TO-ANALOG CONVERTER

SLAS277 –MARCH 2000

9

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

TYPICAL CHARACTERISTICS

†

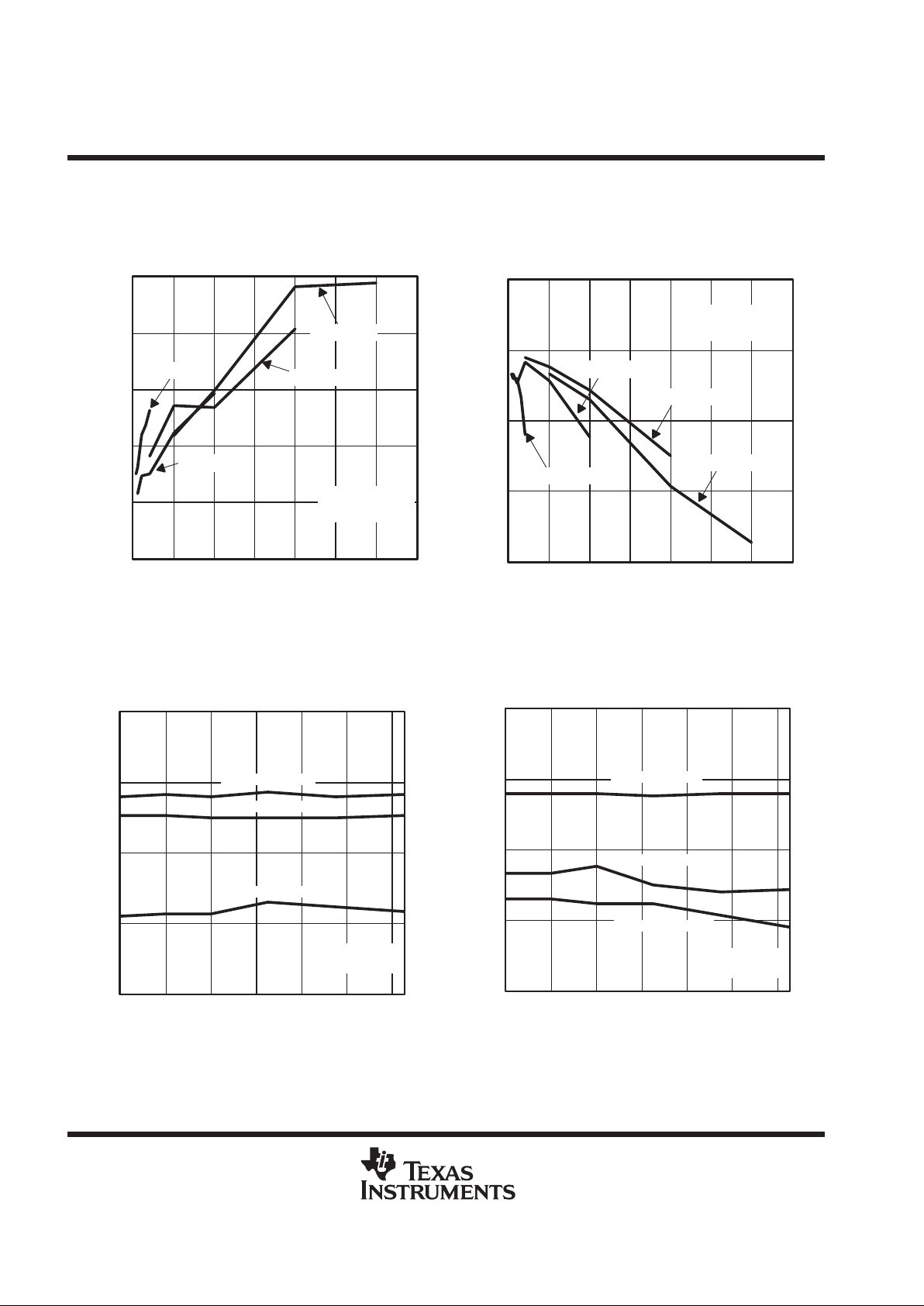

Figure 9

36

42

48

54

60

66

72

78

2 4 6 8 101214161820

SPURIOUS FREE DYNAMIC RANGE

vs

FULL-SCALE OUTPUT CURRENT AT 100 MSPS

IoutFS – mA

SFDR – dBc

Fout = 2.5 MHz

Fout = 10 MHz

Fout = 28.6 MHz

Fout = 40 MHz

AVDD = 5 V

DVDD = 5 V

30

36

42

48

54

2 4 6 8 101214161820

Figure 10

SIGNAL-TO-NOISE AND DISTORTION RATIO

vs

FULL-SCALE OUTPUT CURRENT AT 100 MSPS

IoutFS – mA

SINAD – dB

AVDD = 5 V

DVDD = 5 V

Fout = 2.5 MHz

Fout = 10 MHz

Fout = 28.6 MHz

Fout = 40 MHz

Figure 11

48

54

60

66

72

78

0 5 10 15 20 25

SPURIOUS FREE DYNAMIC RANGE

vs

OUTPUT FREQUENCY AT 50 MSPS

Fout – MHz

SFDR – dBc

DIFFERENTIAL OUTPUT

SINGLE-ENDED

OUTPUT IOUT1

AVDD = 5 V

DVDD = 5 V

Figure 12

42

45

48

51

54

0 5 10 15 20 25

SIGNAL-TO-NOISE AND DISTORTION RATIO

vs

OUTPUT FREQUENCY AT 50 MSPS

Fout – MHz

SINAD – dB

DIFFERENTIAL OUTPUT

SINGLE-ENDED

OUTPUT IOUT1

AVDD = 5 V

DVDD = 5 V

†

AVDD and DVDD specified for each chart seperately, IOUTFS = 20 mA, single-ended output IOUT1, 50 Ω doubly terminated load, TA = 25°C

(unless otherwise noted.)

Loading...

Loading...