THMC50

REMOTE/LOCAL TEMPERATURE MONITOR AND

FAN CONTROLLER WITH SMBus INTERFACE

SLIS090 – JUL Y 1999

1

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

D

T wo-Wire SMBus Serial Interface

D

3.3 V Operation

D

Low Operating and Standby Current

D

Remote and Local Temperature Monitoring

D

0 V to 2.5 V, 8-bit DAC for Fan Speed

Control

D

Two Voltage Supervisors With Reset

Functions

D

Fault Tolerant Fan Control With Automatic

Hardware Trip Point

D

Bidirectional Thermal Overload Indicator

D

ACPI Thermal Model Compliant

1

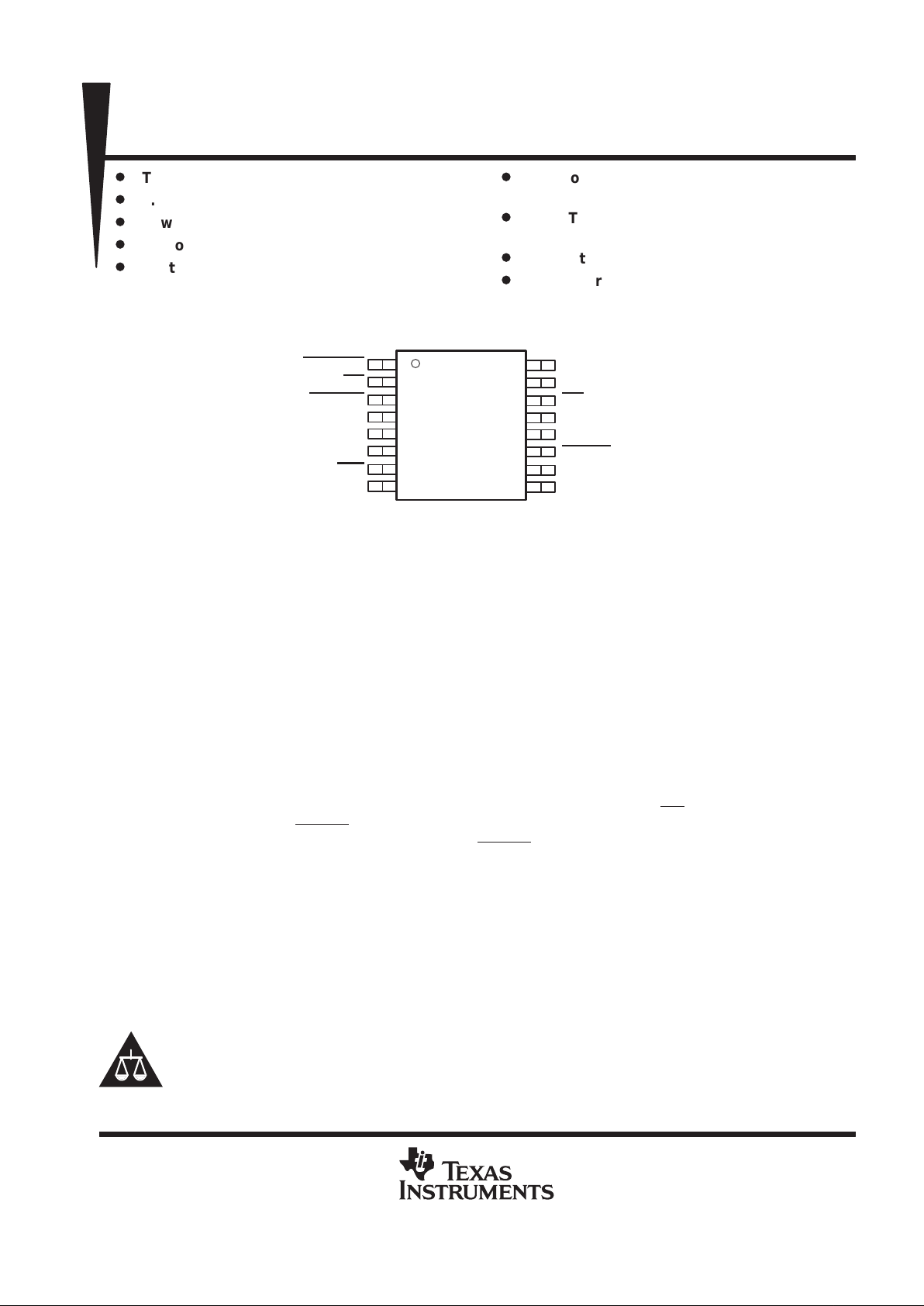

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

FAN_OFF

MR

AUXRST

GND

VCC3AUX

VCC3

RST

FAN_SPD/NTEST_IN

SDA

SCL

INT

ADD/NTEST_OUT

GPI

THERM

REMOTE_DIODE+

REMOTE_DIODE–

16-Pin SSOP DBQ Package

(TOP VIEW)

NOTE: Pin assignments are preliminary.

description

The THMC50 is a local/remote temperature monitor with two voltage supervisor circuits and an 8-bit, 0-V to

2.5-V DAC designed for temperature monitoring and fan control via a two-wire SMBus serial interface. The

THMC50 is intended for use in personal computer applications according to the Advanced Configuration and

Power Interface (ACPI) thermal model. The device is also suitable for use in network routers and hubs, office

equipment, telephone switching networks, industrial control applications, and any other application requiring

temperature monitoring, fan speed control, and two 3.3-V supply voltage supervisors.

T emperature data is reported in a 2s complement, 8-bit binary format. The local temperature sensor can be used

to monitor the ambient temperature, while a remote thermal diode, such as the one present on the Intel

Pentium II, III, and the Sun UltraSPARC microprocessors, can be used to monitor the actual CPU die

temperature. For applications not using a microprocessor with an integrated thermal diode, an inexpensive

diode-connected 2N3904 NPN transistor can also be used to sense the remote temperature.

The THMC50 provides maskable interrupts for under/over temperature condition with default or user adjustable

limit values. If the temperature limit values are exceeded, the THMC50 asserts INT

low. If the default thermal

limits are exceeded, the THERM

terminal is asserted low, and the F AN_SPD analog output automatically goes

to full-scale voltage to set the fan at maximum speed. THERM

can also be used as an input to instantly command

full fan speed.

The 8-bit, 0–2.5 V DAC output of the THMC50, along with an external amplifier circuit, provides the means to

control the speed of a cooling fan. Fault tolerant fan-speed control is achieved through default and

user-programmable values for high temperature limits that command the fan to full speed once the temperature

limits are exceeded.

The THMC50 also provides two reset functions for the V

(VCC3AUX)

and V

(VCC3)

supply voltage. The reset

functions are assured down to 1-V supply voltage.

Copyright 1999, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Intel and Pentium are registered trademarks of Intel Corporation.

Sun is a registered trademark and UltraSPARC is a trademark of Sun Microsystems.

THMC50

REMOTE/LOCAL TEMPERATURE MONITOR AND

FAN CONTROLLER WITH SMBus INTERFACE

SLIS090 – JUL Y 1999

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

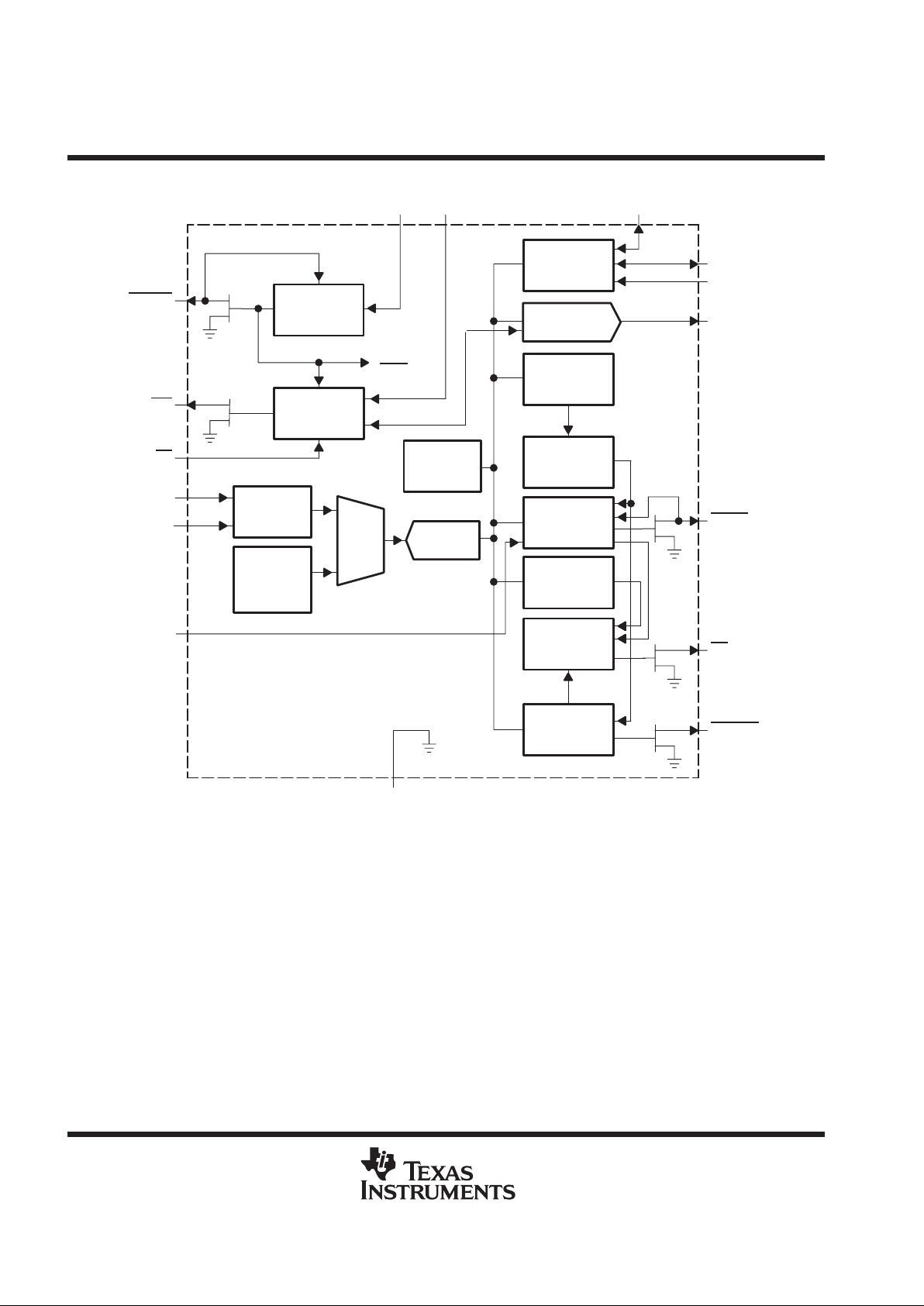

schematic/block diagram

ADC

Aux Reset

Generator

Bandgap

Temperature

Sensor

(Ambient)

Signal

Conditioning

Main Reset

Generator

Analog

Mux

SDA

Analog Output

Register & DAC

Configuration

Register

Mask

Gating

Interrupt

Mask

Register

Interrupt

Status

Registers

Limit

Comparators

Value & Limit

Registers

Serial Bus

Interface

GND

SCL

FAN_SPD/NTEST_IN

THERM

INT

FAN_OFF

AUXRST

RST

MR

REMOTE_DIODE+

REMOTE_DIODE–

GPI

VCC3AUX VCC3 ADD/NTEST_OUT

Address

Pointer

Register

Internal

Reset

THMC50

REMOTE/LOCAL TEMPERATURE MONITOR AND

FAN CONTROLLER WITH SMBus INTERFACE

SLIS090 – JUL Y 1999

3

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

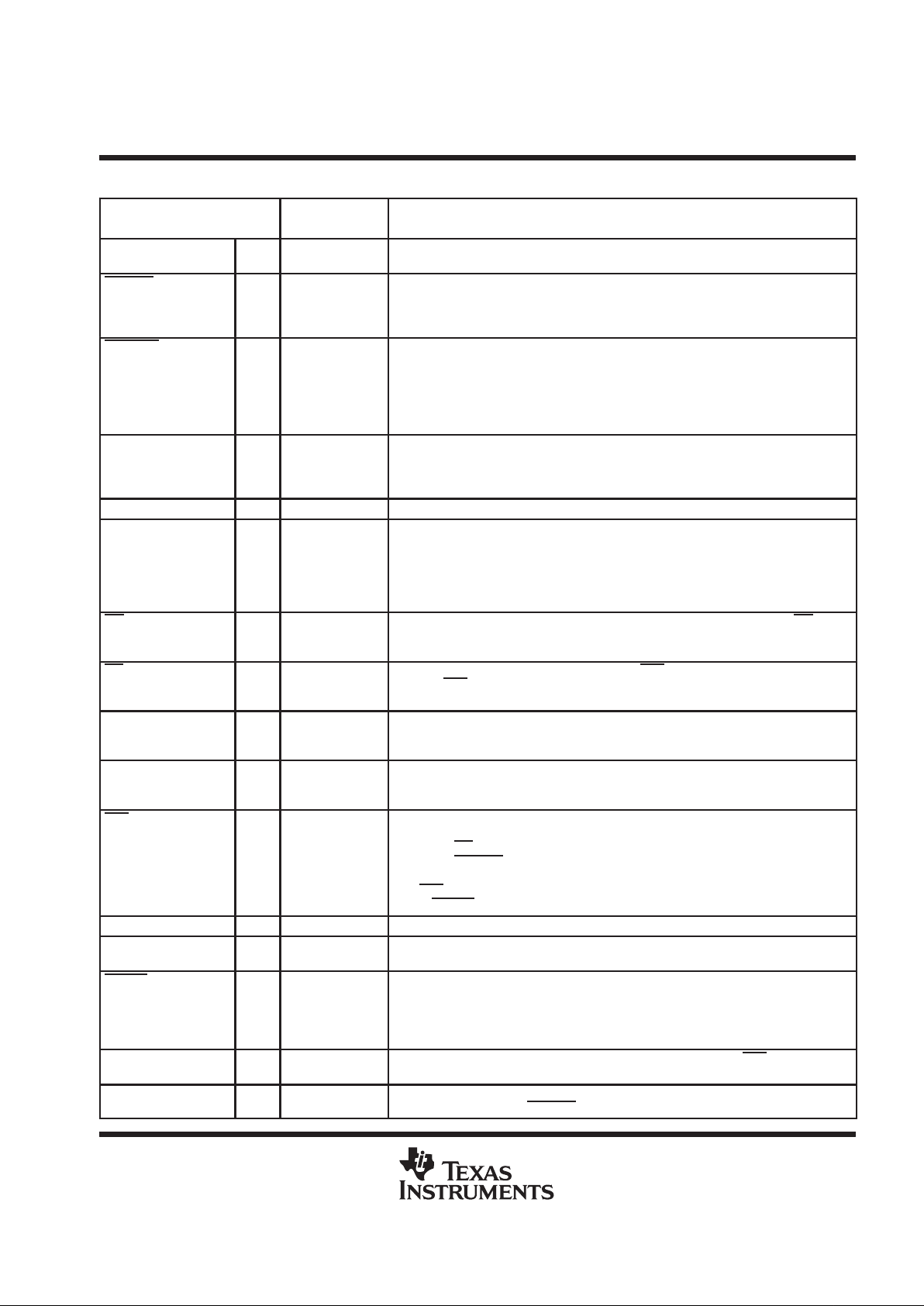

Terminal Functions

TERMINAL

NAME NO.

I/O

DESCRIPTION

ADD/NTEST_OUT 13 Digital I/O This terminal is used to determine the two LSBs of the SMBus address during initial

power on and it also functions as a digital output when doing a NAND tree test.

AUXRST 3 Digital I/O

(open drain)

This terminal is asserted low while VCC3AUX remains below the reset threshold. It

remains asserted for the reset timeout period after the reset condition is terminated. It is

bidirectional so that the THMC50 can be optionally reset; external logic must be used to

prevent a system auxiliary reset from occurring.

FAN_OFF 1 Digital output

(open drain)

Fan off request output. When commanded low via bit 5 in the configuration register

(0×40), this indicates a request to shut the fan off independent of the F AN_SPD output.

When commanded high via bit 5 in the configuration register (0×40), it indicates that the

fan may be turned on. This is an open-drain output requiring an external pullup.

Note: This terminal requires external circuitry to turn the fan off. It does not command the

analog output to 0×00 (see

Typical Application Schematic

).

FAN_SPD/NTEST_IN 8 Analog

output/test input

This terminal is an active-high input that enables NAND tree board-level connectivity

testing during device power up. Refer to the section on NAND tree testing. Also used as

the analog output of the 8-bit DAC for fan speed control when not in NAND tree test

mode.

GND 4 Ground

GPI 12 Digital input General-purpose input. The logic state of this terminal is reflected in bit 4 of the interrupt

status register (0x41). The logic state of the GPI terminal reported in bit 4 of the interrupt

status register (0x41) is inverted from the actual GPI logic state if bit 6 of the configuration

register (0x40) is set to a 1. If bit 6 of the configuration register (0×40) is set to a 0, then bit

4 of the interrupt status register (0×41) reports the same logic state present on the GPI

terminal.

INT 14 Digital output

(open drain)

System interrupt output. This signal indicates a violation of a set trip point. The INT output

is enabled when bit 1 of the configuration register (0x40) is set to 1. The default state is

disabled.

MR 2 Digital input Manual reset. A logic low on this input causes RST to be asserted. Once this input is

negated, RST

remains asserted for approximately 180 ms. This input has an internal

20-kΩ pullup resistor. Leave unconnected if not used.

REMOTE_DIODE– 9 Remote thermal

diode negative

input

This is the negative input (current sink) from the remote thermal diode.

REMOTE_DIODE+ 10 Remote thermal

diode positive

input

This is the positive input (current source) from the remote thermal diode.

RST 7 Digital output

(open drain)

This terminal is asserted low under any of the following conditions:

• VCC3 remains below the reset threshold

• While MR

is held low

• While AUXRST

is asserted

It remains asserted for the reset timeout period after the reset conditions are terminated.

The RST

function also resets the FAN_SPD analog output to 0xoo when asserted,

unless THERM

is asserted, then the FAN_SPD analog output will be 0xFF.

SCL 15 Digital input Serial SMBus clock

SDA 16 Digital I/O

(open drain)

Serial SMBus bidirectional data

THERM 11 Digital I/O

(open drain)

This is an active low thermal overload output that indicates a violation of a temperature

set point (overtemperature) for at least three monitoring cycles. Also acts as an input to

indicate a thermal event for fan control. When this signal is asserted low externally, a

status bit is set. The automatic fan control is activated to full on whenever this signal is

low.

VCC3 6 Analog input This is a 3.3-V main voltage monitor input for main reset generator (RST). This is not the

power supply terminal for THMC50.

VCC3AUX 5 Power supply

voltage input

This 3.3-V auxiliary voltage is the THMC50 power source and voltage monitor input for

auxiliary reset generator (AUXRST

). This terminal powers all THMC50 internal circuitry.

THMC50

REMOTE/LOCAL TEMPERATURE MONITOR AND

FAN CONTROLLER WITH SMBus INTERFACE

SLIS090 – JUL Y 1999

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

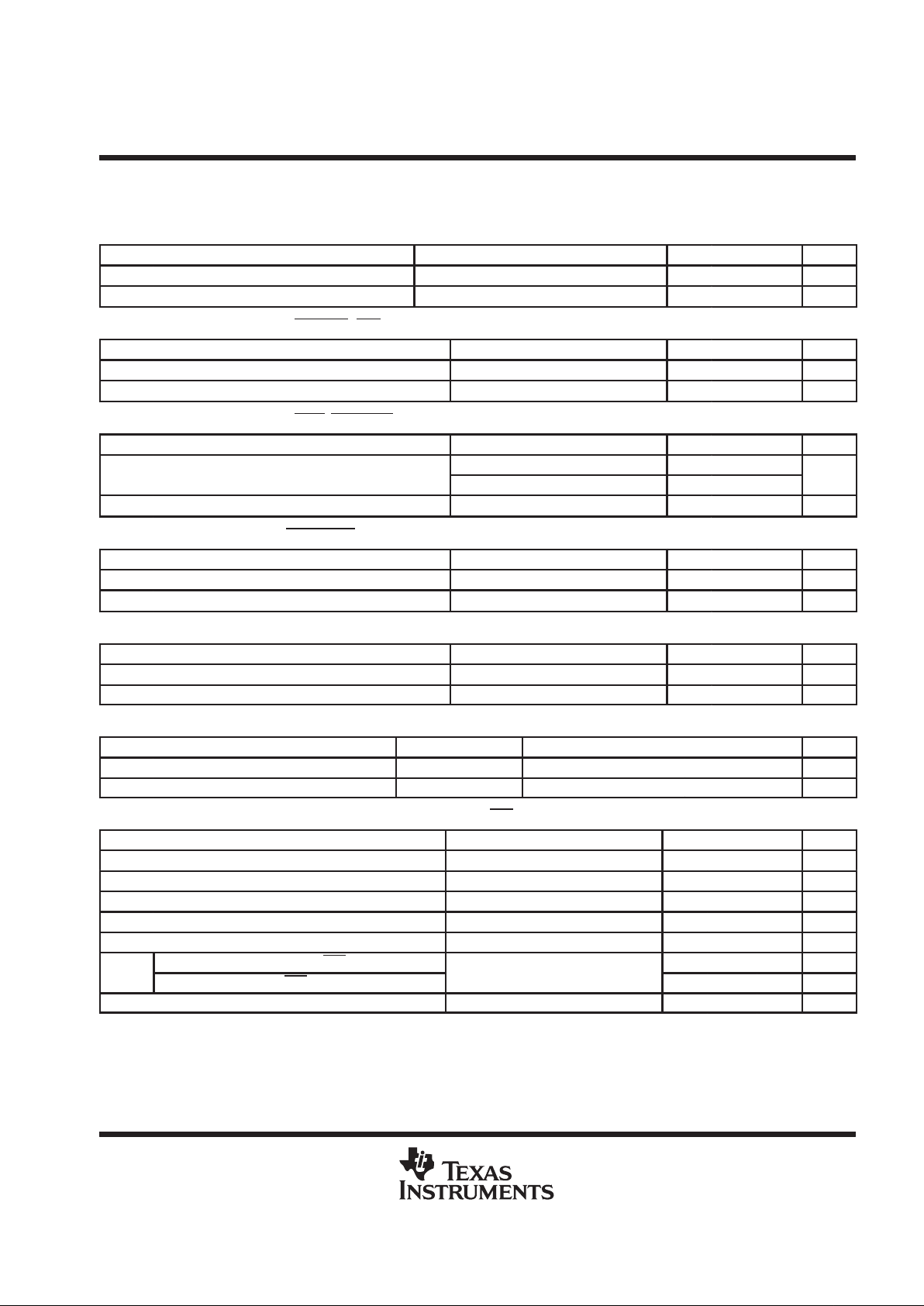

absolute maximum ratings over operating case temperature (see Note 1) (unless otherwise noted)

†

Voltage on VCC3AUX supply terminal, V

(VCC3AUX)

–0.3 V to 5.75 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Maximum voltage allowed for FAN_OFF

pullup, V

(FAN_OFF)

5.5 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input voltage on any I/O terminals (except analog inputs), V

(IOIN)

–0.3 V to V

(VCC3AUX)

+0.3 V. . . . . . . . . .

Input current on any I/O terminal (see Note 2), I

(IOIN)

–5 mA to 5 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Package input current (see Note 2), I

(PACKAGE)

–20 mA to 20 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input voltage on REMOTE_DIODE– terminal,V

(REMOTE_DIODE–)

–0.3 V to 0.8 V. . . . . . . . . . . . . . . . . . . . . .

REMOTE_DIODE– input current, I

(REMOTE_DIODE–)

–1 mA to 1 mA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Human body model ESD susceptibility, V

(HBMESD)

±2 kV. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Continuous power dissipation (see Note 3), P

D

330 mW. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating case temperature range, T

C

–40°C to 125°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature (see Note 4), T

stg

–65°C to 165°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Junction temperature, T

J

150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Lead temperature (soldering, 10 sec), T

(LEAD)

300°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

†

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. All voltages are measured with respect to GND, unless otherwise specified.

2. The 20-mA maximum package input current rating limits the number of terminals that can safely exceed the power supplies with

an input current of 5 mA to four terminals.

3. The maximum power dissipation must be derated at elevated temperatures and is dictated by T

Jmax

, θJA and the ambient

temperature, TA. The maximum allowable power dissipation at any temperature is PD = (T

Jmax

– TA)/θJA.

4. Solder accordingly to IPC standards.

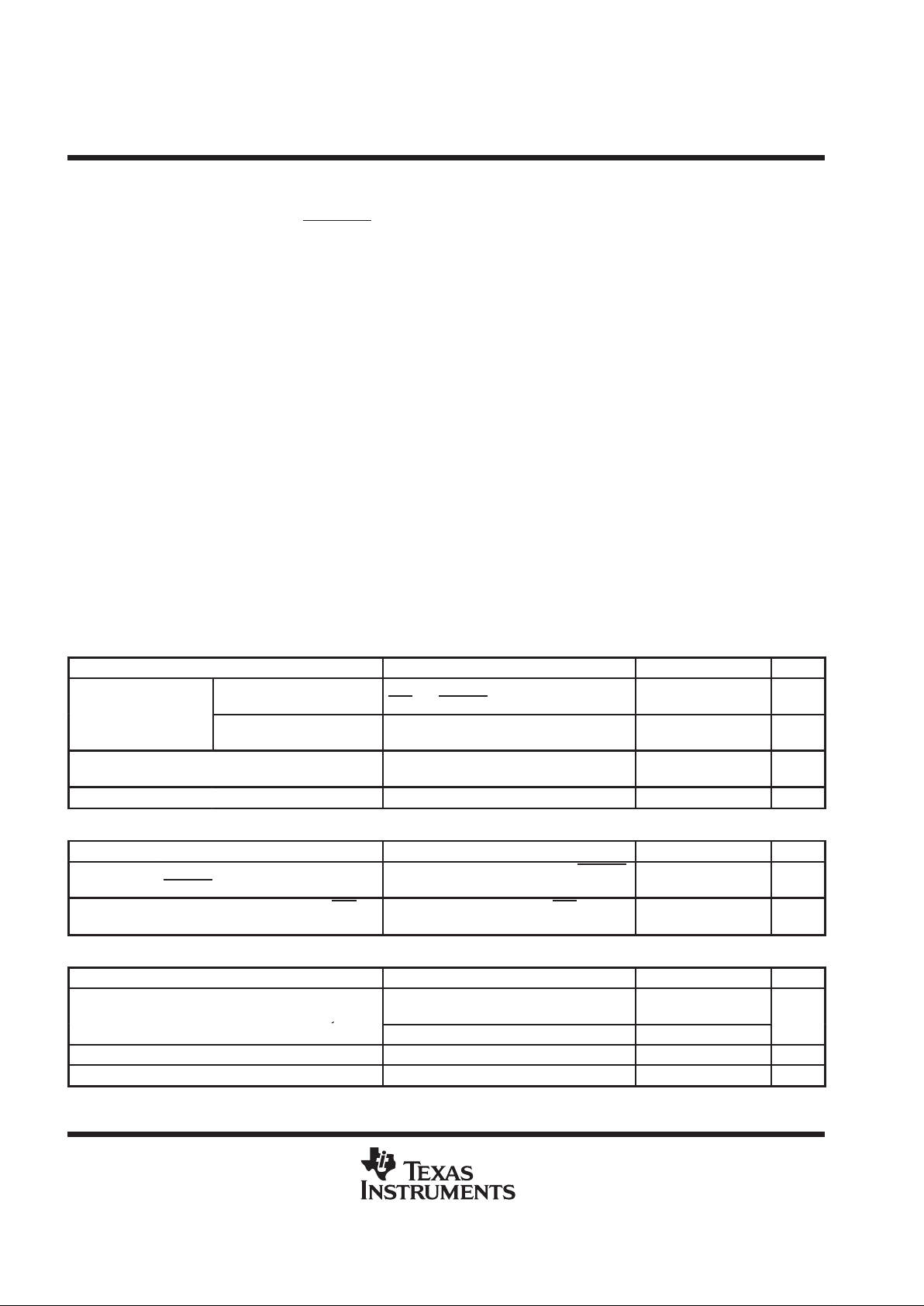

dc electrical characteristics, V

CC3

= V

(VCC3AUX)

= 3.3 V, TA = 25°C (unless otherwise noted)

power supply

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

VCC3AUX reset generator

supply voltage

Voltage on VCC3AUX needed to guarantee

RST

and AUXRST to stay valid

1 3.8 V

V

(VCC3AUX_RST)

VCC3AUX supply voltage

Normal operating supply voltage for all other

THMC50 circuits

3 3.3 3.8 V

I

(VCC3AUX)

Supply current

(interface inactive)

Exclude D/A converter source/sink current 1 2 mA

I

(VCC3AUX_STANDBY)

Standby mode 500 µA

voltage supervisors

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

V

THAUXRST

Threshold voltage on VCC3AUX for

AUXRST

active

Reduce VCC3AUX from 3.8 V until AUXRST

is low.

2.88 3 V

V

THRST

Threshold voltage on VCC3 for RST

active

Reduce VCC3 from 3.8 V until RST is low

with VCC3AUX = 3.3 V

2.88 3 V

temperature-to-digital converter

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

T

Measured temperature accurac

y

–40°C ≤TA < 60°C and

100°C <TA ≤ 125°C

–5 5

°C

(ACC)

y

60°C ≤TA ≤ 100°C –3 3

T

(RES)

Temperature resolution Design parameter – not tested 1 °C

V

(THRESH)

Remote_Diode+ open fault threshold 2.4 V

THMC50

REMOTE/LOCAL TEMPERATURE MONITOR AND

FAN CONTROLLER WITH SMBus INTERFACE

SLIS090 – JUL Y 1999

5

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

dc electrical characteristics, V

CC3

= V

(VCC3AUX)

= 3.3 V, TA = 25°C (unless otherwise noted)

(continued)

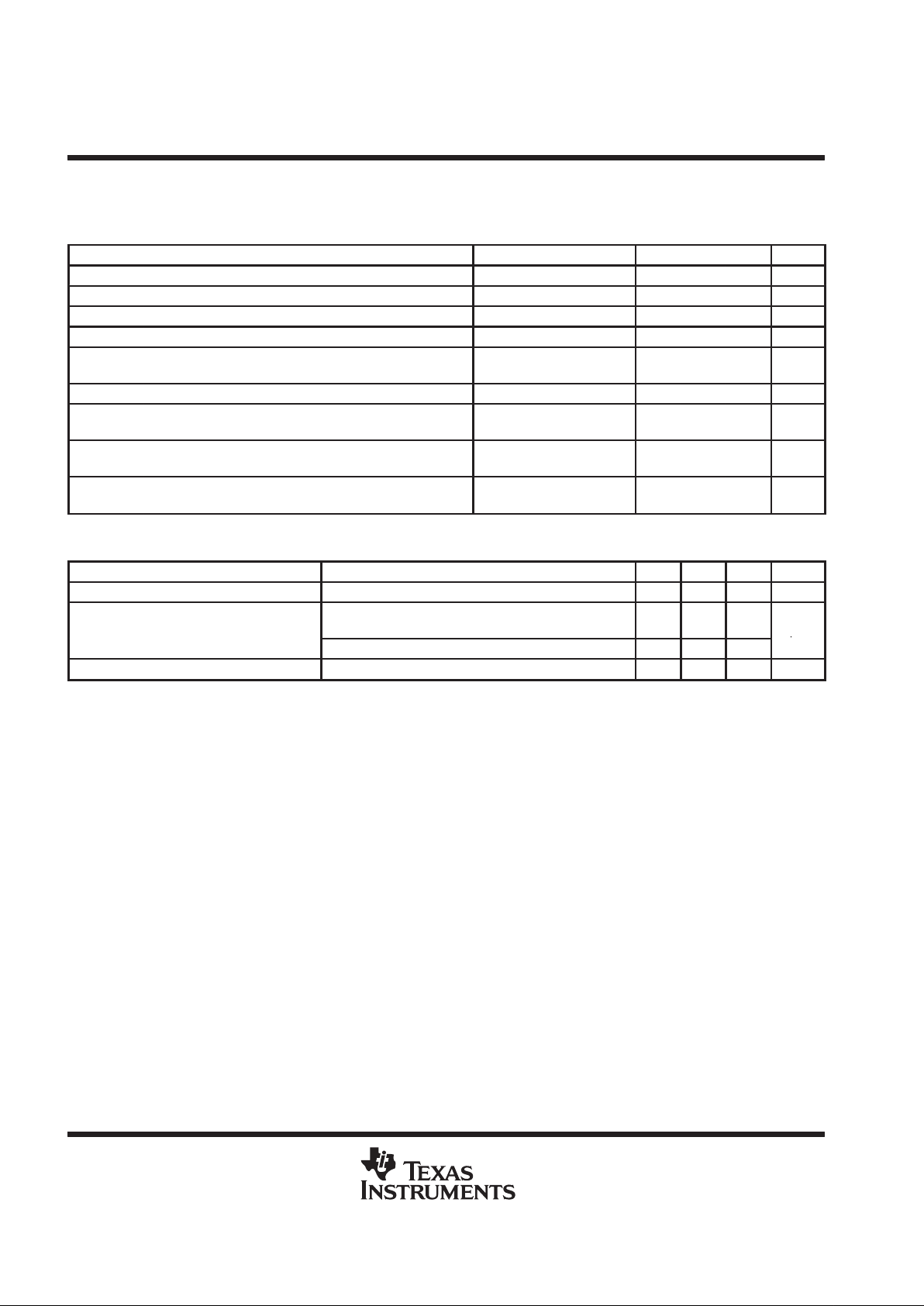

digital output: ADD/NTEST_OUT

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

V

OH

Logical 1 output voltage I

OUT

= –3 mA at V

(VCC3AUX)

= 2.85 V 2.4 V

V

OL

Logical 0 output voltage I

OUT

= 3 mA at V

(VCC3AUX)

= 3.8 V 0.4 V

open-drain digital outputs: THERM, INT

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

V

OL

Logical 0 output voltage I

OUT

= 3 mA at V

(VCC3AUX)

= 3.8 V 0.4 V

I

OH

High level output current V

OUT

= V

(VCC3AUX)

= 3.8 V 0.1 100 µA

open-drain digital outputs: RST, AUXRST

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

p

I

OUT

= 3 mA at V

(VCC3AUX)

= 3.8 V 0.4

VOLLogical 0 output voltage

I

OUT

= 3 mA at V

(VCC3AUX)

= 1 V 0.4

V

I

OH

High level output current V

OUT

= V

(VCC3AUX)

= 3.8 V 0.1 100 µA

open-drain digital output: FAN_OFF

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

V

OL

Logical 0 output voltage I

OUT

= 6 mA at V

(VCC3AUX)

= 3.8 V 0.4 V

I

OH

High level output current V

OUT

= V

(VCC3AUX)

= 3.8 V 0.1 100 µA

open-drain SMBus output: SDA

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

V

OL

Logical 0 output voltage I

OUT

= 3 mA at V

(VCC3AUX)

= 3.8 V 0.4 V

I

OH

High level output current V

OUT

= V

(VCC3AUX)

= 3.8 V 0.1 100 µA

SMBus digital inputs: SCL, SDA

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

V

IH

Logical 1 input voltage 0.7 × V

(VCC3AUX)

V

V

IL

Logical 0 input voltage 0.3 × V

(VCC3AUX)

V

digital inputs: FAN_SPD/NTEST_IN, ADD/NTEST_OUT, MR, GPI

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

V

IH

Logical 1 input voltage (5 V) 2.4 V

V

IL

Logical 0 input voltage (5 V) 0.8 V

V

IH

Logical 1 input voltage (3.3 V) 2 V

V

IL

Logical 0 input voltage (3.3 V) 0.4 V

I

IH

Logical 1 input current VIN = V

(VCC3AUX)

–0.005 –1 mA

Logical 0 input current (except MR)

0.005 1 mA

I

IL

Logical 0 input current (MR)

V

IN

=

0 V dc

165 250 µA

C

(IN)

Digital input terminal capacitance Design parameter only – not tested 20 pF

THMC50

REMOTE/LOCAL TEMPERATURE MONITOR AND

FAN CONTROLLER WITH SMBus INTERFACE

SLIS090 – JUL Y 1999

6

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

dc electrical characteristics, V

CC3

= V

(VCC3AUX)

= 3.3 V, TA = 25°C (unless otherwise noted)

(continued)

analog output: FAN_SPD/NTEST_IN

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

V

OUT

Output voltage range 0 2.5 V

Total unadjusted error (TUE) (see Note 5) IL = –2 mA –3% 3%

Full-scale error –3% ±1% 3%

Zero error, LSB No load 2

Differential nonlinearity (DNL), LSB (monotonic by design)

DAC setting

0 × 16 to 0 ×FF

–1 1

Integral nonlinearity , LSB ±1

C

(LOAD)

Maximum external load capacitance allow to insure DAC

stability

Design parameter only –

not tested

50 pF

I

(SOURCE)

Output source current

DAC setting

0 × 16 to 0 ×FF

–2 mA

I

(SINK)

Output sink current

DAC setting

0 × 16 to 0 ×FF

1 mA

NOTE 5: Total unadjusted error (TUE) includes offset, gain, and linearity errors of the DAC.

remote thermal diode sensing

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

T

(RES)

T emperature resolution 1 °C

I

Diode source current

REMOTE_DIODE+ = REMOTE_DIODE– + 0.65 V ,

high level

80 130

µ

A

(DIODE)

Low level 8 13

µ

I

(RATIO)

Diode source current ratio High level/low level 9.8 10 10.2

THMC50

REMOTE/LOCAL TEMPERATURE MONITOR AND

FAN CONTROLLER WITH SMBus INTERFACE

SLIS090 – JUL Y 1999

7

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

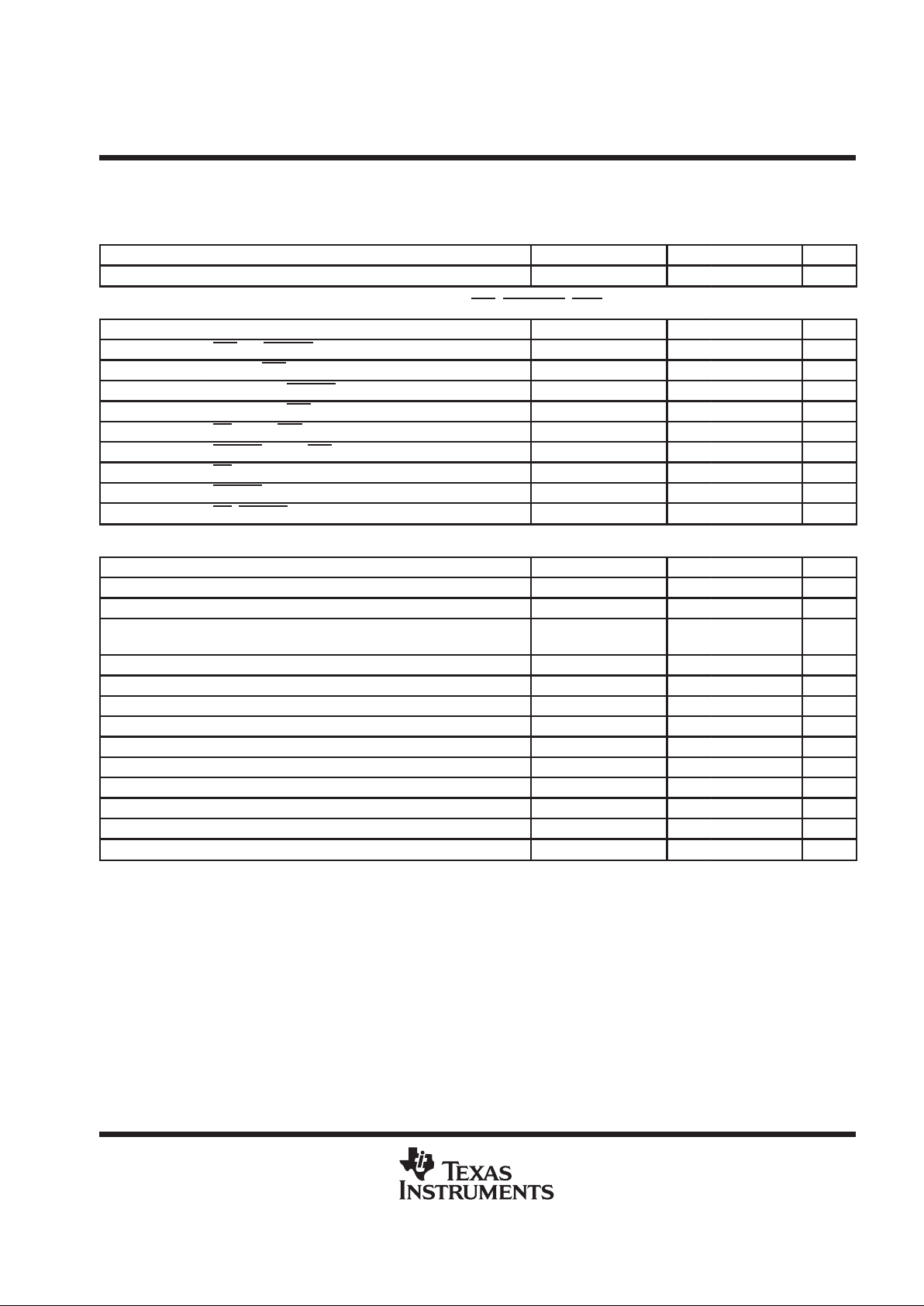

ac electrical characteristics, V

CC3

= V

(VCC3AUX)

= 3.3 V, TA = 25°C (see Notes 6 and 7) (unless

otherwise noted)

temperature-to-digital converter timing parameters: Remote_Diode+, Remote_Diode–

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

t

(SAMPLE)

T emperature-to-digital acquisition sample rate 0.75 1 1.25 sa/s

reset function timing parameters: VCC3, VCC3AUX, MR, AUXRST, RST

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

t

(RP)

RST and AUXRST pulse duration See Figures 17–20 140 560 ms

t

(VCC3RST)

VCC3 to RST delay See Figures 17–20 20 µs

t

(VCC3AUX1)

VCC3AUX to AUXRST delay See Figures 17–20 20 µs

t

(VCC3AUX2)

VCC3AUX to RST delay See Figures 17–20 20 µs

t

(MR)

MR input to RST delay See Figures 17–20 0.5 µs

t

(RST)

AUXRST input to RST delay See Figures 17–20 0.5 µs

t

(MRMIN)

MR input minimum pulse width 10 µs

t

(AUXRSTMIN)

AUXRST input minimum pulse width 10 µs

t

(GLITCH)

MR, AUXRST glitch immunity 100 ns

SMBus interface timing parameters: SCL, SDA

PARAMETER TEST CONDITIONS MIN TYP MAX UNITS

f

(SCL)

SCL operating frequency See Figure 1 10 100 kHz

t

(BUF)

Bus free time between stop and start condition See Figure 1 4.7 µs

t

(HDSTA)

Hold time after (repeated) start condition. After this period,

the first clock is generated

See Figure 1 4 µs

t

(SUSTA)

Repeated start condition setup time See Figure 1 4.7 µs

t

(SUSTO)

Stop condition setup time See Figure 1 4 µs

t

(HDDAT)

Data hold time See Figure 1 300 ns

t

(SUDAT)

Data setup time See Figure 1 250 ns

t

(LOW)

SCL clock low period See Figure 1 4.7 µs

t

(HIGH)

SCL clock high period See Figure 1 4 50 µs

t

(LOWSEXT)

Cumulative clock low extend time (slave device) See Figure 1 25 ms

t

(LOWMEXT)

Cumulative clock low extend time (master device) See Figure 1 10 ms

t

F

Clock/data fall time See Figure 1 300 ns

t

R

Clock/data rise time See Figure 1 1000 ns

NOTES: 6. Typicals are at TJ = TA = 25°C with V

(VCC3AUX)

= 3.3 V and represent most likely parametric norm.

7. Timing specifications are tested at the TTL logic levels, VIL = 0.4 V for a falling edge and VIH = 2.4 V for a rising edge. The 3-state

output voltage is forced to 1.4 V.

THMC50

REMOTE/LOCAL TEMPERATURE MONITOR AND

FAN CONTROLLER WITH SMBus INTERFACE

SLIS090 – JUL Y 1999

8

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

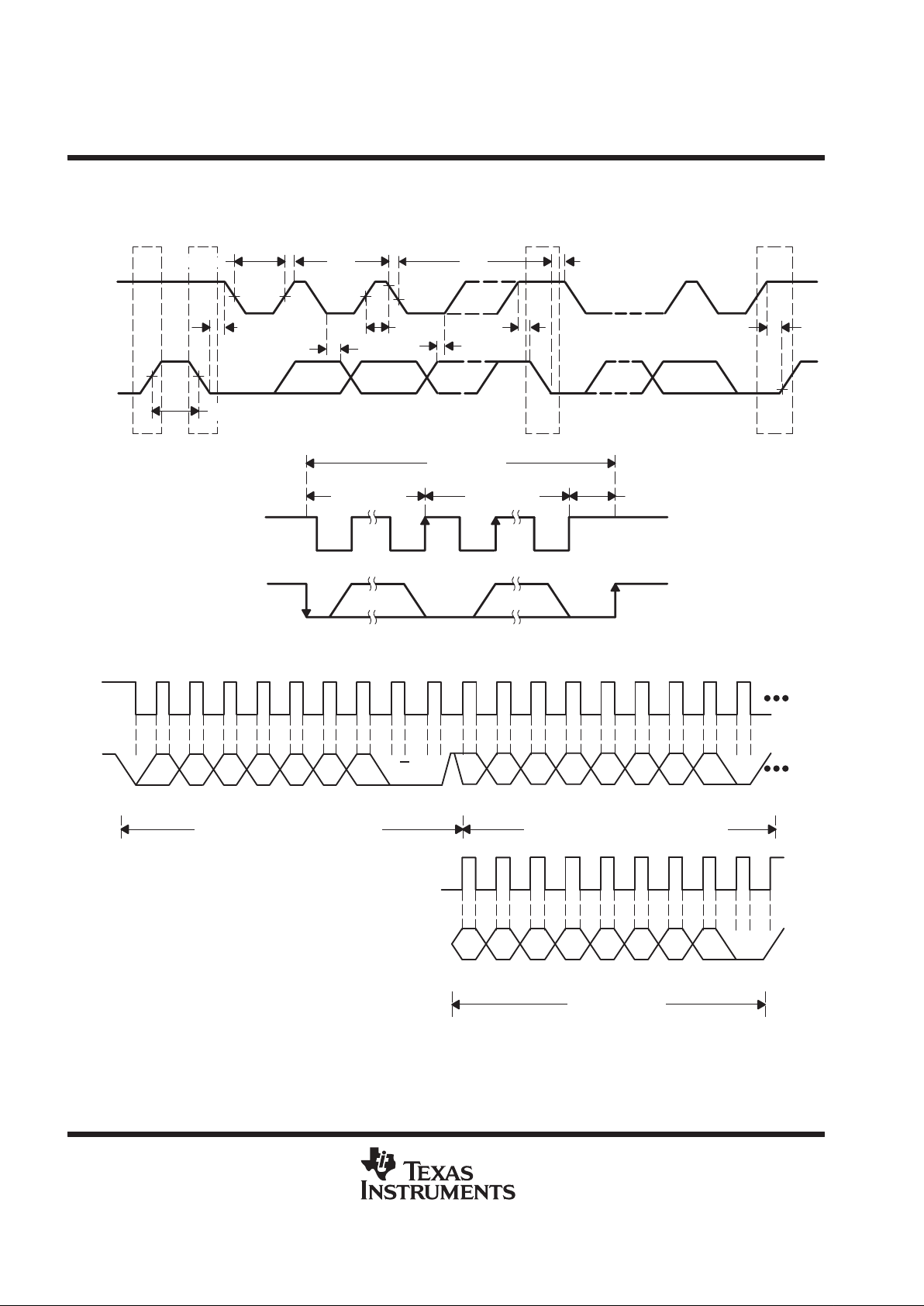

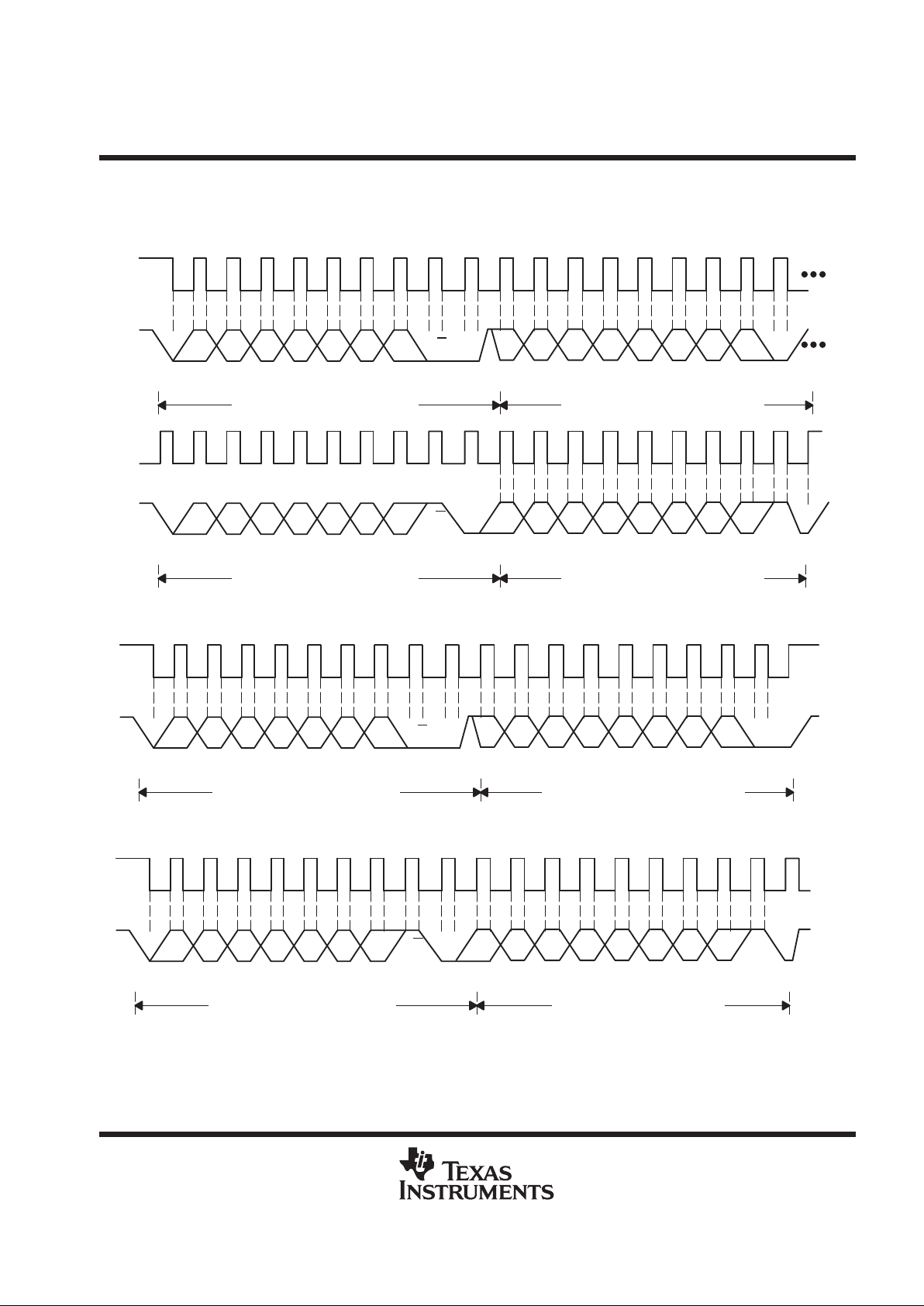

PARAMETER MEASUREMENT INFORMATION

SMBus timing diagrams

PS

t

(HDSTA)

t

(HDDAT)

t

(HIGH)

t

(SUDAT)

t

(SUSTA)

t

(HDSTA)

t

(SUSTO)

SP

SCLK

SDATA

Start

Stop

SCLK

ACK

SCLK

ACK

t

(LOWMEXT)

SCLK

SDATA

t

(LOW)

t

(LOWSEXT)

t

F

t

R

t

(BUF)

t

(LOWMEXT)

t

(LOWMEXT)

Figure 1. SMBus Timing Diagram

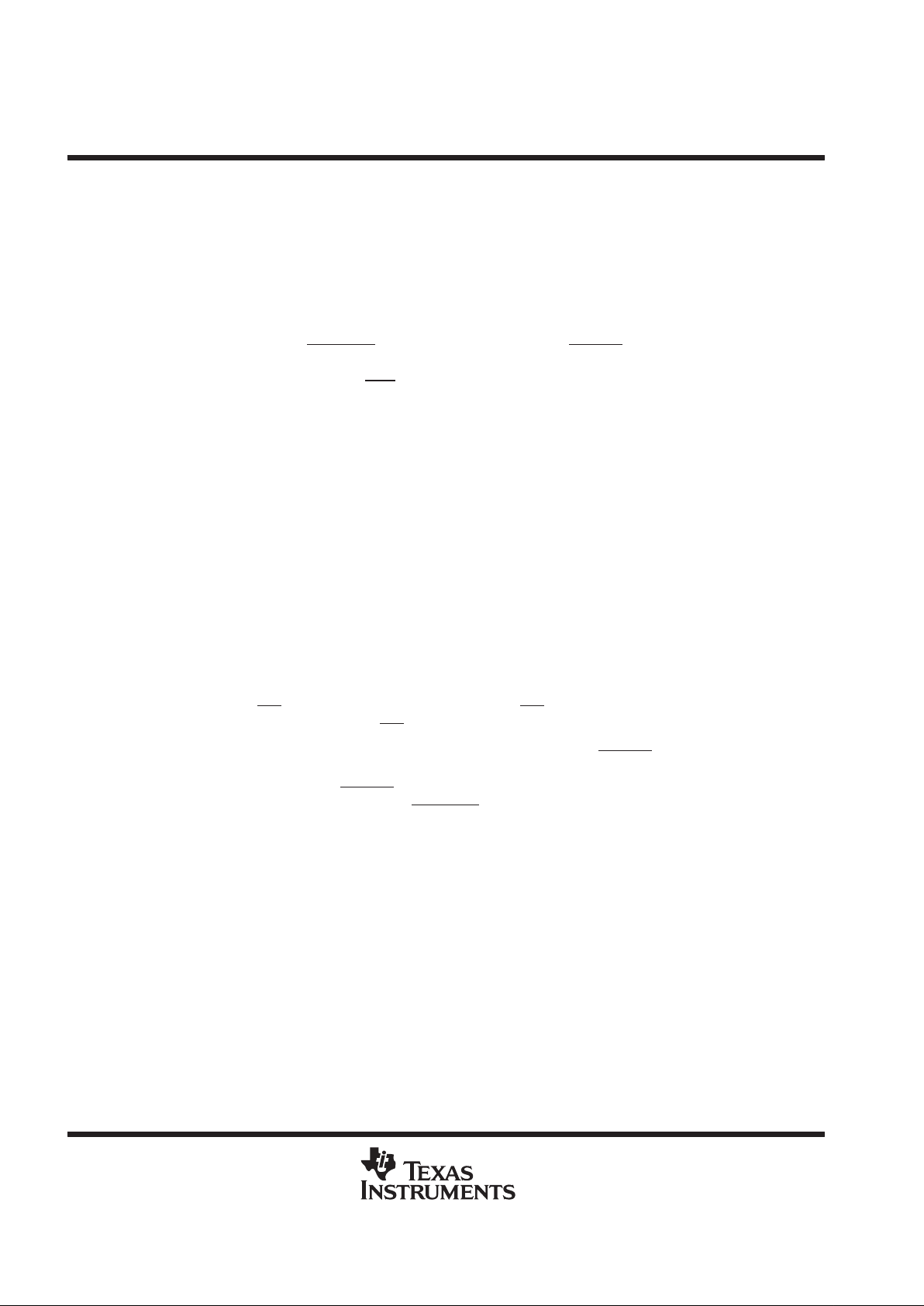

Frame 3 Data Byte

Frame 1 SMBus Slave Address Byte

Frame 2 Address Pointer Register Byte

A6 A5 A4 A3 A2 A1 A0 D7 D6 D5 D4 D3 D2 D1 D0R/W

SCLK

SDATA

Start By

Master

ACK By

THMC50

ACK By

Master

D7 D6 D5 D4 D3 D2 D1 D0

ACK By

THMC50

Stop By

Master

SCLK

(Continued)

SDATA

(Continued)

1

91 9

19

Figure 2. SMBus Timing Diagram for Write Byte Format

THMC50

REMOTE/LOCAL TEMPERATURE MONITOR AND

FAN CONTROLLER WITH SMBus INTERFACE

SLIS090 – JUL Y 1999

9

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

PARAMETER MEASUREMENT INFORMATION

SMBus timing diagrams (continued)

Frame 1 SMBus Slave Address Byte

Frame 2 Address Pointer Register Byte

A6 A5 A4 A3 A2 A1 A0 D7 D6 D5 D4 D3 D2 D1 D0R/W

SCLK

SDATA

Start By

Master

ACK By

THMC50

ACK By

Master

SCLK

(Continued)

SDATA

(Continued)

1

91 9

Frame 3 SMBus Slave Address Byte

Frame 4 Data Byte Read From THMC50

A6 A5 A4 A3 A2 A1 A0 D7 D6 D5 D4 D3 D2 D1 D0R/W

Start By

Master

ACK By

THMC50

NACK By

THMC50

1

91 9

Stop By

Master

Figure 3. SMBus Timing Diagram for Read Byte Format

Frame 1 SMBus Slave Address Byte

Frame 2 Address Pointer Register Byte

A6 A5 A4 A3 A2 A1 A0 D7 D6 D5 D4 D3 D2 D1 D0R/W

SCLK

SDATA

Start By

Master

ACK By

THMC50

ACK By

THMC50

1

91 9

Stop By

Master

Figure 4. SMBus Timing Diagram for Send Byte Format

Frame 1 SMBus Slave Address Byte

Frame 2 Data Byte From THMC50

A6 A5 A4 A3 A2 A1 A0 D7 D6 D5 D4 D3 D2 D1 D0R/W

SCLK

SDATA

Start By

Master

ACK By

THMC50

NACK

By Master

1

91 9

Stop By

Master

Figure 5. SMBus Timing Diagram for Recieve Byte Format

THMC50

REMOTE/LOCAL TEMPERATURE MONITOR AND

FAN CONTROLLER WITH SMBus INTERFACE

SLIS090 – JUL Y 1999

10

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

PRINCIPLES OF OPERATION

functional description

The THMC50 provides a remote thermal diode temperature sensor, an internal ambient temperature sensor,

an analog output, and two voltage supervisors/reset generators.

Temperatures read from the remote and internal sensors are converted into an 8-bit, 2s-complement digital

word with a 1°C LSB (least significant bit). The analog output is a 0-V to 2.5-V output from an 8-bit DAC that

is used along with external circuitry to control the fan speed. The analog output is automatically set by the

THMC50 to full on (0×FF), the FAN_OFF

output floats (fan is on), and THERM is asserted low when either of

two automatic trip points is exceeded for more than three monitoring cycle times. The FAN_SPD analog output

will be reset to full off (0x00) whenever RST

is asserted.

The THMC50 provides a number of internal registers, as detailed in Table 1. These include:

Register: Function:

Configuration register Provides control and configuration, as well as initialization

Interrupt status register Provides status of each limit or interrupt event

Interrupt status register mirror Mirror registers can be used by second agent needing to monitor

the THMC50 status.

Interrupt mask register Allows masking of individual interrupt sources, as well as

separate masking for the hardware interrupt output

Value RAM The monitoring results and limits for temperature are all

contained in the value RAM.

When the THMC50 is first started, it performs temperature conversions at a rate of 1Hz. Each measured

temperature value is compared to values stored in the limit registers. When the measured value exceeds the

programmed limit, the THMC50 sets a corresponding error bit in the interrupt status register. An open drain

hardware interrupt line, INT

, is available to generate an interrupt. INT is fully programmable with masking of each

interrupt source, and with masking of the INT

output.

The temperature monitoring section also has an open drain input/output, THERM

. This line is asserted low

internally whenever a critical temperature limit is exceeded for at least three monitoring cycles. It can also be

asserted low externally. Whenever THERM

is asserted low, either internally or externally, the analog output

automatically goes to full scale (0xFF) and the FAN_OFF

output floats (fan is on) in order to command the fan

to full speed.

SMBus interface

When using the SMBus interface, a write always consists of the THMC50 SMBus interface address byte,

followed by the internal address register byte, then the data byte (see Figure 2). There are two cases for a read:

1. If the internal address register is known to be at the desired address, simply read the THMC50 with the

SMBus interface address byte, followed by the data byte read from the THMC50 (see Figure 5).

2. If the internal address register value is unknown, write to the THMC50 with the SMBus interface address

byte, followed by the internal address register byte (see Figure 4). Next, restart the serial communication

with a read consisting of the SMBus interface address byte, followed by the data byte read from the

THMC50.

The default power-on SMBus address for the THMC50 is 0101 1XX binary, where XX reflects the state defined

by the add terminal. This allows up to three THMC50 devices to be used on a single system. T able 1 shows how

the state of the add terminal is used to define the THMC50 SMBus slave address.

Loading...

Loading...