Texas Instruments SM320C30HFGM50, SM320C30TBM33, SM320C30GBM33, SM320C30GBM40, SM320C30GBM50 Datasheet

...

SMJ320C30

DIGITAL SIGNAL PROCESSOR

SGUS014F – FEBRUARY 1991 – REVISED FEBRUARY 1999

1

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

2

D

–55°C to 125°C Operating Temperature

Range, QML Processing

D

Processed to MIL-PRF-38535 (QML)

D

Performance

– SMJ320C30-40 (50-ns Cycle)

40 MFLOPS

20 MIPS

– SMJ320C30-50 (40-ns Cycle)

50 MFLOPS

25 MIPS

D

Two 1K-Word × 32-Bit Single-Cycle

Dual-Access On-Chip RAM Blocks

D

Validated Ada Compiler

D

64-Word × 32-Bit Instruction Cache

D

32-Bit Instruction and Data Words,

24-Bit Addresses

D

40 / 32-Bit Floating-Point /Integer Multiplier

and Arithmetic Logic Unit (ALU)

D

Parallel ALU and Multiplier Execution in a

Single Cycle

D

On-Chip Direct Memory Access (DMA)

Controller for Concurrent I/O and CPU

Operation

D

Integer, Floating-Point, and Logical

Operations

D

One 4K-Word × 32-Bit Single-Cycle

Dual-Access On-Chip ROM Block

D

Two 32-Bit External Ports

(24- and 13-Bit Address)

D

T wo Serial Ports With Support for

8- / 16- /24- /32-Bit Transfers

D

Packaging

– 181-Pin Grid Array Ceramic Package

(GB Suffix)

– 196-Pin Ceramic Quad Flatpack With

Nonconductive Tie-Bar (HFG Suffix)

D

SMD Approval for 40- and 50-MHz Versions

D

T wo Address Generators With Eight

Auxiliary Registers and Two Auxiliary

Register Arithmetic Units (ARAUs)

D

Zero-Overhead Loops With Single-Cycle

Branches

D

Interlocked Instructions for

Multiprocessing Support

D

32-Bit Barrel Shifter

D

Eight Extended-Precision Registers

(Accumulators)

D

Two- and Three-Operand Instructions

D

Conditional Calls and Returns

D

Block Repeat Capability

D

Fabricated Using Enhanced Performance

Implanted CMOS (EPICt) by Texas

Instruments (TIt)

D

Two 32-Bit Timers

description

The SMJ320C30 internal busing and special digital signal processor (DSP) instruction set has the speed and

flexibility to execute up to 50 MFLOPS. The SMJ320C30 device optimizes speed by implementing functions

in hardware that other processors implement through software or microcode. This hardware-intensive approach

provides performance previously unavailable on a single chip. The emphasis on total system cost has resulted

in a less expensive processor that can be designed into systems currently using costly bit-slice processors.

D

SMJ320C30-40: 50-ns single-cycle execution time, 5% supply

D

SMJ320C30-50: 40-ns single-cycle execution time, 5% supply

Copyright 1998, Texas Instruments Incorporated

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

EPIC and TI are trademarks of Texas Instruments Incorporated.

On products compliant to MIL-PRF-38535, all parameters are tested

unless otherwise noted. On all other products, production

processing does not necessarily include testing of all parameters.

SMJ320C30

DIGITAL SIGNAL PROCESSOR

SGUS014F – FEBRUARY 1991 – REVISED FEBRUARY 1999

2

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

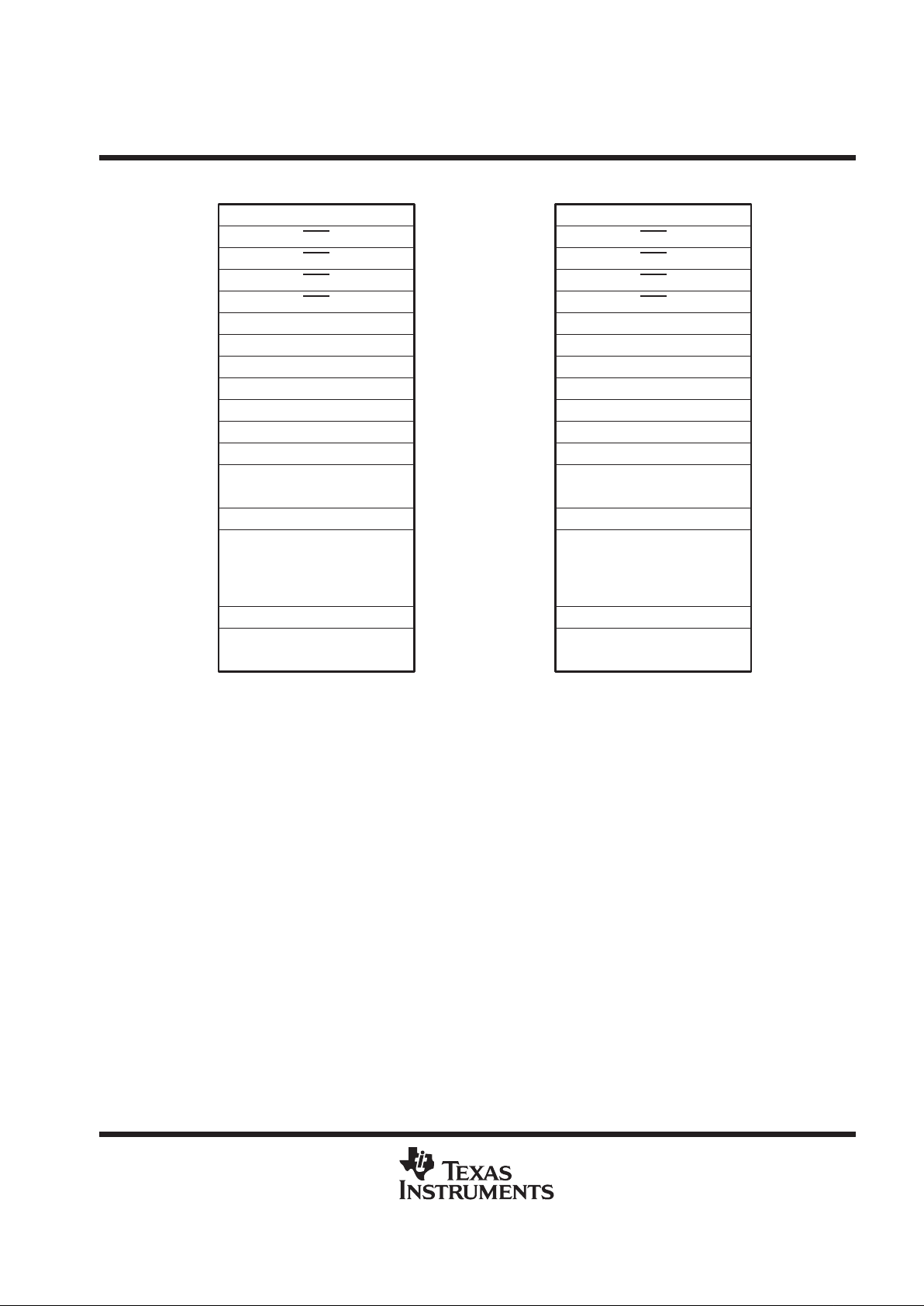

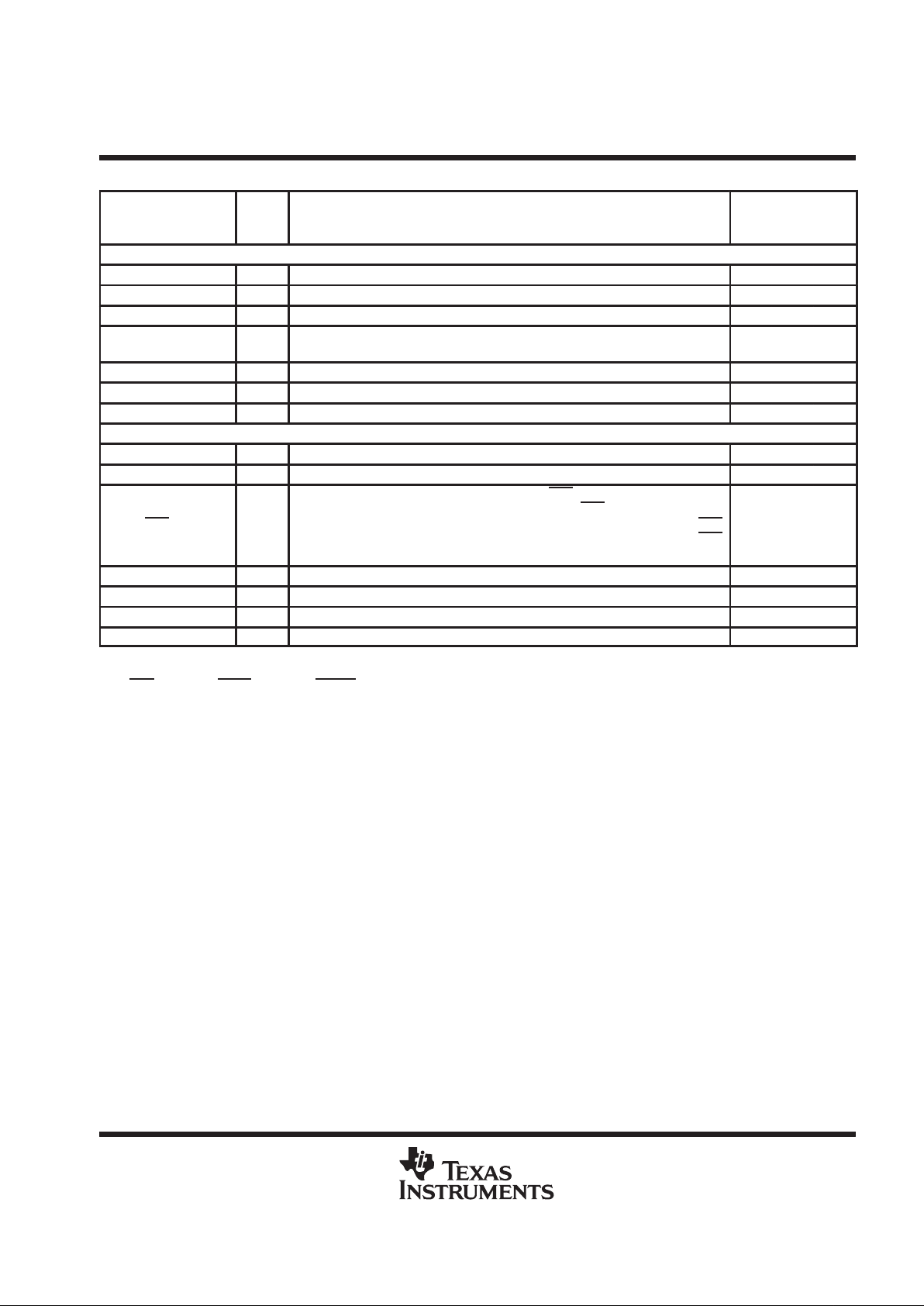

ABCDEFGHJKLMNPR

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

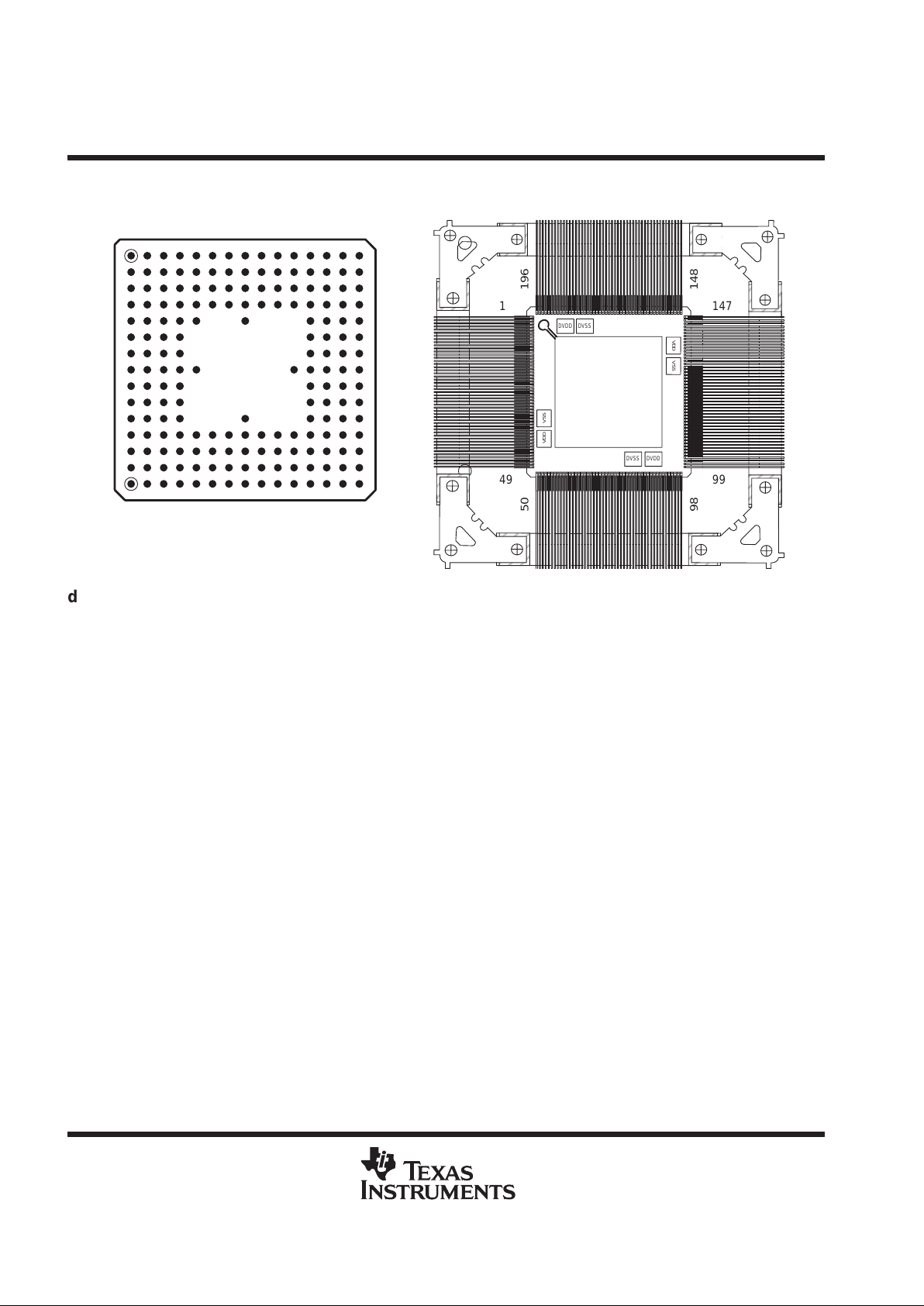

181-Pin GB Grid Array Package

(BOTTOM VIEW)

196-Pin HFG Quad Flatpack

(TOP VIEW)

DVDD DVSS

VDD

DVSS DVDD

VSS

VSSVDD

148

1471

196

98

50

9949

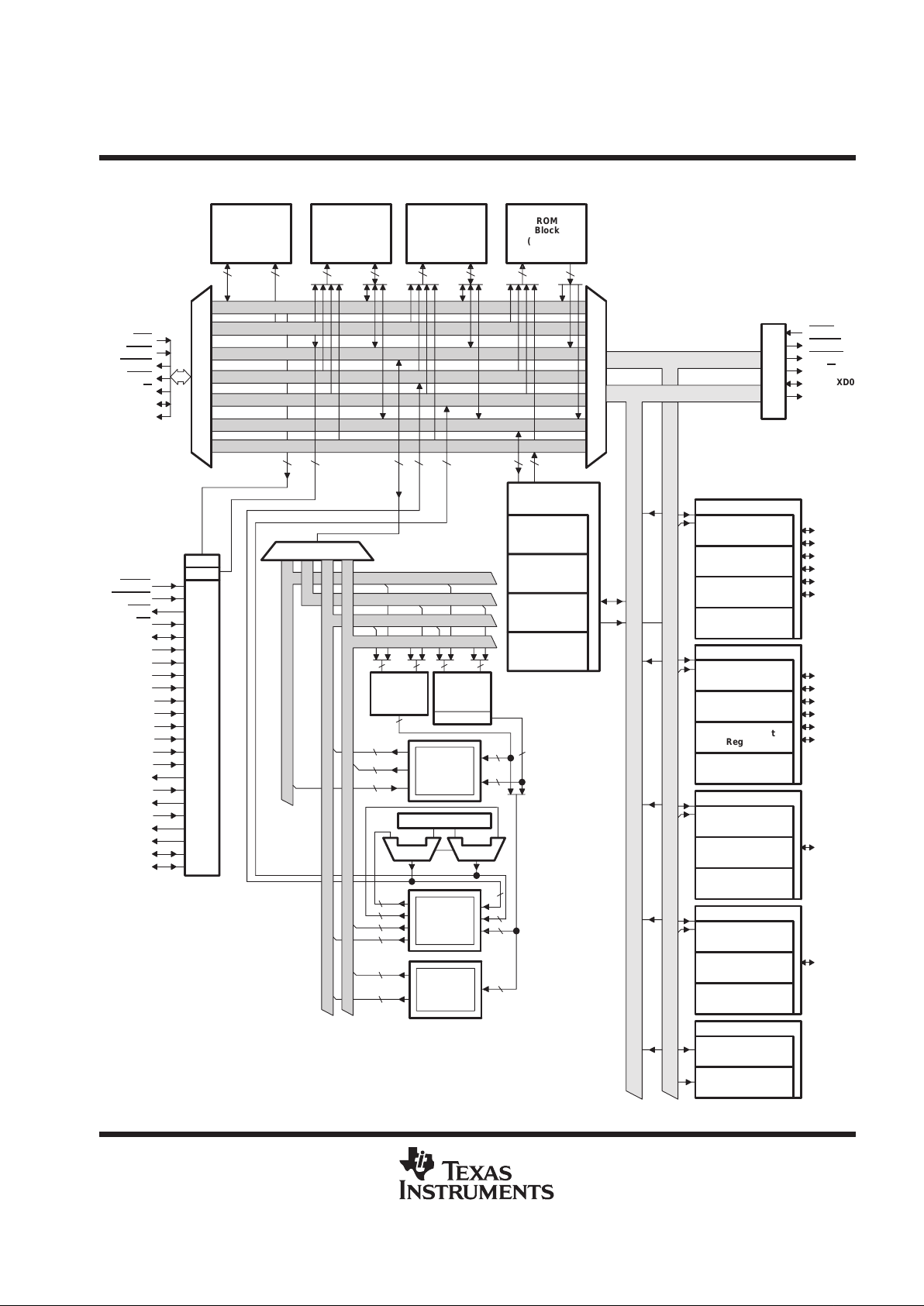

description (continued)

The SMJ320C30 can perform parallel multiply and ALU operations on integer or floating-point data in a single

cycle. Each processor also possesses a general-purpose register file, a program cache, dedicated ARAUs,

internal dual-access memories, one DMA channel supporting concurrent I/O, and a short machine-cycle time.

High performance and ease of use are results of these features.

General-purpose applications are enhanced by the large address space, multiprocessor interface, internally

and externally generated wait states, two external interface ports, two timers, two serial ports, and multiple

interrupt structure. The SMJ320C30 supports a wide variety of system applications from host processor to

dedicated coprocessor.

High-level language support is implemented easily through a register-based architecture, large address space,

powerful addressing modes, flexible instruction set, and well-supported floating-point arithmetic.

SMJ320C30

DIGITAL SIGNAL PROCESSOR

SGUS014F – FEBRUARY 1991 – REVISED FEBRUARY 1999

3

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

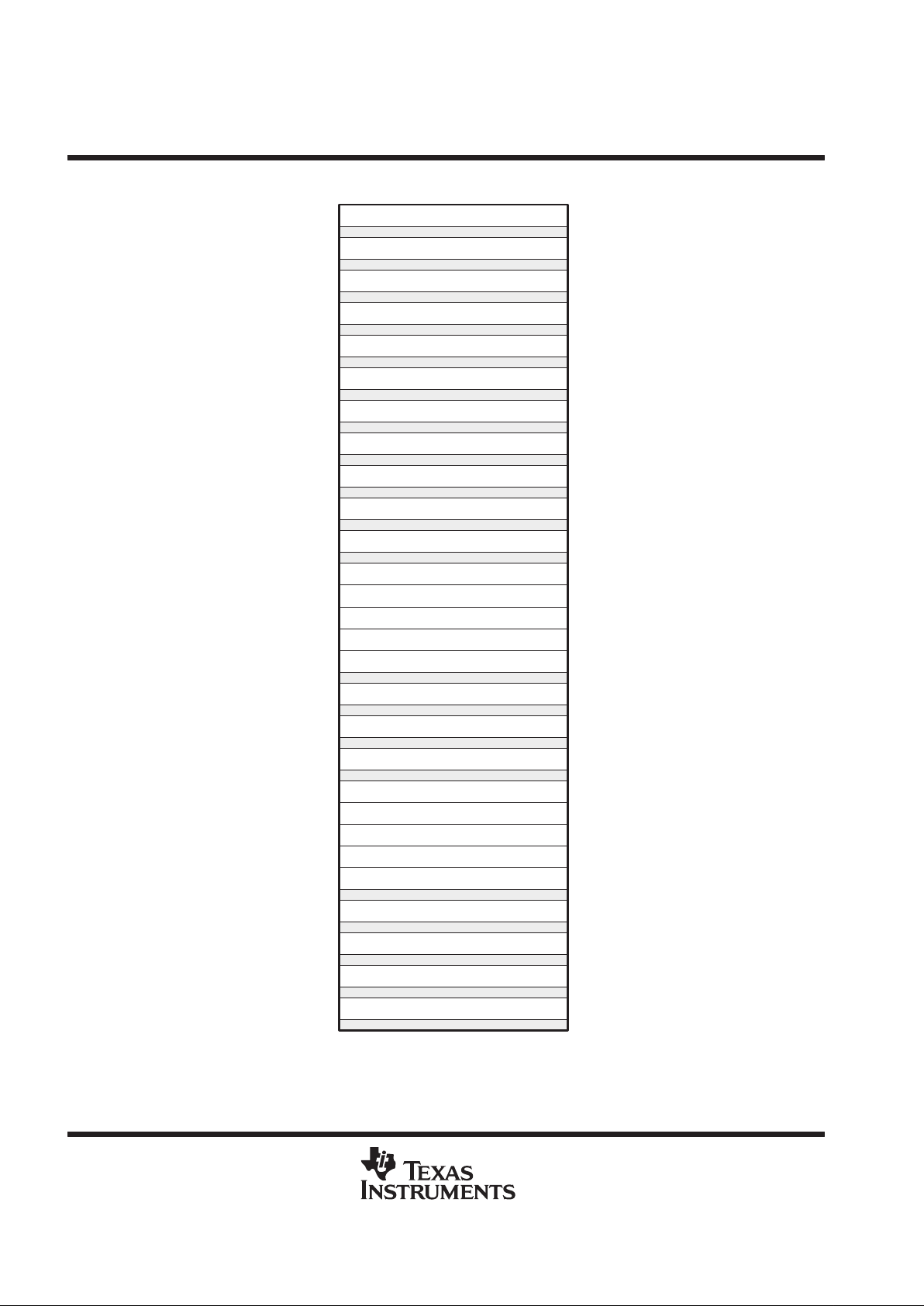

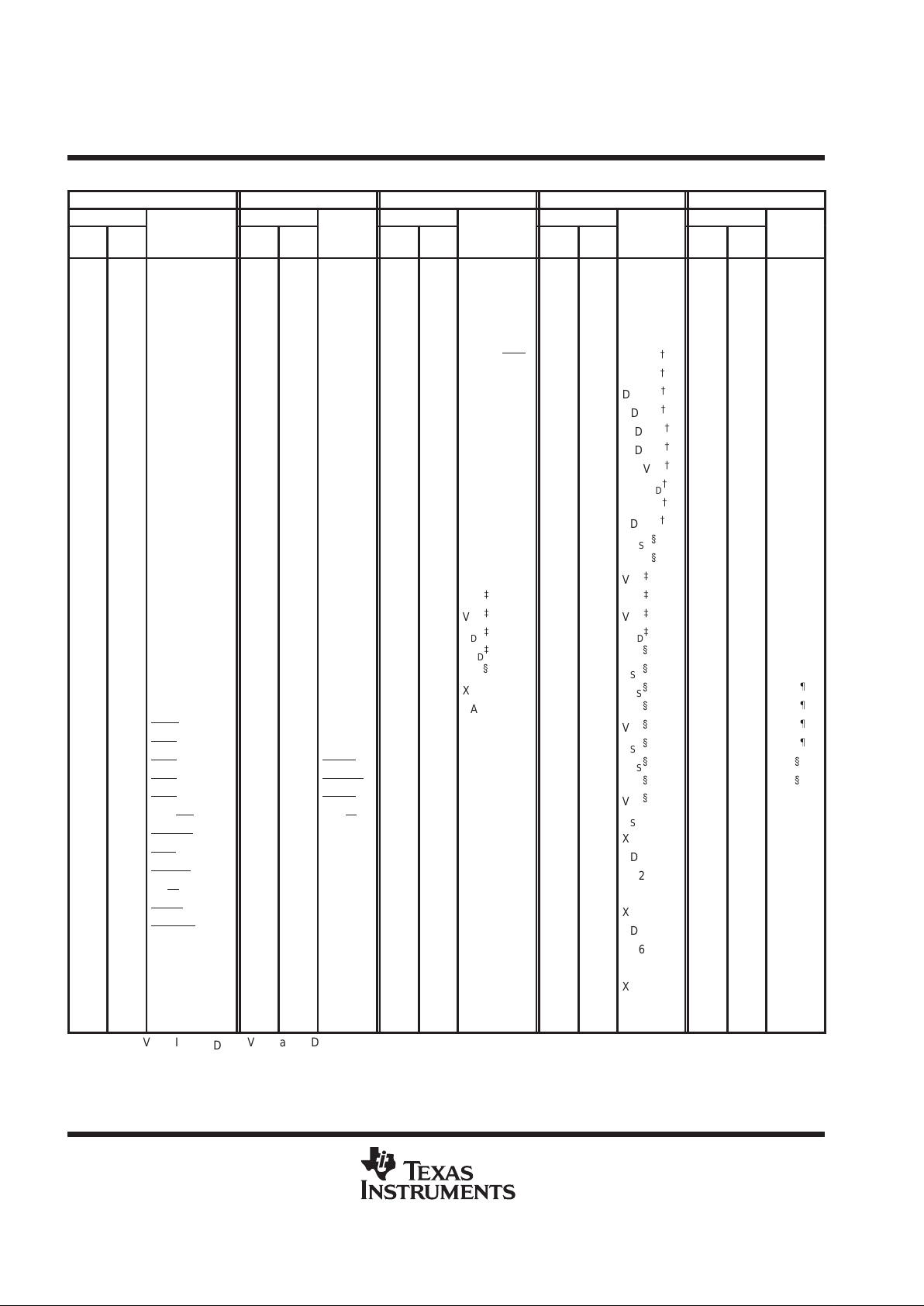

functional block diagram

ROM

Block

(4K

× 32)

Cache

(64

× 32)

RAM

Block 0

(1K

× 32)

RAM

Block 1

(1K

× 32)

RDY

HOLD

HOLDA

STRB

R/W

D31–D0

A23–A0

RESET

IR

PC

CPU1

REG1

REG2

XRDY

MSTRB

IOSTRB

XR/W

XD31–XD0

XA12–XA

0

MUX

40

32

32

32

32

32

32

32

24

24

24

24

BK

ARAU0 ARAU1

DISP0, IR0, IR1

Extended-

Precision

Registers

(R7–R0)

Auxiliary

Registers

(AR0–AR7)

Other

Registers

(12)

40

40

40

40

Multiplier

32-Bit

Barrel

Shifter

ALU

DMA Controller

Global-Control

Register

Source-Address

Register

Destination-

Address

Register

Serial Port 0

Serial-Port-Control

Register

Receive/Transmit

(R/X) Timer Register

Data-Transmit

Register

Data-Receive

Register

FSX0

DX0

CLKX0

FSR0

DR0

CLKR0

Serial Port 1

Data-Transmit

Register

Data-Receive

Register

FSX1

DX1

CLKX1

FSR1

DR1

CLKR1

Timer 0

Global-Control

Register

Timer-Period

Register

Timer-Counter

Register

TCLK0

Timer 1

Global-Control

Register

Timer-Period

Register

Timer-Counter

Register

TCLK1

Port Control

Primary-Control

Register

Expansion-Control

Register

Transfer-

Counter

Register

PDATA Bus

PADDR Bus

DDATA Bus

DADDR1 Bus

DADDR2 Bus

DMADATA Bus

DMAADDR Bus

24

40

32 32 24 24 32 24

INT(3–0)

IACK

MC/MP

XF(1,0)

V

DD

IODV

DD

ADV

DD

PDV

DD

DDV

DD

MDV

DD

V

SS

DV

SS

CV

SS

IV

SS

V

BBP

V

SUBS

X1

X2/CLKIN

H1

H3

EMU(6–0)

RSV(10–0)

32 24 24 24 2432 32 32

CPU2

32 32 40 40

Serial-Port-Control

Register

MUX

Controller

Peripheral Data Bus

Peripheral Address Bus

CPU1

REG1

REG2

MUX

Receive/Transmit

(R/X) Timer Register

SMJ320C30

DIGITAL SIGNAL PROCESSOR

SGUS014F – FEBRUARY 1991 – REVISED FEBRUARY 1999

4

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

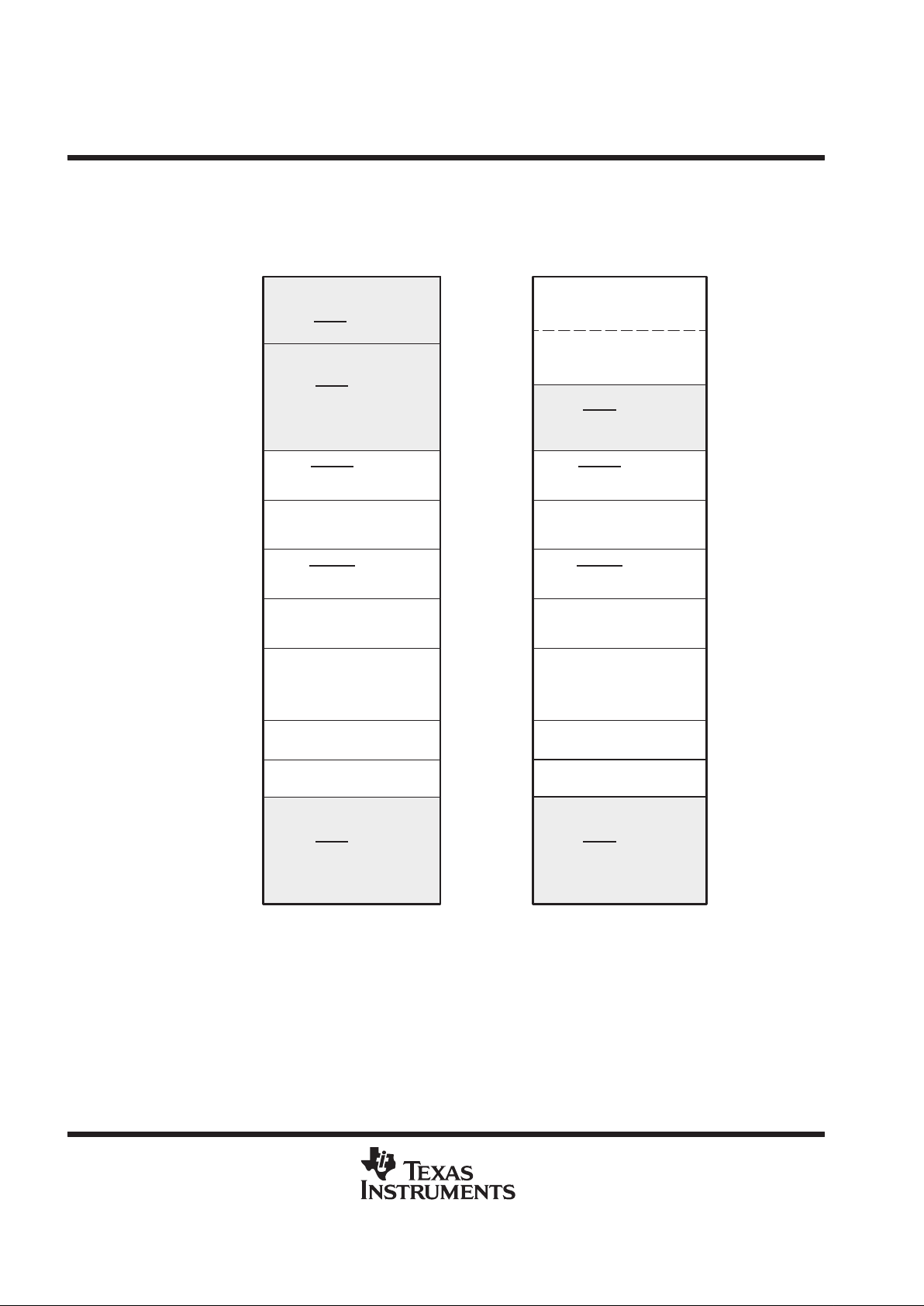

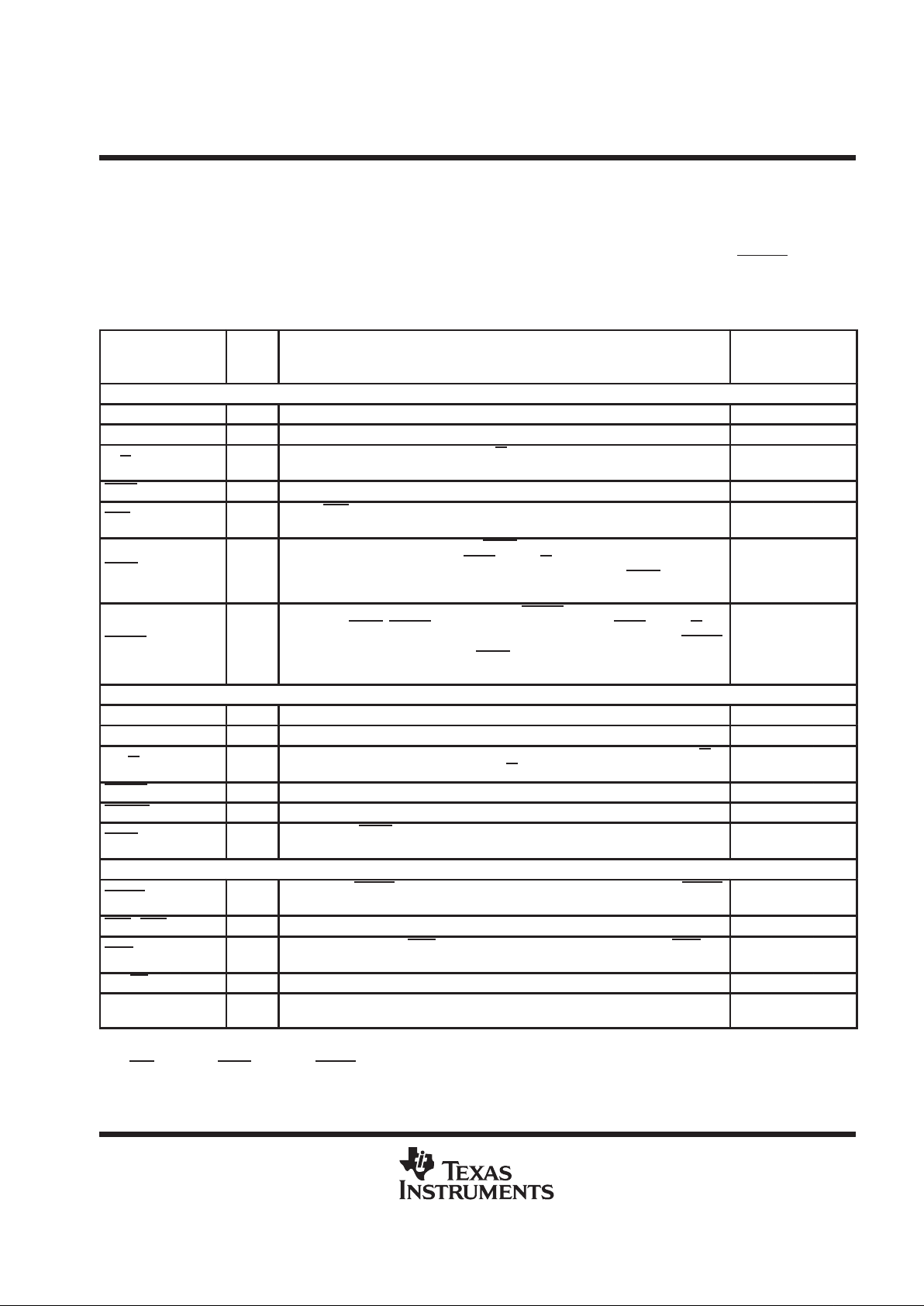

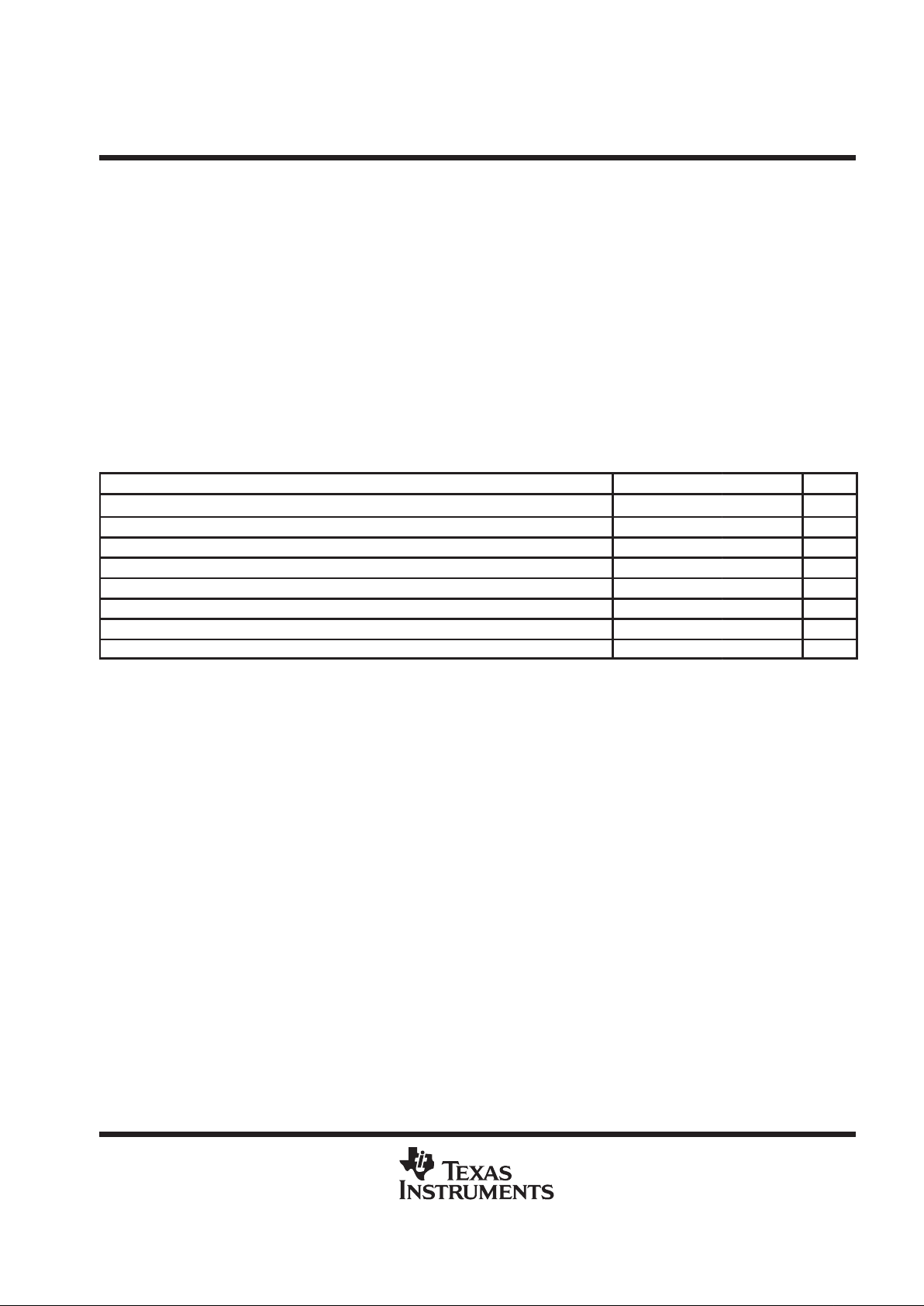

memory map

Figure 1 shows the memory map for the SMJ320C30. See the

TMS320C3x User’s Guide

(literature number

SPRU031) for a detailed description of this memory mapping. Figure 2 shows the reset, interrupt, and trap

vector/branches memory-map locations. Figure 3 shows the peripheral bus memory-mapped registers.

Expansion-Bus

IOSTRB Active

(8K Words)

Reserved

(8K Words)

Expansion-Bus

IOSTRB

Active

(8K Words)

Reserved

(8K Words)

Expansion-Bus

MSTRB

Active

(8K Words)

Expansion-Bus

MSTRB Active

(8K Words)

Reset, Interrupt, Trap

Vectors, and Reserved

Locations (64) (External

STRB

Active)

0h

03Fh

040h

7FFFFFh

800000h

801FFFh

Reserved

(8K Words)

802000h

803FFFh

804000h

805FFFh

806000h

807FFFh

808000h

Peripheral-Bus

Memory-Mapped

Registers

(6K Words Internal)

8097FFh

RAM Block 0

(1K Word Internal)

809800h

809BFFh

RAM Block 1

(1K Word Internal)

809C00h

809FFFh

External

STRB Active

(8M Words – 40K Words)

80A000h

0FFFFFFh

Reset, Interrupt,

Trap V ectors, and Reserved

Locations (192)

0h

0BFh

7FFFFFh

800000h

801FFFh

Reserved

(8K Words)

802000h

803FFFh

804000h

805FFFh

806000h

807FFFh

808000h

Peripheral-Bus

Memory-Mapped

Registers

(6K Words Internal)

8097FFh

RAM Block 0

(1K Word Internal)

809800h

809BFFh

RAM Block 1

(1K Word Internal)

809C00h

809FFFh

80A000h

0FFFFFFh

(a) Microprocessor Mode (b) Microcomputer Mode

ROM

(Internal)

0C0h

0FFFh

External

STRB Active

(8M Words – 4K Words)

1000h

External

STRB Active

(8M Words – 40K Words)

External

STRB

Active

(8M Words – 64 Words)

Figure 1. Memory Map

SMJ320C30

DIGITAL SIGNAL PROCESSOR

SGUS014F – FEBRUARY 1991 – REVISED FEBRUARY 1999

5

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

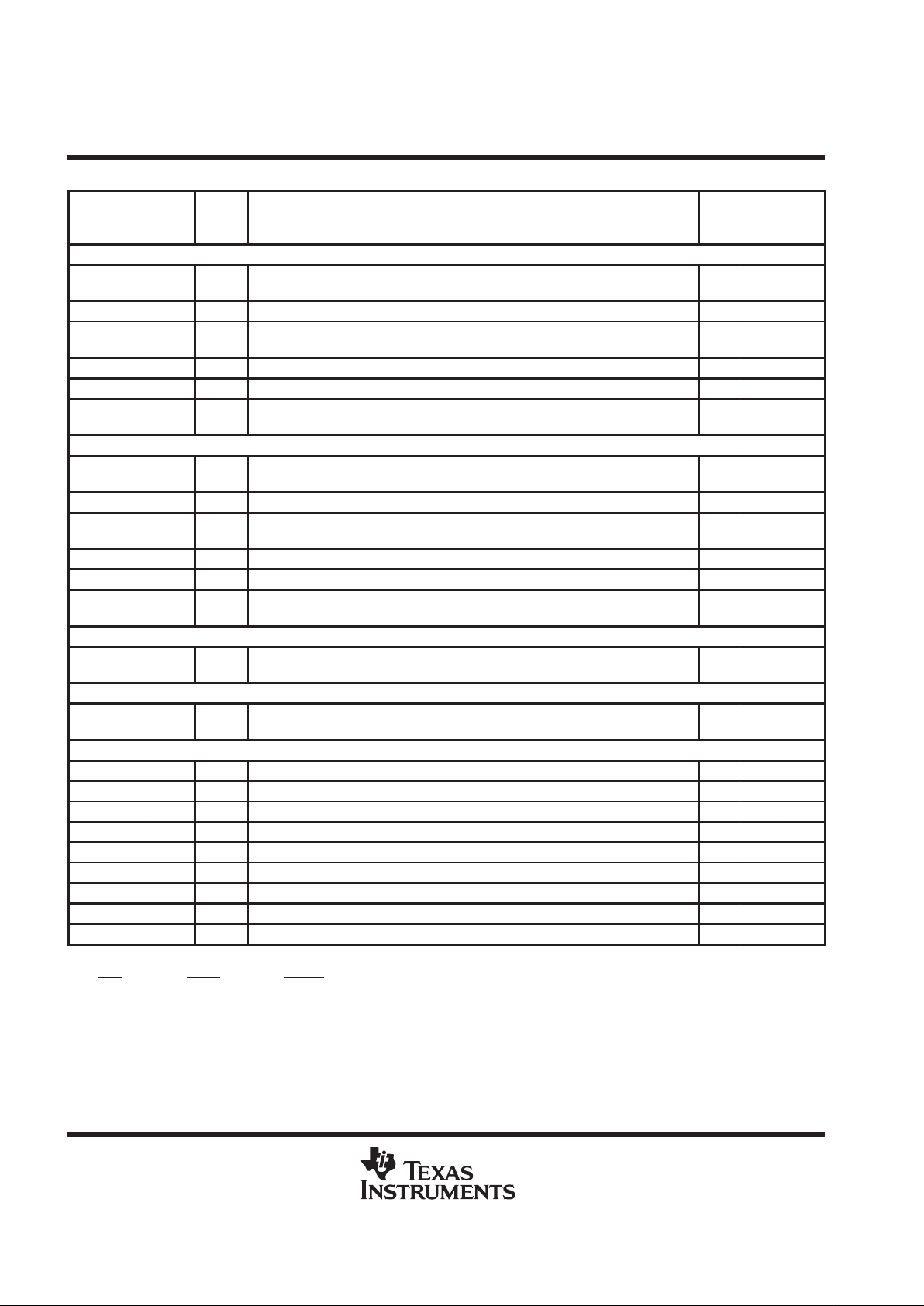

memory map (continued)

00h

01h

02h

03h

04h

05h

06h

07h

08h

09h

0Ah

0Bh

0Ch

1Fh

20h

3Bh

3Ch

3Fh

Reset

INT0

INT1

INT2

INT3

XINT0

RINT0

XINT1

RINT1

TINT0

TINT1

DINT

Reserved

TRAP 0

.

.

.

TRAP 27

Reserved

00h

01h

02h

03h

04h

05h

06h

07h

08h

09h

0Ah

0Bh

0Ch

1Fh

20h

3Bh

3Ch

BFh

Reset

INT0

INT1

INT2

INT3

XINT0

RINT0

XINT1

RINT1

TINT0

TINT1

DINT

Reserved

TRAP 0

.

.

.

TRAP 27

Reserved

(a) Microprocessor Mode (a) Microcomputer Mode

Figure 2. Reset, Interrupt, and Trap Vector/Branches Memory-Map Locations

SMJ320C30

DIGITAL SIGNAL PROCESSOR

SGUS014F – FEBRUARY 1991 – REVISED FEBRUARY 1999

6

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

memory map (continued)

FSX/DX/CLKX Serial Port 0 Control

FSR/DR/CLKR Serial Port 0 Control

Serial Port 0 R/X Timer Control

Serial Port 0 R/X Timer Counter

Serial Port 0 R/X Timer Period

Serial Port 0 Data Transmit

Serial Port 0 Data Receive

Serial Port 1 Global Control

FSX/DX/CLKX Serial Port 1 Control

FSR/DR/CLKR Serial Port 1 Control

Serial Port 1 R/X Timer Control

Serial Port 1 R/X Timer Counter

Serial Port 1 R/X Timer Period

Serial Port 1 Data Transmit

Serial Port 1 Data Receive

Expansion-Bus Control

Primary-Bus Control

DMA Global Control

DMA Source Address

DMA Destination Address

DMA Transfer Counter

Timer 0 Global Control

Timer 0 Counter

Timer 0 Period

Timer 1 Global Control

Timer 1 Counter

Timer 1 Period Register

Serial Port 0 Global Control

808000h

808004h

808006h

808008h

808020h

808024h

808028h

808030h

808034h

808038h

808040h

808042h

808043h

808044h

808045h

808046h

808048h

80804Ch

808050h

808052h

808053h

808054h

808055h

808056h

808058h

80805Ch

808060h

808064h

†

Shading denotes reserved address locations

Figure 3. Peripheral Bus Memory-Mapped Registers

†

SMJ320C30

DIGITAL SIGNAL PROCESSOR

SGUS014F – FEBRUARY 1991 – REVISED FEBRUARY 1999

7

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

pin functions

This section gives signal descriptions for the SMJ320C30 devices in the microprocessor mode. The following

tables list each signal, the number of pins, type of operating mode(s) (that is, input, output, or high-impedance

state as indicated by I, O, or Z, respectively), and a brief function description. All pins labeled NC have special

functions and should not be connected by the user. A line over a signal name (for example, RESET

) indicates

that the signal is active low (true at logic-0 level). The signals are grouped according to functions.

Pin Functions

PIN

CONDITIONS

NAME QTY

‡

TYPE

†

DESCRIPTION

WHEN

SIGNAL IS Z TYPE

§

PRIMARY BUS INTERFACE

D31–D0 32 I/O/Z 32-bit data port of the primary bus interface S H

A23–A0 24 O/Z 24-bit address port of the primary bus interface S H R

R/W 1 O/Z

Read/write for primary bus interface. R/W is high when a read is performed and low

when a write is performed over the parallel interface.

S H R

STRB 1 O/Z External access strobe for the primary bus interface S H

RDY 1 I

Ready. RDY indicates that the external device is prepared for a primary bus interface

transaction to complete.

HOLD 1 I

Hold for primary bus interface. When HOLD is a logic low, any ongoing transaction

is completed. A23–A0, D31–D0, STRB

, and R/W are in the high-impedance state

and all transactions over the primary bus interface are held until HOLD

becomes a

logic high or the NOHOLD bit of the primary bus control register is set.

HOLDA 1 O/Z

Hold acknowledge for primary bus interface. HOLDA is generated in response to a

logic low on HOLD

. HOLDA indicates that A23–A0, D31–D0, STRB, and R/W are

in the high-impedance state and that all transactions over the bus are held. HOLDA

is high in response to a logic high of HOLD or when the NOHOLD bit of the primary

bus control register is set.

S

EXPANSION BUS INTERFACE

XD31–XD0 32 I/O/Z 32-bit data port of the expansion bus interface S R

XA12–XA0 13 O/Z 13-bit address port of the expansion bus interface S R

XR/W 1 O/Z

Read/write signal for expansion bus interface. When a read is performed, XR/W is

held high; when a write is performed, XR/W

is low.

S R

MSTRB 1 O/Z External memory access strobe for the expansion bus interface S

IOSTRB 1 O/Z External I/O access strobe for the expansion bus interface S

XRDY 1 I

Ready signal. XRDY indicates that the external device is prepared for an expansion

bus interface transaction to complete.

CONTROL SIGNALS

RESET 1 I

Reset. When RESET is a logic low, the device is in the reset condition. When RESET

becomes a logic high, execution begins from the location specified by the reset vector.

INT3–INT0 4 I External interrupts

IACK 1 O/Z

Interrupt acknowledge. IACK is set to a logic high by the IACK instruction. IACK can

be used to indicate the beginning or end of an interrupt-service routine.

S

MC/MP 1 I Microcomputer/microprocessor mode

XF1, XF0 2 I/O/Z

External flags. XF1 and XF0 are used as general-purpose I/Os or to support

interlocked processor instructions.

S R

†

I = input, O = output, Z = high-impedance state, NC = no connect

‡

For GB package

§

S = SHZ

active, H = HOLD active, R = RESET active

SMJ320C30

DIGITAL SIGNAL PROCESSOR

SGUS014F – FEBRUARY 1991 – REVISED FEBRUARY 1999

8

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

Pin Functions (Continued)

PIN

CONDITIONS

NAME QTY

‡

TYPE

†

DESCRIPTION

WHEN

SIGNAL IS Z TYPE

§

SERIAL PORT 0 SIGNALS

CLKX0 1 I/O/Z

Serial port 0 transmit clock. CLKX0 is the serial-shift clock for the serial port 0

transmitter.

S R

DX0 1 I/O/Z Data transmit output. Serial port 0 transmits serial data on DX0. S R

FSX0 1 I/O/Z

Frame synchronization pulse for transmit. The FSX0 pulse initiates the transmit-data

process over DX0.

S R

CLKR0 1 I/O/Z Serial port 0 receive clock. CLKR0 is the serial-shift clock for the serial port 0 receiver. S R

DR0 1 I/O/Z Data receive. Serial port 0 receives serial data on DR0. S R

FSR0 1 I/O/Z

Frame synchronization pulse for receive. The FSR0 pulse initiates the receive-data

process over DR0.

S R

SERIAL PORT 1 SIGNALS

CLKX1 1 I/O/Z

Serial port 1 transmit clock. CLKX1 is the serial-shift clock for the serial port 1

transmitter.

S R

DX1 1 I/O/Z Data transmit output. Serial port 1 transmits serial data on DX1. S R

FSX1 1 I/O/Z

Frame synchronization pulse for transmit. The FSX1 pulse initiates the transmit-data

process over DX1.

S R

CLKR1 1 I/O/Z Serial port 1 receive clock. CLKR1 is the serial-shift clock for the serial port 1 receiver. S R

DR1 1 I/O/Z Data receive. Serial port 1 receives serial data on DR1. S R

FSR1 1 I/O/Z

Frame synchronization pulse for receive. The FSR1 pulse initiates the receive-data

process over DR1.

S R

TIMER 0 SIGNALS

TCLK0 1 I/O/Z

Timer clock 0. As an input, TCLK0 is used by timer 0 to count external pulses. As an

output, TCLK0 outputs pulses generated by timer 0.

S R

TIMER 1 SIGNALS

TCLK1 1 I/O/Z

Timer clock 1. As an input, TCLK1 is used by timer 1 to count external pulses. As an

output, TCLK1 outputs pulses generated by timer 1.

S R

SUPPLY AND OSCILLATOR SIGNALS (see Note 1)

V

DD

4 I 5-V supply

¶

IODV

DD

2 I 5-V supply

¶

ADV

DD

2 I 5-V supply

¶

PDV

DD

1 I 5-V supply

¶

DDV

DD

2 I 5-V supply

¶

MDV

DD

1 I 5-V supply

¶

V

SS

4 I Ground

DV

SS

4 I Ground

CV

SS

2 I Ground

†

I = input, O = output, Z = high-impedance state, NC = no connect

‡

For GB package

§

S = SHZ

active, H = HOLD active, R = RESET active

¶

Recommended decoupling capacitor is 0.1 µF.

NOTE 1: CVSS, VSS, and IVSS are on the same plane.

SMJ320C30

DIGITAL SIGNAL PROCESSOR

SGUS014F – FEBRUARY 1991 – REVISED FEBRUARY 1999

9

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

Pin Functions (Continued)

PIN

CONDITIONS

NAME QTY

‡

TYPE

†

DESCRIPTION

WHEN

SIGNAL IS Z TYPE

§

SUPPLY AND OSCILLATOR SIGNALS (see Note 1) (CONTINUED)

IV

SS

1 I Ground

V

BBP

1 NC VBB pump oscillator output

V

SUBS

1 I Substrate pin. Tie to ground

X1 1 O

Output from the internal oscillator for the crystal. If a crystal is not used, X1 must

be left unconnected.

X2/CLKIN 1 I Input to the internal oscillator from the crystal or a clock

H1 1 O/Z External H1 clock. H1 has a period equal to twice CLKIN. S

H3 1 O/Z External H3 clock. H3 has a period equal to twice CLKIN. S

RESERVED (see Note 2)

EMU0–EMU2 3 I Reserved. Use pullup resistors to 5 V

EMU3 1 O/Z Reserved S

EMU4/SHZ 1 I

Shutdown high impedance. When active, EMU4/SHZ shuts down the SMJ320C30

and places all pins in the high-impedance state. EMU4/SHZ

is used for board-level

testing to ensure that no dual-drive conditions occur. CAUTION: A low on SHZ

corrupts SMJ320C30 memory and register contents. Reset the device with SHZ

high to restore it to a known operating condition.

EMU5, EMU6 2 NC Reserved

RSV0–RSV4 5 I Reserved. Tie pins directly to 5 V

RSV5–RSV10 6 I/O Reserved. Use pullups on each pin to 5 V

Locator 1 NC Reserved

†

I = input, O = output, Z = high-impedance state, NC=No Connect

‡

For GB package

§

S = SHZ

active, H = HOLD active, R = RESET active

NOTES: 1. CVSS, VSS, IVSS are on the same plane.

2. The connections specified for the reserved pins must be followed. For best results, 18-kΩ–22-kΩ pullup resistors are

recommended. All 5-V supply pins must be connected to a common supply plane, and all ground pins must be connected to a

common ground plane.

SMJ320C30

DIGITAL SIGNAL PROCESSOR

SGUS014F – FEBRUARY 1991 – REVISED FEBRUARY 1999

10

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

Pin Assignments

PIN PIN PIN PIN PIN

NUMBER NUMBER NUMBER NUMBER NUMBER

GB

PKG

HFG

PKG

NAME

GB

PKG

HFG

PKG

NAME

GB

PKG

HFG

PKG

NAME

GB

PKG

HFG

PKG

NAME

GB

PKG

HFG

PKG

NAME

F15

G12

G13

G14

G15

H15

H14

J15

J14

J13

K15

J12

K14

L15

K13

L14

M15

K12

L13

M14

N15

M13

L12

N14

E5

G1

H2

H1

J1

J2

D15

E3

E1

F1

G4

F2

F4

C4

D5

A2

A3

B4

82

81

80

79

78

77

72

71

70

69

68

67

66

65

63

62

61

60

59

58

57

56

55

54

170

171

176

177

178

88

157

164

167

166

165

158

144

143

142

141

140

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

LOCATOR/NC

IACK

INT0

INT1

INT2

INT3

MC/MP

MSTRB

RDY

RESET

R/ W

STRB

IOSTRB

D0

D1

D2

D3

D4

C5

D6

A4

B5

C6

A5

B6

D7

A6

C7

B7

A7

A8

B8

A9

B9

C9

A10

D9

B10

A11

C10

B11

A12

D10

C11

B12

F3

E2

D2

D1

P3

R2

N4

M5

R1

R3

M3

P1

L4

N2

N1

139

138

137

136

135

134

133

132

131

130

129

128

127

122

121

120

119

118

117

116

115

113

112

111

110

109

108

161

160

156

159

4

7

5

6

3

8

191

194

192

193

190

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D30

D31

HOLD

HOLDA

XRDY

XR/W

FSR0

FSX0

CLKR0

CLKX0

DR0

DX0

FSR1

FSX1

CLKR1

CLKX1

DR1

P2

F14

E15

F13

E14

F12

C1

M6

B3

A1

C2

B1

P4

N5

G2

G3

D3

E4

H4

D8

M8

H12

N8

A13

A14

D11

C12

B13

A15

B15

C14

E12

D13

C15

D14

E13

J3

J4

K1

K2

L1

K3

195

83

84

85

86

87

155

11

145

146

152

151

9

10

169

168

154

153

123

73

74

124

27

107

106

105

104

103

102

95

94

93

92

91

90

89

179

180

181

182

183

184

DX1

EMU0

EMU1

EMU2

EMU3

EMU4/SHZ

EMU5

EMU6

H1

H3

X1

X2/CLKIN

TCLK0

TCLK1

XF0

XF1

V

BBP

V

SUBS

V

DD

}

V

DD

}

V

DD

}

V

DD

}

V

SS

w

XA0

XA1

XA2

XA3

XA4

XA5

XA6

XA7

XA8

XA9

XA10

XA11

XA12

RSV0

RSV1

RSV2

RSV3

RSV4

RSV5

L2

K4

M1

L3

M2

D12

H11

D4

E8

L8

M12

H5

M4

B2

P14

C8

H3

H13

R4

P5

N6

R5

P6

M7

R6

N7

P7

R7

P8

185

186

187

188

189

100

64

114

147

15

16

49

162

163

1

51

52

25

26

172

173

28

75

76

125

126

149

150

174

175

99

12

13

14

17

18

19

20

21

22

23

24

RSV6

RSV7

RSV8

RSV9

RSV10

ADV

DD

{

ADV

DD

{

DDV

DD

{

DDV

DD

{

IODV

DD

{

IODV

DD

{

IODV

DD

{

MDV

DD

{

MDV

DD

{

PDV

DD

{

CV

SS

w

CV

SS

w

V

DD

}

V

DD

}

V

DD

}

V

DD

}

V

SS

w

V

SS

w

V

SS

w

V

SS

w

V

SS

w

V

SS

w

V

SS

w

V

SS

w

V

SS

w

V

SUBS

XD0

XD1

XD2

XD3

XD4

XD5

XD6

XD7

XD8

XD9

XD10

R8

R9

P9

N9

R10

M9

P10

R11

N10

P11

R12

M10

N11

P12

R13

R14

M11

N12

P13

R15

P15

C3

C13

N3

N13

B14

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

53

2

101

50

98

148

196

96

97

XD11

XD12

XD13

XD14

XD15

XD16

XD17

XD18

XD19

XD20

XD21

XD22

XD23

XD24

XD25

XD26

XD27

XD28

XD29

XD30

XD31

DV

DD

DV

DD

DV

SS

W

DV

SS

W

DV

SS

W

DV

SS

W

IV

SS

w

IV

SS

w

†

ADVDD, DDVDD, IODVDD, MDVDD, and PDVDD are on a common plane internal to the device.

‡

VDD is on a common plane internal to the device.

§

VSS, CVSS, and IVSS are on a common plane internal to the device.

¶

DVSS is on a common plane internal to the device.

SMJ320C30

DIGITAL SIGNAL PROCESSOR

SGUS014F – FEBRUARY 1991 – REVISED FEBRUARY 1999

11

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

absolute maximum ratings over operating case temperature range (unless otherwise noted)

†

Supply voltage range, V

CC

(see Note 3) –0.3 V to 7 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Input voltage range, VI – 0.3 V to 7 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Output voltage range, VO –0.3 V to 7 V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Continuous power dissipation (see Note 4) 3.15 W. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Operating case temperature range, T

C

– 55°C to 125°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Storage temperature range, T

stg

– 65°C to 150°C. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

†

Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and

functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 3. All voltage values are with respect to VSS.

4. Actual operating power is less. This value was obtained under specially produced worst-case test conditions, which are not

sustained during normal device operation. These conditions consist of continuous parallel writes of a checkerboard pattern to both

primary and extension buses at the maximum rate possible. See normal (ICC) current specification in the electrical characteristics

table and also read

Calculation of TMS320C30 Power Dissipation Application Report

(literature number SPRA020)

.

recommended operating conditions (see Note 5)

MIN NOM

‡

MAX UNIT

pp

VDDSuppl

y v

oltage (AV

DD

,

etc.)

4.7555.25

V

V

SS

Supply voltage (CVSS, etc.) 0 V

V

IH

High-level input voltage 2.1 VDD+ 0.3* V

V

TH

High-level input voltage for CLKIN 3 VDD+ 0.3* V

V

IL

Low-level input voltage – 0.3* 0.8 V

I

OH

High-level output current – 300 µA

I

OL

Low-level output current 2 mA

T

C

Operating case temperature (see Note 6) – 55 125 °C

‡

All nominal values are at VDD = 5 V, TA (ambient-air temperature)= 25°C.

* This parameter is not production tested.

NOTE 5: All input and output voltage levels are TTL compatible.

NOTE 6: TC MAX at maximum rated operating conditions at any point on the case, TC MIN at initial (time zero) power up

SMJ320C30

DIGITAL SIGNAL PROCESSOR

SGUS014F – FEBRUARY 1991 – REVISED FEBRUARY 1999

12

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

electrical characteristics over recommended ranges of supply voltage (unless otherwise noted)

(see Note 5)

PARAMETER TEST CONDITIONS

†

MIN TYP‡MAX UNIT

V

OH

High-level output voltage VDD = MIN, IOH = MAX 2.4 3 V

p

For XA12–XA0 VDD = MIN, IOL = MAX 0.6* V

VOLLow-level output voltage

All others VDD = MIN, IOL = MAX 0.3 0.6 V

I

Z

High-impedance current VDD = MAX ± 20 µA

I

I

Input current VI = VSS to V

DD

± 10 µA

I

IP

Input current Inputs with internal pullups (see Note 7) – 600 20 µA

I

IC

Input current (X2/CLKIN) VI = VSS to V

DD

± 50 µA

pp

V

= MAX, T

= 25°C,

ICCSupply current

DD

,

A

,

t

c(CI)

= MIN, See Note 8

200

600

mA

I

DD

Supply current, standby; IDLE2, clock shut off VDD = 5 V, TA = 25°C 50 mA

C

i

Input capacitance 15* pF

C

o

Output capacitance 20* pF

C

x

X2/CLKIN capacitance 25* pF

†

For conditions shown as MIN/MAX, use the appropriate value specified in recommended operating conditions.

‡

All typical values are at VDD = 5 V, TA = 25°C.

* This parameter is not production tested.

NOTES: 5. All input and output voltage levels are TTL compatible.

7. Pins with internal pullup devices: INT0

– INT3, MC /MP, RSV0–RSV10. Although RSV0–RSV10 have internal pullup devices,

external pullups should be used on each pin as identified in the pin function tables.

8. Actual operating current is less than this maximum value. This value was obtained under specially produced worst-case test

conditions, which are not sustained during normal device operation. These conditions consist of continuous parallel writes of a

checkerboard pattern to both primary and expansion buses at the maximum rate possible. See

Calculation of TMS320C30 Power

Dissipation Application Report

(literature number SPRA020)

.

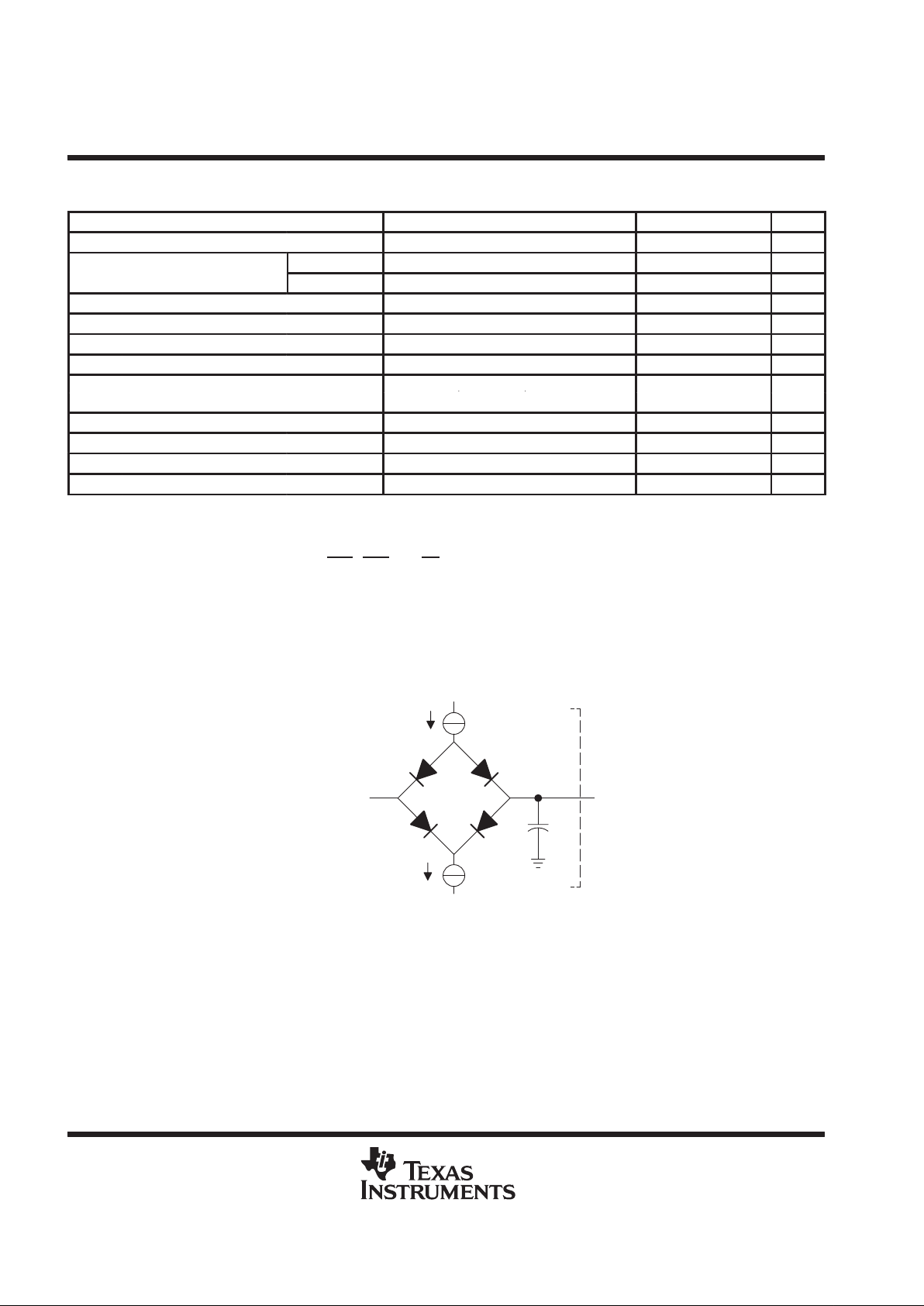

PARAMETER MEASUREMENT INFORMATION

Tester Pin

Electronics

V

LOAD

I

OL

C

T

I

OH

Output

Under

Test

Where: I

OL

= 2 mA (all outputs)

I

OH

= 300 µA (all outputs)

V

LOAD

= Selected to emulate 50 Ω termination (typical value = 1.54 V).

C

T

= 80-pF typical load-circuit capacitance

Figure 4. Test Load Circuit

SMJ320C30

DIGITAL SIGNAL PROCESSOR

SGUS014F – FEBRUARY 1991 – REVISED FEBRUARY 1999

13

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

PARAMETER MEASUREMENT INFORMATION

signal transition levels

TTL-level outputs are driven to a minimum logic-high level of 2.4 V and to a maximum logic-low level of 0.6 V .

Output transition times are specified as follows:

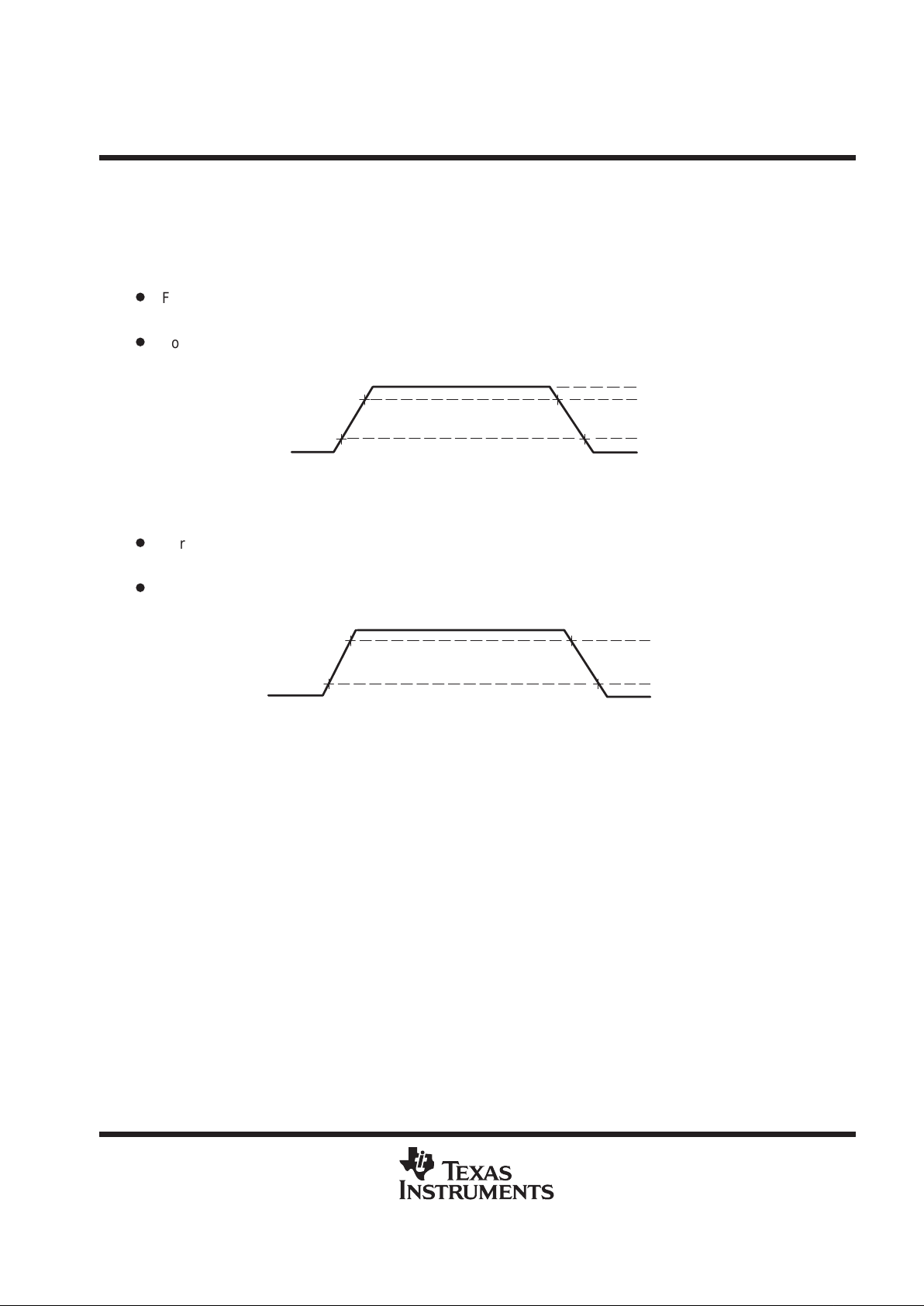

D

For a high-to-low transition on a TTL-compatible output signal, the level at which the output is said to be

no longer high is 2 V and the level at which the output is said to be low is 1 V.

D

For a low-to-high transition, the level at which the output is said to be no longer low is 1 V and the level at

which the output is said to be high is 2 V.

0.6 V

1 V

2 V

2.4 V

Figure 5. TTL-Level Outputs

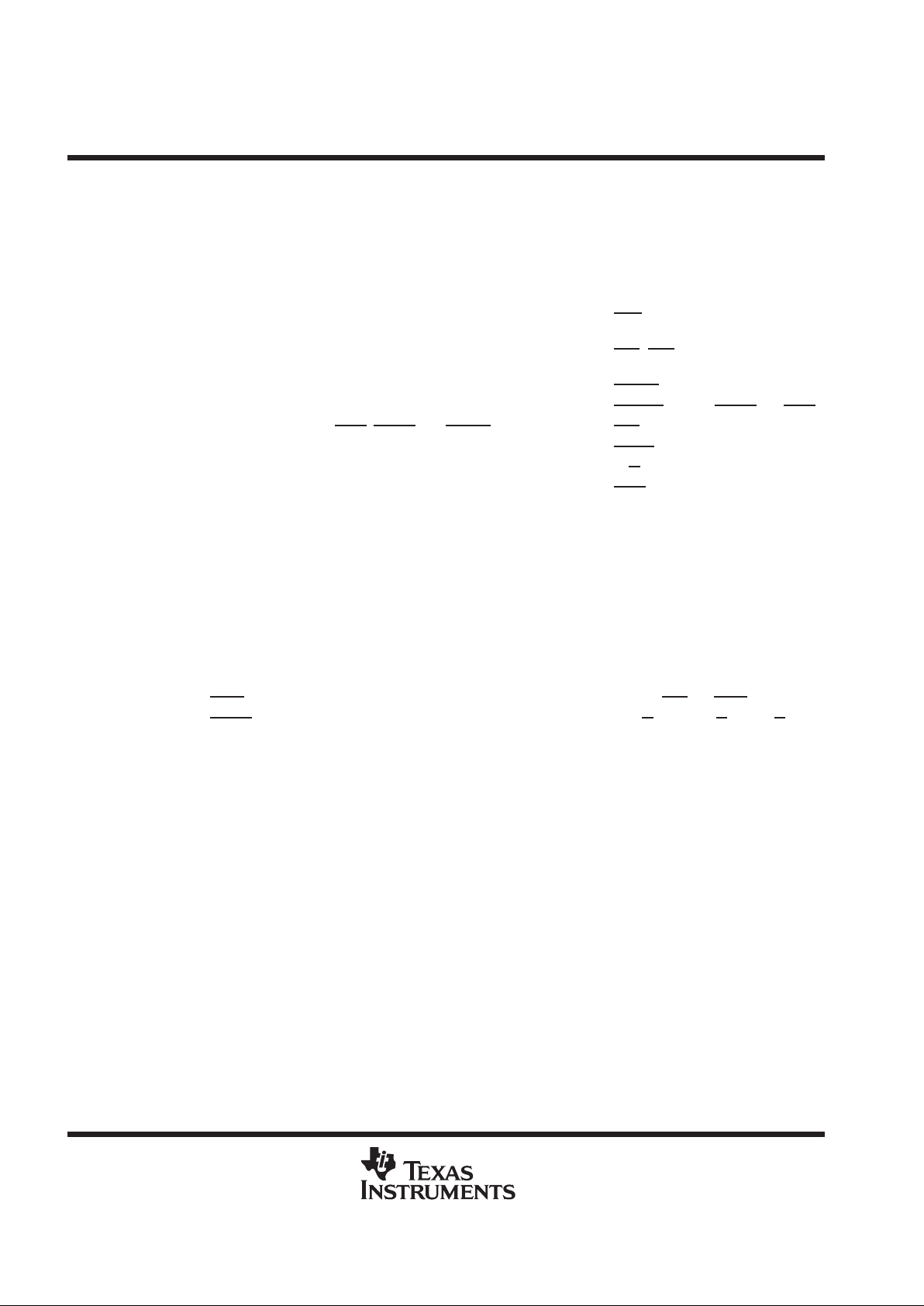

Transition times for TTL-compatible inputs are specified as follows:

D

For a high-to-low transition on an input signal, the level at which the input is said to be no longer high is

2.1 V and the level at which the input is said to be low is 0.8 V.

D

For a low-to-high transition on an input signal, the level at which the input is said to be no longer low is

0.8 V and the level at which the input is said to be high is 2.1 V.

0.8 V

2.1 V

Figure 6. TTL-Level Inputs

SMJ320C30

DIGITAL SIGNAL PROCESSOR

SGUS014F – FEBRUARY 1991 – REVISED FEBRUARY 1999

14

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251–1443

PARAMETER MEASUREMENT INFORMATION

timing parameter symbology

Timing parameter symbols used herein were created in accordance with JEDEC Standard 100-A. To shorten

the symbols, some of the terminal names and other related terminology have been abbreviated as follows,

unless otherwise noted:

A A23–A0 IACK IACK

ASYNCH Asynchronous reset signals include XF0, XF1,

CLKX0, DX0, FSX0, CLKR0, DR0, FSR0, CLKX1,

DX1, FSX1, CLKR1, DR1, FSR1, TCLK0, and TCLK1

INT INT3

–INT0

CH CLKX includes CLKX0 and CLKX1 IOS IOSTRB

CI CLKIN (M)S (M)STRB includes MSTRB and STRB

CONTROL Control signals include STRB, MSTRB, and IOSTRB RDY RDY

D D31–D0 RESET RESET

DR Includes DR0, DR1 RW R/W

DX Includes DX0, DX1 S STRB

FS FSX/R includes FSX0, FSX1, FSR0, and FSR1

SCK CLKX/R includes CLKX0, CLKX1,

CLKR0, and CLKR1

FSR Includes FSR0, FSR1 TCLK TCLK0, TCLK1

FSX Includes FSX0, FSX1 (X)A Includes A23–A0 and XA12–XA0

GPIO General-purpose input/output; peripheral pins include

CLKX0/1, CLKR0/1, DX0/1, DR0/1, FSX0/1, FSR0/1,

and TCLK0/1

(X)D Includes D31–D0 and XD31–XD0

H Includes H1, H3 XF XFx includes XF0 and XF1

H1 H1 XF0 XF0

H3 H3 XF1 XF1

HOLD HOLD

(X)RDY Includes RDY and XRDY

HOLDA HOLDA (X)RW (X)R/W includes R/W and XR/W

Loading...

Loading...