Page 1

Product

Folder

Order

Now

Technical

Documents

Tools &

Software

Support &

Community

TMS320C6748™ Fixed- and Floating-Point DSP

1 Device Overview

1.1 Features

1

• 375- and 456-MHz C674x Fixed- and FloatingPoint VLIW DSP

• C674x Instruction Set Features

– Superset of the C67x+ and C64x+ ISAs

– Up to 3648 MIPS and 2746 MFLOPS

– Byte-Addressable (8-, 16-, 32-, and 64-Bit Data)

– 8-Bit Overflow Protection

– Bit-Field Extract, Set, Clear

– Normalization, Saturation, Bit-Counting

– Compact 16-Bit Instructions

• C674x Two-Level Cache Memory Architecture

– 32KB of L1P Program RAM/Cache

– 32KB of L1D Data RAM/Cache

– 256KB of L2 Unified Mapped RAM/Cache

– Flexible RAM/Cache Partition (L1 and L2)

• Enhanced Direct Memory Access Controller 3

(EDMA3):

– 2 Channel Controllers

– 3 Transfer Controllers

– 64 Independent DMA Channels

– 16 Quick DMA Channels

– Programmable Transfer Burst Size

• TMS320C674x Floating-Point VLIW DSP Core

– Load-Store Architecture With Nonaligned

Support

– 64 General-Purpose Registers (32-Bit)

– Six ALU (32- and 40-Bit) Functional Units

– Supports 32-Bit Integer, SP (IEEE Single

Precision/32-Bit) and DP (IEEE Double

Precision/64-Bit) Floating Point

– Supports up to Four SP Additions Per Clock,

Four DP Additions Every Two Clocks

– Supports up to Two Floating-Point (SP or DP)

Reciprocal Approximation (RCPxP) and

Square-Root Reciprocal Approximation

(RSQRxP) Operations Per Cycle

– Two Multiply Functional Units:

– Mixed-Precision IEEE Floating-Point Multiply

Supported up to:

– 2 SP × SP → SP Per Clock

– 2 SP × SP → DP Every Two Clocks

TMS320C6748

SPRS590G –JUNE 2009–REVISED JANUARY 2017

– 2 SP × DP → DP Every Three Clocks

– 2 DP × DP → DP Every Four Clocks

– Fixed-Point Multiply Supports Two 32 × 32-

Bit Multiplies, Four 16 × 16-Bit Multiplies, or

Eight 8 × 8-Bit Multiplies per Clock Cycle,

and Complex Multiples

– Instruction Packing Reduces Code Size

– All Instructions Conditional

– Hardware Support for Modulo Loop Operation

– Protected Mode Operation

– Exceptions Support for Error Detection and

Program Redirection

• Software Support

– TI DSP BIOS™

– Chip Support Library and DSP Library

• 128KB of RAM Shared Memory

• 1.8-V or 3.3-V LVCMOS I/Os (Except for USB and

DDR2 Interfaces)

• Two External Memory Interfaces:

– EMIFA

– NOR (8- or 16-Bit-Wide Data)

– NAND (8- or 16-Bit-Wide Data)

– 16-Bit SDRAM With 128-MB Address Space

– DDR2/Mobile DDR Memory Controller With one

of the Following:

– 16-Bit DDR2 SDRAM With 256-MB Address

Space

– 16-Bit mDDR SDRAM With 256-MB Address

Space

• Three Configurable 16550-Type UART Modules:

– With Modem Control Signals

– 16-Byte FIFO

– 16x or 13x Oversampling Option

• LCD Controller

• Two Serial Peripheral Interfaces (SPIs) Each With

Multiple Chip Selects

• Two Multimedia Card (MMC)/Secure Digital (SD)

Card Interfaces With Secure Data I/O (SDIO)

Interfaces

• Two Master and Slave Inter-Integrated Circuits

(I2C Bus™)

1

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

Page 2

TMS320C6748

SPRS590G –JUNE 2009–REVISED JANUARY 2017

www.ti.com

• One Host-Port Interface (HPI) With 16-Bit-Wide

Muxed Address and Data Bus For High Bandwidth

• Programmable Real-Time Unit Subsystem

(PRUSS)

– Two Independent Programmable Real-Time Unit

(PRU) Cores

– 32-Bit Load-Store RISC Architecture

– 4KB of Instruction RAM Per Core

– 512 Bytes of Data RAM Per Core

– PRUSS can be Disabled Through Software to

Save Power

– Register 30 of Each PRU is Exported From

the Subsystem in Addition to the Normal R31

Output of the PRU Cores.

– Standard Power-Management Mechanism

– Clock Gating

– Entire Subsystem Under a Single PSC Clock

Gating Domain

– Dedicated Interrupt Controller

– Dedicated Switched Central Resource

• USB 1.1 OHCI (Host) With Integrated PHY (USB1)

• USB 2.0 OTG Port With Integrated PHY (USB0)

– USB 2.0 High- and Full-Speed Client

– USB 2.0 High-, Full-, and Low-Speed Host

– End Point 0 (Control)

– End Points 1, 2, 3, and 4 (Control, Bulk,

Interrupt, or ISOC) RX and TX

• One Multichannel Audio Serial Port (McASP):

– Two Clock Zones and 16 Serial Data Pins

– Supports TDM, I2S, and Similar Formats

– DIT-Capable

– FIFO Buffers for Transmit and Receive

• Two Multichannel Buffered Serial Ports (McBSPs):

– Supports TDM, I2S, and Similar Formats

– AC97 Audio Codec Interface

– Telecom Interfaces (ST-Bus, H100)

– 128-Channel TDM

– FIFO Buffers for Transmit and Receive

• 10/100 Mbps Ethernet MAC (EMAC):

– IEEE 802.3 Compliant

– MII Media-Independent Interface

– RMII Reduced Media-Independent Interface

– Management Data I/O (MDIO) Module

• Video Port Interface (VPIF):

– Two 8-Bit SD (BT.656), Single 16-Bit or Single

Raw (8-, 10-, and 12-Bit) Video Capture

Channels

– Two 8-Bit SD (BT.656), Single 16-Bit Video

Display Channels

• Universal Parallel Port (uPP):

– High-Speed Parallel Interface to FPGAs and

Data Converters

– Data Width on Both Channels is 8- to 16-Bit

Inclusive

– Single-Data Rate or Dual-Data Rate Transfers

– Supports Multiple Interfaces With START,

ENABLE, and WAIT Controls

• Serial ATA (SATA) Controller:

– Supports SATA I (1.5 Gbps) and SATA II

(3.0 Gbps)

– Supports All SATA Power-Management

Features

– Hardware-Assisted Native Command Queueing

(NCQ) for up to 32 Entries

– Supports Port Multiplier and Command-Based

Switching

• Real-Time Clock (RTC) With 32-kHz Oscillator and

Separate Power Rail

• Three 64-Bit General-Purpose Timers (Each

Configurable as Two 32-Bit Timers)

• One 64-Bit General-Purpose or Watchdog Timer

(Configurable as Two 32-Bit General-Purpose

Timers)

• Two Enhanced High-Resolution Pulse Width

Modulators (eHRPWMs):

– Dedicated 16-Bit Time-Base Counter With

Period and Frequency Control

– 6 Single-Edge Outputs, 6 Dual-Edge Symmetric

Outputs, or 3 Dual-Edge Asymmetric Outputs

– Dead-Band Generation

– PWM Chopping by High-Frequency Carrier

– Trip Zone Input

• Three 32-Bit Enhanced Capture (eCAP) Modules:

– Configurable as 3 Capture Inputs or 3 Auxiliary

Pulse Width Modulator (APWM) Outputs

– Single-Shot Capture of up to Four Event

Timestamps

• Packages:

– 361-Ball Pb-Free Plastic Ball Grid Array (PBGA)

[ZCE Suffix], 0.65-mm Ball Pitch

– 361-Ball Pb-Free PBGA [ZWT Suffix],

0.80-mm Ball Pitch

• Commercial, Extended, or Industrial Temperature

2

Device Overview Copyright © 2009–2017, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: TMS320C6748

Page 3

www.ti.com

1.2 Applications

• Currency Inspection

• Biometric Identification

1.3 Description

The TMS320C6748 fixed- and floating-point DSP is a low-power applications processor based on a C674x

DSP core. This DSP provides significantly lower power than other members of the TMS320C6000™

platform of DSPs.

The device enables original-equipment manufacturers (OEMs) and original-design manufacturers (ODMs)

to quickly bring to market devices with robust operating systems, rich user interfaces, and high processor

performance through the maximum flexibility of a fully integrated, mixed processor solution.

The device DSP core uses a 2-level cache-based architecture. The level 1 program cache (L1P) is a

32-KB direct mapped cache, and the level 1 data cache (L1D) is a 32-KB 2-way, set-associative cache.

The level 2 program cache (L2P) consists of a 256-KB memory space that is shared between program

and data space. L2 memory can be configured as mapped memory, cache, or combinations of the two.

Although the DSP L2 is accessible by other hosts in the system, an additional 128KB of RAM shared

memory is available for use by other hosts without affecting DSP performance.

For security-enabled devices, TI’s Basic Secure Boot lets users protect proprietary intellectual property

and prevents external entities from modifying user-developed algorithms. By starting from a hardwarebased “root-of-trust," the secure boot flow ensures a known good starting point for code execution. By

default, the JTAG port is locked down to prevent emulation and debug attacks; however, the JTAG port

can be enabled during the secure boot process during application development. The boot modules are

encrypted while sitting in external nonvolatile memory, such as flash or EEPROM, and are decrypted and

authenticated when loaded during secure boot. Encryption and decryption protects customers’ IP and lets

them securely set up the system and begin device operation with known, trusted code.

TMS320C6748

SPRS590G –JUNE 2009–REVISED JANUARY 2017

• Machine Vision (Low-End)

Basic Secure Boot uses either SHA-1 or SHA-256, and AES-128 for boot image validation. Basic Secure

Boot also uses AES-128 for boot image encryption. The secure boot flow employs a multilayer encryption

scheme which not only protects the boot process but also offers the ability to securely upgrade boot and

application software code. A 128-bit device-specific cipher key, known only to the device and generated

using a NIST-800-22 certified random number generator, is used to protect customer encryption keys.

When an update is needed, the customer uses the encryption keys to create a new encrypted image.

Then the device can acquire the image through an external interface, such as Ethernet, and overwrite the

existing code. For more details on the supported security features or TI’s Basic Secure Boot, see the

TMS320C674x/OMAP-L1x Processor Security User’s Guide.

The peripheral set includes: a 10/100 Mbps Ethernet media access controller (EMAC) with a management

data input/output (MDIO) module; one USB2.0 OTG interface; one USB1.1 OHCI interface; two I2C Bus

interfaces; one multichannel audio serial port (McASP) with 16 serializers and FIFO buffers; two

multichannel buffered serial ports (McBSPs) with FIFO buffers; two serial peripheral interfaces (SPIs) with

multiple chip selects; four 64-bit general-purpose timers each configurable (one configurable as a

watchdog); a configurable 16-bit host-port interface (HPI); up to 9 banks of general-purpose input/output

(GPIO) pins, with each bank containing 16 pins with programmable interrupt and event generation modes,

multiplexed with other peripherals; three UART interfaces (each with RTS and CTS); two enhanced highresolution pulse width modulator (eHRPWM) peripherals; three 32-bit enhanced capture (eCAP) module

peripherals which can be configured as 3 capture inputs or 3 APWM outputs; two external memory

interfaces: an asynchronous and SDRAM external memory interface (EMIFA) for slower memories or

peripherals; and a higher speed DDR2/Mobile DDR controller.

The EMAC provides an efficient interface between the device and a network. The EMAC supports both

10Base-T and 100Base-TX, or 10 Mbps and 100 Mbps in either half- or full-duplex mode. Additionally, an

MDIO interface is available for PHY configuration. The EMAC supports both MII and RMII interfaces.

Submit Documentation Feedback

Product Folder Links: TMS320C6748

Device OverviewCopyright © 2009–2017, Texas Instruments Incorporated

3

Page 4

TMS320C6748

SPRS590G –JUNE 2009–REVISED JANUARY 2017

The Serial ATA (SATA) controller provides a high-speed interface to mass data storage devices. The

SATA controller supports both SATA I (1.5 Gbps) and SATA II (3.0 Gbps).

The Universal Parallel Port (uPP) provides a high-speed interface to many types of data converters,

FPGAs, or other parallel devices. The uPP supports programmable data widths between 8- to 16-bits on

both channels. Single-data rate and double-data rate transfers are supported as well as START, ENABLE,

and WAIT signals to provide control for a variety of data converters.

A video port interface (VPIF) provides a flexible video I/O port.

The rich peripheral set provides the ability to control external peripheral devices and communicate with

external processors. For details on each peripheral, see the related sections in this document and the

associated peripheral reference guides.

The device has a complete set of development tools for the DSP. These tools include C compilers, a DSP

assembly optimizer to simplify programming and scheduling, and a Windows®debugger interface for

visibility into source code execution.

www.ti.com

Device Information

PART NUMBER PACKAGE BODY SIZE

TMS320C6748ZCE NFBGA (361) 13,00 mm x 13,00 mm

TMS320C6748ZWT NFBGA (361) 16,00 mm x 16,00 mm

(1) For more information on these devices, see Section 8.

(1)

4

Device Overview Copyright © 2009–2017, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: TMS320C6748

Page 5

Switched Central Resource (SCR)

BOOT ROM

256KB L2 RAM

32KB

L1 RAM

32KB

L1 Pgm

AET

C674x™

DSP CPU

DSP Subsystem

JTAG Interface

System Control

Input

Clock(s)

Power/Sleep

Controller

Pin

Multiplexing

PLL/Clock

Generator

w/OSC

GeneralPurpose

Timer (x3)

Serial Interfaces

Audio Ports

McASP

w/FIFO

DMA

Peripherals

Display Internal Memory

LCD

Ctlr

128KB

RAM

External Memory InterfacesConnectivity

EDMA3

(x2)

Control Timers

ePWM

(x2)

eCAP

(x3)

EMIFA(8b/16B)

NAND/Flash

16b SDRAM

DDR2/MDDR

Controller

RTC/

32-kHz

OSC

I C

(x2)

2

SPI

(x2)

UART

(x3)

McBSP

(x2)

Video

VPIF

Parallel Port

uPP

EMAC

10/100

(MII/RMII)

MDIO

USB1.1

OHCI Ctlr

PHY

USB2.0

OTG Ctlr

PHY

HPI

MMC/SD

(8b)

(x2)

SATA

Customizable Interface

PRU Subsystem

Memory

Protection

www.ti.com

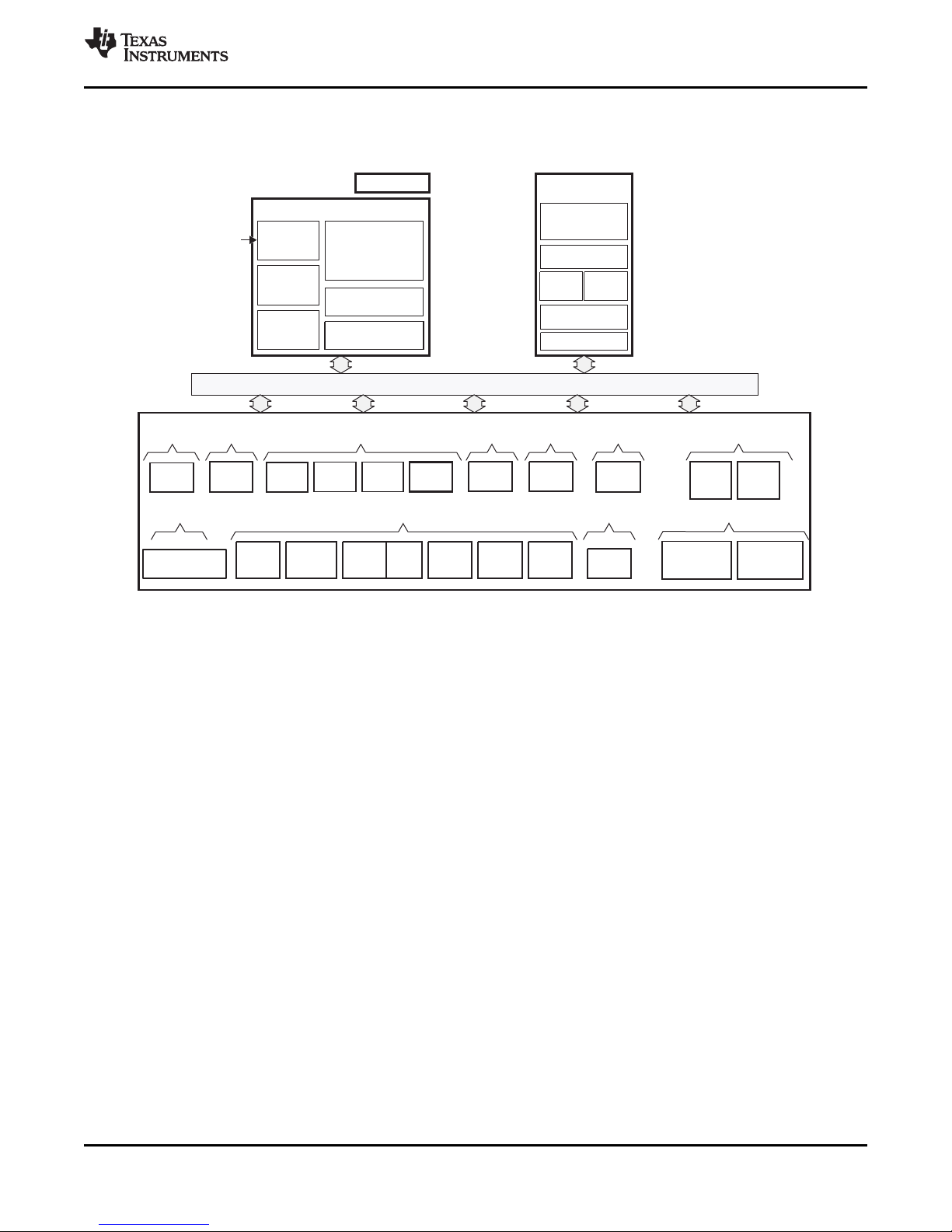

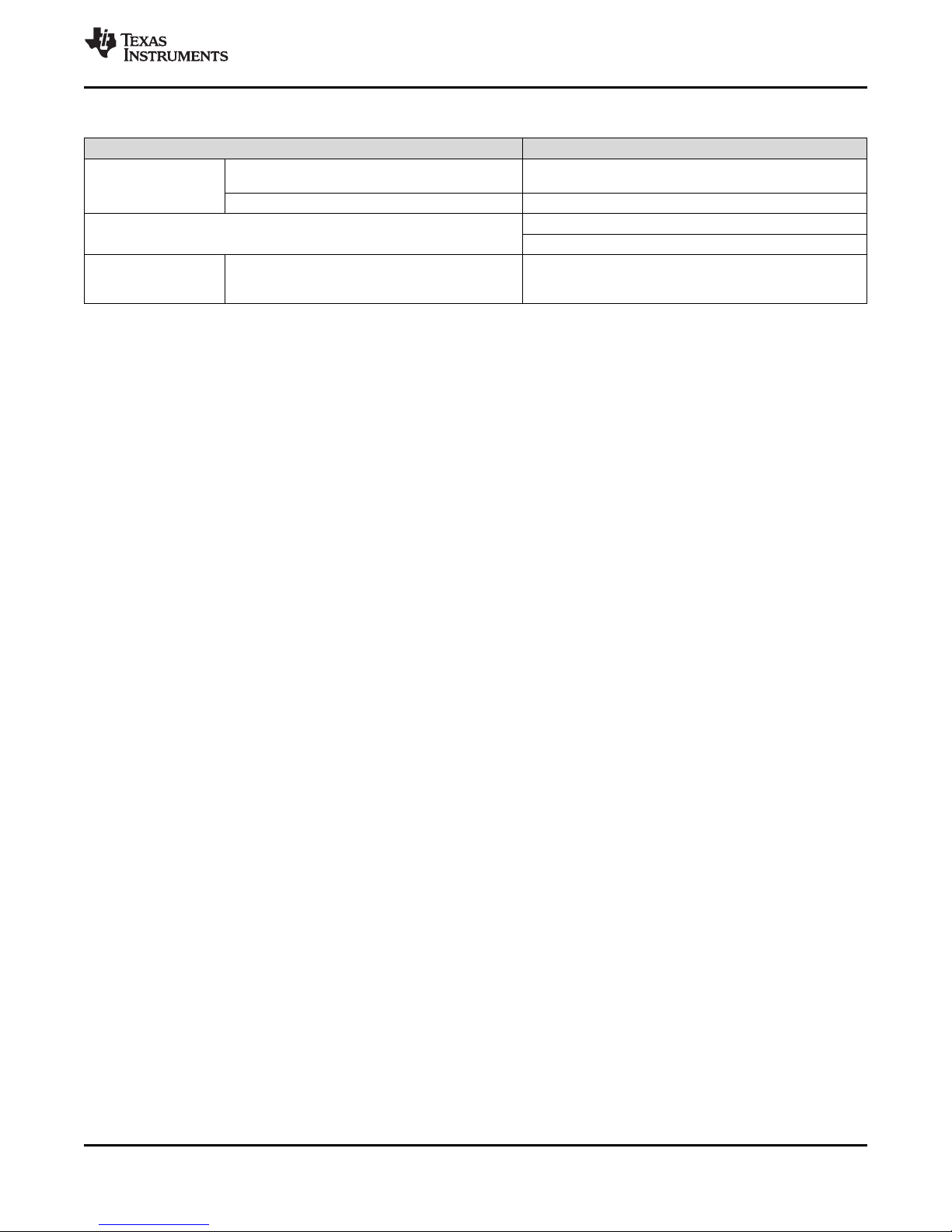

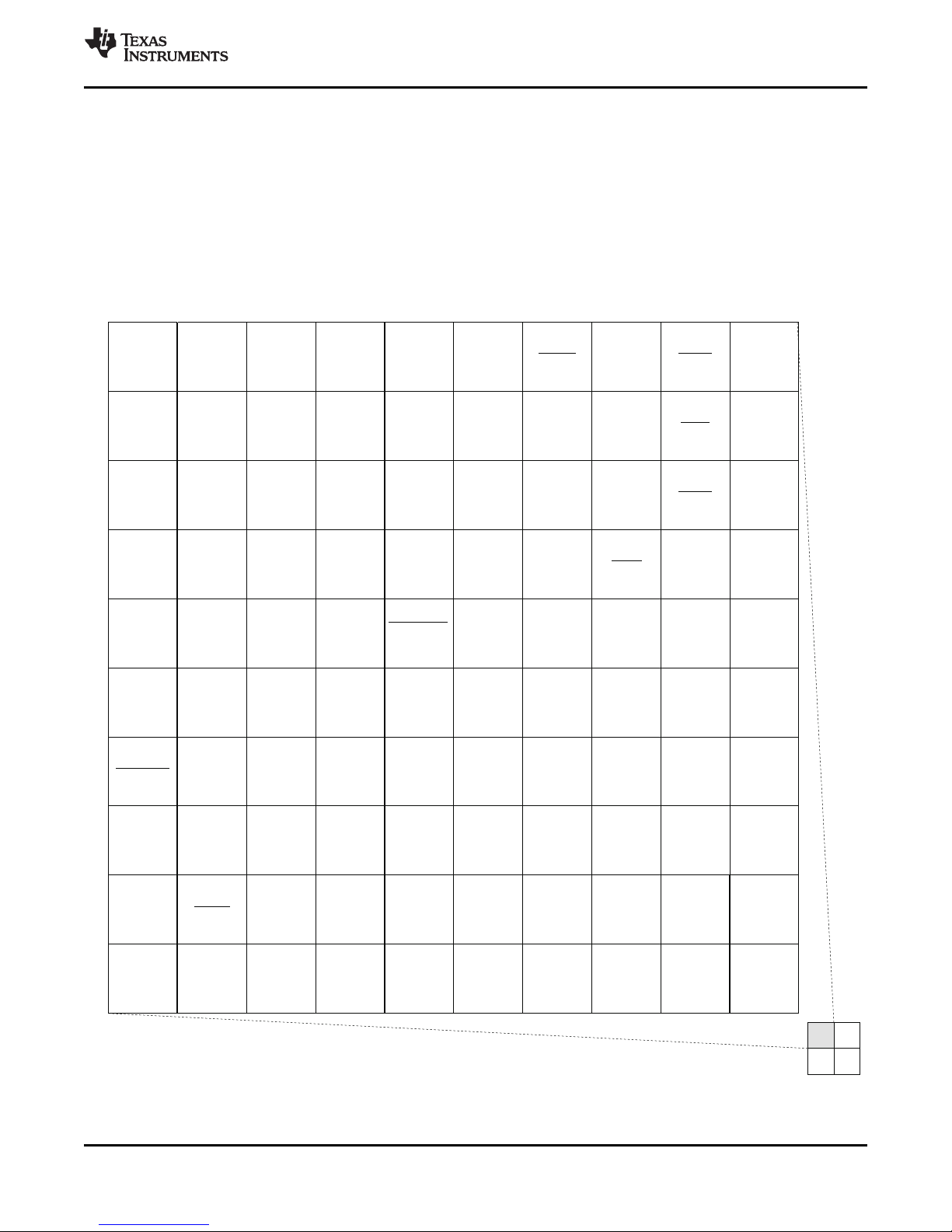

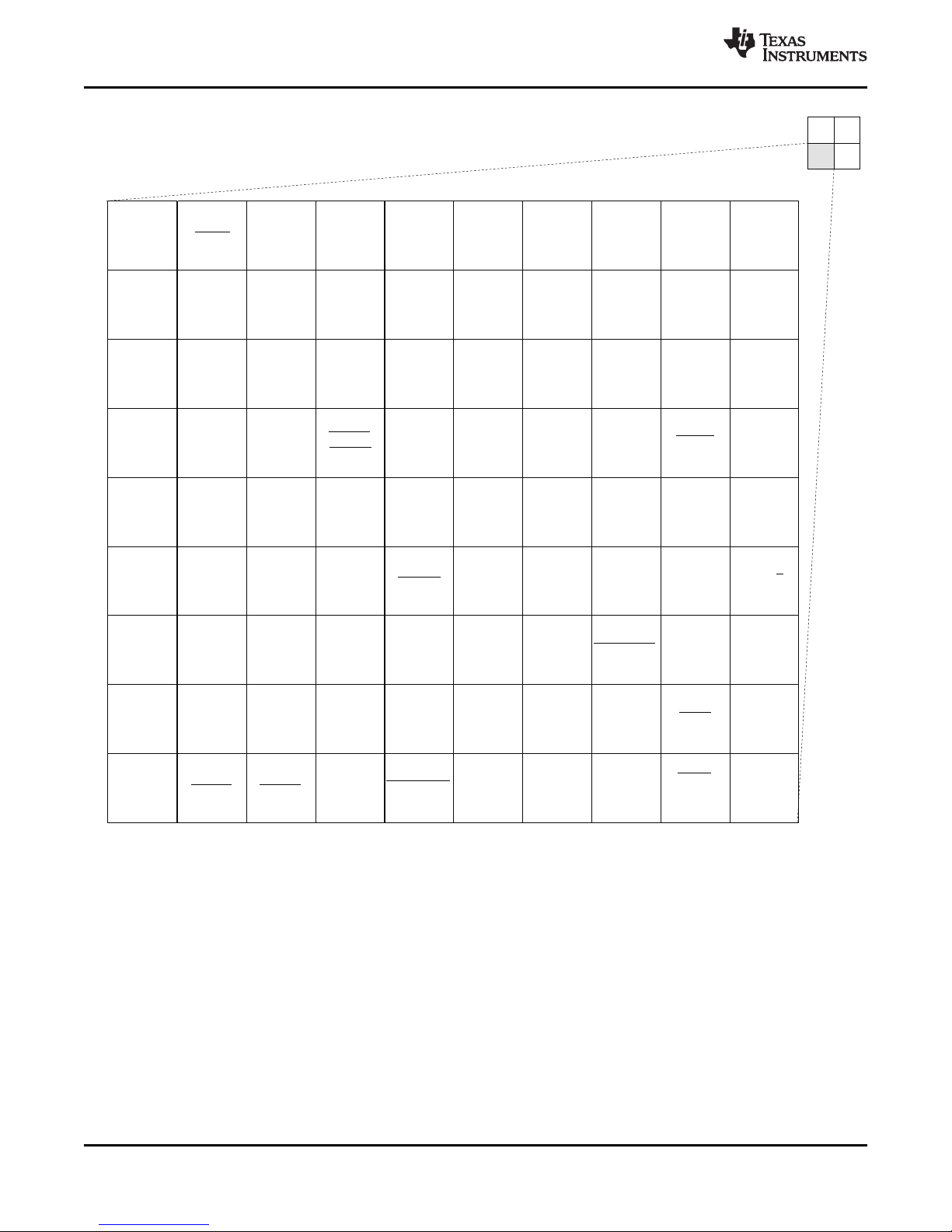

1.4 Functional Block Diagram

Figure 1-1 shows the functional block diagram of the device.

TMS320C6748

SPRS590G –JUNE 2009–REVISED JANUARY 2017

Figure 1-1. Functional Block Diagram

Submit Documentation Feedback

Product Folder Links: TMS320C6748

Device OverviewCopyright © 2009–2017, Texas Instruments Incorporated

5

Page 6

TMS320C6748

SPRS590G –JUNE 2009–REVISED JANUARY 2017

www.ti.com

Table of Contents

1 Device Overview ........................................ 1

1.1 Features .............................................. 1

1.2 Applications........................................... 3

1.3 Description............................................ 3

1.4 Functional Block Diagram ............................ 5

2 Revision History ......................................... 7

3 Device Comparison ..................................... 8

3.1 Device Characteristics................................ 8

3.2 Device Compatibility.................................. 9

3.3 DSP Subsystem ...................................... 9

3.4 Memory Map Summary ............................. 20

3.5 Pin Assignments .................................... 23

3.6 Pin Multiplexing Control............................. 26

3.7 Terminal Functions .................................. 27

3.8 Unused Pin Configurations.......................... 69

4 Device Configuration .................................. 71

4.1 Boot Modes ......................................... 71

4.2 SYSCFG Module.................................... 71

4.3 Pullup/Pulldown Resistors .......................... 74

5 Specifications........................................... 75

5.1 Absolute Maximum Ratings Over Operating

Junction Temperature Range

(Unless Otherwise Noted) ................................. 75

5.2 Handling Ratings .................................... 75

5.3 Recommended Operating Conditions............... 76

5.4 Notes on Recommended Power-On Hours (POH) . 78

5.5 Electrical Characteristics Over Recommended

Ranges of Supply Voltage and Operating Junction

Temperature (Unless Otherwise Noted) ............ 79

6 Peripheral Information and Electrical

Specifications........................................... 80

6.1 Parameter Information .............................. 80

6.2 Recommended Clock and Control Signal Transition

Behavior............................................. 81

6.3 Power Supplies...................................... 81

6.4 Reset ................................................ 82

6.5 Crystal Oscillator or External Clock Input........... 86

6.6 Clock PLLs .......................................... 87

6.7 Interrupts ............................................ 92

6.8 Power and Sleep Controller (PSC).................. 96

6.9 Enhanced Direct Memory Access Controller

(EDMA3) ........................................... 101

6.10 External Memory Interface A (EMIFA) ............. 107

6.11 DDR2/mDDR Memory Controller .................. 119

6.12 Memory Protection Units .......................... 132

6.13 MMC / SD / SDIO (MMCSD0, MMCSD1) ......... 135

6.14 Serial ATA Controller (SATA)...................... 138

6.15 Multichannel Audio Serial Port (McASP) .......... 143

6.16 Multichannel Buffered Serial Port (McBSP)........ 152

6.17 Serial Peripheral Interface Ports (SPI0, SPI1)..... 161

6.18 Inter-Integrated Circuit Serial Ports (I2C) .......... 182

6.19 Universal Asynchronous Receiver/Transmitter

(UART)............................................. 186

6.20 Universal Serial Bus OTG Controller (USB0)

[USB2.0 OTG] ..................................... 188

6.21 Universal Serial Bus Host Controller (USB1)

[USB1.1 OHCI]..................................... 195

6.22 Ethernet Media Access Controller (EMAC) ........ 196

6.23 Management Data Input/Output (MDIO)........... 203

6.24 LCD Controller (LCDC) ............................ 205

6.25 Host-Port Interface (UHPI)......................... 220

6.26 Universal Parallel Port (uPP) ...................... 228

6.27 Video Port Interface (VPIF) ........................ 233

6.28 Enhanced Capture (eCAP) Peripheral............. 239

6.29 Enhanced High-Resolution Pulse-Width Modulator

(eHRPWM)......................................... 242

6.30 Timers.............................................. 247

6.31 Real Time Clock (RTC) ............................ 249

6.32 General-Purpose Input/Output (GPIO)............. 252

6.33 Programmable Real-Time Unit Subsystem

(PRUSS) ........................................... 256

6.34 Emulation Logic .................................... 259

7 Device and Documentation Support.............. 263

7.1 Device Nomenclature .............................. 263

7.2 Tools and Software ................................ 264

7.3 Documentation Support............................ 264

7.4 Community Resources............................. 265

7.5 Trademarks ........................................ 265

7.6 Electrostatic Discharge Caution ................... 265

7.7 Export Control Notice .............................. 265

7.8 Glossary............................................ 265

8 Mechanical Packaging and Orderable

Information............................................. 266

8.1 Thermal Data for ZCE Package ................... 266

8.2 Thermal Data for ZWT Package................... 267

8.3 Packaging Information ............................. 267

6

Table of Contents Copyright © 2009–2017, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: TMS320C6748

Page 7

TMS320C6748

www.ti.com

SPRS590G –JUNE 2009–REVISED JANUARY 2017

2 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Changes from March 31, 2014 to January 31, 2017 Page

• Removed internal pullup designation from RESET in Table 3-5.............................................................. 27

• Added footnote to CLKOUT Description in Table 3-6 .......................................................................... 28

• Added new column to Table 3-32 called "Configuration (When USB1 is used and USB0 is not used)" ................ 69

Submit Documentation Feedback

Product Folder Links: TMS320C6748

Revision HistoryCopyright © 2009–2017, Texas Instruments Incorporated

7

Page 8

TMS320C6748

SPRS590G –JUNE 2009–REVISED JANUARY 2017

3 Device Comparison

3.1 Device Characteristics

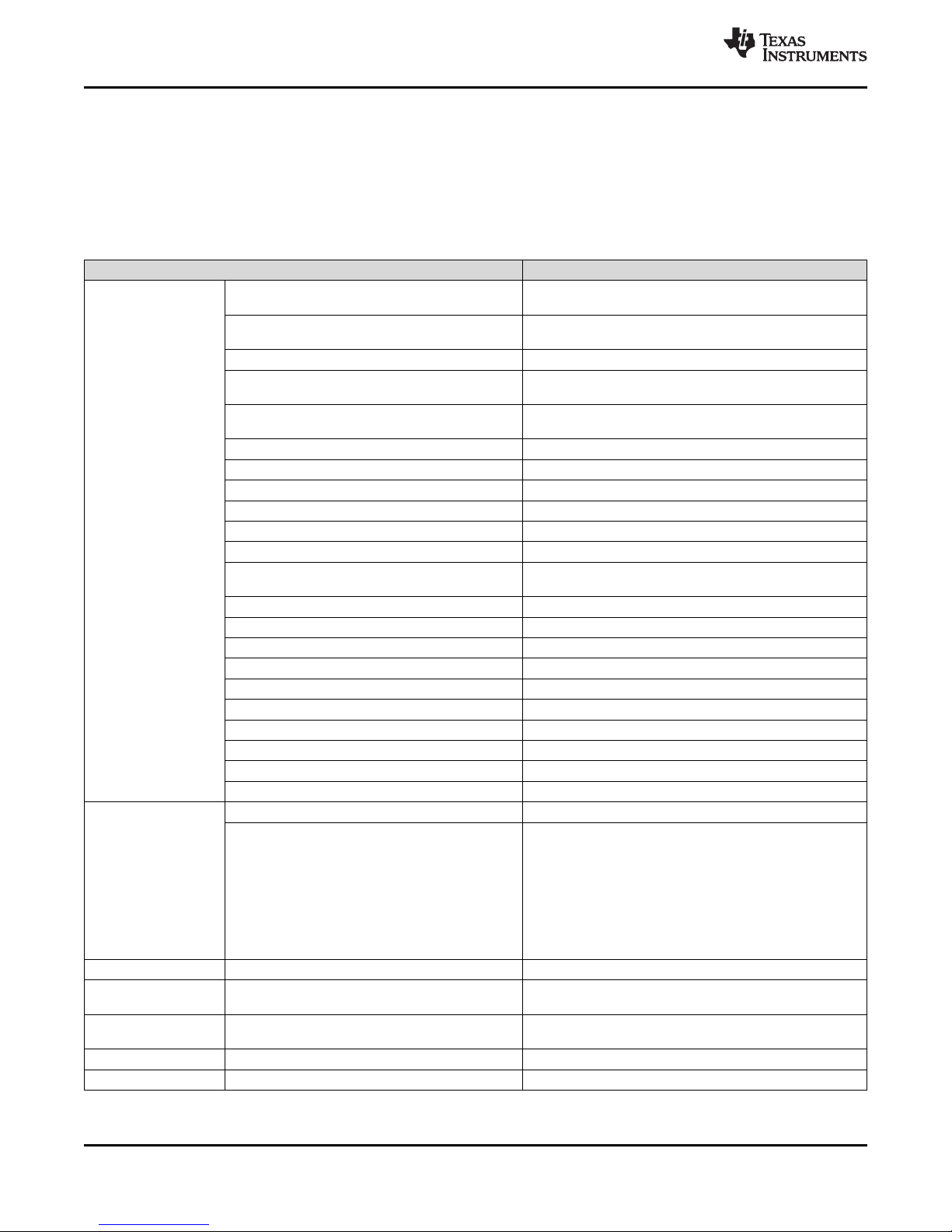

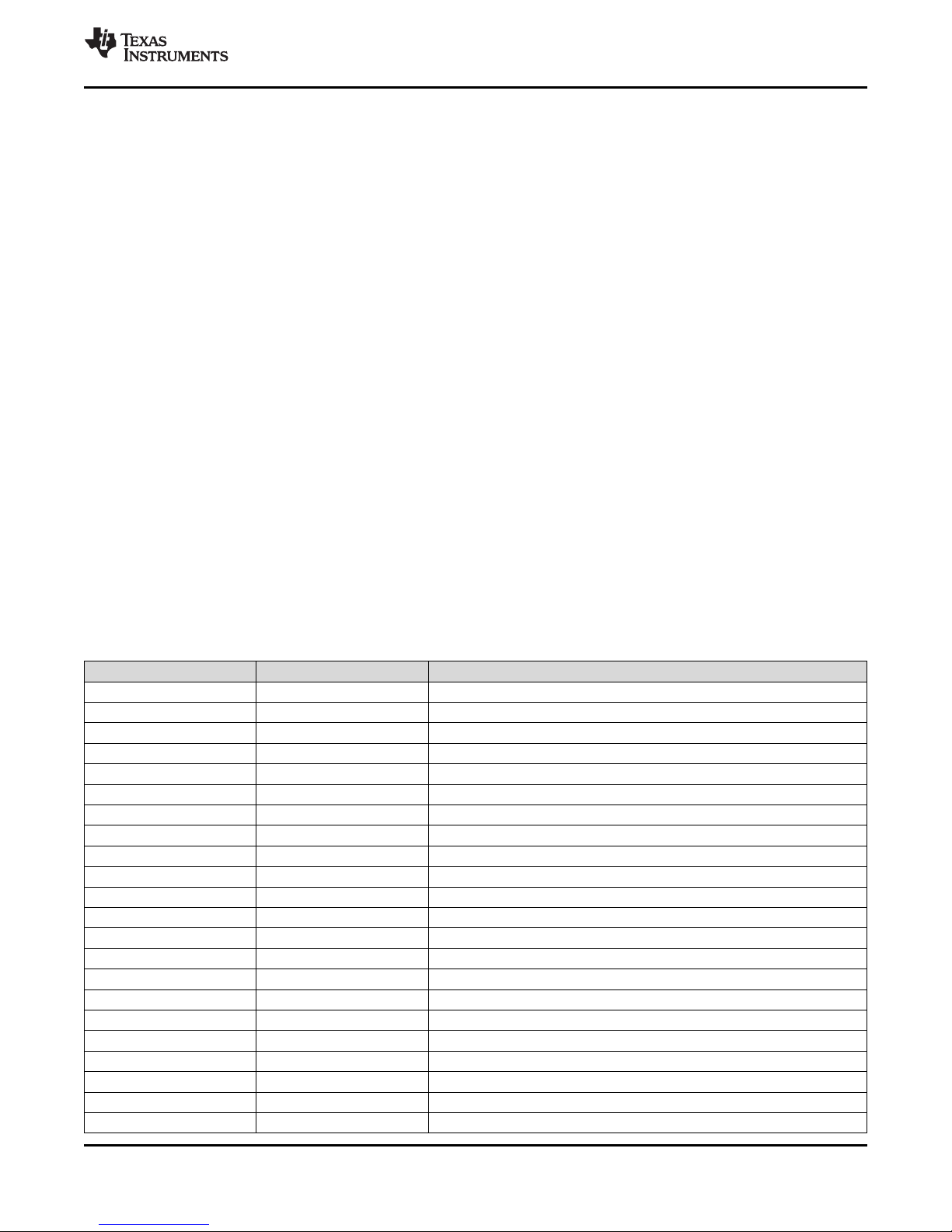

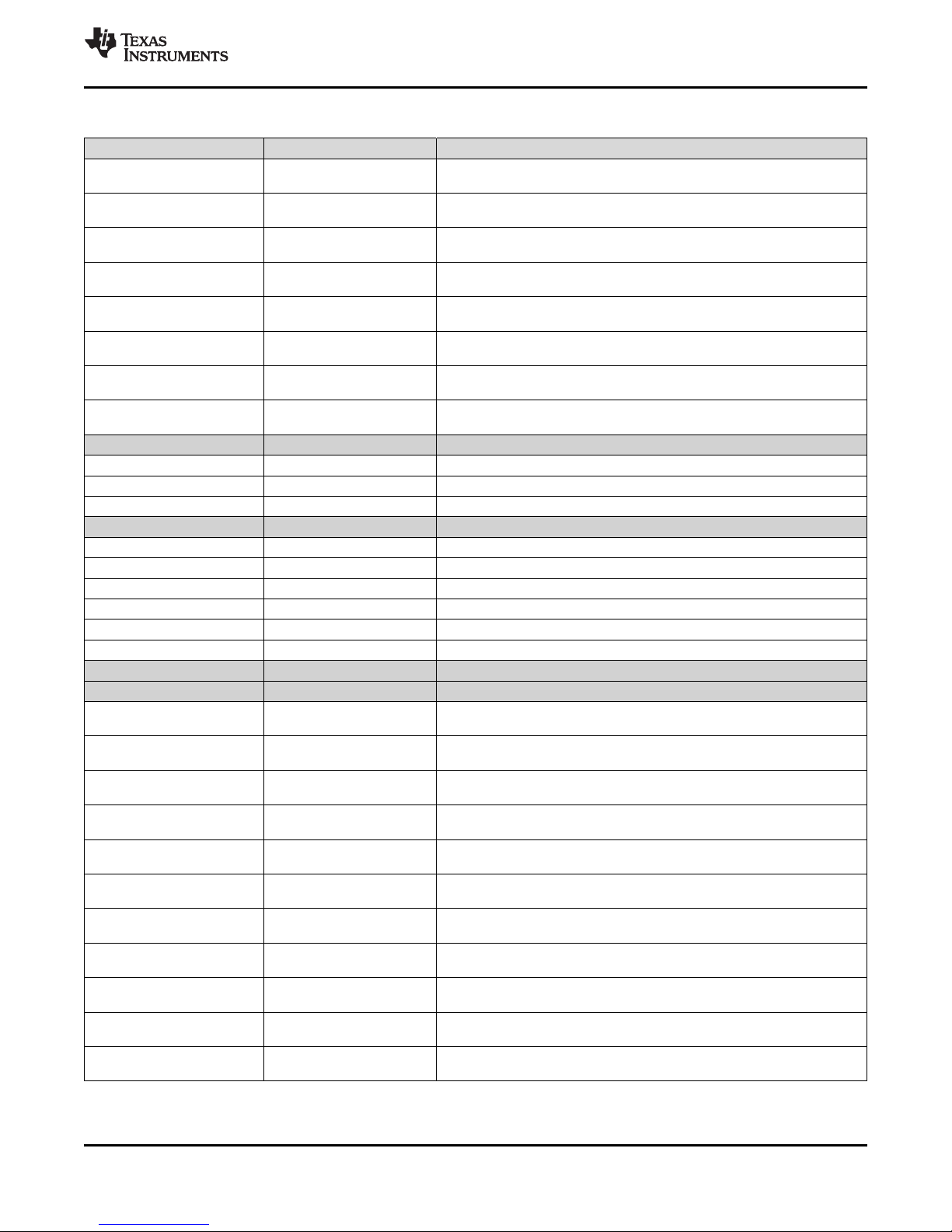

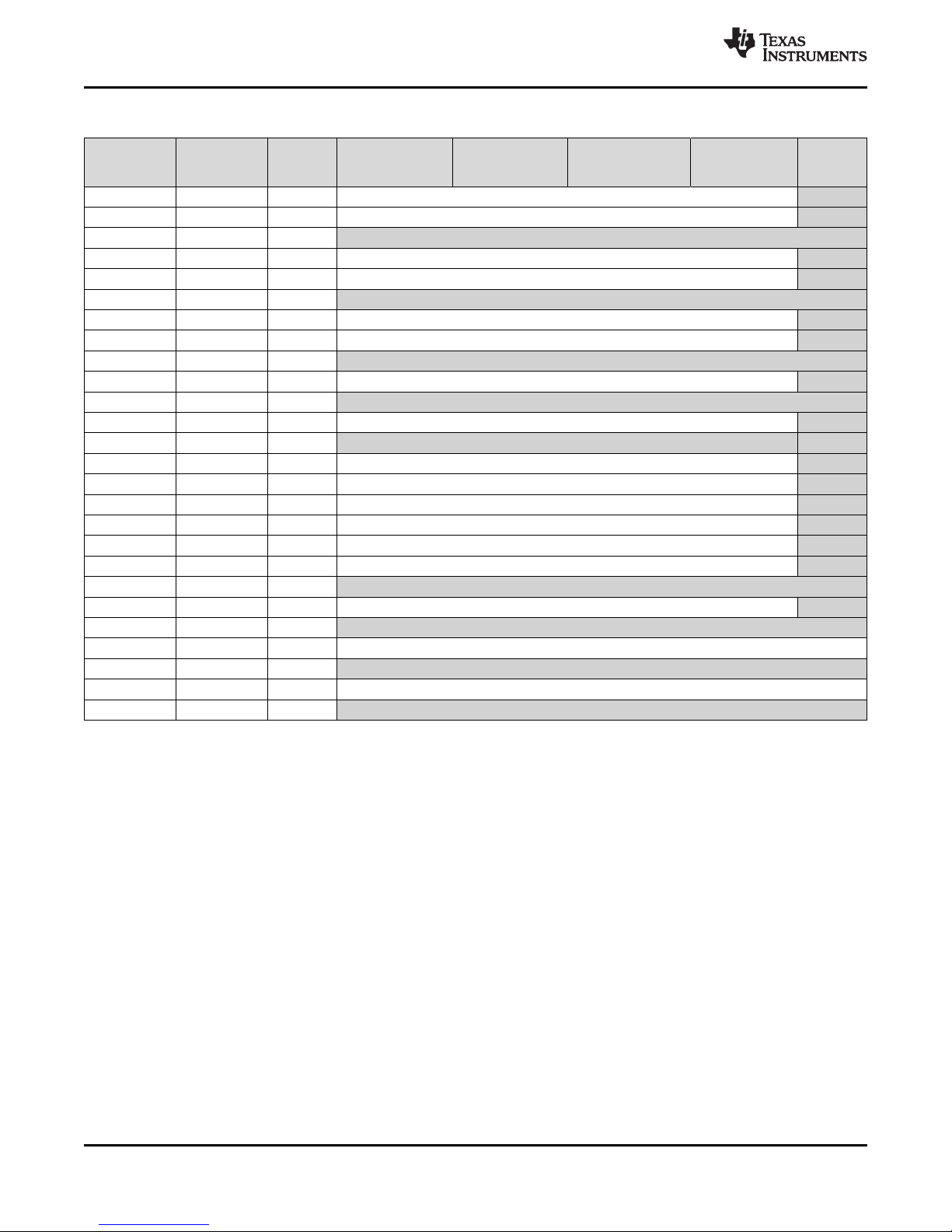

Table 3-1 provides an overview of the device. The table shows significant features of the device, including

the capacity of on-chip RAM, peripherals, and the package type with pin count.

HARDWARE FEATURES C6748

DDR2/mDDR Memory Controller

EMIFA

Flash Card Interface 2 MMC and SD cards supported

EDMA3

Timers

UART 3 (each with RTS and CTS flow control)

SPI 2 (Each with one hardware chip select)

Peripherals

Not all peripherals pins

are available at the

same time (for more

detail, see the Device

Configurations section).

On-Chip Memory

I2C 2 (both Master/Slave)

Multichannel Audio Serial Port [McASP] 1 (each with transmit/receive, FIFO buffer, 16 serializers)

Multichannel Buffered Serial Port [McBSP] 2 (each with transmit/receive, FIFO buffer, 16)

10/100 Ethernet MAC with Management Data I/O 1 (MII or RMII Interface)

eHRPWM

eCAP 3 32-bit capture inputs or 3 32-bit auxiliary PWM outputs

UHPI 1 (16-bit multiplexed address/data)

USB 2.0 (USB0) High-Speed OTG Controller with on-chip OTG PHY

USB 1.1 (USB1) Full-Speed OHCI (as host) with on-chip PHY

General-Purpose Input/Output Port 9 banks of 16-bit

LCD Controller 1

SATA Controller 1 (Supports both SATA I and SATAII)

Universal Parallel Port (uPP) 1

Video Port Interface (VPIF) 1 (video in and video out)

PRU Subsystem (PRUSS) 2 Programmable PRU Cores

Size (Bytes) 448KB RAM

Organization

www.ti.com

Table 3-1. Characteristics of C6748

DDR2, 16-bit bus width, up to 156 MHz

Mobile DDR, 16-bit bus width, up to 150 MHz

Asynchronous (8/16-bit bus width) RAM, Flash,

16-bit SDRAM, NOR, NAND

64 independent channels, 16 QDMA channels,

2 channel controllers, 3 transfer controllers

4 64-Bit General Purpose (each configurable as 2 separate

32-bit timers, one configurable as Watch Dog)

4 Single Edge, 4 Dual Edge Symmetric, or

2 Dual Edge Asymmetric Outputs

DSP

32KB L1 Program (L1P)/Cache (up to 32KB)

32KB L1 Data (L1D)/Cache (up to 32KB)

256KB Unified Mapped RAM/Cache (L2)

DSP Memories can be made accessible to EDMA3 and

other peripherals.

Security Secure Boot TI Basic Secure Boot

C674x CPU ID + CPU

Rev ID

C674x Megamodule

Revision

JTAG BSDL_ID DEVIDR0 Register see Section 6.34.4.1, JTAG Peripheral Register Description

CPU Frequency MHz 674x DSP 375 MHz (1.2V) or 456 MHz (1.3V)

8

Device Comparison Copyright © 2009–2017, Texas Instruments Incorporated

Control Status Register (CSR.[31:16]) 0x1400

Revision ID Register (MM_REVID[15:0]) 0x0000

ADDITIONAL MEMORY

128KB RAM

Submit Documentation Feedback

Product Folder Links: TMS320C6748

Page 9

TMS320C6748

www.ti.com

SPRS590G –JUNE 2009–REVISED JANUARY 2017

Table 3-1. Characteristics of C6748 (continued)

HARDWARE FEATURES C6748

Voltage

Packages

Product Status

(1) ADVANCE INFORMATION concerns new products in the sampling or preproduction phase of development. Characteristic data and

other specifications are subject to change without notice. PRODUCTION DATA information is current as of publication date. Products

conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include

testing of all parameters.

(1)

Core (V)

I/O (V) 1.8V or 3.3 V

Product Preview (PP),

Advance Information (AI),

or Production Data (PD)

Variable (1.2V-1.0V) for 375 MHz version

Variable (1.3V-1.0V) for 456 MHz version

13 mm x 13 mm, 361-Ball 0.65 mm pitch, PBGA (ZCE)

16 mm x 16 mm, 361-Ball 0.80 mm pitch, PBGA (ZWT)

375 MHz versions - PD

456 MHz versions - PD

3.2 Device Compatibility

The C674x DSP core is code-compatible with the C6000™ DSP platform and supports features of both

the C64x+ and C67x+ DSP families.

3.3 DSP Subsystem

The DSP Subsystem includes the following features:

• C674x DSP CPU

• 32KB L1 Program (L1P)/Cache (up to 32KB)

• 32KB L1 Data (L1D)/Cache (up to 32KB)

• 256KB Unified Mapped RAM/Cache (L2)

• Boot ROM (cannot be used for application code)

• Little endian

Submit Documentation Feedback

Product Folder Links: TMS320C6748

Device ComparisonCopyright © 2009–2017, Texas Instruments Incorporated

9

Page 10

Instruction Fetch

C674x

Fixed/Floating Point CPU

Register

File A

Register

File B

Cache Control

Memory Protect

Bandwidth Mgmt

L1P

256

Cache Control

Memory Protect

Bandwidth Mgmt

L1D

64 64

8 x 32

32K Bytes

L1D RAM/

Cache

32K Bytes

L1P RAM/

Cache

256

Cache Control

Memory Protect

Bandwidth Mgmt

L2

256K Bytes

L2 RAM

256

BOOT

ROM

256

CFG

MDMA SDMA

EMC

Power Down

Interrupt

Controller

IDMA

256

256

256

256

256

64

High

Performance

Switch Fabric

64

64 64

Configuration

Peripherals

Bus

32

TMS320C6748

SPRS590G –JUNE 2009–REVISED JANUARY 2017

www.ti.com

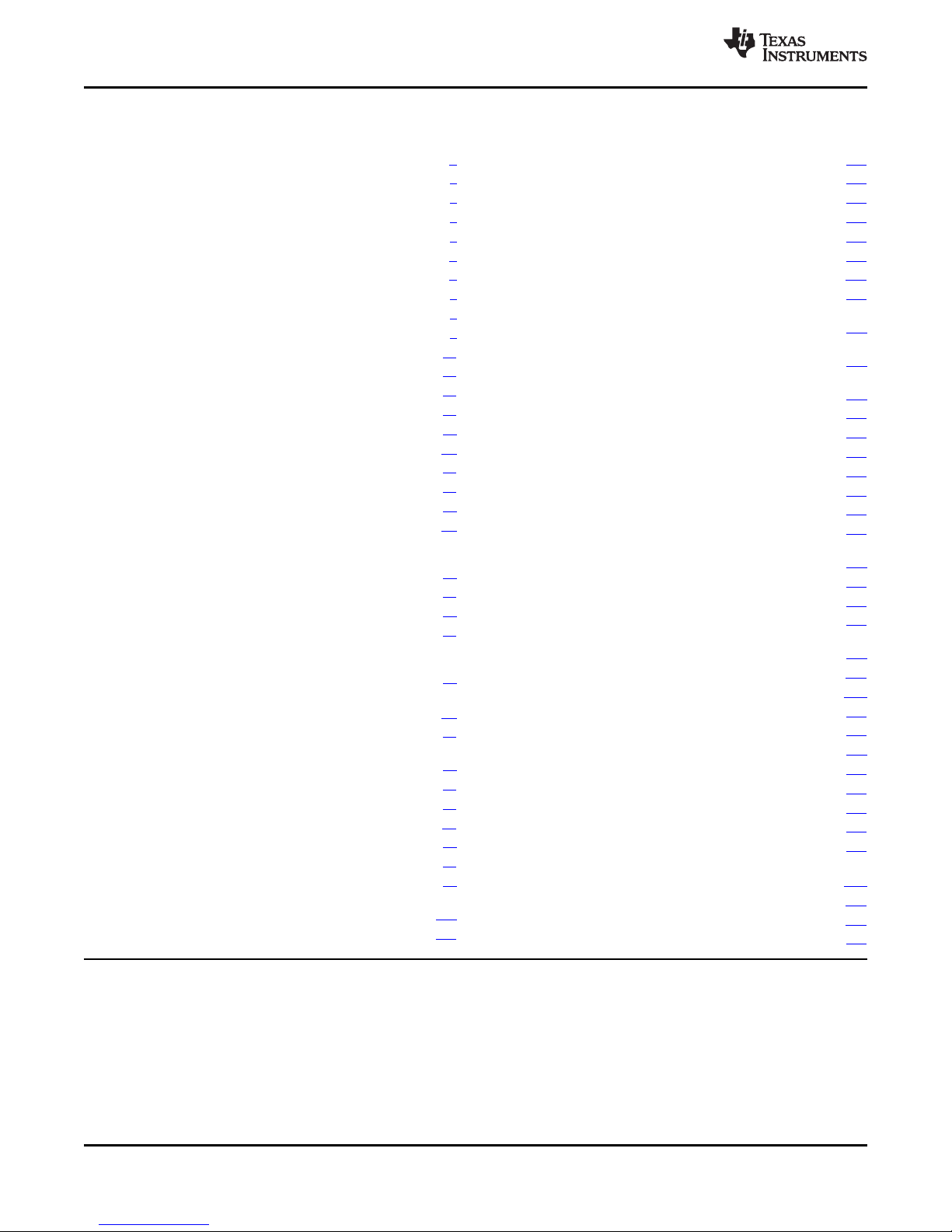

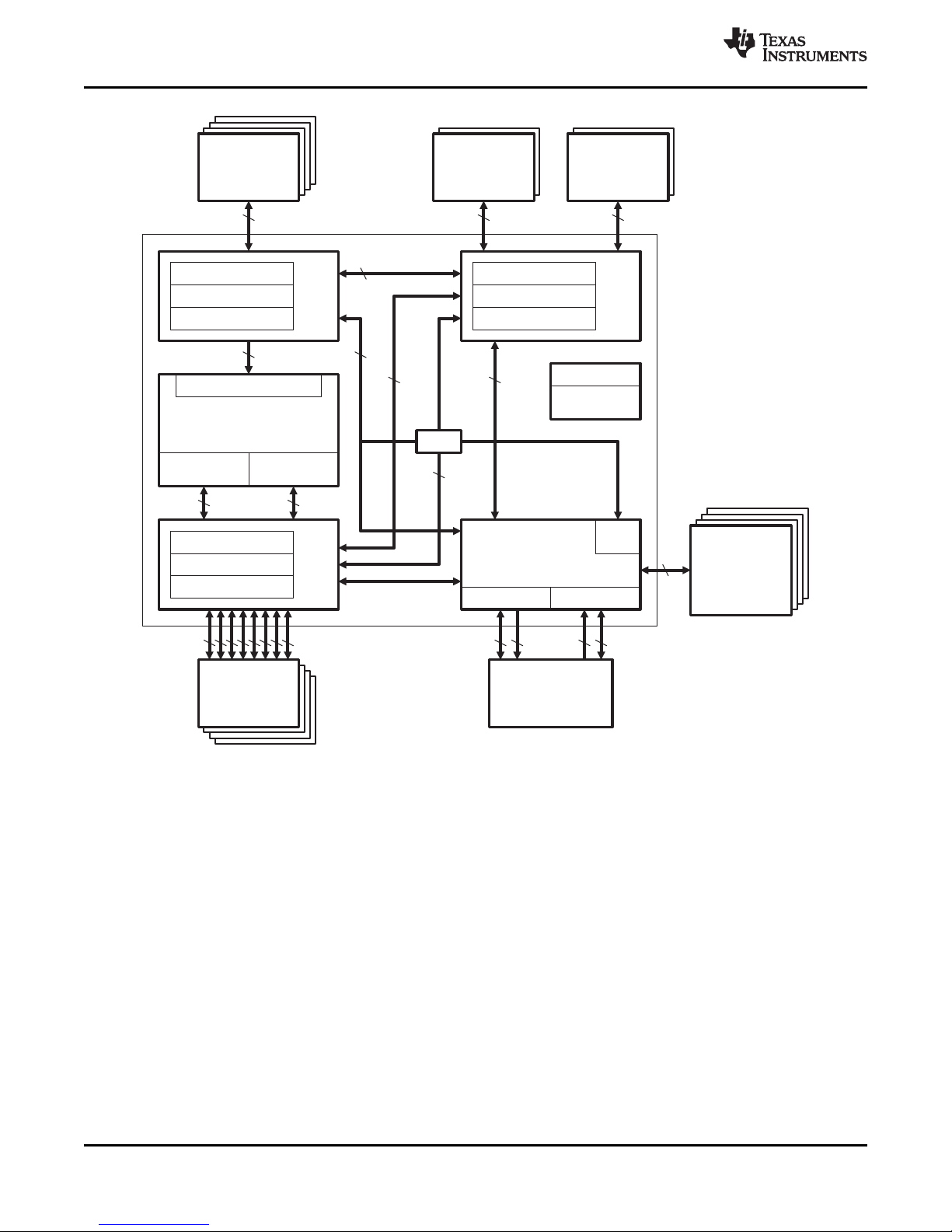

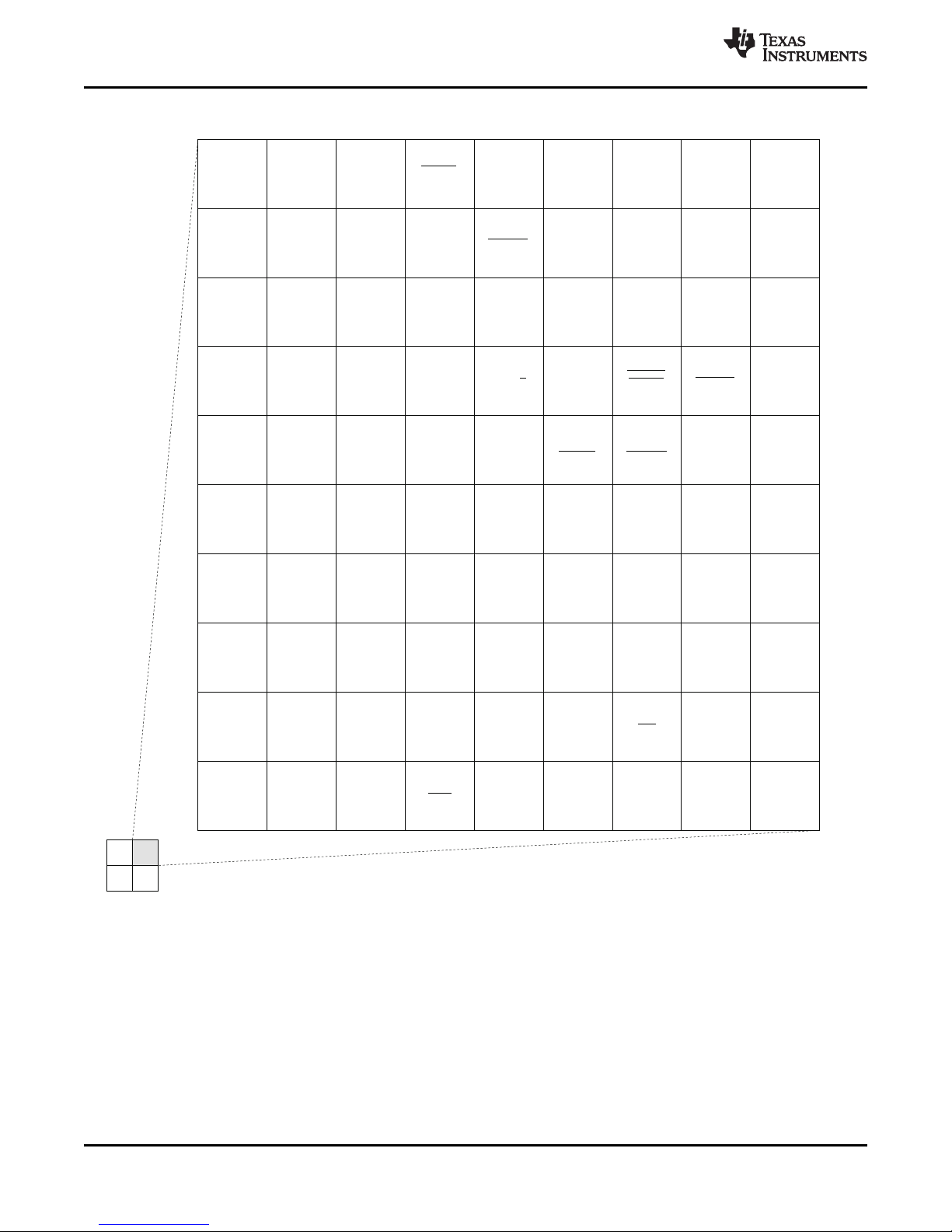

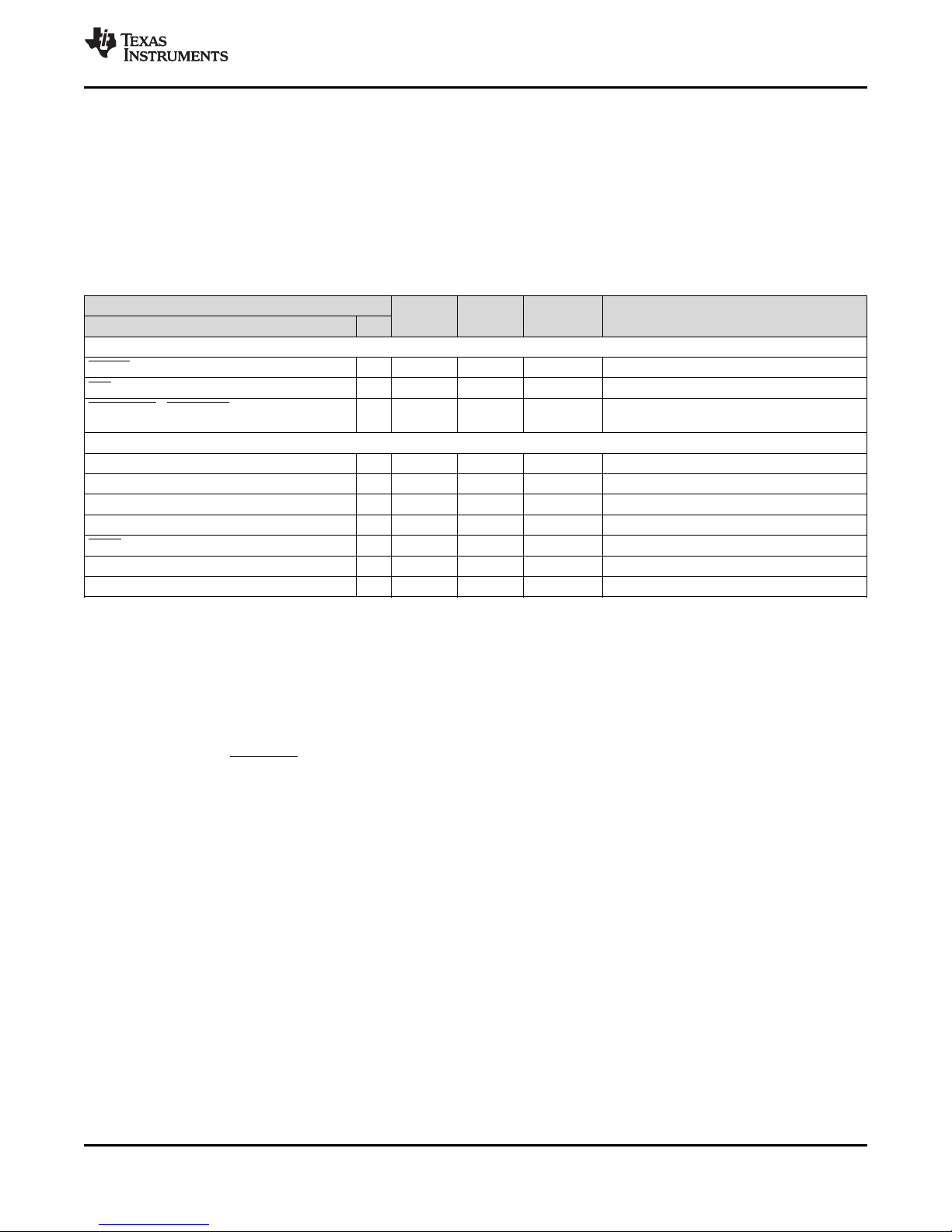

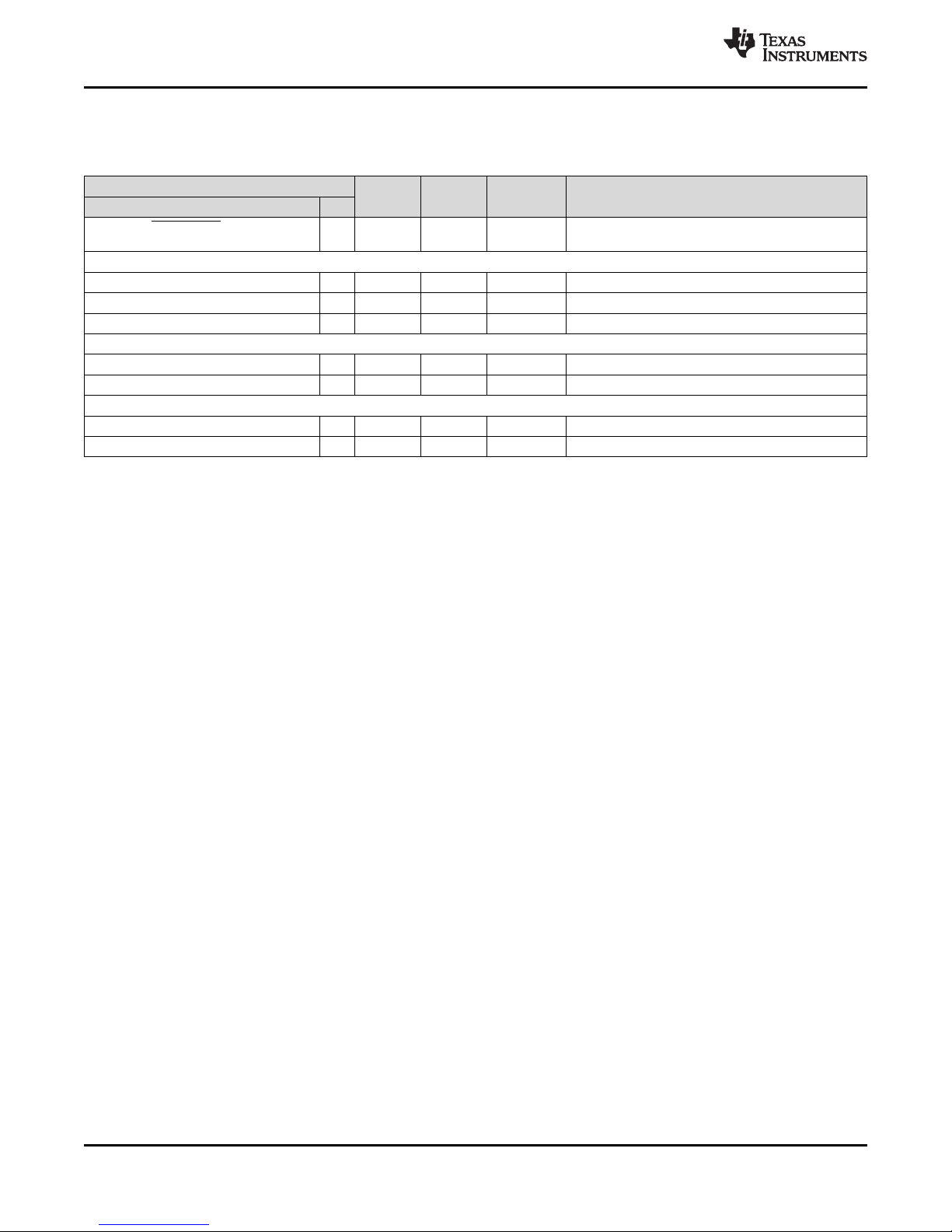

3.3.1 C674x DSP CPU Description

The C674x Central Processing Unit (CPU) consists of eight functional units, two register files, and two

data paths as shown in Figure 3-2. The two general-purpose register files (A and B) each contain 32 32bit registers for a total of 64 registers. The general-purpose registers can be used for data or can be data

address pointers. The data types supported include packed 8-bit data, packed 16-bit data, 32-bit data, 40bit data, and 64-bit data. Values larger than 32 bits, such as 40-bit-long or 64-bit-long values are stored in

register pairs, with the 32 LSBs of data placed in an even register and the remaining 8 or 32 MSBs in the

next upper register (which is always an odd-numbered register).

The eight functional units (.M1, .L1, .D1, .S1, .M2, .L2, .D2, and .S2) are each capable of executing one

instruction every clock cycle. The .M functional units perform all multiply operations. The .S and .L units

perform a general set of arithmetic, logical, and branch functions. The .D units primarily load data from

memory to the register file and store results from the register file into memory.

The C674x CPU combines the performance of the C64x+ core with the floating-point capabilities of the

C67x+ core.

Figure 3-1. C674x Megamodule Block Diagram

10

Device Comparison Copyright © 2009–2017, Texas Instruments Incorporated

Product Folder Links: TMS320C6748

Submit Documentation Feedback

Page 11

www.ti.com

Each C674x .M unit can perform one of the following each clock cycle: one 32 x 32 bit multiply, one 16 x

32 bit multiply, two 16 x 16 bit multiplies, two 16 x 32 bit multiplies, two 16 x 16 bit multiplies with

add/subtract capabilities, four 8 x 8 bit multiplies, four 8 x 8 bit multiplies with add operations, and four

16 x 16 multiplies with add/subtract capabilities (including a complex multiply). There is also support for

Galois field multiplication for 8-bit and 32-bit data. Many communications algorithms such as FFTs and

modems require complex multiplication. The complex multiply (CMPY) instruction takes for 16-bit inputs

and produces a 32-bit real and a 32-bit imaginary output. There are also complex multiplies with rounding

capability that produces one 32-bit packed output that contain 16-bit real and 16-bit imaginary values. The

32 x 32 bit multiply instructions provide the extended precision necessary for high-precision algorithms on

a variety of signed and unsigned 32-bit data types.

The .L or (Arithmetic Logic Unit) now incorporates the ability to do parallel add/subtract operations on a

pair of common inputs. Versions of this instruction exist to work on 32-bit data or on pairs of 16-bit data

performing dual 16-bit add and subtracts in parallel. There are also saturated forms of these instructions.

The C674x core enhances the .S unit in several ways. On the previous cores, dual 16-bit MIN2 and MAX2

comparisons were only available on the .L units. On the C674x core they are also available on the .S unit

which increases the performance of algorithms that do searching and sorting. Finally, to increase data

packing and unpacking throughput, the .S unit allows sustained high performance for the quad 8-bit/16-bit

and dual 16-bit instructions. Unpack instructions prepare 8-bit data for parallel 16-bit operations. Pack

instructions return parallel results to output precision including saturation support.

Other new features include:

• SPLOOP - A small instruction buffer in the CPU that aids in creation of software pipelining loops where

• Compact Instructions - The native instruction size for the C6000 devices is 32 bits. Many common

• Instruction Set Enhancement - As noted above, there are new instructions such as 32-bit

• Exceptions Handling - Intended to aid the programmer in isolating bugs. The C674x CPU is able to

• Privilege - Defines user and supervisor modes of operation, allowing the operating system to give a

• Time-Stamp Counter - Primarily targeted for Real-Time Operating System (RTOS) robustness, a free-

TMS320C6748

SPRS590G –JUNE 2009–REVISED JANUARY 2017

multiple iterations of a loop are executed in parallel. The SPLOOP buffer reduces the code size

associated with software pipelining. Furthermore, loops in the SPLOOP buffer are fully interruptible.

instructions such as MPY, AND, OR, ADD, and SUB can be expressed as 16 bits if the C674x

compiler can restrict the code to use certain registers in the register file. This compression is

performed by the code generation tools.

multiplications, complex multiplications, packing, sorting, bit manipulation, and 32-bit Galois field

multiplication.

detect and respond to exceptions, both from internally detected sources (such as illegal op-codes) and

from system events (such as a watchdog time expiration).

basic level of protection to sensitive resources. Local memory is divided into multiple pages, each with

read, write, and execute permissions.

running time-stamp counter is implemented in the CPU which is not sensitive to system stalls.

For more details on the C674x CPU and its enhancements over the C64x architecture, see the following

documents:

• TMS320C64x/C64x+ DSP CPU and Instruction Set Reference Guide (literature number SPRUFE8)

• TMS320C64x Technical Overview (literature number SPRU395)

Submit Documentation Feedback

Product Folder Links: TMS320C6748

Device ComparisonCopyright © 2009–2017, Texas Instruments Incorporated

11

Page 12

src2

src2

.D1

.M1

.S1

.L1

long src

odd dst

src2

src1

src1

src1

src1

even dst

even dst

odd dst

dst1

dst

src2

src2

src2

long src

DA1

ST1b

LD1b

LD1a

ST1a

Data path A

Odd

register

file A

(A1, A3,

A5...A31)

Odd

register

file B

(B1, B3,

B5...B31)

.D2

src1

dst

src2

DA2

LD2a

LD2b

src2

.M2

src1

dst1

.S2

src1

even dst

long src

odd dst

ST2a

ST2b

long src

.L2

even dst

odd dst

src1

Data path B

Control Register

32 MSB

32 LSB

dst2

(A)

32 MSB

32 LSB

2x

1x

32 LSB

32 MSB

32 LSB

32 MSB

dst2

(B)

(B)

(A)

8

8

8

8

32

32

32

32

(C)

(C)

Even

register

file A

(A0, A2,

A4...A30)

Even

register

file B

(B0, B2,

B4...B30)

(D)

(D)

(D)

(D)

A. On .M unit, dst2 is 32 MSB.

B. On .M unit, dst1 is 32 LSB.

C. On C64x CPU .M unit, src2 is 32 bits; on C64x+ CPU .M unit, src2 is 64 bits.

D. On .L and .S units, odd dst connects to odd register files and even dst connects to even register files.

TMS320C6748

SPRS590G –JUNE 2009–REVISED JANUARY 2017

www.ti.com

12

Device Comparison Copyright © 2009–2017, Texas Instruments Incorporated

Figure 3-2. TMS320C674x CPU (DSP Core) Data Paths

Product Folder Links: TMS320C6748

Submit Documentation Feedback

Page 13

www.ti.com

3.3.2 DSP Memory Mapping

The DSP memory map is shown in Section 3.4.

By default the DSP also has access to most on and off chip memory areas.

Additionally, the DSP megamodule includes the capability to limit access to its internal memories through

its SDMA port; without needing an external MPU unit.

3.3.2.1 External Memories

The DSP has access to the following External memories:

• Asynchronous EMIF / SDRAM / NAND / NOR Flash (EMIFA)

• SDRAM (DDR2)

3.3.2.2 DSP Internal Memories

The DSP has access to the following DSP memories:

• L2 RAM

• L1P RAM

• L1D RAM

3.3.2.3 C674x CPU

TMS320C6748

SPRS590G –JUNE 2009–REVISED JANUARY 2017

The C674x core uses a two-level cache-based architecture. The Level 1 Program cache (L1P) is 32 KB

direct mapped cache and the Level 1 Data cache (L1D) is 32 KB 2-way set associated cache. The Level 2

memory/cache (L2) consists of a 256 KB memory space that is shared between program and data space.

L2 memory can be configured as mapped memory, cache, or a combination of both.

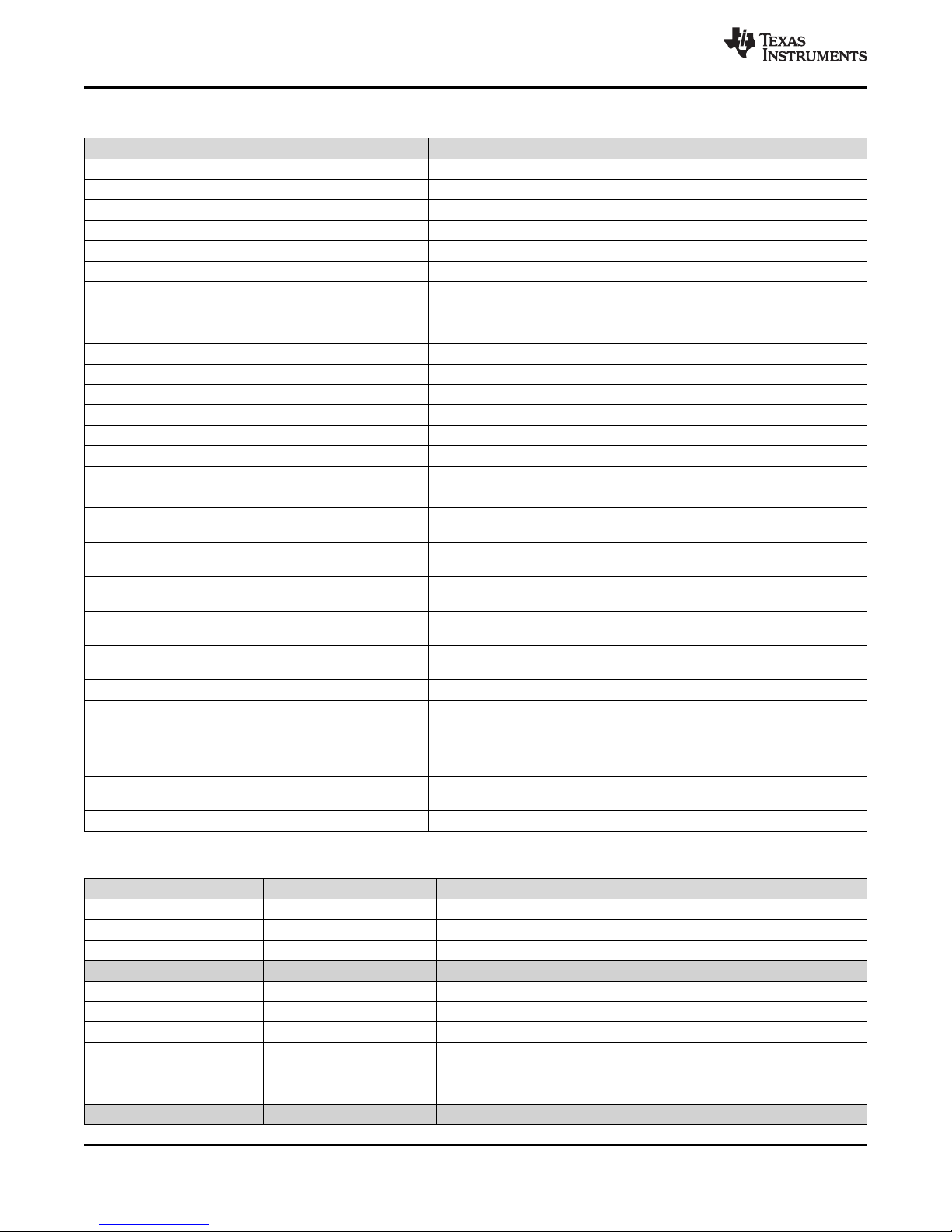

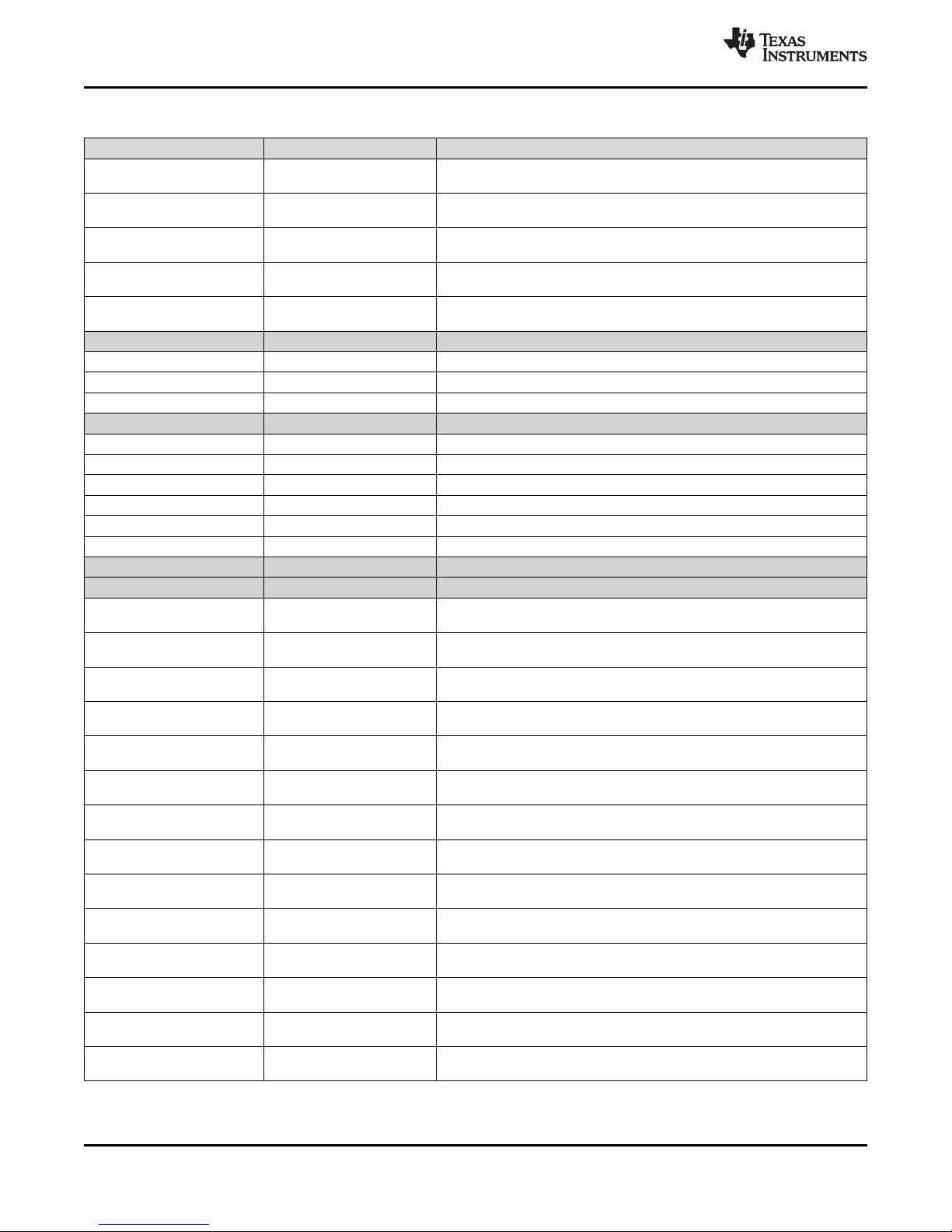

Table 3-2 shows a memory map of the C674x CPU cache registers for the device.

Table 3-2. C674x Cache Registers

Byte Address Register Name Register Description

0x0184 0000 L2CFG L2 Cache configuration register

0x0184 0020 L1PCFG L1P Size Cache configuration register

0x0184 0024 L1PCC L1P Freeze Mode Cache configuration register

0x0184 0040 L1DCFG L1D Size Cache configuration register

0x0184 0044 L1DCC L1D Freeze Mode Cache configuration register

0x0184 0048 - 0x0184 0FFC - Reserved

0x0184 1000 EDMAWEIGHT L2 EDMA access control register

0x0184 1004 - 0x0184 1FFC - Reserved

0x0184 2000 L2ALLOC0 L2 allocation register 0

0x0184 2004 L2ALLOC1 L2 allocation register 1

0x0184 2008 L2ALLOC2 L2 allocation register 2

0x0184 200C L2ALLOC3 L2 allocation register 3

0x0184 2010 - 0x0184 3FFF - Reserved

0x0184 4000 L2WBAR L2 writeback base address register

0x0184 4004 L2WWC L2 writeback word count register

0x0184 4010 L2WIBAR L2 writeback invalidate base address register

0x0184 4014 L2WIWC L2 writeback invalidate word count register

0x0184 4018 L2IBAR L2 invalidate base address register

0x0184 401C L2IWC L2 invalidate word count register

0x0184 4020 L1PIBAR L1P invalidate base address register

0x0184 4024 L1PIWC L1P invalidate word count register

0x0184 4030 L1DWIBAR L1D writeback invalidate base address register

Submit Documentation Feedback

Product Folder Links: TMS320C6748

Device ComparisonCopyright © 2009–2017, Texas Instruments Incorporated

13

Page 14

TMS320C6748

SPRS590G –JUNE 2009–REVISED JANUARY 2017

Table 3-2. C674x Cache Registers (continued)

Byte Address Register Name Register Description

0x0184 4034 L1DWIWC L1D writeback invalidate word count register

0x0184 4038 - Reserved

0x0184 4040 L1DWBAR L1D Block Writeback

0x0184 4044 L1DWWC L1D Block Writeback

0x0184 4048 L1DIBAR L1D invalidate base address register

0x0184 404C L1DIWC L1D invalidate word count register

0x0184 4050 - 0x0184 4FFF - Reserved

0x0184 5000 L2WB L2 writeback all register

0x0184 5004 L2WBINV L2 writeback invalidate all register

0x0184 5008 L2INV L2 Global Invalidate without writeback

0x0184 500C - 0x0184 5027 - Reserved

0x0184 5028 L1PINV L1P Global Invalidate

0x0184 502C - 0x0184 5039 - Reserved

0x0184 5040 L1DWB L1D Global Writeback

0x0184 5044 L1DWBINV L1D Global Writeback with Invalidate

0x0184 5048 L1DINV L1D Global Invalidate without writeback

0x0184 8000 – 0x0184 80FF MAR0 - MAR63 Reserved 0x0000 0000 – 0x3FFF FFFF

0x0184 8100 – 0x0184 817F MAR64 – MAR95

0x0184 8180 – 0x0184 8187 MAR96 - MAR97

0x0184 8188 – 0x0184 818F MAR98 – MAR99

0x0184 8190 – 0x0184 8197 MAR100 – MAR101

0x0184 8198 – 0x0184 819F MAR102 – MAR103

0x0184 81A0 – 0x0184 81FF MAR104 – MAR127 Reserved 0x6800 0000 – 0x7FFF FFFF

0x0184 8200 MAR128

0x0184 8204 – 0x0184 82FF MAR129 – MAR191 Reserved 0x8200 0000 – 0xBFFF FFFF

0x0184 8300 – 0x0184 837F MAR192 – MAR223

0x0184 8380 – 0x0184 83FF MAR224 – MAR255 Reserved 0xE000 0000 – 0xFFFF FFFF

Memory Attribute Registers for EMIFA SDRAM Data (CS0)

External memory addresses 0x4000 0000 – 0x5FFF FFFF

Memory Attribute Registers for EMIFA Async Data (CS2)

External memory addresses 0x6000 0000 – 0x61FF FFFF

Memory Attribute Registers for EMIFA Async Data (CS3)

External memory addresses 0x6200 0000 – 0x63FF FFFF

Memory Attribute Registers for EMIFA Async Data (CS4)

External memory addresses 0x6400 0000 – 0x65FF FFFF

Memory Attribute Registers for EMIFA Async Data (CS5)

External memory addresses 0x6600 0000 – 0x67FF FFFF

Memory Attribute Register for RAM

External memory addresses 0x8000 0000 – 0x8001 FFFF

Reserved 0x8002 0000 – 0x81FF FFFF

Memory Attribute Registers for DDR2 Data (CS2)

External memory addresses 0xC000 0000 – 0xDFFF FFFF

www.ti.com

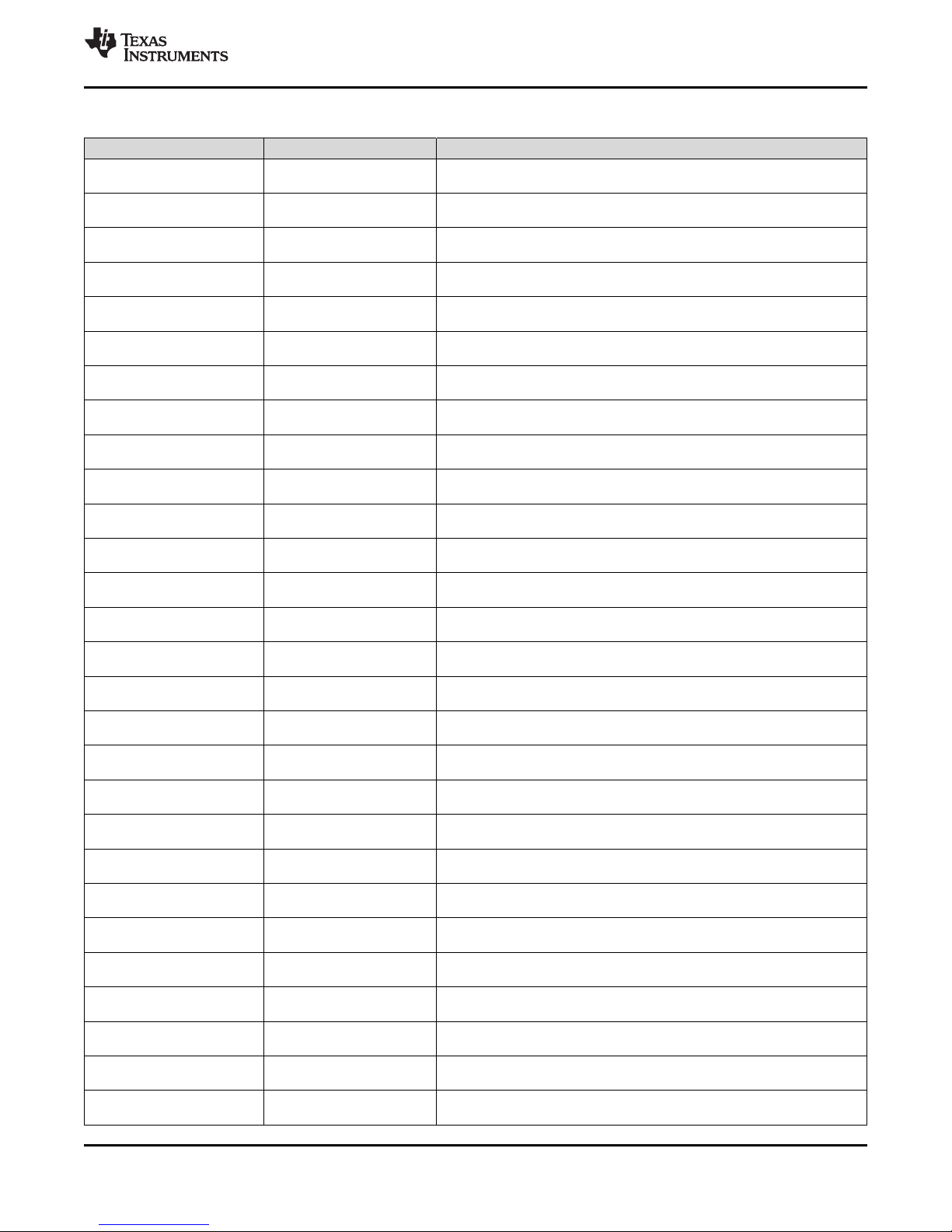

Table 3-3. C674x L1/L2 Memory Protection Registers

HEX ADDRESS RANGE REGISTER ACRONYM DESCRIPTION

0x0184 A000 L2MPFAR L2 memory protection fault address register

0x0184 A004 L2MPFSR L2 memory protection fault status register

0x0184 A008 L2MPFCR L2 memory protection fault command register

0x0184 A00C - 0x0184 A0FF - Reserved

0x0184 A100 L2MPLK0 L2 memory protection lock key bits [31:0]

0x0184 A104 L2MPLK1 L2 memory protection lock key bits [63:32]

0x0184 A108 L2MPLK2 L2 memory protection lock key bits [95:64]

0x0184 A10C L2MPLK3 L2 memory protection lock key bits [127:96]

0x0184 A110 L2MPLKCMD L2 memory protection lock key command register

0x0184 A114 L2MPLKSTAT L2 memory protection lock key status register

0x0184 A118 - 0x0184 A1FF - Reserved

14

Device Comparison Copyright © 2009–2017, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: TMS320C6748

Page 15

www.ti.com

SPRS590G –JUNE 2009–REVISED JANUARY 2017

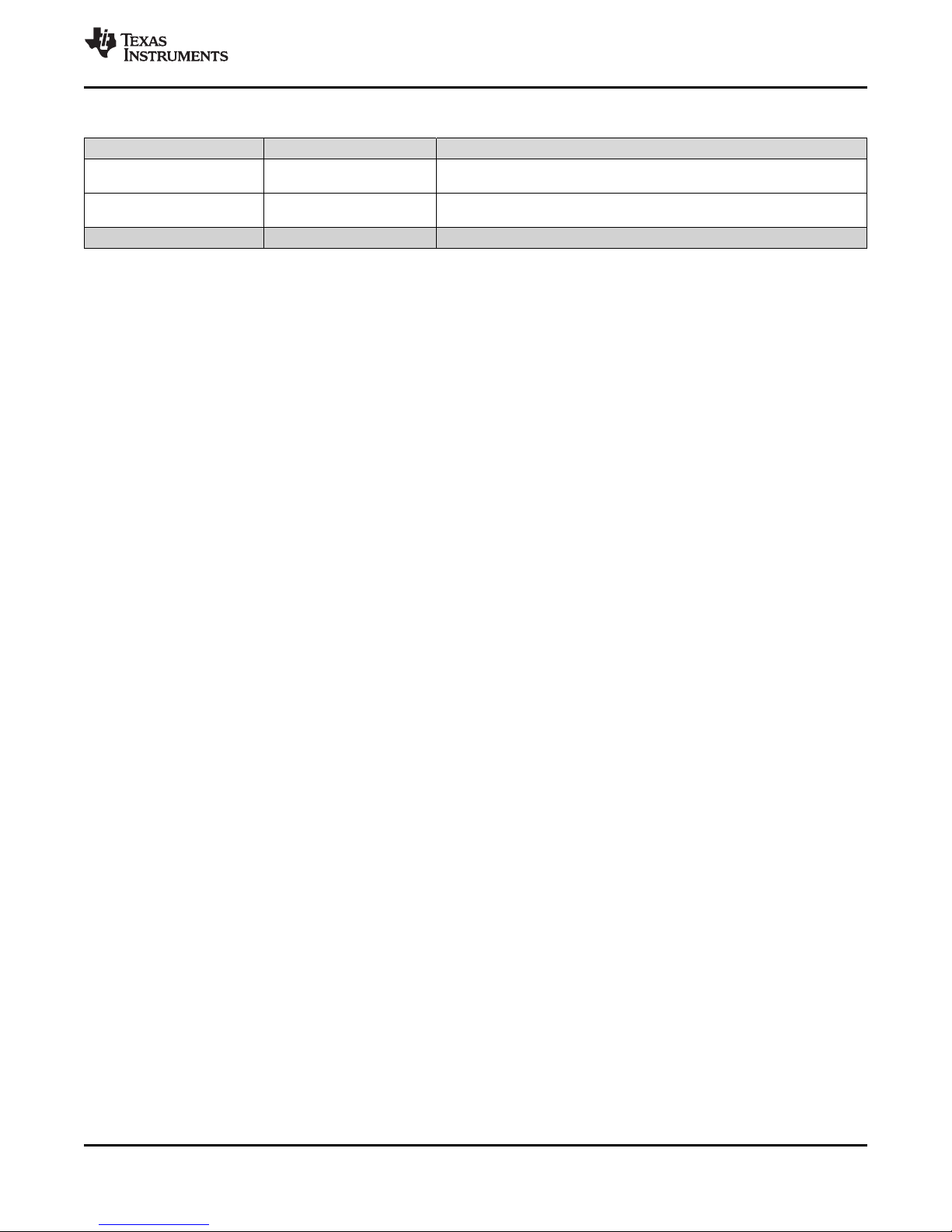

Table 3-3. C674x L1/L2 Memory Protection Registers (continued)

HEX ADDRESS RANGE REGISTER ACRONYM DESCRIPTION

0x0184 A200 L2MPPA0

0x0184 A204 L2MPPA1

0x0184 A208 L2MPPA2

0x0184 A20C L2MPPA3

0x0184 A210 L2MPPA4

0x0184 A214 L2MPPA5

0x0184 A218 L2MPPA6

0x0184 A21C L2MPPA7

0x0184 A220 L2MPPA8

0x0184 A224 L2MPPA9

0x0184 A228 L2MPPA10

0x0184 A22C L2MPPA11

0x0184 A230 L2MPPA12

0x0184 A234 L2MPPA13

0x0184 A238 L2MPPA14

0x0184 A23C L2MPPA15

0x0184 A240 L2MPPA16

0x0184 A244 L2MPPA17

0x0184 A248 L2MPPA18

0x0184 A24C L2MPPA19

0x0184 A250 L2MPPA20

0x0184 A254 L2MPPA21

0x0184 A258 L2MPPA22

0x0184 A25C L2MPPA23

0x0184 A260 L2MPPA24

0x0184 A264 L2MPPA25

0x0184 A268 L2MPPA26

0x0184 A26C L2MPPA27

L2 memory protection page attribute register 0 (controls memory address

0x0080 0000 - 0x0080 1FFF)

L2 memory protection page attribute register 1 (controls memory address

0x0080 2000 - 0x0080 3FFF)

L2 memory protection page attribute register 2 (controls memory address

0x0080 4000 - 0x0080 5FFF)

L2 memory protection page attribute register 3 (controls memory address

0x0080 6000 - 0x0080 7FFF)

L2 memory protection page attribute register 4 (controls memory address

0x0080 8000 - 0x0080 9FFF)

L2 memory protection page attribute register 5 (controls memory address

0x0080 A000 - 0x0080 BFFF)

L2 memory protection page attribute register 6 (controls memory address

0x0080 C000 - 0x0080 DFFF)

L2 memory protection page attribute register 7 (controls memory address

0x0080 E000 - 0x0080 FFFF)

L2 memory protection page attribute register 8 (controls memory address

0x0081 0000 - 0x0081 1FFF)

L2 memory protection page attribute register 9 (controls memory address

0x0081 2000 - 0x0081 3FFF)

L2 memory protection page attribute register 10 (controls memory address

0x0081 4000 - 0x0081 5FFF)

L2 memory protection page attribute register 11 (controls memory address

0x0081 6000 - 0x0081 7FFF)

L2 memory protection page attribute register 12 (controls memory address

0x0081 8000 - 0x0081 9FFF)

L2 memory protection page attribute register 13 (controls memory address

0x0081 A000 - 0x0081 BFFF)

L2 memory protection page attribute register 14 (controls memory address

0x0081 C000 - 0x0081 DFFF)

L2 memory protection page attribute register 15 (controls memory address

0x0081 E000 - 0x0081 FFFF)

L2 memory protection page attribute register 16 (controls memory address

0x0082 0000 - 0x0082 1FFF)

L2 memory protection page attribute register 17 (controls memory address

0x0082 2000 - 0x0082 3FFF)

L2 memory protection page attribute register 18 (controls memory address

0x0082 4000 - 0x0082 5FFF)

L2 memory protection page attribute register 19 (controls memory address

0x0082 6000 - 0x0082 7FFF)

L2 memory protection page attribute register 20 (controls memory address

0x0082 8000 - 0x0082 9FFF)

L2 memory protection page attribute register 21 (controls memory address

0x0082 A000 - 0x0082 BFFF)

L2 memory protection page attribute register 22 (controls memory address

0x0082 C000 - 0x0082 DFFF)

L2 memory protection page attribute register 23 (controls memory address

0x0082 E000 - 0x0082 FFFF)

L2 memory protection page attribute register 24 (controls memory address

0x0083 0000 - 0x0083 1FFF)

L2 memory protection page attribute register 25 (controls memory address

0x0083 2000 - 0x0083 3FFF)

L2 memory protection page attribute register 26 (controls memory address

0x0083 4000 - 0x0083 5FFF)

L2 memory protection page attribute register 27 (controls memory address

0x0083 6000 - 0x0083 7FFF)

TMS320C6748

Submit Documentation Feedback

Product Folder Links: TMS320C6748

Device ComparisonCopyright © 2009–2017, Texas Instruments Incorporated

15

Page 16

TMS320C6748

SPRS590G –JUNE 2009–REVISED JANUARY 2017

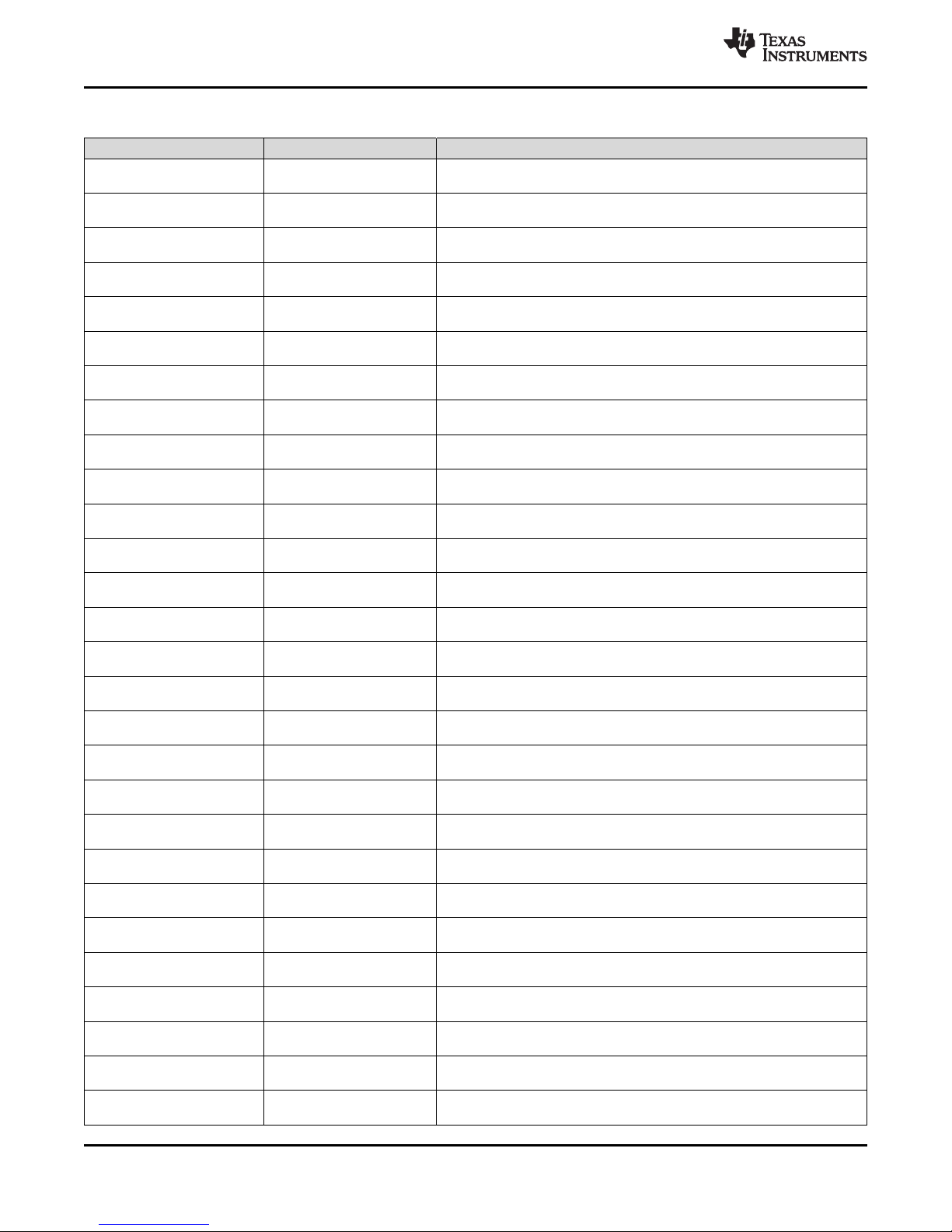

Table 3-3. C674x L1/L2 Memory Protection Registers (continued)

HEX ADDRESS RANGE REGISTER ACRONYM DESCRIPTION

0x0184 A270 L2MPPA28

0x0184 A274 L2MPPA29

0x0184 A278 L2MPPA30

0x0184 A27C L2MPPA31

0x0184 A280 L2MPPA32

0x0184 A284 L2MPPA33

0x0184 A288 L2MPPA34

0x0184 A28C L2MPPA35

0x0184 A290 L2MPPA36

0x0184 A294 L2MPPA37

0x0184 A298 L2MPPA38

0x0184 A29C L2MPPA39

0x0184 A2A0 L2MPPA40

0x0184 A2A4 L2MPPA41

0x0184 A2A8 L2MPPA42

0x0184 A2AC L2MPPA43

0x0184 A2B0 L2MPPA44

0x0184 A2B4 L2MPPA45

0x0184 A2B8 L2MPPA46

0x0184 A2BC L2MPPA47

0x0184 A2C0 L2MPPA48

0x0184 A2C4 L2MPPA49

0x0184 A2C8 L2MPPA50

0x0184 A2CC L2MPPA51

0x0184 A2D0 L2MPPA52

0x0184 A2D4 L2MPPA53

0x0184 A2D8 L2MPPA54

0x0184 A2DC L2MPPA55

L2 memory protection page attribute register 28 (controls memory address

0x0083 8000 - 0x0083 9FFF)

L2 memory protection page attribute register 29 (controls memory address

0x0083 A000 - 0x0083 BFFF)

L2 memory protection page attribute register 30 (controls memory address

0x0083 C000 - 0x0083 DFFF)

L2 memory protection page attribute register 31 (controls memory address

0x0083 E000 - 0x0083 FFFF)

L2 memory protection page attribute register 32 (controls memory address

0x0070 0000 - 0x0070 7FFF)

L2 memory protection page attribute register 33 (controls memory address

0x0070 8000 - 0x0070 FFFF)

L2 memory protection page attribute register 34 (controls memory address

0x0071 0000 - 0x0071 7FFF)

L2 memory protection page attribute register 35 (controls memory address

0x0071 8000 - 0x0071 FFFF)

L2 memory protection page attribute register 36 (controls memory address

0x0072 0000 - 0x0072 7FFF)

L2 memory protection page attribute register 37 (controls memory address

0x0072 8000 - 0x0072 FFFF)

L2 memory protection page attribute register 38 (controls memory address

0x0073 0000 - 0x0073 7FFF)

L2 memory protection page attribute register 39 (controls memory address

0x0073 8000 - 0x0073 FFFF)

L2 memory protection page attribute register 40 (controls memory address

0x0074 0000 - 0x0074 7FFF)

L2 memory protection page attribute register 41 (controls memory address

0x0074 8000 - 0x0074 FFFF)

L2 memory protection page attribute register 42 (controls memory address

0x0075 0000 - 0x0075 7FFF)

L2 memory protection page attribute register 43 (controls memory address

0x0075 8000 - 0x0075 FFFF)

L2 memory protection page attribute register 44 (controls memory address

0x0076 0000 - 0x0076 7FFF)

L2 memory protection page attribute register 45 (controls memory address

0x0076 8000 - 0x0076 FFFF)

L2 memory protection page attribute register 46 (controls memory address

0x0077 0000 - 0x0077 7FFF)

L2 memory protection page attribute register 47 (controls memory address

0x0077 8000 - 0x0077 FFFF)

L2 memory protection page attribute register 48 (controls memory address

0x0078 0000 - 0x0078 7FFF)

L2 memory protection page attribute register 49 (controls memory address

0x0078 8000 - 0x0078 FFFF)

L2 memory protection page attribute register 50 (controls memory address

0x0079 0000 - 0x0079 7FFF)

L2 memory protection page attribute register 51 (controls memory address

0x0079 8000 - 0x0079 FFFF)

L2 memory protection page attribute register 52 (controls memory address

0x007A 0000 - 0x007A 7FFF)

L2 memory protection page attribute register 53 (controls memory address

0x007A 8000 - 0x007A FFFF)

L2 memory protection page attribute register 54 (controls memory address

0x007B 0000 - 0x007B 7FFF)

L2 memory protection page attribute register 55 (controls memory address

0x007B 8000 - 0x007B FFFF)

www.ti.com

16

Device Comparison Copyright © 2009–2017, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: TMS320C6748

Page 17

www.ti.com

SPRS590G –JUNE 2009–REVISED JANUARY 2017

Table 3-3. C674x L1/L2 Memory Protection Registers (continued)

HEX ADDRESS RANGE REGISTER ACRONYM DESCRIPTION

0x0184 A2E0 L2MPPA56

0x0184 A2E4 L2MPPA57

0x0184 A2E8 L2MPPA58

0x0184 A2EC L2MPPA59

0x0184 A2F0 L2MPPA60

0x0184 A2F4 L2MPPA61

0x0184 A2F8 L2MPPA62

0x0184 A2FC L2MPPA63

0x0184 A300 - 0x0184 A3FF - Reserved

0x0184 A400 L1PMPFAR L1P memory protection fault address register

0x0184 A404 L1PMPFSR L1P memory protection fault status register

0x0184 A408 L1PMPFCR L1P memory protection fault command register

0x0184 A40C - 0x0184 A4FF - Reserved

0x0184 A500 L1PMPLK0 L1P memory protection lock key bits [31:0]

0x0184 A504 L1PMPLK1 L1P memory protection lock key bits [63:32]

0x0184 A508 L1PMPLK2 L1P memory protection lock key bits [95:64]

0x0184 A50C L1PMPLK3 L1P memory protection lock key bits [127:96]

0x0184 A510 L1PMPLKCMD L1P memory protection lock key command register

0x0184 A514 L1PMPLKSTAT L1P memory protection lock key status register

0x0184 A518 - 0x0184 A5FF - Reserved

0x0184 A600 - 0x0184 A63F - Reserved

0x0184 A640 L1PMPPA16

0x0184 A644 L1PMPPA17

0x0184 A648 L1PMPPA18

0x0184 A64C L1PMPPA19

0x0184 A650 L1PMPPA20

0x0184 A654 L1PMPPA21

0x0184 A658 L1PMPPA22

0x0184 A65C L1PMPPA23

0x0184 A660 L1PMPPA24

0x0184 A664 L1PMPPA25

0x0184 A668 L1PMPPA26

L2 memory protection page attribute register 56 (controls memory address

0x007C 0000 - 0x007C 7FFF)

L2 memory protection page attribute register 57 (controls memory address

0x007C 8000 - 0x007C FFFF)

L2 memory protection page attribute register 58 (controls memory address

0x007D 0000 - 0x007D 7FFF)

L2 memory protection page attribute register 59 (controls memory address

0x007D 8000 - 0x007D FFFF)

L2 memory protection page attribute register 60 (controls memory address

0x007E 0000 - 0x007E 7FFF)

L2 memory protection page attribute register 61 (controls memory address

0x007E 8000 - 0x007E FFFF)

L2 memory protection page attribute register 62 (controls memory address

0x007F 0000 - 0x007F 7FFF)

L2 memory protection page attribute register 63 (controls memory address

0x007F 8000 - 0x007F FFFF)

(1)

L1P memory protection page attribute register 16 (controls memory address

0x00E0 0000 - 0x00E0 07FF)

L1P memory protection page attribute register 17 (controls memory address

0x00E0 0800 - 0x00E0 0FFF)

L1P memory protection page attribute register 18 (controls memory address

0x00E0 1000 - 0x00E0 17FF)

L1P memory protection page attribute register 19 (controls memory address

0x00E0 1800 - 0x00E0 1FFF)

L1P memory protection page attribute register 20 (controls memory address

0x00E0 2000 - 0x00E0 27FF)

L1P memory protection page attribute register 21 (controls memory address

0x00E0 2800 - 0x00E0 2FFF)

L1P memory protection page attribute register 22 (controls memory address

0x00E0 3000 - 0x00E0 37FF)

L1P memory protection page attribute register 23 (controls memory address

0x00E0 3800 - 0x00E0 3FFF)

L1P memory protection page attribute register 24 (controls memory address

0x00E0 4000 - 0x00E0 47FF)

L1P memory protection page attribute register 25 (controls memory address

0x00E0 4800 - 0x00E0 4FFF)

L1P memory protection page attribute register 26 (controls memory address

0x00E0 5000 - 0x00E0 57FF)

TMS320C6748

(1) These addresses correspond to the L1P memory protection page attribute registers 0-15 (L1PMPPA0-L1PMPPA15) of the C674x

megamaodule. These registers are not supported for this device.

Submit Documentation Feedback

Product Folder Links: TMS320C6748

Device ComparisonCopyright © 2009–2017, Texas Instruments Incorporated

17

Page 18

TMS320C6748

SPRS590G –JUNE 2009–REVISED JANUARY 2017

Table 3-3. C674x L1/L2 Memory Protection Registers (continued)

HEX ADDRESS RANGE REGISTER ACRONYM DESCRIPTION

0x0184 A66C L1PMPPA27

0x0184 A670 L1PMPPA28

0x0184 A674 L1PMPPA29

0x0184 A678 L1PMPPA30

0x0184 A67C L1PMPPA31

0x0184 A67F – 0x0184 ABFF - Reserved

0x0184 AC00 L1DMPFAR L1D memory protection fault address register

0x0184 AC04 L1DMPFSR L1D memory protection fault status register

0x0184 AC08 L1DMPFCR L1D memory protection fault command register

0x0184 AC0C - 0x0184 ACFF - Reserved

0x0184 AD00 L1DMPLK0 L1D memory protection lock key bits [31:0]

0x0184 AD04 L1DMPLK1 L1D memory protection lock key bits [63:32]

0x0184 AD08 L1DMPLK2 L1D memory protection lock key bits [95:64]

0x0184 AD0C L1DMPLK3 L1D memory protection lock key bits [127:96]

0x0184 AD10 L1DMPLKCMD L1D memory protection lock key command register

0x0184 AD14 L1DMPLKSTAT L1D memory protection lock key status register

0x0184 AD18 - 0x0184 ADFF - Reserved

0x0184 AE00 - 0x0184 AE3F - Reserved

0x0184 AE40 L1DMPPA16

0x0184 AE44 L1DMPPA17

0x0184 AE48 L1DMPPA18

0x0184 AE4C L1DMPPA19

0x0184 AE50 L1DMPPA20

0x0184 AE54 L1DMPPA21

0x0184 AE58 L1DMPPA22

0x0184 AE5C L1DMPPA23

0x0184 AE60 L1DMPPA24

0x0184 AE64 L1DMPPA25

0x0184 AE68 L1DMPPA26

0x0184 AE6C L1DMPPA27

0x0184 AE70 L1DMPPA28

0x0184 AE74 L1DMPPA29

L1P memory protection page attribute register 27 (controls memory address

0x00E0 5800 - 0x00E0 5FFF)

L1P memory protection page attribute register 28 (controls memory address

0x00E0 6000 - 0x00E0 67FF)

L1P memory protection page attribute register 29 (controls memory address

0x00E0 6800 - 0x00E0 6FFF)

L1P memory protection page attribute register 30 (controls memory address

0x00E0 7000 - 0x00E0 77FF)

L1P memory protection page attribute register 31 (controls memory address

0x00E0 7800 - 0x00E0 7FFF)

(2)

L1D memory protection page attribute register 16 (controls memory address

0x00F0 0000 - 0x00F0 07FF)

L1D memory protection page attribute register 17 (controls memory address

0x00F0 0800 - 0x00F0 0FFF)

L1D memory protection page attribute register 18 (controls memory address

0x00F0 1000 - 0x00F0 17FF)

L1D memory protection page attribute register 19 (controls memory address

0x00F0 1800 - 0x00F0 1FFF)

L1D memory protection page attribute register 20 (controls memory address

0x00F0 2000 - 0x00F0 27FF)

L1D memory protection page attribute register 21 (controls memory address

0x00F0 2800 - 0x00F0 2FFF)

L1D memory protection page attribute register 22 (controls memory address

0x00F0 3000 - 0x00F0 37FF)

L1D memory protection page attribute register 23 (controls memory address

0x00F0 3800 - 0x00F0 3FFF)

L1D memory protection page attribute register 24 (controls memory address

0x00F0 4000 - 0x00F0 47FF)

L1D memory protection page attribute register 25 (controls memory address

0x00F0 4800 - 0x00F0 4FFF)

L1D memory protection page attribute register 26 (controls memory address

0x00F0 5000 - 0x00F0 57FF)

L1D memory protection page attribute register 27 (controls memory address

0x00F0 5800 - 0x00F0 5FFF)

L1D memory protection page attribute register 28 (controls memory address

0x00F0 6000 - 0x00F0 67FF)

L1D memory protection page attribute register 29 (controls memory address

0x00F0 6800 - 0x00F0 6FFF)

www.ti.com

(2) These addresses correspond to the L1D memory protection page attribute registers 0-15 (L1DMPPA0-L1DMPPA15) of the C674x

megamaodule. These registers are not supported for this device.

18

Device Comparison Copyright © 2009–2017, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: TMS320C6748

Page 19

www.ti.com

SPRS590G –JUNE 2009–REVISED JANUARY 2017

Table 3-3. C674x L1/L2 Memory Protection Registers (continued)

HEX ADDRESS RANGE REGISTER ACRONYM DESCRIPTION

0x0184 AE78 L1DMPPA30

0x0184 AE7C L1DMPPA31

0x0184 AE80 – 0x0185 FFFF - Reserved

L1D memory protection page attribute register 30 (controls memory address

0x00F0 7000 - 0x00F0 77FF)

L1D memory protection page attribute register 31 (controls memory address

0x00F0 7800 - 0x00F0 7FFF)

TMS320C6748

Submit Documentation Feedback

Product Folder Links: TMS320C6748

Device ComparisonCopyright © 2009–2017, Texas Instruments Incorporated

19

Page 20

TMS320C6748

SPRS590G –JUNE 2009–REVISED JANUARY 2017

3.4 Memory Map Summary

Note: Read/Write accesses to illegal or reserved addresses in the memory map may cause undefined

behavior.

Table 3-4. C6748 Top Level Memory Map

Start Address End Address Size DSP Mem Map EDMA Mem Map PRUSS Mem Map Master

0x0000 0000 0x0000 0FFF 4K PRUSS Local

0x0000 1000 0x006F FFFF

0x0070 0000 0x007F FFFF 1024K DSP L2 ROM

0x0080 0000 0x0083 FFFF 256K DSP L2 RAM

0x0084 0000 0x00DF FFFF

0x00E0 0000 0x00E0 7FFF 32K DSP L1P RAM

0x00E0 8000 0x00EF FFFF

0x00F0 0000 0x00F0 7FFF 32K DSP L1D RAM

0x00F0 8000 0x017F FFFF

0x0180 0000 0x0180 FFFF 64K DSP Interrupt

0x0181 0000 0x0181 0FFF 4K DSP Powerdown

0x0181 1000 0x0181 1FFF 4K DSP Security ID

0x0181 2000 0x0181 2FFF 4K DSP Revision ID

0x0181 3000 0x0181 FFFF 52K

0x0182 0000 0x0182 FFFF 64K DSP EMC

0x0183 0000 0x0183 FFFF 64K DSP Internal

0x0184 0000 0x0184 FFFF 64K DSP Memory

0x0185 0000 0x01BF FFFF

0x01C0 0000 0x01C0 7FFF 32K EDMA3 CC

0x01C0 8000 0x01C0 83FF 1K EDMA3 TC0

0x01C0 8400 0x01C0 87FF 1K EDMA3 TC1

0x01C0 8800 0x01C0 FFFF

0x01C1 0000 0x01C1 0FFF 4K PSC 0

0x01C1 1000 0x01C1 1FFF 4K PLL Controller 0

0x01C1 2000 0x01C1 3FFF

0x01C1 4000 0x01C1 4FFF 4K SYSCFG0

0x01C1 5000 0x01C1 FFFF

0x01C2 0000 0x01C2 0FFF 4K Timer0

0x01C2 1000 0x01C2 1FFF 4K Timer1

0x01C2 2000 0x01C2 2FFF 4K I2C 0

0x01C2 3000 0x01C2 3FFF 4K RTC

0x01C2 4000 0x01C3 FFFF

0x01C4 0000 0x01C4 0FFF 4K MMC/SD 0

0x01C4 1000 0x01C4 1FFF 4K SPI 0

0x01C4 2000 0x01C4 2FFF 4K UART 0

0x01C4 3000 0x01CF FFFF

0x01D0 0000 0x01D0 0FFF 4K McASP 0 Control

0x01D0 1000 0x01D0 1FFF 4K McASP 0 AFIFO Ctrl

(1) The DSP L2 ROM is used for boot purposes and cannot be programmed with application code

20

Device Comparison Copyright © 2009–2017, Texas Instruments Incorporated

Controller

Controller

Reserved

System

Product Folder Links: TMS320C6748

(1)

Submit Documentation Feedback

Address Space

Peripheral Mem

Map

www.ti.com

LCDC

Mem Map

Page 21

www.ti.com

SPRS590G –JUNE 2009–REVISED JANUARY 2017

Table 3-4. C6748 Top Level Memory Map (continued)

Start Address End Address Size DSP Mem Map EDMA Mem Map PRUSS Mem Map Master

0x01D0 2000 0x01D0 2FFF 4K McASP 0 Data

0x01D0 3000 0x01D0 BFFF

0x01D0 C000 0x01D0 CFFF 4K UART 1

0x01D0 D000 0x01D0 DFFF 4K UART 2

0x01D0 E000 0x01D0 FFFF

0x01D1 0000 0x01D1 07FF 2K McBSP0

0x01D1 0800 0x01D1 0FFF 2K McBSP0 FIFO Ctrl

0x01D1 1000 0x01D1 17FF 2K McBSP1

0x01D1 1800 0x01D1 1FFF 2K McBSP1 FIFO Ctrl

0x01D1 2000 0x01DF FFFF

0x01E0 0000 0x01E0 FFFF 64K USB0

0x01E1 0000 0x01E1 0FFF 4K UHPI

0x01E1 1000 0x01E1 2FFF

0x01E1 3000 0x01E1 3FFF 4K LCD Controller

0x01E1 4000 0x01E1 4FFF 4K Memory Protection Unit 1 (MPU 1)

0x01E1 5000 0x01E1 5FFF 4K Memory Protection Unit 2 (MPU 2)

0x01E1 6000 0x01E1 6FFF 4K UPP

0x01E1 7000 0x01E1 7FFF 4K VPIF

0x01E1 8000 0x01E1 9FFF 8K SATA

0x01E1 A000 0x01E1 AFFF 4K PLL Controller 1

0x01E1 B000 0x01E1 BFFF 4K MMCSD1

0x01E1 C000 0x01E1 FFFF

0x01E2 0000 0x01E2 1FFF 8K EMAC Control Module RAM

0x01E2 2000 0x01E2 2FFF 4K EMAC Control Module Registers

0x01E2 3000 0x01E2 3FFF 4K EMAC Control Registers

0x01E2 4000 0x01E2 4FFF 4K EMAC MDIO port

0x01E2 5000 0x01E2 5FFF 4K USB1

0x01E2 6000 0x01E2 6FFF 4K GPIO

0x01E2 7000 0x01E2 7FFF 4K PSC 1

0x01E2 8000 0x01E2 8FFF 4K I2C 1

0x01E2 9000 0x01E2 BFFF

0x01E2 C000 0x01E2 CFFF 4K SYSCFG1

0x01E2 D000 0x01E2 FFFF

0x01E3 0000 0x01E3 7FFF 32K EDMA3 CC1

0x01E3 8000 0x01E3 83FF 1K EDMA3 TC2

0x01E3 8400 0x01EF FFFF

0x01F0 0000 0x01F0 0FFF 4K eHRPWM 0

0x01F0 1000 0x01F0 1FFF 4K HRPWM 0

0x01F0 2000 0x01F0 2FFF 4K eHRPWM 1

0x01F0 3000 0x01F0 3FFF 4K HRPWM 1

0x01F0 4000 0x01F0 5FFF

0x01F0 6000 0x01F0 6FFF 4K ECAP 0

0x01F0 7000 0x01F0 7FFF 4K ECAP 1

0x01F0 8000 0x01F0 8FFF 4K ECAP 2

0x01F0 9000 0x01F0 BFFF

0x01F0 C000 0x01F0 CFFF 4K Timer2

Peripheral Mem

Map

TMS320C6748

LCDC

Mem Map

Submit Documentation Feedback

Product Folder Links: TMS320C6748

Device ComparisonCopyright © 2009–2017, Texas Instruments Incorporated

21

Page 22

TMS320C6748

SPRS590G –JUNE 2009–REVISED JANUARY 2017

Table 3-4. C6748 Top Level Memory Map (continued)

Start Address End Address Size DSP Mem Map EDMA Mem Map PRUSS Mem Map Master

0x01F0 D000 0x01F0 DFFF 4K Timer3

0x01F0 E000 0x01F0 EFFF 4K SPI1

0x01F0 F000 0x01F0 FFFF

0x01F1 0000 0x01F1 0FFF 4K McBSP0 FIFO Data

0x01F1 1000 0x01F1 1FFF 4K McBSP1 FIFO Data

0x01F1 2000 0x116F FFFF

0x1170 0000 0x117F FFFF 1024K DSP L2 ROM

0x1180 0000 0x1183 FFFF 256K DSP L2 RAM

0x1184 0000 0x11DF FFFF

0x11E0 0000 0x11E0 7FFF 32K DSP L1P RAM

0x11E0 8000 0x11EF FFFF

0x11F0 0000 0x11F0 7FFF 32K DSP L1D RAM

0x11F0 8000 0x3FFF FFFF

0x4000 0000 0x5FFF FFFF 512M EMIFA SDRAM data (CS0)

0x6000 0000 0x61FF FFFF 32M EMIFA async data (CS2)

0x6200 0000 0x63FF FFFF 32M EMIFA async data (CS3)

0x6400 0000 0x65FF FFFF 32M EMIFA async data (CS4)

0x6600 0000 0x67FF FFFF 32M EMIFA async data (CS5)

0x6800 0000 0x6800 7FFF 32K EMIFA Control Regs

0x6800 8000 0x7FFF FFFF

0x8000 0000 0x8001 FFFF 128K On-chip RAM

0x8002 0000 0xAFFF FFFF

0xB000 0000 0xB000 7FFF 32K DDR2/mDDR Control Regs

0xB000 8000 0xBFFF FFFF

0xC000 0000 0xCFFF FFFF 256M DDR2/mDDR Data

0xD000 0000 0xFFFF FFFF

(1)

Peripheral Mem

Map

www.ti.com

LCDC

Mem Map

22

Device Comparison Copyright © 2009–2017, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: TMS320C6748

Page 23

W

V

U

T

R

P

N

M

L

K

10987654321

10987654321

DVDD3318_C

VP_CLKOUT3/

PRU1_R30[0]/

GP6[1]/

PRU1_R31[1]

SATA_VSS

SATA_RXP

VP_CLKOUT2/

MMCSD1_DAT[2]/

PRU1_R30[2]/

GP6[3]/

PRU1_R31[3]

SATA_RXN

SATA_VDD

SATA_REFCLKN

SATA_REGSATA_REFCLKP SATA_VDD

SATA_VDD SATA_VDDRSATA_VDD

DVDD3318_C

DDR_A[11]

VP_DOUT[15]/

LCD_D[15]/

UPP_XD[7]/

GP7[7]/

BOOT[7]

DV

DD3318_C

DV

DD18

DDR_DVDD18 DDR_DVDD18

DDR_D[15]

DDR_RAS

DDR_CLKP

DDR_CLKN

DDR_A[2]DDR_A[10]

V

SS

LCD_AC_ENB_CS/

GP6[0]/

PRU1_R31[28]

DDR_A[13]

DDR_CAS

DDR_A[5]

DDR_CKE

DDR_BA[0]

V

SS

CV

DD

RV

DD

DDR_A[9] DDR_A[1]

DDR_WE

DDR_D[10]

DDR_A[7]

DDR_A[0] DDR_D[12]

DDR_A[12] DDR_A[3]

DDR_CS

DDR_A[6]

DDR_DQM[1]

SATA_VSS

CV

DD

SATA_VSS

DDR_DVDD18

VP_DOUT[12]/

LCD_D[12]/

UPP_XD[4]/

GP7[4]/

BOOT[4]

DDR_VREF

DDR_BA[1]

DDR_A[8]

DDR_A[4]

DDR_BA[2]

SATA_VSS

W

V

U

T

R

P

N

M

L

K

DDR_D[13]

V

SS

V

SS

V

SS

V

SS

DV

DD18

V

SS

V

SS

V

SS

V

SS

NC

V

SS

V

SS

V

SS

V

SS

CV

DD

CV

DD

V

SS

DDR_DVDD18DDR_DVDD18DDR_DVDD18DDR_DVDD18

DVDD3318_C

VP_DOUT[13]/

LCD_D[13]/

UPP_XD[5]/

GP7[5]/

BOOT[5]

VP_DOUT[14]/

LCD_D[14]/

UPP_XD[6]/

GP7[6]/

BOOT[6]

DDR_DVDD18 DDR_DVDD18 DDR_DVDD18

VP_DOUT[9]/

LCD_D[9]/

UPP_XD[1]/

GP7[1]/

BOOT[1]

VP_DOUT[10]/

LCD_D[10]/

UPP_XD[2]/

GP7[2]/

BOOT[2]

VP_DOUT[11]/

LCD_D[11]/

UPP_XD[3]/

GP7[3]/

BOOT[3]

VP_DOUT[6]/

LCD_D[6]/

UPP_XD[14]/

GP7[14]/

PRU1_R31[14]

VP_DOUT[7]/

LCD_D[7]/

UPP_XD[15]/

GP7[15]/

PRU1_R31[15]

VP_DOUT[8]/

LCD_D[8]/

UPP_XD[0]/

GP7[0]/

BOOT[0]

VP_DOUT[3]/

LCD_D[3]/

UPP_XD[11]/

GP7[11]/

PRU1_R31[11]

VP_DOUT[4]/

LCD_D[4]/

UPP_XD[12]/

GP7[12]/

PRU1_R31[12]

VP_DOUT[5]/

LCD_D[5]/

UPP_XD[13]/

GP7[13]/

PRU1_R31[13]

VP_DOUT[0]/

LCD_D[0]/

UPP_XD[8]/

GP7[8]/

PRU1_R31[8]

VP_DOUT[1]/

LCD_D[1]/

UPP_XD[9]/

GP7[9]/

PRU1_R31[9]

VP_DOUT[2]/

LCD_D[2]/

UPP_XD[10]/

GP7[10]/

PRU1_R31[10]

www.ti.com

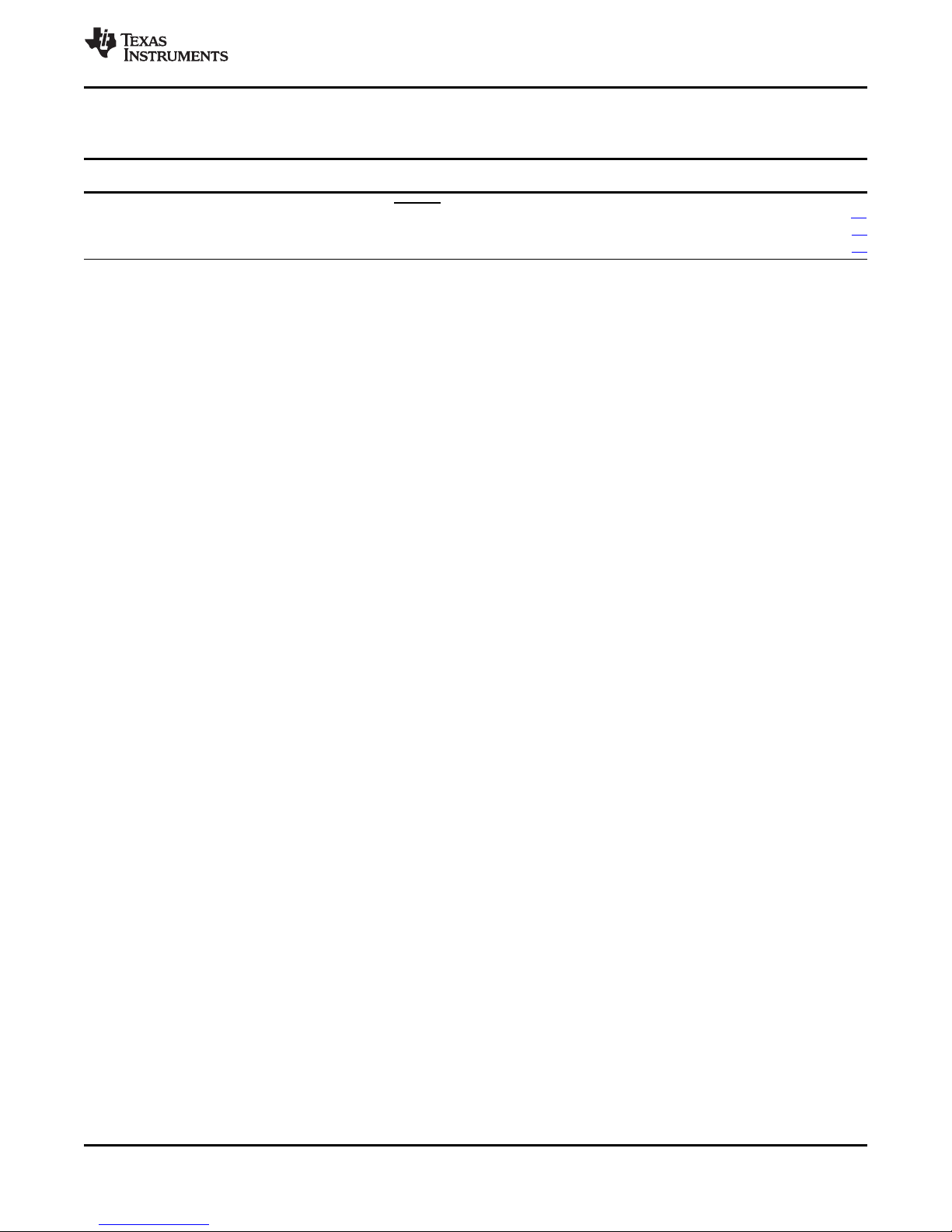

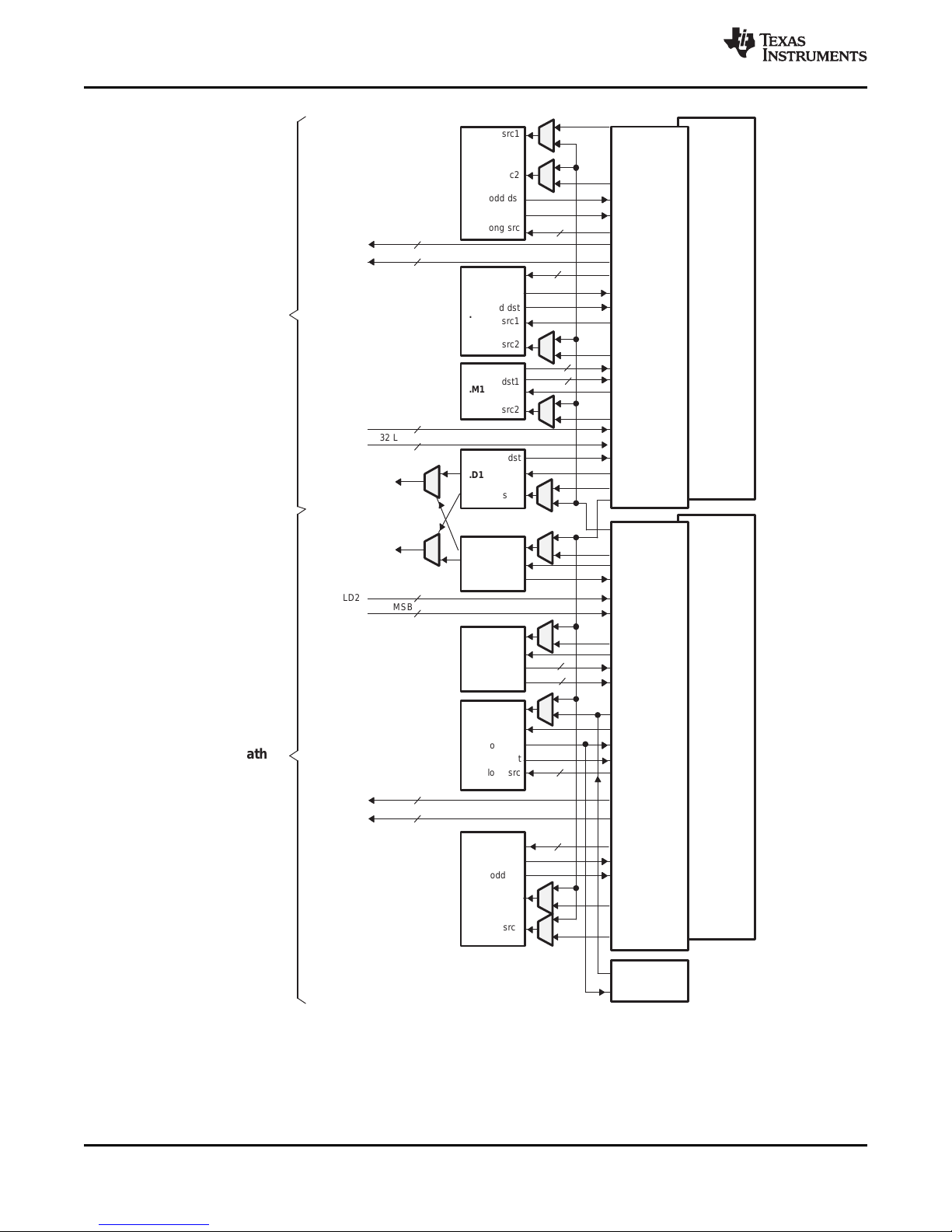

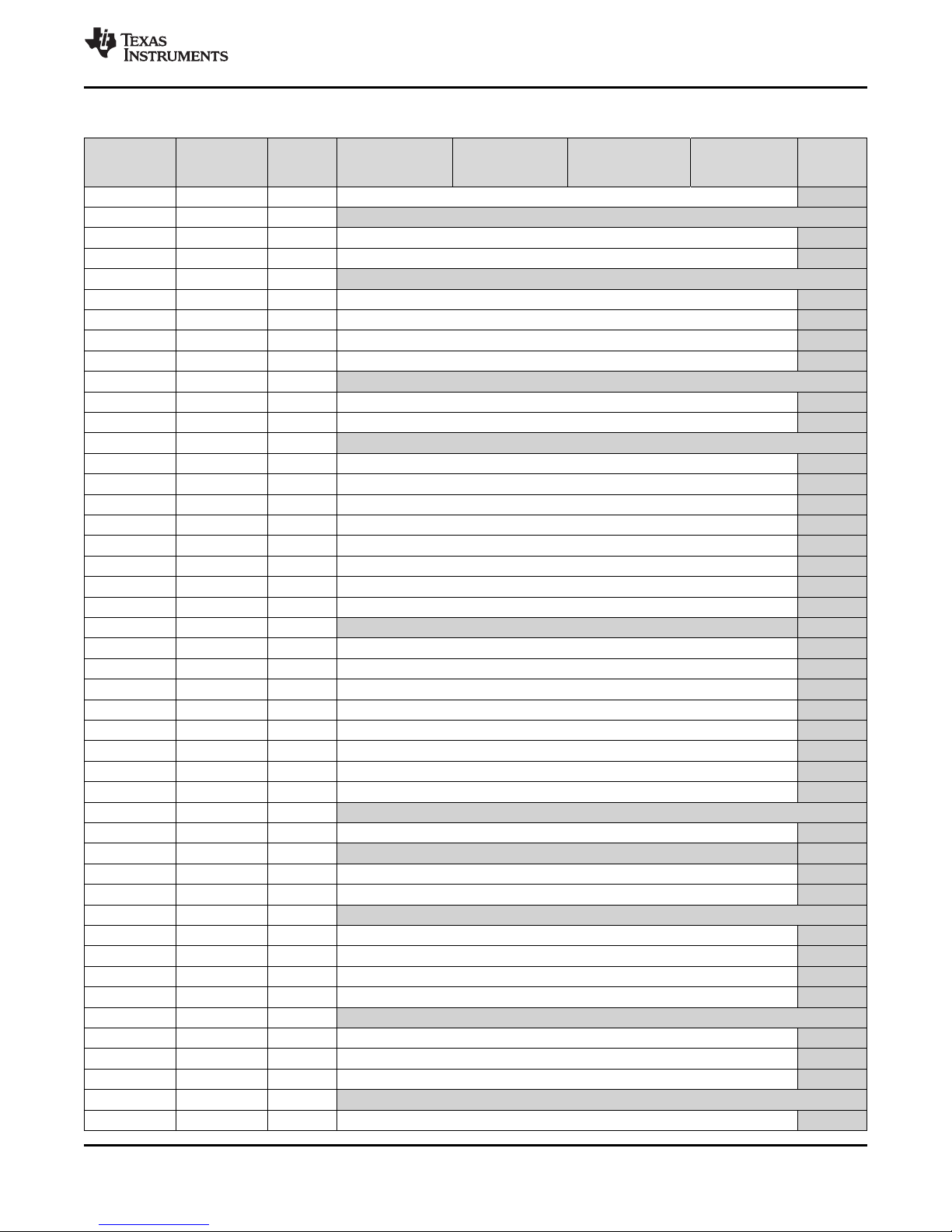

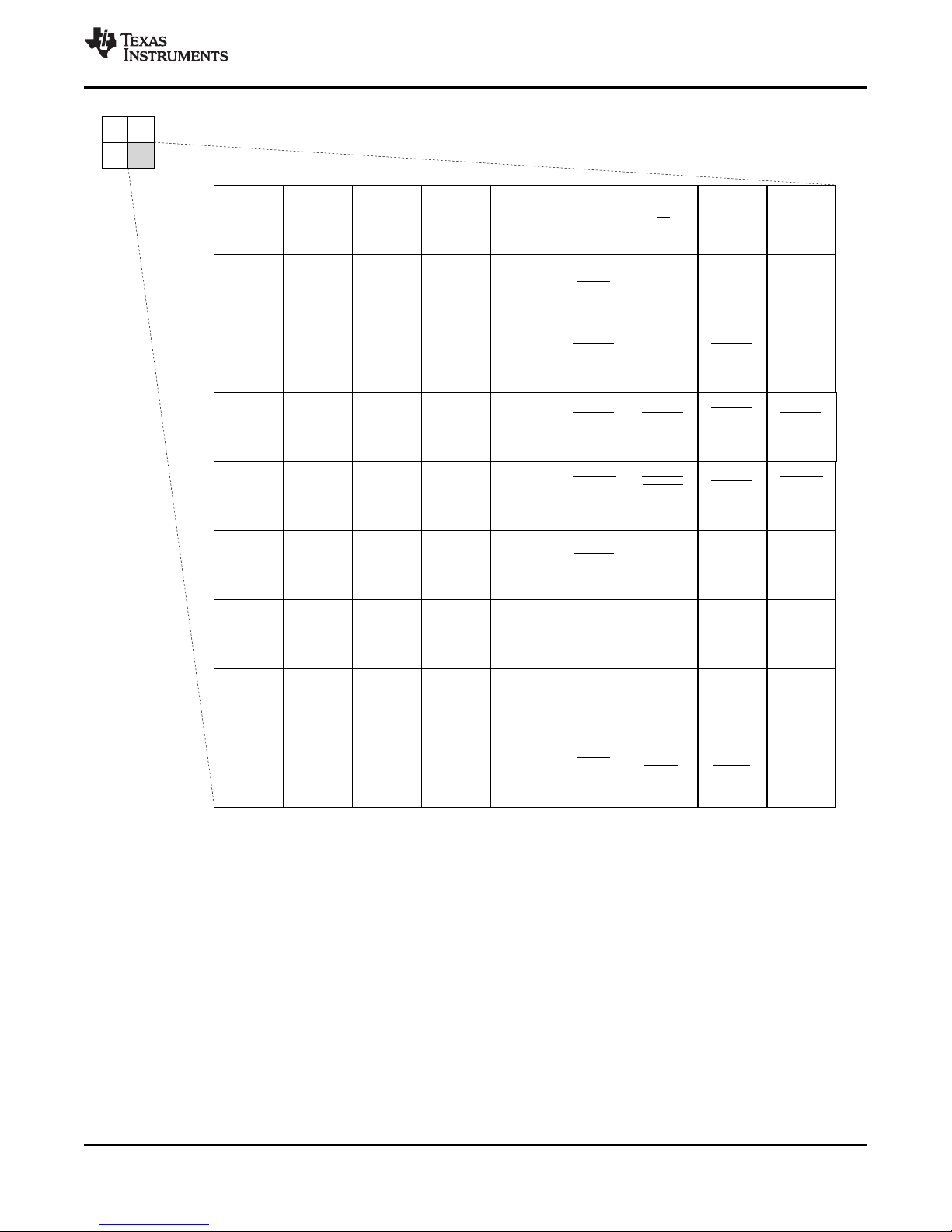

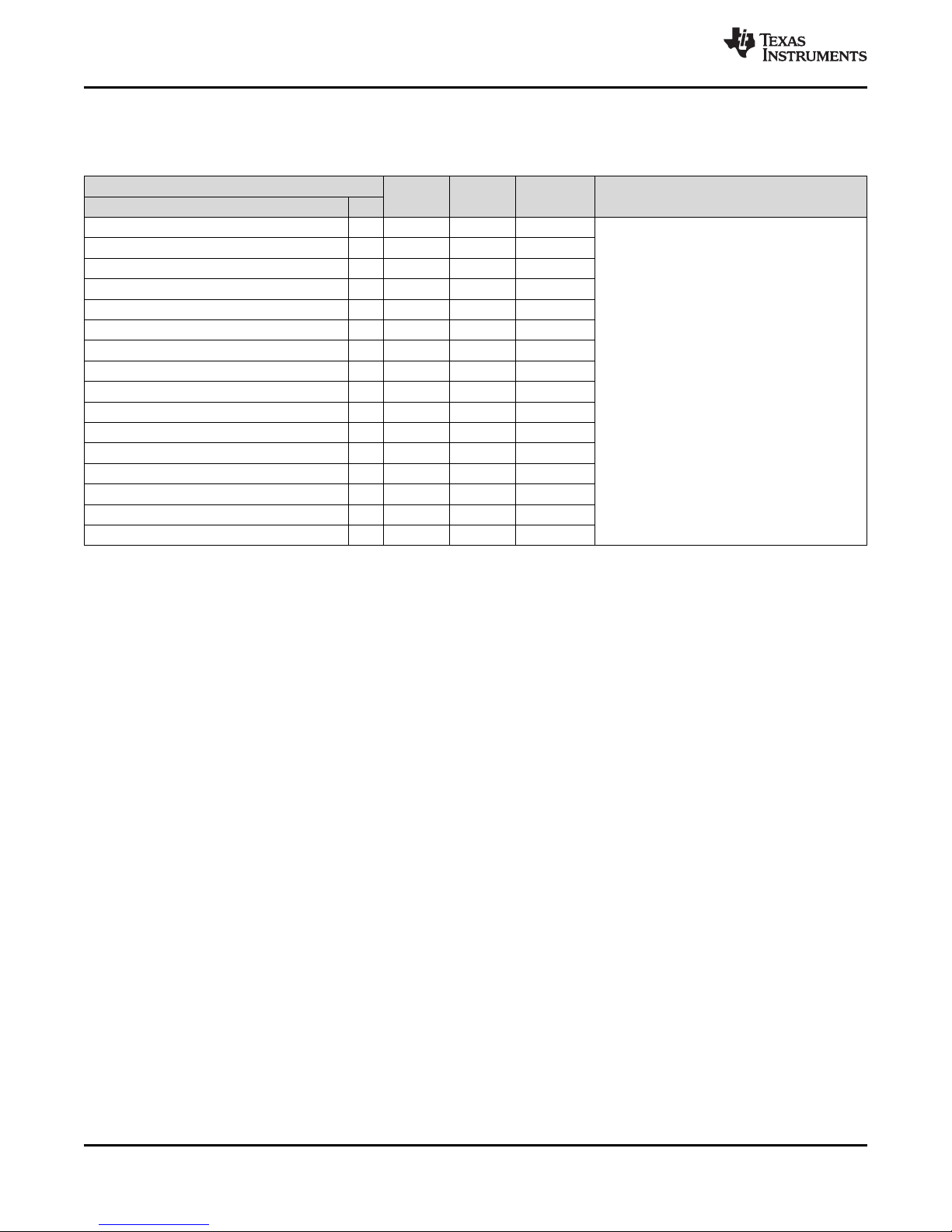

3.5 Pin Assignments

Extensive use of pin multiplexing is used to accommodate the largest number of peripheral functions in

the smallest possible package. Pin multiplexing is controlled using a combination of hardware

configuration at device reset and software programmable register settings.

3.5.1 Pin Map (Bottom View)

The following graphics show the bottom view of the ZCE and ZWT packages pin assignments in four

quadrants (A, B, C, and D). The pin assignments for both packages are identical.

TMS320C6748

SPRS590G –JUNE 2009–REVISED JANUARY 2017

Figure 3-3. Pin Map (Quad A)

Submit Documentation Feedback

Product Folder Links: TMS320C6748

Device ComparisonCopyright © 2009–2017, Texas Instruments Incorporated

23

Page 24

W

V

U

T

R

P

N

M

L

K

191817161514131211

191817161514131211

USB1_VDDA33

DVDD3318_C

CV

DD

USB_CVDD

DVDD3318_C

DDR_DQGATE0

DVDD18

DDR_DQGATE1

DDR_D[9] DDR_D[8]DDR_D[11]

DVDD18

RTC_CVDD

RESET

USB0_DM USB0_DP

VP_DIN[11]/

UHPI_HD[3]/

UPP_D[3]/

PRU0_R30[11]/

PRU0_R31[11]

USB0_VDDA33 USB0_VBUS

USB1_DM

VP_DIN[0]/

UHPI_HD[8]/

UPP_D[8]/

RMII_CRS_DV/

PRU1_R31[29]

VP_DIN[1]/

UHPI_HD[9]/

UPP_D[9]/

RMII_MHZ_50_CLK/

PRU0_R31[23]

VP_DIN[2]/

UHPI_HD[10]/

UPP_D[10]/

RMII_RXER/

PRU0_R31[24]

VP_DIN[4]/

UHPI_HD[12]/

UPP_D[12]/

RMII_RXD[1]/

PRU0_R31[26]

PRU0_R30[28]/

UHPI_HCNTL1/

UPP_CHA_START/

GP6[10]

USB1_DP

PLL0_VDDA

PRU0_R30[30]/

/

PRU1_R30[11]/

GP6[12]

UHPI_HINT

USB0_VDDA18

VP_DIN[5]/

UHPI_HD[13]/

UPP_D[13]/

RMII_TXEN/

PRU0_R31[27]

DDR_D[1]

VP_DIN[7]/

UHPI_HD[15]/

UPP_D[15]/

RMII_TXD[1]/

PRU0_R31[29]

OSCVSS

DDR_D[2]

VP_DIN[6]/

UHPI_HD[14]/

UPP_D[14]/

RMII_TXD[0]/

PRU0_R31[28]

VP_DIN[3]/

UHPI_HD[11]/

UPP_D[11]/

RMII_RXD[0]/

PRU0_R31[25]

VP_DIN[14]_

HSYNC/

UHPI_HD[6]/

UPP_D[6]/

PRU0_R30[14]/

PRU0_R31[14]

EMU1

VP_DIN[8]/

UHPI_HD[0]/

UPP_D[0]/

GP6[5]/

PRU1_R31[0]

USB0_VDDA12

TDI

NC

PRU0_R30[26]/

UHPI_HR /

UPP_CHA_WAIT/

GP6[8]/

PRU1_R31[17]

W

VP_DIN[12]/

UHPI_HD[4]/

UPP_D[4]/

PRU0_R30[12]/

PRU0_R31[12]

RESETOUT

UHPI_HAS//

PRU1_R30[14]/

GP6[15]

RSV2

GP8[0]

OSCOUT

DDR_D[0]

PRU0_R30[27]/

UHPI_HHWIL/

UPP_CHA_ENABLE/

GP6[9]

VP_DIN[13]_

FIELD/

UHPI_HD[5]/

UPP_D[5]/

PRU0_R30[13]/

PRU0_R31[13]

TRST

OSCIN

VP_CLKIN1/

/

PRU1_R30[9]/

GP6[6]/

PRU1_R31[16]

UHPI_HDS1

VP_DIN[15]_

VSYNC/

UHPI_HD[7]/

UPP_D[7]/

PRU0_R30[15]/

PRU0_R31[15]

VP_CLKIN0/

/

PRU1_R30[10]/

GP6[7]/

UPP_2xTXCLK

UHPI_HCS

VP_DIN[10]/

UHPI_HD[2]/

UPP_D[2]/

PRU0_R30[10]/

PRU0_R31[10]

V

SS

DVDD3318_B

PLL0_VSSA

TMS

PRU0_R30[31]/

/

PRU1_R30[12]/

GP6[13]

UHPI_HRDY

NC PLL1_VSSA

PLL1_VDDA

USB1_VDDA18 USB0_ID

VP_DIN[9]/

UHPI_HD[1]/

UPP_D[1]/

PRU0_R30[9]/

PRU0_R31[9]

CLKOUT/

/

PRU1_R30[13]/

GP6[14]

UHPI_HDS2

USB0_DRVVBUS

DDR_DQS[0]

PRU0_R30[29]/

UHPI_HCNTL0/

UPP_CHA_CLOCK/

GP6[11]

W

V

U

T

R

P

N

M

L

K

DDR_DQM[0]

DDR_D[3]

DDR_D[4]

DDR_D[6]

DDR_ZP

DDR_D[5]

DDR_D[7]

DDR_D[14]

DDR_DQS[1]

V

SS

V

SS

V

SS

V

SS

V

SS

CV

DD

DVDD3318_C

DVDD3318_C

DVDD3318_C

TMS320C6748

SPRS590G –JUNE 2009–REVISED JANUARY 2017

www.ti.com

Figure 3-4. Pin Map (Quad B)

24

Device Comparison Copyright © 2009–2017, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links: TMS320C6748

Page 25

H

G

F

E

D

C

B

A

191817161514131211

191817161514131211

CV

DD

EMA_A[8]/

PRU1_R30[16]/

GP5[8]

EMA_A[14]/

MMCSD0_DAT[7]/

PRU1_R30[22]/

GP5[14]/

PRU1_R31[22]

EMA_A[15]/

MMCSD0_DAT[6]/

PRU1_R30[23]/

GP5[15]/

PRU1_R31[23]

EMA_A[10]/

PRU1_R30[18]/

GP5[10]/

PRU1_R31[18]

EMA_A[9]/

PRU1_R30[17]/

GP5[9]

EMA_A[13]/

PRU0_R30[21]/

PRU1_R30[21] /

GP5[13]/

PRU1_R31[21]

EMA_A[12]/

PRU1_R30[20]/

GP5[12]/

PRU1_R31[20]

EMA_A[16]/

MMCSD0_DAT[5]/

PRU1_R30[24]/

GP4[0]

EMA_A[18]/

MMCSD0_DAT[3]/

PRU1_R30[26]/

GP4[2]

DV

DD3318_B

DV

DD18

EMA_A[6]/

GP5[6]

EMA_A[5]/

GP5[5]

EMA_A[2]/

GP5[2]

EMA_A[7]/

PRU1_R30[15]/

GP5[7]

EMA_A[4]/

GP5[4]

SPI0_SIMO/

EPWMSYNCO/

GP8[5]/

MII_CRS

SPI0_SCS[5]/

UART0_RXD/

GP8[4]/

MII_RXD[3]

SPI1_SCS[1]/

EPWM1A/

PRU0_R30[8]/

GP2[15]/

TM64P2_IN12

SPI0_SCS[4]/

UART0_TXD/

GP8[3]/

MII_RXD[2]

SPI0_CLK/

EPWM0A/

GP1[8]/

MII_RXCLK

SPI1_SCS[3]/

UART1_RXD/

SATA_LED/

GP1[1]

SPI1_SCS[0]/

EPWM1B/

PRU0_R30[7]/

GP2[14]/

TM64P3_IN12

EMA_OE/

GP3[10]

SPI1_SCS[4]/

UART2_TXD/

I2C1_SDA/

GP1[2]

EMA_A[3]/

GP5[3]

DV

DD18

RTC_VSS

EMA_WAIT[0]/

PRU0_R30[0]/

GP3[8]/

PRU0_R31[0]

EMA_RAS/

PRU0_R30[3]/

GP2[5]/

PRU0_R31[3]

SPI0_SCS[3]

UART0_CTS//

GP8[2]/

MII_RXD[1]/

SATA_MP_SWITCH

SPI0_SCS[0]/

TM64P1_OUT12/

GP1[6]/

MDIO/

TM64P1_IN12

SPI0_SOMI/

EPWMSYNCI/

GP8[6]/

MII_RXER

SPI0_SCS[2]

UART0_RTS//

GP8[1]/

MII_RXD[0]/

SATA_CP_DET

SPI1_SCS[7]/

I2C0_SCL/

TM64P2_OUT12/

GP1[5]

SPI1_SIMO/

GP2[10]

SPI1_CLK/

GP2[13]

EMA_CS[3]/

GP3[14]

V

SS

V

SS

SPI1_ENA/

GP2[12]

RTC_XO

EMA_CS[2]/

GP3[15]

EMA_WAIT[1]/

PRU0_R30[1]/

GP2[1]/

PRU0_R31[1]

EMA_A[20]/

MMCSD0_DAT[1]/

PRU1_R30[28]/

GP4[4]

EMA_BA[1]/

GP2[9]

SPI0_ENA/

EPWM0B/

PRU0_R30[6]/

MII_RXDV

EMA_CS[5]/

GP3[12]

SPI1_SCS[5]/

UART2_RXD/

I2C1_SCL/

GP1[3]

EMA_A[0]/

GP5[0]

EMA_BA[0]/

GP2[8]

EMA_A[1]/

GP5[1]

DV

DD3318_B

SPI0_SCS[1]/

TM64P0_OUT12/

GP1[7]/

MDCLK/

TM64P0_IN12

DV

DD3318_A

SPI1_SCS[6]/

I2C0_SDA/

TM64P3_OUT12/

GP1[4]

EMA_CS[0]/

GP2[0]

CV

DD

SPI1_SOMI/

GP2[11]

H

G

F

E

D

C

B

A

J

TDO

TCK

EMU0

RTC_XI

NMI

J

SPI1_SCS[2]/

UART1_TXD/

SATA_CP_POD/

GP1[0]

EMA_A[11]/

PRU1_R30[19]/

GP5[11]/

PRU1_R31[19]

EMA_A[17]/

MMCSD0_DAT[4]/

PRU1_R30[25]

GP4[1]

DV

DD3318_B

DV

DD3318_B

DV

DD18

CV

DD

DV

DD3318_A

DV

DD3318_A

RV

DD

CV

DD

CV

DD

V

SS

CV

DD

DV

DD18

DV

DD3318_B

www.ti.com

TMS320C6748

SPRS590G –JUNE 2009–REVISED JANUARY 2017

Figure 3-5. Pin Map (Quad C)

Submit Documentation Feedback

Product Folder Links: TMS320C6748

Device ComparisonCopyright © 2009–2017, Texas Instruments Incorporated

25

Page 26

J

H

G

F

E

D

C

B

A

10987654321

10987654321

EMA_D[15]/

GP3[7]

AXR15/

EPWM0TZ[0]/

ECAP2_APWM2/

GP0[7]

ACLKR/

PRU0_R30[20]/

GP0[15]/

PRU0_R31[22]

ACLKX/

PRU0_R30[19]/

GP0[14]/

PRU0_R31[21]

AHCLKX/

USB_REFCLKIN/

/

GP0[10]/

PRU0_R31[17]

UART1_CTS

AFSX/

GP0[12]/

PRU0_R31[19]

AFSR/

GP0[13]/

PRU0_R31[20]

AXR9/

DX1/

GP0[1]

AXR4/

FSR0/

GP1[12]/

MII_COL

AXR5/

CLKX0/

GP1[13]/

MII_TXCLK

AXR7/

EPWM1TZ[0]/

PRU0_R30[17]

GP1[15]/

PRU0_R31[7]

AXR10/

DR1/

GP0[2]

AXR1/

DX0/

GP1[9]/

MII_TXD[1]

AXR3/

FSX0/

GP1[11]/

MII_TXD[3]

AXR2/

DR0/

GP1[10]/

MII_TXD[2]

MMCSD1_DAT[6]/

LCD_MCLK/

PRU1_R30[6]/

GP8[10]/

PRU1_R31[7]

RTC_ALARM/

/

GP0[8]/

UART2_CTS

DEEPSLEEP

AXR0/

ECAP0_APWM0/

GP8[7]/

MII_TXD[0]/

CLKS0

PRU0_R30[24]/

MMCSD1_CLK/

UPP_CHB_START/

GP8[14]/

PRU1_R31[26]

MMCSD1_DAT[4]/

LCD_VSYNC/

PRU1_R30[4]/

GP8[8]/

PRU1_R31[5]

SATA_VSS

PRU0_R30[22]/

PRU1_R30[8]/

UPP_CHB_WAIT/

GP8[12]/

PRU1_R31[24]

AXR8/

CLKS1/

ECAP1_APWM1/

GP0[0]/

PRU0_R31[8]

AXR12/

FSR1/

GP0[4]

EMA_D[4]/

GP4[12]

AXR14/

CLKR1/