Dual high side smart power solid state relay

Features

Type V

demag

(1)

VNI2140J VCC-45 V 0.08 Ω 1 A

1. Per channel

2. Current limitation

■ Nominal current: 0.5 A per channel

■ Shorted load protections

■ Junction overtemperature protection

■ Case overtemperature protection for thermal

independence of the channels

■ Thermal case shutdown restart not

simultaneous for the various channels

■ Protection against loss of ground

■ Current limitation 1 A per channel

■ Undervoltage shutdown

■ Open load in off-state and short to V

detection

■ Open-drain diagnostic outputs

■ 3.3 V CMOS/TTL compatible inputs

■ Fast demagnetization of inductive loads

■ Conforms to IEC 61131-2

R

DSon

(1)

I

out

(1)

(2)

CC

V

CC

45 V

VNI2140J

PowerSSO-12

Description

The VNI2140J is a monolithic device designed

using STMicroelectronics' VIPower technology.

The device drives two independent resistive or

inductive loads with one side connected to

ground. Active current limitation prevents a drop

in system power supply in cases of shorted-load,

and built-in thermal shutdown protects the chip

from damage due to over-temperature and shortcircuit. In overload conditions, channel turns OFF

and ON automatically to maintain the junction

temperature between TTSD and TR. If the case

temperature reaches TCSD, the overloaded

channel is turned OFF and restarts only when

case temperature decreases down to TCR. In

order to avoid high-peak current from the supply,

when more than one channel is overloaded the

TCSD restart is not simultaneous. Non

overloaded channels continue to operate

normally. The open-drain diagnostics output

indicates over-temperature conditions and openload in off state.

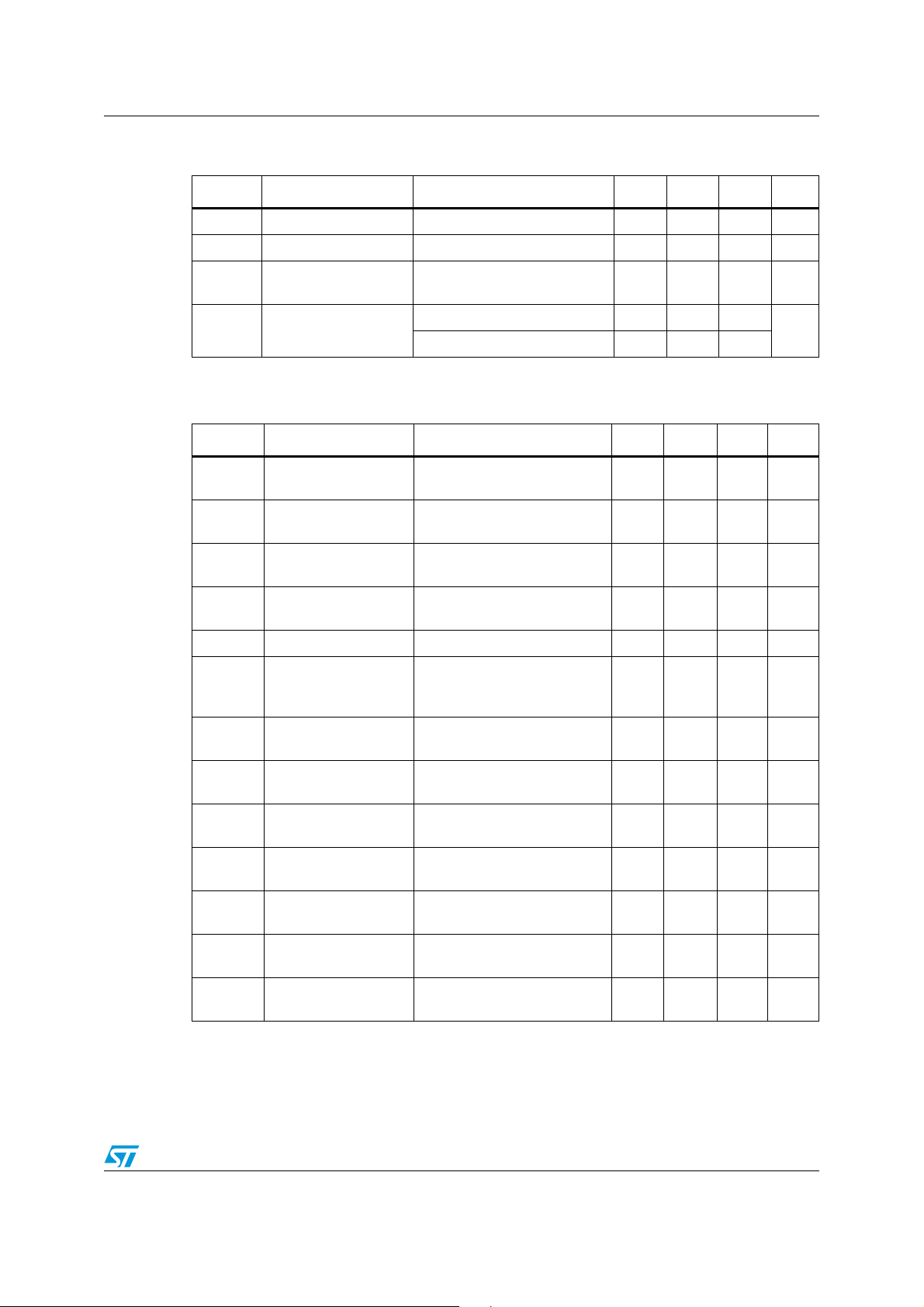

Table 1. Device summary

Order codes Package Packaging

VNI2140J

PowerSSO-12

VNI2140JTR Tape and reel

November 2011 Doc ID 15187 Rev 8 1/23

Tube

www.st.com

23

Contents VNI2140J

Contents

1 Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

2 Pin connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3 Maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3.1 Thermal data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

4 Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

5 Truth table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

6 Switching waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

7 Open load . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

8 Package and PCB thermal data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

9 Reverse polarity protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

10 Package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

11 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

2/23 Doc ID 15187 Rev 8

VNI2140J Block diagram

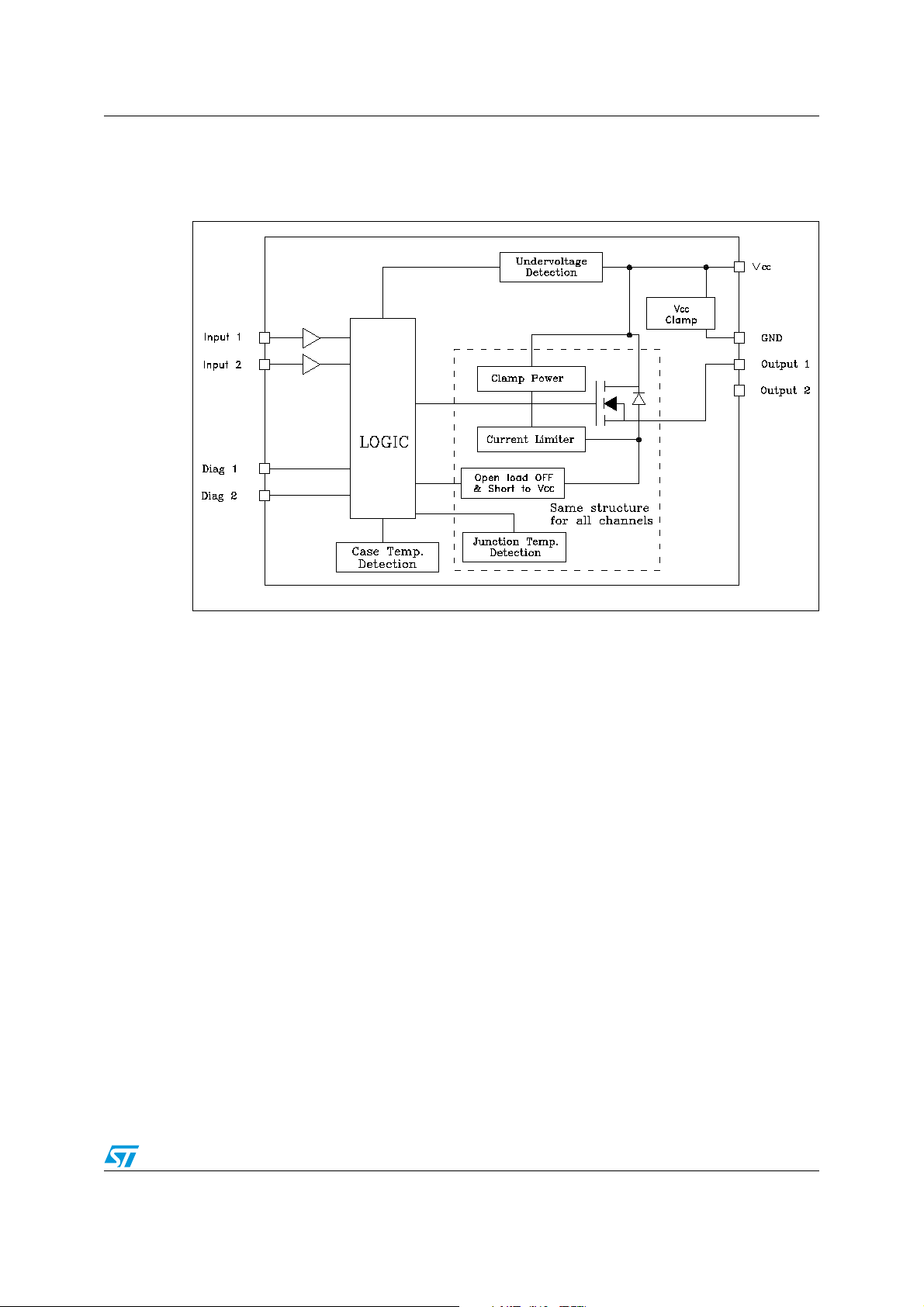

1 Block diagram

Figure 1. Block diagram

Doc ID 15187 Rev 8 3/23

Pin connections VNI2140J

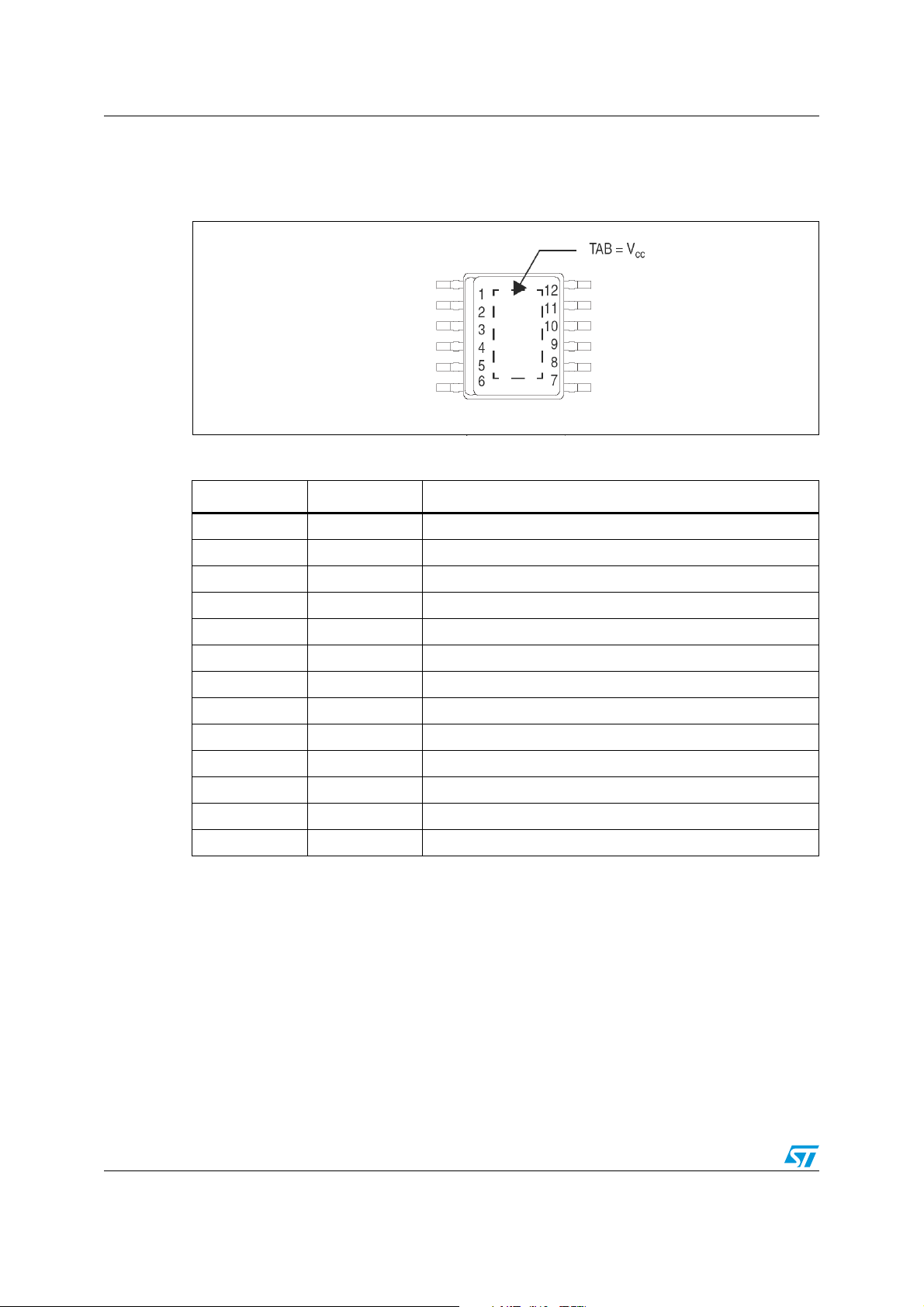

2 Pin connections

Figure 2. Pin connections (top view)

Input 1

Diag 1

Diag 2

Input 2

Table 2. Pin description

n° Name Description

1 NC Not connected

2 Input 1 Channel 1 input 3.3 V CMOS/TTL compatible

3 Diag 1 Channel 1 diagnostic in open-drain configuration

4 GND Device ground connection

5 Diag 2 Channel 2 diagnostic in open-drain configuration

6 Input 2 Channel 2 input 3.3 V CMOS/TTL compatible

7 VCC Supply voltage

8 Output 2 Channel 2 power stage output, internally protected

9 Output 2 Channel 2 power stage output, internally protected

NC

GND

VCC

Output 1

Output 1

Output 2

Output 2

VCC

10 Output 1 Channel 1 power stage output, internally protected

11 Output 1 Channel 1 power stage output, internally protected

12 VCC Supply voltage

TAB TAB Supply voltage

4/23 Doc ID 15187 Rev 8

VNI2140J Maximum ratings

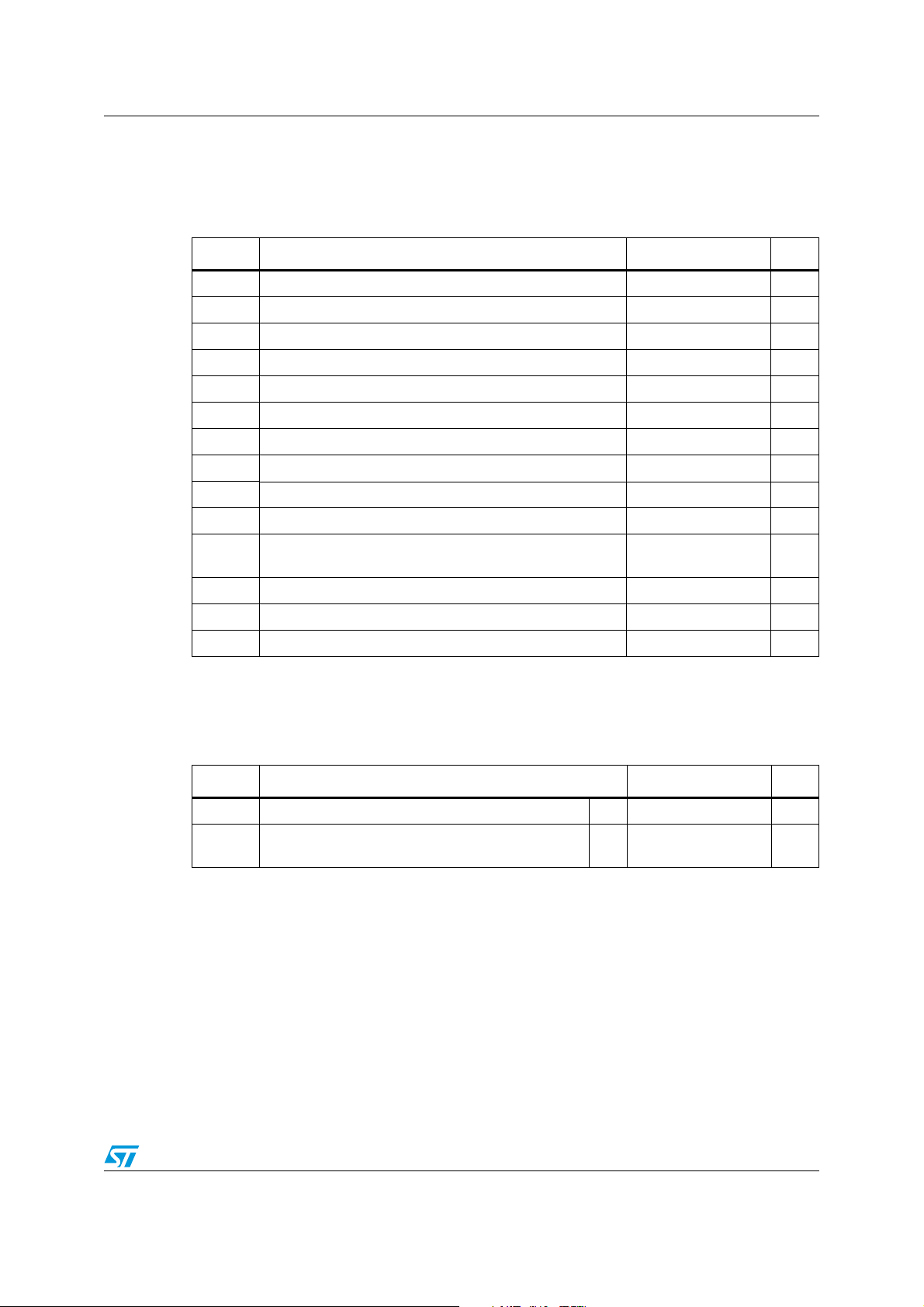

3 Maximum ratings

Table 3. Absolute maximum ratings

Symbol Parameter Value Unit

V

-V

I

GND

I

V

I

DIAG

V

E

P

T

OUT

V

DIAG

Power supply voltage 45 V

CC

Reverse supply voltage -0.3 V

CC

DC ground reverse current -250 mA

Output current (continuous) Internally limited A

Reverse output current (per channel) -5 A

I

R

Input current (per channel) ± 10 mA

I

IN

Input voltage +V

IN

Diag pin voltage +V

Diag pin current ± 10 mA

Electrostatic discharge (R = 1.5 kΩ; C = 100 pF) 2000 V

ESD

Single pulse avalanche energy per channel not

AS

simultaneously

Power dissipation at Tc = 25 °C Internally limited W

TOT

Junction operating temperature Internally limited °C

T

J

Storage temperature -55 to 150 °C

STG

3.1 Thermal data

CC

CC

V

V

300 mJ

Table 4. Thermal data

Symbol Parameter Value Unit

R

R

th(JC)

th(JA)

Thermal resistance junction-case

Thermal resistance junction-ambient

1. Per channel

2. When mounted using minimum recommended pad size on FR-4 board

Doc ID 15187 Rev 8 5/23

(1)

(2)

Max 1 °C/W

Max

See Figure 11 on

page 15

°C/W

Electrical characteristics VNI2140J

4 Electrical characteristics

9 V < VCC < 36 V; -40 °C < TJ < 125 °C; unless otherwise specified

Table 5. Power section

Symbol Parameter Test conditions Min. Typ. Max. Unit

Vcc Supply voltage 9 45 V

I

R

DS(ON)

V

CLAMP

I

S

I

LGND

V

OUT(OFF)

= 0.5 A at TJ = 25 °C

On-state resistance

OUT

I

OUT

= 0.5 A

Clamp voltage Is = 20 mA 45 52 V

All channel in off-state

Supply current

Output current at

turn-off

Off-state output

voltage

On-state with V

= 125 °C)

(T

J

VCC = V

V

V

= 24 V, V

GND

= 0 V and I

IN

DIAG

=5 V

IN

= VIN =

= 0 V

OUT

= 0 A 3 V

OUT

0.080

300

1.9 4

0.150ΩΩ

µA

mA

1mA

I

(OFF)

OUT

I

OUT

V

= 24

CC

OFF-state output

current

(OFF1)

V

IN

V

IN

= V

= 0 V 0 5 µA

OUT

= 0 V; V

= 4 V -35 0 µA

OUT

Table 6. Switching

Symbol Parameter Test conditions Min. Typ. Max. Unit

= 0.5 A, resistive load

I

t

d(ON)

t

d(OFF)

t

DOL

dV/dt

dV/dt(off)

Turn-on delay time of

output current

Rise time of output

t

r

current

Turn-off delay time of

output current

Fall time of output

t

f

current

Delay time for open

load detection

Turn ON voltage slope - 3 - V/µS

(ON)

Turn OFF voltage

slope

OUT

Input rise time < 0.1 μs,

= 25 °C

T

J

= 0.5 A, resistive load

I

OUT

Input rise time < 0.1 μs,

= 25 °C

T

J

= 0.5 A, resistive load

I

OUT

Input rise time < 0.1 μs,

= 25 °C

T

J

= 0.5 A, resistive load

I

OUT

Input rise time < 0.1 μs,

= 25 °C

T

J

-20 -µs

-10 -µs

-30 -µs

-8 -µs

- 500 - µs

-4 -V/µS

6/23 Doc ID 15187 Rev 8

VNI2140J Electrical characteristics

Table 7. Logical input

Symbol Parameter Test conditions Min. Typ. Max. Unit

V

V

V

I(HYST)

I

Input low level voltage 0.8 V

IL

Input high level voltage 2.20 V

IH

Input hysteresis

voltage

Input current

IN

V

= 15 V 10

IN

= 36 V 210

V

IN

0.15 V

Table 8. Protection and diagnostic

Symbol Parameter Test conditions Min. Typ. Max. Unit

Diag voltage output

V

DIAG

V

USD

V

USDHYS

I

LIM

I

LDIAG

V

OL

T

TSD

(1)

low

Undervoltage

protection

Undervoltage

hysteresis

DC short circuit

current

Diag leakage current VCC = 32 V 30 μA

Open-load off-state

voltage detection

threshold

Junction shutdown

temperature

I

= 1.5 mA (fault condition) 0.6 V

DIAG

79V

0.4 0.5 V

V

= 24 V; R

CC

< 10 mΩ 12A

LOAD

VIN = 0 V 2 3 4 V

150 170 °C

μA

T

T

HIST

T

CSD

T

T

CHYST

V

demag

1. Diag determination > 100 ms after the switching edge.

Junction reset

R

temperature

Junction thermal

hysteresis

Case shutdown

temperature

Case reset

CR

temperature

Case thermal

hysteresis

Output voltage at

turn-OFF

I

OUT

= 0.5 A; L

LOAD

>= 1 mH

135 155 200 °C

715 °C

125 130 135 °C

110 °C

715 °C

-45VCC-50VCC-

V

CC

52

V

Doc ID 15187 Rev 8 7/23

Electrical characteristics VNI2140J

Figure 3. Current and voltage conventions

8/23 Doc ID 15187 Rev 8

VNI2140J Truth table

5 Truth table

Table 9. Truth table

INPUTn OUTPUTn DIAGn

Normal operation

Overtemperature

Undervoltage

Shorted load

(Current limitation)

Output voltage > V

Short to V

1. Z = Depending on the external circuit

OL

CC

L

H

L

H

L

H

L

H

L

H

L

H

Z

L

H

L

L

L

L

L

X

(1)

H

H

H

H

H

H

L

X

X

H

H

L

H

L

H

Doc ID 15187 Rev 8 9/23

Switching waveforms VNI2140J

6 Switching waveforms

Figure 4. Switching waveforms

10/23 Doc ID 15187 Rev 8

VNI2140J Switching waveforms

Figure 5. Switching waveforms (continued)

Figure 6. Switching parameter test conditions

I

OUT

V

IN

Doc ID 15187 Rev 8 11/23

Switching waveforms VNI2140J

Figure 7. Typical application circuit

12/23 Doc ID 15187 Rev 8

VNI2140J Open load

7 Open load

In order to detect the open load fault a pull-up resistor must be connected between the VCC

line and the output pin.

In a normal condition a current flows through the network made up of a pull-up resistor and

a load. The voltage across the load is less than V

This is the result in the condition:

Equation 1

R

LOAD

----------------------------------- -

V

CC

R

+

LOADRPU

or

Equation 2

V

CC

⎛⎞

------------------- - 1–

⎝⎠

V

OLMIN

R

⋅ RPU<

LOAD

; so the diag pin is kept high.

OLMIN

V

<

OLMIN

When a open load event occurs the voltage on the output pin rises to a value higher than

V

(depending on the pull-up resistor). The diag pin will go down.

OLMAX

This result in the condition:

Equation 3

V

–

CCVOLMAX

----------------------------------------- -

R

<

PU

I

OUT OFF1()MIN

Figure 8. Open load detection

Doc ID 15187 Rev 8 13/23

Open load VNI2140J

Figure 9. Turn on/off to open load

14/23 Doc ID 15187 Rev 8

VNI2140J Package and PCB thermal data

8 Package and PCB thermal data

Figure 10. PowerSSO-12 PC board

Figure 11. R

vs PCB copper area in open box free air condition

thJA

Figure 12. PowerSSO-12 thermal Impedance junction ambient single pulse

Doc ID 15187 Rev 8 15/23

Package and PCB thermal data VNI2140J

Pulse calculation formula

Equation 4

where δ = t

= RTH x δ + Z

Z

THδ

/T

P

THtp

(1 – δ)

Figure 13. Thermal fitting model of a double channel HSD in PowerSSO-12

Table 10. Thermal parameter

Area/island (cm2) Footprint 2 8

R1 (°C/W) 0.1

R2 (°C/W) 0.2

R3 (°C/W) 7

R4 (°C/W) 10 10 9

R5 (°C/W) 22 15 10

R6 (°C/W) 26 20 15

C1 (W.s/°C) 0.0001

C2 (W.s/°C) 0.002

C3 (W.s/°C) 0.05

C4 (W.s/°C) 0.2 0.1 0.1

C5 (W.s/°C) 0.27 0.8 1

C6 (W.s/°C) 3 6 9

16/23 Doc ID 15187 Rev 8

VNI2140J Reverse polarity protection

9 Reverse polarity protection

This schematic can be used with any type of load.

The following is an indication on how to dimension the R

R

= (-VCC) / (-I

GND

where -I

is the DC reverse ground pin current and can be found in the absolute

GND

GND

)

GND

resistor.

maximum rating section of the device datasheet.

Power dissipation in R

PD = (-V

CC

)2/R

GND

(when VCC < 0: during reverse polarity situations) is:

GND

Note: In normal condition (no reverse polarity) due to the diode there will be a voltage drop

between GND of the device and GND of the system.

Figure 14. Reverse polarity protection

+ Vcc

+ Vcc

Input

Input

i

i

Output

Diag

Diag

Output

i

i

GND

GND

i

i

Load

Load

R

R

GND

GND

Doc ID 15187 Rev 8 17/23

Diode

Diode

Package mechanical data VNI2140J

10 Package mechanical data

In order to meet environmental requirements, ST offers these devices in different grades of

ECOPACK

®

packages, depending on their level of environmental compliance. ECOPACK®

specifications, grade definitions and product status are available at: www.st.com.

ECOPACK is an ST trademark.

18/23 Doc ID 15187 Rev 8

VNI2140J Package mechanical data

Table 11. PowerSSO-12™ mechanical data

mm

Symbol

Min. Typ. Max.

A 1.250 1.620

A1 0.000 0.100

A2 1.100 1.650

B 0.230 0.410

C 0.190 0.250

D 4.800 5.000

E 3.800 4.000

e 0.800

H 5.800 6.200

h 0.250 0.500

L 0.400 1.270

k 0° 8°

X 1.900 2.500

Y 3.600 4.200

ddd 0.100

Figure 15. PowerSSO-12™ package dimensions

Doc ID 15187 Rev 8 19/23

Package mechanical data VNI2140J

Figure 16. PowerSSO-12™ tube shipment (no suffix)

Figure 17. PowerSSO-12™ tape and reel shipment (suffix “TR”)

20/23 Doc ID 15187 Rev 8

VNI2140J Package mechanical data

Figure 18. Suggested footprint

Doc ID 15187 Rev 8 21/23

Revision history VNI2140J

11 Revision history

Table 12. Document revision history

Date Revision Changes

16-Dec-2008 1 Initial release

29-Apr-2009 2 Updated Table 5 on page 6

03-Jul-2009 3 Updated features in coverpage and Table 5 on page 6

27-Aug-2009 4 Updated Section 9: Reverse polarity protection

25-Mar-2010 5 Updated Coverpage and Table4 on page5

26-Apr-2010 6 Updated Table 5 on page 6

21-Jul-2010 7 Updated Table 8 on page 7

15-Nov-2011 8 Updated Figure 18 on page 21

22/23 Doc ID 15187 Rev 8

VNI2140J

Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the

right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any

time, without notice.

All ST products are sold pursuant to ST’s terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no

liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this

document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products

or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such

third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED

WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED

WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS

OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY TWO AUTHORIZED ST REPRESENTATIVES, ST PRODUCTS ARE NOT

RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING

APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY,

DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE

GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER’S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void

any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any

liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2011 STMicroelectronics - All rights reserved

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -

STMicroelectronics group of companies

Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

Doc ID 15187 Rev 8 23/23

Loading...

Loading...