Features

Type R

VNH5180A-E

Automotive fully integrated H-bridge motor driver

DS(on)

180 mΩ max

(per leg)

I

outVCCmax

8A 41V

VNH5180A-E

■ Output current: 8 A

■ 3 V CMOS compatible inputs

■ Undervoltage shutdown

■ Overvoltage clamp

■ Thermal shutdown

■ Cross-conduction protection

■ Current and power limitation

■ Very low standby power consumption

■ PWM operation up to 20 KHz

■ Protection against loss of ground and loss of

V

CC

Current sense output proportional to motor

■

current

■ Output protected against short to ground and

short to V

Package: ECOPACK

■

CC

®

Description

The VNH5180A-E is a full bridge motor driver

intended for a wide range of automotive

applications. The device incorporates a dual

monolithic high-side driver and two low-side

switches. Both switches are designed using

STMicroelectronics’ well known and proven

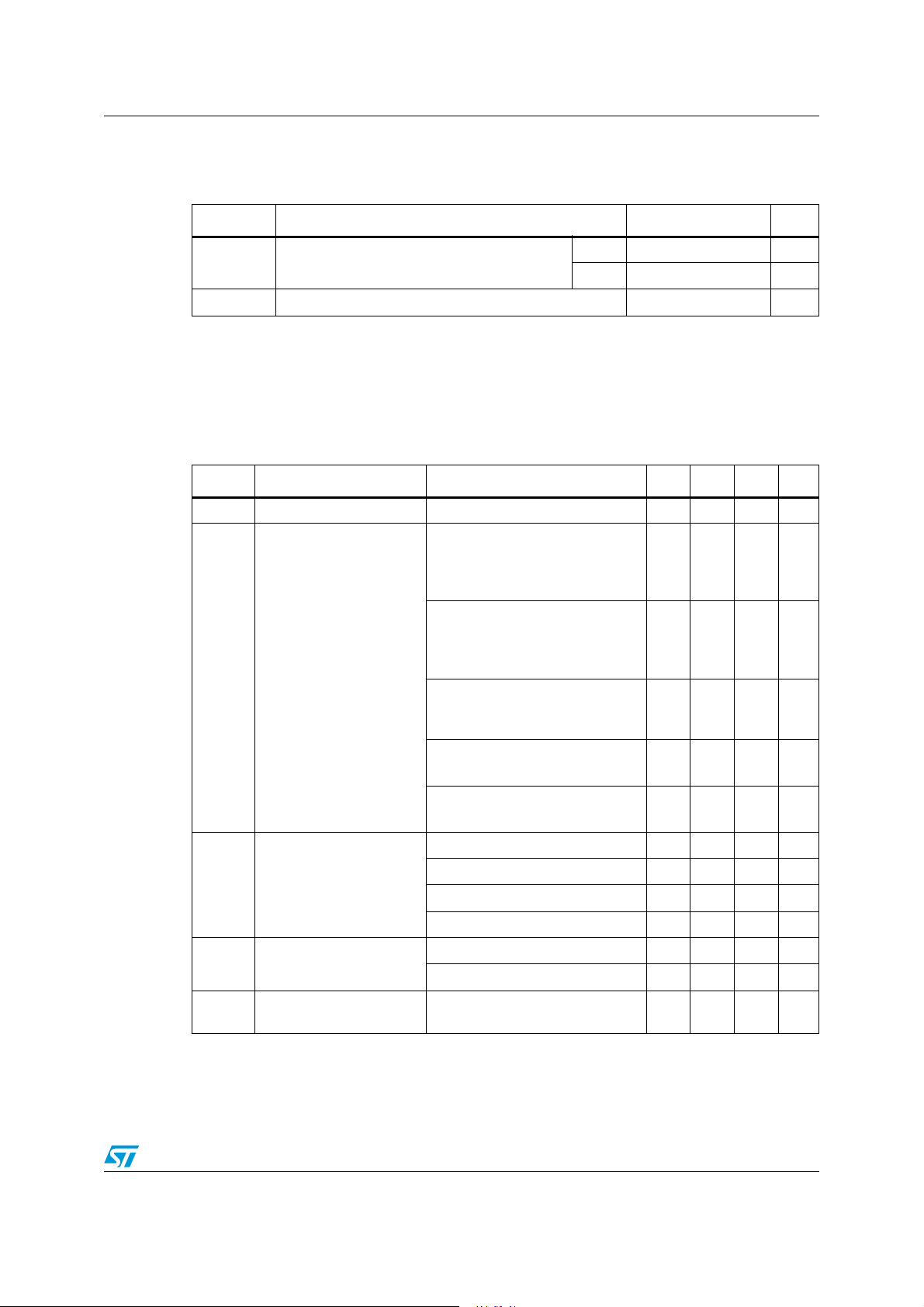

Table 1. Device summary

Package

PowerSSO-36 TP

proprietary VIPower

to efficiently integrate on the same die a true

Power MOSFET with an intelligent

signal/protection circuitry. The three dies are

assembled in PowerSSO-36 TP package on

electrically isolated leadframes. This package,

specifically designed for the harsh automotive

environment offers improved thermal

performance thanks to exposed die pads.

Moreover, its fully symmetrical mechanical design

allows superior manufacturability at board level.

The input signals IN

interface to the microcontroller to select the motor

direction and the brake condition. The DIAG

or DIAG

/ENB, when connected to an external

B

pull-up resistor, enables one leg of the bridge.

Each DIAG

/ENA provides a feedback digital

A

diagnostic signal as well. The normal operating

condition is explained in the truth table. The CS

pin allows to monitor the motor current by

delivering a current proportional to its value when

CS_DIS pin is driven low or left open. When

CS_DIS is driven high, CS pin is in high

impedance condition. The PWM, up to 20 KHz,

allows to control the speed of the motor in all

possible conditions. In all cases, a low level state

on the PWM pin turns off both the LS

switches.

Order codes

Tube Tape and reel

®

M0 technology that allows

and INB can directly

A

and LSB

A

/ENA

A

PowerSSO-36 TP VNH5180A-E VNH5180ATR-E

December 2011 Doc ID 17074 Rev 5 1/31

www.st.com

1

Contents VNH5180A-E

Contents

1 Block diagram and pin description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

2 Electrical specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

2.1 Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

2.2 Thermal data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

2.3 Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

2.4 Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

3 Application information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.1 Reverse battery protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

4 Package and PCB thermal data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

4.1 PowerSSO-36 thermal data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

4.1.1 Thermal calculation in clockwise and anti-clockwise operation in

steady-state mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

4.1.2 Thermal calculation in transient mode . . . . . . . . . . . . . . . . . . . . . . . . . . 24

5 Package and packing information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

5.1 ECOPACK® . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

5.2 PowerSSO-36 TP package information . . . . . . . . . . . . . . . . . . . . . . . . . . 27

5.3 PowerSSO-36 TP packing information . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

6 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

2/31 Doc ID 17074 Rev 5

VNH5180A-E List of tables

List of tables

Table 1. Device summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Table 2. Block description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Table 3. Suggested connections for unused and not connected pins . . . . . . . . . . . . . . . . . . . . . . . . 6

Table 4. Pin definitions and functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Table 5. Pin functions description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Table 6. Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Table 7. Thermal data. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Table 8. Power section . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Table 9. Logic inputs (INA, INB, ENA, ENB, PWM, CS_DIS). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Table 10. Switching (VCC = 13 V, RLOAD = 5 W) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Table 11. Protections and diagnostics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Table 12. Current sense (9 V < VCC < 18 V) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Table 13. Truth table in normal operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Table 14. Truth table in fault conditions (detected on OUTA). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Table 15. Electrical transient requirements (part 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Table 16. Electrical transient requirements (part 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Table 17. Electrical transient requirements (part 3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Table 18. Thermal calculation in clockwise and anti-clockwise operation in steady-state mode . . . . 23

Table 19. Thermal parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Table 20. PowerSSO-36 TP mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Table 21. Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Doc ID 17074 Rev 5 3/31

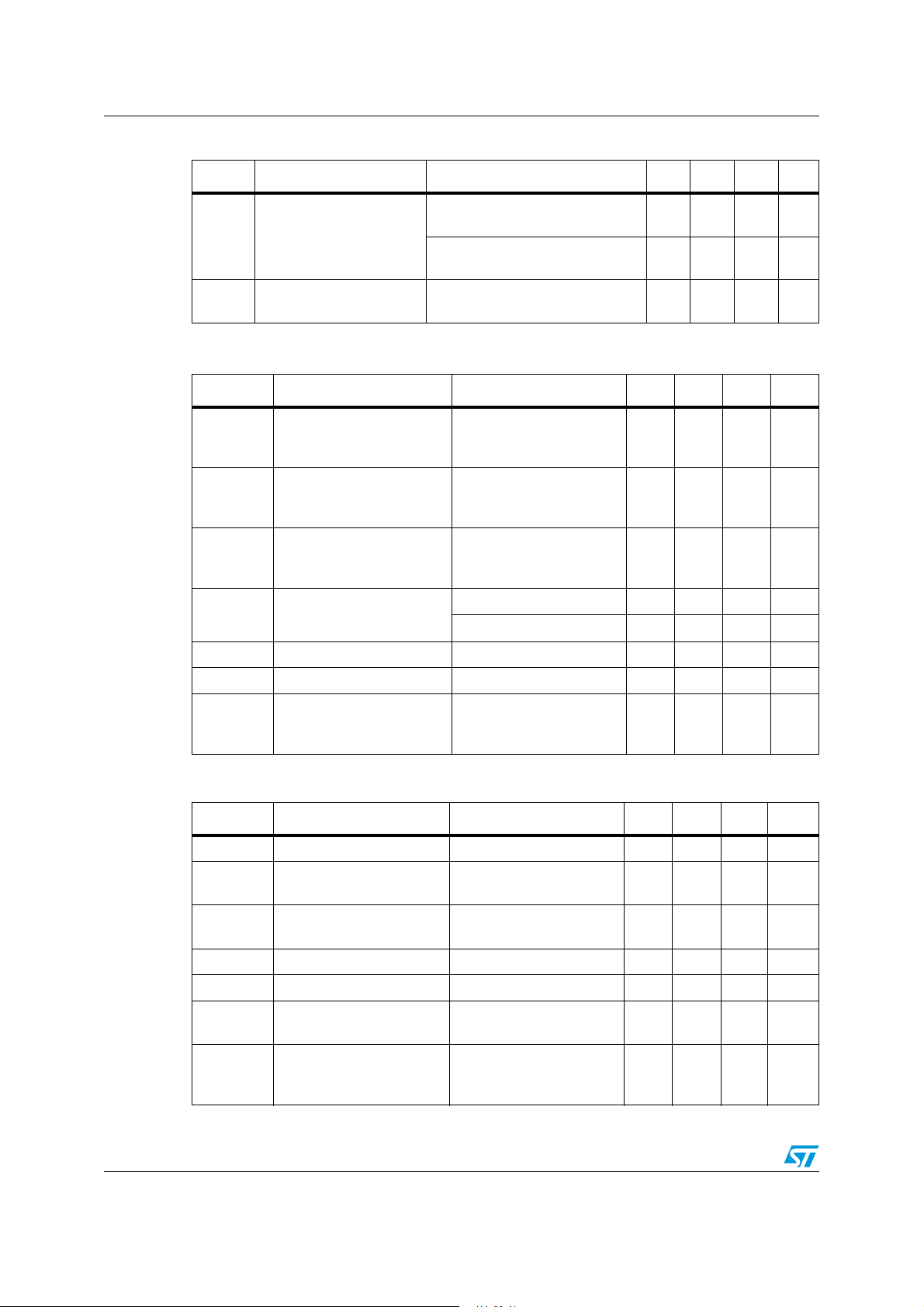

List of figures VNH5180A-E

List of figures

Figure 1. Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Figure 2. Configuration diagram (top view) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Figure 3. Current and voltage conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Figure 4. Definition of the delay times measurement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Figure 5. Definition of the low-side switching times . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Figure 6. Definition of the high-side switching times . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Figure 7. Definition of dynamic cross conduction current during a PWM operation. . . . . . . . . . . . . . 14

Figure 8. Definition of delay response time of sense current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Figure 9. Waveforms in full-bridge operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Figure 10. Waveforms in full-bridge operation (continued) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Figure 11. Typical application circuit for DC to 20 kHz PWM operation short circuit protection . . . . . 19

Figure 12. Behavior in fault condition (how a fault can be cleared) . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Figure 13. Half-bridge configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Figure 14. Multi-motors configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Figure 15. PowerSSO-36™ PC board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Figure 16. Chipset configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Figure 17. Auto and mutual Rthj-amb vs PCB copper area in open box free air condition . . . . . . . . . 23

Figure 18. Detailed chipset configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Figure 19. PowerSSO-36 HSD thermal impedance junction ambient single pulse . . . . . . . . . . . . . . . 25

Figure 20. PowerSSO-36 LSD thermal impedance junction ambient single pulse . . . . . . . . . . . . . . . 25

Figure 21. Thermal fitting model of an H-bridge in PowerSSO-36. . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Figure 22. PowerSSO-36 TP package dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Figure 23. PowerSSO-36 TP tube shipment (no suffix) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Figure 24. PowerSSO-36 TP tape and reel shipment (suffix “TR”) . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

4/31 Doc ID 17074 Rev 5

VNH5180A-E Block diagram and pin description

1 Block diagram and pin description

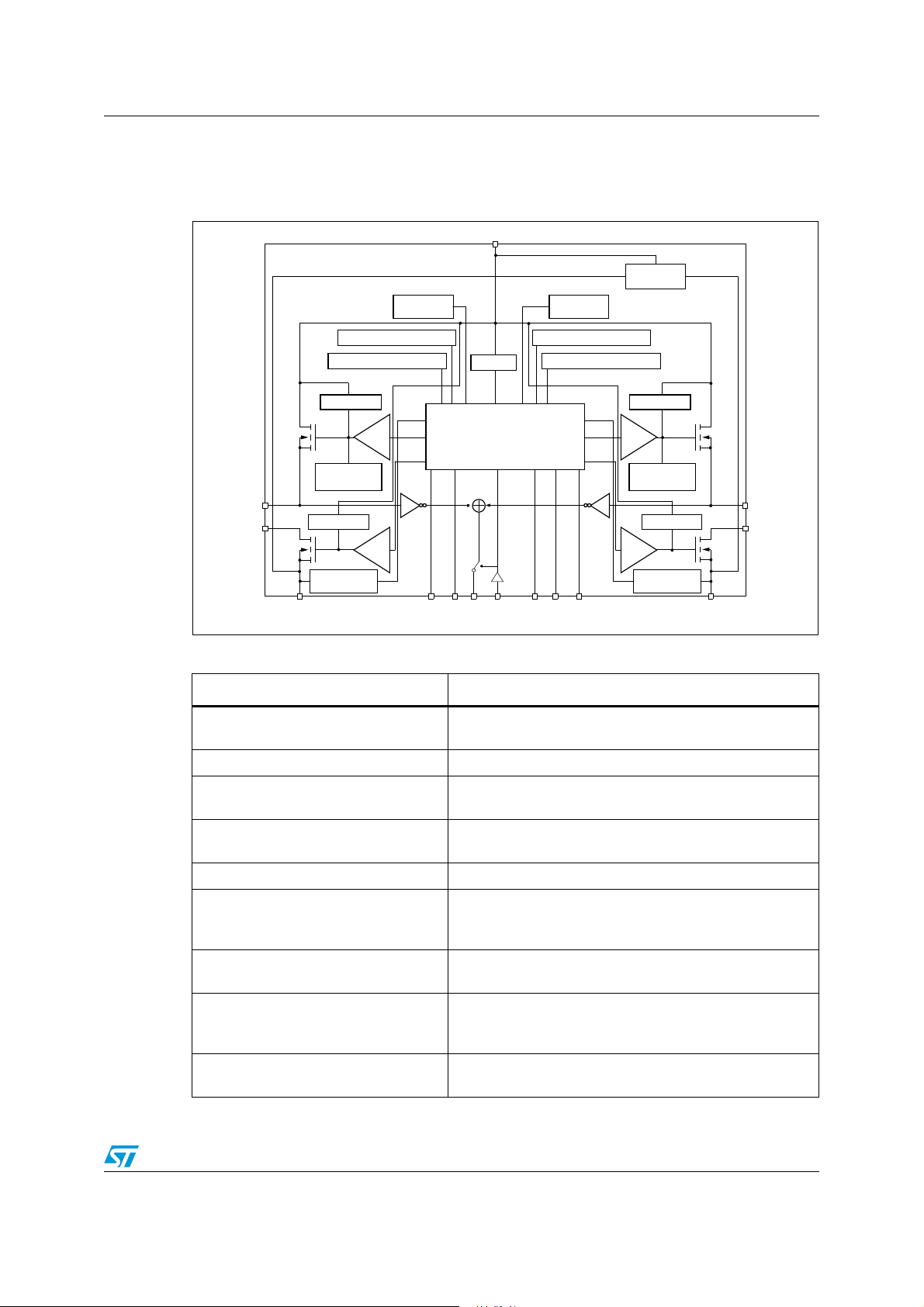

Figure 1. Block diagram

6

##

3)'.!,

#,!-0

&!5,4

$%4%#4)/.

,3!?/6%24%-0% 2!452%

5

6

0/7%2

)4!4)/.

,)-

,3"?/6%24%-0%2!452%

(3"?/6%24%-0%2!452%(3!?/6%24%-0%2! 452%

#,!-0?(3

!

(3

!

3/52#%?(3

Table 2. Block description

$2!).?,3

!

!

,3

!

'.$

#,!-0?,3

/6%2,/!$

$%4%#4/2?!

!

$2)6%2

#522%.4

,)-)4!4)/.?!

!

$2)6%2

(3

!

,3

!

,/')#

+

$)!'!%.!).!#3 #3?$)3 07- )."$)!'"%.

+

#,!-0?(3

$2)6%2

(3

"

#522%.4

,)-)4!4)/.?"

$2)6%2

,3

"

$%4%#4/2?"

"

"

#,!-0?,3

/6%2,/!$

(3

"

3/52#%?(3

"

'.$

,3

"

"

$2!).?,3

("1($'5

Name Description

Logic control

Allows the turn-on and the turn-off of the high-side and the

low-side switches according to the truth table.

Undervoltage Shuts down the device for battery voltage lower than 5V.

High-side and low-side clamp voltage

High-side and low-side driver

Protect the high-side and the low-side switches from the

high voltage on the battery line.

Drive the gate of the concerned switch to allow a proper

R

for the leg of the bridge.

DS(on)

Current limitation Limits the motor current in case of short circuit.

"

"

High-side and low-side overtemperature

protection

Low-side overload detector

In case of short-circuit with the increase of the junction

temperature, it shuts down the concerned driver to prevent

degradation and to protect the die.

Detects when low side current exceeds shutdown current

and latches off the concerned Low side.

Signalizes the abnormal behaviour of the switch (output

Fault detection

Power limitation

shorted to ground or output shorted to battery) by pulling

down the concerned ENx/DIAGx pin.

Limits the power dissipation of the high-side driver inside

safe range in case of short to ground condition.

Doc ID 17074 Rev 5 5/31

Block diagram and pin description VNH5180A-E

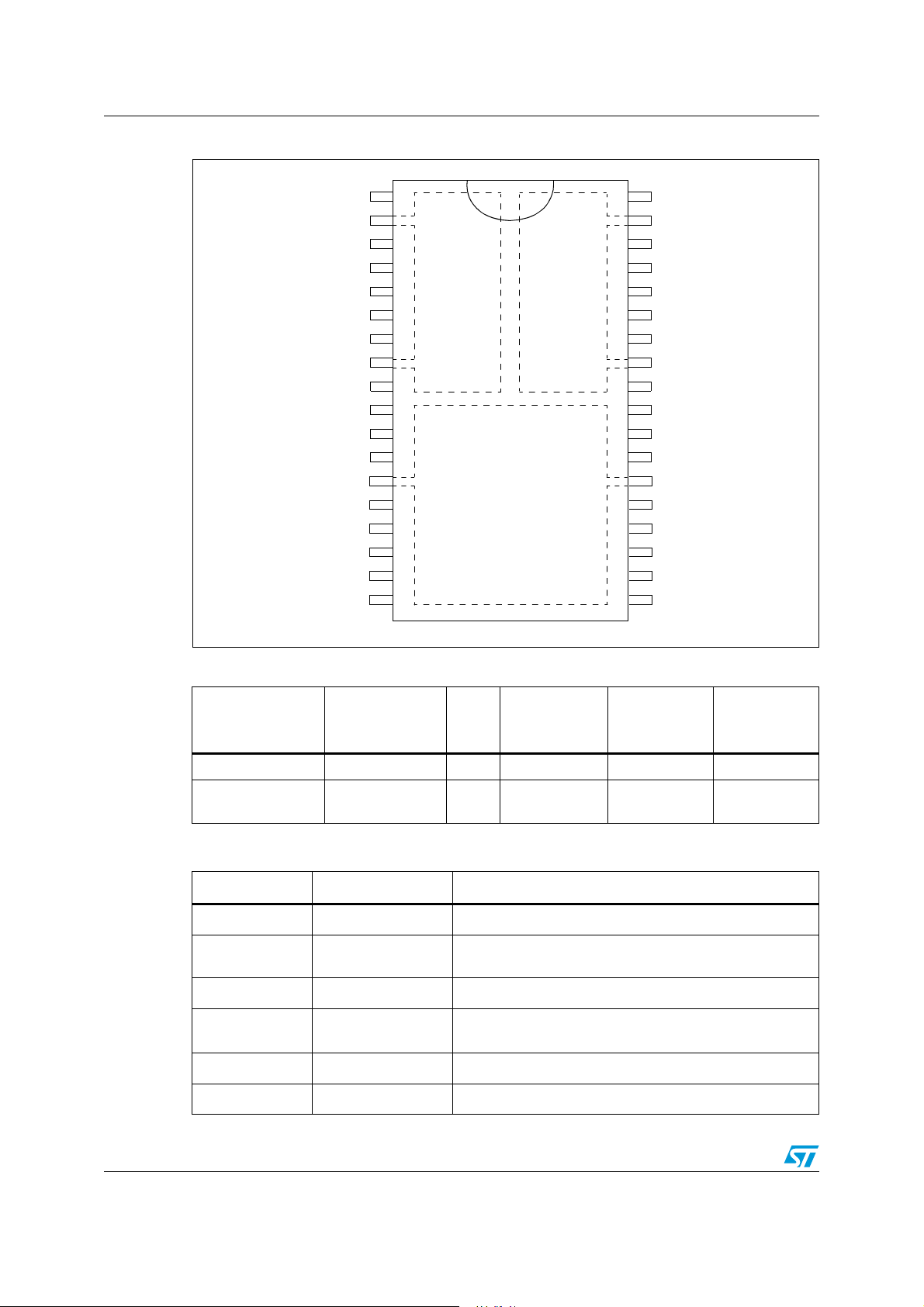

Figure 2. Configuration diagram (top view)

NC

DRAIN LS

GND_A

GND_A

NC

GND_A

GND_A

DRAIN LS

NC

SOURCE HS

SOURCE HS

SOURCE HS

V

NC

IN_A

EN/DIAG_A

IN_PWM

NC

CC

1

A

36

NC

DRAIN LS

B

GND_B

GND_B

Slug2

Slug3

NC

GND_B

GND_B

A

DRAIN LS

B

NC

A

A

A

Slug1

SOURCE HS

SOURCE HS

SOURCE HS

V

CC

NC

B

B

B

IN_B

EN/DIAG_B

CS_DIS

18

19

CS

Table 3. Suggested connections for unused and not connected pins

INPUTx, PWM

Connection / pin Current sense N.C. SOURCE_HSx DRAIN_LSx

Floating Not allowed X X X X

To ground

Table 4. Pin definitions and functions

Pin N° Symbol Function

13, 24 V

1, 5, 9, 14, 18, 23,

28, 32, 36

15 INA Clockwise input

16 ENA/DIAGA

17 IN_PWM PWM input.

19 CS Output of current sense.

Through 1 kΩ

resistor

, Heat Slug1 Drain of high-side switches and power supply voltage.

CC

NC Not connected.

X Not allowed X

Status of high-side and low-side switches A;

open drain output.

DIAGx/ENx

CS_DIS

Through 10 kΩ

resistor

6/31 Doc ID 17074 Rev 5

VNH5180A-E Block diagram and pin description

Table 4. Pin definitions and functions (continued)

Pin N° Symbol Function

20 CS_DIS

21 EN

22 IN

25, 26, 27, 29, 35 OUT

B/DIAGB

B Counter clockwise input.

B

Heat Slug3 Source of high-side switch B / drain of low-side switch B.

,

Active high CMOS compatible pin to disable current sense

pin.

Status of high-side and low-side switches b;

open drain output.

30, 31, 33, 34 GNDB Source of low-side switch B.

2, 8, 10, 11, 12 OUTA, Heat Slug2 Source of high-side switch A / drain of low-side switch A.

3, 4, 6, 7 GND

Table 5. Pin functions description

A Source of low-side switch A.

Name Description

V

CC

GND Power ground.

OUT

OUT

IN

A

IN

B

Battery connection.

A

Power connections to the motor.

B

Voltage controlled input pins with hysteresis, CMOS compatible. These two pins

control the state of the bridge in normal operation according to the truth table (brake

to VCC, Brake to GND, clockwise and counterclockwise).

Voltage controlled input pin with hysteresis, CMOS compatible. Gates of low-side

PWM

FETS get modulated by the PWM signal during their ON phase allowing speed control

of the motor.

Open drain bidirectional logic pins.These pins must be connected to an external pull

/DIAG

EN

A

ENB/DIAG

up resistor. When externally pulled low, they disable half-bridge A or B. In case of fault

A

detection (thermal shutdown of a high-side FET or excessive ON-state voltage drop

B

across a low-side FET), these pins are pulled low by the device (see

table in fault conditions (detected on OUTA)

).

Table 14: Truth

Analog current sense output. This output delivers a current proportional to the motor

CS

current if CS_DIS is low or left open. The information can be read back as an analog

voltage across an external resistor.

CS_DIS Active high CMOS compatible pin to disable the current sense pin.

Doc ID 17074 Rev 5 7/31

Electrical specifications VNH5180A-E

2 Electrical specifications

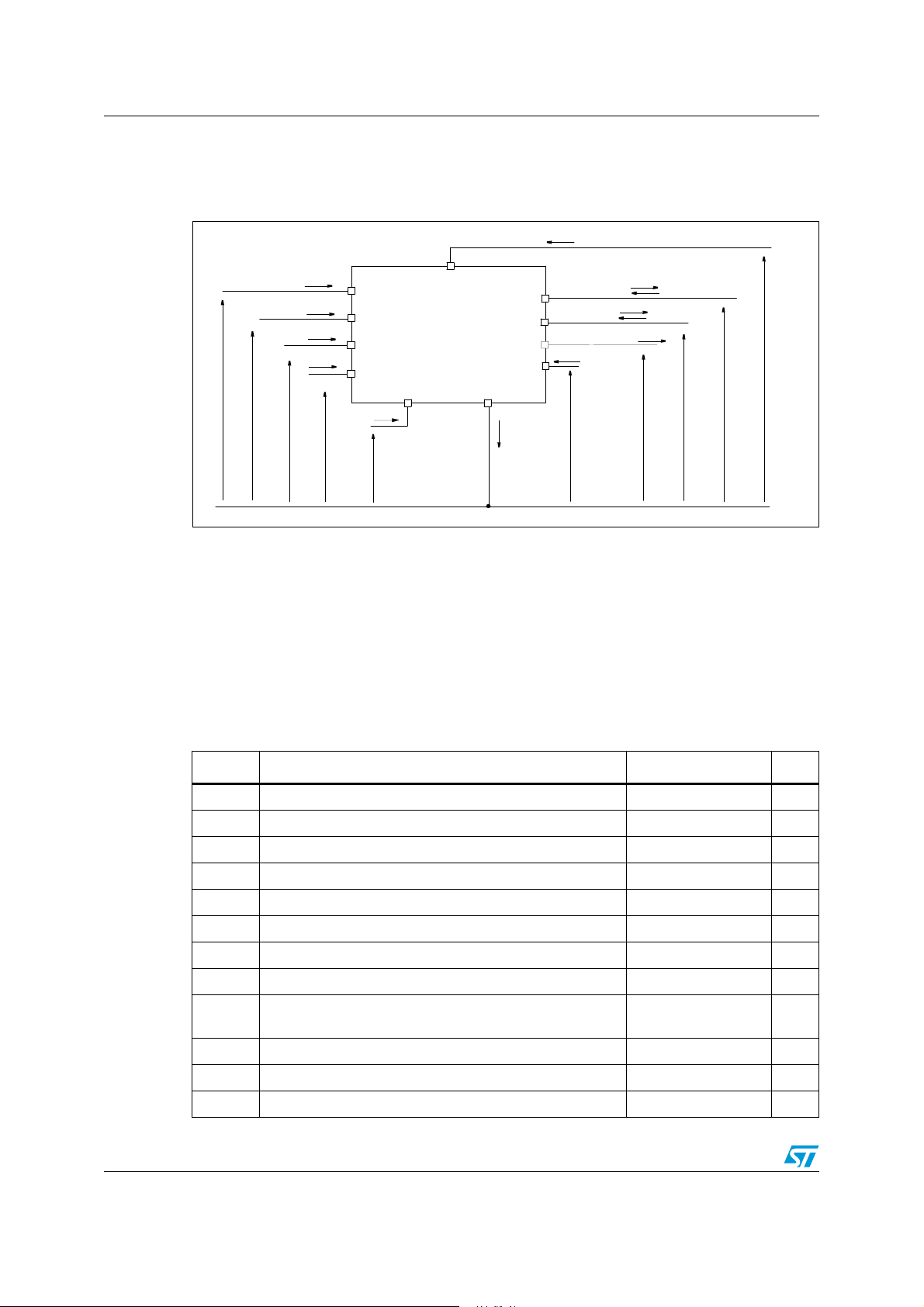

Figure 3. Current and voltage conventions

I

S

V

I

I

I

INA

INB

ENA

I

ENB

IN

A

IN

B

DIAGA/EN

DIAGB/EN

PWM

I

pw

V

CC

OUT

A

OUT

B

A

B

CS

CS_DIS

I

CSD

V

SENSE

I

SENSE

I

OUTB

I

OUTA

V

OUTB

V

OUTA

GND

V

I

GND

CSD

CC

V

V

INA

INB

V

V

ENA

ENB

V

2.1 Absolute maximum ratings

Stressing the device above the rating listed in the

cause permanent damage to the device. These are stress ratings only and operation of the

device at these or any other conditions above those indicated in the Operating sections of

this specification is not implied. Exposure to Absolute Maximum Rating conditions for

extended periods may affect device reliability. Refer also to the STMicroelectronics SURE

Program and other relevant quality document.

Table 6. Absolute maximum ratings

Symbol Parameter Value Unit

V

I

max

I

I

I

CS_DIS

V

V

T

I

GND

Supply voltage + 41 V

CC

Maximum output current (continuous) Internally limited A

Reverse output current (continuous) -15 A

I

R

I

Input current (INA and INB pins) +/- 10 mA

IN

Enable input current (DIAGA/ENA and DIAGB/ENB pins) +/- 10 mA

EN

PWM Input current +/- 10 mA

pw

CS_DIS input current +/- 10 mA

Current sense maximum voltage VCC-41/+V

CS

Electrostatic discharge

ESD

(Human body model: R=1.5 kΩ, C=100 pF)

Junction operating temperature -40 to 150 °C

T

c

Storage temperature -55 to 150 °C

STG

DC reverse ground pin current 200 mA

pw

Table 6: Absolute maximum ratings

CC

may

V

2kV

8/31 Doc ID 17074 Rev 5

VNH5180A-E Electrical specifications

2.2 Thermal data

Table 7. Thermal data

Symbol Parameter Max. value Unit

R

thj-case

R

thj-amb

Thermal resistance junction-case (per leg)

Thermal resistance junction-ambient See

2.3 Electrical characteristics

Values specified in this section are for VCC = 9 V up to 18 V; -40 °C < TJ < 150 °C, unless

otherwise specified.

Table 8. Power section

Symbol Parameter Test conditions Min. Typ. Max. Unit

V

R

ONHS

R

ONLS

Operating supply voltage 5.5 18 V

CC

I

Supply current

S

Static high-side resistance

Static low-side resistance

High-side free-wheeling

V

f

diode forward voltage

HSD 4.8 °C/W

LSD 4.6

Figure 17

Off-state with all fault cleared and

ENx = 0 (standby)

IN

=INB=PWM=0; Tj = 25 °C;

A

=13V

V

CC

36µA

Off-state with all fault cleared and

ENx = 0 (standby)

IN

=INB=PWM=0;

A

=13V; Tj=- 40 to 150 °C

V

CC

Off-state (no standby)

=INB=PWM=0; ENx=5V;

IN

A

=- 40 to 150 °C

T

j

On-state:

IN

or INB= 5 V; no PWM

A

36mA

On-state:

IN

or INB=5V; PWM=20kHz

A

I

= 2.5 A; Tj= -40 °C 75 mΩ

OUT

I

= 2.5 A; Tj=25°C 115 mΩ

OUT

I

= 2.5 A; Tj= 150 °C 230 mΩ

OUT

I

= 2.5 A; Tj=- 40 to 150 °C 250 mΩ

OUT

I

= 2.5A; Tj=25°C 53.5 mΩ

OUT

I

= 2.5A; Tj=- 40 to 150 °C 110 mΩ

OUT

=-2.5A; Tj= 150 °C 0.7 0.9 V

I

OUT

°C/W

10 µA

5mA

6mA

Doc ID 17074 Rev 5 9/31

Electrical specifications VNH5180A-E

Table 8. Power section (continued)

Symbol Parameter Test conditions Min. Typ. Max. Unit

Tj=25°C; V

=13V

V

I

L(off)

I

Table 9. Logic inputs (INA, INB, ENA, ENB, PWM, CS_DIS)

High-side off-state output

current (per channel)

Dynamic cross-

RM

conduction current

CC

Tj= 125 °C; V

=13V

V

CC

I

= 2.5A (see

OUT

=ENX=0V;

OUTX

OUTX

Figure 6

03µA

=ENX=0V;

05µA

)0.6A

Symbol Parameter Test conditions Min. Typ. Max. Unit

Normal operation

V

Input low level voltage

IL

(DIAGX/ENX pin acts as an

0.9 V

input pin)

Normal operation

V

Input high level voltage

IH

(DIAGX/ENX pin acts as an

2.1 V

input pin)

Normal operation

V

IHYST

Input hysteresis voltage

(DIAGX/ENX pin acts as an

0.15 V

input pin)

I

= 1 mA 5.5 6.3 7.5 V

V

I

I

V

ICL

INL

INH

DIAG

Input clamp voltage

Input current VIN=0.9V 1 µA

Input current VIN=2.1V 10 µA

Enable output low

level voltage

IN

I

=-1mA -1.0-0.7-0.3 V

IN

Fault operation

(DIAG

/ENX pin acts as an

X

output pin); I

EN

=1mA

0.4 V

Table 10. Switching (VCC=13V, R

Symbol Parameter Test conditions Min. Typ. Max. Unit

f PWM frequency 0 20 kHz

t

d(on)

t

d(off)

t

t

t

DEL

Turn-on delay time

Turn-off delay time

Rise time See

r

Fall time See

f

Delay time during change

of operating mode

High-side free wheeling

t

diode reverse recovery

rr

time

10/31 Doc ID 17074 Rev 5

=5Ω)

LOAD

Input rise time < 1µs

(see

Figure 6

)

Input rise time < 1µs

(see

Figure 6

)

Figure 5

Figure 5

See

Figure 4

Figure 7

See

250 µs

250 µs

12µs

12µs

200 400 1600 µs

400 ns

VNH5180A-E Electrical specifications

Table 11. Protections and diagnostics

Symbol Parameter Test conditions Min. Typ. Max. Unit

V

USD

V

USDhyst

I

LIM_H

I

SD_LS

V

CLPH

Undervoltage shutdown 3 5 V

Undervoltage shutdown

hysteresis

High-side current limitation 8 12 16 A

Shutdown LS current 16 30 52 A

High-side clamp voltage (VCC to

=0 or OUTB=0)

OUT

A

Low-side clamp voltage

V

CLPLS

T

TSD

T

TR

T

HYST

T

TSD_LS

V

CLP

t

SD_LS

1. T

TSD

2. Valid for both HSD and LSD.

(OUT

A=VCC

= V

OUT

B

CC

(1)

Thermal shutdown temperature VIN= 2.1 V 150 175 200 °C

(2)

Thermal reset temperature 135 °C

(2)

Thermal hysteresis (TSD-TR)7°C

Low-side thermal shutdown

temperature

Total clamp voltage (V

Time to shutdown for the low-side 10 µs

is the minimum threshold temperature between HS and LS

or

to GND)

to GND) I

CC

0.5 V

= 2.5 A 41 46 52 V

I

OUT

I

=2.5A 41 46 52 V

OUT

= 2.1 V 150 175 200 °C

V

IN

=2.5A 41 46 52 V

OUT

Table 12. Current sense (9 V < VCC<18V)

Symbol Parameter Test conditions Min. Typ. Max. Unit

I

=0.35A; V

K

K

K

K

dK

0/K0

dK

1/K1

dK

2/K2

dK

V

3/K3

SENSE

I

0

OUT/ISENSE

I

1

OUT/ISENSE

I

2

OUT/ISENSE

I

3

OUT/ISENSE

Analog sense

(1)

current drift

Analog sense

(1)

current drift

Analog sense

(1)

current drift

Analog sense

(1)

current drift

Max analog sense

output voltage

OUT

=0V; Tj= - 40 to 150 °C

V

CSD

I

=1A; V

OUT

V

CSD

I

= 2.5 A; V

OUT

V

CSD

I

=4A; V

OUT

= - 40 to 150 °C

T

j

I

= 0.35A; V

OUT

V

CSD

I

=1A; V

OUT

V

CSD

=2.5A; V

I

OUT

V

CSD

I

=4A; V

OUT

T

= - 40 to 150 °C

j

I

=2.5A; V

OUT

R

SENSE

SENSE

=0V; Tj= - 40 to 150 °C

SENSE

=0V; Tj= - 40 to 150 °C

SENSE

=0V; Tj= - 40 to 150 °C

SENSE

=0V; Tj= - 40 to 150 °C

SENSE

=0V; Tj= - 40 to 150 °C

SENSE

CSD

=2KΩ

SENSE

= 0.98 V;

SENSE

= 0.98 V;

=4V; V

=0V;

= 0.32 V;

=2.4V;

=4V; V

= 0.32V;

=2.4V;

CSD

CSD

=0V;

=0V;

645 840 1140

700 820 955

710 810 900

690 790 900

-18 18 %

-13 13 %

-13 13 %

-13 13 %

5V

Doc ID 17074 Rev 5 11/31

Electrical specifications VNH5180A-E

Table 12. Current sense (9 V < VCC< 18 V) (continued)

Symbol Parameter Test conditions Min. Typ. Max. Unit

=0A; V

I

OUT

=0V; Tj= - 40 to 150 °C

V

IN

I

SENSE0

Analog sense

leakage current

Delay response time

t

DSENSEH

from falling edge of

CS_DIS pin

Delay response time

t

DSENSEL

from rising edge of

CS_DIS pin

1. Analog sense current drift is deviation of factor K for a given device over (-40 °C to 150 °C and

9V < VCC < 18 V) with respect to its value measured at TJ = 25 °C, VCC = 13 V.

V

=0V; VIN=5V;

CSD

= - 40 to.150 °C

T

j

=5V; VIN=5V; I

V

CSD

T

= - 40 to.150 °C

j

VIN=5V; V

=90% of I

I

SENSE

(see

Figure 8

=5V; V

V

IN

I

=10% of I

SENSE

(see

Figure 8

SENSE

SENSE

SENSE

)

)

=0V; V

OUT

<4V, I

OUT

SENSEmax

<4V; I

OUT

SENSEmax

=5V;

CSD

=2.5A;

=2.5A,

=2.5A;

05µA

0 180 µA

05µA

Figure 4. Definition of the delay times measurement

V

INA

V

INB

50 µs

20 µs

t

PWM

I

LOAD

t

DEL

12/31 Doc ID 17074 Rev 5

t

t

t

DEL

t

VNH5180A-E Electrical specifications

Figure 5. Definition of the low-side switching times

PWM

t

V

OUTA, B

90%

80%

t

f

20%

10%

t

r

t

Figure 6. Definition of the high-side switching times

V

INA

V

OUTA

t

D(on)

t

D(off)

90%

10%

t

t

Doc ID 17074 Rev 5 13/31

Electrical specifications VNH5180A-E

Figure 7. Definition of dynamic cross conduction current during a PWM operation

INA= 1, INB=0

PWM

t

I

MOTOR

t

V

OUTB

t

I

CC

I

RM

t

t

rr

Figure 8. Definition of delay response time of sense current

INPUT

CS_DIS

LOAD CURRENT

SENSE CURRENT

t

DSENSEH

t

DSENSEL

14/31 Doc ID 17074 Rev 5

VNH5180A-E Electrical specifications

Table 13. Truth table in normal operating conditions

INAINBDIAGA/ENADIAGB/ENBOUTAOUT

1

1

H

B

H High Imp. Brake to V

0L

11

1

0

L

H Counterclockwise (CCW)

CS Operating mode

Clockwise (CW)

I

SENSE=IOUT

/K

CC

0 L High Imp. Brake to GND

Table 14. Truth table in fault conditions (detected on OUTA)

IN

1

IN

A

1

B

DIAGA/EN

A

DIAGB/EN

B

OUT

A

OUT

CS (V

B

CSD

H

High Imp.

0L

1

1HI

0

0

OPEN

OUTB

0L

High Imp.

X X 0 OPEN

Fault Information Protection Action

Note: In normal operating conditions the DIAGX/ENX pin is considered as an input pin by the

device. This pin must be externally pulled high.

=0V)

/K

Doc ID 17074 Rev 5 15/31

Electrical specifications VNH5180A-E

Table 15. Electrical transient requirements (part 1)

ISO 7637-2:

2004(E)

Test pulse

Test levels

(1)

Number of

pulses or

III IV Min. Max.

test times

Burst cycle/pulse

repetition time

Delays and

Impedance

1 -75V -100V 5000 pulses 0.5s 5s 2 ms, 10Ω

2a +37V +50V 5000 pulses 0.2s 5s 50µs, 2Ω

3a -100V -150V 1h 90ms 100ms 0.1µs, 50Ω

3b +75V +100V 1h 90ms 100ms 0.1µs, 50Ω

4 -6V -7V 1 pulse 100ms, 0.01Ω

(2)

5b

+65V +87V 1 pulse 400ms, 2Ω

1. The above test levels must be considered referred to VCC= 13.5 V except for pulse 5b.

2. Valid in case of external load dump clamp: 40V maximum referred to ground.

Table 16. Electrical transient requirements (part 2)

ISO 7637-2:

Test level results

(1)

2004(E)

Test pulse

III IV

1C C

2a C C

3a C C

3b C C

4C C

(2)

5b

CC

1. The above test levels must be considered referred to VCC = 13.5 V except for pulse 5b.

2. Valid in case of external load dump clamp: 40V maximum referred to ground.

Table 17. Electrical transient requirements (part 3)

Class Contents

C All functions of the device are performed as designed after exposure to disturbance.

E

One or more functions of the device are not performed as designed after exposure to

disturbance and cannot be returned to proper operation without replacing the device.

16/31 Doc ID 17074 Rev 5

VNH5180A-E Electrical specifications

2.4 Waveforms

Figure 9. Waveforms in full-bridge operation

NORMAL OPERATION (DIAGA/ENA=1, DIAGB/ENB=1)

DIAGA/EN

DIAGB/EN

IN

A

IN

B

A

B

LOAD CONNECTED BETWEEN OUTA, OUT

PWM

OUT

A

OUT

I

B

OUTA->OUTB

CS (*)

t

CS_DIS

(*) CS BEHAVIOUR DURING PWM MODE DEPENDS ON PWM FREQUENCY AND DUTY CYCLE

DEL

NORMAL OPERATION (DIAGA/ENA=1, DIAGB/ENB=0 and DIAGA/ENA=0, DIAGB/ENB=1)

LOAD CONNECTED BETWEEN OUTA, OUT

DIAGA/EN

DIAGB/EN

IN

IN

PWM

OUT

OUT

I

OUTA->OUTB

CS_DIS

A

B

A

B

A

B

CS

B

t

DEL

B

CURRENT LIMITATION/THERMAL SHUTDOWN or OUTA SHORTED TO GROUND

IN

A

IN

B

I

OUTA->OUTB

T

DIAGA/EN

DIAGB/EN

jHSA

I

LIM

Tj =T

TSD

Tj < T

TSD

A

B

Tj > T

TR

T

TSD_HSA

T

TR_HSA

CS

CS_DIS

limitation

normal operation

current

power limitation

shorted to ground

OUT

A

normal operation

Doc ID 17074 Rev 5 17/31

Electrical specifications VNH5180A-E

Figure 10. Waveforms in full-bridge operation (continued)

OUTA shorted to VCC (resistive short) and undervoltage shutdown

CS_DIS

IN

A

IN

B

OUT

A

OUT

B

I

OUTA->OUTB

I

SD_LS

I

LSA

T

TSD_LS

T

j_LSA

DIAGB/EN

DIAGA/EN

CS

CS_DIS

IN

A

IN

B

OUT

A

OUT

B

I

OUTA->OUTB

I

LSA

T

j_LSA

DIAGB/EN

DIAGA/EN

CS

B

A

V<nominal

normal operation OUTA softly shorted to V

OUTA shorted to VCC (pure short) and undervoltage shutdown

I

SD_LS

T

TSD_LS

B

A

V<nominal

CC

normal operation under voltage shutdown

normal operation OUTA hardly shorted to V

18/31 Doc ID 17074 Rev 5

CC

normal operation undervoltage shutdown

VNH5180A-E Application information

3 Application information

In normal operating conditions the DIAGX/ENX pin is considered as an input pin by the

device. This pin must be externally pulled high.

PWM pin usage: In all cases, a “0” on the PWM pin turns off both LS

When PWM rises back to “1”, LS

or LSB turn on again depending on the input pin state.

A

and LSB switches.

A

Figure 11. Typical application circuit for DC to 20 kHz PWM operation short circuit

protection

V

CC

Reg 5V

μC

33nF

1K

DIAG

1K

1k

10K

3.3K

1K

1.5K

A

/EN

PWM

CS_DIS

CS

+ 5V

V

CC

A

IN

A

HS

A HS

OUT

A

LS

A

OUT

B

B

LS

M

GND

100K

S

G

b) N MOSFET

D

DIAGA/EN

B

+5V

A

GND

3.3K

DIAGB/EN

IN

B

1K

B

1K

Vcc

Note: The value of the blocking capacitor (C) depends on the application conditions and defines

voltage and current ripple on supply line at PWM operation. Stored energy of the motor

inductance may fly back into the blocking capacitor, if the bridge driver goes into 3-state.

This causes a hazardous overvoltage if the capacitor is not big enough. As basic orientation,

500 µF per 10 A load current is recommended.

In case of a fault condition the DIAGX/ENX pin is considered as an output pin by the device.

The fault conditions are:

– Overtemperature on one or both high-sides

– Short to battery condition on the output (overcurrent detection on the low-side

Power MOSFE T)

Possible origins of fault conditions may be:

OUT

is shorted to ground → overtemperature detection on high-side A

A

OUT

is shorted to VCC → low-side Power MOSFET overcurrent detection

A

When a fault condition is detected, the user can identify which power element is in fault by

monitoring the IN

, INB, DIAGA/ENA and DIAGB/ENB pins.

A

Doc ID 17074 Rev 5 19/31

Application information VNH5180A-E

In any case, when a fault is detected, the faulty leg of the bridge is latched off. To turn on the

respective output (OUT

) again, the input signal must rise from low to high level.

X

Figure 12. Behavior in fault condition (how a fault can be cleared)

Note: In case of the fault condition is not removed, the procedure for unlatching and sending the

device in Stby mode is:

- Clear the fault in the device (toggle: IN

- Pull low all inputs, PWM and Diag/EN pins within t

if ENA= 0 or INB if ENB=0)

A

.

DEL

If the Diag/En pins are already low, PWM = 0, the fault can be cleared simply toggling the

input. The device enters in stby mode as soon as the fault is cleared.

3.1 Reverse battery protection

Three possible solutions can be considered:

– A Schottky diode D connected to V

– An N-channel MOSFET connected to the GND pin (see

application circuit for DC to 20 kHz PWM operation short circuit protection

– A P-channel MOSFET connected to the V

The device sustains no more than -15 A in reverse battery conditions because of the two

Body diodes of the Power MOSFETs. Additionally, in reverse battery condition the I/Os of

VNH5180A-E is pulled down to the V

line (approximately -1.5 V).

CC

CC

pin

CC

Figure 11: Typical

pin

)

20/31 Doc ID 17074 Rev 5

VNH5180A-E Application information

Series resistor must be inserted to limit the current sunk from the microcontroller I/Os. If

I

is the maximum target reverse current through microcontroller I/Os, series resistor is:

Rmax

V

–

IOsVCC

---------------------------------=

R

I

Rmax

Figure 13. Half-bridge configuration

V

CC

/EN

DIAG

A

DIAGB/EN

PWM

OUT

IN

A

IN

B

A

B

B

IN

A

IN

B

DIAG

A

DIAGB/EN

PWM

OUT

A

/EN

A

B

GND

OUT

B

M

OUT

A

GND

Note: The VNH5180A-E can be used as a high power half-bridge driver achieving an On

resistance per leg of 90 m

Ω

.

Figure 14. Multi-motors configuration

V

CC

/EN

DIAG

A

DIAGB/EN

PWM

OUT

IN

A

IN

B

A

B

B

IN

A

IN

B

DIAG

A

DIAGB/EN

PWM

OUT

A

/EN

A

B

OUT

B

M

2

OUT

A

GND

M

1

Note: The VNH5180A-E can easily be designed in multi-motors driving applications such as seat

positioning systems where only one motor must be driven at a time. DIAG

GND

M

3

/ENX pins allow

X

to put unused half-bridges in high impedance.

Doc ID 17074 Rev 5 21/31

Package and PCB thermal data VNH5180A-E

4 Package and PCB thermal data

4.1 PowerSSO-36 thermal data

Figure 15. PowerSSO-36™ PC board

Double layers: footprint

Double layers: 2cm

Double layers: 8cm

Note:

Board finish thickness 1.6 mm +/- 10 %, Board double layers, Board dimension 129 mm x 60 mm, Board Material FR4, Cu

thickness 0.070 mm (front and back side), Ther mal vias spaced on a 1.2 mm x 1.2 mm grid, Vias pad clearance thickness

0.2 mm, Thermal via diameter 0.3 mm +/- 0.08 mm, Cu thickness on vias 0.025 mm.

22/31 Doc ID 17074 Rev 5

2

of Cu

2

of Cu

VNH5180A-E Package and PCB thermal data

Figure 16. Chipset configuration

CHIP 1

R

thA

Figure 17. Auto and mutual R

condition

80

70

60

50

40

°C/W

30

20

R

thAB

CHIP 2

R

thB

thj-amb

R

thAC

CHIP 3

R

thBC

R

thC

vs PCB copper area in open box free air

RthA

RthB = RthC

RthAB = RthAC

RthBC

10

0

0123456789

cm2 of Cu Area (re fer to PCB layout)

4.1.1 Thermal calculation in clockwise and anti-clockwise operation in steady-state mode

Table 18. Thermal calculation in clockwise and anti-clockwise operation in steady-

state mode

HSAHSBLSALS

ON OFF OFF ON

OFF ON ON OFF

B

P

x R

P

x R

dHSA

thHSLS

dHSB

thHSLS

x R

x R

T

jHSAB

thHS

+ T

thHS

+ T

+ P

amb

+ P

amb

dLSB

dLSA

P

dHSA

P

dLSB

P

dHSB

P

dLSA

x R

x R

x R

x R

T

jLSA

thHSLS

thLSLS

thHSLS

thLS

+ T

+

+ T

+

amb

amb

P

x R

P

x R

dHSA

dHSB

Doc ID 17074 Rev 5 23/31

x R

+ T

thLS

x R

thLSLS

T

jLSB

thHSLS

amb

thHSLS

+ T

amb

+ P

+ P

dLSB

dLSA

Package and PCB thermal data VNH5180A-E

4.1.2 Thermal calculation in transient mode

T

= P

= P

= P

• Zhs + Z

dhs

• Zls + P

dlsA

• Zls + P

dlsB

hs

T

lsA

T

lsB

Figure 18. Detailed chipset configuration

hsls

dhs

dhs

• (P

• Z

• Z

dlsA

hsls

hsls

+ P

+ P

+ P

dlsB

dlsB

dlsA

) + T

• Z

• Z

amb

+ T

hsls

+ T

hsls

CHIP 1

Z

ts

amb

amb

Z

hsls

CHIP 2

Z

ls

Equation 1: pulse calculation formula

Z

THδRTH

δ Z

THtp

1 δ–()+⋅=

where

δ tpT⁄=

Z

hsls

CHIP 3

Z

lsls

Z

ls

24/31 Doc ID 17074 Rev 5

VNH5180A-E Package and PCB thermal data

Figure 19. PowerSSO-36 HSD thermal impedance junction ambient single pulse

100

HSD-8 cm^2 Cu

HSD-2 cm^2 Cu

HSD-footpr int

HsLsD-8 cm^2 Cu

HsLsD-2 cm^2 Cu

HsLsD-footprint

10

°C/W

1

0.1

0.001 0.01 0.1 1 10 100 1000time (se c)

Figure 20. PowerSSO-36 LSD thermal impedance junction ambient single pulse

ZTH -HSD @ cu area

100

ZTH -LSD @ cu area

LSD-8 cm ^2 Cu

LSD-2 cm ^2 Cu

LSD-footpri nt

LsLsD-8 cm^2 Cu

LsLsD-2 cm^2 Cu

LsLsD-footprint

10

Z

ls

°C/W

1

0.1

0.001 0.01 0.1 1 10 100 1000time (sec)

Z

lsls

Doc ID 17074 Rev 5 25/31

Package and PCB thermal data VNH5180A-E

Figure 21. Thermal fitting model of an H-bridge in PowerSSO-36

Table 19. Thermal parameters

(1)

Area/island (cm2) Footprint 2 8

R1 = R7 (°C/W) 0.4

R2 = R8 (°C/W) 3.5

R3 (°C/W) 8

R4 (°C/W) 30 16 11

R5 (°C/W) 40 30 14

R6 (°C/W) 36 34 21

R9 = R15 (°C/W) 0.1

R10 = R16 (°C/W) 5.2

R11 = R17 (°C/W) 32 14 14

R12 = R18 (°C/W) 49 21 21

R13 = R19 (°C/W) 52 36 24

R14 = R20 (°C/W) 50 40 33

R21 = R22 = R23 (°C/W) 80 77 75

C1 = C7 = C9 = C15 (W.s/°C) 0.0005

C2 = C8 (W.s/°C) 0.008

C3 (W.s/°C) 0.09

C4 (W.s/°C) 0.5 0.8 0.8

C5 (W.s/°C) 0.8 1.4 2

C6 (W.s/°C) 7 8 10

C10 = C16 (W.s/°C) 0.009

C11 = C17 (W.s/°C) 0.09 0.07 0.07

C12 = C18 (W.s/°C) 0.45 0.45 0.45

C13 = C19 (W.s/°C) 0.8 1.2 1.4

C14 = C20 (W.s/°C) 4 5 8

C21 = C22 = C23 (W.s/°C) 0.005 0.003 0.003

1. The blank space means that the value is the same as the previous one.

26/31 Doc ID 17074 Rev 5

VNH5180A-E Package and packing information

5 Package and packing information

5.1 ECOPACK

®

In order to meet environmental requirements, ST offers these devices in different grades of

ECOPACK

®

packages, depending on their level of environmental compliance. ECOPACK®

specifications, grade definitions and product status are available at: www.st.com

ECOPACK

®

is an ST trademark.

5.2 PowerSSO-36 TP package information

Figure 22. PowerSSO-36 TP package dimensions

.

Doc ID 17074 Rev 5 27/31

Package and packing information VNH5180A-E

Table 20. PowerSSO-36 TP mechanical data

Millimeters

Symbol

Min. Typ. Max.

A 2.15 - 2.47

A2 2.15 - 2.40

a1 0 - 0.1

b 0.18 - 0.36

c 0.23 - 0.32

D 10.10 - 10.50

E 7.4 - 7.6

e-0.5-

e3 - 8.5 -

F2.3

G- -0.1

H 10.1 - 10.5

h--0.4

k 0 deg 8 deg

L0.6 - 1

M4.3

N - - 10 deg

O1.2

Q0.8

S2.9

T3.65

U1.0

X1 1.85 2.35

Y1 3 3.5

X2 1.85 2.35

Y2 3 3.5

X3 4.7 - 5.2

Z1 0.4

Z2 0.4

Y3 3 - 3.5

28/31 Doc ID 17074 Rev 5

VNH5180A-E Package and packing information

5.3 PowerSSO-36 TP packing information

Figure 23. PowerSSO-36 TP tube shipment (no suffix)

Base Qty 49

C

B

A

Figure 24. PowerSSO-36 TP tape and reel shipment (suffix “TR”)

Bulk Qty 1225

Tube length (±0.5) 532

A 3.5

B 13.8

C (±0.1) 0.6

All dimensions are in mm.

Reel dimensions

Base Qty 1000

Bulk Qty 1000

A (max) 330

B (min) 1.5

C (±0.2) 13

F 20.2

G (+2 / -0) 24.4

N (min) 100

T (max) 30.4

Tape dimensions

According to Electronic Industries Association

(EIA) Standard 481 rev. A, Feb. 1986

Tape width W 24

Tape Hole Spacing P0 (±0.1) 4

Component Spacing P 12

Hole Diameter D (±0.05) 1.55

Hole Diameter D1 (min) 1.5

Hole Position F (±0.1) 11.5

Compartment Depth K (max) 2.85

Hole Spacing P1 (±0.1) 2

End

All dimensions are in mm.

Start

Top

cover

tape

500mm min

Empty components pockets

sealed with cover tape.

User direct ion of feed

No componentsNo components Components

500mm min

Doc ID 17074 Rev 5 29/31

Revision history VNH5180A-E

6 Revision history

Table 21. Document revision history

Date Revision Changes

11-Feb-2010 1 Initial release.

Updated following tables:

–

28-Sep-2010 2

13-Oct-2010 3

Table 7: Thermal data

–

Table 8: Power section

–

Table 12: Current sense (9 V < VCC < 18 V)

Updated

Chapter 3: Application information

Updated following tables:

–

Table 18: Thermal calculation in clockwise and anti-clockwise

operation in steady-state mode

–

Table 19: Thermal parameters

20-Oct-2010 4

22-Dec-2011 5

Changed document status from target specification to definitive

datasheet

Updated

Added

Figure 1: Block diagram

Table 3: Suggested connections for unused and not

connected pins

Table 11: Protections and diagnostics

–T

, TTR, T

TSD

Updated

Figure 9: Waveforms in full-bridge operation

: added note

HYST

:

and

Figure 10: Waveforms in full-bridge operation (continued)

30/31 Doc ID 17074 Rev 5

VNH5180A-E

Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the

right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any

time, without notice.

All ST products are sold pursuant to ST’s terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no

liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this

document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products

or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such

third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED

WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED

WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS

OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY TWO AUTHORIZED ST REPRESENTATIVES, ST PRODUCTS ARE NOT

RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING

APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY,

DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE

GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER’S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void

any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any

liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2011 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -

Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

Doc ID 17074 Rev 5 31/31

Loading...

Loading...