®

查询STV8207供应商

®

for A2 and NICAM Television/Video Recorders

Key Features

■ Full-Automatic Multi-Standard Demodulation

● B / G / I / L / M / N / D / K Standards

● Mono AM and FM

● FM 2-Carrier (German and Korean Zweiton) and

NICAM

■ Multi-Channel Capability

● 3 I²S digital inputs, S/PDIF (in/out)

● 5.1 analog outputs

● Dolby® Pro Logic®

● Dolby® Pro Logic II®

■ Sound Processing

● ST royalty-free processing: ST WideSurround, ST

OmniSurround, ST Dynamic Bass, SRS® WOW™,

SRS® TruSurround XT™ which is Virtual Dolby®

Surround and Virtual Dolby® Digital compliant

● Independent Volume / Balance for Loudspeakers

and Headphone

● Loudspeakers: Smart Volume Control (SVC),

5-band equalizer and loudness

● Headphone: Smart Volume Control (SVC), Bass-

Treble, Loudness and SRS® Tru B a s s™

■ Analog Audio Matrix

● 4 stereo inputs

● 3 stereo outputs

● THRU mode

■ Audio Delay for Audio Video Synchronization

● Embedded stereo delay up to 120 ms for lip-sync

function (up to 180 ms for tuner input)

● Independent delay on headphone and loudspeaker

channels

The STV82x7 family, based on audio digital signal

processors (DSP), performs high quality and advanced

dedicated digital audio processing.These devices

provide all of the necessary resources for automatic

detection and demodulation of analog audio

transmissions for European and Asian terrestrial TV

broadcasts.

STV82x7

Digital Audio Decoder/Processor

PRELIMINARY DATA

Virtual or true, multi-channel capabilities and easy digital

links make them ideal for digital audio low cost consumer

applications. Starting from enhanced stereo up to

independent control of 5 loudspeakers and a subwoofer

(5.1 channels), the STV82x7 family offers standard and

advanced features plus sound enhancements, spatial

and virtual effects to enhance television viewer comfort

and entertainment.

Typical Applications

● Analog and digital TV with virtual surround sound

● Analog and digital TV with multi-channel surround

sound

● DVD and HDD recorders

● “Palm size” portable TV

7

x

2

8

V

T

S

© 2004 SRS Labs, Inc. All rights reserved, SRS and

the SRS logo are registered trademarks of SRS Labs, Inc.

“Dolby”, “Pro Logic”, and the double-D symbol are trademarks of

Dolby Laboratories.

Rev. 3

February 2005 1/149

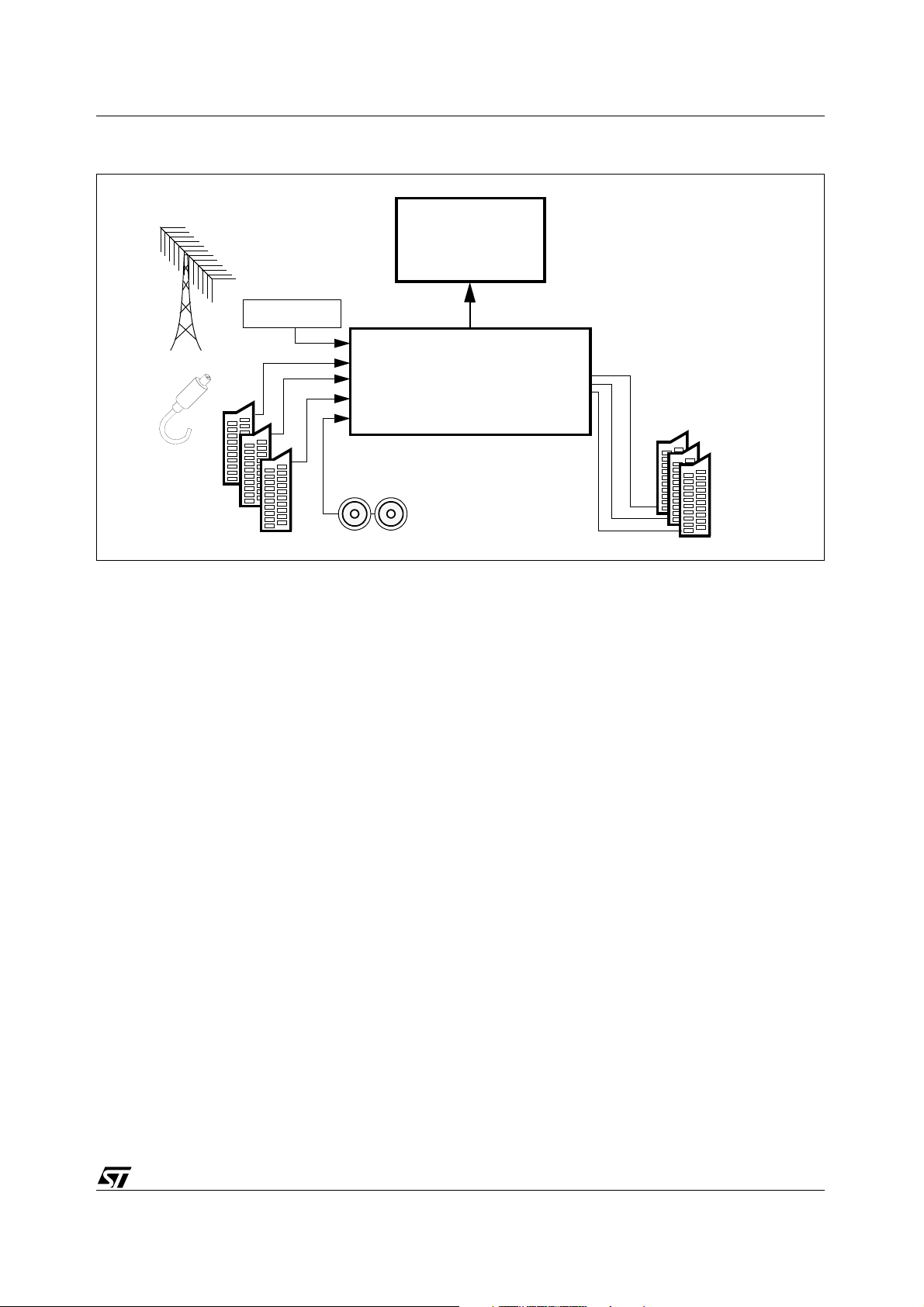

Block Diagram

LS_L

Loudspeakers

LS_C

LS_R

LS_SUB

Headphone / Surround

HP_LSS_L

HP_LSS_R

SC1_OUT_L

SC1_OUT_R

SC2_OUT_L

SC2_OUT_R

SC3_OUT_L

SC3_OUT_R

SCART

STV82x7

Outputs

™

Trubass

®

Bass/Treble, SRS

RMS

2 V

Stereo

DAC

Audio

Loudspeakers

Digital Audio Processing

RMS

0.9 V

DAC

Audio

Stereo

™

®,

®

Pro Logic

Pro Logic II

®

®

Dolby

Dolby

Volume, Equalizer, Balance,

ST WideSurround, ST Dynamic Bass,

ST OmniSurround,

Loudness,Smart Volume Control,

or TruSurround XT

™

WOW

Bass Management, Beeper

®

SRS

RMS

0.9 V

DAC

Audio

Stereo

Headphone

Digital Audio Processing

Volume, Balance, Loudness,

Smart Volume Control,

Digital Audio Matrix

In / Out

S/PDIF

Pre-scaler

Output

Analog

2 V

RMS

RMS

2 V

Audio

Matrix

Management

Power Supply

XTALOUT

XTALIN

Clock

Generator

CLK_SEL

clocks

I²S

data

I²S

Interface

Digital

FM/AM

NICAM

FM 2-carrier

Demodulation

A/D

IRQ

Logic

Control

AGC

SIF

Detection

Headphone

Sound IF

2/149

Mono Input

A/D

Audio

Input

Audio

Analog

SC2_IN_L

SC1_IN_L

MONO_IN

SC1_IN_R

SC2_IN_R

I²C

Interface

I²C

SCL SDA

Matrix

SC3_IN_L

SC4_IN_L

SC3_IN_R

SC4_IN_R

SCART

Inputs

STV82x7

Table of Contents

Chapter 1 General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6

1.1 STV82x7 Overview ..............................................................................................................8

1.1.1 Core Features ............................................................................................................................................8

1.1.2 Software Information .................................................................................................................................9

1.1.3 Device Input Modes ...................................................................................................................................9

1.1.4 Electrical Features ...................................................................................................................................10

1.2 Typical Applications ...........................................................................................................10

1.3 Pin Descriptions and Application Diagrams .......................................................................14

Chapter 2 System Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

Chapter 3 Digital Demodulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

3.1 Sound IF Signal ..................................................................................................................21

3.2 Demodulation .....................................................................................................................22

Chapter 4 Dedicated Digital Signal Processor (DSP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

4.1 Back-end Processing .........................................................................................................24

4.2 Audio Processing ...............................................................................................................25

4.3 ST WideSurround ...............................................................................................................28

4.4 ST OmniSurround ..............................................................................................................28

4.5 Dolby Pro Logic II Decoder ................................................................................................28

4.6 Bass Management .............................................................................................................28

4.6.1 Bass Management Configuration 0 .........................................................................................................29

4.6.2 Bass Management Configuration 1 .........................................................................................................30

4.6.3 Bass Management Configuration 2 .........................................................................................................31

4.6.4 Bass Management Configuration 3 .........................................................................................................32

4.6.5 Bass Management Configuration 4 .........................................................................................................33

4.7 SRS WOW and TruSurround XT ......................................................................................33

4.7.1 SRS TruSurround ....................................................................................................................................33

4.7.2 SRS WOW ...............................................................................................................................................34

4.8 Smart Volume Control (SVC) .............................................................................................34

4.9 ST Dynamic Bass ..............................................................................................................35

4.10 5-Band Audio Equalizer .....................................................................................................35

4.11 Bass/Treble Control ...........................................................................................................35

4.12 Automatic Loudness Control ..............................................................................................36

4.13 Volume/Balance Control ....................................................................................................36

4.14 Soft Mute Control ...............................................................................................................37

3/149

STV82x7

4.15 Beeper ................................................................................................................................37

Chapter 5 Analog Audio Matrix (In / Out) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

Chapter 6 I²S Interface (In / Out) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

6.1 I²S Inputs ............................................................................................................................40

6.2 I²S Output ...........................................................................................................................41

Chapter 7 S/PDIF Input/Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .42

Chapter 8 Power Supply Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .43

8.1 Standby Mode (Loop-through mode) .................................................................................43

Chapter 9 Additional Controls and Flag . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

9.1 Headphone Detection ........................................................................................................44

9.2 IRQ Generation ..................................................................................................................44

9.3 I²C Bus Expander ...............................................................................................................44

Chapter 10 STV82x7 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

Chapter 11 I²C Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

11.1 I²C Address and Protocol ...................................................................................................46

11.2 Start-up and Configuration Change Procedure ..................................................................47

Chapter 12 Register List . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

12.1 I²C Register Map ................................................................................................................49

12.2 STV82x7 General Control Registers ..................................................................................55

12.3 Clocking 1 ..........................................................................................................................56

12.4 Demodulator .......................................................................................................................59

12.5 Demodulator Channel 1 .....................................................................................................62

12.6 Demodulator Channel 2 .....................................................................................................66

12.7 NICAM Registers ...............................................................................................................71

12.8 Stereo Mode .......................................................................................................................73

12.9 Analog Control ...................................................................................................................74

12.10 Clocking 2 ..........................................................................................................................76

12.11 DSP Control .......................................................................................................................77

4/149

STV82x7

12.12 Automatic Standard Recognition ........................................................................................81

12.13 Audio Preprocessing and Selection Registers ...................................................................85

12.14 Matrixing .............................................................................................................................93

12.15 Audio Processing ...............................................................................................................98

12.16 5-Band Equalizer / Bass-Treble for Loudspeakers ..........................................................112

12.17 Headphone Bass-Treble ..................................................................................................113

12.18 Volume .............................................................................................................................116

12.19 Beeper ..............................................................................................................................126

12.20 Mute .................................................................................................................................127

12.21 S/PDIF ..............................................................................................................................128

12.22 Headphone Configuration ................................................................................................128

12.23 DAC Control .....................................................................................................................129

12.24 AutoStandard Coefficients Settings .................................................................................130

Chapter 13 Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .132

13.1 Absolute Maximum Ratings ............................................................................................132

13.2 Thermal Data ..................................................................................................................132

13.3 Power Supply Data ..........................................................................................................132

13.4 Crystal Oscillator .............................................................................................................133

13.5 Analog Sound IF Signal ..................................................................................................133

13.6 SIF to I²S Output Path Characteristics .............................................................................134

13.7 SCART to SCART Analog Path Characteristics ..............................................................134

13.8 SCART and MONO IN to I²S Path Characteristics ..........................................................135

13.9 I2S to LS/HP/SUB/C Path Characteristics .......................................................................135

13.10 I²S to SCART Path Characteristics ..................................................................................136

13.11 MUTE Characteristics ......................................................................................................136

13.12 Digital I/Os Characteristics ...............................................................................................136

13.13 I²C Bus Characteristics ..................................................................................................137

13.14 I2S Bus Interface ..............................................................................................................138

Chapter 14 Input/Output Groups . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .140

Chapter 15 Package Mechanical Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .145

Chapter 16 Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .146

5/149

General Description STV82x7

1 General Description

The STV82x7 is a multistandard TV sound demodulator and audio processor which integrates

SRS® WOW™, SRS® TruSurround XT™, Dolby® Pro Logic®, Dolby® Pro Logic II®,Virtual

Dolby® Surround (VDS) and Virtual Dolby® Digital (VDD) capability.

ST advanced algorithms such as ST OmniSurround, ST WideSurround, ST Dynamic Bass are

also available in this audio sound processor. ST OmniSurround is a certified Dolby® algorithm for

the Virtual Dolby® Digital (VDD) and the Virtual Dolby® Surround (VDS). When using VDD or

VDS, either a Dolby® Digital or a Pro Logic® (or Pro Logic II®) decoder is mandatory

respectively.

This chip performs automatic multistandard analog TV stereo sound identification and

demodulation (no specific I²C programming is required). It offers various audio processing

functions such as equalization, loudness, beeper, volume, balance, and surround effects. It provides

a cost-effective solution for analog and digital TV designs.

The STV82x7 is perfectly suited to current and future digital TV platforms, based on audio/video

digital chips (STD2000, (DTV100 platform) and the future WorldWide iDTV one chip) which

include an internal digital decoder (MPEG, Dolby® Digital...). In the case where a Dolby® Digital

decoder is embedded in the audio/video digital chip, Virtual Dolby® Digital could be obtained.

For the CTV100/120 platform, the device is offered as an alternative solution to the first-generation

chassis that uses the STV82x6.

6/149

STV82x7 General Description

®

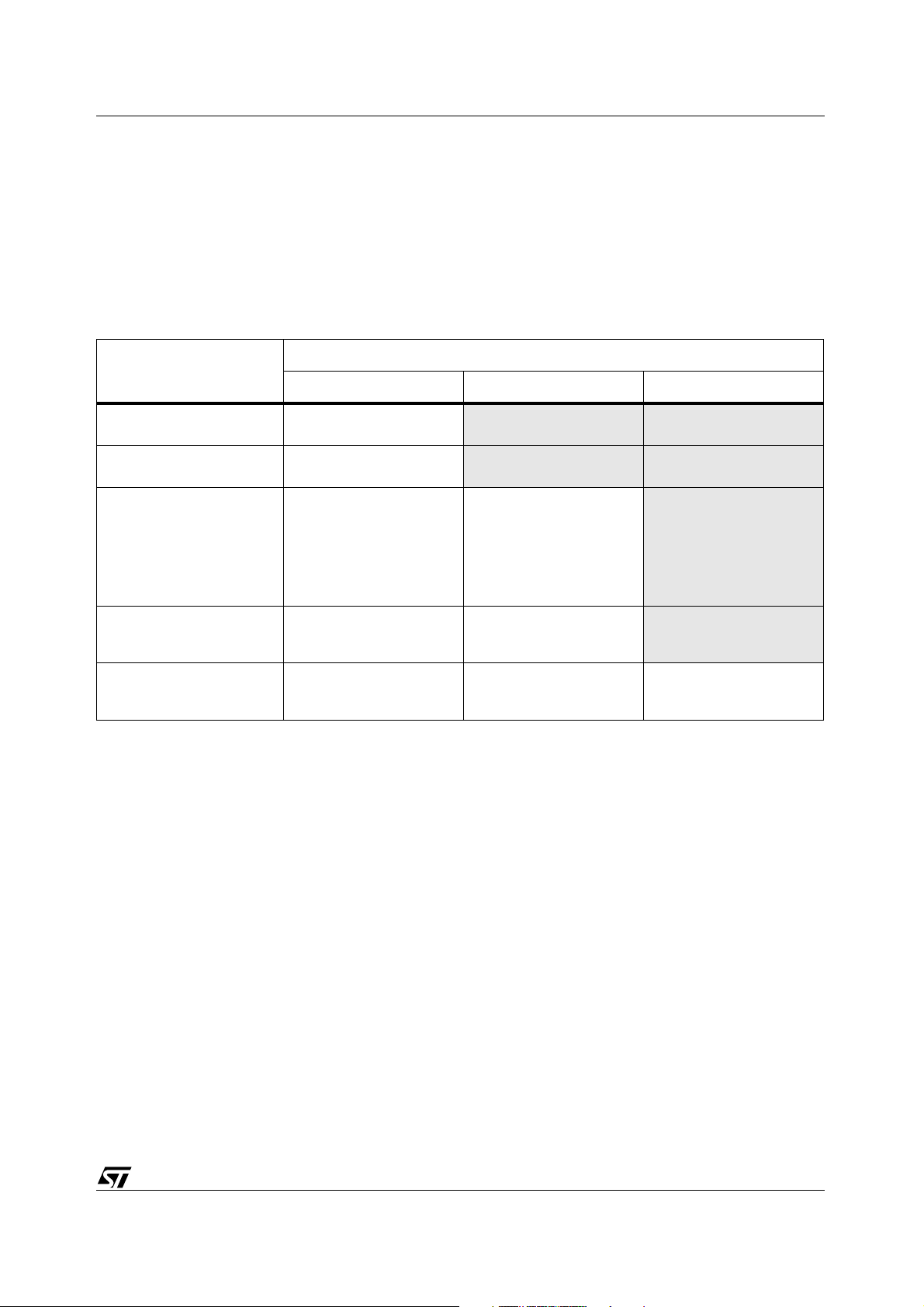

Table 1: STV82x7 Version List

STV8247 STV8257 STV8267 STV8277 STV8287

Demodulation

AM/FM - Mono, FM 2-carrier

NICAM

Multi-Channel Capability

3 x I²S In or 1 I²S Out,

S/PDIF (Pass-thru)

5.1 Analog Out for Loudspeakers

Virtual Dolby® Surround

Virtual Dolby® Digital capability

Dolby® Pro Logic®

Dolby® Pro Logic II®

Audio Processing

SRS® WOW™

SRS® TruSurround XT™

ST Voice, ST Dynamic Bass,

ST WideSurround

ST OmniSurround

2

S

T

T

V

V

8

8

2

2

1

0

7

7

T

T

V

V

8

8

2

2

3

2

7

7

S

S

S

S

T

S

T

V

8

2

4

7

D

S

V

T

8

V

2

8

4

2

7

5

D

7

S

X

S

S

T

T

V

V

8

8

2

2

5

5

7

7

D

D

S

X

S

T

S

T

V

8

2

6

7

D

S

V

T

8

V

2

8

6

2

7

7

D

7

S

X

S

T

S

V

T

8

V

2

8

7

2

7

7

D

7

S

D

X

XXXXXXXXXXXXXXXX

X XXXXXXXXXXXXX

XXX XXXXX

XXXXXXX

XX XXXX XXXX

1

XXX XXXXX

XX XX

XX

XXXXX

XXXXXXXXXXXXXXXX

XXXXXXXXXXXX

S

T

S

V

T

8

V

2

8

8

2

7

8

D

7

S

D

X

XX

1. Virtual Dolby Digital capability is obtained with the use of external Dolby Digital decoder (for

example STD05x0).

2. When using VDD or VDS with ST OmniSurround or SRS TruSurround XTTM, either a Dolby®

Digital or a Pro Logic® (or Pro Logic II®) decoder is mandatory respectively.

Figure 1: Package Ordering Information

Order Code:

STV82x7 (Tray)

STV82x7/T (Tape & Reel)

0

8

P

F

Q

T

For Example: STV8257DSX/T will be delivered in Tape & Reel conditioning

7/149

General Description STV82x7

1.1 STV82x7 Overview

1.1.1 Core Features

● Single audio source processing:

— IF source and/or analog stereo input (SCART)

— one digital source with a maximum of 6 synchronous channels (5.1 is obtained across three

I²S)

● SIF input signal with Automatic Gain Control (AGC)

● Digital Demodulator with automatic standard detection and demodulation for AM, FM mono,

FM 2 carriers (German or Korean FM 2-carrier) and NICAM

● Audio processor working at 32 kHz, 44.1 kHz or 48 kHz with specific features:

— For Loudspeakers (L, R, L

Dolby® Pro Logic II ® Decoder with Bass Management

SRS® WOW™ or TruSurround XT™ including Virtual Dolby® Surround and Virtual Dolby®

Digital

ST WideSurround

ST OmniSurround

ST Dynamic Bass

5-band Equalizer or Bass-Treble

Loudness

Smart Volume Control

Volume/Balance/Soft-mute

Beeper

Video Processing Delay Compensation

— For Headphone:

SRS® Tr u B a s s ™

Smart Volume Control

Bass-Treble

Loudness

Volume/Balance/Soft-mute

Beeper

Video Processing Delay Compensation

● Shared outputs for headphone and loudspeakers (surround channels);

● Analog matrix with:

— five external inputs:

four SCART inputs (2 V

one analog mono input (0.5 V

— one internal input from a digital matrix via a DAC

— three external outputs (2 V

— one internal output for the digital matrix (using an internal ADC)

● Digital matrix with:

— three input modes (Demodulator/SCART, SCART only and I²S)

— three stereo outputs (Loudspeakers, Headphone and SCART)

● High-end audio DAC

● S/PDIF output for connection with an external amplifier/decoder

● Internal multiplexer for the S/PDIF output (to share the internal S/PDIF output and the S/PDIF

output generated by the external decoder of the digital broadcast)

, RS, SubW, C):

S

capable)

RMS

RMS

capable)

RMS

)

8/149

STV82x7 General Description

● Specific stand-by mode (Loop-through)

● Control by I²C bus (two I²C addresses)

● System PLL and Clock Generation using either a single quartz oscillator or a differential clock

input

1.1.2 Software Information

The different software combinations are listed in Tab l e 2 .

Table 2: Input/Output Software Configurations

Output (Number of Channels)

Input (Number of Channels)

2 (+1) 4 (+1) 5 (+1)

1

2 (L and R)

2 (LT and RT)

4 (+1)

5 (+1)

ST WideSurround or

SRS® WOW™

ST WideSurround or

SRS® WOW™

ST WideSurround or

SRS® TruSurround XT™ or

ST OmniSurround or

Dolby® Pro Logic® + SRS®

TruSurround XT™ or

Dolby® Pro Logic® + ST

OmniSurround

SRS® TruSurround XT™ or

ST OmniSurround or

Downmix

SRS® TruSurround XT™or

ST OmniSurround or

Downmix

Dolby® Pro Logic®

No processing

Downmix No processing

Note: In addition to the above sound processing, it is always possible to add ST Voice and also ST

Dynamic Bass algorithms.

Note: The SRS® TruSurround® and ST OmniSurround are approved by Dolby as Virtual Dolby Surround

(VDS) and Virtual Dolby Digital (VDD).

The SRS® TruSurround XT™ system is composed of:

● SRS® TruSurround®

● SRS® WOW™

The SRS® WOW™ system also includes:

● SRS® Dialog Clarity™

● SRS® TruBass™

1.1.3 Device Input Modes

● Demodulator and SCART Mode (with output f

● SCART Only Mode (with output f

● I²S Mode (with output f

= 48 kHz)

S

= 32, 44.1 or 48 kHz)

S

9/149

= 32 kHz)

S

General Description STV82x7

— External audio input interface using 3 x I²S (for decoded streams such as Dolby® Digital

and/or standard stereo streams)

1.1.4 Electrical Features

Multi Power Supply: 1.8 V, 3.3 V and 8 V.

Power Consumption:

● lower than 1 W in Functional mode (full features)

● 200 mW in Loop-through mode corresponding to Switch-off of all digital blocks

1.2 Typical Applications

The STV82x7 is specified to enable flexible, analog and digital TV chassis design (refer to Figure 2,

Figure 3, Figure 4 and Figure 5).

The main considerations are:

● all necessary connections between devices can be provided through the TV set,

● pseudo stand-by mode used to copy to VCR or the DVD sources when the TV set is OFF,

● possible application compatibility with STV82x6 (TQFP80 package) TV design,

● pin-to-pin compatibility with STV82x8 (TQFP80 package) TV design.

The STV82x7 is used to process a single audio source (analog or digital). However, it is possible to

process two audio sources simultaneously using an STV82x7 interconnection (two chips can be

easily connected).

In the case of a single audio source, it is possible to hear and record in the same time: the same

audio stream can be simultaneously output on headphone, loudspeakers, S/PDIF and the SCART

connectors.

Note: Headphone and loudspeakers can be used simultaneously for dual-language purposes or for

different sound settings (e.g. volume). In this case, certain restrictions occur (see Section 4.2: Audio

Processing).

For more connections, the SCART-to-SCART path can be used. The use of these full analog paths

implies that the sound is not digitally processed.

10/149

STV82x7 General Description

Figure 2: STV8237 Typical Application (Enhanced Stereo)

or

Tu ne r

STV8237

Multistandard Demodulation

- FM 2-carrier and NICAM

Sound Processing

- Volume, Balance, 5-Band Equalizer

- ST WideSurround

- SRS® WOW™

Left Right

Figure 3: STV8247 Typical Application (Analog Virtual Sound)

R

SubW

L

Tu ne r

STV8247

Multistandard Demodulation

or

Left Right

1. When using VDS with ST OmniSurround or SRS TruSurround XTTM, a Pro Logic® decoder is mandatory.

- FM 2-carrier and NICAM

Sound Processing

- Volume, Balance, 5-Band Equalizer

- SRS® TruSurround XT™

- ST OmniSurround

- Virtual Dolby® Surround

1

R

SubW

L

11/149

General Description STV82x7

Figure 4: STV8257 Typical Application (Digital: Virtual Sound)

Multi-Channel Digital Decoder

or

(Dolby® Digital)

I²S

Tuner

Left Right

S/PDIF Pass-thru

STV8257

Multistandard Demodulation

- FM 2-carrier and NICAM

Audio Processing

- Volume, Balance, 5-Band Equalizer

- SRS® TruSurround XT™

- ST OmniSurround

- Virtual Dolby® Surround

- Virtual Dolby® Digital2

1

SubW

R

L

1. When using VDS with ST OmniSurround or SRS TruSurround XTTM, a Pro Logic® decoder is mandatory.

2. When using VDD with ST OmniSurround or SRS TruSurround XTTM, a Dolby® Digital decoder is mandatory.

Figure 5: STV8277 Typical Application (Digital TV: Multi-Channel and Virtual Sound)

Multi-Channel Digital Decoder

or

(Dolby® Digital)

I²S

Tuner

S/PDIF Pass-thru

STV8277

Multistandard Demodulation

- FM 2-carrier and NICAM

Audio Processing

SubW

R

RS

C

LS

L

- Volume, Balance, 5-Band Equalizer

- Dolby® Pro Logic II®

- 5.1 Analog Outputs

- SRS® TruSurround XT™

- Virtual Dolby® Surround

- Virtual Dolby® Digital

1

2

Left Right

1. When using VDS with ST OmniSurround or SRS TruSurround XTTM, a Pro Logic® decoder is mandatory.

2. When using VDD with ST OmniSurround or SRS TruSurround XT

12/149

TM

, a Dolby® Digital decoder is mandatory.

STV82x7 General Description

Figure 6: STV8217 Typical Application (Digital Recorder)

MPEG Codec

or

Tuner

I²S

STV8217

Multistandard Demodulation

- FM 2-carrier and NICAM

Left Right

13/149

General Description STV82x7

1.3 Pin Descriptions and Application Diagrams

● AP = Analog Power

● DP = Digital Power

● I= Input

● O = Output

● OD = Open-Drain

● B = Bi-Directional

● A = Analog

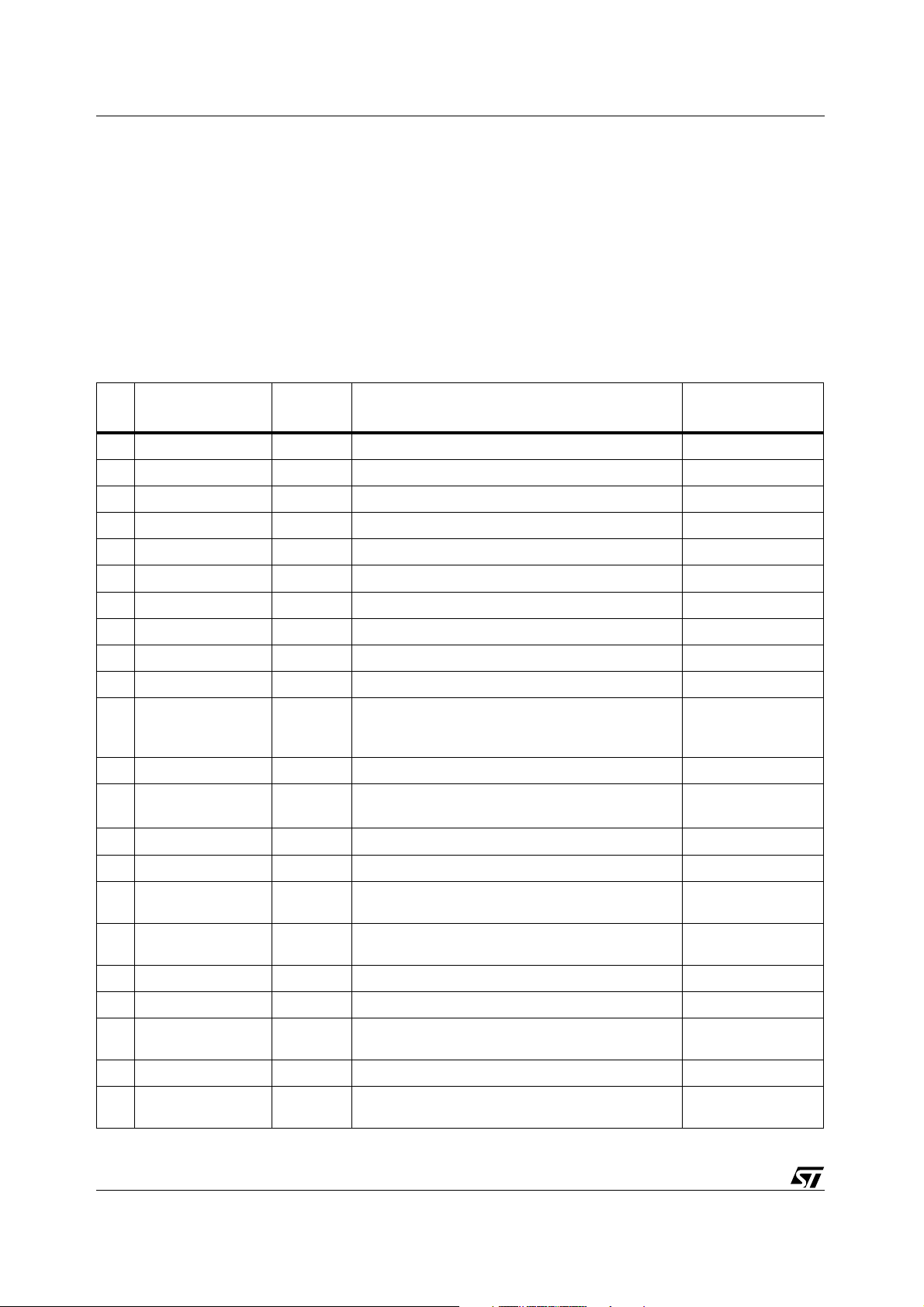

Table 3: TQFP80 Pin Description (Sheet 1 of 3)

Pin

No.

1 SC1_OUT_L A SCART1 Audio Output Left AO1L

2 SC1_OUT_R A SCART1 Audio Output Right AO1R

3 VCC_H AP 8V Power for Audio I/O & ESD Not connected

4 GND_H AP High Current Ground for Audio Outputs Connected to Ground

5 SC3_OUT_L A SCART3 Audio Output Left Not connected

6 SC3_OUT_R A SCART3 Audio Output Right Not connected

7 VCC33_SC AP 3.3V Power for Audio Buffers & DAC / ADC VDDC

8 GND33_SC AP Ground for Audio Buffers & DAC / ADC GNDC

9 SC1_IN_L A SCART1 Audio Input Left AI1L

10 SC1_IN_R A SCART1 Audio Input Right AI1R

11 VREFA A

12 GND_SA AP Ground for DACs Connected to Ground

13 VBG A

14 SC2_IN_L A SCART2 Audio Input Left AI2L

STV82x7

Pin Name

Typ e

(STV82x7)

Function for STV82x7

(Function for STV82x6 in italic characters)

Audio Bias Voltage Decoupling 1.55V

(Switched V

(VMCP))

Bandgap Voltage Reference Decoupling 1.2V

(V

decoupling pin for Audio Converters (VMC))

REF

decoupling pin for Audio Converters

REF

STV82x6

Pin Name

VMC1

VMC2

15 SC2_IN_R A SCART2 Audio Input Right AI2R

16 VCC33_LS AP

17 GND33_LS AP

18 SC2_OUT_L A SCART2 Audio Output Left AO2L

19 SC2_OUT_R A SCART2 Audio Output Right AO2R

20 VCC_NISO AP

21 VSS33_CONV AP Ground for DAC 1.8 to 3.3V Converters Connected to Ground

22 VDD33_CONV AP

3.3V Power for Audio DACs

(3.3V Power Supply for Audio Buffers and SCART)

Ground for Audio DACs

(Ground for Audio Buffers and SCART)

Polarization of the NISO (connected to 3.3V)

(8V / 5V Power supply for SCART & Audio buffers)

3.3V Power for DAC 1.8 to 3.3V Converters

(Voltage Reference for Audio buffers)

VDDA

GNDAH

VDDH

VREFA

14/149

STV82x7 General Description

Table 3: TQFP80 Pin Description (Sheet 2 of 3)

Pin

No.

23 SC3_IN_L A SCART3 Audio Input Left AI3L

24 SC3_IN_R A SCART3 Audio Input Right AI3R

25 SCL_FLT A SCART Filtering Left Not connected

26 SCR_FLT A

27 LS_C A Center Output Not connected

28 LS_L A Left Loudspeaker Output LSL

29 LS_R A Right Loudspeaker Output LSR

30 LS_SUB A Subwoofer Output SW

31 HP_LSS_L A Left Headphone Output or Left Surround Output HPL

32 HP_LSS_R A Right Headphone Output or Right Surround Output HPR

33 VSS18_CONV DP

34 VDD18_CONV DP 1.8V Power for Digital part of the DAC/ADC Not connected

35 HP_DET

36 ADR_SEL I Hardware Address selection for I²C Bus ADR

37 VSS18 DP Ground for Digital part Connected to Ground

STV82x7

Pin Name

Typ e

(STV82x7)

I Headphone Detection HPD

(Function for STV82x6 in italic characters)

SCART Filtering Right

(Bandgap Voltage Source Decoupling)

Ground for Digital part of the DAC/ADC

(Substrate Analog/Digital Shield)

Function for STV82x7

STV82x6

Pin Name

BGAP

GNDSA

38 VDD18 DP 1.8V Power for Digital part Not connected

39 SCL OD I²C Clock Input SCL

40 SDA OD I²C Data I/O SDA

41 VSS18 DP Ground for Digital part Connected to Ground

42 VDD18 DP

43 RST

44 S/PDIF_IN I

45 S/PDIF_OUT O

46 VDD33_IO1 DP 3.3V Power for Digital part VDD1

47 VSS33_IO1 DP Ground for Digital part GND1

48 CK_TST_CTRL D To be Grounded Not connected

49 VSS18 DP Ground for Digital part GNDSP

50 VDD18 DP 1.8V Power for Digital part Not connected

51 CLK_SEL I Clock Input Format Selection Not connected

52 XTALIN_CLKXTP I

I Main Reset Input RESET

1.8V Power for Digital part

(5V Power Regulator Control)

Serial Audio Data Input

(System Clock output)

Serial Audio Data Output

(I²S Master Clock output)

Crystal Oscillator Input or Differential Input Positive

(Crystal Oscillator Input)

REG

SYSCK

MCK

XTI

15/149

General Description STV82x7

Table 3: TQFP80 Pin Description (Sheet 3 of 3)

Pin

No.

53 XTALOUT_CLKXTM O

54 VCC18_CLK1 AP

55 GND18_CLK1 AP Ground for Clock PLL Analog & Crystal Oscillator 1/2 GNDP

56 GND18_CLK2 AP Ground for Clock PLL Digital 1/2 GND2

57 VCC18_CLK2 DP

58 VSS33_IO2 DP Ground for Digital IO pins 60 to 69 Connected to Ground

59 VDD33_IO2 DP 3.3V power for Digital IO pins 60 to 69 Not connected

60 I2S_PCM_CLK I/O I²S Slave Clock Input/Output Channel 1, 2 & 3 Not connected

61 I2S_SCLK I/O

62 I2S_LR_CLK I/O

63 I2S_DATA0 I/O

64 I2S_DATA1 I

STV82x7

Pin Name

Typ e

(STV82x7)

Function for STV82x7

(Function for STV82x6 in italic characters)

Crystal Oscillator Output or Differential Input Negative

(Crystal Oscillator Output)

1.8V Power for Clock PLL Analog & Crystal Oscillator 1/2

(3.3V Power supply for Analog PLL Clock)

1.8V Power for Clock PLL Digital 1/2

(3.3V Power supply for Digital core, DSPs & IO Cells)

I²S Clock Input/Output Channel 1, 2 & 3 (I²S bus data

output)

I²S Word Select Input/Output Channel 1,2 & 3

(Stereo Detection output / I²S Bus Data input)

I²S Data Input/Output Stereo Channel 1

(I²S Bus Word Select output)

I²S Data Input Stereo Channel 2

(I²S Bus Clock output)

STV82x6

Pin Name

XTO

VDDP

VDD2

SDO

ST/SDI

WS

SCK

65 I2S_DATA2 I

66 VDD18 DP 1.8V Power for Digital Core & I/O Cells Pin Not connected

67 VSS18 DP Ground for Digital Core & I/O Cells Pin Connected to Ground

68 BUS_EXP O

69 IRQ O Interrupt Request to Microprocessor IRQ

70 GND_PSUB AP Ground Substrate Connection Connected to Ground

71 VDD18_ADC DP VDD 1.8V for ADC (Digital Part) Not connected

72 VSS18_ADC DP Ground to Complement 1.8V VDD for ADC Connected to Ground

73 SIF_P A Sound IF input (positive) SIF

74 SIF_N A

75 GNDPW_IF AP

76 VCC18_IF AP 1.8V Power for IF AGC & ADC VDDIF

77 GND18_IF AP Ground for IF AGC & ADC GNDIF

78 MONO_IN A Mono Input (for AM Mono) MONOIN

79 SC4_IN_L A SCART4 Audio Input Left Not connected

80 SC4_IN_R A SCART4 Audio Input Right Not connected

I²S Data Input Stereo Channel 3

(Bus Expander Output 1)

Bus Expander Function

(Bus Expander Output 2)

Sound IF input (negative) (ADC V

Polarization for the IF block

(Voltage Reference for AGC Decoupling pin)

Decoupling pin)

TOP

BUS1

BUS0

VTOP

VREFIF

16/149

STV82x7 General Description

Figure 7: STV82x7 Application Diagram

SC3 IN Right

SC2 OUT Right

SC3 IN Left

C61

C60

1µF

1µF

+

+

C59

+

C64

33nF

1µF

C3

+

C65

33nF

1µF

C4

+

C66

33nF

1µF

C5

+

C67

33nF

1µF

L16

C6

+

L17

100µH

L18

1µF

C68

33nF

C7

+

1µF

C69

33nF

C8

+

C9

330µF

+

100µH

100µH

C10

C63

33nF

C62

33nF

L13

100µH

L14

100µH

L15

100µH

100nF

SL1

Address select

123

1

3

C12

100nF

+3.3V

C14

C13

100nF

SC2 OUT Left

+

+

10µF

C56

C55

10µF

330pF

C75

+3.3V

L1

10µH

220

R9

R8

47µF

C58

100nF

100nF

21

22

23

24

SCL_FLT

25

26

LS_C

27

LS_L

28

LS_R

29

LS_SUB

30

31

32

33

34

HP_DET

35

36

VSS18

37

VDD18

38

SCL

39

SDA

40

C15

100nF

SC2 IN Right

+

+

1µF

C53

C54

330pF

C74

220

C57

20

VCC_NISO

VSS33_CONV

SC2_OUT_R

VDD33_CONV

SC3_IN_L

SC3_IN_R

SCR_FLT

HP_LSS_L

HL_LSS_R

VSS18_CONV

VDD18_CONV

ADR_SEL

VSS18

VDD18

41424344454647484950515253545556575859

SC2 IN Left

1µF

100nF

SC2_OUT_L

RST_N

C50

C52 100nF

VCC33_LS

GND33_LS

SPDIF_IN

SPDIF_OUT

100nF

C51

10µF

+

VBG

SC2_IN_L

SC2_IN_R

IC1

STV82x7

VDD33_IO

VSS33_IO

CK_TST_CTRL

C19

100nF

C18

100nF

C49

GND_SA

VSS18

+

+

C46

VREFA

SC1_IN_R

TQFP80

VDD18

CLK_SEL

10µF

1µF

SC1_IN_L

XTALIN/CLKXTP

SC1 IN Right

+

1µF

C45

220

R7

VCC33_SC

GND33_SC

XTALOUT/CLKXTM

VCC18_CLK1

C25

SC1 IN Left

SC3 OUT Right

+

C47

C44

100nF

330pF

C73

C72

220

R6

GND_H

SC3_OUT_L

SC3_OUT_R

GND18_CLK1

GND18_CLK2

VCC18_CLK2

100nF

C48

+

10µF

330pF

C41

C42

VCC_H

VSS33_IO

SC3 OUT Left

10µF

10µH

10µF

+

100nF

12345678910111213141516171819

SC1_OUT_L

SC1_OUT_R

VDD33_IO

I2S_PCM_CLK

60

C26

100nF

I2S SCLK

I2S LR CLK

SC1 OUT Left

SC1 OUT Right

SC4 IN Right

SC4 IN Left

Mono IN

C38

+

1µF

+

1µF

C37

+

+

10µF

+

C39

C36 1µF

10µF

C40

+8V

330pF

C71

L12

330pF

220

220

R4 C70

R5

C43

+

SC4_IN_R

80

SC4_IN_L

C33

79

MONO_IN

78

GND18_IF

77

VCC18_IF

76

GND_PWIF

220nF

C32

75

SIF_N

74

SIF_P

73

VSS18_ADC

72

VDD18_ADC

71

GND_PSUB

70

IRQ

69

BUS_EXP

68

VSS18

67

VDD18

66

I2S_DATA2

65

I2S_DATA1

64

I2S_DATA0

63

I2S_LR_CLK

62

I2S_SCLK

61

C27

100nF

I2S DATA 2

IRQ

SIF

BUS EXPANDER

100pF

C35

L11

560

R3

+1.8V

C34

22nF

L10

10µH

47µF

100nF

C30

C29

100nF

10µH

100nF

I2S DATA 0

I2S DATA 1

I2S PCM CLK

L2

10µH

Reset

C16

470nF

470K

R1

+1.8V

HP Right/LS surround Right

LS Right

Subwoofer

LS Left

LS Center

HP Left/LS surround Left

Headphone detection

+3.3V

SCL

SDA

SPDIF IN

10µF

C17

+

L4

10µH

+3.3V

SPDIF OUT

XT1

27MHz

CRYSTAL

C22

27pF

C21

27pF

+1.8V

1.8V

1.8V

47µF

C23

+

L6

10µH

1.8V

17/149

General Description STV82x7

Figure 8: STV82x6/STV82x7 Compatible Application Electrical Diagram

SC2 IN Right

10µH

10µH

Not Connected

Not Connected

with STV82x7

10µH

10µH

Not Connected

Not Connected

with STV82x6

Part

L4

L2

L1

10µH

10µH

100µH *L13,L14

100µH *

100µH *

strap

strap

strap

Not Connected

Not Connected

L5,L6

L8

L17,L18

L15,L16

0 ohm

Not Connected

270K

Not Connected

R2

R11

R10 330 Not Connected

R12 82 Not Connected

R13 Not Connected 0 ohm

Not Connected0 ohm

0 ohm

0 ohm Not Connected

Not Connected 0 ohmR16

Not Connected 0 ohmR17

R14 Not Connected

R15

R18

Not Connected 0 ohm

R19

SC3 IN Left

SC3 IN Right

100 nF

10 µF

Not Connected

Not Connected

C63 100 nF 33 nF

C41 10 µF Not Connected

C42

C43

C59 10 µF 47 µF

1µF

C3

+

1µF

C4

+

1µF

C5

+

1µF

C6

+

L17

1µF

C7

+

1µF

C8

+

330 pFNot ConnectedC72,C73

between 1-2L3between 1-2

between 2-3

between 2-3

Not Connected 33 nFC68,C69

SL2

C66,C67 Not Connected 33 nF

C64

C65

C66

C67

100µH

C68

C69

10µH

33nF

33nF

33nF

33nF

33nF

33nF

C9

+

C70,C71 Not Connected 330 pF

L18

330µF

C74,C75 Not Connected 330 pF

C76,C77 10 µF Not Connected

C78 10 µF Not Connected

*

L16

100µH

*

100µH

C10

C79 10 µF 47 µF

L15

100nF

SL3

*

L14

*

100µH

1

C64,C65 Not Connected 33 nF

*

L8

*

L13

100µH

100µH

SL1

123

C12

100nF

+3.3V

10µF

C78

+

C63

C62

33nF

C13

Address select

3

C61

C60

1µF

1µF

+

+

+3.3V

L1

10µH

C59

47µF

+

0

+8V

L2

10µH

C14

100nF

100nF

100 nF

100 nF

100 nF Not Connected

Not ConnectedC15,C18 100 nF

Not Connected

Not Connected

C3 Not Connected 1 µF

C9 Not Connected 330 µF

C10,C13 Not Connected 100 nF

C21,C22 22 pF 27 pF

C23 Not Connected 47 µF

C27,C29

C30

C31

SC2 IN Left

SC2 OUT Left

SC2 OUT Right

+

+

+

1µF

+

10µF

C53

C54

C56

C55

10µF

+8V

R10

330pF

C75

C74

330pF

220

220

R9

R8

C76

10µF

+

R19

R13

C57

C77

10µF

+

C58

100nF

20

VCC_NISO

SC2_OUT_L

SC2_OUT_R

VSS33_CONV

21

VDD33_CONV

22

SC3_IN_L

23

SC3_IN_R

24

SCL_FLT

25

SCR_FLT

26

LS_C

27

LS_L

28

LS_R

29

LS_SUB

30

HP_LSS_L

31

HL_LSS_R

32

VSS18_CONV

33

VDD18_CONV

34

HP_DET

35

ADR_SEL

36

VSS18

37

VDD18

38

SCL

39

SDA

40

VSS18

VDD18

RST_N

41424344454647484950515253545556575859

C15

100nF

0

R14

C50

C52 100nF

1µF

0

0

100nF

VCC33_LS

GND33_LS

SPDIF_IN

SPDIF_OUT

100nF

C49

C51

10µF

+

330

R11

VBG

GND_SA

SC2_IN_L

SC2_IN_R

IC1

STV82x6 / STV82x7

VDD33_IO

VSS33_IO

CK_TST_CTRL

VSS18

C19

100nF

C18

100nF

+

+

C46

VREFA

TQFP80

VDD18

10µF

1µF

+

C45

SC1_IN_L

SC1_IN_R

CLK_SEL

XTAL I N / C L K XTP

SC1 OUT Right

SC1 IN Right

C48

+

+

10µF

C47

1µF

+8V

R12

82

C41

10µF

+

C44

100nF

330pF

C73

C72

220

330pF

R7

C43

220

R6

C42

VCC_H

GND_H

VCC33_SC

GND33_SC

SC3_OUT_L

SC3_OUT_R

XTALOUT/CLKXTM

VCC18_CLK1

GND18_CLK1

GND18_CLK2

VCC18_CLK2

VSS33_IO

C25

100nF

SC4 IN Left

SC1 OUT Left

C38

+

1µF

10µF

+

C37

+

10µF

+

C39

10µF

C40

+8V

330pF

10µH

C71

L3

330pF

10µF

+

220

220

R4 C70

R5

100nF

12345678910111213141516171819

SC1_OUT_L

SC1_OUT_R

SC4_IN_R

80

SC4_IN_L

79

MONO_I N

78

GND18_IF

77

VCC18_IF

76

GND_PWIF

75

SIF_N

74

SIF_P

73

VSS18_ADC

72

VDD18_ADC

71

GND_PSUB

70

IRQ

69

BUS_EXP

68

VSS18

67

VDD18

66

I2S_DATA2

65

I2S_DATA1

64

I2S_DATA0

63

I2S_LR_CLK

62

I2S_SCLK

61

VDD33_IO

I2S_PCM_CLK

60

C27

100nF

C26

100nF

0

R15

SC4 IN Right

SC3 OUT Right

SC1 IN Left

SC3 OUT Left

SIF

Mono IN

1µF

+

R16

IRQ

BUS EXPANDER / BUS0

C36 1µF

100pF

+1.8V

+3.3VL6

C35

L5

L4

10µH

10µH

C34

22nF

C79

47µF

+

100nF

C33

C32

220nF

0

I2S SCLK / SDO

I2S DATA 1 / SCK

I2S DATA 2 / BUS1

10µH

L11

560

R3

0

R17

C31

100nF

C30

100nF

C29

100nF

I2S PCM CLK

I2S DATA 0 / WS

I2S LR CLK / SDI

Reset

C16

470K

R1

+1.8V

LS Left

Subwoofer

LS Center

HP Left/LS surround Left

HP Right/LS s urround Right

LS Right

Headphone detection

+3.3V

SCL

SDA

18/149

0

470nF

R18

10µF

C17

+

L7

10µH

+3.3V

SPDIF IN

SPDIF OUT

+1.8V

C21

SL2

123

+1.8V

XT1

R2

27MHz

CRYSTAL

270k

SL3

123

+1.8V

47µF

C23

+

C22

10µH

1.8V

Note : components with * are only mandatory in case of DOLBY certification

STV82x7 General Description

Figure 9: STV82x7/STV82x8 Compatible Application Electrical Diagram (TQFP80)

SIF

SC3 IN Right

C61

C61

1µF

1µF

C60

+

+

+

SC3 IN Left

1µF+C60

1µF

SC2 OUT Right

SC2 OUT Left

+

+

+

10µF

10µF

C56

C56

C55

SC1 IN Left

SC3 OUT Right

+

+

C47

C47

SC3 OUT Left

C48

C48

+

+

10µF

10µF

SC1 OUT Left

SC4 IN Right

SC4 IN Left

C38

C38

+

+

10µF

10µF

1µF

1µF

+

+

1µF

1µF

C37

C37

R12

10K

R12

10K

SC2 IN Right

SC2 IN Left

+

+

+

+

1µF

1µF

1µF

1µF

C54

C54

C53

C53

10µF+C55

10µF

SC1 IN Right

100nF

100nF

+

+

C50

C50

C49

C49

10µF

10µF

C51

10µF+C51

10µF

+

C52 100nFC52 100nF

+

+

1µF

1µF

+

+

C46

C46

1µF

1µF

C45

C45

Mono IN

SC1 OUT Right

IRQ

I2S DATA 2

I2S DATA 1

I2S DATA 0

I2S LR CLK

I2S SCLK

BUS EXPANDER

10K

10K

R11

R11

I2S PCM CLK

Table 1 : SL1 configuration

20 connected to 3.3V)

between 2 and 3 (pin

STV82x7 :

STV82x8 : between 1 and 2 (pin 20 connected to ground)

C64

33nF

C64

33nF

1µF

1µF

C3

C3

+

+

C65

33nF

C65

33nF

1µF

1µF

C4

C4

+

+

C66

33nF

C66

33nF

1µF

1µF

C5

C5

+

+

*

C67

33nF

C67

33nF

1µF

1µF

L16

100µH

L16

C6

C6

+

+

1µF

1µF

C7

C7

+

+

1µF

1µF

C8

C8

+

+

100µH

*

L17

100µH

L17

100µH

*

L18

L18

100µH

100µH

C68

33nF

C68

33nF

C10

C10

C69

33nF

C69

33nF

C9

C9

330µF

330µF

+

+

C63

33nF

C63

33nF

*

C62

33nF

C62

33nF

L13

L13

100µH

100µH

*

L14

L14

100µH

100µH

*

L15

L15

100µH

100µH

100nF

100nF

SL1SL1

123

1

+3.3V

C13

100nF

C13

100nF

Address select

3

C12

100nF

C12

100nF

330pF

C75C75

+3.3V

330pF

C74C74

L1

10µHL110µH

220

220

R9R9

R8R8

C59

47µF+C59

47µF

+

C57

100nF

C57

100nF

SL1 ( see Table 1)SL1 ( see Table 1)

1

3

2

C58

100nF

C58

100nF

16

19

17

20

18

C14

100nF

C14

100nF

VCC_NISO

VSS33_CONV

SC2_OUT_L

SC2_OUT_R

21

VDD33_CONV

22

SC3_IN_L

23

SC3_IN_R

24

SCL_FLT

25

SCR_FLT

26

LS_C

27

LS_L

28

LS_R

29

LS_SUB

30

HP_LSS_L

31

HL_LSS_R

32

VSS18_CONV

33

VDD18_CONV

34

HP_DET

35

ADR_SEL

36

VSS18

37

VDD18

38

SCL

39

SDA

40

VSS1841VDD1842RST_N43SPDIF_IN44SPDIF_OUT45VDD33_IO46VSS33_IO47CK_TST_CTRL48VSS1849VDD1850CLK_SEL51XTALIN/CLKXTP52XTALOUT/CLKXTM

C15

100nF

C15

100nF

15

SC2_IN_R

VCC33_LS

GND33_LS

14

13

SC2_IN_L

IC1IC1

C19

C19

C18

C18

VBG

STV82x7 or STV82x8

100nF

100nF

100nF

100nF

12

GND_SA

11

10

VREFA

SC1_IN_R

TQFP80

8

9

SC1_IN_L

53

7

GND33_SC

+

+

+

+

C39

C39

10µF

10µF

C44

100nF

C44

100nF

C40

C40

330pF

C73C73

+8V

10µH

10µH

220

C72C72

330pF

L12

L12

R7R7

220

C41

10µF+C41

10µF

+

220

R6R6

R5R5

C42

C42

100nF

100nF

2

6

3

1

5

4

VCC_H

GND_H

VCC33_SC

SC1_OUT_L

SC3_OUT_L

SC1_OUT_R

SC3_OUT_R

VCC18_CLK154GND18_CLK155GND18_CLK256VCC18_CLK257VSS33_IO58VDD33_IO59I2S_PCM_CLK

60

C27

C27

C25

C25

C26

C26

100nF

100nF

100nF

100nF

10µF

10µF

C70C70

C71C71

330pF

R4R4

SC4_IN_R

SC4_IN_L

MONO_IN

GND18_IF

VCC18_IF

GND_PWIF

SIF_N

SIF_P

VSS18_ADC

VDD18_ADC

GND_PSUB

IRQ

BUS_EXP

VSS18

VDD18

I2S_DATA2

I2S_DATA1

I2S_DATA0

I2S_LR_CLK

I2S_SCLK

100nF

100nF

330pF

220

+

C36 1µF+C36 1µF

100pF

100pF

C35

C35

10µH

10µH

L11

L11

560R3560

R3

+1.8V

C34

22nF

C34

22nF

L10

L10

10µH

10µH

C43

47µF+C43

47µF

+

100nF

100nF

80

C33

C33

79

78

77

76

220nF

220nF

C32

C32

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

C30

C30

100nF

100nF

C29

100nF

C29

100nF

LS Center

LS Left

LS Right

HP Left/LS surround Left

Subwoofer

HP Right/LS surround Right

L2

10µHL210µH

Reset

C16

470nF

C16

470nF

470KR1470K

R1

+1.8V

Headphone detection

+3.3V

SCL

SDA

SPDIF IN

L4

SPDIF OUT

10µF

10µF

C17

C17

+

+

10µHL410µH

+3.3V

XT1

27MHz

XT1

27MHz

CRYSTAL

C22

27pF

C22

27pF

C21

C21

27pF

27pF

+1.8V

1.8V

1.8V

47µF

47µF

C23

C23

+

+

L6

10µHL610µH

1.8V

Note : components with * are only mandatory in case of Dolby certification

19/149

System Clock STV82x7

2 System Clock

The System Clock integrates 2 independent frequency synthesizers.

The first frequency synthesizer can be used in one of two modes:

● In Mode 1, it is used by the demodulator, and the frequecy is 49.152 MHz.

● In Mode 2, it is used by the I²S input and is synchronous with the input frequency

or 48 kHz) and the frequency is 49.152 MHz (for f

= 32 or 48 KHz) or 45.1584 MHz (for fS =

S

44.1 KHz).

The second frequency synthesizer is used by the DSP core and can be adjusted between 100 and

150 MHz depending on the application (around 106 MHz at reset value).

The default values are designed for a standard 27-MHz reference frequency provided by a stable

single crystal or an external differential clock signal (for example, from the STV35x0) depending on

the CLK_SEL pin configuration (CLK_SEL = 1 means a single crystal, 0 means an external

differential clock). The 27-MHz value is the recommended frequency for minimizing potential RF

interference in the application. The sinusoidal clock frequency, and any harmonic products, remain

outside the TV picture and sound IFs (PIF/SIF) and Band-I RF.

Note: A change in the reference frequency is compatible with other default I²C programming values,

including those of the built-in Automatic Standard Recognition System.

= 32, 44.1

(fS

20/149

STV82x7 Digital Demodulator

3 Digital Demodulator

The Digital Demodulator (see Figure 10) is composed of two channels. The first channel

demodulates an FM or an AM signal. The second channel demodulates FM 2-carrier or NICAM

signals (stereo demodulation).

All channel parameters are programmed automatically by the built-in Automatic Standard

Recognition System (Autostandard) in order to find the correct sound standard. Channels can also

be programmed manually via the I²C interface for very specific standards not included among the

known standards.

Figure 10: Demodulator Block Diagram

Channel 1 = Mono Left

SIF

AGC

Amp

A/D

AGC

Control

AGC_CTRL (0Eh)

AGC_GAIN (0Fh)

3.1 Sound IF Signal

DCO1+

Mixer

CAROFFSET1 (22h)

AUTOSTD_STATUS (8Eh)

AUTOSTD_TIMERS (8Dh)

AUTOSTD_CTRL (8Ah)

AUTOSTD_STANDARD_DETECT (8Bh)

AUTOSTD_STEREO_DETECT (8Ch)

DCO2 +

Mixer

CAROFFSET2 (3Ah)

Channel

Filter

FIR1

AUTOSTD

Channel

Filter

FIR2

Channel 2 = Stereo/Mono Right

AM

Demodulator

FM

Demodulator

DEMOD_STAT(0Dh)

ZWT_STAT (42h)

NICAM_STAT(3Fh)

FM

Demodulator

DQPSK

Demodulator

AM

FML

Zweiton

Decoder

NICAM

Decoder

AM/FM Mono

(To Sound Preprocessing)

FM Stereo

(To Sound Preprocessing)

NICAM L

NICAM R

(To Sound Preprocessing)

The Analog Sound Carrier IF is connected to the STV82x7 via the SIF pin. Before Analog-to-Digital

Conversion (ADC), an Automatic Gain Control (AGC) is performed to adjust the incoming IF signal

to the full scale of the ADC. A preliminary video rejection is recommended to optimize conversion

and demodulation performances. The AGC system provides a gain value allowing for a wide range

of SIF input levels and is activated for all standards, except L/L’. In this particular case, the sound

carrier is AM-modulated and an automatic level adjustment would only damage the transmitted

audio signal. A preset I²C parameter is provided to define the gain of the AGC used in Manual mode

(Registers AGC_CTRL and AGC_GAIN).

Note: For optimum AM demodulation performance, it is recommended to use the MONO Input.

21/149

Digital Demodulator STV82x7

3.2 Demodulation

The demodulation system operates by default in Automatic mode. In this mode, the STV82x7 is able

to identify and demodulate any TV sound standard including NICAM and A2 systems (see

Ta bl e 4 ) without any external control via the I²C interface. It consists of the two demodulation

channels (Channel 1 = Mono Left and Channel 2 = Mono Right/Stereo) to simultaneously process

two sound carriers in order to handle all transmission modes (stereo and up to three mono

languages). The built-in Automatic Standard Recognition System (Autostandard) automatically

programs the appropriate bits in the I²C registers which are forced to Read-only mode for users (see

Section 12.1). The programming is optimized for each standard to be identified and demodulated.

Each mono and stereo standard can be removed (or added) from the List of Standards to be

recognized by programming registers AUTOSTD_STANDARD_DETECT and

AUTOSTD_STEREO_DETECT, respectively. The identified standard is displayed in register

AUTOSTD_STATUS and any change to standard is flagged to the host system via pin IRQ. This flag

must be reset by re-programming the MSBs of register AUTOSTD_CTRL while checking the

detected standard status by reading registers AUTOSTD_STATUS, NICAM_STAT and ZWT_STAT.

Moreover, the detection of Stereo mode during demodulation is also flagged in register

AUTOSTD_STATUS.

Important: L/L’ and D/K standards cannot be automatically processed because the same frequency

is used for the MONO carrier. An exclusive L/DK selection must programmed in register

AUTOSTD_CTRL. This may be externally controlled by detecting the RF modulation sign, which is

negative for all TV standards except L/L’.

To recover out-of standard FM deviations or the Sound Carrier Frequency Offset, additional I²C

controls are provided without interfering with the Automatic Standard Recognition System

(Autostandard).

DK-NICAM Overmodulation Recovery: Four different FM deviation ranges can be selected (via

register AUTOSTD_CTRL) for the DK standard while the Autostandard system remains active. The

maximum FM deviation is 500 kHz in DK Mono mode and 350 kHz in DK NICAM mode (limited by

overlapping FM and NICAM spectrum values). The demodulated signal peak level (proportional to

the FM deviation) is detected by the Peak Detector and written to registers PEAK_DET_L and

PEAK_DET_R. This value is used to implement Automatic Overmodulation Detection via an

external I²C control.

Important: Only the selection of the 50 kHz FM deviation standard is compatible with the other DKA2* standards (DK1, DK2 or DK3). These standards must be removed from the list of standards

(registers AUTOSTD_STANDARD_DETECT and AUTOSTD_STEREO_DETECT) when

programming larger FM deviations reserved only for DK-NICAM standards.

System Sound Type

FM Mono 5.5

B/G

FM/NICAM 5.5 5.850 27 50 80 J17 40

Typ e

Name

Table 4: Recognized Standards

Carrier 1

(MHz)

Carrier 2

(MHz)

FM Deviation

Nom. Max. Over

De-

emphasis

Roll

-off

(%)

Pilot

Frequency

(kHz)

FM 2-Carrier A2 5.5 5.742 27 50 80 50 µs 54.6875

D/K

D/K1 FM 2-Carrier A2* 6.5 6.258 50 µs 54.6875

22/149

FM Mono 6.5

FM/NICAM 6.5 5.850 27 50 80 J17 40

STV82x7 Digital Demodulator

Table 4: Recognized Standards (Continued)

System Sound Type

D/K2 FM 2-Carrier A2* 6.5 6.742 50 µs 54.6875

D/K3 FM 2-Carrier A2* 6.5 5.742 50 µs 54.6875

FM Mono 6.0

I

FM/NICAM 6.0 6.552 27 50 80 J17 100

L AM/NICAM 6.5 5.850 J17 40

FM Mono 4.5 15 27 50 75 µs

M/N

FM 2-Carrier A2+ 4.5 4.724 15 27 50 75 µs 55.069

Typ e

Name

Carrier 1

(MHz)

Carrier 2

(MHz)

FM Deviation

Nom. Max. Over

De-

emphasis

Roll

-off

(%)

Pilot

Frequency

(kHz)

For Chinese TV transmissions (DK-NICAM) which are subject to overmodulation, different FM

deviations are proposed for sound demodulation.

Sound Carrier Frequency Offset Recovery: Both Mono and Stereo IF Carrier frequencies can be

adjusted independently (registers CAROFFSET1 and CAROFFSET2) within a large range (up to

120 kHz for standard mono FM deviations) while the Automatic Standard Recognition System

remains active. The frequency offset estimation is written in registers DC_REMOVAL_L and

DC_REMOVAL_R (Mono Left / Channel 1 and Mono Right / Channel 2, respectively) and can be

used to implement the Automatic Frequency Control (AFC) via an external I²C control.

Manual Mode: If required, the Automatic Standard Recognition System system can be disabled

(Manual mode) and the user can control all registers including those only controlled by the

Automatic Standard Recognition System function when active. Manual mode is selected in register

AUTOSTD_STANDARD_DETECT (bit LDK_SCK, I_SCK, BG_SCK and MN_SCK set to 0).

23/149

Dedicated Digital Signal Processor (DSP) STV82x7

4 Dedicated Digital Signal Processor (DSP)

A dedicated Digital Signal Processor (DSP) takes charge of all audio processing features and the

low frequency signal processing features of the demodulator. The internal 24-bit architecture will

ensure a high quality signal treatment and an excellent dynamic.

4.1 Back-end Processing

The “back-end” processing corresponds to the low frequency signal processing (32 kHz or higher

frequencies) of the demodulator and other inputs (I²S, ADC).

Figure 11 shows a flowchart of the back-end processing tasks. However, the figure shows that the

processing is only a SINGLE SOURCE PROCESSING flow (no processing is possible with

“Demod + SCART” and I²S inputs simultaneously) and that the selection of a headphone output

restricts the loudspeakers configuration to 2+1 instead of 5+1.

Figure 11: Back-end Audio Processing

“Demod + SCART” or “SCART only” Input Modes

FM Channel1

FM Channel2

NICAM L

NICAM R

SCART L

SCART R

“I2S” Input Mode

I2S in 1

I2S in 2

I2S in 3

Stereo Peak Detector: 9D, bit 7 = 1

SRC X2/X4

DC

Removal

DC

Removal

DC

Removal

Autostandard

FM FM

De-emphasis

NICAM

De-emphasis

Stereo Peak Detector: 9D, bit 7 = 1

FM

Prescale

NICAM

Prescale

SCART

Prescale

I²S

Prescale

Dematrix

NICAM

Dematrix

LS

2

(L and R)

HP

2

(L and R)

SCART

Stereo Peak Detector: 9D, bit 7 = 0

Digital Audio Matrix

(L and R)

2 to 6

(L,R,C,LFE,Ls,Rs)

(L and R)

2

LS

HP

2

DownMix

SCART

2

Stereo Peak Detector: 9D, bit 7 = 0

(L and R)

24/149

STV82x7 Dedicated Digital Signal Processor (DSP)

The main features depend on the path:

● FM Channel

— DC Removal

—Prescaling

— De-emphasis (50 or 75 us)

— Stereo Dematrix

● NICAM Channel

— DC Removal

—Prescaling

— De-emphasis (J17)

— Dematrix

● Input SCART Channel

— DC Removal

—Prescaling

● Input I²S Channel

— I²S Prescaling

● Digital Audio Matrix

— Audio Channel Multiplexer between the different sources (IF, I²S, SCART) towards all

outputs (S/PDIF, LS, HP or SCART).

● Autostandard management

— device configuration depending on the standard to be detected

— freeze the device when a standard is detected

— once a standard detected, check that there is no change in the detection status

— set the correct action depending on any change in the detection status (mono backup or

mute setup and new standard detection)

● SCART

— Downmixing: L

— Soft Mute

/ RT or L0 / R0 (see AC-3 specification)

T

4.2 Audio Processing

The following software is provided for main loudspeakers (L, R, C, LS, RS, SubW):

● Downmix

● Dolby® Pro Logic II® Decoder (L

● ST WideSurround, ST OmniSurround, SRS® WOW™ or SRS® TruSurround XT® (certified

Virtual Dolby® Surround and Virtual Dolby® Digital)

● ST Dynamic Bass

● Smart Volume Control (SVC)

● 5-band Equalizer or Bass-Treble

● Loudness

● Volume with independent channels (Smooth Volume Control)

● Master Volume Control

● Mute/soft-mute

, RT → L, R, C, Ls, Rs, SubW) with Bass Management

T

25/149

Dedicated Digital Signal Processor (DSP) STV82x7

● Balance

● Beeper

● Pink Noise Generator (used to position the loudspeakers)

● Programmable Delay for each loudspeaker

● Adjustable Delay for “lip sync” up to 120 ms (to compensate audio/video latency) in SCART

Only Mode and up to 180 ms in Demodulator and SCART Mode

The following software is provided for the headphone or auxiliary output:

● Downmix

● SRS® TruBass™

● Smart Volume Control (SVC)

● Bass/Treble

● Loudness

● Independent Volume for each channel (Smooth Volume Control)

● Soft Mute

● Balance

● Beeper

● Adjustable Delay for “lip sync” up to 120 ms (to compensate audio/video latency) in SCART

Only Mode and up to 180 ms in Demodulator and SCART Mode

The following software is provided for SCART or S/PDIF outputs:

● Downmix

● Soft Mute

26/149

STV82x7 Dedicated Digital Signal Processor (DSP)

Figure 12: Audio Processing for Loudspeakers, Headphone, SCART and S/PDIF outputs

output Select

LS

S/PDIF

Output

SCART

Output

Output

Center

Output

Subwoofer

Output

Surround

Output

Headphone

Output

Input

S/PDIF

Digital

Vol um e

Bass/

SVC

SRS

S

Soft

Mute

Balance

ness

Loud-

Tr e bl e

Tr u B as s

Beeper

S

Digital

Soft

Vol um e

Bass /

Treble or

ST

Dynamic

SRS

Mute

Balance

5 bands

Bass

TruBass

Digital

Soft

Vol um e

Balance

Mute

Digital

Soft

Mute

Select

S/PDIF

Digital

Soft

Mute

Digital

Soft

Mute

Digital

Soft

Mute

2/0

Bass

Mgmt.

Loud-

and

3/2

ness

SVC

Vol um e

Vol um e

Balance

Vol um e

Equalizer

or

or

Pro Logic

C

ST

OmniSurnd

Decoder

Pro Logic II

LFE

Delay

Adjustable

L HP

Ls

Rs

R HP

SRS

XT

TruSurround

ST Wide

Surround

1to2/2to2

Dolby

Delay

L SCART

R SCART

Adjustable

L

R

27/149

Dedicated Digital Signal Processor (DSP) STV82x7

4.3 ST WideSurround

STV82x7 offers three preset ST WideSurround Sound effects on the Loudspeakers path:

● Music, a concert hall effect

● Movie, for films on TV

● Simulated Stereo, which generates a pseudo-stereo effect from mono source

“ST WideSurround Sound” is an extension of the conventional stereo concept which improves the

spatial characteristics of the sound. This could be done simply by adding more speakers and coding

more channels into the source signal as is done in the cinema, but this approach is too costly for

normal home use. The ST WideSurround system exploits a method of phase shifting to achieve a

similar result using only two speakers. It restores spatiality by adding artificial phase differences.

The Surround/Pseudo-stereo mode is automatically selected by the Automatic Standard

Recognition System (Autostandard) depending on the detected stereo or mono source. By default,

“Movie” is selected for Surround mode. This value may be changed to “Music” by the

STSRND_MODE bit in the STSRND_CONTROL register.

Additional user controls are provided to better adapt the spatial effect to the source. The ST

WideSurround Gain (STSRND_LEVEL) and ST WideSurround Frequency (STSRND_FREQ)

registers can be used to enhance Music Predominancy in Music mode and Theater effect and Voice

Predominancy in Movie mode.

4.4 ST OmniSurround

STV82x7 offers a spatial virtualizer to output any multi-channel input in stereo on the Loudspeakers

path:

“ST OmniSurround” will recreate a multi-channel spatial sound environment using only the Left and

Right front speakers. It can be adapted to any input configuration (OMNISRND_INPUT_MODE).

ST Voice will allow you to enhance the voice content of your program to increase the intellegibility

and the presence of the sound.

4.5 Dolby Pro Logic II Decoder

Dolby® Pro Logic II® is a matrix decoder that decodes the five channels of surround sound that

have been encoded onto the stereo sound tracks of Dolby® Surround program material such as

DVD movies and TV shows.

It is even possible to decode standard stereo signals like music or non encoded movies.

Furthermore, it is an active process designed to enhance sound localization through the use of very

high-separation decoding techniques.

The Dolby® Pro Logic II® decoder is also able to emulate the former Dolby® Pro Logic® decoder

in a specific mode.

4.6 Bass Management

This processing will generate the subwoofer signal and adjust all loudspeakers channels gain and

bandwidth.

Speakers capable of reproducing the entire frequency range will be referred to as “full range

speakers”, then signals sent to full range speaker will be full bandwidth (no filtering).

28/149

STV82x7 Dedicated Digital Signal Processor (DSP)

Speakers that have limited bass handling capabilities will be referred to as “satellite speakers”, then

signals sent to satellite speaker will be high-pass filtered to remove bass information below 100 Hz.

In the STV82x7, five output configuration modes have been implemented according to “Dolby

Digital Consumer Decoder” specifications. They are described below.

4.6.1 Bass Management Configuration 0

In some cases, the bass management filters are available in the decoder itself, so there is no need

to reproduce these filters. The output configuration shown in Figure 13 offers this possibility.

Figure 13: Bass Management Configuration 0 (with Pro Logic switch indicating its reset state)

L

R

C

Ls

Rs

LFE

-5 dB

-15 dB

+

L

R

C

Ls

Rs

SubW

29/149

Dedicated Digital Signal Processor (DSP) STV82x7

4.6.2 Bass Management Configuration 1

Configuration 1, shown in Figure 14, assumes that all five speakers are not full range and that all of

the bass information will be redirected to and reproduced by a single subwoofer. This configuration

is intended for use with 5 satellite speakers.

To prevent signal overload, the five main channels are attenuated by 15 dB, while the LFE channel

is attenuated by 5dB to maintain the proper mixing ratio.

Figure 14: Bass Management Configuration 1 (with Pro Logic switch indicating its reset state)

L

R

C

Ls

Rs

LFE

-5 dB

-15 dB

+

L

R

C

Ls

Rs

SubW

30/149

STV82x7 Dedicated Digital Signal Processor (DSP)

4.6.3 Bass Management Configuration 2

Configuration 2 assumes that the left and right speakers, are full range while the center and

surround speakers are smaller speakers. Also, all bass data is redirected to the left and right

speakers.

This configuration include output level adjustment that allows 12 dB attenuation for the 3 smaller

speakers (C, Ls, Rs). When the level adjustment will be disabled the decoder boosts by 12 dB the

full range speakers (Left, Right).

Figure 15: Bass Management Configuration 2 (all switches indicate their reset state)

Level Adjustment

OFF Switch

Ls

Rs

LFE

L

C

R

-5 dB

-12 dB

-12 dB

-15 dB

+

-1.5 dB

+

-1.5 dB

+

+12 dB

-12 dB

+12 dB

-12 dB

-12 dB

Subwoofer

ON Switch

+

L

C

R

Ls

Rs

SubW

31/149

Dedicated Digital Signal Processor (DSP) STV82x7

4.6.4 Bass Management Configuration 3

The third configuration, shown in Figure 16, assumes that all speakers except the center are full

range, then all bass information will be directed to and reproduced by the front left and front right

and both surround speakers. In order to provide more flexibility to this configuration, a switch will

offer an option which will produce a subwoofer channel by the LFE channel.

When the Subwoofer Switch is OFF, the input channels will be attenuated by 8 dB. Configuration 3

is required in certain high-end products.

Figure 16: Bass Management Configuration 3 (all switches indicate their reset state)

Level Adjustment

OFF Switch

Ls

Rs

LFE

L

C

R

-8dB

-4dB

-8dB

-4dB

-4.5dB

-8dB

-4dB

-8dB

-4dB

-8dB

-4dB

-8dB

-4dB

+

+

+

+

+

+

+10dB

+8dB

+4dB

+8dB

+4dB

+8dB

+4dB

+8dB

+4dB

+8dB

+4dB

L

C

R

Ls

Rs

SubW

Subwoofer

ON Switch

32/149

Subwoofer

ON Switch

STV82x7 Dedicated Digital Signal Processor (DSP)

4.6.5 Bass Management Configuration 4

This configuration implements the Simplified Dolby configuration. The center, left surround and right