Page 1

Programmable poly-phase energy calculator IC

Features

■ Supports 1-, 2- or 3-phase WYE and Delta

services, from 2 to 4 wires

■ Computes cumulative active and reactive wide-

band and fundamental harmonic energies

■ Computes active and reactive energies, RMS

and momentary voltage and current values for

each phase

■ Supports Rogowski coil, current transformer,

Shunt or Hall current sensors

■ Exclusive ripple-free energy calculation

algorithm

■ Programmable pulsed output

■ Stepper motor outputs

■ Neutral current, temperature, and magnetic

field monitoring

■ OTP memory for configuration and calibration

■ SPI interface

■ Supports IEC 62052-11 / 62053-21 / 62053-23

standards

■ Less than 0.1 % error over 1:1000 dynamic

range

Applications

■ Power metering

Description

The STPMC1 device functions as an energy

calculator and is an ASSP designed for effective

energy measurement in power line systems

utilizing Rogowski, current transformer, Shunt or

Hall current sensors. Used in combination with

one or more STPMSx ICs, it implements all the

functions needed in a 1-, 2- or 3-phase energy

Table 1. Device summary

Order code Temperature range Package Packaging

STPMC1

Datasheet − production data

TSSOP20

meter. It can be coupled with a microprocessor for

multi-function energy meters, or it can directly

drive a stepper motor for a simple active energy

meter. The calculator has five input data pins. The

first three receive the voltage and current

information of the phases. In fact, each data input

processes two ΔΣ signals, multiplexed in time and

generated by the STPMSx device. The fourth

input receives multiplexed ΔΣ signals also, and

can be used to sense the neutral current or

another signal - temperature, for example. The

fifth input data pin accepts non-multiplexed ΔΣ

signals and it can be used for sensing the

magnetic field information from a Hall sensor.

Four internal hard-wired DSP (digital signal

processing) units perform all the computations on

the ΔΣ streams in real time by means of ΔΣ

arithmetic blocks. This allows the achievement of

very high computation precision with fast and

efficient digital architecture. All the data recorded

by the STPMC1 are accessible through an SPI

port, which is also used to configure and calibrate

the device. The configuration and calibration data

can be saved in a 112-bit OTP block, or

dynamically set in microprocessor-based meters.

STPMC1BTR - 40 to 85 °C TSSOP20 (tape and reel) 2500 parts per reel

April 2012 Doc ID 15728 Rev 6 1/77

This is information on a product in full production.

www.st.com

77

Page 2

Contents STPMC1

Contents

1 Functional block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

2 Pin configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3 Maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

4 Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

5 Application . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

6 Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

7 Terminology . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

7.1 Measurement error . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

7.2 Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

7.3 Notation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

8 Typical performance characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

9 Theory of operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

9.1 General operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

9.2 Power supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

9.3 Resetting the STPMC1 (status bit HLT) . . . . . . . . . . . . . . . . . . . . . . . . . . 21

9.4 Clock generator (bits MDIV, FR1, HSA) . . . . . . . . . . . . . . . . . . . . . . . . . . 21

9.5 Zero crossing detection (signal ZCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

9.6 Period and line voltage measurement (status bits: LIN, BFR, LOW, BFF) 23

9.7 Single wire operation mode: SWM (status bits: NAH, BFR,

configuration bit FRS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

9.8 Load monitoring (status bit BIL, configuration bit LTCH) . . . . . . . . . . . . . 26

9.9 Error detection (status bits: BCF, PIN) . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

9.10 Tamper detection module (status bits: BCS, BSF, BIF,

configuration bit ENH) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

9.10.1 Sum of currents is above tamper threshold (status bit BCS) . . . . . . . . . 28

9.10.2 Phase sequence is wrong (status bit BSF) . . . . . . . . . . . . . . . . . . . . . . 31

9.10.3 Phase active powers do not have the same sign (status bit BIF) . . . . . 32

2/77 Doc ID 15728 Rev 6

Page 3

STPMC1 Contents

9.10.4 EMI is detected . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

9.11 Energy to frequency conversion (configuration bits: APL, KMOT,

LVS, FUND) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

9.12 Using STPMC1 in microcontroller based meter - peripheral

operating mode (configuration bits: APL, KMOT, LVS, FUND) . . . . . . . . . 34

9.13 Driving a stepper motor - standalone operating mode

(configuration bits: APL, LVS, KMOT) . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

9.14 Negative power accumulation (configuration bit ABS, status bit SIGN) . . 37

9.15 Phase delay calculation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

9.16 Calibration (configuration bits: PM, TCS, CIX, CVX, CCA, CCB, CPX) . . 40

9.16.1 Voltage and current channels calibration . . . . . . . . . . . . . . . . . . . . . . . . 40

9.16.2 Phase compensation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

9.16.3 Mutual current compensation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

9.17 Data records map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

9.17.1 Group 0 data records . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

9.17.2 Group 1 data records . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

9.17.3 Group 2 data records . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

9.17.4 Group 3 data records . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

9.17.5 Group 4 data records . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

9.17.6 Group 5 data records . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

9.17.7 Group 6 data records . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

9.17.8 Parity calculation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

9.18 Status bits map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

9.19 Configuration bits map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

9.20 Mode signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

9.21 SPI interface (configuration bit SCLP) . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

9.21.1 Remote reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

9.21.2 Reading data records . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

9.21.3 Writing procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

9.21.4 Interfacing the standard 3-wire SPI with STPMC1 SPI . . . . . . . . . . . . . 65

9.21.5 Permanent writing of the CFG bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

10 Energy calculation algorithm . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

10.1 Active energy calculation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

10.2 Reactive energy calculation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

10.3 Voltage and current RMS values calculation . . . . . . . . . . . . . . . . . . . . . . 71

Doc ID 15728 Rev 6 3/77

Page 4

Contents STPMC1

10.4 Energy integration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

10.5 Fundamental power calculation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

11 Package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

12 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

4/77 Doc ID 15728 Rev 6

Page 5

STPMC1 List of tables

List of tables

Table 1. Device summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Table 2. Pin description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Table 3. Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Table 4. Thermal data. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Table 5. Programmable pin functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Table 6. Typical external components . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Table 7. Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Table 8. Notation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Table 9. Input channels from the STPMSx . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Table 10. Frequency settings through MDIV and FR1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Table 11. CLK pin frequency settings through HSA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Table 12. STPMC1 configuration for STPMS2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Table 13. Good frequency ranges for different clock source values. . . . . . . . . . . . . . . . . . . . . . . . . . 24

Table 14. No-load detection thresholds . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Table 15. Tamper conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Table 16. Pin description versus SYS configuration (uX and iX represent the voltage

and the current signals) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Table 17. Energy registers LSB value . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Table 18. LED pin configuration for APL = 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Table 19. LED pin configuration for APL = 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Table 20. Configuration of MOP and MON driving signals with APL = 1, 2, 3 . . . . . . . . . . . . . . . . . . 36

Table 21. LED pin configuration for APL = 2, 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Table 22. Accumulation mode for negative power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Table 23. f

Table 24. f

Table 25. f

Table 26. Phase compensation for PM = 0, TCS = 0, fline = 50 Hz . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Table 27. Phase compensation for PM = 0, TCS = 1, fline = 50 Hz . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Table 28. Phase compensation for PM = 1, fline = 50 Hz . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Table 29. Mutual current compensation matrix for single-phase systems (SYS > 3) . . . . . . . . . . . . . 45

Table 30. Mutual current compensation matrix for three-phase systems (SYS < 4) . . . . . . . . . . . . . 45

Table 31. 3-phase status bits description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Table 32. X-phase status bits description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Table 33. Configuration bits map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Table 34. Mode signals description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Table 35. Functional description of commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Table 36. Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

frequency settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

phc

frequency values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

phc

frequency settings for PM = 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

phc

Doc ID 15728 Rev 6 5/77

Page 6

List of figures STPMC1

List of figures

Figure 1. STPMC1 device block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Figure 2. Pin connections (top view) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Figure 3. Application schematic in standalone operating mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Figure 4. Application schematic using an MCU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Figure 5. Supply current vs. supply voltage, T

Figure 6. Digital voltage regulator: line - load regulation. (f

across V

and VSS; 1 µF across VDD and V

CC

Figure 7. Gain response of decimator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Figure 8. Connections of oscillator: (a) quartz, (b) external source . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Figure 9. ZCR signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Figure 10. LIN and BFR behavior when f

line

Figure 11. Currents of the three phase system in example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Figure 12. Stepper driving signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

Figure 13. Phase delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Figure 14. Group 0 data records . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

Figure 15. Group 1 data records . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Figure 16. Group 2 data records . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Figure 17. Group 3 data records . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Figure 18. Group 4 data records . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Figure 19. Group 5 data records . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Figure 20. Group 6 data records . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Figure 21. Timing for providing remote reset request . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Figure 22. Timing for data records reading . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Figure 23. Data records reconstruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Figure 24. Timing for writing configuration and mode bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

> f

MCLK

= 25°C (f

A

/2

= 4.194 MHz, f

XTAL1

SSA

16

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

= 0; 100 nF

XTAL1

; TA = 25 °C). . . . . . . . . . . . . . . . . . . . . . 17

= 8.192 MHz) . 17

XTAL1

6/77 Doc ID 15728 Rev 6

Page 7

STPMC1 Functional block diagram

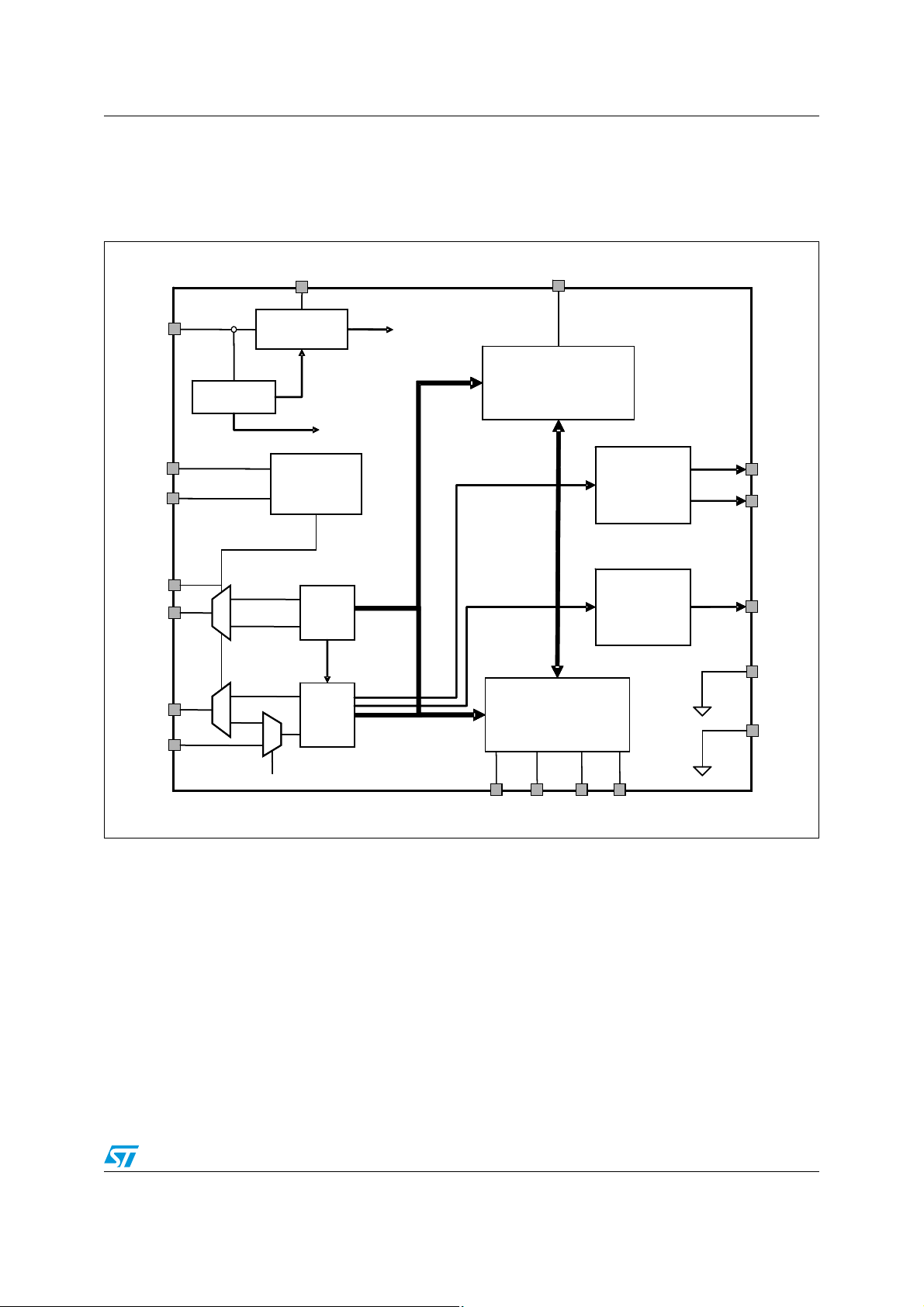

1 Functional block diagram

Figure 1. STPMC1 device block diagram

VDD

VCC

VCC

XTAL1

XTAL1

XTAL2

XTAL2

Band Gap

Band Gap

VDD

Linear Vregs

Linear Vregs

VBG

VBG

BIAS

BIAS

Clock

Clock

Generator

Generator

POR

POR

CONFIGURATORS

CONFIGURATORS

VOTP

VOTP

112 OTP

112 OTP

STEPPER

STEPPER

DRIVER

DRIVER

MOP

MOP

MON

MON

CLK

CLK

DAx

DAx

DAN

DAN

DAH

DAH

0

0

1

1

0

0

1

1

DAx-C

DAx-C

DAx-V

DAx-V

DAN-C

DAN-C

DAN-V

DAN-V

ENH

ENH

xDSP

xDSP

NDSP

NDSP

SPI Interface

SPI Interface

SCS SYN

SCL

SCS SYN

SCL

Energy to Freq

Energy to Freq

Converters

Converters

SDA

SDA

Note: DAx stands for DAR, DAS, DAT, and xDSP stands for RDSP, SDSP, TDSP.

LED

LED

VSSA

VSSA

VSS

VSS

Doc ID 15728 Rev 6 7/77

Page 8

Pin configuration STPMC1

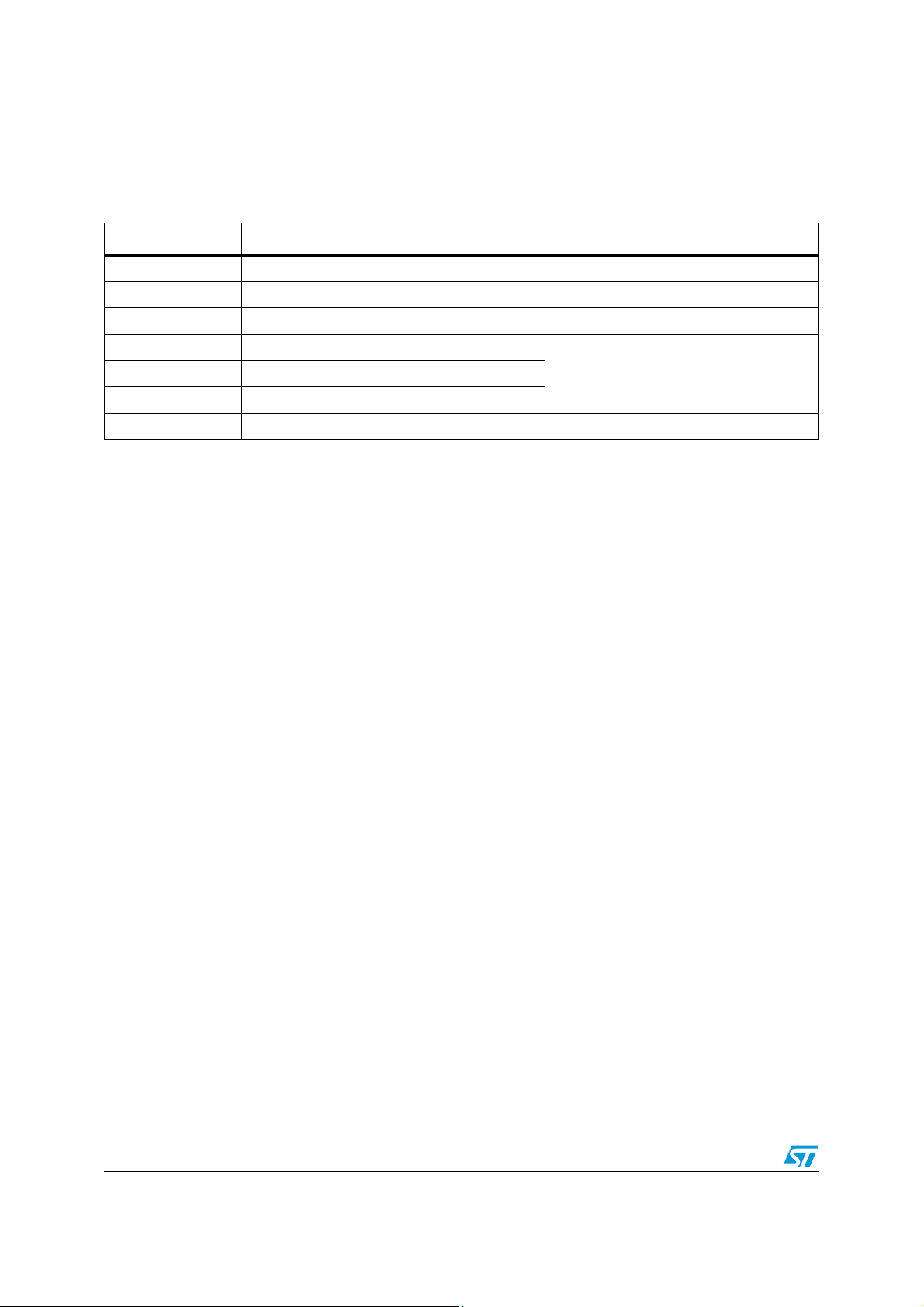

2 Pin configuration

Figure 2. Pin connections (top view)

MON

MON

MOP

MOP

SCS

SCS

V

V

DD

DD

V

V

SS

SS

V

V

CC

CC

V

V

OTP

OTP

DAH

DAH

DAR

DAR

DAS

DAS

STPMC1

STPMC1

LED

LED

SDATD

SDATD

SCLNLC

SCLNLC

XTAL1

XTAL1

XTAL2

XTAL2

SYN

SYN

V

V

SSA

SSA

CLK

CLK

DAN

DAN

DAT

DAT

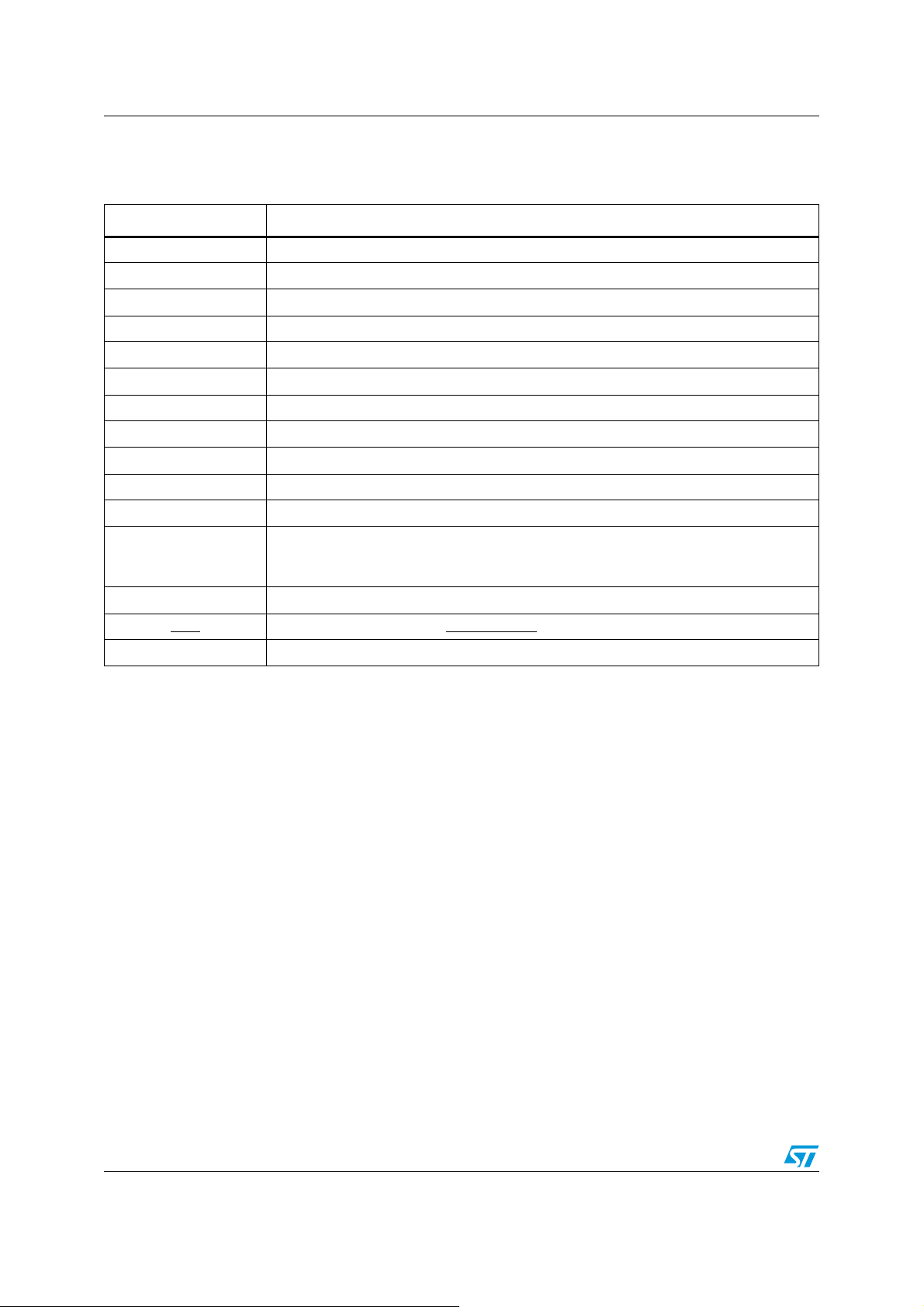

Table 2. Pin description

Pin n° Symbol Type

(1)

Name and function

1 MON D / P O Programmable output pin, see

2 MOP D / P O Programmable output pin, see

3 SCS D I Digital input pin, see

Ta bl e 5

Ta b l e 5

Ta b l e 5

4VDDA O 1.8 V output of internal low drop regulator which supplies the digital core

5V

SS

A GND Ground level for pad-ring and power supply return

6VCCP I Supply voltage

7V

OTP

P I Supply voltage for OTP cells

8 DAH D I Input for non-multiplexed ΔΣ signals

9 DAR D I Input for multiplexed ΔΣ R-phase signals

10 DAS D I Input for multiplexed ΔΣ S-phase signals

11 DAT D I Input for multiplexed ΔΣ T-phase signals

12 DAN D I Input for multiplexed ΔΣ PTAT and neutral signal

13 CLK D O 2 mA clock output for STPMSx devices

14 V

SSA

15 SYN D I/O Programmable input/output pin, see

A GND Ground level of core

Ta bl e 5

16 XTAL2 A Crystal oscillator pin

17 XTAL1 A Crystal oscillator pin

18 SCLNLC D I/O Programmable input/output pin, see

19 SDATD D I/O Programmable input/output pin, see

20 LED D O Programmable output pin, see

1. A: Analog, D: Digital, P: Power, I: Input, O: Output, GND: Ground

8/77 Doc ID 15728 Rev 6

Ta bl e 5

Ta bl e 5

Ta b l e 5

Page 9

STPMC1 Maximum ratings

3 Maximum ratings

Table 3. Absolute maximum ratings

Symbol Parameter Value Unit

DC input voltage - 0.3 to 6 V

Current on any pin (sink/source) ± 150 mA

Input voltage at all pins -0.3 to V

+ 0.3 V

CC

Input voltage at OTP pin - 0.3 to 25 V

V

V

I

V

CC

PIN

ID

OTP

ESD Human body model (all pins) ± 3.5 kV

T

T

T

STG

OP

J

Operating ambient temperature - 40 to 85 °C

Junction temperature - 40 to 150 °C

Storage temperature range - 55 to 150 °C

Note: Absolute maximum ratings are those values beyond which damage to the device may occur.

Functional operation under these condition is not implied.

Table 4. Thermal data

Symbol Parameter Value Unit

R

thJA

1. This value refers to single-layer PCB, JEDEC standard test board.

Thermal resistance junction-ambient 114.5

(1)

°C/W

Doc ID 15728 Rev 6 9/77

Page 10

Functions STPMC1

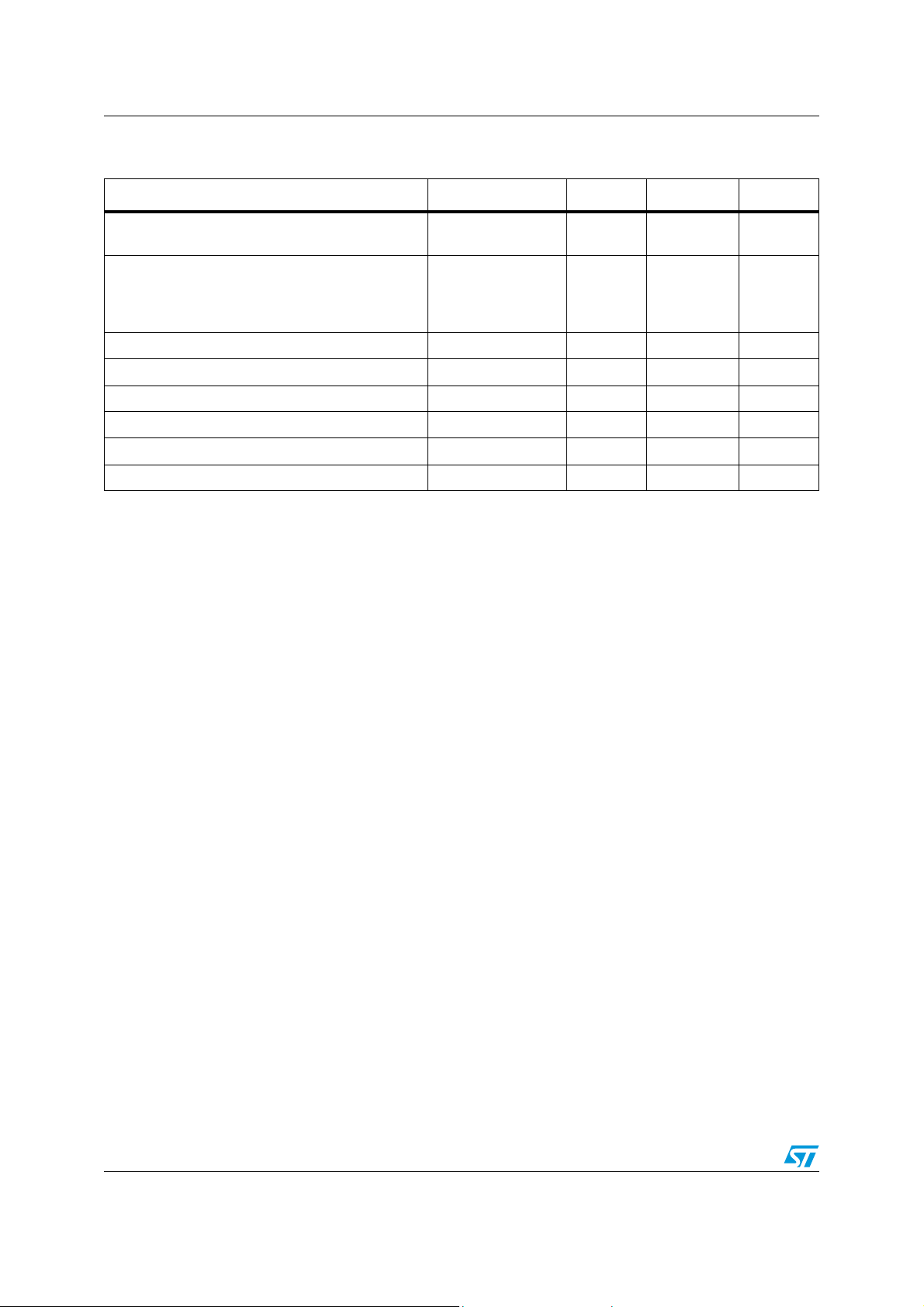

4 Functions

Table 5. Programmable pin functions

Programmable pin Standalone mode (APL = 2 or 3) Peripheral mode (APL = 0 or 1)

MON Output for stepper node (MB) - charge pump Watchdog reset

MOP Output for stepper node (MA) - charge pump

LED 3-phase energy pulsed output Programmable energy pulsed output

SCLNLC No load indicator

SYN-NP Negative power indicator

SCS SPI data transmission enable

ZCR

SPI interfaceSDATD Tamper indicator

signal

10/77 Doc ID 15728 Rev 6

Page 11

STPMC1 Application

5 Application

Figure 3. Application schematic in standalone operating mode

N R S T

N R S T

Current

Current

Sensor

Sensor

Voltage

Voltage

Sensor

Sensor

Current

Current

Sensor

Sensor

Voltage

Voltage

Sensor

Sensor

Current

Current

Sensor

Sensor

Voltage

Voltage

Sensor

Sensor

STPMS1

STPMS1

STPMS1

STPMS1

STPMS1

STPMS1

3 V to 5.5 V

3 V to 5.5 V

VCC

VCC

DAR

DAR

DAS

DAS

DAT

DAT

DAN

DAN

DAH

DAH

CLK XTAL1 XTAL2

CLK XTAL1 XTAL2

Stepper

Stepper

Counter

Counter

MOPMONVOTP

MOPMONVOTP

STPMC1

STPMC1

VSS

VSS

LED

LED

SCS

SCS

SYN-NP

SYN-NP

SCL-NC

SCL-NC

SDA-TD

SDA-TD

VDD

VDD

VSSA

VSSA

Pulsed output

Pulsed output

Negative power

Negative power

No load condition

No load condition

Tamper Detection

Tamper Detection

Current

Current

Sensor

Sensor

Figure 4. Application schematic using an MCU

N R S T

N R S T

Current

Current

Sensor

Sensor

Voltage

Voltage

Sensor

Sensor

Current

Current

Sensor

Sensor

Voltage

Voltage

Sensor

Sensor

Current

Current

Sensor

Sensor

Voltage

Voltage

Sensor

Sensor

STPMS1

STPMS1

STPMS1

STPMS1

STPMS1

STPMS1

STPMS1

STPMS1

3 V to 5.5 V

3 V to 5.5 V

Zero

Zero

Crossing

Crossing

DAR

DAR

DAS

DAS

STPMC1

DAT

DAT

DAN

DAN

DAH

DAH

STPMC1

CLK XTAL1 XTAL 2

CLK XTAL1 XTAL 2

MOPMONVOTPVCC

MOPMONVOTPVCC

VSS

VSS

Watchdog

Watchdog

LED

LED

SCS

SCS

SYN-NP

SYN-NP

SCL-NC

SCL-NC

SDA-TD

SDA-TD

VDD

VDD

VSSA

VSSA

Pulsed

Pulsed

Output

Output

Energy

Energy

To MCU

To MCU

Current

Current

Sensor

Sensor

TEMP

TEMP

Sensor

Sensor

STPMS1

STPMS1

Doc ID 15728 Rev 6 11/77

Page 12

Application STPMC1

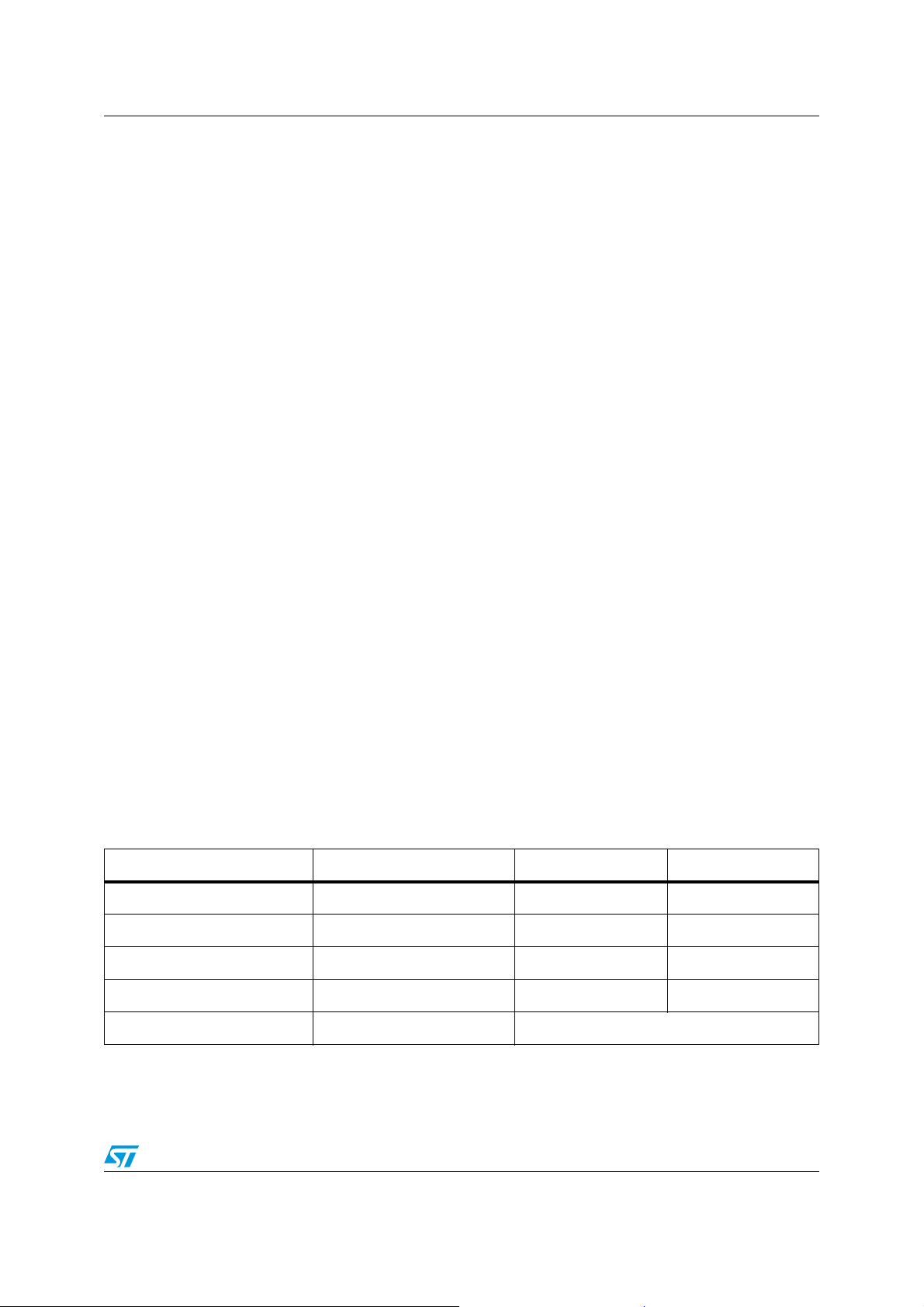

Table 6. Typical external components

Function Component Value Tolerance Unit

Reads or writes to a calculator device via SPI and

performs computation

Measurement reference clock Crystal oscillator

Interface R-phase voltage, current STPMSx --- --- ---

Interface S-phase voltage, current STPMSx --- --- ---

Interface T-phase voltage, current STPMSx --- --- ---

Interface PTAT, neutral current STPMSx --- --- ---

Interface PTAT or hall STPMSx --- --- ---

Low-end user interface Stepper counter

Microprocessor --- --- ---

4.194

8.192

4.915

9.830

± 30 ppm MHz

Note: The components listed above refer to a typical metering application. In any case, STPMC1

operation is not limited to the choice of these external components.

12/77 Doc ID 15728 Rev 6

Page 13

STPMC1 Electrical characteristics

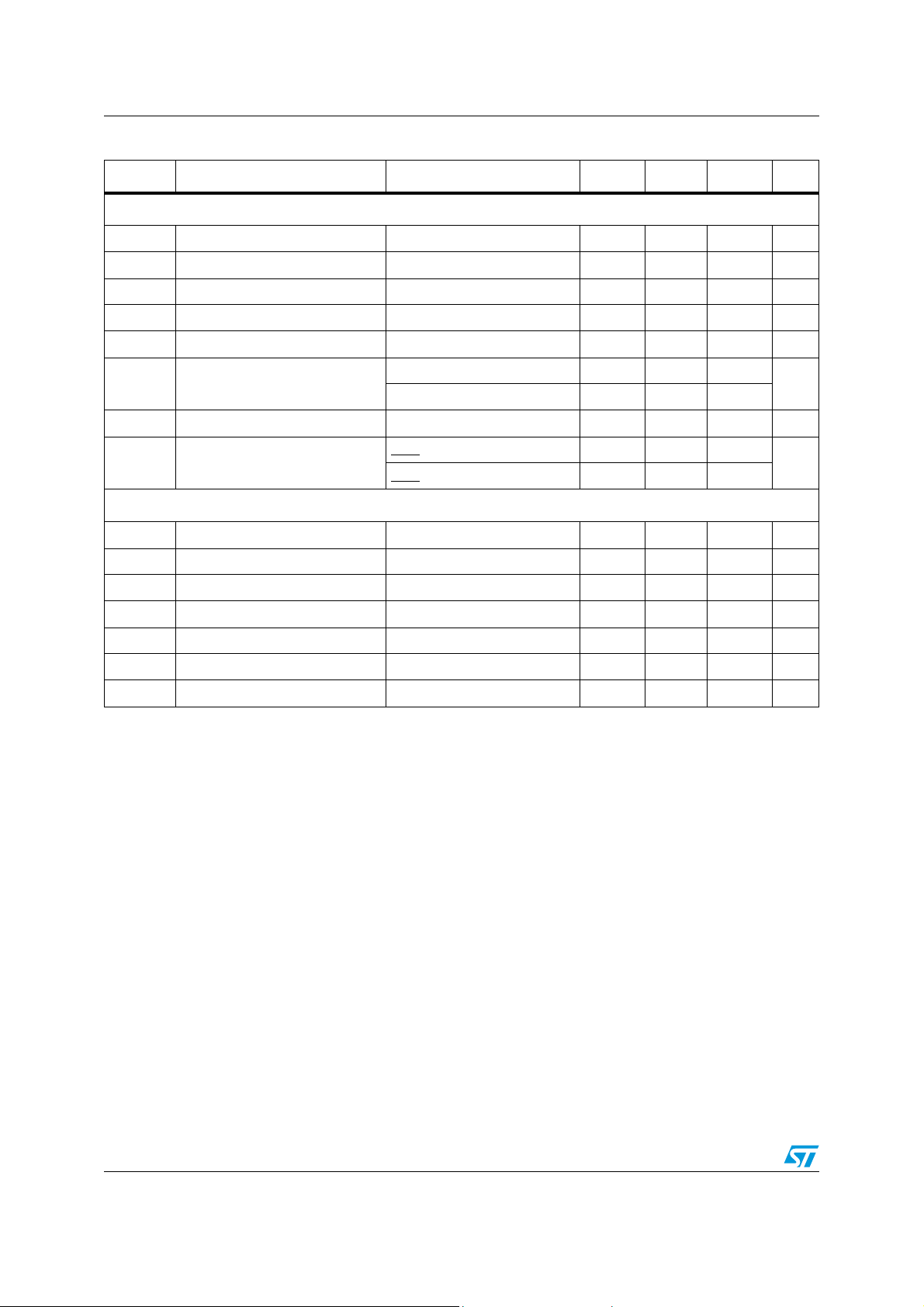

6 Electrical characteristics

(VCC = 5 V, TA= - 40 to + 85 °C, 100 nF across VCC and VSS; 1 µF across VDD and V

SSA

unless otherwise specified).

Table 7. Electrical characteristics

Symbol Parameter Test conditions Min. Typ. Max. Unit

Energy measurement accuracy

f

BW

General Section

V

CC

I

CC

ΔI

CC

POR Power on reset on V

V

DD

V

OTP

I

OTP

Effective bandwidth Limited by digital filtering

5400Hz

Operating supply voltage 3.17 5.5 V

Supply current. Configuration

registers cleared or device

locked

f

=4.194MHz;

XTAL1

V

=3.2V; CL=100nF; no

CC

loads

567mA

Increase of supply current per

configuration bit, during

f

=4.194MHz; VCC=3.2V 100 µA/bit

XTAL1

programming

f

CC

=4.194MHz 2.5 V

XTAL1

Digital supply voltage 1.70 1.80 1.90 V

OTP programming voltage 14 20 V

OTP programming current per

bit

Single bit programming 5 mA

,

t

OTP

I

LATCH

OTP programming time per bit Single bit programming 500 µs

Current injection latch-up

immunity

Digital I/O (DAH, DAR, DAS, DAT, DAN, CLK, SDA, SCS, SYN, LED)

V

V

V

V

I

t

Input high voltage Other pins 0.75V

IH

Input low voltage Other pins 0.25V

IL

Output high voltage IO=-2mA VCC-0.4 V

OH

Output low voltage IO=+2mA 0.4 V

OL

Pull up current 15 µA

UP

Transition time C

TR

LOAD

=50pF, V

=5V 10 ns

CC

Power I/O (MOP, MON)

V

V

t

Output high voltage IO=-16mA 0.9V

OH

Output low voltage IO=+16mA 0.1V

OL

Transition time C

TR

LOAD

=50pF, V

=5V 10 ns

CC

CC

CC

300 mA

V

V

CC

V

V

CC

Doc ID 15728 Rev 6 13/77

Page 14

Electrical characteristics STPMC1

Table 7. Electrical characteristics (continued)

Symbol Parameter Test conditions Min. Typ. Max. Unit

Crystal oscillator

V

V

I

R

C

f

XTAL1

f

MCLK

f

CLK

Input high voltage 1.2 V

IH

Input low voltage 0.6 V

IL

Input current on XTAL2 V

in

External resistor 1 4 MΩ

p

External capacitors 22 pF

p

Nominal output frequency

Internal clock frequency see

Output CLK pin frequency

SPI interface timing

F

SCLKr

F

SCLKw

t

t

t

t

OFF

t

SYN

DH

ON

Data read speed TA= 25°C 32 MHz

Data write speed TA= 25°C 100 kHz

Data setup time 20 ns

DS

Data hold time 0 ns

Data driver on time 20 ns

Data driver off time 20 ns

SYN active width 2/f

=5.3V -1 +1 µA

CC

4.000 4.194 4.915

8.000 8.192 9.830

Ta bl e 1 0

HSA

= 0 f

= 1 f

HSA

8.000 8.192 9.830 MHz

/4

XTAL1

/2

XTAL1

XTAL1

MHz

MHz

s

Note: Typical value, not production tested.

14/77 Doc ID 15728 Rev 6

Page 15

STPMC1 Terminology

7 Terminology

7.1 Measurement error

The error associated with the energy measured by the STPMC1 is defined as:

EnergyTrue)reading(1SPMC

−

EnergyTrue

7.2 Conventions

The lowest analog and digital power supply voltage is called VSS which represents the

system ground (GND). All voltage specifications for digital input/output pins are referred to

GND.

Positive currents flow into a pin. “Sinking current” is the current flowing into the pin, and so it

is positive. “Sourcing current” is the current flowing out of the pin, and so it is negative.

Signal timing specifications treated by a digital control part are relative to XTAL1. This signal

is provided from the crystal oscillator or from an external source as specified in paragraph

9.4

.

ErrorPercentage

=

Signal timing specifications of the SPI interface are relative to the SCLNLC. There is no

direct relationship between the clock (SCLNLC) of the SPI interface and the clock of the

DSP block (XTAL1).

A positive logic convention is used in all equations.

Doc ID 15728 Rev 6 15/77

Page 16

Terminology STPMC1

7.3 Notation

Table 8. Notation

Label Description

uVoltage

i Current

u

X

i

X

i

N

U

X

I

X

P Active energy full bandwidth

F Active energy fundamental

Q Reactive energy full bandwidth

R Reactive energy fundamental

X

Y

PIN Pin names are UPPERCASE

CFG

Phase X voltage (X = R, S, T)

Phase X current (X = R, S, T)

Neutral current

Phase X RMS voltage (X = R, S, T)

Phase X RMS current (X = R, S, T)

X energy type per Y phase

X = P, F, Q, R

Y = R, S, T or Σ for 3-phase

Configuration bit names are UNDERLINED

SIG

Internal signals and status bits are in

ITALICS

16/77 Doc ID 15728 Rev 6

Page 17

STPMC1 Typical performance characteristics

8 Typical performance characteristics

Figure 5. Supply current vs. supply voltage, TA = 25°C (f

8

8

7,5

7,5

7

7

6,5

6,5

6

6

(mA)

(mA)

CC

CC

I

I

5,5

5,5

5

5

4,5

4,5

4

4

3 3,5 4 4,5 5 5,5 6

3 3,5 4 4,5 5 5,5 6

V

V

CC

CC

(V)

(V)

XTAL1

Figure 6. Digital voltage regulator: line - load regulation. (f

1 µF across V

2,5

2,5

DD

and V

; TA = 25 °C)

SSA

= 4.194 MHz, f

ICC25°C

ICC25°C

ICC-40°C

ICC-40°C

ICC85°C

ICC85°C

= 0; 100 nF across VCC and VSS;

XTAL1

= 8.192 MHz)

XTAL1

2

2

1,5

1,5

(V)

(V)

1

1

DD

DD

V

V

0,5

0,5

0

0

0123456

0123456

-0,5

-0,5

V

V

(V)

(V)

CC

CC

Doc ID 15728 Rev 6 17/77

Page 18

Typical performance characteristics STPMC1

Figure 7. Gain response of decimator

Flat band (10Hz Flat band (10Hz – 300Hz)

Flat band (10Hz Flat band (10Hz – 300Hz)

3 dB band (4Hz 3 dB band (4Hz –700Hz)

3 dB band (4Hz 3 dB band (4Hz –700Hz)

18/77 Doc ID 15728 Rev 6

Page 19

STPMC1 Theory of operation

9 Theory of operation

9.1 General operation

The STPMC1 (also called a calculator) is an ASSP designed for effective measurement in

power line systems utilizing the Rogowski coil, current transformer, Shunt or Hall current

sensors. This device, used with the STMicroelectronics STPMSx companion chip (an

analog front-end device), can be implemented as standalone or as a peripheral in a

microprocessor based 1-, 2- or 3-phase energy meter.

The calculator consists of three sections: analog, digital and OTP (see

● The analog section is composed of a band-gap voltage reference and a low-drop

voltage regulator.

● The digital section consists of a system control, clock generator, three PDSP and a

NDSP, a SPI interface.

● The 112-bit OTP block and the 16 system signals, used for testing, configuration and

calibration purposes, are controlled through SPI by means of a dedicated command

set.

The calculator has five input data pins, of which four are fed by signals generated by the

STPMSx, see

Ta b le 9

.

Three of them (DAR/DAS/DAT) are used to receive multiplexed signals of voltage and

current, implementing energy measurement in 1-, 2- and 3-phase (3 and 4 wires) systems.

After being de-multiplexed, each phase input is sent to the correspondent DSP unit that

processes voltage and current information and performs energy calculation, according to

the settings of the configuration bits (see

The DAN input, which also receives a multiplexed signal output from STPMSx device, is

typically used to monitor neutral current for anti tampering functions in 1-, 2- and 3-phase (4

wires) systems. Normally the STPMSx monitors current and voltage but in case of neutral

monitoring the voltage channel can be connected to a different type of sensor, for example a

temperature sensor.

The fifth input data pin (DAH) accepts non-multiplexed ΔΣ signals. It can be used for EMI

sensing through Hall sensors or for temperature sensing.

Table 9. Input channels from the STPMSx

Ta bl e 33

Figure 1

):

).

Channel name Property Signal 1 Signal 2

DAR Multiplexed Voltage Current

DAS Multiplexed Voltage Current

DAT Multiplexed Voltage Current

DAN Multiplexed Temperature Current

DAH Not multiplexed EMI or temperature

The companion chip (STPMSx) embeds 2 ΔΣ ADC converters and the necessary logic

capable of providing the multiplexed ΔΣ streams.

See the STPMSx documentation for more details.

Doc ID 15728 Rev 6 19/77

Page 20

Theory of operation STPMC1

These four multiplexed signals are separated, by a digital de-multiplexer, back into eight ΔΣ

signals, called streams. The signal coming from the voltage channel of the STPMSx is

named with the suffix V, while the stream coming from the current channel is named with the

suffix C. For example, the voltage stream of the S-phase is named DAS-V.

Then, each pair of phase the voltage and current stream coming from DAR, DAS and DAT is

connected to a dual-channel RDSP, SDSP, TDSP unit (i.e. DAR-V and DAR-C are

connected to RDSP).

Each phase voltage input stream is proportional to phase voltage u. Each phase current

input stream is proportional to derivation of phase current di/dt, when it originates from

Rogowski coil, or to phase current i, when it originates from Shunt or CT or Hall sensor. In

this case a derivative is inserted into the voltage channel to get a stream proportional to

du/dt. The sensors differ from each other for sensitivity, phase error and susceptibility to

external EM fields.

Each of these DSP units performs the following:

● checks the integrity of the streams

● calibrates streams

● filters both streams with a dedicated decimation filter

● computes active and reactive energies, momentary and RMS values for voltage and

current, period of power line voltage signal.

In each DSP there are calibrators capable of adjusting the readings ±12.5%.

The power computer does the final calculations of the value and direction of the power and

checks for no-load condition.

Another dual DSP unit, called NDSP, processes the streams coming from DAN and DAH. In

fact, using the ENH

bit (see

Ta bl e 33

), the user can select either the voltage stream of the

DAN pin (DAN-V) or the DAH stream as the input of the NDSP unit, while the current stream

DAN-C is always processed as neutral current.

In its voltage channel, the NDSP unit uses a 2 s time multiplex to process two streams.

During the first half of the interval the voltage input stream is processed (which can be DANV or DAH, according to the ENH

bit), while during the second half a stream constituted by

the sum of all four calibrated currents (i.e. DAR-C + DAS-C + DAT-C + DAN-C).

In its current channel the NDSP unit process the current stream of the neutral conductor as

follows:

● checks the integrity of stream

● calibrates the stream

● filters the stream with a dedicated decimation filter

● computes momentary and RMS values of the stream

● if no errors have been detected in the phase timing, computes phase frequency,

integrates the phase powers by means of 3-input integrators of energies and generates

all pulse output signals.

When the DAH input stream is selected, it is checked to detect an external magnetic

influence (EMI) to the meter.

20/77 Doc ID 15728 Rev 6

Page 21

STPMC1 Theory of operation

The calculator, thanks to its flexibility, can work in all worldwide distribution network

standards. By programming the SYS

OTP bits, it is possible to implement the following

systems:

● 3-phase, 4-wire RSTN, 4-system RSTN (tamper);

● 3-phase, 4-wire RSTN, 3-system RST;

● 3-phase, 3-wire RST_, 3-system RST_ (tamper);

● 3-phase, 3-wire RST_, 2-system R_T_ (Aron);

● 2-phase, 3-wire _STN, 2-system _ST_ (America);

● 1-phase, 2-wire __TN, 2-system _ST_ (tamper coil:coil);

● 1-phase, 2-wire __TN, 2-system _ST_ (tamper coil:shunt);

● 1-phase, 2-wire __TN, 1-system __T_.

The results of all DSP units are available as pulse frequency on pin LED, MOP and MON,

which can also drive a stepper counter, and as states on the digital outputs of device or as

data bits in data records, which can be read from the device by means of SPI interface from

pins SDA, SNC, SCL and SYN. This system bus interface is also used during temporary or

permanent programming OTP bits and system signals or to execute a remote reset request.

A logic block common to all DSP units performs other operations like:

● selecting the valid phase period result from which line frequency is computed in NDSP

unit

● checking the equality of phase angles between all three phase voltages

● preparing current values for compensation of external intermediate phase magnetic

influences

● checking the sum of currents

● computing intermediate phase voltages

● combining the 3-phase status bits

● performing a watchdog user function

After the device is fully tested, configured and calibrated, a dedicated bit of the OTP block,

called TSTD, can be written permanently in order to prevent the change of any configuration

bit.

9.2 Power supply

The supply pins for the analog part are VCC and VSS. The VCC is the power input of the 1.8

V low drop regulator, band-gap reference and bias generators.

From the V

used to power the OTP module and digital core. The V

for all the internal signals. 100 nF low ESR capacitors should be connected between V

and V

SS

to the device.

The STPMC1 contains a power on reset (POR) detection circuit. If the V

than 2.5 V then the STPMC1 goes into an inactive state, all the functions are blocked

asserting a reset condition. This is useful to ensure correct device operation at power-up

and during power-down. The power supply monitor has built-in hysteresis and filtering,

which gives a high degree of immunity from false triggering due to noisy supplies.

A bandgap voltage reference (VBG) of 1.23 V ±1% is used as a reference voltage level

pin a linear regulator generates the +1.8 V voltage supply level (VDD) which is

CC

, and 1 µF between VDD and V

pin represents the reference point

SS

. All these capacitors must be placed very close

SSA

supply is less

CC

Doc ID 15728 Rev 6 21/77

CC

Page 22

Theory of operation STPMC1

source for the linear regulator. Also, this module produces several bias currents and

voltages for all other analog modules and for the OTP module.

9.3 Resetting the STPMC1 (status bit

HLT

The STPMC1 has no reset pin. The device is automatically reset by the power-on-reset

detection circuit (POR) when the V

crosses the 2.5 V value, but it can be reset also

CC

through the SPI interface through a dedicated remote reset request (RRR) command (see

paragraph

9.21

for RRR details).

The reset through SPI is used during production testing or in an application with some onboard microprocessors when a malfunction of the device is detected.

Resetting the STPMC1 causes all the functional modules of STPMC1 to be cleared,

including the OTP shadow latches (see paragraph

9.19

for an OTP shadow latch memory

description). In case of reset through SPI the mode signals (see paragraph

description of the mode signals) are not cleared.

In cases of reset caused by the POR circuit all blocks of the digital part, except the SPI

interface, are held in a reset state for 125 ms after the reset condition. When the reset is

performed through SPI, no delayed turn-on is generated.

During the device reset, the status bit

HLT

is held high, meaning that data read from the

device register are not valid.

9.4 Clock generator (bits MDIV, FR1, HSA)

All the internal timing of the STPMC1 is based on the XTAL1 signal. This signal can be

generated in two different ways:

● Quartz: the oscillator works with an external crystal.

● External clock: the clock is provided by an external source connected to XTAL1.

)

9.20

for a

The suggested circuits are depicted in

Figure 8. Connections of oscillator: (a) quartz, (b) external source

22/77 Doc ID 15728 Rev 6

Figure 8

.

Page 23

STPMC1 Theory of operation

The clock generator is responsible for two tasks.

The first is to retard the turn-on of some functional blocks after POR in order to help a

smooth start of external power supply circuitry by keeping off all major loads. For this

reason, all blocks of the digital part, except the SPI interface, are held in a reset state for 125

ms after a power on reset (see

Section 9.3

).

The second task of the clock generator is to provide all necessary clocks for the digital part.

In this task, a MDIV

nominal frequency value from XTAL1 (f

Four nominal frequencies are possible through proper setting of the MDIV

Ta bl e 10

).

and FR1 programming bits are used to inform the device about the

).

XTAL1

and FR1 bits (see

The internal master clock f

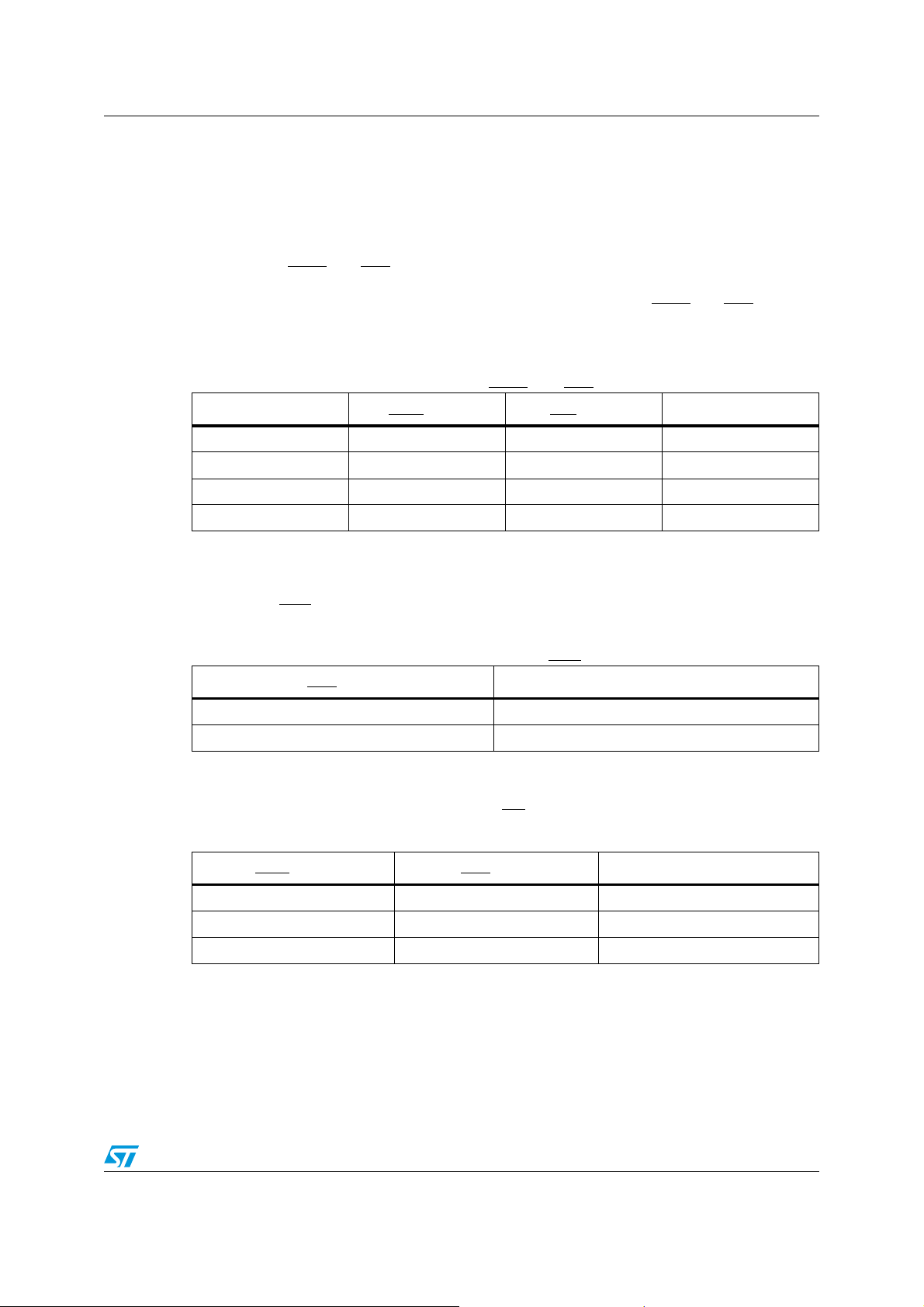

Table 10. Frequency settings through MDIV

f

XTAL1

4.194 MHz 0 0 8.389 MHz

4.915 MHz 0 1 9.830 MHz

8.192 MHz 1 0 8.192 MHz

9.830 MHz 1 1 9.830 MHz

1. 4 MHz and 8 MHz clock are also supported. MDIV and FR1 have to be set as for 4.194 MHz and 8.192

MHz respectively.

Through the HSA bit the frequency of the output pin CLK (f

the STPMSx devices, can be derived as reported in

Table 11. CLK pin frequency settings through HSA

HSA (1 bit) f

0f

1f

To properly work with STPMS2, the clock configurations in

Moreover, with STPMS2 companion chip the PM

Table 12. STPMC1 configuration for STPMS2

is derived from f

MCLK

MDIV (1 bit) FR1 (1 bit) f

as shown in

XTAL1

and FR1

Ta bl e 11

Ta bl e 10

(1)

), which provides the clock for

CLK

.

STPMC1

CLK

/ 4

XTAL1

/ 2

XTAL1

Ta bl e 12

must be used.

bit must always be set.

.

MCLK

MDIV (1 bit) HSA (1 bit) f

00f

10f

01f

9.5 Zero crossing detection (signal

The STPMC1 has a zero crossing detection circuit on the voltage channel that can be used

to synchronize some utility equipment to zero crossing or max of line voltage events. This

circuit produces the internal signal

the line voltages and a rising edge every peak (positive or negative) of one of the line

voltages.

ZCR

that has a falling edge every zero crossing of one of

Doc ID 15728 Rev 6 23/77

ZCR

CLK

/ 4

XTAL1

/ 4

XTAL1

/ 2

XTAL1

)

Page 24

Theory of operation STPMC1

The

ZCR

Figure 9.

signal is a 3-phase voltage zero cross signal. It is the result of a XNOR of the

of each phase. The

is 300 Hz signal. The

ZCR

of each of the three-phases is a 100 Hz signal, so a 3-phase

ZCR

signal is available on the MOP pin only when the STPMC1 works

as a peripheral with the configuration bit APL

ZCR

signal

=0.

ZCR

ZCR

9.6 Period and line voltage measurement (status bits:

LOW, BFF

From voltage channels, a base frequency signal

voltage is rising and it is low when the line voltage is falling, so that,

the sign of dv/dt. With further elaboration, the

A period meter, which is counting up pulses of f

period of voltage channel base frequency and checks if the voltage signal frequency is in the

band going from f

This is done, phase by phase, by means of the signal

and it is used to reset the period meter.

Table 13. Good frequency ranges for different clock source values

4.194 MHz 8.389 MHz 32.0 Hz 128.0 Hz

4.915 MHz 9.830 MHz 37.5 Hz 150.0 Hz

8.192 MHz 8.192 MHz 31.3 Hz 125.0 Hz

9.830 MHz 9.830 MHz 37.5 Hz 150.0 Hz

f

XTAL

If the counted number of f

18

2

equivalent pulses or if the counting is never stopped (no more

base frequency exceeds the lower limit and an error flag

the 8-bit status byte of each phase (see

)

f

MCLK

MCLK

/(2

LIN

is obtained, which is high when the line

ZCR

signal is also produced.

/8 reference signal, measures the

MCLK

18

- 23) ≈ f

freq. min. = f

/8 pulses between two trailing edges of

MCLK

MCLK

/218 to f

MCLK

/216.

MCLK

LIN

, which trailing edge is extracted

/218 freq. max. = f

BFR

Ta bl e 32

).

LIN

signal represents

LIN

is higher than the

LIN

trailing edge), the

is set. This error flag is part of

LIN, BFR

16

/2

MCLK

,

24/77 Doc ID 15728 Rev 6

Page 25

STPMC1 Theory of operation

Figure 10.

If the counted number of f

16

2

equivalent pulses, the base frequency exceeds the upper limit. In this case, such error

must be repeated three times, in order to set the error flag

LIN

and

BFR

behavior when f

/8 pulses between two trailing edges of

MCLK

line

> f

MCLK

/2

16

BFR

, as shown in

LIN

is lower than the

Figure 10

.

The in-band base frequency resets the flag

BFR

. If

BFR

is cleared, the measured period

value is latched, otherwise a default value of period is used as a stable data to compute

frequency needed to adapt the decimation filter and to perform frequency compensation of

reactive energy and RMS current I

The

BFR

flag is also set if the register value of the RMS is too low. In this case also the

status bit

The condition for setting

(U

Xmax

LOW

is set.

LOW

= 212) it means if the UX register drops below 128

the register value goes above 256 (U

in case of non Rogowski current sensor.

X

and consequently

BFR

of each phase is UX < U

LOW

X

> U

Xmax

/16).

BFR

, then, gives also information about

and

BFR

the presence of the line voltage.

When the

BFR

error is set, the computation of power is zero and the energy registers

(active, reactive and fundamental) are blocked, unless single wire mode operation is entered

(see

Section 9.7

).

When the MOP, MON and LED pins are configured to provide the pulsed energy information

they are held low if

The 3-ph status bit

BFR

is set.

BFF

is the OR of each phase bit

BFR

.

9.7 Single wire operation mode: SWM (status bits:

configuration bit FRS

The STPMC1 supports single wire meter (SWM) operation. In this condition, since there is

no voltage information, the current RMS values, instead of the energies, are accumulated in

20-bit dedicated registers located in ACR, ACS, ACT (20-bit accumulator of RMS I

[Ah]).

)

/32

Xmax

are cleared when

NAH, BFR

per hour

X

,

Doc ID 15728 Rev 6 25/77

Page 26

Theory of operation STPMC1

Each ACx register contains a 20-bit accumulator of the relative phase current IX [Ah] and an

8-bit register carrying the information about phase delay between voltage channels.

The SWM mode is indicated by status bit

● Bit

NAH

I

/4096 = 16 (I

Xmax

=0 (SWM on) happens when

= 216). In this case frequency is out of limits and RMS current IX

Xmax

NAH

=0:

BFR

=1 and RMS value of current signal is IX >

is big enough, so it is accumulated in the corresponding ACx phase register.

● Bit

When bit

are blocked. Then, if RMS value of current signal is big enough, bit

NAH

I

/8192 = 8, or

Xmax

current I

BFR

=1 (SWM off) happens if

BFR

=0. In this case either voltage frequency is out of limits but RMS

is too small to enter SWM mode, or voltage frequency is in the correct range.

X

BFR

=1 and RMS value of current signal is IX <

is set, for a certain phase, its energy registers (active, reactive, fundamental)

NAH

is cleared (0) and a

SWM operation is entered. In this case the RMS value of current signal is accumulated in

ACx register and the value of voltage RMS U

is set to zero.

X

Example 1: Single wire operation with SYS = 0

SYS = 0 (3-phase system) is set and in the R-phase the voltage signal is too low

(status bits of phase R

BFR

= 1 and

LOW

= 1).

Because of the too low voltage signal the frequency can't be calculated and energy

registers related to the R-phase are blocked.

If RMS value of current signal is big enough, the device enters SWM and clears

R phase. The ACR register is incremented by adding I

, the RMS value of current

R

NAH

signal.

Example 2: Single wire operation with SYS = 0 and TCS = 1

of

SYS = 0 (3-phase system) and TCS = 1 (CT sensor selection) are set and in all phases

(R, S and T) the voltage signal is too low (status bits

phases).

Because of the too low voltage signal the frequency could not be calculated and all

energy registers are blocked.

Since when TCS

= 1, a frequency value is needed to calculate the RMS value of the

current signal, the default value of 50 Hz or 60 Hz (if bit FRS

value of current signal is big enough, the device enters SWM and clears

phases and ACR, ACS and ACT registers is fed with the correspondent I

The accumulators ACx can be read by means of SPI.

To retrieve energy information, RMS value of current signal accumulated in registers ACx

can be multiplied by a constant representing the value of RMS voltage. This operation must

be executed by a microcontroller.

Usually the supply voltage for the electronic meter is taken from the line voltage. In SWM,

since the line voltage is not present anymore, some other power source must be used in

order to provide the necessary supply to STPMC1 and the other electronic components of

the meter.

9.8 Load monitoring (status bit

The STPMC1 includes in each phase a no-load condition detection circuit with adjustable

threshold. This circuit monitors the voltage and the current channels and, when the

measured voltage is below the set threshold, an internal signal

BFR

= 1 and

LOW

=1) is taken. If the RMS

BIL

, configuration bit LTCH)

BIL

becomes high. The

= 1 for all

NAH

of all

.

X

26/77 Doc ID 15728 Rev 6

Page 27

STPMC1 Theory of operation

information about this signal is also available in the status bit

Ta bl e 32

The three phase status bit

The no-load condition occurs when the product between U

a given value. This value can be set by the LTCH

threshold values can be chosen according to the two LTCH

When a no-load condition occurs (

load condition flag

brought out to the output selector forcing SCLNLC pin low. In peripheral mode, the

signal can be accessed through the SPI interface.

The minimum output frequency (at no-load threshold) is given as % of the full-scale (FS)

output frequency, where FS internal AW frequency is 1370 Hz per phase.

Table 14. No-load detection thresholds

LTCH (2 bits) NLC threshold

).

BIL

BIL

in standalone mode blocks generation of pulses for stepper and is

0 0,00125*FS

1 0,0025*FS

2 0,005*FS

3 0,010*FS

BIL

, one per each phase (see

is the AND of each phase status bit

and IX register values is below

configuration bits. Four different no-load

BIL

= 1) the integration of power is suspended. The no-

X

bits as reported in

BIL

.

Ta bl e 14

BIL

.

Example 3: No-load condition threshold calculation

An energy meter has a power constant of C = 64000 pulses/kWh on LED pin.

It is valid the following relation:

C = 3600000 * f / P

where 3600000 is the factor between kWh and Ws and f is the output frequency on the

LED pin if P power is applied to the meter.

The minimum output frequency if LTCH

f = 0,010 * 1370 Hz = 0,137 Hz

which gives a no-load condition power threshold equal to:

P = 3600000 * 0,137 Hz / 64000imp/kWh = 7,7 W

In this example, the no-load threshold is equivalent to 7,7 W of load or to a start-up

current of 32 mA at 240 V.

In NLC function is also implemented an hysteresis. When the current is falling the threshold

is half lower than that described above.

9.9 Error detection (status bits:

The STPMC1 has two error detection circuits that checks:

● the ΔΣ signals

● the state of output pins

[0] = LTCH [1] = 1 is:

BCF, PIN

)

The first error detection circuit checks if any of the ΔΣ signals from the analog part is stuck at

1 or 0 within the period of observation (250 µs). In case of detected error the corresponding

ΔΣ signal is replaced with an idle ΔΣ signal, which represents a constant value 0. When this

Doc ID 15728 Rev 6 27/77

Page 28

Theory of operation STPMC1

error occurs the correspondent phase bit

again the

The 3-ph status bit

connection of the neutral wire (DAN-I stream).

The other error condition occurs if the MOP, MON and LED pin outputs signals are different

from the internal signals that drive them. This can occur if some of this pin is forced to GND

or to some other imposed voltage value. In this case the internal status bit

immediately activated providing the information that some hardware problem has been

detected, for example the stepper motor has been mechanically blocked.

These two error condition don't influence energy accumulation.

BCF

flag is cleared immediately.

BCF

is the OR of each phase bit BFC, but it takes into account also the

BCF

is set. When the ΔΣ signal becomes correct

9.10 Tamper detection module (status bits:

configuration bit ENH

The tamper detection module is used to prevent theft of energy through improper connection

of the meter. The tamper indicator is activated when:

● sum of currents is above tamper threshold (status bit

● phase sequence is wrong (status bit

● phase active powers don't have the same sign (status bit

● electromagnetic interference (EMI) is detected (only with ENH = 1).

)

BSF

= 1),

PIN

BCS, BSF, BIF

BCS

= 1),

BIF

= 1),

is

,

In standalone application mode (APL

condition.

In 3-phase system (SYS

BCS, BSF, BIF

In other systems (SYS

has been set or if EMI has been detected.

= 0, 1, 2) this output is set if at least one of the internal status bits:

≠ 0, 1, 2) it indicates only

[1] = 1) the SDATD pin is used to notify the tamper

BCS

or EMI.

Example 4: Tamper output on SDATD pin

SYS = 0, 1 or 2 and APL [1] = 1:

BCS

= 0,

BSF

= 0,

BIF

= 0 → Tamper (SDATD pin) = 0

BCS

= 0,

BSF

= 1,

BIF

= 1 → Tamper (SDATD pin) = 1

SYS

= 0, 1 or 2, APL [1] = 1 and ENH = 1:

BCS

= 0,

BSF

= 0,

BIF

= 0, EMI = 0 → Tamper (SDATD pin) = 0

BCS

= 0,

BSF

= 0,

BIF

= 0, EMI = 1 → Tamper (SDATD pin) = 1

BCS

= 1,

BSF

= 1,

BIF

= 1, EMI = 1 → Tamper (SDATD pin) = 1

In peripheral application mode these information can be read out by SPI interface checking

the 3-ph status bits, or the status bits corresponding to each phase.

9.10.1 Sum of currents is above tamper threshold (status bit

Tamper detection through bit

neutral wire). In other measurement systems it is not useful because there are not enough

input current streams.

BCS

is meaningful only for SYS = 0, 2, 5, 6 (systems with

BCS

)

The STPMC1 check tamper detection only if

28/77 Doc ID 15728 Rev 6

Page 29

STPMC1 Theory of operation

I

max

I

>

X

∑

256

Where:

= 2

16

I

max

Σ IX = IR + IS + IT + IN for SYS = 0, 1, 2, 3, 4, 7

Σ I

= IS + IT for SYS = 5, 6

X

Bit

BCS

is set according to

Ta bl e 1 5

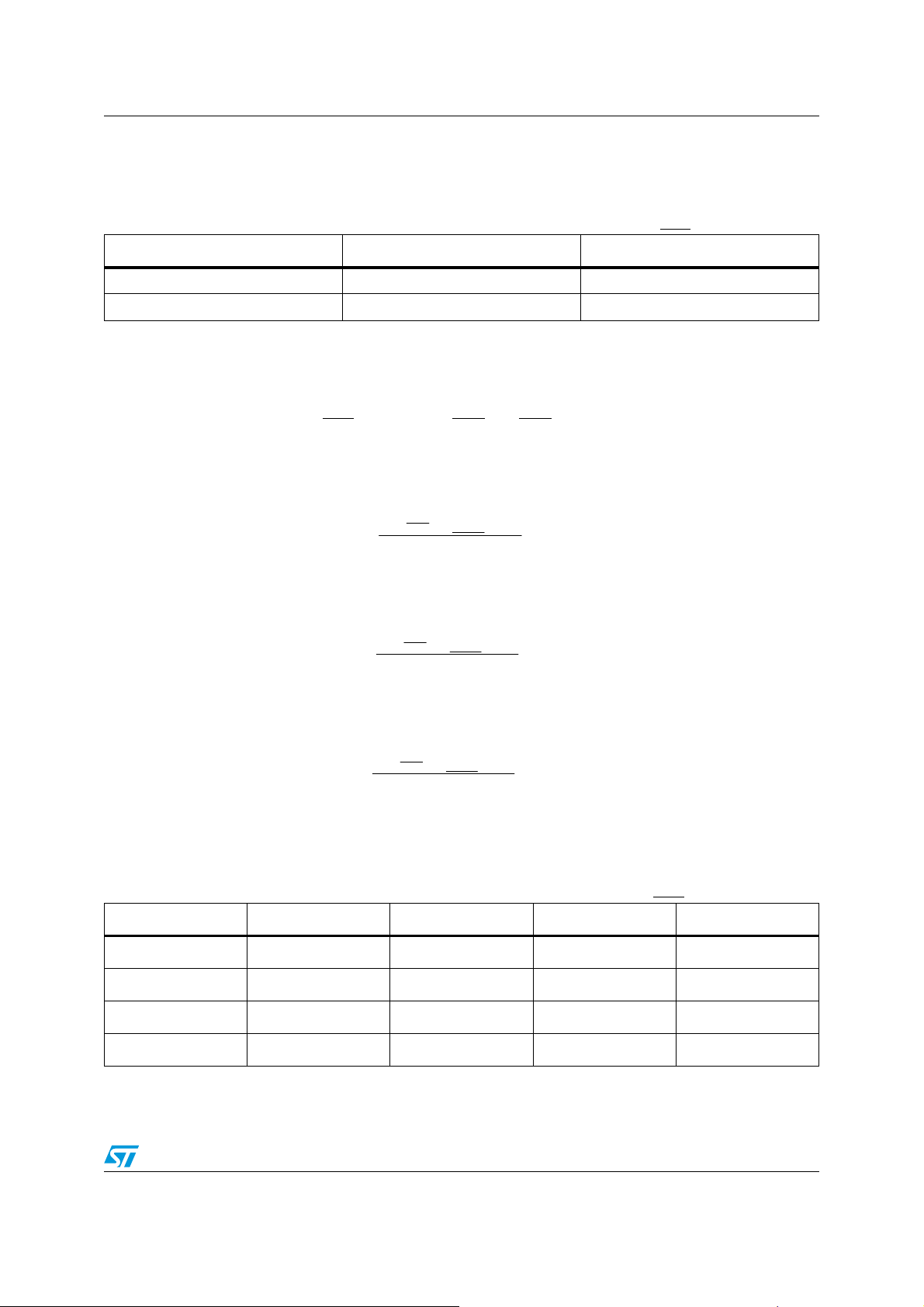

Table 15. Tamper conditions

BCS

0

1

SYS = 0, 1, 2, 3, 4, 7 SYS = 5, 6

I

X

RMS

RMS

∑

<

8

I

X

∑

>

8

RMS

()

i

∑

X

()

i

∑

X

with (Σ iX)

= (iR + iS + iT + iN)

RMS

7

9

7

9

9

I

II

<<

STS

7

9

I

II

>>

STS

7

or

or

or

7

9

7

9

Example 5: 3-ph system - BCS = 0

Let us consider a three-phase, four wires system where the RMS values of the current

applied are:

I

= 5 A

R

I

= 5 A

S

I

= 4.4 A

T

I

= 0 A

N

The sum of all instantaneous currents (i

there is a tamper condition.

The STPMC1 calculates this sum and put its RMS value divided by four (called sIRMS)

into register DMN (see paragraph

This value should always be zero (or very close).

In our case:

9.17.2

+ iS + iT + iN) should always be zero, unless

R

).

9

I

II

<<

TST

7

9

I

II

>>

TST

7

sIRMS

The currents are shown in

i

∑

below.

⎞

X

4

⎟

⎠

RMS

=

A149967.0

⎛

=

⎜

⎝

Figure 11

Doc ID 15728 Rev 6 29/77

Page 30

Theory of operation STPMC1

()

Figure 11. Currents of the three phase system in example

The value I

register (internal value FFFF). It is a function of the sensor type, sensitivity and of the

current channel gain. Let us suppose that

I

= 180 A

MAX

The tamper condition is evaluated only if

This means that the sum of the RMS value of currents is not negligible with respect to

I

(the threshold corresponds to about 0.4% of I

MAX

In this case this is true since:

I

+ IS +IT +IN = 14.4 A > 0,703125 A = I

R

The criterion for tamper detection is

This can also be expressed as

corresponds to the maximum current value hold by each RMS current

MAX

I

MAX

>+++=

IIIII

MAX

/ 256

∑

>

∑

NTSRX

256

).

MAX

I

X

8

i

X

RMS

4

I

X

∑

>=

32

sIRMS

∑

()

i

X

∑

RMS

i

⎞

⎛

X

=

⎜

⎝

∑

⎟

4

⎠

RMS

which means the sIRMS value must not exceed 3.13% of (I

In this example:

sIRMS = 0,149967 < 0.45 = (I

Then BCS = 0.

30/77 Doc ID 15728 Rev 6

+ IS +IT +IN) / 32

R

+ IS +IT +IN).

R

Page 31

STPMC1 Theory of operation

Example 6: 3-ph system - BCS = 1

Let us consider a three-phase, four wires system where:

I

= 5 A

R

I

= 5 A

S

I

= 3.2 A

T

I

= 0 A

N

The tamper is evaluated because

I

+ IS +IT +IN = 13.2 A > 0,703125 A = I

R

MAX

/ 256

In this case

sIRMS = 0,449901 A > 0,4125 A = (I

+ IS +IT +IN) / 32

R

Then BCS = 1.

Example 7: 1-ph system - BCS = 0

Let us consider a single phase systems with only S and T wires connected where

I

= 5 A

S

I

= 4 A

T

I

= 180 A

MAX

In this case the criterion for tamper evaluation is verified since:

(I

+ IT) = 9 A > 0,703125 A = I

S

But BCS = 0 because

7/9 I

= 3.11 A < IS = 5 A < 9/7 IT = 5.14 A

T

and

7/9 I

= 3.88 A < IT = 4 A < 9/7 IS = 6.43 A

S

MAX

/ 256

Example 8: 1-ph system - BCS = 1

Let us consider the case in which:

I

= 5 A

S

I

= 3 A

T

I

= 180 A

MAX

Also in this case the criterion for tamper evaluation is verified:

(I

+ IT) = 8 A > 0,703125 A = I

S

MAX

/ 256

Now BCS = 1 because

7/9 I

= 3.88 A > IT = 3 A

S

9.10.2 Phase sequence is wrong (status bit

One tamper condition is that phase sequence is not correct. A 3-ph phase status bit

checks the sequence of phases, which, in a three phase system is one of the following:

● R → S → T

● S → T → R

● T → R → S

In one of the above cases

BSF

is cleared, otherwise bit

BSF

)

BSF

BSF

is set.

Doc ID 15728 Rev 6 31/77

Page 32

Theory of operation STPMC1

Whatever the SYS bits setting (indicating phases presence and configuration), bit

always calculated, but it is valid only in cases SYS

three phase voltage signals (u

In cases SYS

is 4, 5, 6, 7, only two or one voltage signal are available (uS and/or uT), so that

the sequence cannot be checked. Bit

, uS, uT) are available and can be checked, as shown in 0.

R

BSF

is always set in the status byte, but it must be

is 0, 1, 2 and 3. In fact in this case all the

BSF

is

ignored.

In standalone application for SYS

= 0, 1 or 2 (3-phase systems) bit

BSF

is available as

output on SDATD pin.

Table 16. Pin description versus SYS configuration (uX and iX represent the voltage and the

current signals)

SYS

Pin01234567

DAR u

DAS u

DAT u

DAN i

DAR i

DAS i

DAT i

R

S

T

N

R

S

T

u

R

u

S

u

T

-------

i

R

i

S

i

T

u

R

u

S

u

T

i

R

i

S

i

T

u

R

u

S

u

T

i

R

-iSi

i

T

----

u

S

u

T

----

i

T

---

u

T

S

i

T

u

T

i

S

i

T

u

T

-

i

T

9.10.3 Phase active powers do not have the same sign (status bit

The 3-phase status bit

equal in all three phases (R, S and T), then bit

In a standalone application for SYS

output on SDATD pin.

Example 9: status bit

SIGN

SIGN

SIGN

SIGN

= 0,

R

= 1,

R

= 1,

R

= 0,

R

SIGN

SIGN

SIGN

SIGN

BIF

is produced from status bit

= 0, 1 or 2 (3-phase system) bit

BIF

= 0,

SIGN

S

= 1,

S

= 0,

S

= 1,

S

SIGN

SIGN

SIGN

= 0 →

T

= 1 →

T

= 0 →

T

= 0 →

T

BIF

BIF

BIF

BIF

BIF

= 0

= 0

= 1

= 1

SIGN

is set.

of each phase. If bit

BIF

is available as

9.10.4 EMI is detected

EMI tamper detection is enabled by configuring bits ENH = 1 and APL [1] = 1 (APL [1] sets

standalone application mode).

The DAH signal is checked to verify that:

● its DC component does not exceed DC

● its RMS value does not exceed the maximum value RMS

where DC

MAX

= RMS

= 216 with hysteresis.

MAX

If these condition are not verified the EMI tamper is detected.

MAX

/16

MAX

/16

BIF

)

SIGN

is not

32/77 Doc ID 15728 Rev 6

Page 33

STPMC1 Theory of operation

EMI tamper condition is not available as internal status signal, but it is available (in OR with

other tamper conditions) on the SDATD pin of the device.

In peripheral application mode it is possible to detect EMI tamper comparing the value of the

16-bit DCuN and of the 12-bit RMSuN to the threshold through a microcontroller.

9.11 Energy to frequency conversion (configuration bits: APL,

KMOT

The STPMC1 provides energy to frequency conversion both for calibration and energy

readout purposes.

The three hard-wired xDSP, implemented as four 2-channel ΔΣ signal processors perform all

calculations and produce output data and signals. Inside them, each three stage decimation

filter inputs a filtered ΔΣ signal and its integral as parallel bus or stream to the power and

RMS computer. All three streams of power (active, reactive and active from the fundamental

harmonic) are connected to the corresponding integrators.

Within the integrators, all three powers are accumulated into energies of 20-bit values

according to configuration bit ABS

frequency of which is proportional to the accumulated energies. Each of these signals can

be brought out to the LED pin.

, LVS, FUND)

and the results are converted into pulse train signals, the

Due to the innovative and proprietary power calculation algorithm the frequency signal is not

affected by any ripple at twice the line frequency. This feature strongly reduces the

calibration time of the meter.

Through calibration the meter is configured to provide a certain number of pulses per kWh

(referred to as power meter constant C) on the LED pin. According to the APL

and FUND

as shown in paragraphs

configuration bits, the frequency of LED signal can provide different information,

9.12

Given C, the number of pulses per kWh provided, the relationship between the LSB value of

the source energy registers and the number of pulses provided to LED pin is indicated in the

table below:

Table 17. Energy registers LSB value

Register SYS = 0, 1, 2, 4, 5, 6, 7 SYS = 3

3-ph active energy wide band (P)

3-ph reactive energy wide band (Q)

3-ph active energy fundamental (F)

and

9.13

.

1000

------------- ----

K

P

⋅

C2

1000

-----------------

K

Q

⋅

C2

1000

------------ -----

K

F

⋅

C2

, KMOT, LVS

1000

------------- ----

Wh[]=

10

Varh[]=

10

Wh[]=

10

K

P

C2

1000

------------- --

K

Q

C29⋅

------------- --

K

F

C2

⋅

1000

⋅

Wh[]=

10

Varh[]=

Wh[]=

9

3-ph reactive energy fundamental (R)

1000

------------ -----

K

R

C210⋅

Varh[]=

1000

------------ ---

K

R

⋅

C2

Varh[]=

9

Doc ID 15728 Rev 6 33/77

Page 34

Theory of operation STPMC1

Example 10: energy registers LSB value for SYS = 0, 1, 2, 4, 5, 6, 7

C = 64000 pulses/kWh = 17.7 Hz*kW

K

= KF = 15.258 *10-6 Wh

P

K

= KR = 15.258 *10-6 VArh

Q

This means that the reading of 0x00001 in the active energy register represents 15.258

µWh, while 0xFFFFF represents 16 Wh.

Example 11: Energy registers LSB value for SYS = 3

C = 64000 pulses/kWh = 17.7 Hz*kW

K

= 15.258 *10-6 Wh

P

K

= 30.517 *10-6 Wh

F

K

= KR = 30.517 *10-6 VArh

Q

From 3-phase active energy wide band signal the stepper driving signals

(output from MOP and MON pins) are generated. The frequency of these signals can be

configured as shown in paragraph

9.13

.

MA

and MB

9.12 Using STPMC1 in microcontroller based meter - peripheral

operating mode (configuration bits: APL

, KMOT, LVS, FUND)

The higher flexibility of the STPMC1 allows its use in microcontroller based energy meters.

In this case the STPMC1 must be programmed to work in peripheral mode setting bit APL

[1] = 0. All the SPI pins (SCS, SCLNCL, SDATD, SYN) are used only for communication

purposes, allowing the microcontroller to write and read the internal STPMC1 registers.

The peripheral mode has two further different configuration modes according to the status of

the APL

described below.

APL

In the MOP pin, the

The pin MON provides the WatchDOG signal. The DOG signal generates a 16 ms long

positive pulse every 1.6 seconds. Generation of these pulses can be suspended if data are

read in intervals shorter than 1.6 ms. The DOG signal is actually a watchdog reset signal

that can be used to control an operation of an on-board microcontroller. It is set to high

whenever the V

run.

It is expected that an application microcontroller should access the data in the metering

device on regular basis, at least 1/s (recommended is 32/s). Every latching of results in the

metering device requested from the microcontroller also resets the watchdog. If latching

requests does not follow each other within 1.6 second, an active high pulse on MON is

produced, because device assumes that microcontroller does not operate properly. This

signal can be either control the RESET pin of the microcontroller or it can be tied to some

interrupt pin. The second chance is recommended for a battery backup application which

can enter some sleep mode due to power down condition and should not be reset by

metering device.

configuration bit, which changes the function of MOP, MON and LED pins as

= 0:

ZCR

signal is available (see paragraph

voltage is below 2.5 V, but after VCC goes above 2.5 V this signal starts to

CC

9.5

for details on

ZCR

signal);

The LED pin can be configured through LVS

signals, as shown in the table below.

34/77 Doc ID 15728 Rev 6

, FUND and KMOT to output different energy

Page 35

STPMC1 Theory of operation

Table 18. LED pin configuration for APL

LV S (1 bit) FUND (1 bit) KMOT (2 bits) LED energy output Phase Freq

0

1R

00

2S

3T

0

1R

01

2S

3T

0

1R

10

2S

3T

0

1R

11

2S

= 0

3-ph

Active energy wide band P

3-ph

Active energy fundamental F

3-ph

Reactive energy wide band Q

3-ph

Reactive energy fundamental R

C

(1)

C

C

C

3T

1. C is the number of pulses per kWh set with calibration.

APL = 1:

MOP/MON provides stepper motor driving signals from 3-phase active energy wide band

register with frequency CM related to C (number of pulses on LED pin, see par.

according to

LED pin provides 3-phase energy pulses according to

to KMOT

.

Ta bl e 20

.

Ta bl e 19

with frequency C not related

Table 19. LED pin configuration for APL = 1

LV S (1 bit) FUND (1 bit) LED energy output Phase Freq

0 0 Active energy wide band P

0 1 Active energy fundamental F

1 0 Reactive energy wide band Q

1 1 Reactive energy fundamental R

3-ph C

9.13 Driving a stepper motor - standalone operating mode

(configuration bits: APL

, LVS, KMOT)

9.11

)

When used in standalone mode (APL[1] = 1), the STPMC1 is able to directly drive a stepper

motor.

Doc ID 15728 Rev 6 35/77

Page 36

Theory of operation STPMC1

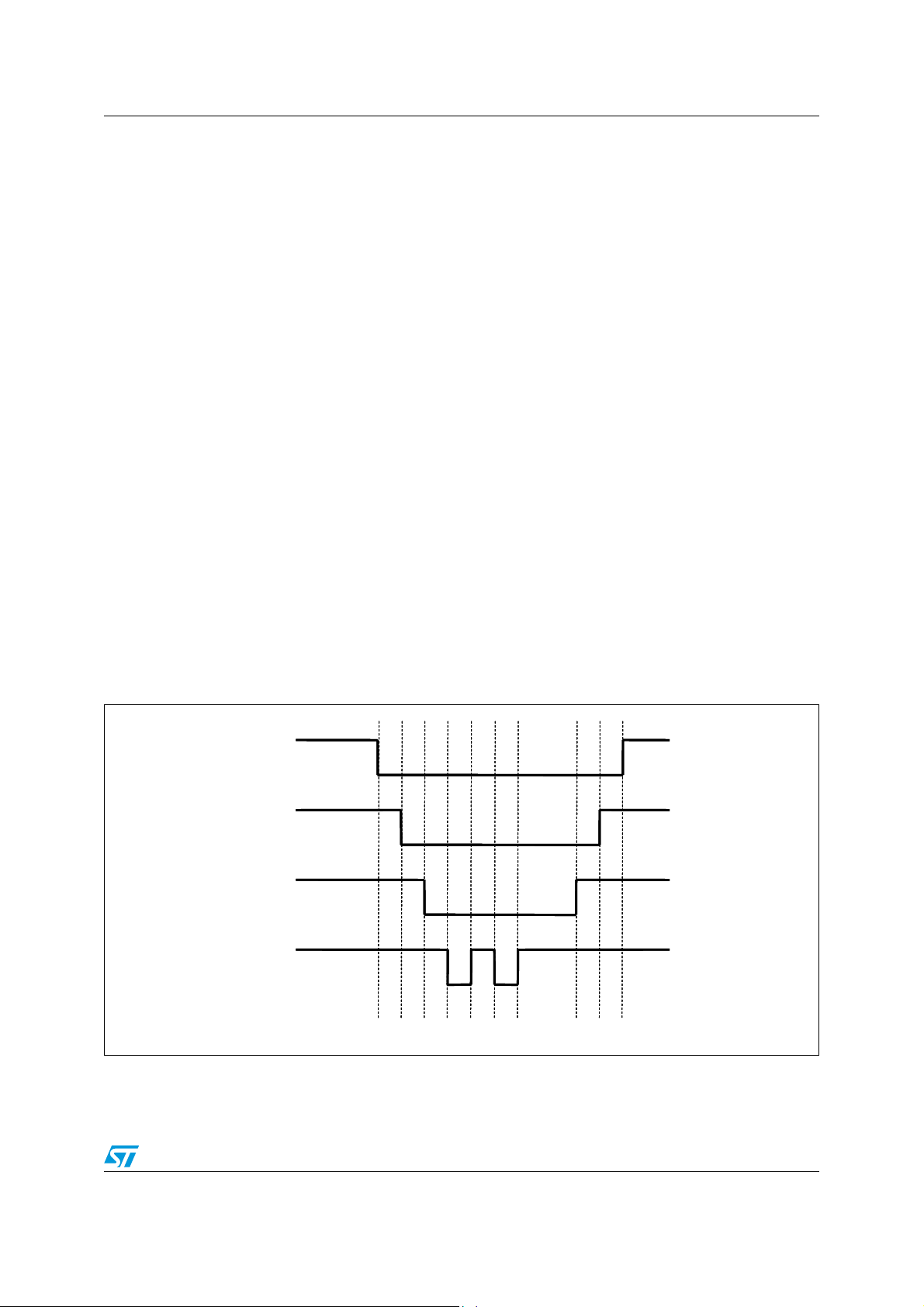

From signal PΣ (3-ph active energy), stepper motor driving signals MA and MB (see

Figure 12

) are generated by means of internal divider, mono-flop and decoder and brought

to MOP and MON pins.

Figure 12. Stepper driving signals

Hi

Hi

MON

MON

Low

Low

Hi

Hi

MOP

MOP

Low

Low

The numbers of pulses per kWh on MOP and MON outputs (CM) is related to the number of

pulses on LED pin (C, see par.

9.11

) following the table below.