Programmable single-phase energy metering IC

Features

■ Measures active, reactive, and apparent

energies

■ Current, voltage RMS and instantaneous

measurement

■ Frequency measurement

■ Ripple-free active energy pulsed output

■ Live and neutral monitoring for tamper

detection

■ Fast and simple one-point digital calibration

over the whole current range

■ Integrated linear voltage regulators for digital

and analog supply

■ Selectable RC or crystal oscillator

■ Supports 50 - 60 Hz - IEC62052-11, IEC62053-

2x specifications

■ Less than 0.1% error in the 1000:1 range

■ Precision voltage reference: 1.23 V with 30

ppm/°C max

Description

The STPM10 is designed for effective

measurement of active, reactive and apparent

energy in a power line system using current

transformer and shunt sensors. The device can

be implemented for peripheral measurement in a

microcontroller-based single-phase or poly-phase

energy meter. The STPM10 consists of two main

sections: analog and digital. The analog part is

composed of preamplifier and first-order sigmadelta A/D converter blocks, a band-gap voltage

reference and low-drop voltage regulator. The

digital part is composed of system control,

oscillator, hard-wired DSP and SPI interface.

There is also an internal volatile memory, which is

Table 1. Device summary

STPM10

with tamper detection

TSSOP20

controlled through the SPI by means of a

dedicated command set. The configured bits are

used for configuration and calibration purposes.

From a pair of sigma-delta output signals

produced by the analog section, the DSP unit

computes the amount of active, reactive and

apparent energy consumed, as well as the RMS

and instantaneous voltage and current values.

The results of the computation are available as

pulse frequencies and states on the digital

outputs of the device, or as data bits in a data

stream, which can be read from the device by

means of the SPI interface. The system bus

interface is also used for temporary programming

of bits of internal volatile memory. The STPM10

generates an output signal with a pulse frequency

proportional to the energy, and this signal is used

in the calibration phase of the energy metering

application.

Order code Temperature range Package Packaging

STPM10BTR - 40 to 85 °C TSSOP20 (tape and reel) 2500 parts per reel

June 2011 Doc ID 17728 Rev 3 1/51

www.st.com

51

Contents STPM10

Contents

1 Schematic diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

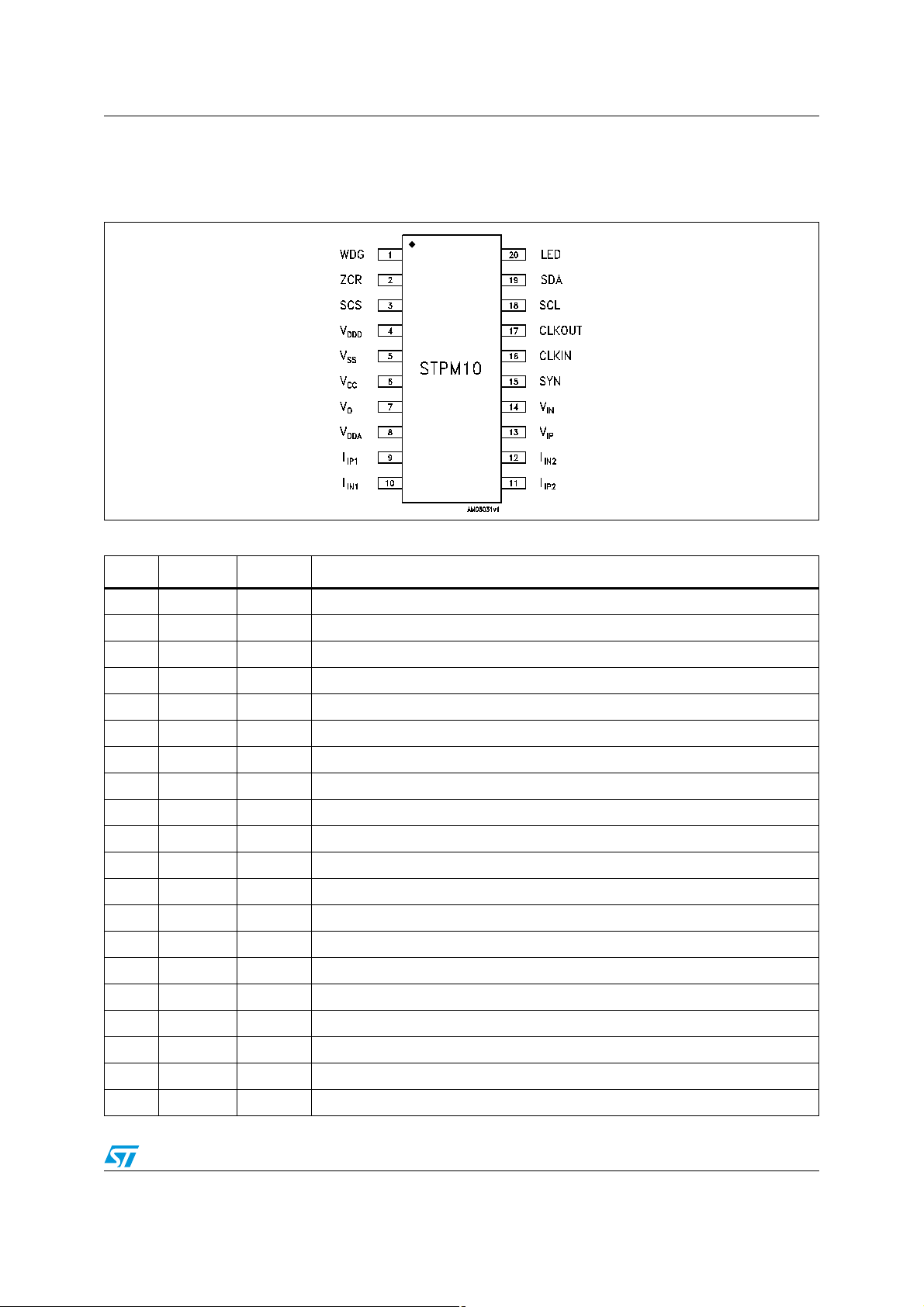

2 Pin configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

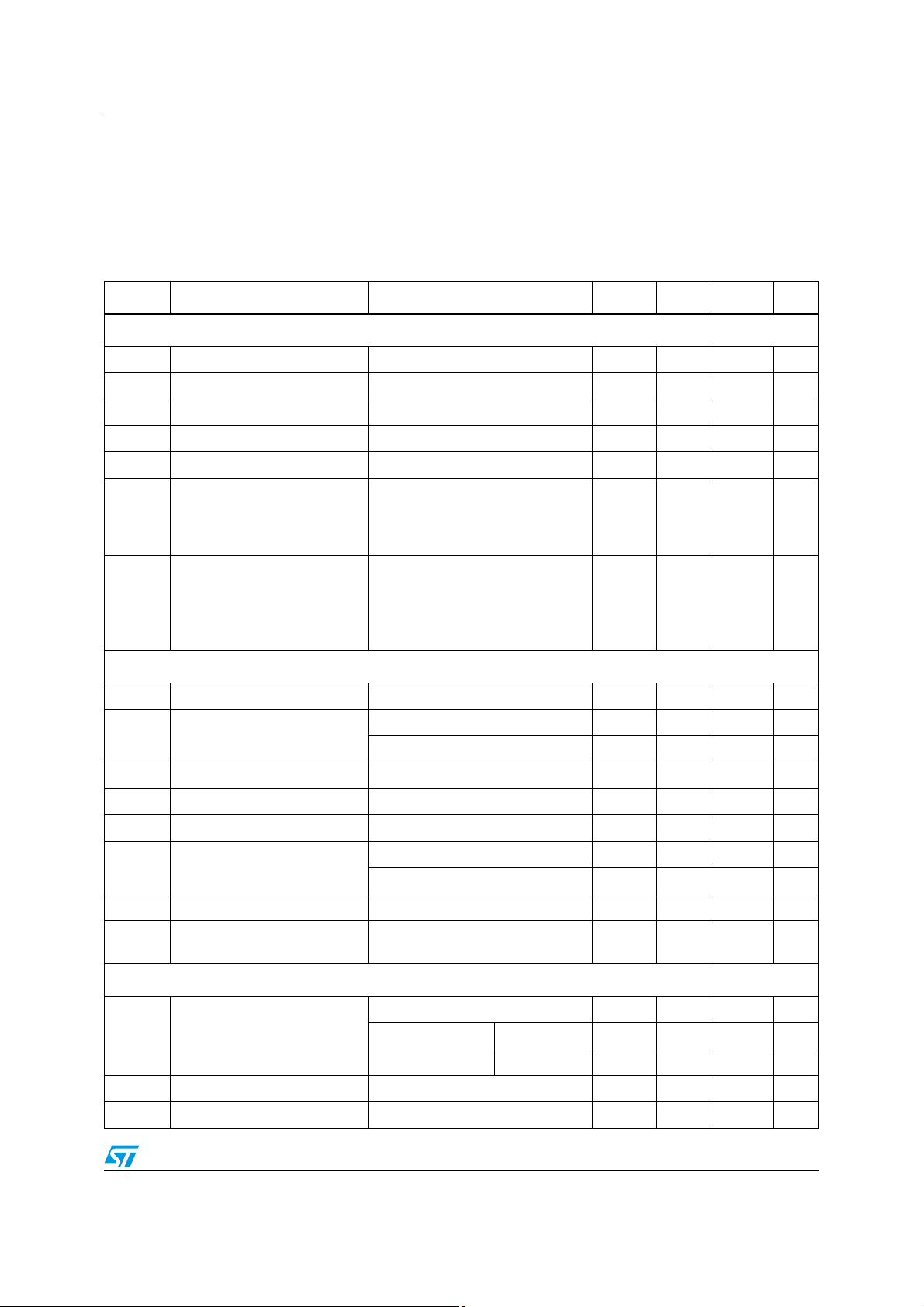

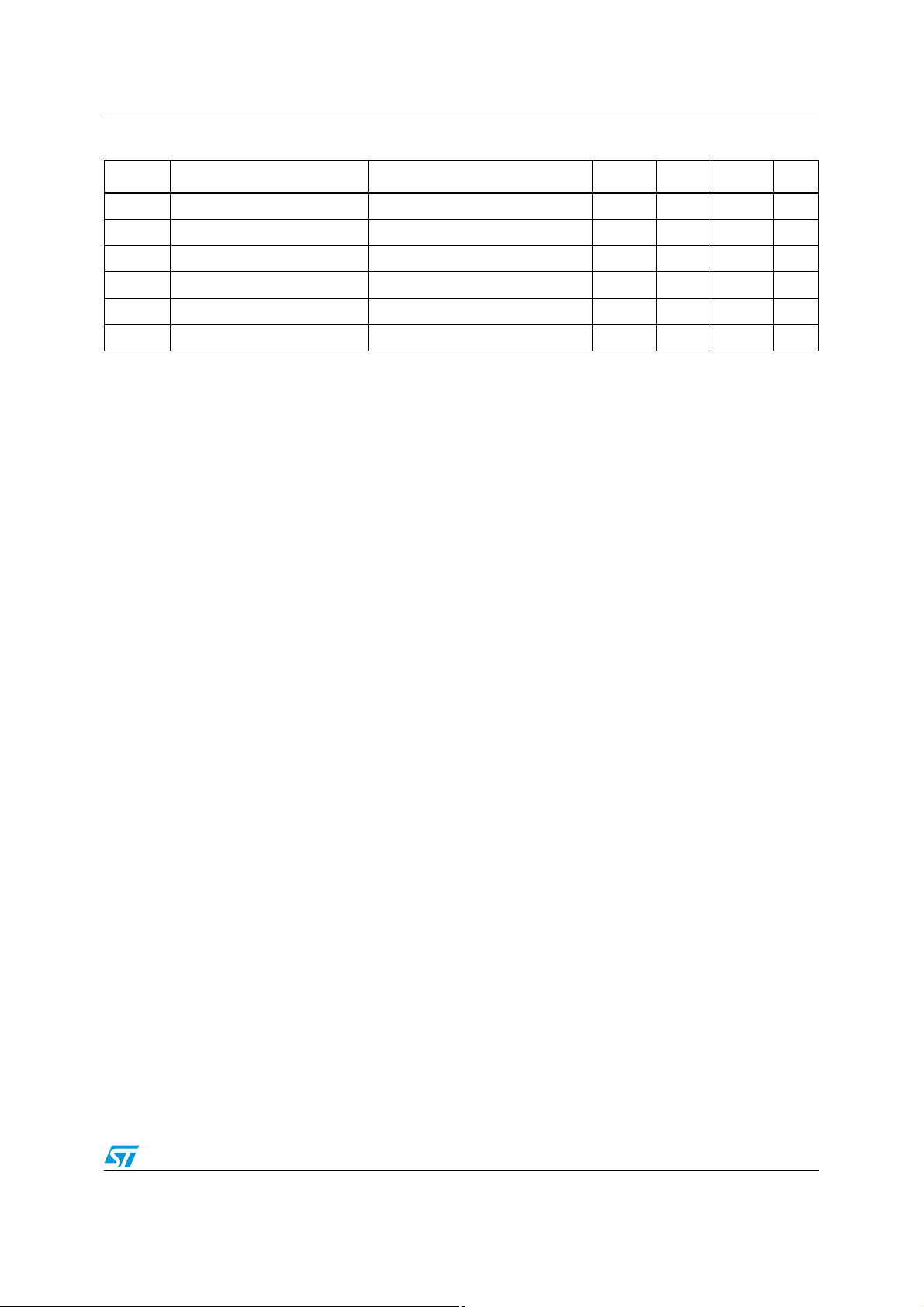

3 Maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

4 Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

5 Terminology . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

5.1 Measurement error . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

5.2 ADC offset error . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

5.3 Gain error . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

5.4 Power supply DC and AC rejection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

5.5 Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

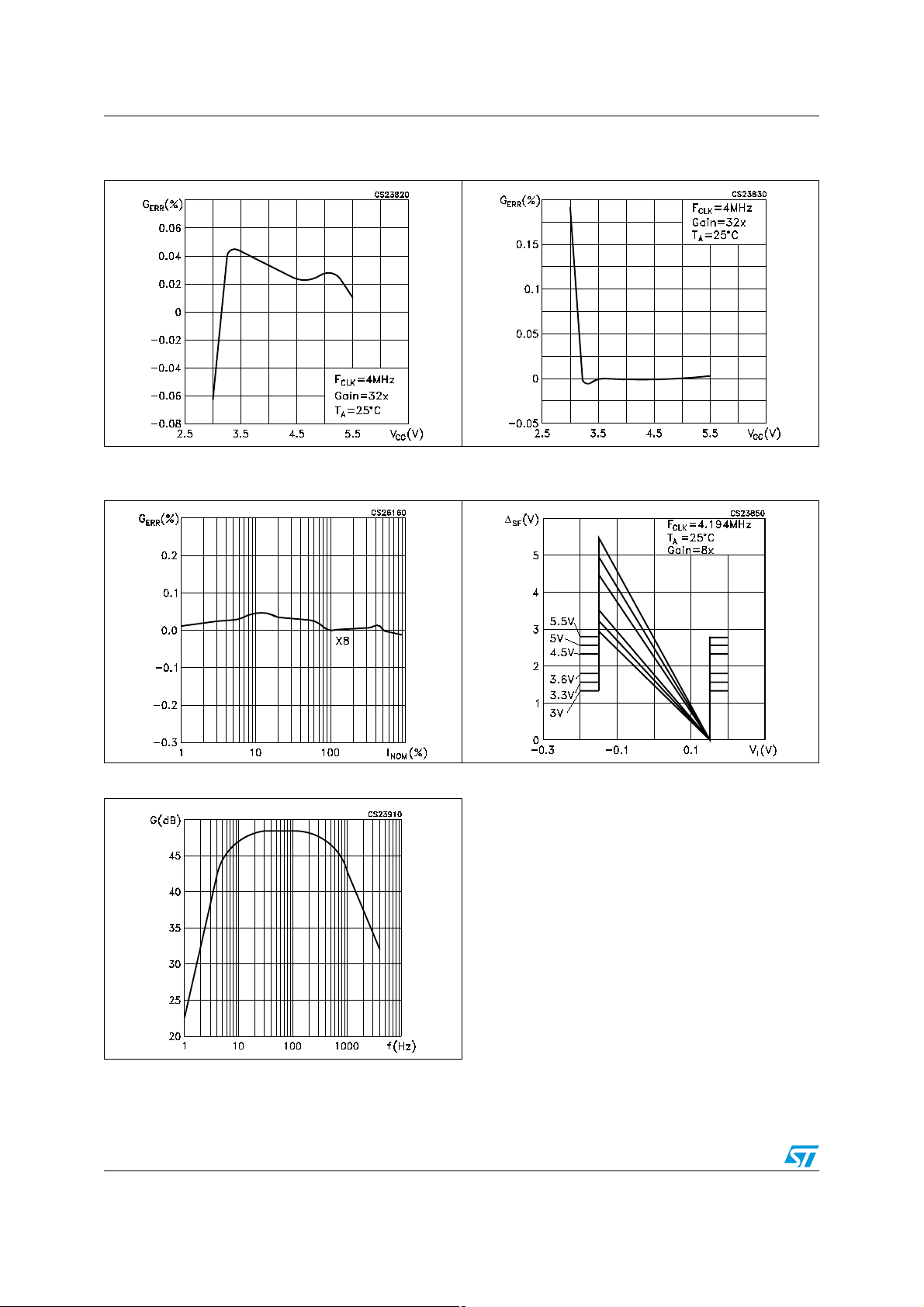

6 Typical performance characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

7 Theory of operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

7.1 General operation description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

7.2 Analog inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

7.3 ΣΔ A/D converters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

7.4 Zero-crossing detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

7.5 Period and line voltage measurement . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

7.6 Power supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

7.7 Load monitoring . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

7.8 Error detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

7.9 Tamper detection module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

7.9.1 Detailed operational description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

7.10 Phase compensation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

7.11 Clock generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

7.11.1 RC startup procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

7.12 Resetting the STPM10 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

7.13 Using the STPM10 in microcontroller-based meters . . . . . . . . . . . . . . . . 24

2/51 Doc ID 17728 Rev 3

STPM10 Contents

7.14 Energy to frequency conversion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

7.15 Status bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

7.16 Programming the STPM10 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

7.16.1 Data records . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

7.17 Configuration bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

7.18 Mode signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

7.19 SPI interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

7.20 Remote reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

7.21 Reading data records . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

7.22 Writing procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

7.22.1 Interfacing the standard 3-wire SPI with the STPM10 SPI . . . . . . . . . . 36

7.23 Energy calculation algorithm . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

7.23.1 Active power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

7.23.2 Reactive power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

7.23.3 Apparent power and RMS values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

7.24 STPM10 calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

8 Application design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

9 Package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

10 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Doc ID 17728 Rev 3 3/51

List of tables STPM10

List of tables

Table 1. Device summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Table 2. Pin description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Table 3. Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Table 4. Thermal data. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Table 5. Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Table 6. Gain of voltage and current channels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Table 7. Configuration of current sensors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Table 8. No-load detection thresholds . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Table 9. LED pin configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Table 10. Status bit description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Table 11. Configuration bit map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Table 12. Mode signal description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Table 13. Working point settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Table 14. Device constants . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Table 15. Resistor divider ratio . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Table 16. Current channel typical components . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Table 17. Footprint data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Table 18. Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

4/51 Doc ID 17728 Rev 3

STPM10 List of figures

List of figures

Figure 1. Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Figure 2. Pin connections (top view) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Figure 3. Supply current vs. supply voltage, T

Figure 4. RC oscillator frequency vs. V

CC

Figure 5. RC oscillator: frequency jitter vs. temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Figure 6. Analog voltage regulator: line - load regulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Figure 7. Digital voltage regulator: line - load regulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Figure 8. Voltage channel linearity at different V

Figure 9. Power supply AC rejection vs. V

Figure 10. Power supply DC rejection vs. V

Figure 11. Error over dynamic range gain dependence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Figure 12. Primary current channel linearity at different V

Figure 13. Gain response of ΔΣ A/D converters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Figure 14. First-order ΣΔ A/D converter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Figure 15. ZCR signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Figure 16. LIN and BFR signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Figure 17. Band-gap temperature variation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Figure 18. Timings of tamper module - Primary channel selected. . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Figure 19. Timings of tamper module - Secondary channel selected . . . . . . . . . . . . . . . . . . . . . . . . . 22

Figure 20. Different oscillator circuits with (a) quartz, (b) internal oscillator, (c) external source . . . . . 23

Figure 21. STPM10 data records map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Figure 22. Timing for providing remote reset request . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Figure 23. Data record reconstruction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Figure 24. Timing for data record reading . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Figure 25. Timing for writing configuration and mode bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Figure 26. Active energy computation diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Figure 27. STPM10 reference schematic with one current transformer and one shunt. . . . . . . . . . . . 45

Figure 28. TSSOP20 footprint recommended data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

= 25 °C (f = 4.194 MHz, 8.192 MHz). . . . . . . . . . . . 13

A

, R = 12 kΩ, TA = 25 °C . . . . . . . . . . . . . . . . . . . . . . . . . . 13

voltages. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

CC

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

CC

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

CC

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

CC

Doc ID 17728 Rev 3 5/51

Schematic diagram STPM10

1 Schematic diagram

Figure 1. Block diagram

VCC

VIP

VIN

IIN1

IIP2

IIN2

VSS

VDDA VDDD

Voltage Ref

+

4

-

Gain: 8-32

IIPI

+

-

Gain: 8-32

ΔΣ A/D

Tamper

Linear Vregs

ΔΣ A/D

φ

VO

56-bit

Configurators

DSP

Energies

and

RMS Values

Energy to Freq

Converters

LED

WDG

+

-

Registers

Oscillator

and

SPI Interface

SDA/TDSYNSCSSCL/NCCLKOUTCLKIN

ZCR

AM00176v1

6/51 Doc ID 17728 Rev 3

STPM10 Pin configuration

2 Pin configuration

Figure 2. Pin connections (top view)

Table 2. Pin description

Pin Symbol Type

(1)

1 WDG D O Watchdog

2 ZCR D O Zero-crossing signal

3 SCS D IN SPI interface Enable pin

4V

5V

6V

7V

8V

9I

10 I

11 I

12 I

13 V

14 V

DDD

SS

CC

O

DDA

IP1

IN1

IP2

IN2

IP

IN

A OUT 1.8 V output of internal low drop regulator which supplies the digital core

GND Ground

P IN Supply voltage

P OUT Output of internal low drop regulator

A OUT 3 V output of internal low drop regulator which supplies the analog part

A IN Positive input of primary current channel

A IN Negative input of primary current channel

A IN Positive input of secondary current channel

A IN Negative input of secondary current channel

A IN Positive input of voltage channel

A IN Negative input of voltage channel

15 SYN D I/O SPI interface pin

Description

16 CLKIN A IN Crystal oscillator input

17 CLKOUT A OUT Crystal oscillator output

18 SCL D I/O SPI interface clock pin

19 SDA D I/O SPI interface data pin

20 LED D O Active energy pulsed output

1. A: analog, D: digital, P: power

Doc ID 17728 Rev 3 7/51

Maximum ratings STPM10

3 Maximum ratings

Table 3. Absolute maximum ratings

Symbol Parameter Value Unit

V

I

V

V

CC

PIN

ID

IA

DC input voltage -0.3 to 6 V

Current on any pin (sink/source) ± 150 mA

Input voltage at digital pins (SCS, ZCR, WDG, SYN, SDA,

SCL, LED)

Input voltage at analog pins (I

IP1

, I

, I

, I

IN1

, VIP, VIN) -0.7 to 0.7 V

IP2

IN2

-0.3 to V

+ 0.3 V

CC

ESD Human body model (all pins) ± 3.5 kV

T

T

OP

T

J

STG

Operating ambient temperature - 40 to 85 °C

Junction temperature - 40 to 150 °C

Storage temperature range - 55 to 150 °C

Note: Absolute maximum ratings are those values beyond which damage to the device may occur.

Functional operation under these condition is not implied.

Table 4. Thermal data

Symbol Parameter Value Unit

R

thJA

1. This value is based on a single-layer PCB, JEDEC standard test board.

Thermal resistance junction-to-ambient 114.5

(1)

°C/W

8/51 Doc ID 17728 Rev 3

STPM10 Electrical characteristics

4 Electrical characteristics

VCC = 5 V, TA = 25 °C,100 nF to 1 µF between V

and V

Table 5. Electrical characteristics

, 100 nF to 1 µF between VCC and VSS unless otherwise specified.

SS

and VSS, 100 nF to 1 µF between V

DDA

Symbol Parameter Test conditions Min. Typ. Max. Unit

Energy measurement accuracy

f

e

e

e

Effective bandwidth Limited by digital filtering (-3 dB) 4 800 Hz

BW

Accuracy of active power Over 1 to 1000 of dynamic range 0.1 %

AW

Accuracy of reactive power Over 1 to 1000 of dynamic range 0.1 %

RW

Accuracy of apparent power Over 1 to 500 of dynamic range 0.1 %

SW

SNR Signal-to-noise ratio Over the entire bandwidth 52 db

PSRR

Power supply DC rejection

DC

Voltage signal: 200 mV

Current signal: 10 mV

f

= 4.194 MHz

CLK

rms

rms

/50Hz

/50Hz

0.2 %

VCC=3.3V±10%, 5V±10%

PSRR

Power supply AC rejection

AC

Voltage signal: 200 mV

Current signal: 10 mV

f

= 4.194 MHz

CLK

=3.3 V+0.2 V

V

CC

VCC=5.0 V+0.2 V

rms

rms

/50 Hz

rms

/50 Hz

rms

1@100 Hz

1@100 Hz

0.1 %

General section

DDD

V

I

Operating supply voltage 3.165 5.5 V

CC

Supply current. Configuration

CC

registers cleared

POR Power on reset on V

V

V

f

CLK

f

LINE

I

LATCH

Analog inputs (I

V

f

ADC

f

SPL

Analog supply voltage 2.85 3.00 3.15 V

DDA

Digital supply Voltage 1.725 1.80 1.875 V

DDD

Oscillator clock frequency

Nominal line frequency 45 65 Hz

Current injection latch-up

immunity

, I

IP1

IN1

Maximum input signal levels

MAX

A/D converter bandwidth 10 kHz

A/D sampling frequency F

4 MHz; V

8 MHz; V

CC

=5 V 3 4 mA

CC

=5 V 5 6 mA

CC

2.5 V

MDIV bit=0 4.000 4.194 MHz

MDIV bit=1 8.000 8.192 MHz

300 mA

, I

, I

, VIP, VIN)

IP2

IN2

Voltage channel -0.3 +0.3 V

Gain 8X -0.15 +0.15 V

Current channels:

Gain 32X -0.035 +0.035

/4 Hz

CLK

Doc ID 17728 Rev 3 9/51

Electrical characteristics STPM10

Table 5. Electrical characteristics (continued)

Symbol Parameter Test conditions Min. Typ. Max. Unit

V

Z

Z

G

I

Amplifier offset ±20 mV

OFF

VIP, VIN impedance

IP

I

, I

, I

, I

IN

IP1

IN1

Current channels gain error ±10 %

ERR

Voltage channel leakage

VL

current

IP2

impedance

IN2

Over the total operating voltage

range

Over the total operating voltage

range

Channel disabled (PST=0 to 1

Current channel leakage

I

IL

current

CH2 disabled if CSEL=0; CH1

disabled if CSEL=1) or device off

Input enabled -10 10 µA

Digital I/O Characteristics (SDA, CLKIN, CLKOUT, SCS, SYN, LED)

SDA, SCS, SYN, LED 0.75V

V

Input high voltage

IH

CLKIN 1.5

SDA, SCL, SYN, LED 0.25V

V

V

V

I

t

Input low voltage

IL

Output high voltage IO=-2 mA VCC-0.4 V

OH

Output low voltage IO=+2 mA 0.4 V

OL

Pull up current 15 µA

UP

Transition time C

TR

CLKIN 0.8

=50 pF 10 ns

LOAD

Crystal oscillator (see circuit Figure 19)

100 400 kΩ

100 kΩ

-1 1 µA

-1 1 µA

CC

CC

V

V

I

Input current on CLKIN 1 µA

I

R

External resistor 1 4 MΩ

P

Cp External capacitors 22 pF

4.00 4.194

f

CLK

I

CLKIN

R

t

Nominal output frequency

8.00 8.192

Settling current f

Settling resistor 12 kΩ

SET

Frequency jitter 1 ns

JIT

= 4 MHz 40 60 µA

CLK

On chip reference voltage

Reference voltage 1.23 V

V

REF

Reference accuracy ±1 %

Temperature coefficient After calibration 30 50

T

C

SPI interface timing

F

SCLKr

Data read speed After calibration 32 MHz

10/51 Doc ID 17728 Rev 3

MHz

ppm/

°C

STPM10 Electrical characteristics

Table 5. Electrical characteristics (continued)

Symbol Parameter Test conditions Min. Typ. Max. Unit

F

SCLKw

t

t

DH

t

ON

t

OFF

t

SYN

Data write speed 100 kHz

Data setup time 20 ns

DS

Data hold time 0 ns

Data driver on time 20 ns

Data driver off time 20 ns

SYN active width 2/f

CLK

s

Doc ID 17728 Rev 3 11/51

Terminology STPM10

5 Terminology

5.1 Measurement error

The error associated with the energy measurement made by the STPM10 is defined as:

Percentage error = [STPM10 (reading) - true energy] / true energy

5.2 ADC offset error

This is the error due to the DC component associated with the analog inputs of the A/D

converters. Due to the internal automatic DC offset cancellation, the STPM10 measurement

is not affected by DC components in the voltage and current channel. The DC offset

cancellation is implemented in the DSP.

5.3 Gain error

The gain error is gain due to the signal channel gain amplifiers. This is the difference

between the measured ADC code and the ideal output code. The difference is expressed as

percentage of the ideal code.

5.4 Power supply DC and AC rejection

This parameter quantifies the STPM10 measurement error as a percentage of the reading

when the power supplies are varied. For the PSRRAC measurement, a reading at two

nominal supply voltages (3.3 and 5 V) is taken. A second reading is obtained with the same

input signal levels when an AC (200 mV

Any error introduced by this AC signal is expressed as a percentage of the reading. For the

PSRRDC measurement, a reading at two nominal supply voltages (3.3 and 5 V) is taken. A

second reading is obtained with the same input signal levels when the supplies are varied ±

10%. Any error introduced is again expressed as a percentage of the reading.

/100 Hz) signal is introduced on the supplies.

RMS

5.5 Conventions

The lowest analog and digital power supply voltage is called VSS, which represents system

ground (GND). All voltage specifications for digital input/output pins are referred to GND.

Positive currents flow into a pin. Sinking current refers to the current flowing into the pin, and

thus it is positive. Sourcing current means that the current is flowing out of the pin, so it is

negative.

Timing specifications of signals treated by the digital control part are relative to CLKOUT.

This signal is provided by the 4.194 MHz nominal-frequency crystal oscillator or from the

internal RC oscillator. An external source of 4.194 MHz or 8.192 MHz can also be used.

Timing specifications of signals from the SPI interface are relative to the SCL, and there is

no direct relationship between the clock (SCL) of the SPI interface and the clock of the DSP

block. A positive logic convention is used in all equations.

12/51 Doc ID 17728 Rev 3

STPM10 Typical performance characteristics

6 Typical performance characteristics

Figure 3. Supply current vs. supply voltage,

T

= 25 °C (f = 4.194MHz, 8.192MHz)

A

Figure 5. RC oscillator: frequency jitter vs.

temperature

Figure 4. RC oscillator frequency vs. V

R = 12 kΩ, T

= 25 °C

A

CC

,

Figure 6. Analog voltage regulator: line - load

regulation

Figure 7. Digital voltage regulator: line - load

regulation

Doc ID 17728 Rev 3 13/51

Figure 8. Voltage channel linearity at

different V

voltages

CC

Typical performance characteristics STPM10

Figure 9. Power supply AC rejection vs. V

CC

Figure 11. Error over dynamic range gain

dependence

Figure 10. Power supply DC rejection vs. V

CC

Figure 12. Primary current channel linearity at

different V

CC

Figure 13. Gain response of ΔΣ A/D converters

14/51 Doc ID 17728 Rev 3

STPM10 Theory of operation

7 Theory of operation

7.1 General operation description

The STPM10 is capable of performing measurements of active, reactive and apparent

energy, RMS and instantaneous voltage and current values, and line frequency information.

Most of the functions are fully programmable using internal configuration bits accessible

through the SPI interface. The STPM10 works as a peripheral in microcontroller-based

metering systems. The ZCR and WDG pins are used to provide zero-crossing and watchdog information, and the SPI pins are used to communicate with the microcontroller.

The STPM10 includes volatile internal registers that hold the useful information for the

metering system. Two kinds of active energy are available: wide-band active energy (AW)

which includes all harmonic content (also called type 0) and fundamental active energy

(AF), limited to the 1st harmonic (also called type 1). This latter energy value is obtained by

filtering type 0 active energy. Both the two active energies are stored in up-down counting

accumulator registers with a 20-bit length. Reactive and apparent energies are also

available with a 20-bit accumulation.

The STPM10 also provides the RMS values for voltage and current. Due to the modest

dynamic variation of the voltage, the RMS value is stored with a resolution of 11 bits, while

the RMS current value has a resolution of 16 bits. The instantaneous (momentary) sampled

value of voltage and current are also available with a resolution of 11 and 16 bits,

respectively. The line frequency value is stored with a resolution of 14 bits.

Due to the proprietary energy computation algorithm, the STPM10 calibration is quick and

simple, allowing calibration at only one point over the entire current range.

The configuration and calibration parameters must be downloaded in the internal nonvolatile memory of STPM10 at power-up.

7.2 Analog inputs

Input amplifiers

The STPM10 has one fully differential voltage input channel and two fully differential current

input channels.

The voltage channel consists of a differential amplifier with a gain of 4. The maximum

differential input voltage for the voltage channel is ± 0.3 V.

The two current channels are multiplexed (see Chapter 7.9 for details) to provide a single

input to a preamplifier with a gain of 4. The output of this preamplifier is connected to the

input of a programmable gain amplifier (PGA) with possible gain selections of 2 and 8. The

total gain of the current channels are then 8 and 32. The gain selections are made by writing

to the gain register, and they can be different for the two current channels. If the tamper

function is not used, the secondary current can be disabled.

The maximum differential input voltage is dependent on the selected gain, in accordance

with Ta bl e 6 .

Doc ID 17728 Rev 3 15/51

Theory of operation STPM10

Table 6. Gain of voltage and current channels

Voltage channels Current channels

Gain Max input voltage (V) Gain Max input voltage (V)

4 ±0.30

8X ±0.15

32X ±0.035

The gain register is included in the device configuration register with the address name

PST. The table below shows the gain configuration according to the register values:

Table 7. Configuration of current sensors

Primary Secondary

Gain Sensor Gain Sensor PST TMP

8 CT Disabled Disabled 0 0

32 Shunt Disabled Disabled 1 0

8

CT

8 32 Shunt 1 1

8CT0 1

Configuration

Bits

Configuration

Bits

Note: If the device is used in configuration PST = 1, TMP = 1 (primary channel with CT, secondary

channel with Shunt), the shunt Ks must always be equal to one fourth of the current

transformer Ks.

Both the voltage and current channels implement an active offset correction architecture

which provides the benefit of avoiding any offset compensation.The analog voltage and

current signals are processed by the Σ Δ analog-to-digital converters, which feed the hardwired DSP. The DSP implements an automatic digital offset cancellation that makes it

possible to avoid any manual offset calibration on the analog inputs.

7.3 ΣΔ A/D converters

Analog-to-digital conversion in the STPM10 is carried out using two first-order Σ Δ

converters. The device performs A/D conversions of analog signals on two independent

channels in parallel. The current channel is multiplexed as a primary or secondary current

channel in order to perform the tamper function, if enabled. The converted Σ Δ signals are

supplied to the internal hard-wired DSP unit, which filters and integrates these signals in

order to boost the resolution and to yield all the necessary signals for the computations.

A Σ Δ modulator converts the input signal into a continuous serial stream of 1’s and 0’s at a

rate determined by the sampling clock. In the STPM10, the sampling clock is equal to

f

/4.

CLK

The 1-bit DAC in the feedback loop is driven by the serial data stream. The DAC output is

subtracted from the input signal. If the loop gain is high enough, the average value of the

DAC output (and therefore the bit stream) can approach that of the input signal level. When

a large number of samples are averaged, a very precise value for the analog signal is

obtained. This averaging is carried out in the DSP section, which implements decimation,

16/51 Doc ID 17728 Rev 3

STPM10 Theory of operation

integration and DC offset cancellation of the supplied Σ Δ signals. The gain of the

decimation filters is 1.004 for the voltage channel and 0.502 for the current channel. The

resulting signal has a resolution of 11 bits per voltage channel and 16 bits per current

channel.

Figure 14. First-order ΣΔ A/D converter

f

/4

CLK

Integrator

Output digital signal

Input analog signal

+

Σ

∫

-

DAC

7.4 Zero-crossing detection

The STPM10 has a zero-crossing detector circuit on the voltage channel which can be used

by application for synchronization of some utility equipment in the event of zero-crossing of

the line voltage. This circuit produces the internal signal ZCR which has a rising edge every

time the line voltage crosses zero, and a negative edge every time the voltage reaches its

positive or negative peak. The ZCR signal is then at twice the line voltage frequency. The

ZCR signal is available on the ZCR pin.

Figure 15. ZCR signal

Doc ID 17728 Rev 3 17/51

Theory of operation STPM10

7.5 Period and line voltage measurement

The period module measures the period of the base frequency of the voltage channel and

checks if the voltage signal frequency is within the f

LIN signal is produced, which is low when the line voltage is rising, and high when the line

voltage is falling. This means that the LIN signal is the sign of dv/dt. With further elaboration,

the ZCR signal is also produced. On the trailing edge of LIN (line frequency) the period

counter starts counting up pulses of the f

on the status bit register (see Tab le 10 ).

If the counted number of pulses between two trailing edges of LIN is higher than 2

the counting is never stopped (no LIN trailing edge) this means that the base frequency is

lower than f

Figure 16. LIN and BFR signals

/217 Hz and a BFR (base frequency range) error flag is set.

CLK

/4 reference signal. The LIN signal is available

CLK

CLK

/217 to f

/215 band. To do this, the

CLK

15

, or if

If the number of pulses counted between two trailing edges of LIN is lower than 213, the

base frequency exceeds the limit (this means it is higher than f

error must be repeated three consecutive times in order to set the BFR error flag.

For example, with a 4.194304 MHz oscillator frequency and MDIV bit clear (or 8.192 MHz

with MDIV set), f

/4 is 1.048576 MHz. If the line frequency is 30 Hz, the counted f

CLK

pulses between two LIN trailing edges are 34952, more than 2

The BFR low frequency limit is then:

f

/217 = 4194304/131072 = 32 Hz

CLK

18/51 Doc ID 17728 Rev 3

/215). In this case, the

CLK

15

(32768 pulses).

CLK

/4

STPM10 Theory of operation

With the same clock frequency, if the line frequency is 130 Hz, the f

two LIN trailing edges are 8066, less than 2

f

/215 = 4194304/32768 = 128 Hz.

CLK

The BFR flag is also set if the register value of the RMS voltage drops below 64. BFR is

cleared when the register value goes above 128. The BFR, then, also gives information

about the presence of the line voltage within the meter.

When the BFR error is set, the computation of power is zero unless the FRS bit is set.

In fact, the effect of the BFR bit can be overridden by setting FRS configuration bit.

It means that if FRS is set and BFR is also set, all the energy computation is carried on as

BFR was cleared. In this case then p=u*i, where u could be zero or not (if BFR was set

because voltage RMS register value is below 64).

When the line frequency re-enters the nominal band, the BFR flag is automatically reset.

This BFR error flag is also assembled as part of the 8-bit status register (see Ta bl e 10 ).

7.6 Power supply

The main STPM10 supply pin is the VCC pin. From the VCC pin two linear regulators

provide the necessary voltage for the analog part VDDA (3 V) and for the digital part VDDD

(1.8 V).

The VSS pin represents the reference point for all the internal signals. A 100 nF low ESR

capacitor should be connected between VCC and VSS, VDDA and VSS, VDDD and VSS.

All these capacitors must be located very close to the device.

/4 pulses between

13

(8192). The BFR high frequency limit is then:

CLK

The STPM10 contains a power on reset (POR) detection circuit. If the VCC supply is less

than 2.5 V, then the STPM10 goes into an inactive state, all the functions are blocked and a

reset condition is asserted. This is useful to ensure correct device operation at power-up

and during power-down. The power supply monitor has built-in hysteresis and filtering,

which give a high degree of immunity from false triggering due to noisy supplies.

A band-gap voltage reference (VBG) of 1.23 V ±1% is used as the reference voltage level

source for the two linear regulators and for the A/D converters. Also, this module produces

several bias currents and voltages for all other analog modules. The band-gap voltage can

be compensated regardless of the temperature variations with the BGTC bits.

Figure 17. Band-gap temperature variation

1,29

1,29

1,28

1,28

1,27

1,27

1,26

1,26

1,25

1,25

1,24

1,24

VBG

VBG

1,23

1,23

1,22

1,22

1,21

1,21

1,20

1,20

-40 0 40 80

-40 0 40 80

Temperature °C

Temperature °C

BGTC=0

BGTC=0

BGTC=1

BGTC=1

BGTC=2

BGTC=2

BGTC=3

BGTC=3

100

100

Doc ID 17728 Rev 3 19/51

Theory of operation STPM10

7.7 Load monitoring

The STPM10 includes a no-load condition detection circuit with adjustable threshold. This

circuit monitors the voltage and the current channels and, when the measured voltage is

below the set threshold, the internal signal BIL becomes high. Information about this signal

is also available in the status bit BIL.

The no-load condition occurs when the product of the VRMS and IRMS register values is

below a given value. This value can be set with the LTCH configuration bits. Four different

no-load threshold values can be chosen according to the two configuration bits LTCH (see

Ta bl e 8 ).

When a no-load condition occurs (BIL=1) the integration of power is suspended and the

tamper module is disabled. The BIL signal can be accessed only through the SPI interface.

Table 8. No-load detection thresholds

LTCH K

0800

1 1600

2 3200

3 6400

7.8 Error detection

In addition to the no-load condition and the line frequency band, the integration of power can

also be suspended due to an error detected on the source signals.

There are two kinds of error-detection circuits involved. The first checks all the Σ Δ signals

from the analog part if any is stacked at 1 or 0 within the 1/128 of f

In case of a detected error, the corresponding Σ Δ signal is replaced with an idle Σ Δ signal,

which represents a constant value of 0. All error and other resolved flags are treated as bits

of a device status and can be read out by means of the SPI interface.

Another error condition occurs if LED pin output signals are different from the internal

signals that drive them. This can occur if some of these pins are forced to GND or to some

other imposed voltage value. In this case, the internal status bit PIN is activated, providing

the information that some hardware problem has been detected.

LT CH

period of observation.

CLK

7.9 Tamper detection module

The STPM10 is able to measure the current in both live and neutral wire with a time domain

multiplexing approach on a unique sigma delta modulator. This mechanism is adopted to

implement anti-tamper function. If this function is selected (see Ta bl e 7), the live and neutral

wire currents are monitored; when the difference between the two measurements exceeds a

rated threshold the STPM10 enters the "tamper state", while in "normal state" the two

measurements are below the threshold.

In particular, both channels are not observed all the time, rather a time multiplex mechanism

is used. During the observation time of each channel, its active energy is calculated. A

tamper condition occurs when the absolute value of the difference between the two active

20/51 Doc ID 17728 Rev 3

STPM10 Theory of operation

energy values is greater than a certain percentage of the averaged energy during the

activated tamper module (see Equation 1).

This percentage value can be selected between two different values (12.5 % and 6.25 %)

according to the value of the configuration bit CRIT.

The tamper condition is detected when the following formula is satisfied:

Equation 1

EnergyCH1 - EnergyCH2 > K

where K

can be 12.5 % or 6.25 %.

CRIT

(EnergyCH1 + EnergyCH2)/2;

CRIT

The detection threshold is much higher than the accuracy difference of the current channels,

which should be less than 0.2 %, but, some headroom should be left for possible transition

effect, due to accidental synchronism of actual load current change with the rhythm of taking

the energy samples.

The tamper circuit works if the energies associated with the two current channels are both

positive or negative, if the two energies have different sign, the tamper is on all the time

however, the channel with the associated higher power is selected for the final computation

of energy.

When internal signals are not good enough to perform the calculations, i.e. line period is out

or range or ΔΣ signals from analog section are stacked at high or low logic level, or no load

condition is activated, the tamper module is disabled and its state is preset to normal.

7.9.1 Detailed operational description

The meter is initially set to normal state, i.e. tamper not detected.In this condition the

primary channel is selected for final integration of energy. In such state the values of both

load currents should not differ more than the accuracy difference of the channels does.

Sixty-four periods of line voltage is used as a tamper checking period.

After 24 periods of line voltage two internal signals MUX and INH are changed in order to

enable secondary current channel and to freeze the last power and RMS values of primary

current channel. The following 16 periods of line frequency are used for tamper detection

integration. During this gap, the final energy calculation does not use the signal from

selected channel but the frozen values.

Four line periods after the INH switch, the integration of power from secondary current

channel is started and lasts four periods. Additional four line periods later MUX signal is

switched back to primary current channel and the integration for tamper detection is started.

The timings of MUX and INH signals are shown in Figure 18 below.

Figure 18. Timings of tamper module - Primary channel selected

MUX Ch1Ch2Ch1Ch1

INH

Tampe rpowerintegrators B A

Cycles 444424 24

Doc ID 17728 Rev 3 21/51

Theory of operation STPM10

When the secondary channel is selected to be integrated by the final energy integrator, the

MUX and INH signals change according to Figure 19 below.

Figure 19. Timings of tamper module - Secondary channel selected

This means that energy of four periods from secondary channel followed by energy of four

periods from primary channel is sampled within the tamper module. From these two

samples, called B and A respectively, the criteria of tamper is calculated and the channel

with higher current is selected, resulting in a new tamper state. If four consecutive new

results of criteria happen, i.e. after elapsed 5.12 s at 50 Hz, the meter will enter into tamper

state. Thus, the channel with the higher current will be selected for the energy calculation. If

samples of power A and B would have different signs, the Tamper would be on all the time

but, the channel with bigger power would be still selected for the final integration of energy.

If a tamper status has been detected, the multiplex ratio will be 56:8 if the primary channel

energy is greater than the secondary one, otherwise it will be 8:56.

The detected tamper condition is stored in the BIT status bit. If BIT = 0 tamper is not

detected, if BIT = 1 a tamper condition has been detected. In standalone mode the BIT flag

is also available in the SDATD pin.

7.10 Phase compensation

The STPM10 does not introduce any phase shift between the voltage and current channel.

However, the voltage and current signals come from transducers, which could have inherent

phase errors. For example, a phase error of 0.1° to 0.3° is not uncommon for a current

transformer (CT). These phase errors can vary from part to part, and they must be corrected

in order to perform accurate power calculations. The errors associated with phase mismatch

are particularly noticeable at low power factors. The STPM10 provides a means of digitally

calibrating these small phase errors by introducing delays on the voltage or current signal.

The amount of phase compensation can be set using the 4 bits of the phase calibration

register (CPH).

The default value of this register is at a value of 0, which gives 0° phase compensation.

When the 4 bits give a CPH of 15 (1111) the compensation introduced is +0.576°. This

compensates the phase shift usually introduced by the current sensor, while the voltage

sensor, normally a resistor divider, does not introduce any delay. The resolution step of the

phase compensation is 0.038°.

7.11 Clock generator

All the internal timing of the STPM10 is based on the CLKOUT signal. This signal can be

generated in three different ways:

22/51 Doc ID 17728 Rev 3

STPM10 Theory of operation

1. RC: this oscillator mode can be selected using the RC configuration bit. If RC = 1, the

STPM10 runs using the RC oscillator. A resistor connected between CLKIN and

ground sets the RC current. For 4 MHz operation, the recommended settling resistor is

12 kΩ. The oscillator frequency can be compensated using the CRC configuration bit.

2. Quartz: If RC = 0, the oscillator works with an external crystal. The recommended

circuit is depicted in Figure 20 (b).

3. External clock: by keeping RC=0, it is also possible to feed the CLKOUT pin with an

external oscillator signal.

Figure 20. Different oscillator circuits with (a) quartz, (b) internal oscillator, (c) external source

The clock generator is powered from an analog supply and is responsible for two tasks. The

first is to retard the turn-on of some function blocks after POR in order to help smooth the

start of the external power supply circuitry by keeping off all major loads. The second task of

the clock generator is to provide all necessary clocks for the analog and digital parts. During

this task, the MDIV configuration bit is used to inform the device about the nominal

frequency value of CLKOUT. Two nominal frequency ranges are expected to be from 4.000

MHz to 4.194 MHz (MDIV = 0) or from 8.000 MHz to 8.192 MHz (MDIV = 1).

7.11.1 RC startup procedure

To use the device with RC oscillator the configuration bit RC (see Ta b le 1 1) must be set.

Since the default configuration is for a crystal oscillator, when a RC oscillator is used instead

and the device is supplied for the very first time it is not internally clocked and consequently

the DSP is inactive. In this condition it is not possible to set RC or any other configuration bit.

The following SPI procedure can be run in order to set the RC bit and provide the clock to

the device:

● Set the mode signal BANK;

● Perform a software reset;

● Read the registers: BANK mode signal should be checked and the records should

show something (not 000000F0);

● Clear the mode signal BANK;

● DO NOT perform a reading, and write configuration bit RC;

In this way the RC oscillator is started. If the registers are read again, it can be seen that RC

bit is set and BANK is cleared. Once the RC startup procedure is complete, the device is

clocked and active. For details on mode signals refer to Chapter 7.18, for SPI operations

refer to Chapter 7.19.

Doc ID 17728 Rev 3 23/51

Theory of operation STPM10

7.12 Resetting the STPM10

The STPM10 has no reset pin. The device is automatically reset by the POR circuit when

the V

providing a dedicated command (see Section 7.19 for remote reset command details).

In case of reset caused by the POR circuit, all clocks and both DC buffers in the analog part

are kept off for about 30 ms, as well as all blocks of the digital part, except for the SPI

interface, which is held in a reset state for about 125 ms after a reset condition.

When a reset is performed through SPI, no delayed turn-on is generated.

Resetting the STPM10 causes all the functional modules of the STPM10 to be cleared,

including the volatile memory.

The reset through SPI (remote reset request) normally takes place during production

testing.

crosses the 2.5 V value, but it can also be reset through the SPI interface by

CC

7.13 Using the STPM10 in microcontroller-based meters

The STPM10 can be used in microcontroller-based energy meters.

The SPI pins (SCS, SCL, SDA, SYN) are used for communication purposes, allowing the

microcontroller to write and read the internal STPM10 registers.

The zero-crossing signal is available at the ZCR pin (see Section 7.4 for details about the

ZCR signal).

The WDG pin provides the watchdog signal (DOG). The DOG signal generates a 16 ms

long positive pulse every 1.6 seconds. Generation of these pulses can be suspended if data

are read in intervals shorter than 1.6 s. The DOG signal is actually a watchdog reset signal

which can be used to control operation of an on-board microcontroller. It is set to high

whenever the VDDA voltage is below 2.5 V, but after VDDA goes above 2.5 V this signal

starts running.

It is expected that an application microcontroller should access the data in the metering

device on a regular basis at least 1/s (recommended is 32/s). Every latching of results in the

metering device requested from the microcontroller also resets the watchdog. If latching

requests are not 1.6 seconds from one another, an active high pulse on WDG is produced,

because the device assumes that the microcontroller is not operating properly. An

application can use this signal either to control the reset pin of its microcontroller, or it can

be tied to an interrupt pin. The latter option is recommended for a battery-backup application

which can enter a sleep mode due to power-down conditions, and should not be reset by a

metering device as it would exit from sleep mode.

7.14 Energy to frequency conversion

The STPM10 provides energy to frequency conversion both for calibration and energy

readout purposes. In fact, one convenient way to verify the meter calibration is to provide a

pulse train signal with 50% duty cycle whose frequency signal is proportional to the active

energy under steady load conditions. In this case, the user chooses a certain number of

pulses on the LED pin that correspond to 1 kWh. This value is called P.

Let us consider the case in which the LED pin is configured to be driven from internal signal

AW (active energy) whose frequency is proportional to the active energy. The signal AW is

24/51 Doc ID 17728 Rev 3

STPM10 Theory of operation

taken from the 11th bit of the active energy register, and consequently a relationship

between the LSB value of the active energy register and the number of pulses provided per

each kWh (P) can be defined as:

Equation 2

1000

=

k

AW

[]

11

⋅

P2

Wh

Due to the innovative and proprietary power calculation algorithm, the frequency signal is

not affected by any ripple at twice the line frequency. This feature strongly reduces the

calibration time of the meter.

In a practical example where the desired P is 64000 pulses/kWh (=17.7 Hz*kW), we have:

Equation 3

k

=7.63*10-6 Wh

AW

This means that the reading of 0x00001 in the active energy register represents 7.63 µWh,

while 0xFFFFF represents 8 Wh.

The LED pin can be driven from AW (active energy wide band), AF (active energy limited at

fundamental), RW (reactive energy) or SW (apparent energy) according to the value of the

KMOT bit.

In this case, since the LED pin is driven by signals different from that of AW, some other

relationship between the LSB of the register and the number of pulses per kWh provided by

the meter (P) must be defined:

Equation 4

k

= 4*kAW [Wh]

AF

k

= 2*kAW [VARh]

RW

k

= kAW [VAh]

SW

Table 9. LED pin configuration

KMOT (2 bits) Signal available on LED pin # of pulses

0 AW Type0* P [kWh]

1 AF Type1* P [kWh]

2 RW P [kVARh]

3 SW P [kVAh]

Doc ID 17728 Rev 3 25/51

Theory of operation STPM10

7.15 Status bits

The STPM10 includes 8 status bits which provide information about the current status of the

meter. The status bits are the following:

Table 10. Status bit description

Bit # Name Description Condition

0 BIL No-load condition

1BCFΣ Δ signals status

2 BFR Line frequency range

3 BIT Tamper condition

4 MUX Current channel selection

5 LIN Trend of the line voltage

6 PIN Output pin check

7 HLT Data validity

BIL = 0: No-load condition not detected

BIL = 1: No-load condition detected

BCF = 0: Σ Δ signals active

BCF = 1: One or both Σ Δ signals are stacked

BFR = 0: Line frequency within the 45 Hz - 65 Hz range

BFR = 1: Line frequency out of range

BIT = 0: Tamper not detected

BIT = 1: Tamper detected

MUX = 0: Primary current channels selected by the tamper

module

MUX = 1: Secondary current channels selected by the tamper

module

LIN = 0: Line voltage going from the minimum to the maximum

value. (dv/dt > 0)

LIN = 1: Line voltage going from the maximum to the minimum

value. (dv/dt < 0)

PIN = 0: Output pins are consistent with the data

PIN = 1: Output pins are different with the data, this means an

output pin is forced to 1 or 0

HLT = 0: Data records reading are valid.

HLT = 1: Data records are not valid. A reset occurred and a

restart is in progress

All these signal can be read through the SPI interface. See

details on the status bit location in the STPM10 data records.

26/51 Doc ID 17728 Rev 3

Section 7.15: Status bits for

STPM10 Theory of operation

7.16 Programming the STPM10

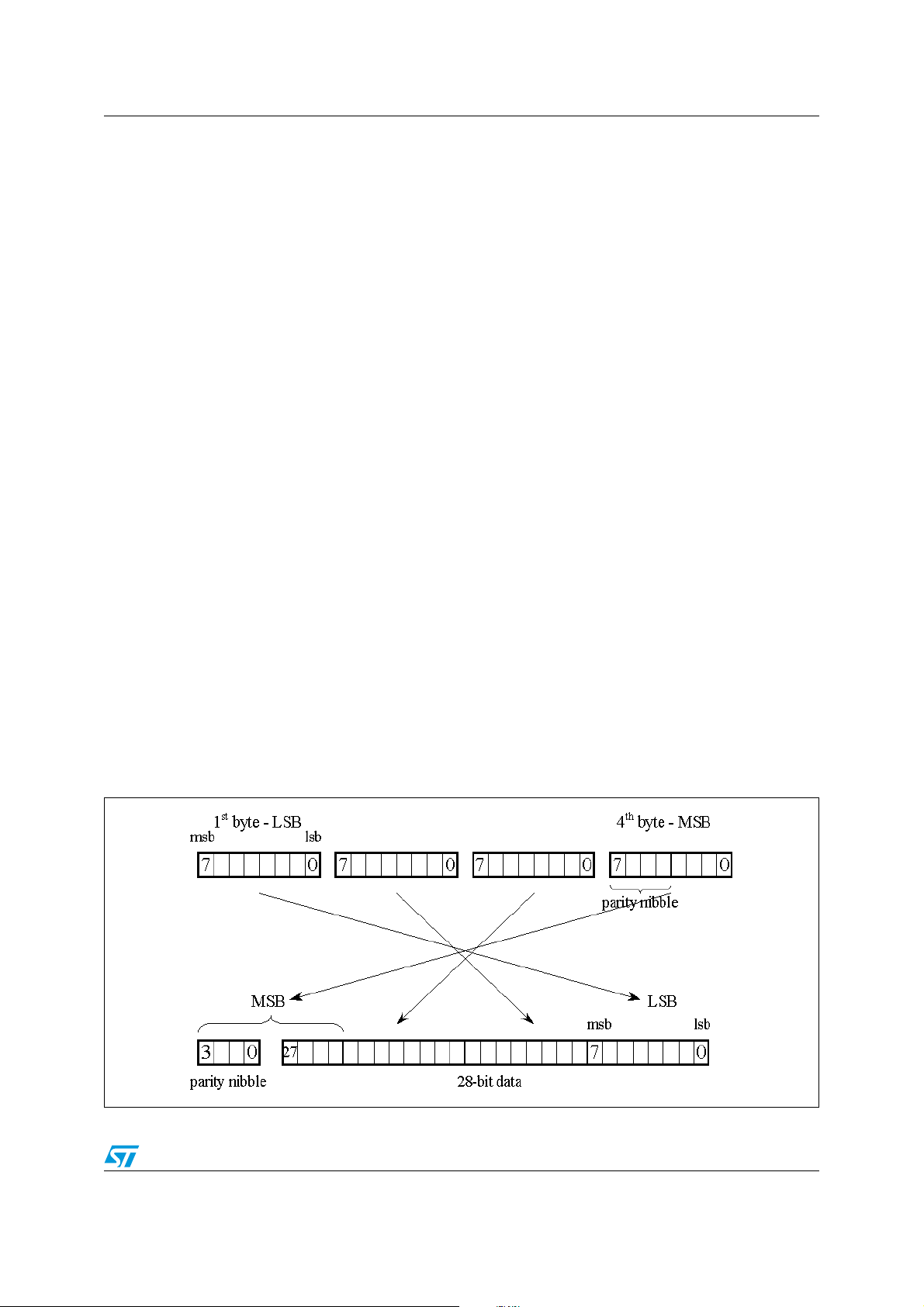

7.16.1 Data records

The STPM10 has 8 internal data record registers. Every data record consists of a 4-bit

parity code and 28-bit data value where the parity code is computed from the data value,

which makes a total of 32 bits, or 4 bytes.

Figure 21 shows the data record structure with the name of the contained information. Each

bit of parity nibble is defined as odd parity of all seven corresponding bits of data nibbles.

The first 6 registers are read-only, except for the 8-bit mode signals in the DFP register (the

mode signals are described later in this paragraph). The last two registers are CFL and

CFH.

Figure 21. STPM10 data records map

20 bit

DAP

4 bit

parity

20 bit 8 bit

1bit

type0 active energy

1bit 1bit

6 bit

Status

DRP

DSP

DFP

DEV

DMV

CFL

CFH

parity

parity

parity

parity

parity

parity

parity

p

p

uMOM

msb lsb

7.17 Configuration bits

All the configuration bits that control the operation of the device (CFL and CFH data records)

can be written in a temporary way. The configuration bit values are written in the so-called

volatile memory, which are simple latches that hold the configuration data until the power is

on or until a reset condition occurs (both POR and remote reset).

reactive energy

apparent energy

type 1 energy

iRMSuRMS

iMOM

lower part of configurators

upper part of configurators

11 bit 16 bit

upper f(u)0 1

lower f(u)

mode signals

As indicated in the data records table, the configuration bits are 56.

Doc ID 17728 Rev 3 27/51

Theory of operation STPM10

Each configuration bit can be written by sending a byte command to STPM10 through its

SPI interface. The procedure to write the configuration bits is described in

interface

Table 11. Configuration bit map

Address

6-bit

binary

000000 0 - 1 Reserved

000001 1 MDIV 1

000010 2 RC 1

000011 3 - 1 Reserved

000100 4 - 1 Reserved

000101 5 PST 1

000110 6 - 1 Reserved

DEC

Name

.

n. of

bits

Measurement frequency range selection:

- MDIV=0: 4.000 MHz to 4.194 MHz

- MDIV=1: 8.000 MHz to 8.192 MHz

Type of internal oscillator selection:

- RC=0:crystal oscillator,

- RC=1:RC oscillator

Current channel sensor type and gain:

If TMP=0

PST=0: primary is CT x8, secondary is not used, no tamper

PST=1: primary is shunt x32, secondary is not used, no tamper

If TMP=1

PST=0: primary is CT x8, secondary is CT x8, tamper

PST=1: primary is CT x8, secondary is shunt x32, tamper

Description

(1)

Section 7.19: SPI

000111 7 TMP 1 Tamper enable

Power calculation when BFR=1

001000 8 FRS 1

- FRS=0: energy accumulation is frozen, power is set to zero;

- FRS=1: normal energy accumulation and power computation (p=u*i);

Bit sequence output during record data reading selection:

001001 9 MSBF 1

- MSBF=0: MSB first

- MSBF=1: LSB first

This bit swaps the information stored in the type0 (first 20 bits of DAP register)

and type1 (first 20 bits of DFP register) active energy.

001010 10 FUND 1

- FUND = 0: type 0 contains wide-band active energy, type1 contains

fundamental active energy

- FUND = 1: type 0 contains fundamental active energy, type1 contains wideband active energy

001100 12

No-load condition threshold as product between V

LTCH=0 800

001101 13

(1)

LT CH 2

LTCH=1 1600

LTCH=2 3200

LTCH=3 6400

001110 14

Selection of pulses for LED:

KMOT=0 Type 0 Active Energy

001111 15

KMOT 2

(1)

KMOT=1 Type 1 Active Energy

KMOT=2 Reactive Energy

KMOT=3 Apparent Energy

RMS

and I

RMS

:

28/51 Doc ID 17728 Rev 3

STPM10 Theory of operation

Table 11. Configuration bit map (continued)

Address

n. of

bits

6-bit

binary

Name

DEC

010000 16 - 1 Reserved

-

1 Reserved010001 17

010010 18

BGTC 2 Band-gap temperature compensation bits. See Figure 17 for details.

010011 19

(1)

010100 20

010101 21

010110 22

010111 23

CPH 4

(1)

4-bit unsigned data for compensation of phase error, 0°+0.576°.

16 values are possible with a compensation step of 0.0384°. When CPH=0 the

compensation is 0°, when CPH=15 the compensation is 0.576°.

011000 24

011001 25

011010 26

8-bit unsigned data for voltage channel calibration.

011011 27

CHV 8

011100 28

256 values are possible. When CHV is 0 the calibrator is at -12.5% of the

nominal value. When CHV is 255 the calibrator is at +12.5%. The calibration

step is then 0.098%.

011101 29

Description

(1)

011110 30

011111 31

100000 32

100001 33

100010 34

100011 35

100100 36

100101 37

100110 38

100111 39

101000 40

101001 41

101010 42

101011 43

101100 44

101101 45

101110 46

101111 47

(1)

(1)

(1)

CHP 8

CHS 8

8-bit unsigned data for primary current channel calibration.

256 values are possible. When CHP is 0 the calibrator is at -12.5% of the

nominal value. When CHP is 255 the calibrator is at +12.5%. The calibration

step is then 0.098%.

8-bit unsigned data for secondary current channel calibration.

256 values are possible. When CHS is 0 the calibrator is at -12.5% of the

nominal value. When CHS is 255 the calibrator is at +12.5%. The calibration

step is then 0.098%.

Doc ID 17728 Rev 3 29/51

Theory of operation STPM10

Table 11. Configuration bit map (continued)

Address

6-bit

binary

DEC

Name

n. of

bits

Description

(1)

110000 48

CRC 2

110001 49

110010 50 - 1 Reserved

110011 51 - 1 Reserved

110100 52 - 1 Reserved

110101 53 CRIT 1

110110 54 - 1 Reserved

110111 55 - 1 Reserved (always set to 1 after production testing of die)

1. IMPORTANT: This bit represents the MSB of the decimal value indicated in the description column.

(1)

2-bit unsigned data for calibration of RC oscillator. (see Tabl e 5 )

CRC=0, or CRC=3 cal=0%

CRC=1, cal=+10%;

CRC=2, cal=-10%.

Selection of tamper threshold:

CRIT=0: 12,5% / CRIT=1: 6,25%

As indicated above, the STPM10 includes 56 CFG bits. The CFG bits are not retained when

the STPM10 supply is not available and they are cleared when a POR occurs, but they are

not cleared when a remote reset command (RRR) is sent through SPI.

Normally, some of these bits must be loaded during power-up of the application. From the

microcontroller, it could also reload the configuration and calibration values after power-on

restart.

7.18 Mode signals

The STPM10 includes 8 mode signals located in the DFP data record. 3 of these are used

only for internal testing purposes while 5 are useful to change some of the operations of the

STPM10. The mode signals are not retained when the STPM10 supply is not available and

they are cleared when a POR occurs, but they are not cleared when a remote reset

command (RRR) is sent through SPI.

The mode signals bit can be written using the normal writing procedure of the SPI interface

(see

Section 7.19).

Table 12. Mode signal description

Bit #

0 BANK

1 Reserved

2 Reserved

3 Reserved

30/51 Doc ID 17728 Rev 3

Signal

name

Bit

value

0

Used for RC startup procedure

1 1111000x F0 or F1

Status

Binary

command

0111000x 70 or 71

Hex

command

STPM10 Theory of operation

Table 12. Mode signal description (continued)

4 CSEL

5 Reserved

6 Reserved

0 Current channel 1 selected when tamper is disabled 0111 100x 78 or 79

1 Current channel 2 selected when tamper is disabled 1111 100x F8 or F9

7 Precharge 1

Swap the 32-bit data record readings. From

1,2,3,4,5,6,7,8, to 5,6,7,8,1,2,3,4 and vice-versa

– CSEL: In normal operation, if the anti-tamper module is not activated (see PST

configuration bits) the STPM10 selects channel 1 as the source of current

information. For debug or calibration purposes it is possible to select channel 2 as the

source of the current channel signal when the tamper module is disabled. This is

done by setting the CSEL mode bit.

–

Precharge: This command swaps the sequence of data records read, allowing the

reading of the last four data records first, and the first four second. The reading

sequence is 5, 6, 7, 8, 1, 2, 3, 4. Unlike the other mode signals, the precharge

command is not retained inside the STPM10, but should be sent each time before the

reading of the data records.

BANK: it is used to activate RC oscillator (see Chapter 7.11.1).

–

7.19 SPI interface

The SPI interface supports a simple serial protocol, which is implemented to enable

communication between some master system (microcontroller or PC) and the device.

Three tasks can be performed with this interface:

– remote resetting of the device

– reading data records

– writing the mode bits and the configuration bits

1111111x FF

Four pins of the device are dedicated to this purpose: SCS, SYN, SCL and SDA.

SCS, SYN and SCL are all input pins, while SDA can be input or output according to

whether the SPI is in write or read mode. A high-level signal for these pins means a voltage

level higher than 0.75 x VCC, while a low-level signal means a voltage value lower than 0.25

x VCC.

The internal registers are not directly accessible. Instead, 32 bits of transmission latches are

used to pre-load the data before being read or written to the internal registers.

The condition in which SCS, SYN and SCL inputs are set to high level determines the idle

state of the SPI interface, and no data transfer occurs.

– SCS: enables SPI operation when low.

– SYN: operates different functions according to the status of the SCS pin. When

SCS is low, the SYN pin status selects if the SPI is in read (SYN = 1) or write

mode (SYN = 0). When the SCS is high and SYN is also high, the results of the

input or output data are transferred to the transmission latches.

– SCL: basically the clock pin of the SPI interface. This pin function is also controlled

by the SCS status. If SCS is low, SCL is the input of the serial bit synchronization

Doc ID 17728 Rev 3 31/51

Theory of operation STPM10

0

clock signal. When SCS is high, SCL is also high, determining the idle state of the

SPI.

– SDA: the data pin. If SCS is low, the operation of SDA is dependent on the status

of the SYN pin. If SYN is high, SDA is the output of the serial bit data (read mode).

If SYN is low, SDA is the input of the serial bit data signal (write mode). If SCS is

high, SDA is the input of the idle signal.

Any pin above has an internal weak pull-up mechanism of nominal 15 µA. This means that

when a pin is not forced by external signals, the state of the pin is logic high. A high state of

any input pin described above is considered an idle (not active) state. For the SPI to operate

correctly, the STPM10 must be correctly supplied as described in

Section 7.6: Power supply.

An idle state of the SPI module is recognized when the signals of pins SYN, SCS, SCL and

SDA are in a logic high state. Any SPI operation should start from this idle state.

When SCS is active (low), signal SDATD should change its state at trailing edge of signal

SCLNLC and the signal SDATD should be stable at next leading edge of signal SCLNLC.

The first valid bit of SDATD is always started with activation of signal SCLNLC.

7.20 Remote reset

The timing diagram of this operation is shown in Figure 22. The time step can be as short as

30 ns.

The internal reset signal is called RRR. Unlike the POR, the RRR signal does not cause the

30 ms delayed restart of the analog module, and the 120 ms delay in the restart of the digital

module. This signal does not clear the mode signals.

Figure 22. Timing for providing remote reset request

SCS

SCS

SYN

SYN

SCLNLC

SCLNLC

SDATD

SDATD

t1t2t3t4t5t6t

(1)

7

t8t9t

1

1. All time intervals must be longer than 30 ns. t7 → t8 is the reset time; this interval must be longer than 30 ns also.

32/51 Doc ID 17728 Rev 3

STPM10 Theory of operation

7.21 Reading data records

A microcontroller is able to read all measurement results and all system signals

(configuration, calibration, status, mode). Again, the time step can be as short as 30 ns.

There are two phases of reading, called latching and shifting.

Latching is used to sample results into transmission latches. The transmission latches are

the flip-flops that hold the data in the SPI interface. This is done with the active pulse on

SYN when SCS is idle. The length of the pulse on SYN must be longer than 2 periods of the

measurement clock, i.e. more than 500 ns at 4 MHz.

The shifting starts when SCS become active. In the beginning of this phase, another much

shorter pulse (30 ns) on SYN should be applied in order to ensure that an internal

transmission serial clock counter is reset to zero. An alternative way is to extend the pulse

on SYN into the second phase of reading. After this reset is done, a 32 serial clocks-perdata record should be applied. Up to 8 data records can be read this way. This procedure

can be aborted at any time through deactivation of SCS (see

The first read-out byte of the data record is the least significant byte (LSB) of the data value

and, of course, the fourth byte is the most significant byte (MSB) of the data value. Each

byte can be further divided into a pair of 4-bit nibbles, referred to as the most and least

significant nibble (MSN, LSN). This division makes sense with the MSB of the data value

because its MSN holds the parity code rather than useful data.

Figure 24).

The sequence of the data record during the read operation is fixed. Normally, an application

reads the 1st through the 6th data record; the 7th and 8th data record would be read only

when it needs to fetch the configuration data. However, an application may apply a

precharge command (see

Ta bl e 1 2) prior to the reading phase. This command forces the

device to respond with the sequence 5th - 8th, 1st - 4th. Such a change of sequence can be

used to skip the first four data records.

The timing diagram of the reading operation is shown in

and beginning of the shifting phase of the first byte (0x5F) of the first data record, and the

end of reading. Also, both alternatives for resetting the internal transmission serial clock

counter are shown in signal SYN.

Figure 23. Data record reconstruction

Figure 24. One can see the latching

Doc ID 17728 Rev 3 33/51

Theory of operation STPM10

Figure 24. Timing for data record reading

SCS

SCS

f(read)

1st byte

1st byte

f(read)

last bit of 32nd byte

last bit of 32nd byte

SYN

SYN

SCLNLC

SCLNLC

SDATD

SDATD

t1t

2

t

t

3

t

t

4

6

5

t1 → t2: Latching phase. Interval value > 2/f

t2 → t3: Data latched, SPI idle. Interval value > 30 ns

t

→ t4: Enable SPI for read operation. Interval value > 30 ns

3

t

→ t5: Serial clock counter is reset. Interval value > 30 ns

4

t

→ t6: SPI reset and enabled for read operation. Interval value > 30 ns

5

t

: Internal data transferred to SDA

7

t

: SDA data is stable and can be read

8

The system that reads the data record from the STPM10 should check the integrity of each

data record. If the check fails, the reading should be repeated, but this time only the shifting

should be applied. Otherwise, new data would be latched into transmission latches and the

one incorrectly read would be lost.

Normally, each byte is read out as the most significant bit (MSB) first. But this can be

changed by setting the MSBF configuration bit in the STPM10 CFL data record. If this is

done, each byte is read out as the least significant bit (LSB) first.

7.22 Writing procedure

Each writable bit (configuration and mode bits) has its own 6-bit absolute address. For the

configuration bits, the 6-bit address value corresponds to its decimal value, while for the

mode bits the addresses are the ones indicated in

t7t

8

CLK

Section 7.18: Mode signals.

In order to change the state of a latch, one must send a byte of data to the STPM10, which

is the normal way to send data via SPI. This byte consists of 1-bit data to be latched (MSB),

followed by the 6-bit address of the destination latch, followed by 1-bit don't care data (LSB),

which makes a total of 8 bits of command byte.

For example, if we want to set configuration bit 47 (part of the secondary current channel

calibrator) to 0, we must convert the decimal 47 to its 6-bit binary value: 101111. The byte

command is then composed as follows:

34/51 Doc ID 17728 Rev 3

STPM10 Theory of operation

1 bit DATA value+6-bits address+1 bit (0 or 1) as depicted in Figure 25. In this case the

binary command is 01011111 (0x5F), which is the one depicted, or 01011110 (0x5E):

Figure 25. Timing for writing configuration and mode bits

→ t2 (> 30 ns): SPI out of idle state

t

1

t

→ t3 (> 30 ns): SPI enabled for write operation

2

t

: data value is placed in SDA

3

t

: SDA value is stable and shifted into the device

4

t

→ t5 (> 10 µs): writing clock period

3

t

→ t5: 1 bit data value

3

t

→ t6: 6 bit address of the destination latch

5

t

→ t7: 1 bit EXE command

6

t

: end of SPI writing

8

t

: SPI enters idle state

9

The same procedure should be applied for the mode signals, but in this case the 6-bit

address must be taken from

Ta bl e 1 2 .

The LSB of the command is also called the EXE bit because instead of the data bit value,

the corresponding serial clock pulse is used to generate the necessary latching signal. This

way the writing mechanism does not need the measurement clock in order to operate, which

makes the operation of SPI module of STPM10 completely independent from the rest of

device logic except for the signal POR.

Commands for changing system signals should be sent during active signals SCS and SYN,

as shown in

Figure 25. The SYN must be put low in order to disable the SDA output driver of

the STPM10 and make the SDA an input pin. A string of commands can be sent within one

period of active SCS and SYN signals, or a command can be followed by reading the data

record. However, in this case, the SYN should be deactivated in order to enable the SDA

output driver, and a SYN pulse should be applied before activation of the SCS in order to

latch the data.

Doc ID 17728 Rev 3 35/51

Theory of operation STPM10

7.22.1 Interfacing the standard 3-wire SPI with the STPM10 SPI

Due to the fact that a 2-wire SPI is implemented in the STPM10, it is clear that sending any

command from a standard 3-wire SPI would require a 3-wire to 2-wire interface, which

should produce a proper signal on SDA from host signals SDI, SDO and SYN. The need for

a single-gate 3-state buffer could be avoided through an emulation of SPI just to send some

commands. On a microcontroller this would be done by performing the following steps:

1. Disable the SPI module

2. Set the SDI pin, which is connected to SDA as an output

3. Activate SYN first, and then SCS

4. Apply a new bit value to SDI, and activate SCL

5. Deactivate SCL

6. Repeat the previous two steps seven times to complete a one byte transfer

7. Repeat the previous three steps for any remaining byte transfers

8. Set the SDI pin as an input

9. Deactivate SCS and SYN

10. Enable the SPI module

In case of a precharge command (0xFF), the emulation above is not necessary. Due to the

pull-up device on the SDA pin of the STPM10, the processor needs to perform the following

steps:

1. Activate SYN first in order to latch the results

2. After at least 1 µs, activate SCS

3. Write one byte to the transmitter of SPI (this produces 8 pulses on SCL with SDI=1)

4. Deactivate SYN

5. Optionally read the data records (the sequence of reading is altered)

6. Deactivate SCS

7.23 Energy calculation algorithm

Within the STPM10, the computing section of the measured active power uses a completely

new patented signal processing approach. This approach allows the device to reach high a

level of performance in terms of accuracy.

The signals, coming from the sensors, for the instantaneous voltage are calculated as

follows:

Equation 5

v(t) = V•sin ωt

where V is the peak voltage and

The instantaneous current is calculated using:

Equation 6

i(t) = I • sin (ωt + ϕ)

36/51 Doc ID 17728 Rev 3

ω is related to the line frequency.

STPM10 Theory of operation