ST STM32F103RF, STM32F103VF, STM32F103ZF, STM32F103RG, STM32F103VG User Manual

...

STM32F103xF

FBGA

LQFP64 10 × 10 mm,

LQFP100 14 × 14 mm,

LQFP144 20 × 20 mm

LFBGA144 10 × 10 mm

STM32F103xG

XL-density performance line ARM-based 32-bit MCU with 768 KB to

1 MB Flash, USB, CAN, 17 timers, 3 ADCs, 13 communication interfaces

Target specification

Features

■ Core: ARM 32-bit Cortex™-M3 CPU with MPU

– 72 MHz maximum frequency,

1.25 DMIPS/MHz (Dhrystone 2.1)

performance at 0 wait state memory

access

– Single-cycle multiplication and hardware

division

■ Memories

– 768 Kbytes to 1 Mbyte of Flash memory

– 96 Kbytes of SRAM

– Flexible static memory controller with 4

Chip Select. Supports Compact Flash,

SRAM, PSRAM, NOR and NAND

– LCD parallel interface, 8080/6800 modes

■ Clock, reset and supply management

– 2.0 to 3.6 V application supply and I/Os

– POR, PDR, and programmable voltage

detector (PVD)

– 4-to-16 MHz crystal oscillator

– Internal 8 MHz factory-trimmed RC

– Internal 40 kHz RC with calibration

– 32 kHz oscillator for RTC with calibration

■ Low power

– Sleep, Stop and Standby modes

–V

■ 3 × 12-bit, 1 µs A/D converters (up to 21

supply for RTC and backup registers

BAT

channels)

– Conversion range: 0 to 3.6 V

– Triple-sample and hold capability

– Temperature sensor

■ 2 × 12-bit D/A converters

■ DMA: 12-channel DMA controller

– Supported peripherals: timers, ADCs, DAC,

SDIO, I

■ Debug mode

2

Ss, SPIs, I2Cs and USARTs

– Serial wire debug (SWD) & JTAG interfaces

– Cortex-M3 Embedded Trace Macrocell™

memories

■ Up to 112 fast I/O ports

– 51/80/112 I/Os, all mappable on 16

external interrupt vectors and almost all

5 V-tolerant

■ Up to 17 timers

– Up to ten 16-bit timers, each with up to 4

IC/OC/PWM or pulse counter and

quadrature (incremental) encoder input

– 2 × 16-bit motor control PWM timers with

dead-time generation and emergency stop

– 2 × watchdog timers (Independent and

Window)

– SysTick timer: a 24-bit downcounter

– 2 × 16-bit basic timers to drive the DAC

■ Up to 13 communication interfaces

– Up to 2 × I

2

C interfaces (SMBus/PMBus)

– Up to 5 USARTs (ISO 7816 interface, LIN,

IrDA capability, modem control)

– Up to 3 SPIs (18 Mbit/s), 2 with I

interface multiplexed

– CAN interface (2.0B Active)

– USB 2.0 full speed interface

– SDIO interface

■ CRC calculation unit, 96-bit unique ID

■ ECOPACK

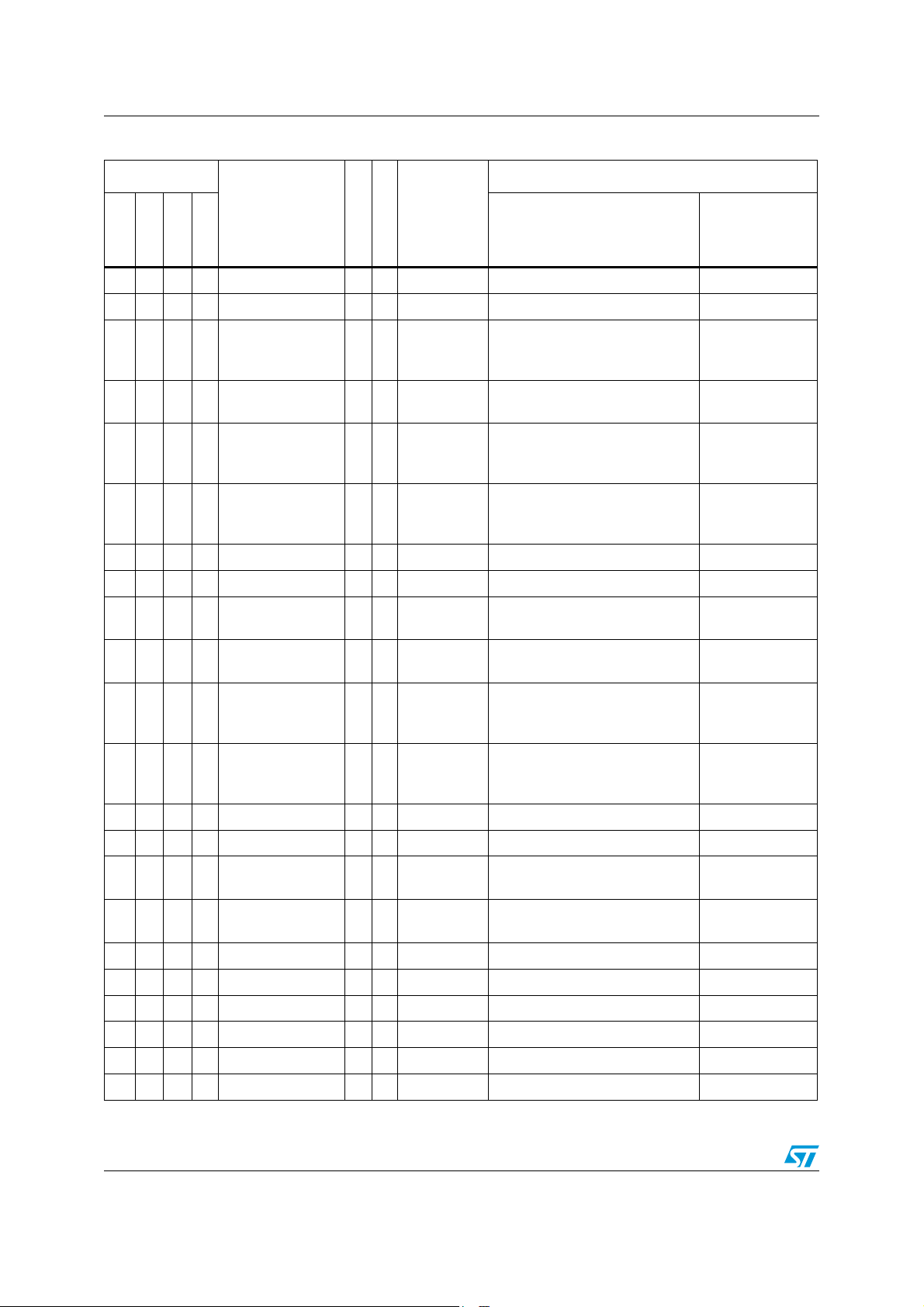

Table 1. Device summary

Reference Part number

STM32F103xF

STM32F103xG

®

packages

STM32F103RF STM32F103VF

STM32F103ZF

STM32F103RG STM32F103VG

STM32F103ZG

2

S

January 2012 Doc ID 16554 Rev 3 1/120

This is preliminary information on a new product foreseen to be developed. Details are subject to change without notice.

www.st.com

1

Contents STM32F103xF, STM32F103xG

Contents

1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

2 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

2.1 Device overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.2 Full compatibility throughout the family . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.3 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.3.1 ARM® Cortex™-M3 core with embedded Flash and SRAM . . . . . . . . . 15

2.3.2 Memory protection unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.3.3 Embedded Flash memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.3.4 CRC (cyclic redundancy check) calculation unit . . . . . . . . . . . . . . . . . . 15

2.3.5 Embedded SRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

2.3.6 FSMC (flexible static memory controller) . . . . . . . . . . . . . . . . . . . . . . . . 16

2.3.7 LCD parallel interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

2.3.8 Nested vectored interrupt controller (NVIC) . . . . . . . . . . . . . . . . . . . . . . 16

2.3.9 External interrupt/event controller (EXTI) . . . . . . . . . . . . . . . . . . . . . . . 16

2.3.10 Clocks and startup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2.3.11 Boot modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2.3.12 Power supply schemes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2.3.13 Power supply supervisor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

2.3.14 Voltage regulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

2.3.15 Low-power modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

2.3.16 DMA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

2.3.17 RTC (real-time clock) and backup registers . . . . . . . . . . . . . . . . . . . . . . 19

2.3.18 Timers and watchdogs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

2.3.19 I²C bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

2.3.20 Universal synchronous/asynchronous receiver transmitters (USARTs) 21

2.3.21 Serial peripheral interface (SPI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

2.3.22 Inter-integrated sound (I

2

S) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

2.3.23 SDIO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

2.3.24 Controller area network (CAN) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

2.3.25 Universal serial bus (USB) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

2.3.26 GPIOs (general-purpose inputs/outputs) . . . . . . . . . . . . . . . . . . . . . . . . 22

2.3.27 ADC (analog to digital converter) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

2.3.28 DAC (digital-to-analog converter) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

2/120 Doc ID 16554 Rev 3

STM32F103xF, STM32F103xG Contents

2.3.29 Temperature sensor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

2.3.30 Serial wire JTAG debug port (SWJ-DP) . . . . . . . . . . . . . . . . . . . . . . . . . 24

2.3.31 Embedded Trace Macrocell™ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

3 Pinouts and pin descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

4 Memory mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

5 Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

5.1 Parameter conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

5.1.1 Minimum and maximum values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

5.1.2 Typical values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

5.1.3 Typical curves . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

5.1.4 Loading capacitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

5.1.5 Pin input voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

5.1.6 Power supply scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

5.1.7 Current consumption measurement . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

5.2 Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

5.3 Operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

5.3.1 General operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

5.3.2 Operating conditions at power-up / power-down . . . . . . . . . . . . . . . . . . 42

5.3.3 Embedded reset and power control block characteristics . . . . . . . . . . . 42

5.3.4 Embedded reference voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

5.3.5 Supply current characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

5.3.6 External clock source characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

5.3.7 Internal clock source characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

5.3.8 PLL characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

5.3.9 Memory characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

5.3.10 FSMC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

5.3.11 EMC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

5.3.12 Absolute maximum ratings (electrical sensitivity) . . . . . . . . . . . . . . . . . 82

5.3.13 I/O current injection characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

5.3.14 I/O port characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

5.3.15 NRST pin characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

5.3.16 TIM timer characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

5.3.17 Communications interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

5.3.18 CAN (controller area network) interface . . . . . . . . . . . . . . . . . . . . . . . . 100

Doc ID 16554 Rev 3 3/120

Contents STM32F103xF, STM32F103xG

5.3.19 12-bit ADC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

5.3.20 DAC electrical specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

5.3.21 Temperature sensor characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

6 Package characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

6.1 Package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

6.2 Thermal characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

6.2.1 Reference document . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

6.2.2 Selecting the product temperature range . . . . . . . . . . . . . . . . . . . . . . . 115

7 Part numbering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

8 Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

4/120 Doc ID 16554 Rev 3

STM32F103xF, STM32F103xG List of tables

List of tables

Table 1. Device summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Table 2. STM32F103xF and STM32F103xG features and peripheral counts . . . . . . . . . . . . . . . . . 11

Table 3. STM32F103xx family . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Table 4. STM32F103xF and STM32F103xG timer feature comparison . . . . . . . . . . . . . . . . . . . . . . 19

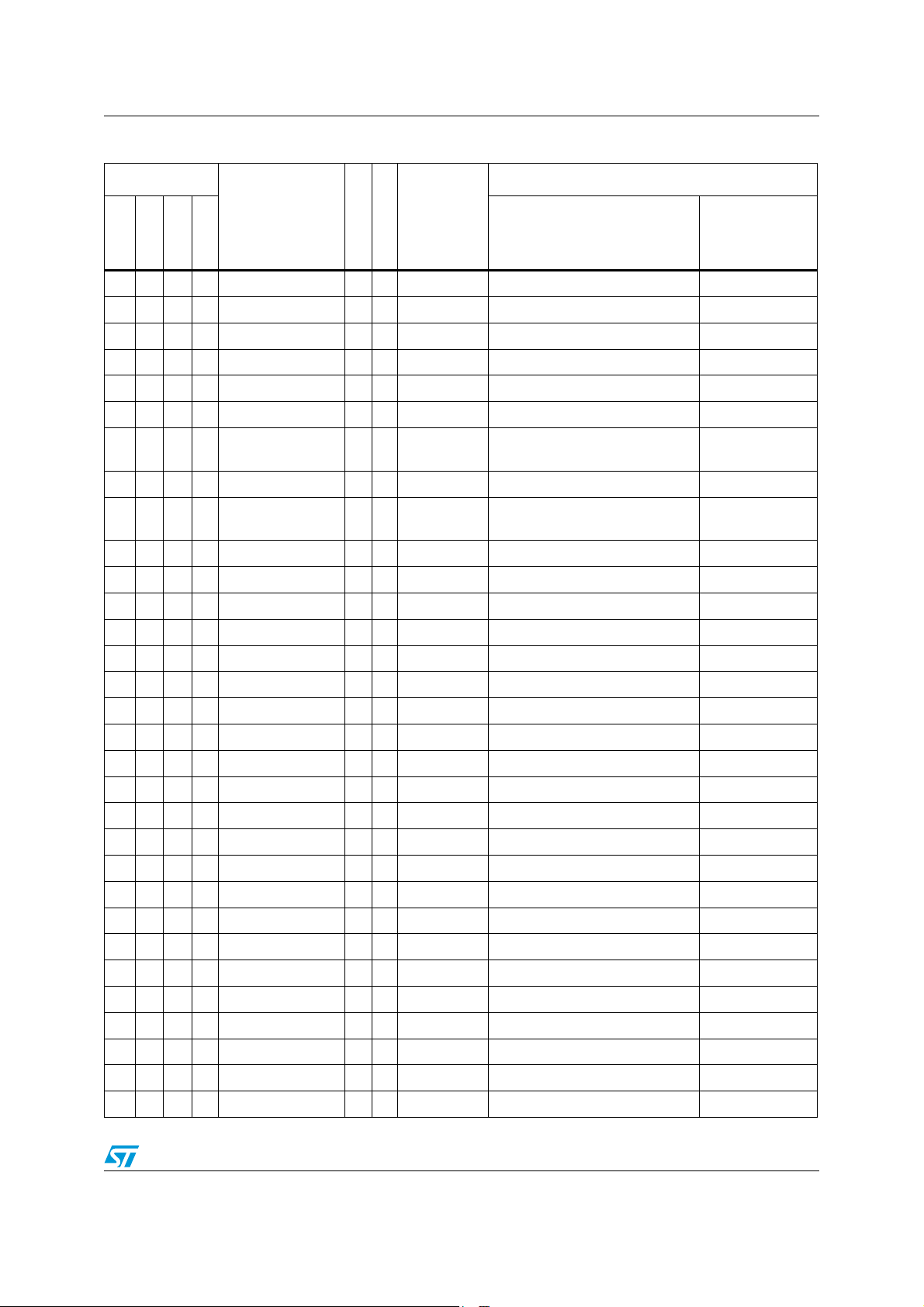

Table 5. STM32F103xF and STM32F103xG pin definitions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Table 6. FSMC pin definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Table 7. Voltage characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Table 8. Current characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Table 9. Thermal characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Table 10. General operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Table 11. Operating conditions at power-up / power-down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Table 12. Embedded reset and power control block characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . 42

Table 13. Embedded internal reference voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Table 14. Maximum current consumption in Run mode, code with data processing

running from Flash . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Table 15. Maximum current consumption in Run mode, code with data processing

running from RAM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Table 16. Maximum current consumption in Sleep mode, code running from Flash or RAM. . . . . . . 46

Table 17. Typical and maximum current consumptions in Stop and Standby modes . . . . . . . . . . . . 47

Table 18. Typical current consumption in Run mode, code with data processing

running from Flash . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Table 19. Typical current consumption in Sleep mode, code running from Flash or

RAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Table 20. Peripheral current consumption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Table 21. High-speed external user clock characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Table 22. Low-speed external user clock characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Table 23. HSE 4-16 MHz oscillator characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Table 24. LSE oscillator characteristics (f

Table 25. HSI oscillator characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Table 26. LSI oscillator characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Table 27. Low-power mode wakeup timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Table 28. PLL characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Table 29. Flash memory characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Table 30. Flash memory endurance and data retention . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Table 31. Asynchronous non-multiplexed SRAM/PSRAM/NOR read timings . . . . . . . . . . . . . . . . . . 63

Table 32. Asynchronous non-multiplexed SRAM/PSRAM/NOR write timings . . . . . . . . . . . . . . . . . . 64

Table 33. Asynchronous read muxed . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Table 34. Asynchronous multiplexed PSRAM/NOR read timings. . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Table 35. Asynchronous multiplexed PSRAM/NOR write timings . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Table 36. Synchronous multiplexed NOR/PSRAM read timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Table 37. Synchronous multiplexed PSRAM write timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Table 38. Synchronous non-multiplexed NOR/PSRAM read timings . . . . . . . . . . . . . . . . . . . . . . . . . 71

Table 39. Synchronous non-multiplexed PSRAM write timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Table 40. Switching characteristics for PC Card/CF read and write cycles in

attribute/common space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Table 41. Switching characteristics for PC Card/CF read and write cycles in I/O space . . . . . . . . . . 78

Table 42. Switching characteristics for NAND Flash read cycles . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

Table 43. Switching characteristics for NAND Flash write cycles. . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

= 32.768 kHz) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

LSE

Doc ID 16554 Rev 3 5/120

List of tables STM32F103xF, STM32F103xG

Table 44. EMS characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Table 45. EMI characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Table 46. ESD absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

Table 47. Electrical sensitivities . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Table 48. I/O current injection susceptibility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Table 49. I/O static characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Table 50. Output voltage characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Table 51. I/O AC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

Table 52. NRST pin characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Table 53. TIMx characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Table 54. I

Table 55. SCL frequency (f

Table 56. SPI characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Table 57. I

2

C characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

= 36 MHz.,VDD = 3.3 V) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

PCLK1

2

S characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

Table 58. SD / MMC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

Table 59. USB startup time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

Table 60. USB DC electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

Table 61. USB: full-speed electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

Table 62. ADC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

Table 63. R

max for f

AIN

= 14 MHz . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

ADC

Table 64. ADC accuracy - limited test conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Table 65. ADC accuracy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Table 66. DAC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

Table 67. TS characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

Table 68. LFBGA144 – 144-ball low profile fine pitch ball grid array, 10 x 10 mm,

0.8 mm pitch, package data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Table 69. LQFP144, 20 x 20 mm, 144-pin low-profile quad flat package mechanical data . . . . . . . 111

Table 70. LQPF100 – 14 x 14 mm 100-pin low-profile quad flat package mechanical data. . . . . . . 112

Table 71. LQFP64 – 10 x 10 mm 64 pin low-profile quad flat package mechanical data. . . . . . . . . 113

Table 72. Package thermal characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

Table 73. STM32F103xF and STM32F103xG ordering information scheme . . . . . . . . . . . . . . . . . . 117

6/120 Doc ID 16554 Rev 3

STM32F103xF, STM32F103xG List of figures

List of figures

Figure 1. STM32F103xF and STM32F103xG performance line block diagram. . . . . . . . . . . . . . . . . 12

Figure 2. Clock tree . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

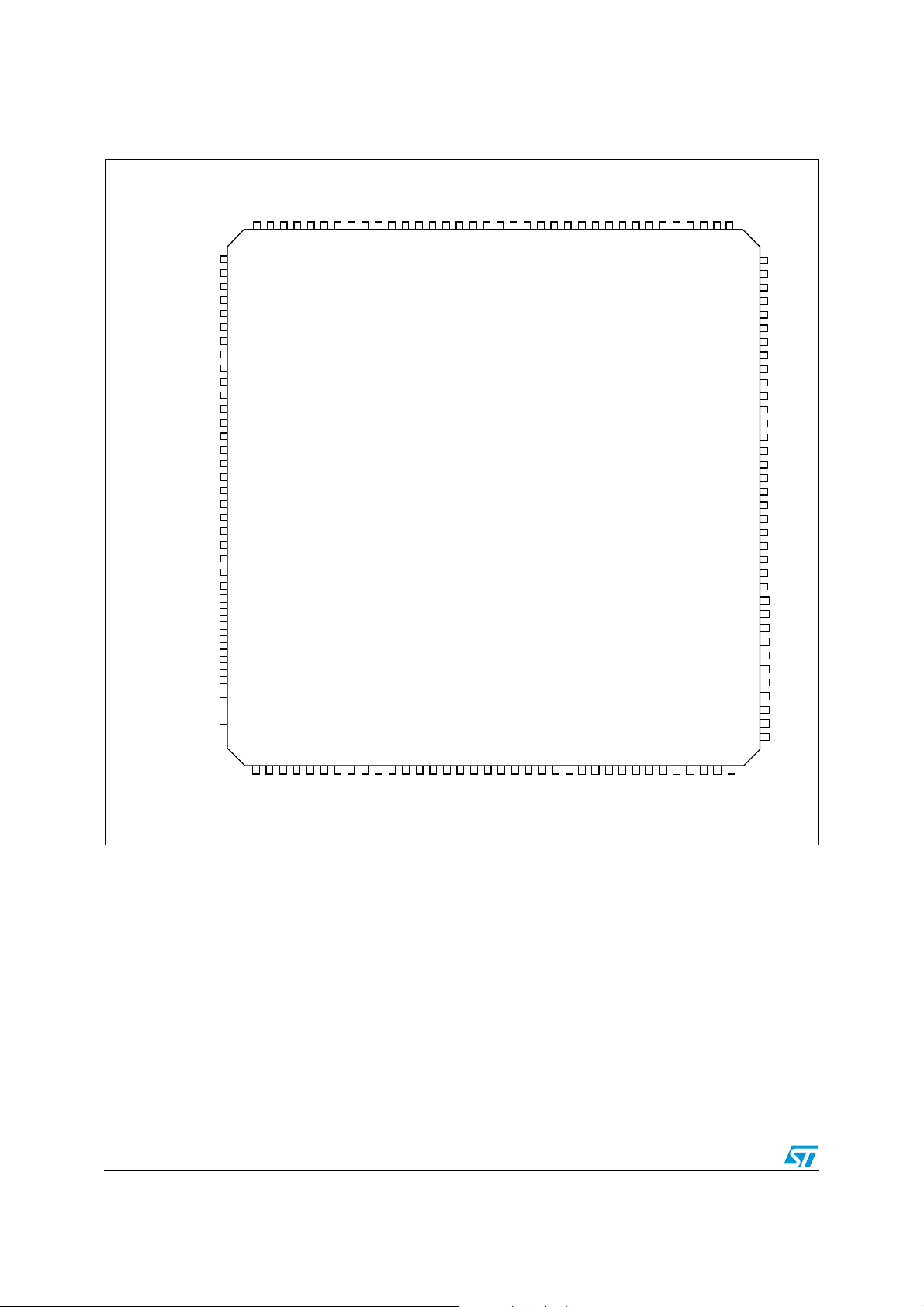

Figure 3. STM32F103xF and STM32F103xG XL-density performance line BGA144 ballout . . . . . . 25

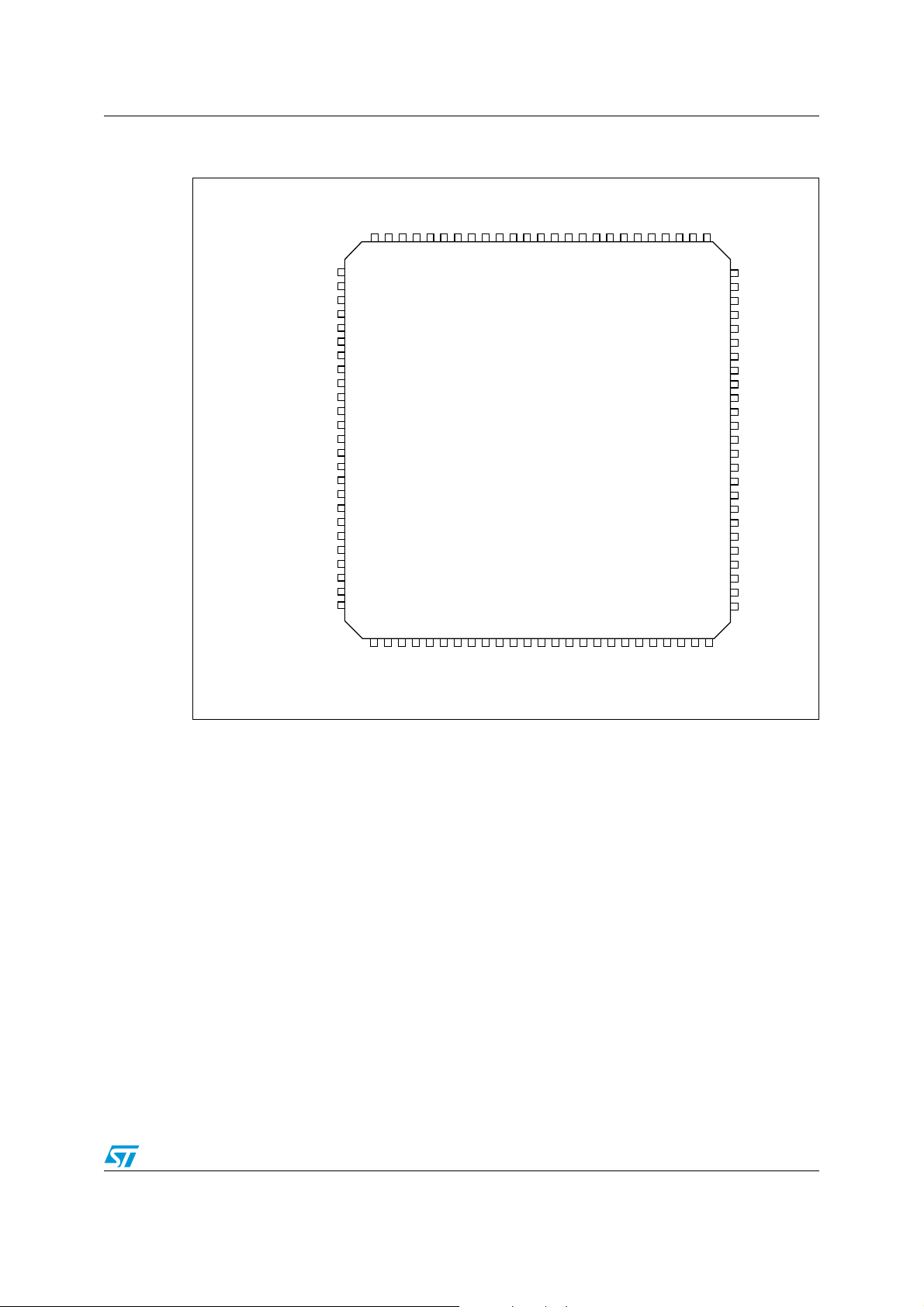

Figure 4. STM32F103xF and STM32F103xG XL-density performance line LQFP144 pinout. . . . . . 26

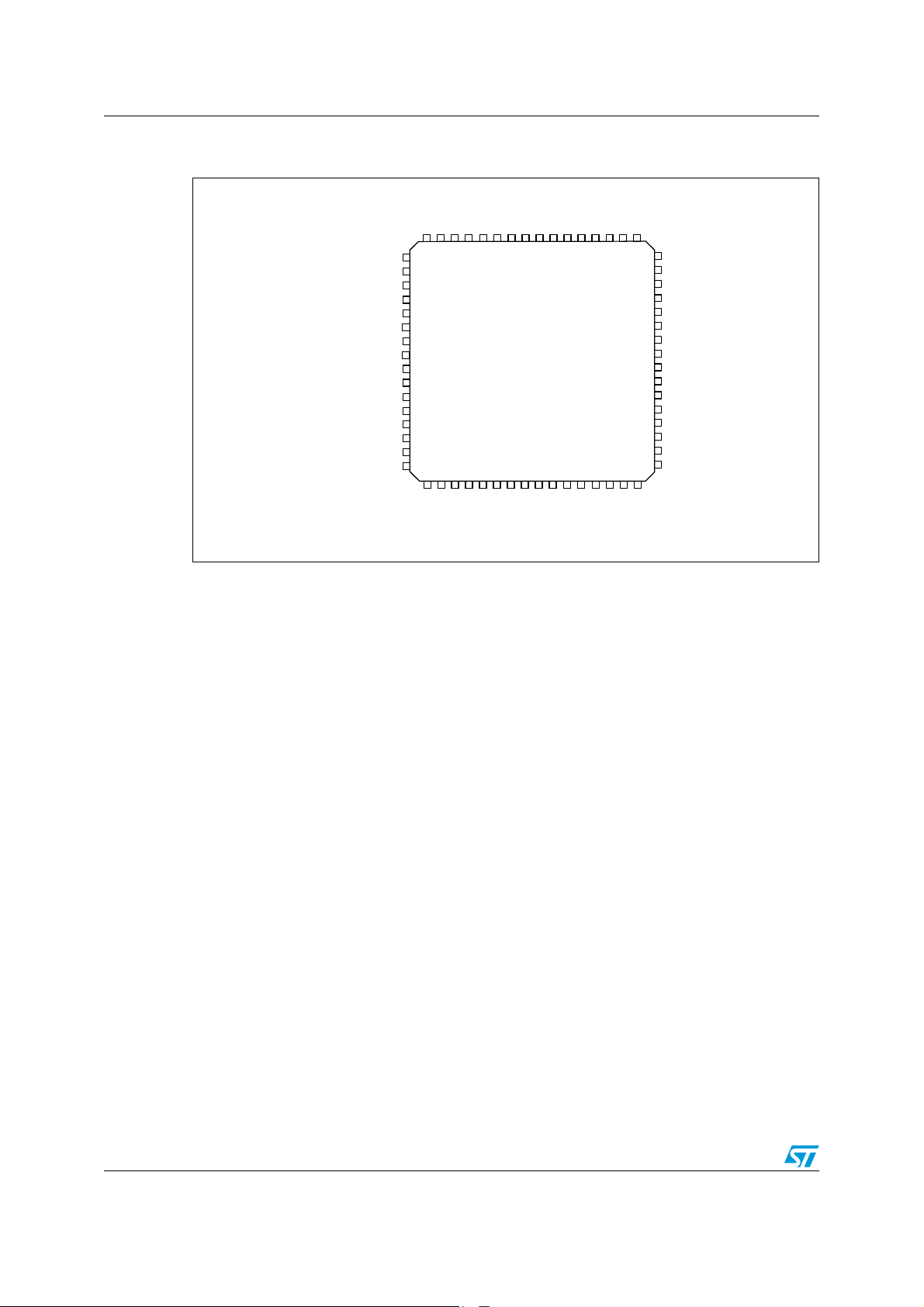

Figure 5. STM32F103xF and STM32F103xG XL-density performance line LQFP100 pinout. . . . . . 27

Figure 6. STM32F103xF and STM32F103xG XL-density performance line

LQFP64 pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Figure 7. Memory map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Figure 8. Pin loading conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Figure 9. Pin input voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Figure 10. Power supply scheme. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Figure 11. Current consumption measurement scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Figure 12. Typical current consumption in Run mode versus frequency (at 3.6 V) -

code with data processing running from RAM, peripherals enabled . . . . . . . . . . . . . . . . . 45

Figure 13. Typical current consumption in Run mode versus frequency (at 3.6 V)-

code with data processing running from RAM, peripherals disabled . . . . . . . . . . . . . . . . 45

Figure 14. Typical current consumption on V

values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Figure 15. Typical current consumption in Stop mode with regulator in run mode

versus temperature at different V

Figure 16. Typical current consumption in Stop mode with regulator in low-power

mode versus temperature at different V

Figure 17. Typical current consumption in Standby mode versus temperature at

different V

values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

DD

Figure 18. High-speed external clock source AC timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Figure 19. Low-speed external clock source AC timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Figure 20. Typical application with an 8 MHz crystal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Figure 21. Typical application with a 32.768 kHz crystal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Figure 22. Asynchronous non-multiplexed SRAM/PSRAM/NOR read waveforms . . . . . . . . . . . . . . . 62

Figure 23. Asynchronous non-multiplexed SRAM/PSRAM/NOR write waveforms . . . . . . . . . . . . . . . 63

Figure 24. Asynchronous multiplexed PSRAM/NOR read waveforms. . . . . . . . . . . . . . . . . . . . . . . . . 65

Figure 25. Asynchronous multiplexed PSRAM/NOR write waveforms . . . . . . . . . . . . . . . . . . . . . . . . 66

Figure 26. Synchronous multiplexed NOR/PSRAM read timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

Figure 27. Synchronous multiplexed PSRAM write timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Figure 28. Synchronous non-multiplexed NOR/PSRAM read timings . . . . . . . . . . . . . . . . . . . . . . . . . 71

Figure 29. Synchronous non-multiplexed PSRAM write timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Figure 30. PC Card/CompactFlash controller waveforms for common memory read access . . . . . . . 73

Figure 31. PC Card/CompactFlash controller waveforms for common memory write access . . . . . . . 74

Figure 32. PC Card/CompactFlash controller waveforms for attribute memory read

access. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

Figure 33. PC Card/CompactFlash controller waveforms for attribute memory write

access. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

Figure 34. PC Card/CompactFlash controller waveforms for I/O space read access . . . . . . . . . . . . . 76

Figure 35. PC Card/CompactFlash controller waveforms for I/O space write access . . . . . . . . . . . . . 77

Figure 36. NAND controller waveforms for read access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Figure 37. NAND controller waveforms for write access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

Figure 38. NAND controller waveforms for common memory read access . . . . . . . . . . . . . . . . . . . . . 79

Figure 39. NAND controller waveforms for common memory write access . . . . . . . . . . . . . . . . . . . . . 80

with RTC on vs. temperature at different V

BAT

values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

DD

values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

DD

BAT

Doc ID 16554 Rev 3 7/120

List of figures STM32F103xF, STM32F103xG

Figure 40. Standard I/O input characteristics - CMOS port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Figure 41. Standard I/O input characteristics - TTL port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Figure 42. 5 V tolerant I/O input characteristics - CMOS port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Figure 43. 5 V tolerant I/O input characteristics - TTL port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Figure 44. I/O AC characteristics definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Figure 45. Recommended NRST pin protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Figure 46. I

Figure 47. SPI timing diagram - slave mode and CPHA = 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

Figure 48. SPI timing diagram - slave mode and CPHA = 1

Figure 49. SPI timing diagram - master mode

Figure 50. I

Figure 51. I

2

C bus AC waveforms and measurement circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

(1)

(1)

2

S slave timing diagram (Philips protocol)

2

S master timing diagram (Philips protocol)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

(1)

(1)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

Figure 52. SDIO high-speed mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Figure 53. SD default mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Figure 54. USB timings: definition of data signal rise and fall time . . . . . . . . . . . . . . . . . . . . . . . . . . 100

Figure 55. ADC accuracy characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 103

Figure 56. Typical connection diagram using the ADC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

Figure 57. Power supply and reference decoupling (V

Figure 58. Power supply and reference decoupling (V

not connected to V

REF+

connected to V

REF+

). . . . . . . . . . . . . 104

DDA

). . . . . . . . . . . . . . . . 105

DDA

Figure 59. 12-bit buffered /non-buffered DAC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

Figure 60. Recommended PCB design rules (0.80/0.75 mm pitch BGA . . . . . . . . . . . . . . . . . . . . . . 109

Figure 61. LFBGA144 – 144-ball low profile fine pitch ball grid array, 10 x 10 mm,

0.8 mm pitch, package outline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Figure 62. LQFP144, 20 x 20 mm, 144-pin low-profile quad

flat package outline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

Figure 63. Recommended footprint

Figure 64. LQFP100, 14 x 14 mm 100-pin low-profile quad flat package outline . . . . . . . . . . . . . . . 112

Figure 65. Recommended footprint

Figure 66. LQFP64 – 10 x 10 mm 64 pin low-profile quad flat package outline . . . . . . . . . . . . . . . . 113

Figure 67. Recommended footprint

Figure 68. LQFP100 P

max vs. TA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

D

(1)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

(1)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

(1)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

8/120 Doc ID 16554 Rev 3

STM32F103xF, STM32F103xG Introduction

1 Introduction

This datasheet provides the ordering information and mechanical device characteristics of

the STM32F103xF and STM32F103xG XL-density performance line microcontrollers. For

more details on the whole STMicroelectronics STM32F103xx family, please refer to

Section 2.2: Full compatibility throughout the family.

The XL-density STM32F103xx datasheet should be read in conjunction with the

STM32F10xxx reference manual.

For information on programming, erasing and protection of the internal Flash memory

please refer to the STM32F10xxx Flash programming manual.

The reference and Flash programming manuals are both available from the

STMicroelectronics website www.st.com.

For information on the Cortex™-M3 core please refer to the Cortex™-M3 Technical

Reference Manual, available from the www.arm.com website at the following address:

http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.ddi0337e/.

Doc ID 16554 Rev 3 9/120

Description STM32F103xF, STM32F103xG

2 Description

The STM32F103xF and STM32F103xG performance line family incorporates the high-

performance ARM

®

Cortex™-M3 32-bit RISC core operating at a 72 MHz frequency, highspeed embedded memories (Flash memory up to 1 Mbyte and SRAM up to 96 Kbytes), and

an extensive range of enhanced I/Os and peripherals connected to two APB buses. All

devices offer three 12-bit ADCs, ten general-purpose 16-bit timers plus two PWM timers, as

well as standard and advanced communication interfaces: up to two I

2

I

Ss, one SDIO, five USARTs, an USB and a CAN.

2

Cs, three SPIs, two

The STM32F103xx XL-density performance line family operates in the –40 to +105 °C

temperature range, from a 2.0 to 3.6

V power supply. A comprehensive set of power-saving

mode allows the design of low-power applications.

These features make the STM32F103xx high-density performance line microcontroller

family suitable for a wide range of applications such as motor drives, application control,

medical and handheld equipment, PC and gaming peripherals, GPS platforms, industrial

applications, PLCs, inverters, printers, scanners, alarm systems and video intercom.

10/120 Doc ID 16554 Rev 3

STM32F103xF, STM32F103xG Description

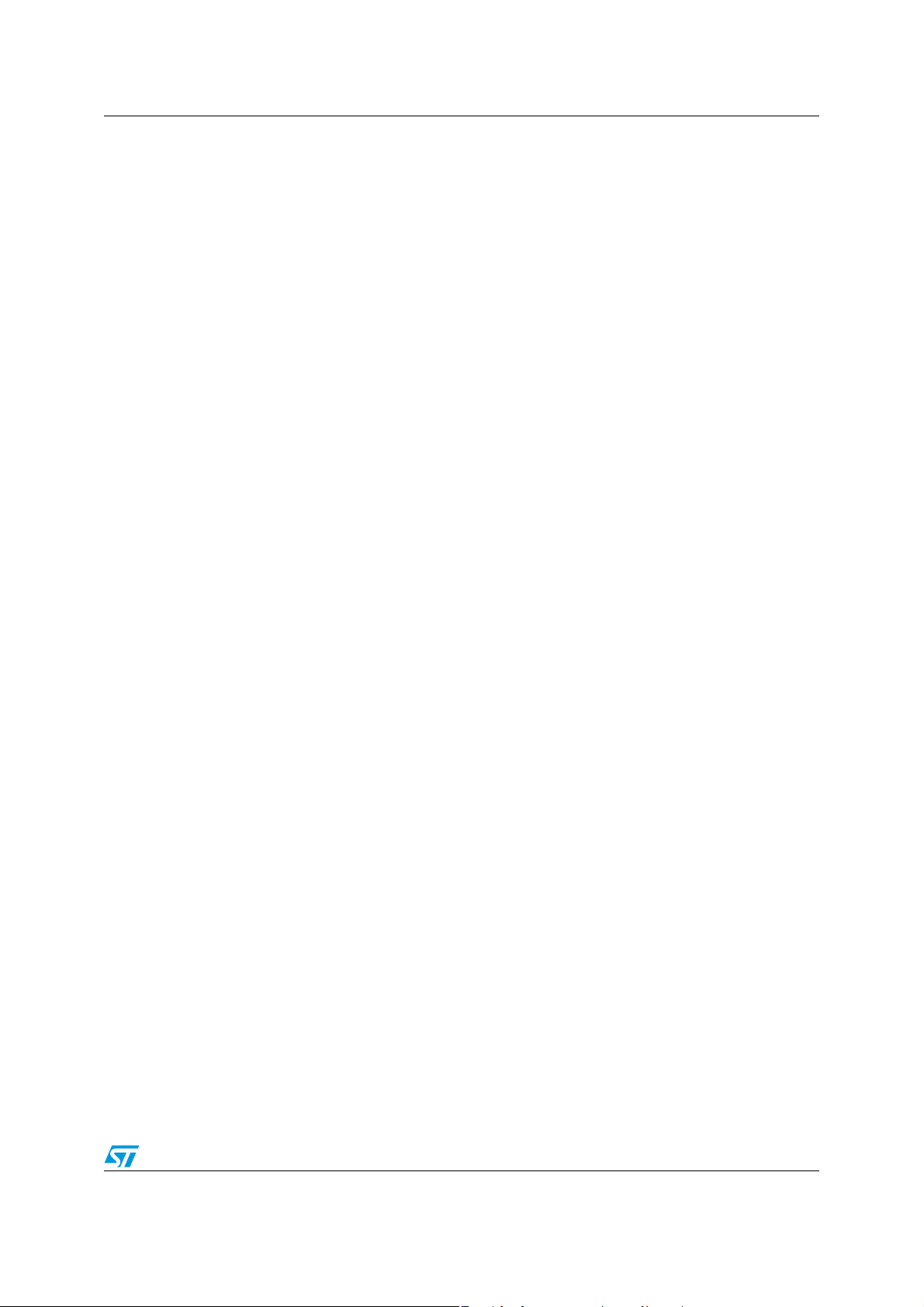

2.1 Device overview

The STM32F103xx XL-density performance line family offers devices in four different

package types: from 64 pins to 144 pins. Depending on the device chosen, different sets of

peripherals are included, the description below gives an overview of the complete range of

peripherals proposed in this family.

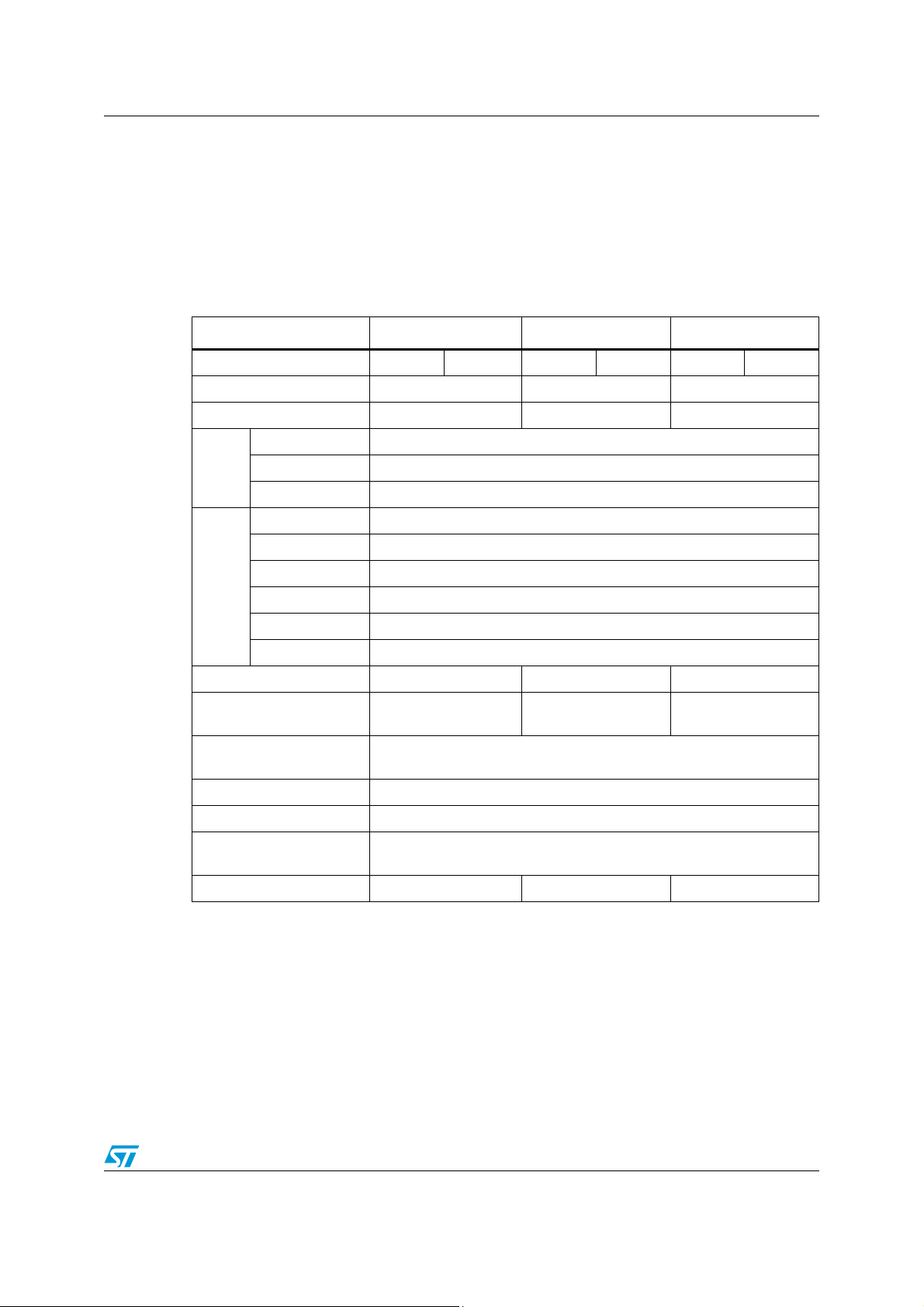

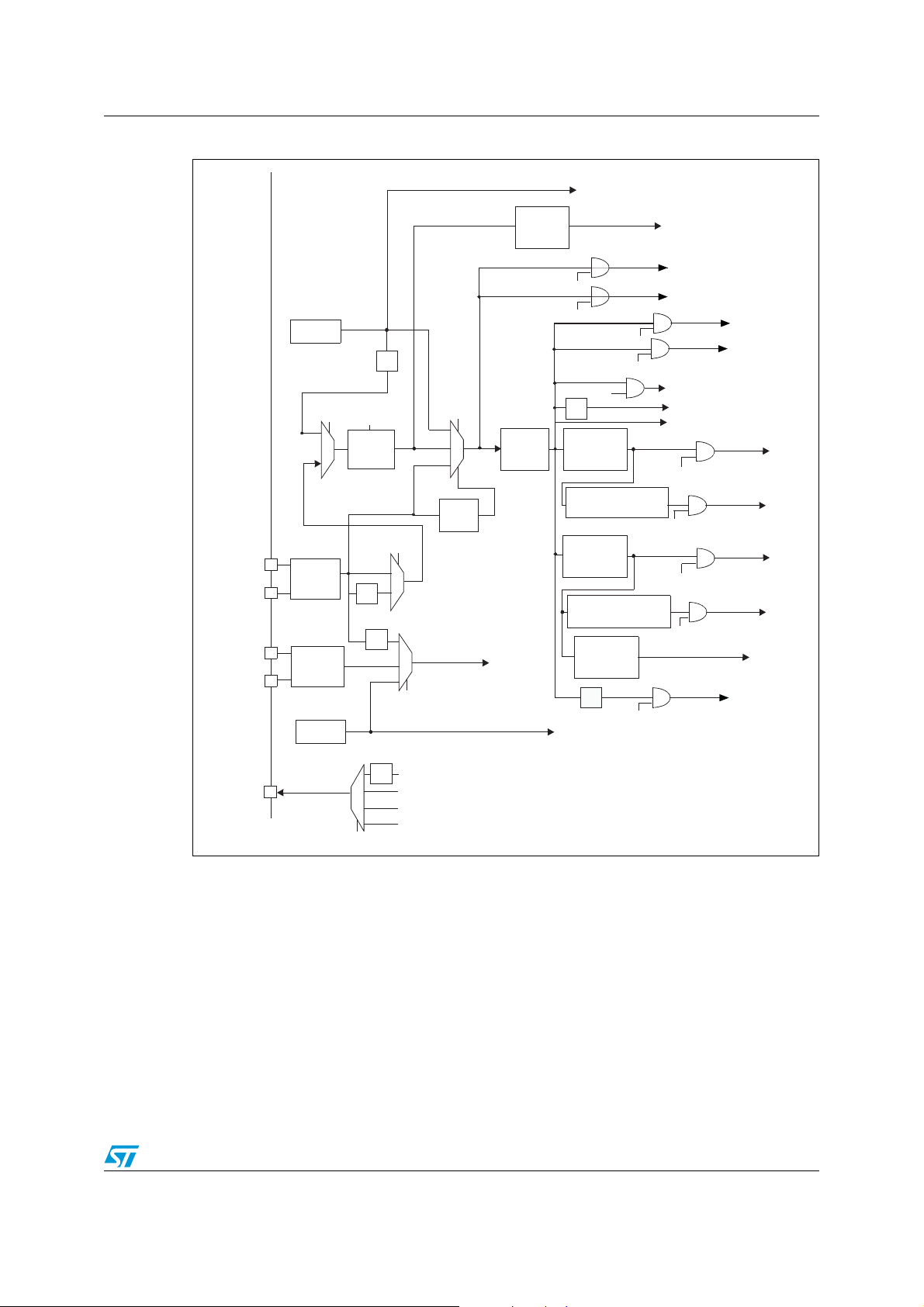

Figure 1 shows the general block diagram of the device family.

Table 2. STM32F103xF and STM32F103xG features and peripheral counts

Peripherals STM32F103Rx STM32F103Vx STM32F103Zx

Flash memory 768 KB 1 MB 768 KB 1 MB 768 KB 1 MB

SRAM in Kbytes 96 96 96

FSMC No Yes

General-purpose 10

Timers

Advanced-control 2

Basic 2

SPI(I2S)

2

I

(2)

3(2)

C2

(1)

Ye s

Comm

USART 5

USB 1

CAN 1

SDIO 1

GPIOs 51 80 112

12-bit ADC

Number of channels

12-bit DAC

Number of channels

16

3

16

3

3

21

2

2

CPU frequency 72 MHz

Operating voltage 2.0 to 3.6 V

Operating temperatures

Ambient temperatures: –40 to +85 °C /–40 to +105 °C (see Ta b l e 1 0 )

Junction temperature: –40 to + 125 °C (see Table 10)

Package LQFP64 LQFP100 LQFP144, BGA144

1. For the LQFP100 package, only FSMC Bank1 and Bank2 are available. Bank1 can only support a

multiplexed NOR/PSRAM memory using the NE1 Chip Select. Bank2 can only support a 16- or 8-bit NAND

Flash memory using the NCE2 Chip Select. The interrupt line cannot be used since Port G is not available

in this package.

2. The SPI2 and SPI3 interfaces give the flexibility to work in an exclusive way in either the SPI mode or the

2

I

S audio mode.

Doc ID 16554 Rev 3 11/120

PA[ 15:0 ]

EXT.IT

WWDG

NVIC

12bit A DC1

8 ADINs common

JTDI

JTCK/SWCLK

JTMS/SWDA T

NJTRST

JTDO

=2 to 3.6V

112 AF

AHB2

MOSI/SD,MISO,

WKUP

F

max

: 48/72 MHz

V

SS

SCL,SDA,SMBA

I2C2

GP DMA1

XTAL OSC

4-16 MHz

XTAL 32 kHz

A

P

B

1:

F

m

a

x

=2

4

/

3

6MHz

HCLK

PCLK1

as AF

Flash1 512 KB

VOLT. RE G.

3.3VTO1.8V

POWER

Backupinterface

as AF

B

us matrix

64 bit

RTC

RC HS

Cortex-M3 CPU

Ibus

Dbus

obl

SRAM 512B

USART1

USART2

SPI2/I2S2

bxCAN device

7channels

Backup

reg

4channels

TIM1

4compl.

SCL,SDA,SMBA

I2C1

as AF

RX,TX, CTS,RTS,

USART3

Temp sen sor

4Ch,ETRas AF

FCLK

RC LS

Standby

IWDG

@VSW

POR / PD R

SUPPLY

@VDDA

V

BAT

=1.8Vto3.6V

CK as AF

RX,TX, CTS,RTS,

CK as AF

RX,TX, CTS,RTS,

CK as AF

A

PB

2:

F

m

a

x

=48 /

72

MH

z

NVIC

SPI1

MOSI,MISO,

SCK,NSS as AF

12bit A DC2

IF

IF

interface

SUPERVISION

PVD

Reset

Int

AWU

POR

TAMPER-RTC

System

SCK/CK ,NSS/WS,

UART4

RX,TX as AF

UART5

RX,TX as AF

Reset &

clock

controller

PCLK2

PLL

12bit DAC1

IFIF

IF

12bit DA C2

DAC1_OUT as AF

DAC2_OUT as AF

to the 3 ADCs

8 ADINs commo n

to the ADC1 & 2

GP DMA2

5channels

(ALARM OUT)

MCLK as AF

MOSI/SD,MISO,

SCK/CK ,NSS/WS,

MCLK as AF

SWJTAG

TPIU

ETM

Trace/Trig

TRACECL K

TRACED[ 0:3]

as AF

USBDM/CAN_RX

USBDP/CAN_TX

SDIO

FSMC

PCLK3

SRAM

96 Kbyte

64 bit

12bit ADC3

IF

5ADINs on ADC3

4

4compl.

BKIN, ETR input as AF

PB[15:0]

PC[ 15:0]

PD[15:0]

PE[1 5:0]

PF[15:0]

PG[15:0]

MPU

2 as AF

1 as AF

1 as AF

4Ch,ETRas AF

4Ch,ETRas AF

4Ch,ETRas AF

D[7: 0], CMD

CK as AF

Flash2 512 KB

A[25:0]

D[15:0]

CLK

NOE

NWE

NE[3:0]

NBL[1:0]

NWAIT

NL

as AF

channels

channels

channels

channels

channel

channel

TIM8

TIM9

TIM10

TIM11

V

REF+

V

REF–

TIM6

TIM7

TIM2

TIM3

TIM4

TIM5

TIM12

TIM13

TIM14

OSC_IN

OSC_OUT

OSC32_IN

OSC32_OUT

V

DD

@V

DD

NRST

V

DDA

V

SSA

V

DD

@V

DD

@V

DDA

@V

DDA

Flash

interface

Flash

interface

obl

2 channels as AF

1 channel as AF

1 channel as AF

ai17352

@V

DDA

GPIO port A

GPIO port B

GPIO port C

GPIO port D

GPIO port E

GPIO port F

GPIO port G

APB3 APB2 APB1

BKIN, ETR input as AF

USB 2.0 FS device

SPI3/I2S3

Description STM32F103xF, STM32F103xG

Figure 1. STM32F103xF and STM32F103xG performance line block diagram

1. TA = –40 °C to +85 °C (suffix 6, see Table 73) or –40 °C to +105 °C (suffix 7, see Table 73), junction temperature up to

2. AF = alternate function on I/O port pin.

105 °C or 125 °C, respectively.

12/120 Doc ID 16554 Rev 3

STM32F103xF, STM32F103xG Description

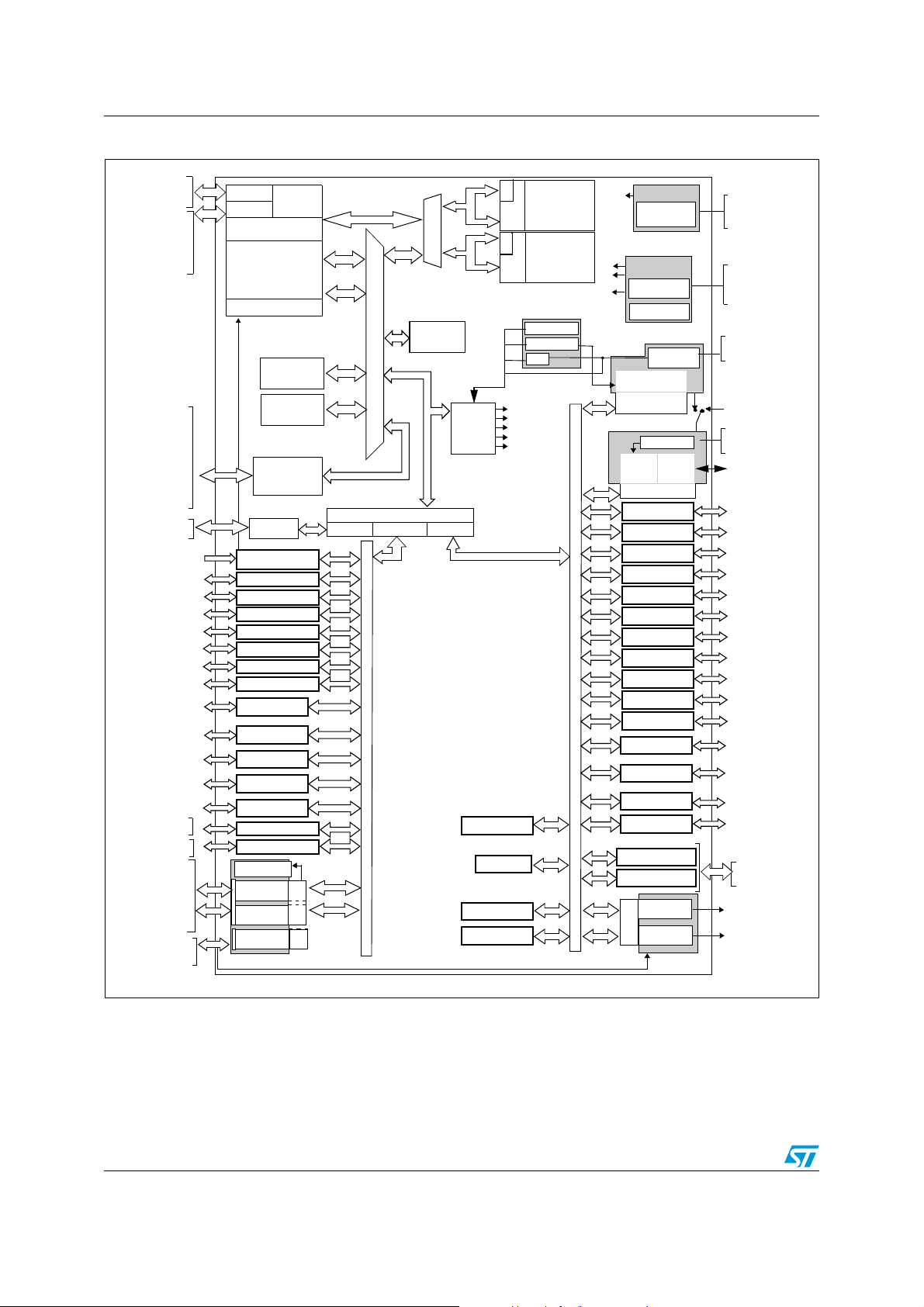

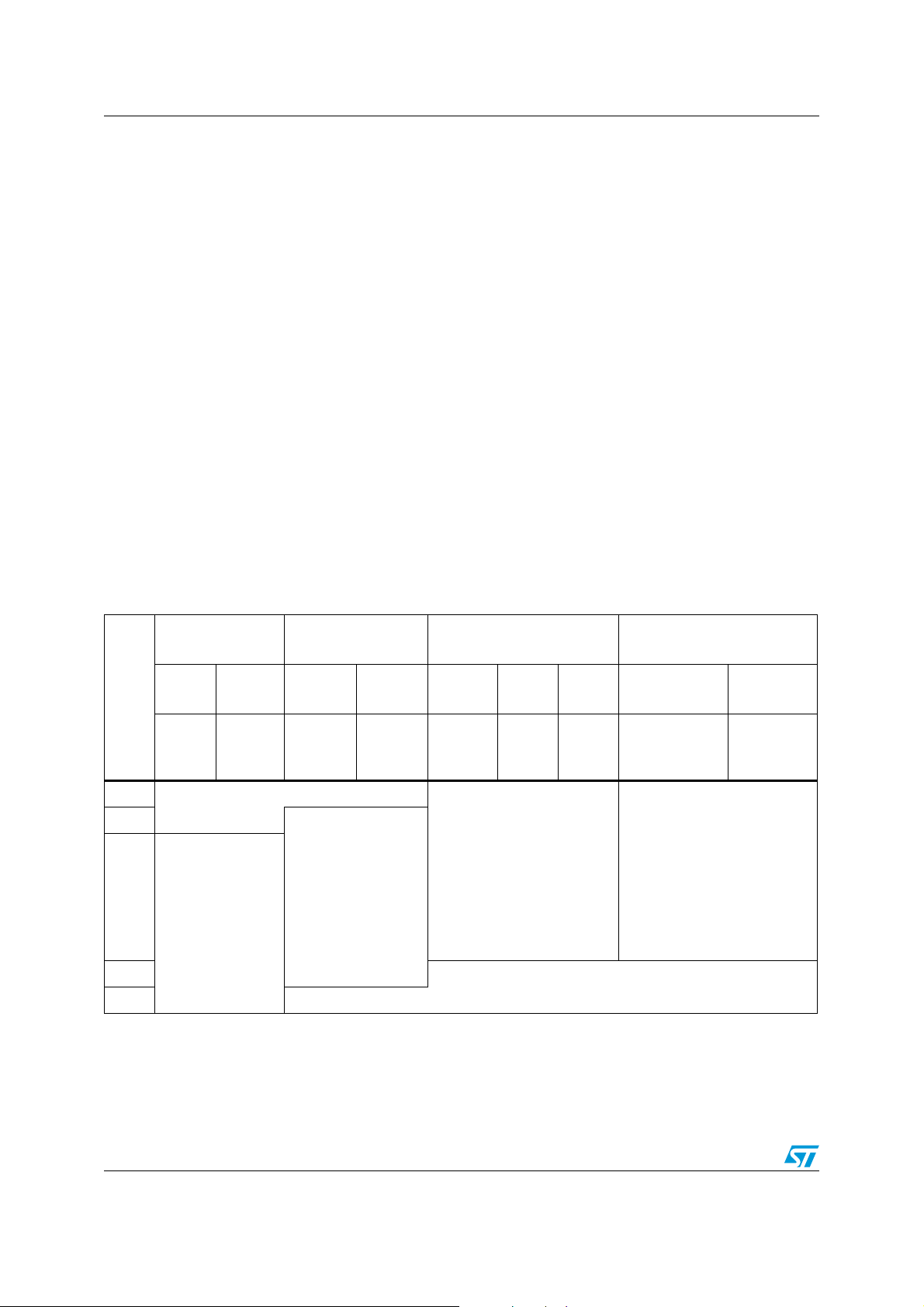

Figure 2. Clock tree

FLITFCLK

to Flash programming interface

USBCLK

to USB interface

I2S3CLK

I2S2CLK

36 MHz max

Peripheral Clock

Enable

else x2

72 MHz max

Peripheral Clock

Enable

else x2

ADCCLK

Peripheral clock

enable

to I2S3

to I2S2

SDIOCLK

FSMCCLK

HCLK

to AHB bus, core,

memory and DMA

to SDIO

to FSMC

to Cortex System timer

FCLK Cortex

free running clock

Peripheral Clock

Enable

PCLK1

to APB1

peripherals

to TIM2/3/4/5/12/13/14

and TIM6/7

TIMxCLK

PCLK2

peripherals to APB2

to TIM1/8

and TIM9/10/11

TIMxCLK

Peripheral Clock

Enable

to ADC1, 2 or 3

HCLK/2

To SDIO AHB interface

OSC_OUT

OSC_IN

OSC32_IN

OSC32_OUT

8 MHz

HSI RC

PLLSRC

4-16 MHz

HSE OSC

LSE OSC

32.768 kHz

LSI RC

40 kHz

HSI

PLLMUL

..., x16

x2, x3, x4

PLL

PLLXTPRE

/2

/128

LSE

RTCSEL[1:0]

LSI

/2

SW

HSI

PLLCLK

HSE

CSS

RTCCLK

to Independent Watchdog (IWDG)

SYSCLK

72 MHz

max

to RTC

AHB

Prescaler

/1, 2..512

IWDGCLK

USB

Prescaler

/1, 1.5

Peripheral clock

enable

Peripheral clock

enable

/1, 2, 4, 8, 16

TIM2,3,4,5,12,13,14,6,7

If (APB1 prescaler =1) x1

/1, 2, 4, 8, 16

48 MHz

Peripheral clock

enable

Peripheral clock

enable

72 MHz max

Clock

Enable

/8

APB1

Prescaler

APB2

Prescaler

TIM1, 8, 9, 10, 11

If (APB2 prescaler =1) x1

ADC

Prescaler

/2, 4, 6, 8

/2

Legend:

HSE = High-speed external clock signal

HSI =

High-speed internal clock signal

LSI =

Low-speed internal clock signal

LSE =

Low-speed external clock signal

ai17354

MCO

Main

Clock Output

/2

PLLCLK

HSI

HSE

SYSCLK

MCO

1. When the HSI is used as a PLL clock input, the maximum system clock frequency that can be achieved is

64 MHz.

2. For the USB function to be available, both HSE and PLL must be enabled, with the USBCLK at 48 MHz.

3. To have an ADC conversion time of 1 µs, APB2 must be at 14 MHz, 28 MHz or 56 MHz.

Doc ID 16554 Rev 3 13/120

Description STM32F103xF, STM32F103xG

2.2 Full compatibility throughout the family

The STM32F103xx is a complete family whose members are fully pin-to-pin, software and

feature compatible. In the reference manual, the STM32F103x4 and STM32F103x6 are

identified as low-density devices, the STM32F103x8 and STM32F103xB are referred to as

medium-density devices, the STM32F103xC, STM32F103xD and STM32F103xE are

referred to as high-density devices and the STM32F103xF and STM32F103xG are called

XL-density devices.

Low-density, high-density and XL-density devices are an extension of the STM32F103x8/B

medium-density devices, they are specified in the STM32F103x4/6, STM32F103xC/D/E and

STM32F103xF/G datasheets, respectively. Low-density devices feature lower Flash

memory and RAM capacities, less timers and peripherals. High-density devices have higher

Flash memory and RAM capacities, and additional peripherals like SDIO, FSMC, I

DAC. XL-density devices bring even more Flash and RAM memory, and extra features,

namely an MPU, a greater number of timers and a dual bank Flash structure while

remaining fully compatible with the other members of the family.

The STM32F103x4, STM32F103x6, STM32F103xC, STM32F103xD, STM32F103xE,

STM32F103xF and STM32F103xG are a drop-in replacement for the STM32F103x8/B

devices, allowing the user to try different memory densities and providing a greater degree

of freedom during the development cycle.

Moreover, the STM32F103xx performance line family is fully compatible with all existing

STM32F101xx access line and STM32F102xx USB access line devices.

Table 3. STM32F103xx family

2

S and

Pinout

144

100

64

48

Low-density

devices

16 KB

Flash

6 KB

RAM

32 KB

Flash

10 KB

RAM

2 × USARTs

2 × 16-bit timers

1 × SPI, 1 × I

2

C,

USB, CAN,

1 × PWM timer

2 × ADCs

Medium-density

devices

64 KB

(1)

Flash

20 KB

RAM

3 × USARTs

3 × 16-bit timers

2 × SPIs, 2 × I2Cs,

USB, CAN,

1 × PWM timer

2 × ADCs

128 KB

Flash

20 KB

RAM

High-density devices XL-density devices

256 KB

Flash

48 or

64 KB

RAM

5 × USARTs

4 × 16-bit timers,

2 × basic timers

3 × SPIs, 2 × I

USB, CAN, 2 × PWM timers

3 × ADCs, 2 × DACs,

1 × SDIO

FSMC (100- and 144-pin

packages

(2)

384 KB

Flash

64 KB

RAM

(3)

)

2

512 KB

Flash

64 KB

RAM

Ss, 2 × I2Cs

768 KB Flash 1 MB Flash

96 KB RAM 96 KB RAM

5 × USARTs

10 × 16-bit timers,

2 × basic timers

3 × SPIs, 2 × I

USB, CAN, 2 × PWM timers

3 × ADCs, 2 × DACs, 1 × SDIO,

Cortex-M3 with MPU

FSMC (100- and 144-pin

packages

(4)

), dual bank Flash

memory

36

1. For orderable part numbers that do not show the A internal code after the temperature range code (6 or 7), the reference

datasheet for electrical characteristics is that of the STM32F103x8/B medium-density devices.

2. 64 KB RAM for 256 KB Flash are available on devices delivered in CSP packages only.

3. Ports F and G are not available in devices delivered in 100-pin packages.

4. Ports F and G are not available in devices delivered in 100-pin packages.

2

Ss, 2 × I2Cs

14/120 Doc ID 16554 Rev 3

STM32F103xF, STM32F103xG Description

2.3 Overview

2.3.1 ARM® Cortex™-M3 core with embedded Flash and SRAM

The ARM Cortex™-M3 processor is the latest generation of ARM processors for embedded

systems. It has been developed to provide a low-cost platform that meets the needs of MCU

implementation, with a reduced pin count and low-power consumption, while delivering

outstanding computational performance and an advanced system response to interrupts.

The ARM Cortex™-M3 32-bit RISC processor features exceptional code-efficiency,

delivering the high-performance expected from an ARM core in the memory size usually

associated with 8- and 16-bit devices.

With its embedded ARM core, STM32F103xF and STM32F103xG performance line family

is compatible with all ARM tools and software.

Figure 1 shows the general block diagram of the device family.

2.3.2 Memory protection unit

The memory protection unit (MPU) is used to separate the processing of tasks from the data

protection. The MPU can manage up to 8 protection areas that can all be further divided up

into 8 subareas. The protection area sizes are between 32 bytes and the whole 4 gigabytes

of addressable memory.

The memory protection unit is especially helpful for applications where some critical or

certified code has to be protected against the misbehavior of other tasks. It is usually

managed by an RTOS (real-time operating system). If a program accesses a memory

location that is prohibited by the MPU, the RTOS can detect it and take action. In an RTOS

environment, the kernel can dynamically update the MPU area setting, based on the

process to be executed.

The MPU is optional and can be bypassed for applications that do not need it.

2.3.3 Embedded Flash memory

768 Kbytes to 1 Mbyte of embedded Flash are available for storing programs and data. The

Flash memory is organized as two banks. The first bank has a size of 512 Kbytes. The

second bank is either 256 or 512 Kbytes depending on the device. This gives the device the

capability of writing to one bank while executing code from the other bank (read-while-write

capability).

2.3.4 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit

data word and a fixed generator polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or

storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of

verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of

the software during runtime, to be compared with a reference signature generated at linktime and stored at a given memory location.

Doc ID 16554 Rev 3 15/120

Description STM32F103xF, STM32F103xG

2.3.5 Embedded SRAM

96 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states.

2.3.6 FSMC (flexible static memory controller)

The FSMC is embedded in the STM32F103xF and STM32F103xG performance line family.

It has four Chip Select outputs supporting the following modes: PC Card/Compact Flash,

SRAM, PSRAM, NOR and NAND.

Functionality overview:

● The three FSMC interrupt lines are ORed in order to be connected to the NVIC

● Write FIFO

● Code execution from external memory except for NAND Flash and PC Card

● The targeted frequency, f

, is HCLK/2, so external access is at 36 MHz when HCLK

CLK

is at 72 MHz and external access is at 24 MHz when HCLK is at 48 MHz

2.3.7 LCD parallel interface

The FSMC can be configured to interface seamlessly with most graphic LCD controllers. It

supports the Intel 8080 and Motorola 6800 modes, and is flexible enough to adapt to

specific LCD interfaces. This LCD parallel interface capability makes it easy to build costeffective graphic applications using LCD modules with embedded controllers or highperformance solutions using external controllers with dedicated acceleration.

2.3.8 Nested vectored interrupt controller (NVIC)

The STM32F103xF and STM32F103xG performance line embeds a nested vectored

interrupt controller able to handle up to 60 maskable interrupt channels (not including the 16

interrupt lines of Cortex™-M3) and 16 priority levels.

● Closely coupled NVIC gives low latency interrupt processing

● Interrupt entry vector table address passed directly to the core

● Closely coupled NVIC core interface

● Allows early processing of interrupts

● Processing of late arriving higher priority interrupts

● Support for tail-chaining

● Processor state automatically saved

● Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimal interrupt

latency.

2.3.9 External interrupt/event controller (EXTI)

The external interrupt/event controller consists of 19 edge detector lines used to generate

interrupt/event requests. Each line can be independently configured to select the trigger

event (rising edge, falling edge, both) and can be masked independently. A pending register

maintains the status of the interrupt requests. The EXTI can detect an external line with a

pulse width shorter than the Internal APB2 clock period. Up to 112 GPIOs can be connected

to the 16 external interrupt lines.

16/120 Doc ID 16554 Rev 3

STM32F103xF, STM32F103xG Description

2.3.10 Clocks and startup

System clock selection is performed on startup, however the internal RC 8 MHz oscillator is

selected as default CPU clock on reset. An external 4-16 MHz clock can be selected, in

which case it is monitored for failure. If failure is detected, the system automatically switches

back to the internal RC oscillator. A software interrupt is generated if enabled. Similarly, full

interrupt management of the PLL clock entry is available when necessary (for example with

failure of an indirectly used external oscillator).

Several prescalers allow the configuration of the AHB frequency, the high speed APB

(APB2) and the low speed APB (APB1) domains. The maximum frequency of the AHB and

the high speed APB domains is 72 MHz. The maximum allowed frequency of the low speed

APB domain is 36 MHz. See

Figure 2 for details on the clock tree.

2.3.11 Boot modes

At startup, boot pins are used to select one of three boot options:

● Boot from user Flash: you have an option to boot from any of two memory banks. By

default, boot from Flash memory bank 1 is selected. You can choose to boot from Flash

memory bank 2 by setting a bit in the option bytes.

● Boot from system memory

● Boot from embedded SRAM

The boot loader is located in system memory. It is used to reprogram the Flash memory by

using USART1.

2.3.12 Power supply schemes

● V

● V

● V

For more details on how to connect power pins, refer to Figure 10: Power supply scheme.

= 2.0 to 3.6 V: external power supply for I/Os and the internal regulator.

DD

Provided externally through V

, V

SSA

= 2.0 to 3.6 V: external analog power supplies for ADC, DAC, Reset blocks,

DDA

RCs and PLL (minimum voltage to be applied to VDDA is 2.4 V when the ADC or DAC

is used). V

= 1.8 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup

BAT

DDA

and V

registers (through power switch) when V

2.3.13 Power supply supervisor

The device has an integrated power-on reset (POR)/power-down reset (PDR) circuitry. It is

always active, and ensures proper operation starting from/down to 2 V. The device remains

in reset mode when V

external reset circuit.

The device features an embedded programmable voltage detector (PVD) that monitors the

V

DD/VDDA

generated when V

than the V

message and/or put the MCU into a safe state. The PVD is enabled by software. Refer to

Ta bl e 12: Embedded reset and power control block characteristics for the values of

V

POR/PDR

power supply and compares it to the V

DD/VDDA

threshold. The interrupt service routine can then generate a warning

PVD

and V

PVD

pins.

DD

must be connected to VDD and VSS, respectively.

SSA

DD

is below a specified threshold, V

DD

drops below the V

PVD

.

is not present.

POR/PDR

threshold. An interrupt can be

PVD

, without the need for an

threshold and/or when VDD/V

is higher

DDA

Doc ID 16554 Rev 3 17/120

Description STM32F103xF, STM32F103xG

2.3.14 Voltage regulator

The regulator has three operation modes: main (MR), low power (LPR) and power down.

● MR is used in the nominal regulation mode (Run)

● LPR is used in the Stop modes.

● Power down is used in Standby mode: the regulator output is in high impedance: the

kernel circuitry is powered down, inducing zero consumption (but the contents of the

registers and SRAM are lost)

This regulator is always enabled after reset. It is disabled in Standby mode.

2.3.15 Low-power modes

The STM32F103xF and STM32F103xG performance line supports three low-power modes

to achieve the best compromise between low power consumption, short startup time and

available wakeup sources:

● Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can

wake up the CPU when an interrupt/event occurs.

● Stop mode

Stop mode achieves the lowest power consumption while retaining the content of

SRAM and registers. All clocks in the 1.8 V domain are stopped, the PLL, the HSI RC

and the HSE crystal oscillators are disabled. The voltage regulator can also be put

either in normal or in low-power mode.

The device can be woken up from Stop mode by any of the EXTI line. The EXTI line

source can be one of the 16 external lines, the PVD output, the RTC alarm or the USB

wakeup.

● Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal

voltage regulator is switched off so that the entire 1.8 V domain is powered off. The

PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering

Standby mode, SRAM and register contents are lost except for registers in the Backup

domain and Standby circuitry.

The device exits Standby mode when an external reset (NRST pin), an IWDG reset, a

rising edge on the WKUP pin, or an RTC alarm occurs.

Note: The RTC, the IWDG, and the corresponding clock sources are not stopped by entering Stop

or Standby mode.

2.3.16 DMA

The flexible 12-channel general-purpose DMAs (7 channels for DMA1 and 5 channels for

DMA2) are able to manage memory-to-memory, peripheral-to-memory and memory-toperipheral transfers. The two DMA controllers support circular buffer management,

removing the need for user code intervention when the controller reaches the end of the

buffer.

18/120 Doc ID 16554 Rev 3

Each channel is connected to dedicated hardware DMA requests, with support for software

trigger on each channel. Configuration is made by software and transfer sizes between

source and destination are independent.

STM32F103xF, STM32F103xG Description

The DMA can be used with the main peripherals: SPI, I2C, USART, general-purpose, basic

and advanced-control timers TIMx, DAC, I

2

S, SDIO and ADC.

2.3.17 RTC (real-time clock) and backup registers

The RTC and the backup registers are supplied through a switch that takes power either on

V

supply when present or through the V

DD

pin. The backup registers are forty-two 16-bit

BAT

registers used to store 84 bytes of user application data when V

They are not reset by a system or power reset, and they are not reset when the device

wakes up from the Standby mode.

The real-time clock provides a set of continuously running counters which can be used with

suitable software to provide a clock calendar function, and provides an alarm interrupt and a

periodic interrupt. It is clocked by a 32.768 kHz external crystal, resonator or oscillator, the

internal low power RC oscillator or the high-speed external clock divided by 128. The

internal low-speed RC has a typical frequency of 40 kHz. The RTC can be calibrated using

an external 512 Hz output to compensate for any natural quartz deviation. The RTC features

a 32-bit programmable counter for long term measurement using the Compare register to

generate an alarm. A 20-bit prescaler is used for the time base clock and is by default

configured to generate a time base of 1 second from a clock at 32.768 kHz.

2.3.18 Timers and watchdogs

The XL-density STM32F103xx performance line devices include up to two advanced-control

timers, up to ten general-purpose timers, two basic timers, two watchdog timers and a

SysTick timer.

power is not present.

DD

Ta bl e 4 compares the features of the advanced-control, general-purpose and basic timers.

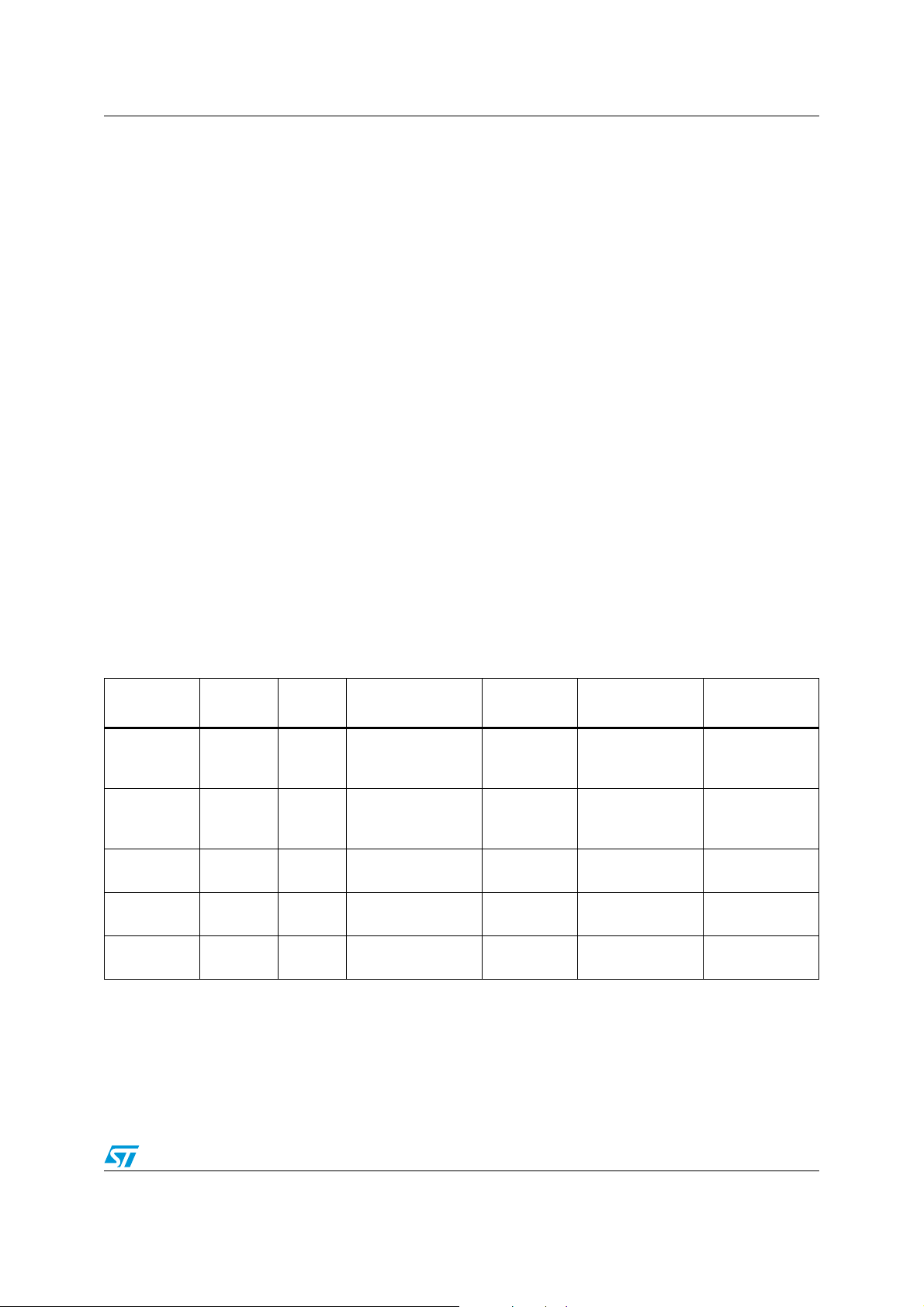

Table 4. STM32F103xF and STM32F103xG timer feature comparison

Timer

TIM1, TIM8 16-bit

TIM2, TIM3,

TIM4, TIM5

TIM9, TIM12 16-bit Up

TIM10, TIM11

TIM13, TIM14

TIM6, TIM7 16-bit Up

Counter

resolution

16-bit

16-bit Up

Counter

type

Up,

down,

up/down

Up,

down,

up/down

Prescaler factor

Any integer between

1 and 65536

Any integer between

1 and 65536

Any integer between

1 and 65536

Any integer between

1 and 65536

Any integer between

1 and 65536

DMA request

generation

Ye s 4 Ye s

Ye s 4 N o

No 2 No

No 1 No

Ye s 0 N o

Capture/compare

channels

Complementary

outputs

Doc ID 16554 Rev 3 19/120

Description STM32F103xF, STM32F103xG

Advanced-control timers (TIM1 and TIM8)

The two advanced-control timers (TIM1 and TIM8) can each be seen as a three-phase

PWM multiplexed on 6 channels. They have complementary PWM outputs with

programmable inserted dead-times. They can also be seen as a complete general-purpose

timer. The 4 independent channels can be used for:

● Input capture

● Output compare

● PWM generation (edge or center-aligned modes)

● One-pulse mode output

If configured as a standard 16-bit timer, it has the same features as the TIMx timer. If

configured as the 16-bit PWM generator, it has full modulation capability (0-100%).

In debug mode, the advanced-control timer counter can be frozen and the PWM outputs

disabled to turn off any power switch driven by these outputs.

Many features are shared with those of the general-purpose TIM timers which have the

same architecture. The advanced-control timer can therefore work together with the TIM

timers via the Timer Link feature for synchronization or event chaining.

General-purpose timers (TIMx)

There are10 synchronizable general-purpose timers embedded in the STM32F103xF and

STM32F103xG performance line devices (see

● TIM2, TIM3, TIM4, TIM5

Ta bl e 4 for differences).

There are up to 4 synchronizable general-purpose timers (TIM2, TIM3, TIM4 and TIM5)

embedded in the STM32F103xF and STM32F103xG access line devices.

These timers are based on a 16-bit auto-reload up/down counter, a 16-bit prescaler

and feature 4 independent channels each for input capture/output compare, PWM or

one-pulse mode output. This gives up to 16 input captures / output compares / PWMs

on the largest packages.

Their counter can be frozen in debug mode. Any of the general-purpose timers can be

used to generate PWM outputs. They all have independent DMA request generation.

These timers are capable of handling quadrature (incremental) encoder signals and the

digital outputs from 1 to 3 hall-effect sensors.

● TIM10, TIM11 and TIM9

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler.

TIM10 and TIM11 feature one independent channel, whereas TIM9 has two

independent channels for input capture/output compare, PWM or one-pulse mode

output. They can be synchronized with the TIM2, TIM3, TIM4, TIM5 full-featured

general-purpose timers. They can also be used as simple time bases.

● TIM13, TIM14 and TIM12

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler.

TIM13 and TIM14 feature one independent channel, whereas TIM12 has two

independent channels for input capture/output compare, PWM or one-pulse mode

output. They can be synchronized with the TIM2, TIM3, TIM4, TIM5 full-featured

general-purpose timers. They can also be used as simple time bases.

20/120 Doc ID 16554 Rev 3

STM32F103xF, STM32F103xG Description

Basic timers TIM6 and TIM7

These timers are mainly used for DAC trigger generation. They can also be used as a

generic 16-bit time base.

Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is

clocked from an independent 40 kHz internal RC and as it operates independently from the

main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog

to reset the device when a problem occurs, or as a free running timer for application timeout

management. It is hardware or software configurable through the option bytes. The counter

can be frozen in debug mode.

Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free running. It

can be used as a watchdog to reset the device when a problem occurs. It is clocked from the

main clock. It has an early warning interrupt capability and the counter can be frozen in

debug mode.

SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard

down counter. It features:

● A 24-bit down counter

● Autoreload capability

● Maskable system interrupt generation when the counter reaches 0.

● Programmable clock source

2.3.19 I²C bus

Up to two I²C bus interfaces can operate in multimaster and slave modes. They can support

standard and fast modes.

They support 7/10-bit addressing mode and 7-bit dual addressing mode (as slave). A

hardware CRC generation/verification is embedded.

They can be served by DMA and they support SMBus 2.0/PMBus.

2.3.20 Universal synchronous/asynchronous receiver transmitters (USARTs)

The STM32F103xF and STM32F103xG performance line embeds three universal

synchronous/asynchronous receiver transmitters (USART1, USART2 and USART3) and

two universal asynchronous receiver transmitters (UART4 and UART5).

These five interfaces provide asynchronous communication, IrDA SIR ENDEC support,

multiprocessor communication mode, single-wire half-duplex communication mode and

have LIN Master/Slave capability.

The USART1 interface is able to communicate at speeds of up to 4.5 Mbit/s. The other

available interfaces communicate at up to 2.25 Mbit/s.

USART1, USART2 and USART3 also provide hardware management of the CTS and RTS

signals, Smart Card mode (ISO 7816 compliant) and SPI-like communication capability. All

interfaces can be served by the DMA controller except for UART5.

Doc ID 16554 Rev 3 21/120

Description STM32F103xF, STM32F103xG

2.3.21 Serial peripheral interface (SPI)

Up to three SPIs are able to communicate up to 18 Mbits/s in slave and master modes in

full-duplex and simplex communication modes. The 3-bit prescaler gives 8 master mode

frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC

generation/verification supports basic SD Card/MMC modes.

All SPIs can be served by the DMA controller.

2.3.22 Inter-integrated sound (I2S)

Two standard I2S interfaces (multiplexed with SPI2 and SPI3) are available, that can be

operated in master or slave mode. These interfaces can be configured to operate with 16/32

bit resolution, as input or output channels. Audio sampling frequencies from 8 kHz up to

48

kHz are supported. When either or both of the I2S interfaces is/are configured in master

mode, the master clock can be output to the external DAC/CODEC at 256 times the

sampling frequency.

2.3.23 SDIO

An SD/SDIO/MMC host interface is available, that supports MultiMediaCard System

Specification Version 4.2 in three different databus modes: 1-bit (default), 4-bit and 8-bit.

The interface allows data transfer at up to 48 MHz in 8-bit mode, and is compliant with SD

Memory Card Specifications Version 2.0.

The SDIO Card Specification Version 2.0 is also supported with two different databus

modes: 1-bit (default) and 4-bit.

The current version supports only one SD/SDIO/MMC4.2 card at any one time and a stack

of MMC4.1 or previous.

In addition to SD/SDIO/MMC, this interface is also fully compliant with the CE-ATA digital

protocol Rev1.1.

2.3.24 Controller area network (CAN)

The CAN is compliant with specifications 2.0A and B (active) with a bit rate up to 1 Mbit/s. It

can receive and transmit standard frames with 11-bit identifiers as well as extended frames

with 29-bit identifiers. It has three transmit mailboxes, two receive FIFOs with 3 stages and

14 scalable filter banks.

2.3.25 Universal serial bus (USB)

The STM32F103xF and STM32F103xG performance line embed a USB device peripheral

compatible with the USB full-speed 12 Mbs. The USB interface implements a full-speed (12

Mbit/s) function interface. It has software-configurable endpoint setting and suspend/resume

support. The dedicated 48 MHz clock is generated from the internal main PLL (the clock

source must use a HSE crystal oscillator).

2.3.26 GPIOs (general-purpose inputs/outputs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as

input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the

GPIO pins are shared with digital or analog alternate functions. All GPIOs are high currentcapable.

22/120 Doc ID 16554 Rev 3

STM32F103xF, STM32F103xG Description

The I/Os alternate function configuration can be locked if needed following a specific

sequence in order to avoid spurious writing to the I/Os registers.

2.3.27 ADC (analog to digital converter)

Three 12-bit analog-to-digital converters are embedded into STM32F103xF and

STM32F103xG performance line devices and each ADC shares up to 21 external channels,

performing conversions in single-shot or scan modes. In scan mode, automatic conversion

is performed on a selected group of analog inputs.

Additional logic functions embedded in the ADC interface allow:

● Simultaneous sample and hold

● Interleaved sample and hold

● Single shunt

The ADC can be served by the DMA controller.

An analog watchdog feature allows very precise monitoring of the converted voltage of one,

some or all selected channels. An interrupt is generated when the converted voltage is

outside the programmed thresholds.

The events generated by the general-purpose timers (TIMx) and the advanced-control

timers (TIM1 and TIM8) can be internally connected to the ADC start trigger and injection

trigger, respectively, to allow the application to synchronize A/D conversion and timers.

2.3.28 DAC (digital-to-analog converter)

The two 12-bit buffered DAC channels can be used to convert two digital signals into two

analog voltage signal outputs. The chosen design structure is composed of integrated

resistor strings and an amplifier in inverting configuration.

This dual digital Interface supports the following features:

● two DAC converters: one for each output channel

● 8-bit or 12-bit monotonic output

● left or right data alignment in 12-bit mode

● synchronized update capability

● noise-wave generation

● triangular-wave generation

● dual DAC channel independent or simultaneous conversions

● DMA capability for each channel

● external triggers for conversion

● input voltage reference V

Eight DAC trigger inputs are used in the STM32F103xF and STM32F103xG performance

line family. The DAC channels are triggered through the timer update outputs that are also

connected to different DMA channels.

REF+

Doc ID 16554 Rev 3 23/120

Description STM32F103xF, STM32F103xG

2.3.29 Temperature sensor

The temperature sensor has to generate a voltage that varies linearly with temperature. The

conversion range is between 2 V < V

< 3.6 V. The temperature sensor is internally

DDA

connected to the ADC1_IN16 input channel which is used to convert the sensor output

voltage into a digital value.

2.3.30 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP Interface is embedded, and is a combined JTAG and serial wire debug

port that enables either a serial wire debug or a JTAG probe to be connected to the target.

The JTAG TMS and TCK pins are shared respectively with SWDIO and SWCLK and a

specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

2.3.31 Embedded Trace Macrocell™

The ARM® Embedded Trace Macrocell provides a greater visibility of the instruction and

data flow inside the CPU core by streaming compressed data at a very high rate from the

STM32F10xxx through a small number of ETM pins to an external hardware trace port

analyzer (TPA) device. The TPA is connected to a host computer using USB, Ethernet, or

any other high-speed channel. Real-time instruction and data flow activity can be recorded

and then formatted for display on the host computer running debugger software. TPA

hardware is commercially available from common development tool vendors. It operates

with third party debugger software tools.

24/120 Doc ID 16554 Rev 3

STM32F103xF, STM32F103xG Pinouts and pin descriptions

AI14798b

V

DD_7

PC3PC2

PF6

V

DD_6

V

SS_4

PF8

H

V

DD_1

D PG13

PG14

PE6PE5

C

PG10

PG11

V

DD_5

PB8

NRST

B PG12PG15

PC15-

OSC32_OUT

PB9

A

87654321

V

BAT

OSC_IN

OSC_OUT

V

SS_5

G

F

E

PF7

PC0

PF0 PF1

PF2

V

SS_10

PG9PF4

PF3

V

SS_3

PF5

V

DD_8

V

DD_3

V

DD_4

V

SS_8

PE4

PB5

PB6

BOOT0 PB7

V

SS_11

PF10

PC1

V

DD_11VDD_10

PF9

109

K

J

V

SS_2

PD3

PD4

PD1

PC12

PC11

PD5

PD2 PD0

V

DD_9

V

SS_9

V

DD_2

PG1

PC5PA5 PE9

PB2/

BOOT1

PC4PA4

PE10

PG0PF13V

REF–

PE12V

SSA

PA1 PE13

PA0-WKUP

PD9

PD10

PG4

PD13

1211

PG8

PA10

NC

PA9

PA11

PA12

PC10

PC9 PA8

PC7

PC6

PC8

PD14

PG3

PG2

PD15

M

L

PF15

PB1PA7 PE7

PF12

PB0PA6

PE8

PF14PF11V

DDA

PE14V

REF+

PA3 PE15

PA2

PB10

PD8

PD12

PB11

PB12

PB14

PB15

PB13

PC13-

TAMPER-RTC

PE3 PE2 PE1 PE0

PB4

JTRST

PB3

JTDO

PD6 PD7

PA15

JTDI

PA14

JTCK

PA13

JTMS

PE11V

SS_6

V

SS_7VSS_1

PG7

PD11

PG5

PG6

PC14-

OSC32_IN

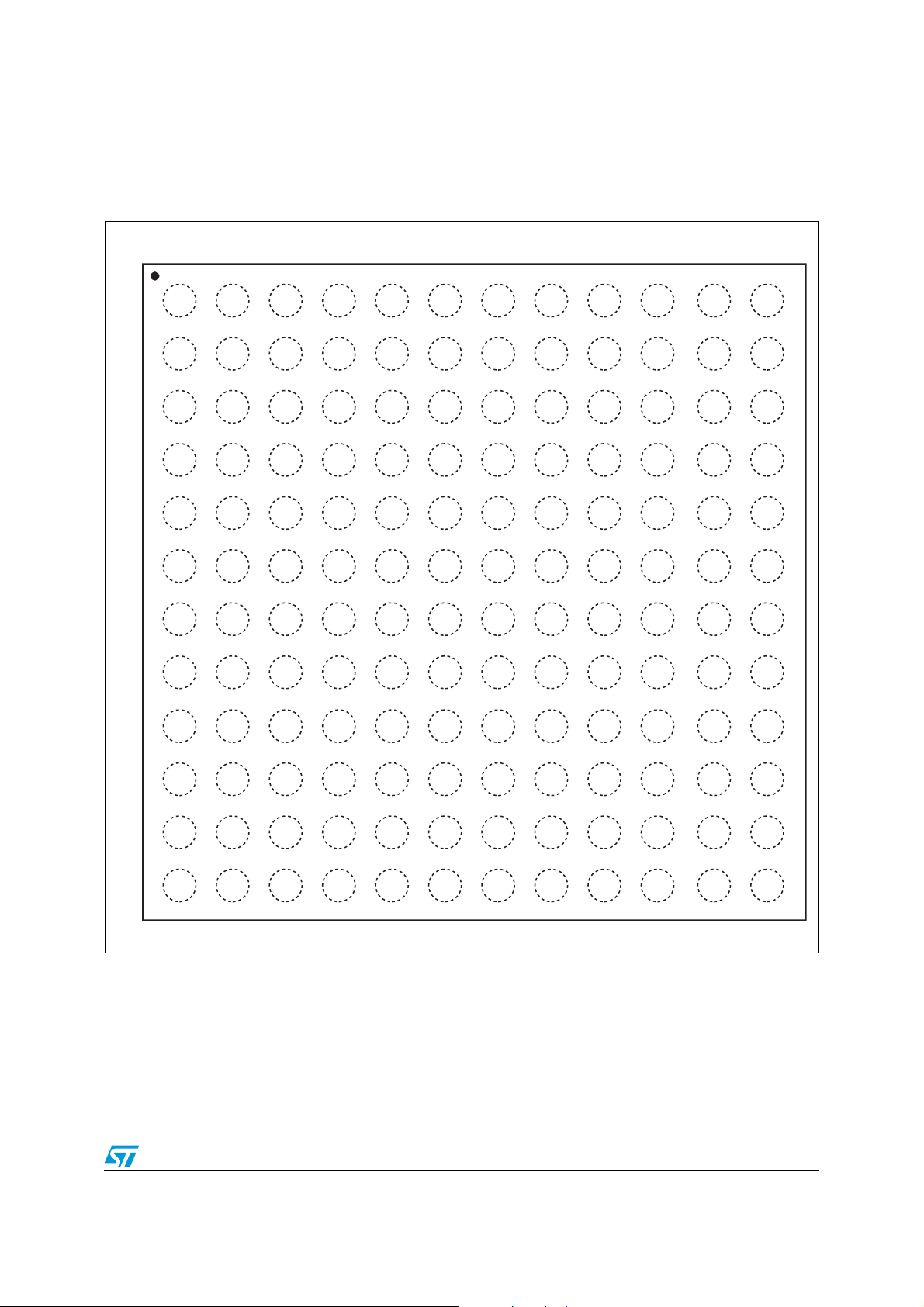

3 Pinouts and pin descriptions

Figure 3. STM32F103xF and STM32F103xG XL-density performance line BGA144 ballout

Doc ID 16554 Rev 3 25/120

Pinouts and pin descriptions STM32F103xF, STM32F103xG

V

DD_3VSS_3

PE1

PE0

PB9

PB8

BOOT0

PB7

PB6

PB5

PB4

PB3

PG15

V

DD_11VSS_11

PG14

PG13

PG12

PG11

PG10

PG9

PD7

PD6

V

DD_10VSS_10

PD5

PD4

PD3

PD2

PD1

PD0

PC12

PC11

PC10

PA15

PA14

PE2

V

DD_2

PE3

V

SS_2

PE4

NC

PE5

PA13

PE6

PA12

VBAT

PA11

PC13-TAMPER-RTC

PA10

PC14-OSC32_IN

PA9

PC15-OSC32_OUT

PA8

PF0

PC9

PF1

PC8

PF2

PC7

PF3

PC6

PF4

V

DD_9

PF5

V

SS_9

V

SS_5

PG8

V

DD_5

PG7

PF6

PG6

PF7

PG5

PF8

PG4

PF9

PG3

PF10

PG2

OSC_IN

PD15

OSC_OUT

PD14

NRST

V

DD_8

PC0

V

SS_8

PC1

PD13

PC2

PD12

PC3

PD11

V

SSA

PD10

V

REF-

PD9

V

REF+

PD8

V

DDA

PB15

PA0-WKUP

PB14

PA1

PB13

PA2

PB12

PA3

V

SS_4

V

DD_4

PA4

PA5

PA6

PA7

PC4

PC5

PB0

PB1

PB2

PF11

PF12

VSS_6

V

DD_6

PF13

PF14

PF15

PG0

PG1

PE7

PE8

PE9

V

SS_7

V

DD_7

PE10

PE11

PE12

PE13

PE14

PE15

PB10

PB11

V

SS_1

V

DD_1

144

143

142

141

140

139

138

137

136

135

134

133

132

131

130

129

128

127

126

125

124

123

122

121

109

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

3738394041424344454647484950515253545556575859

60

72

LQFP144

120

119

118

117

116

115

114

113

112