增强型,32位基于ARM核心的带闪存、USB、CAN的微控制器

功能

■ 内核:ARM 32位的Cortex™-M3 CPU

− 72MHz,1.25DMips/MHz

(Dhrystone2.1),0等待周期的存储器

− 单周期乘法和硬件除法

■ 存储器

− 从32K字节至128K字节的闪存程序存储器

− 从6K字节至20K字节的SRAM

■ 时钟、复位和电源管理

− 2.0至3.6伏供电和I/O管脚

− 上电/断电复位(POR/PDR)、可编程电压监

测器(PVD)

− 内嵌4至16MHz高速晶体振荡器

− 内嵌经出厂调校的8MHz的RC振荡器

− 内嵌40kHz的RC振荡器

− PLL供应CPU时钟

− 带校准功能的32kHz RTC振荡器

■ 低功耗

− 睡眠、停机和待机模式

BAT为RTC和后备寄存器供电

− V

■ 2个12位模数转换器,1us转换时间(16通道)

− 转换范围:0至3.6V

− 双采样和保持功能

− 温度传感器

■ DMA

− 7通道DMA控制器

− 支持的外设:定时器、ADC、SPI、I2C和

USART

■ 多达80个快速I/O口

− 26/37/51/80个多功能双向5V兼容的I/O口

− 所有I/O口可以映像到16个外部中断

数据手册

STM32F103x6

STM32F103x8 STM32F103xB

7个16位定时器、2个ADC 、9个通信接口

■ 调试模式

− 串行线调试(SWD)和JTAG接口

■ 多达7个定时器

− 多达3个16位定时器,每个定时器有多达4

个用于输入捕获/输出比较/PWM或脉冲计数

的通道

− 16位6通道高级控制定时器

− 多达 6 路 PWM输出

− 死区控制、边缘/中间对齐波形和紧急制动

− 2个看门狗定时器(独立的和窗口型的)

− 系统时间定时器:24位自减型

■ 多达9个通信接口

− 多达2个I2C接口(SMBus/PMBus)

− 多达3个USART接口,支持ISO7816,

LIN,IrDA接口和调制解调控制

− 多达2个SPI同步串行接口(18兆位/秒)

− CAN 接口(2.0B 主动)

− USB 2.0 全速接口

■ ECOPACK

表一 器件列表

参 考 基本型号

STM32F103x6 STM32F103C6, STM32F103R6,

STM32F103x8

STM32F103xB

®封装(兼容RoHS)

STM32F103T6

STM32F103C8, STM32F103R8,

STM32F103V8, STM32F103T8

STM32F103RB, STM32F103VB,

STM32F103C8

参照2007年11月 STM32F103数据手册 英文第四版 http://www.st.com/stonline/products/literature/ds/13587.pdf 1/22

数据手册

1 介绍 .....................................................................................................................................................3

2 规格说明 .............................................................................................................................................3

2.1 器件一览 ................................................................................................................................4

2.2 概述 ........................................................................................................................................5

3 管脚定义 ...........................................................................................................................................11

4 存储器映像 .......................................................................................................................................19

5 电气特性 ...........................................................................................................................................20

6 封装参数 ...........................................................................................................................................20

7 订货代码 ...........................................................................................................................................20

7.1 后续的产品系列 ..................................................................................................................21

8 版本历史 ...........................................................................................................................................21

附录A 重要提示.....................................................................................................................................22

A.1 PD0和PD1在输出模式下 .......................................................................................................22

A.2 ADC自动注入通道 .................................................................................................................22

A.3 ADC的混合同步注入+交替模式...........................................................................................22

A.4 ADC通道0 ...............................................................................................................................22

参照2007年11月 STM32F103数据手册 英文第四版 http://www.st.com/stonline/products/literature/ds/13587.pdf 2/22

STM32F103 增强型

1 介绍

本文给出了STM32F103xx增强型的订购信息和器件的机械特性。

有关闪存存储器的编程、擦除和保护等信息,请参考《STM32F10x闪存编程参考手册》。

有关Cortex-M3的信息,请参考《Cortex-M3技术参考手册》

2 规格说明

STM32F103xx增强型系列使用高性能的ARM Cortex-M3 32位的RISC内核,工作频率为72MHz,内

置高速存储器(高达128K字节的闪存和20K字节的SRAM),丰富的增强I/O端口和联接到两条APB总

线的外设。所有型号的器件都包含2个12位的ADC、3个通用16位定时器和一个PWM定时器,还包

含标准和先进的通信接口:多达2个I2C和SPI、3个USART、一个USB和一个CAN。

STM32F103xx增强型系列工作于-40°C至+105°C的温度范围,供电电压2.0V至3.6V,一系列的省电

模式保证低功耗应用的要求。

完整的STM32F103xx增强型系列产品包括从36脚至100脚的五种不同封装形式;根据不同的封装形

式,器件中的外设配置不尽相同。下面给出了该系列产品中所有外设的基本介绍。

这些丰富的外设配置,使得STM32F103xx增强型微控制器适合于多种应用场合:

● 电机驱动和应用控制

● 医疗和手持设备

● PC外设和GPS平台

● 工业应用:可编程控制器、变频器、打印机和扫描仪

● 警报系统,视频对讲,和暖气通风空调系统

图一给出了该产品系列的框图。

2007年11月 第四版 第3页

2.1 器件一览

表二 器件功能和配置(STM32F103xx增强型)

STM32F103 增强型

外设

闪存(K字节)

RAM(K字节)

通用 2 3 2 3 3 2

定时器

高级

SPI 1 1 1 2 2 1

I

通信

通用I/O端口 37 51 8026

12位同步ADC

USART 2 2 2 3 3 2

USB 1 1 1 1 1 1

CAN 1 1 1 1 1 1

2

C

STM32F103Tx

32 64 32 64 128 32 64 128 64 128

10 20 10 20 20 10

1112 2 1

1

2

10通道

STM32F103Cx

111

2

10通道

STM32F103Rx STM32F103Vx

20 20

33

2

3

1

1

2

16通道

2

22

3

1

1

CPU频率

工作电压

工作温度

封装

VFQFPN36

72MHz

2.0至3.6V

-40至+85°C / -40至+105°C

LQFP48 LQFP64

LQFP100,

BGA100

2007年11月 第四版 第4页

2.2 概述

ARM®的Cortex™-M3核心并内嵌闪存和SRAM

ARM的Cortex-M3处理器是最新一代的嵌入式ARM处理器,它为实现MCU的需要提供了低成本的平

台、缩减的管脚数目、降低的系统功耗,同时提供卓越的计算性能和先进的中断系统响应。

ARM的Cortex-M3是32位的RISC处理器,提供额外的代码效率,在通常8和16位系统的存储空间上得

到了ARM核心的高性能。

STM32F103xx增强型系列拥有内置的ARM核心,因此它与所有的ARM工具和软件兼容。

图一是该系列产品的功能框图。

内置闪存存储器

● 高达128K字节的内置闪存存储器,用于存放程序和数据。

内置SRAM

多达20K字节的内置SRAM,CPU能以0等待周期访问(读/写)。

嵌套的向量式中断控制器(NVIC)

STM32F103 增强型

STM32F103xx增强型内置嵌套的向量式中断控制器,能够处理多达43个可屏蔽中断通道(不包括16个

Cortex-M3的中断线)和16个优先级。

● 紧耦合的NVIC能够达到低延迟的中断响应处理

● 中断向量入口地址直接进入核心

● 紧耦合的NVIC接口

● 允许中断的早期处理

● 处理

● 支持中断尾部链接功能

● 自动保存处理器状态

● 中断返回时自动恢复,无需额外指令开销

该模块以最小的中断延迟提供灵活的中断管理功能。

晚到的

较高优先级中断

外部中断/事件控制器(EXTI)

外部中断/事件控制器包含19个边沿检测器,用于产生中断/事件请求。

每个中断线都可以独立地配置它的触发事件(上升沿或下降沿或双边沿),能够单独地被屏蔽;有一

个挂起寄存器维持所有中断请求的状态。EXTI可以检测到脉冲宽度小于内部APB2的时钟周期。多

达80个通用I/O口连接到16个外部中断线。

时钟和启动

系统时钟的选择是在启动时进行,复位时内部8MHz的RC振荡器被选为默认的CPU时钟,随后可以

选择外部的、具失效监控的4~16MHz时钟;当外部时钟失效时,它将被隔离,同时会产生相应的中

断。同样,在需要时可以采取对PLL时钟完全的中断管理(如当一个外接的振荡器失效时)。

具有多个预分频器用于配置AHB的频率、高速APB(APB2)和低速APB(APB1)区域。AHB和高速APB

的最高频率是72MHz,低速APB的最高频率为36MHz。

自举模式

在启动时,自举管脚被用于选择三种自举模式中的一种:

2007年11月 第四版 第5页

● 从用户闪存自举

● 从系统存储器自举

● 从SRAM自举

自举加载器存放于系统存储器中,可以通过USART1对闪存重新编程。详细信息请参考AN2606。

供电方案

● VDD = 2.0至3.6V:VDD管脚提供I/O管脚和内部调压器的供电。

● V

SSA,VDDA

ADC时,V

● V

= 1.8至3.6V:当(通过电源开关)关闭VDD时,为RTC、外部32kHz振荡器和后备寄存器供

BAT

电。

供电监控器

本产品内部集成了上电复位(POR)/掉电复位(PDR)电路,该电路始终处于工作状态,保证系统在供

电超过2V时工作;当V

路。

STM32F103 增强型

= 2.0至3.6V:为ADC、复位模块、RC振荡器和PLL的模拟部分提供供电。使用

不得小于2.4V。

DD

低于设定的阀值(V

DD

)时,置器件于复位状态,而不必使用外部复位电

POR/PDR

器件中还有一个可编程电压监测器(PVD),它监视V

值V

时将产生中断,中断处理程序可以发出警告信息或将微控制器转入安全模式。需要通过程序

PVD

开启PVD。

有关V

POR/PDR和VPVD

电压调压器

调压器有三个操作模式:主模式(MR)、低功耗模式(LPR)和关断模式

● 主模式(MR)用于正常的运行操作

● 低功耗模式(LPR)用于CPU的停机模式

● 关断模式用于CPU的待机模式:调压器的输出为高阻状态,内核电路的供电切断,调压器处于

零消耗状态(但寄存器和SRAM的内容将丢失)

该调压器在复位后始终处于工作状态,在待机模式下关闭处于高阻输出。

低功耗模式

STM32F103xx增强型支持三种低功耗模式,可以在要求低功耗、短启动时间和多种唤醒事件之间达

到最佳的平衡。

● 睡眠模式

在睡眠模式,只有CPU停止,所有外设处于工作状态并可在发生中断/事件时唤醒CPU。

● 停机模式

在保持SRAM和寄存器内容不丢失的情况下,停机模式可以达到最低的电能消耗。在停机模式

下,停止所有内部1.8V部分的供电,PLL、HSI和HSE的RC振荡器被关闭,调压器可以被置于

普通模式或低功耗模式。

可以通过任一配置成EXTI的信号把微控制器从停机模式中唤醒,EXTI信号可以是16个外部I/O

口之一、PVD的输出、RTC闹钟或USB的唤醒信号。

供电并与阀值V

DD

比较,当VDD低于或高于阀

PVD

数值,请参考表九“内置复位和电源控制模块特性”。

● 待机模式

在待机模式下可以达到最低的电能消耗。内部的电压调压器被关闭,因此所有内部1.8V部分的

供电被切断;PLL、HSI和HSE的RC振荡器也被关闭;进入待机模式

内容将消失,但后备寄存器的内容仍然保留,待机电路仍工作。

从待机模式退出的条件是:NRST上的外部复位信号、IWDG复位、WKUP管脚上的一个上升

边沿或RTC的闹钟到时。

2007年11月 第四版 第6页

后,SRAM和寄存器的

STM32F103 增强型

注:在进入停机或待机模式时,

RTC、IWDG

DMA

灵活的7路通用DMA可以管理存储器到存储器、设备到存储器和存储器到设备的数据传输;DMA控

制器支持环形缓冲区的管理,避免了控制器传输到达缓冲区结尾时所产生的中断。

每个通道都有专门的硬件DMA请求逻辑,同时可以由软件触发每个通道;传输的长度、传输的源地

址和目标地址都可以通过软件单独设置。

DMA可以用于主要的外设:SPI、I2C、USART、通用和高级定时器TIMx和ADC。

RTC(实时时钟)和后备寄存器

RTC和后备寄存器通过一个开关供电,在VDD有效时该开关选择VDD供电,否则由V

后备寄存器(10个16位的寄存器)可以用于在V

实时时钟具有一组连续运行的计数器,可以通过适当的软件提供日历时钟功能,还具有闹钟中断和

阶段性中断功能。RTC的驱动时钟可以是一个使用外部晶体的32.768kHz的振荡器、内部低功耗RC

振荡器或高速的外部时钟经128分频。内部低功耗RC振荡器的典型频率为32kHz。为补偿天然晶体

的偏差,RTC的校准是通过输出一个512Hz的信号进行。RTC具有一个32位的可编程计数器,使用

比较寄存器可以产生闹钟信号。有一个20位的预分频器用于时基时钟,默认情况下时钟为32.768kHz

时它将产生一个1秒长的时间基准。

独立的看门狗

和对应的时钟不会被停止。

消失时保存数据。

DD

管脚供电。

BAT

独立的看门狗是基于一个12位的递减计数器和一个8位的预分频器,它由一个独立的32kHz的内部

RC振荡器提供时钟,因为这个RC振荡器独立于主时钟,所以它可运行于停机和待机模式。它可以

被当成看门狗用于在发生问题时复位整个系统,或作为一个自由定时器为应用程序提供超时管理。

通过选择字节可以配置成是软件看门狗或硬件看门狗。在调试模式,计数器可以被冻结。

窗口看门狗

窗口看门狗内有一个7位的递减计数器,并可以设置成自由运行。它可以被当成看门狗用于在发生

问题时复位整个系统。它由主时钟驱动,具有早期预警中断功能;在调试模式,计数器可以被冻

结。

系统时基定时器

这个定时器是专用于操作系统,也可当成一个标准的递减计数器。它具有下述特性:

● 24位的递减计数器

● 重加载功能

● 当计数器为0时能产生一个可屏蔽中断

● 可编程时钟源

通用定时器(TIMx)

STM32F103xx增强型系列产品中内置了多达3个同步的标准定时器。每个定时器都有一个16位的自

动加载递加/递减计数器、一个16位的预分频器和4个独立的通道,每个通道都可用于输入捕获、输

出比较、PWM和单脉冲模式输出,在最大的封装配置中可提供最多12个输入捕获、输出比较或

PWM通道。它们还能通过定时器链接功能与高级控制定时器共同工作,提供同步或事件链接功能。

在调试模式下,计数器可以被冻结。

任一标准定时器都能用于产生PWM输出。每个定时器都有独立的DMA请求机制。

2007年11月 第四版 第7页

高级控制定时器(TIM1)

高级控制定时器(TIM1)可以被看成是一个分配到6个通道的三相PWM发生器,它还可以被当成一个

完整的通用定时器。四个独立的通道可以用于:

● 输入捕获

● 输出比较

● 产生PWM(边缘或中心对齐模式)

● 单脉冲输出

● 反相PWM输出,具程序可控的死区插入功能

配置为16位标准定时器时,它与TIMx定时器具有相同的功能。配置为16位PWM发生器时,它具有

全调制能力(0~100%)。

在调试模式下,计数器可以被冻结。

很多功能都与标准的TIM定时器相同,内部结构也相同,因此高级控制定时器可以通过定时器链接

功能与TIM定时器协同操作,提供同步或事件链接功能。

I2C总线

多达2个I2C总线接口,能够工作于多主和从模式,支持标准和快速模式。

STM32F103 增强型

它们支持双从地址寻址(只有7位)和主模式下的7/10位寻址。内置了硬件CRC发生器/校验器。

它们可以使用DMA操作并支持SM总线2.0版/PM总线

通用同步/异步接受发送器(USART)

其中一个USART接口通信速率可达4.5兆位/秒,其他USART接口通信速率可达2.25兆位/秒。接口具

有硬件的CTS和RTS信号管理、支持IrDA的 SIR ENDEC、与ISO7816兼容并具有LIN主/从功能。

USART接口可以使用DMA操作。

串行外设接口(SPI)

多达2个SPI接口,在从或主模式下,全双工和半双工的通信速率可达18兆位/秒。3位的预分频器可

产生8种主模式频率,可配置成每帧8位或16位。硬件的CRC产生/校验支持基本的SD卡和MMC模

式。

2个SPI接口都可以使用DMA操作。

控制器区域网络(CAN)

CAN接口兼容规范2.0A和2.0B (主动),位速率达1兆位/秒。它可以接收和发送11位标识符的标准

帧,也接收和发送29位标识符的扩展帧。具有2个接收FIFOs,3级14个可调节的滤波器。

通用串行总线(USB)

STM32F103xx增强型系列产品内嵌USB设备控制器,遵循全速USB设备(12兆位/秒)标准,端点可由

软件配置,具有待机/恢复功能。USB专用的48MHz时钟由内部主PLL直接产生。

通用输入输出接口(GPIO)

每个GPIO管脚都可以由软件配置成输出(推拉或开路)、输入(带或不带上拉或下拉)或其它的外设功

能口。多数GPIO管脚都与数字或模拟的外设共用。所有的GPIO管脚都有大电流通过能力。

在需要的情况下,I/O管脚的外设功能可以通过一个特定的操作锁定,以避免意外的写入I/O寄存

器。

在APB2上的I/O脚可达18MHz的翻转速度。

2007年11月 第四版 第8页

ADC(模拟/数字转换器)

STM32F103xx增强型产品内嵌2个12位的模拟/数字转换器(ADC),每个ADC有多达16个外部通道,

可以实现单次或扫描转换。在扫描模式下,转换在选定的一组模拟输入上自动进行。

ADC接口上额外的逻辑功能允许:

● 同时采样和保持

● 交叉采样和保持

● 单次采样

ADC可以使用DMA操作。

模拟看门狗功能允许非常精准地监视一路、多路或所有选中的通道,当被监视的信号超出预置的阀

值时,将产生中断。

由标准定时器(TIMx)和高级控制定时器(TIM1)产生的事件,可以分别内部级联到ADC的开始触发、

外部触发和DMA触发,以使应用程序能同步AD转换和时钟。

温度传感器

温度传感器产生一个随温度线性变化的电压,转换范围在2V < VDDA < 3.6V之间。温度传感器在内

部被连接到ADC12_IN16的输入通道上,用于将传感器的输出转换到数字数值。

STM32F103 增强型

串行线JTAG调试口(SWJ-DP)

内嵌ARM的SWJ-DP接口和JTAG接口,JTAG的TMS和TCK信号分别与SWDIO和 SWCLK共用管

脚,TMS脚上的一个特殊的信号序列用于在JTAG-DP和SWJ-DP间切换。

2007年11月 第四版 第9页

图一 STM32F103xx增强型模块框图

STM32F103 增强型

1. AF:可作为外设功能脚的I/O口

2. 工作温度:-40°C至105°C (结温达125°C)

2007年11月 第四版 第10页

3 管脚定义

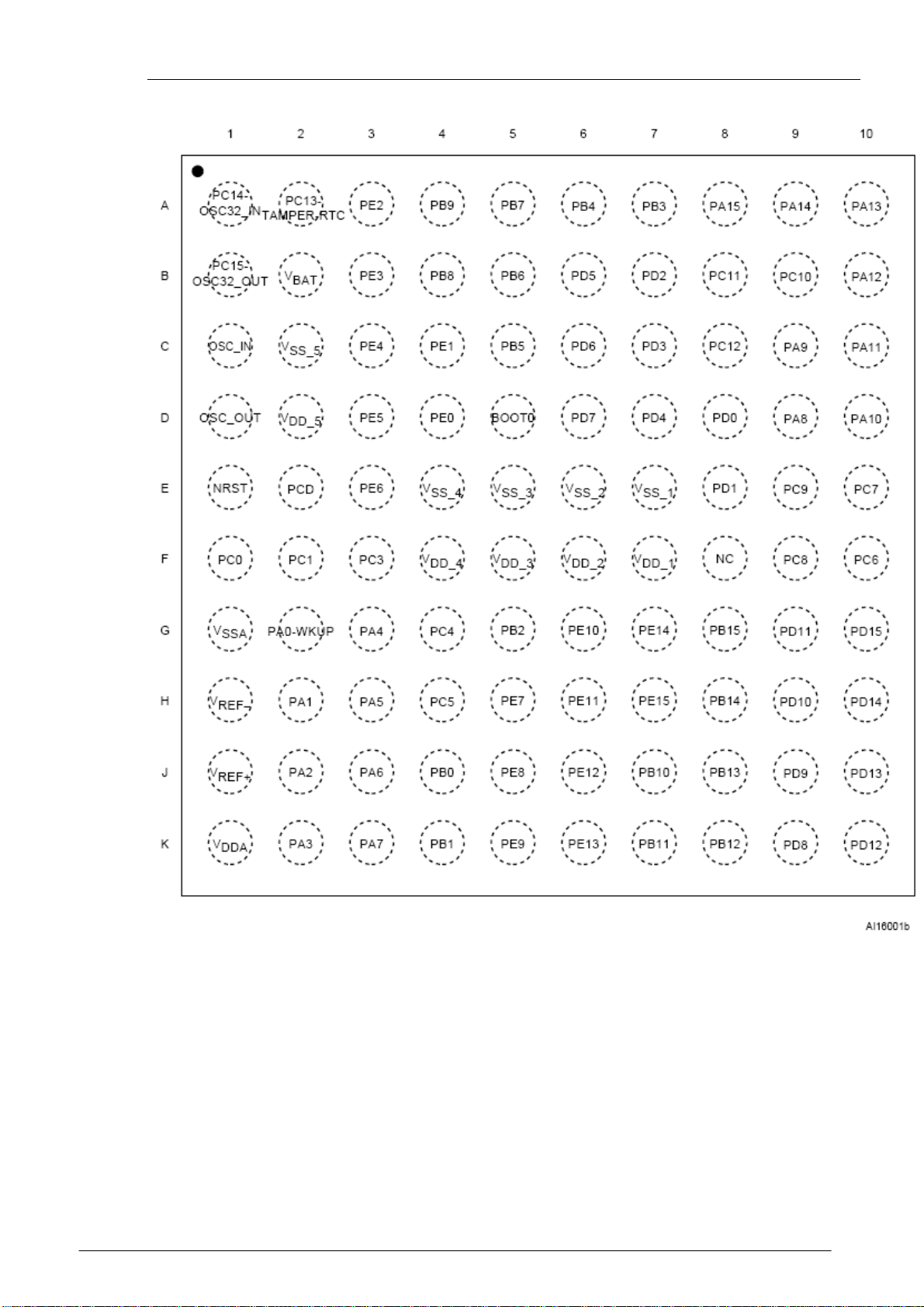

图二 STM32F103xx增强型VFQFPN36管脚

STM32F103 增强型

2007年11月 第四版 第11页

图三 STM32F103xx增强型LQFP100管脚

STM32F103 增强型

2007年11月 第四版 第12页

图四 STM32F103xx增强型LQFP64管脚

STM32F103 增强型

图五 STM32F103xx增强型LQFP48管脚

2007年11月 第四版 第13页

图六 STM32F103xx增强型BGA100管脚

STM32F103 增强型

2007年11月 第四版 第14页

表三 管脚定义

_

_

_

_

_

_

类

管脚名称

型

(1)

BGA100

LQFP48

LQFP64

LQFP100

VFQFPN36

A3 - - 1 - PE2 I/O FT PE2 TRACECK

B3 - - 2 - PE3 I/O FT PE3 TRACED0

C3 - - 3 - PE4 I/O FT PE4 TRACED1

D3 - - 4 - PE5 I/O FT PE5 TRACED2

E3 - - 5 - PE6 I/O FT PE6 TRACED3

B2 1 1 6 - V

A2 2 2 7 -

A1 3 3 8 -

B1 4 4 9 -

C2 - - 10 - V

D2 - - 11 - V

BAT

PC13-TAMPER-

RTC(4)

PC14-

OSC32

IN(4)

PC15-

OSC32

OUT(4)

SS_5

DD_5

S VBAT

I/O PC13(5) TAMPER-RTC

I/O PC14(5) OSC32_IN

I/O PC15(5) OSC32_OUT

SV

SV

C1 5 5 12 2 OSC_IN I OSC_IN

D1 6 6 13 3 OSC_OUT O OSC_OUT

E1 7 7 14 4 NRST I/O NRST

F1 - 8 15 - PC0 I/O PC0 ADC12_IN10

F2 - 9 16 - PC1 I/O PC1 ADC12_IN11

E2 - 10 17 - PC2 I/O PC2 ADC12_IN12

F3 - 11 18 - PC3 I/O PC3 ADC12_IN13

G1 8 12 19 5 V

H1 - - 20 - V

J1 - - 21 - V

K1 9 13 22 6 V

SSA

REF-

REF+

DDA

SV

SV

SV

SV

G2 10 14 23 7 PA0-WKUP I/O PA0

H2 11 15 24 8 PA1 I/O PA1

J2 12 16 25 9 PA2 I/O PA2

K2 13 17 26 10 PA3 I/O PA3

E4 - 18 27 - V

F4 - 19 28 - V

SS_4

DD_4

SV

SV

主功能

(复位后)

(3)

I/O电平(2)

SS_5

DD_5

SSA

REF-

REF+

DDA

SS_4

DD_4

默认功能 重定义功能

WKUP/USART2_C

TS(7)

ADC12_IN0/TIM

2

CH1_ETR(7)

USART2_RTS(7)

/ADC12_IN1/TI

M2

CH2(7)

USART2_TX(7)/

ADC12_IN2/TIM

2

CH3(7)

USART2_RX(7)/

ADC12_IN3/TIM

2

CH4(7)

STM32F103 增强型

可选功能脚位

2007年11月 第四版 第15页

STM32F103 增强型

_

_

_

_

_

_

表三 管脚定义 (续)

可选功能脚位

主功能

(复位后)

(3)

I/O电平(2)

默认功能 重定义功能

BGA100

LQFP48

LQFP64

LQFP100

管脚名称

VFQFPN36

类

型

(1)

SPI1_NSS(7)/US

G3 14 20 29 11 PA4 I/O PA4

H3 15 21 30 12 PA5 I/O PA5

ART2_CK(7)/ADC

12

IN4

SPI1_SCK(7)/AD

C12

IN5

SPI1_MISO(7)/A

J3 16 22 31 13 PA6 I/O PA6

DC12_IN6/TIM3_

TIM1_BKIN

CH1(7)

SPI1_MOSI(7)/A

K3 17 23 32 14 PA7 I/O PA7

DC12_IN7/TIM3_

TIM1_CHIN

CH2(7)

G4 - 24 33 - PC4 I/O PC4 ADC12_IN14

H4 - 25 34 - PC5 I/O PC5 ADC12_IN15

J4 18 26 35 15 PB0 I/O PB0

K4 19 27 36 16 PB1 I/O PB1

ADC12_IN8/TIM3

CH3(7)

ADC12_IN9/TIM3

CH4(7)

TIM1_CH2N

TIM1_CH3N

G5 20 28 37 17 PB2/BOOT1 I/O FT PB2/BOOT1

H5 - - 38 - PE7 I/O FT PE7 TIM1_ETR

J5 - - 39 - PE8 I/O FT PE8 TIM1_CH1N

K5 - - 40 - PE9 I/O FT PE9 TIM1_CH1

G6 - - 41 - PE10 I/O FT PE10 TIM1_CH2N

H6 - - 42 - PE11 I/O FT PE11 TIM1_CH2

J6 - - 43 - PE12 I/O FT PE12 TIM1_CH3N

K6 - - 44 - PE13 I/O FT PE13 TIM1_CH3

G7 - - 45 - PE14 I/O FT PE14 TIM1_CH4

H7 - - 46 - PE15 I/O FT PE15 TIM1_BKIN

J7 21 29 47 - PB10 I/O FT PB10

K7 22 30 48 - PB11 S FT PB11

E7 23 31 49 18 V

F7 24 32 50 19 V

SS_1

DD_1

SV

SV

SS_1

DD_1

I2C2_SCL/USART

3

TX(6)(7)

I2C2_SDA/USART

3

RX(6)(7)

TIM2_CH3

TIM2_CH4

SPI2_NSS(6)/I2

K8 25 33 51 - PB12 I/O FT PB12

C2_SMBAI(6)/US

ART3_CK(6)(7)/

TIM1_BKIN(7)

SPI2_SCK(6)/US

J8 26 34 52 - PB13 I/O FT PB13

ART3_CTS(6)(7)

/TIM1_CH1N(7)

SPI2_MISO(6)/U

H8 27 35 53 - PB14 I/O FT PB14

SART3_RTS(6)(7

)/TIM1_CH2N(7)

2007年11月 第四版 第16页

表三 管脚定义 (续)

_

_

_

_

_

脚位

STM32F103 增强型

可选功能

管脚名称

BGA100

LQFP48

LQFP64

LQFP100

VFQFPN36

G8 28 36 54 - PB15 I/O FT PB15

K9 - - 55 - PD8 I/O FT PD8 USART3_TX

J9 - - 56 - PD9 I/O FT PD9 USART3_RX

H9 - - 57 - PD10 I/O FT PD10 USART3_CK

G9 - - 58 - PD11 I/O FT PD11 USART3_CTS

K10 - - 59 - PD12 I/O FT PD12

J10 - - 60 - PD13 I/O FT PD13 TIM4_CH2

H10 - - 61 - PD14 I/O PD14 TIM4_CH3

G10 - - 62 - PD15 I/O FT PD15 TIM4_CH4

F10 - 37 63 - PC6 I/O FT PC6 TIM3_CH1

E10 - 38 64 - PC7 I/O FT PC7 TIM3_CH2

F9 - 39 65 - PC8 I/O FT PC8 TIM3_CH3

E9 - 40 66 - PC9 I/O FT PC9 TIM3_CH4

D9 29 41 67 20 PA8 I/O FT PA8

C9 30 42 68 21 PA9 I/O FT PA9

D10 31 43 69 22 PA10 I/O FT PA10

C10 32 44 70 23 PA11 I/O FT PA11

B10 33 45 71 24 PA12 I/O FT PA12

A10 34 46 72 25 PA13/JTMS/SWDIO I/O FT JTMS/SWDIO PA13

F8 - - 73 E6 35 47 74 26 V

F6 36 48 75 27 V

A9 37 49 76 28 PA14/JTCK/SWCLK I/O FT JTCK/SWCLK PA14

A8 38 50 77 29 PA15/JTDI I/O FT JTDI PA15

B9 - 51 78 - PC10 I/O FT PC10 USART3_TX

B8 - 52 79 - PC11 I/O FT PC11 USART3_RX

C8 - 53 80 - PC12 I/O FT PC12 USART3_CK

D8 5 5 81 2 PD0 I/O FT OSC_IN(8) CANRX

E8 6 6 82 3 PD1 I/O FT OSC_OUT(8) CANTX

SS_2

DD_2

类

型

SV

SV

主功能

(复位后)

I/O电平

SS_2

DD_2

默认功能 重定义功能

SP12_MOSI(6)/

TIM1

USART1_CK/TIM1_

CH1(7)/MCO

USART1_TX(7)/TI

M1

USART1_RX(7)/TI

M1

USART1_CTS/CANR

X(7)/TIM1_CH4(7

)/USBDM

USART1_RTS/CANT

X(7)/TIM1_ETR(7

)/USBDP

未连接

CH3N(7)

CH2(7)

CH3(7)

TIM4_CH1/

USART3

TIM2_CH1_ETR/

SPI1

RTS

NSS

2007年11月 第四版 第17页

表三 管脚定义 (续)

_

_

_

_

_

STM32F103 增强型

可选功能脚位

BGA100

LQFP48

LQFP64

LQFP100

管脚名称

VFQFPN36

类

型

I/O电平

主功能

(复位后)

默认功能 重定义功能

B7 - 84 83 - PD2 I/O FT PD2 TIM3_ETR

C7 - - 84 - PD3 I/O FT PD3 USART2_CTS

D7 - - 85 - PD4 I/O FT PD4 USART2_RTS

B6 - - 86 - PD5 I/O FT PD5 USART2_TX

C6 - - 87 - PD6 I/O FT PD6 USART2_RX

D6 - - 88 - PD7 I/O FT PD7 USART2_CK

A7 39 55 89 30 PB3/JTDO I/O FT JTDO PB3/TRACESWO

A6 40 56 90 31 PB4/JNTRST I/O FT JNTRST PB4

C5 41 57 91 32 PB5 I/O PB5 I2C1_SMBAI

B5 42 58 92 33 PB6 I/O FT PB6

A5 43 59 93 34 PB7 I/O FT PB7

I2C1_SCL(7)/

CH1(6)(7)

TIM4

I2C1_SDA(7)/

CH2(6)(7)

TIM4

D5 44 60 94 35 BOOT0 I BOOT0

B4 45 61 95 - PB8 I/O FT PB8 TIM4_CH3(6)(7)

A4 46 61 96 - PB9 I/O FT PB9 TIM4_CHR(6)(7)

D4 - - 97 - PE0 I/O FT PE0 TIM4_ETR(6)

C4 - - 98 - PE1 I/O FT PE1

E5 47 63 99 36 V

F5 48 64 100 1 V

1. I : 输入, O:输出, S:电源, HiZ:高阻

SS_3

DD_3

SV

SV

SS_3

DD_3

TIM2_CH2/

SCK

SPI1

TIM3_CH1/

MISO

SPI1

TIM3_CH1/

MOSI

SPI1

USART1_TX

USART1_RX

I2C1_SCL/

CANRX

I2C1_SDA/

CANTX

2. FT:兼容5V

3. 有些功能仅在部分型号芯片中支持。外设的标号遵循由低到高的顺序,例如某个型号的芯片内嵌1个SPI和2个

USARTS功能,这些外设分别被称为SPI1, USART1和USART2。具体信息请参考表2。

4. PC13,PC14和PC15引脚通过电源开关进行供电,因此这三个引脚作为输出引脚时有以下限制:

作为输出脚时只能工作在2MHz模式下

最大驱动负载为30pF

同一时间,三个引脚中只有一个引脚能作为输出引脚。

5. 这些引脚在备份区域第一次上电时处于主功能状态下,之后即使复位,这些引脚的状态仍由备份区域寄存器控制(这

些寄存器不会被复位)。 关于如何控制这些IO口的具体信息,请参考STM32F10xxx参考手册的电池备份区域和BKP

寄存器的相关章节。

6. 仅在内嵌大等于64K Flash的型号中支持此类功能。

7. 此类复用功能能够由软件配置到其他引脚上,详细信息请参考STM32F10xxx参考手册的复用功能I/O章节和调试设置

章节。

8. VFQFPN36封装的2号,3号引脚和LQFP48,LQFP64封装的5号,6号引脚在芯片复位后默认配置为OSC_IN和

OSC_OUT功能脚。软件可以重新设置这两个引脚为PD0和PD1功能脚。但对于LQFP100封装,由于PD0和PD1为固

有的功能脚,因此没有必要再由软件进行设置。更多详细信息请参考STM32F10xxx参考手册的复用功能I/O章节和调

试设置章节。PD0和PD1作为输出引脚只能工作在50MHz模式下。

2007年11月 第四版 第18页

4 存储器映像

图七 存储器图

STM32F103 增强型

2007年11月 第四版 第19页

5 电气特性

请参考英文版数据手册

6 封装参数

请参考英文版数据手册

7 订货代码

订货代码信息图示

例如:

STM32 F 103 C 6 T 7 xxx

芯片系列

STM32代表ARM Cortex-M3内核的32位微控制器

产品类型

STM32F103 增强型

F代表通用系列

芯片子系列

103代表增强型系列

引脚数

T代表36脚

C代表48脚

R代表64脚

V代表100脚

内嵌Flash容量

6代表32K字节Flash

8代表64K字节Flash

B代表128K字节Flash

封装

H代表BGA封装

T代表LQFP封装

U代表VFQFPN封装

工作温度范围

6代表-40 — 85℃

7代表-40 —105℃

选项

xxx代表编程号

TR代表磁带式包装

关于更多的选项列表和其他相关信息,请与ST的销售处联络。

2007年11月 第四版 第20页

STM32F103 增强型

7.1 后续的产品系列

后续的STM32F103xx增强型系列产品将会有更广泛的型号选择,芯片将会有更大的封装尺寸并内嵌

多达512KB的Flash和64KB的SRAM。同时,后续产品会提供可变静态存储控制器(FSMC),SDIO,

I2S,DAC,更多的定时器和USARTS接口功能。

8 版本历史

请参考英文版数据手册

2007年11月 第四版 第21页

STM32F103 增强型

附录A 重要提示

附录所列的提示,仅对STM32F103xx增强型系列芯片的Z版本有效,关于芯片版本号的

具体信息,请参考STM32F10xxx参考手册的20.6.1章节。

A.1 PD0和PD1在输出模式下

由于PD0和PD1仅工作在50MHz模式下,因此这两个引脚在用作输出模式时是限制的。

A.2 ADC自动注入通道

当ADC时钟使用4或8的预分频时,从普通模式转到注入转换时会自动插入一个ADC时

钟的延迟, 当ADC使用2预分频的时钟时,插入的延迟为2个ADC时钟。

A.3 ADC的混合同步注入+交替模式

当ADC使用4预分频的时钟时,交替采样的时间间隔并不平均,也就是说采样的间隔并

不是标准的7个ADC时钟,而是8个ADC时钟和6个ADC时钟交替。

A.4 ADC通道0

当 ADC处于注入触发模式时,在某些特殊情况下,ADC 通道 0会产生一个低幅度的脉

冲尖峰信号。

此脉冲由内部耦合器产生,与正在使用哪个 ADC 注入通道无关,在普通模式和注入模

式切换时产生,并同步到注入序列的开头。

此脉冲的幅度小于 150mV,持续时间的典型值为 10ns。当数字输入和输出信号的负载

低于 5kΩ时,不会产生影响。

。

2007年11月 第四版 第22页

Loading...

Loading...