Datasheet ST72T213G1, ST72T212G2, ST72T101G2, ST72T101G1, ST72101G2 Datasheet (SGS Thomson Microelectronics)

...Page 1

September 1999 1/84

ST72101/ST72212/ST72213

8-BIT MCU WITH 4 TO 8K ROM/OTP/EPROM,

256 BYTES RAM, ADC, WDG, SPI AND 1 OR 2 TIMERS

DATASHEET

■ User Program Memory (ROM/OTP/EPROM):

4 to8K bytes

■ Data RAM: 256 bytes, including 64 bytes of

stack

■ Master Resetand Power-On Reset

■ Run, Wait, Slow, Halt and RAM Retention

modes

■ 22 multifunctionalbidirectional I/O lines:

– 22 programmable interrupt inputs

– 8 high sinkoutputs

– 6 analog alternateinputs

– 10 to 14 alternate functions

– EMI filtering

■ Programmable watchdog (WDG)

■ One or two 16-bit Timers, each featuring:

– 2 Input Captures

– 2 Output Compares

– External Clock input (on Timer A only)

– PWM and Pulse Generator modes

■ Synchronous Serial Peripheral Interface (SPI)

■ 8-bit Analog-to-Digital converter (6 channels)

(ST72212 and ST72213 only)

■ 8-bit Data Manipulation

■ 63 Basic Instructions

■ 17 mainAddressing Modes

■ 8 x8 Unsigned Multiply Instruction

■

True BitManipulation

■ Complete Development Support on PC/DOS-

WINDOWSTMReal-Time Emulator

■ Full Software Package on DOS/WINDOWS

TM

(C-Compiler, Cross-Assembler, Debugger)

Device Summary

SO28

PSDIP32

CSDIP32W

(See ordering information at the end of datasheet)

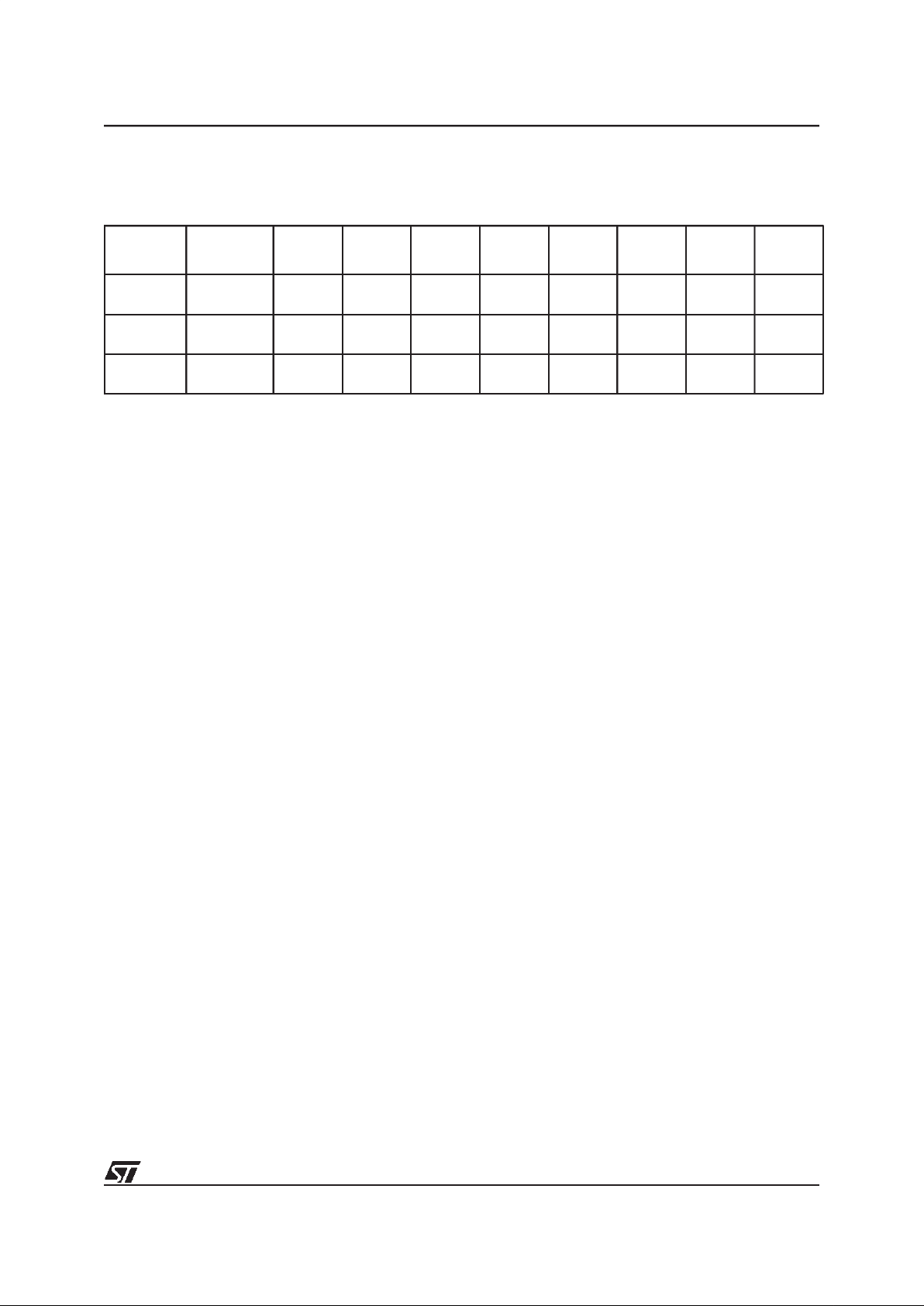

Features ST72101G1 ST72101G2 ST72213G1 ST72212G2

Program Memory- bytes 4K 8K 4K 8K

RAM (stack) - bytes 256 (64)

16-bit Timers one one one two

ADC no no yes yes

Other Peripherals Watchdog, SPI

Operating Supply 3 to 5.5 V

CPU Frequency 8MHz max (16MHz oscillator) - 4MHz max over 85°C

Temperature Range - 40°C to + 125°C

Package SO28 - SDIP32

1

Rev. 1.7

Page 2

2/84

Table of Contents

95

1 GENERAL DESCRIPTION . . . . . . ................................................ 4

1.1 INTRODUCTION . . . . . . . . . . . . ............................................. 4

1.2 PIN DESCRIPTION . . ..................................................... 5

1.3 EXTERNAL CONNECTIONS . .. . . . . . . . . . . . . . . . . . . .. . . . . . . .. . . . . . . . . ......... 9

1.4 MEMORY MAP . . . . . .. . . . ............................................... 10

2 CENTRAL PROCESSING UNIT . . ............................................... 13

2.1 INTRODUCTION . . . . . . . . . . . . ............................................13

2.2 MAIN FEATURES . . . . . . . . . . . . . . . . . . . . . . . . . .............................. 13

2.3 CPU REGISTERS . . . .................................................... 13

3 CLOCKS, RESET, INTERRUPTS & POWER SAVING MODES . . . . . .. . . . . . . ...........16

3.1 CLOCK SYSTEM . . . . . .. . . . . . ............................................16

3.1.1 General Description . . . .. . ...........................................16

3.2 RESET . . . . . . . . . . . . .. . . . . . . .. . . . . . . . . . . . . .............................. 17

3.2.1 Introduction . . . .................................................... 17

3.2.2 External Reset . . . . . . ...............................................17

3.2.3 Reset Operation . . . . . . . . . . . . . . . . . . . . . . . . . ........................... 17

3.2.4 Power-on Reset .................................................... 17

3.3 INTERRUPTS . . . .. . . . . . .. . . . . . . . . . . . . . . . . . . . . .. . . . . . . . . .. . . . . . . .. . . . . . . 18

3.4 POWER SAVING MODES . .. . . . . . . . . . . . . . . . . . . . . .. . . . . . . . . .. . . . . . . ........ 21

3.4.1 Introduction . . . .................................................... 21

3.4.2 Slow Mode . . .. . . . . . . . . . . . . . . . . . . . ................................. 21

3.4.3 Wait Mode . . . . . . . . . . . . . . .. ........................................ 21

3.4.4 Halt Mode . . . . . .................................................... 22

3.5 MISCELLANEOUS REGISTER . . . . .. . . . . . .................................. 23

4 ON-CHIP PERIPHERALS . . . . . . . . . . . ...........................................24

4.1 I/O PORTS . . . . . . . . .. . . . . . . . . ...........................................24

4.1.1 Introduction . . . .................................................... 24

4.1.2 Functional Description . . . . ...........................................24

4.1.3 I/O Port Implementation . . . . . . . . . . . . . . . . . . . ........................... 25

4.1.4 Register Description . . . . . . ...........................................28

4.2 WATCHDOG TIMER (WDG) . . . . . . .. . . . . . . .. . . .. . . .. . . . . . . . . . . . . . . . .. . . . . . . 30

4.2.1 Introduction . . . .................................................... 30

4.2.2 Main Features . .. . . . ...............................................30

4.2.3 Functional Description . . . . ...........................................31

4.2.4 Low Power Modes . . . ............................................... 31

4.2.5 Interrupts . . . . . .. . . . . . . . . . .. . . . . . . ................................. 31

4.2.6 Register Description . . . . . . ...........................................31

4.3 16-BIT TIMER . . . . . . . . . . . . . . . . . . ........................................32

4.3.1 Introduction . . . .................................................... 32

4.3.2 Main Features . .. . . . ...............................................32

4.3.3 Functional Description . . . . ...........................................32

4.3.4 Low Power Modes . . ............................................... 43

4.3.5 Interrupts . . .. . .................................................... 43

4.3.6 Register Description . . . . . . ...........................................44

2

Page 3

3/84

Table of Contents

4.4 SERIAL PERIPHERAL INTERFACE (SPI) . . . . . . . . . . . . . . . .. . . . . . . . . ...........49

4.4.1 Introduction . . . .................................................... 49

4.4.2 Main Features . .. . . . ...............................................49

4.4.3 General description . . . . . .. . . . . . . . .. . . .. . . . . . . . . . .. . . . . . . . . . . . . . . . . . . 49

4.4.4 Functional Description . . . . ...........................................51

4.4.5 Low Power Modes . . . ............................................... 58

4.4.6 Interrupts . . .. . .................................................... 58

4.4.7 Register Description . . . . . . ...........................................59

4.5 8-BIT A/D CONVERTER (ADC) . . . . . .. . . . . . . . . . . . ........................... 62

4.5.1 Introduction . . . .................................................... 62

4.5.2 Main Features . .. . . . ...............................................62

4.5.3 Functional Description . . . . ...........................................63

4.5.4 Low Power Modes . . . ............................................... 63

4.5.5 Interrupts . . . . . .. . . . . . . . . . .. . . . . . . ................................. 63

4.5.6 Register Description . . . . . . ...........................................64

5 INSTRUCTION SET . . . . . . . . . . . . . . . . . . ........................................ 65

5.1 ST7 ADDRESSING MODES . . . . . . . . . . . . . . .. . . . . . . . . . . . . . . . . . . .. . . . . . . . . . . . 65

5.1.1 Inherent . . . . . . . . . . . ...............................................66

5.1.2 Immediate . .. . . . . . . . . . . . . . . . . . . .. . . .. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

5.1.3 Direct . ........................................................... 66

5.1.4 Indexed (No Offset, Short, Long) . . . . . . . . . . . . ........................... 66

5.1.5 Indirect (Short, Long) . . . . .. . . . . . . . . . .. . . . . . . . . . . . .. . . .. . . . . . . . . . . . . . . 66

5.1.6 Indirect Indexed (Short,Long) . ........................................67

5.1.7 Relative mode (Direct,Indirect) . . . .. . . . . . . . . . . . . . . . . . . . . . . .. . . .. . . . . . . . 67

5.2 INSTRUCTION GROUPS . . . . . . . . . . . . . . . . ................................. 68

6 ELECTRICALCHARACTERISTICS . . . . . . . . . . . . . . . . .............................. 71

6.1 ABSOLUTE MAXIMUM RATINGS . . . ........................................71

6.2 RECOMMENDED OPERATING CONDITIONS . . ............................... 72

6.3 DC ELECTRICAL CHARACTERISTICS . . . . . . . . . . . . . .. . . . . . . . . . . . . ...........73

6.4 RESET CHARACTERISTICS . . . . . . . . . ..................................... 74

6.5 OSCILLATOR CHARACTERISTICS . . . .. . . . . . . .............................. 74

6.6 A/D CONVERTERCHARACTERISTICS (ST72212 AND ST72213ONLY) . . . ........ 75

6.7 SPI CHARACTERISTICS . . ...............................................77

7 GENERAL INFORMATION . . . . . . . . . . ........................................... 80

7.1 EPROM ERASURE . . .. . . . . . . . . . . . . .. . . . . . ............................... 80

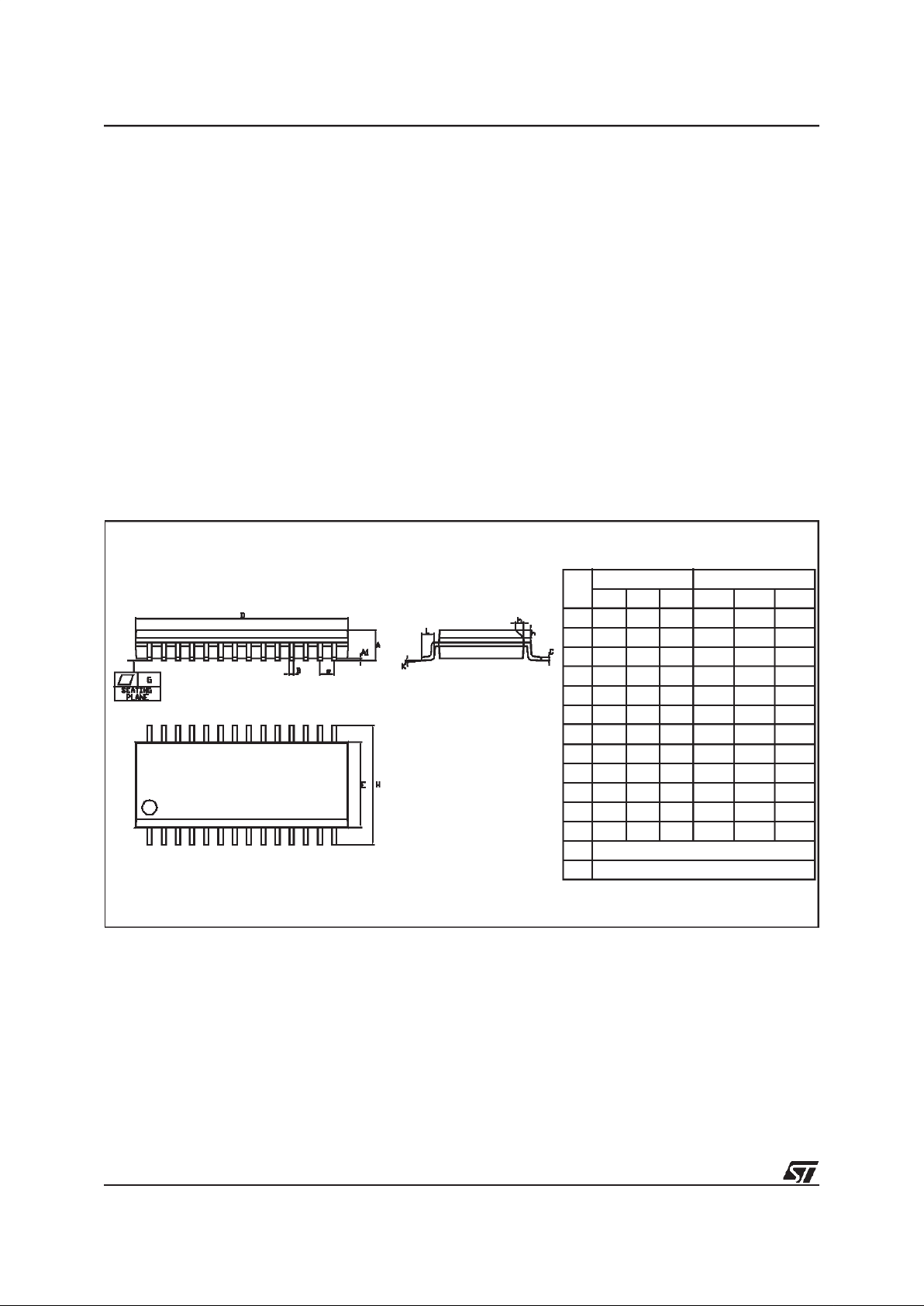

7.2 PACKAGE MECHANICALDATA . . . . . . . . . . . . .. . . . ........................... 80

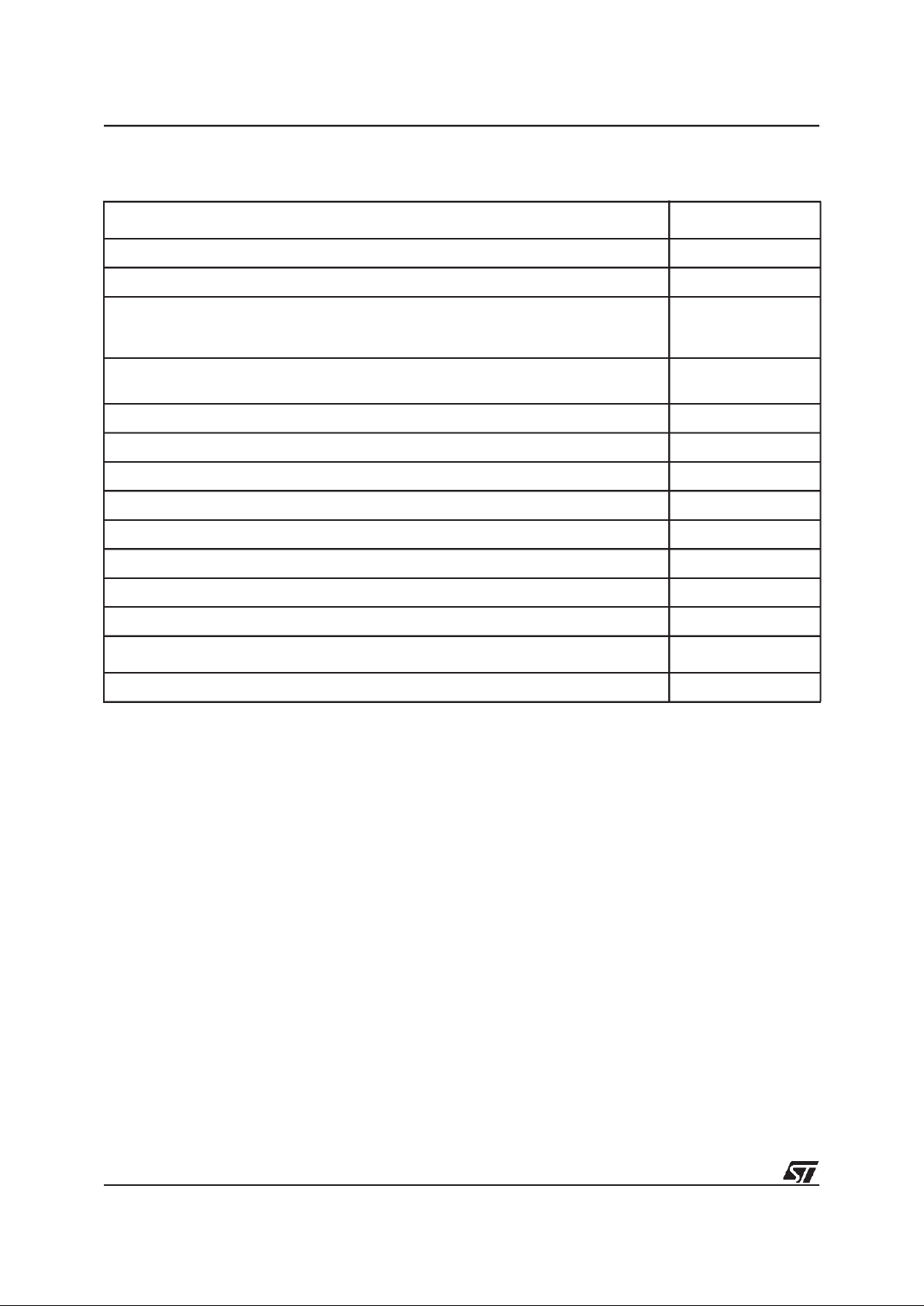

7.3 ORDERING INFORMATION . . . . . .. . . . . . . .................................. 82

7.3.1 Transfer Of CustomerCode . . . . . . . . . . . .. . . .. . . . . . . . . . . . ............... 82

8 SUMMARY OF CHANGES . . . . . . . . . . . . . . . . . . . . . . . . .. . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

3

Page 4

4/84

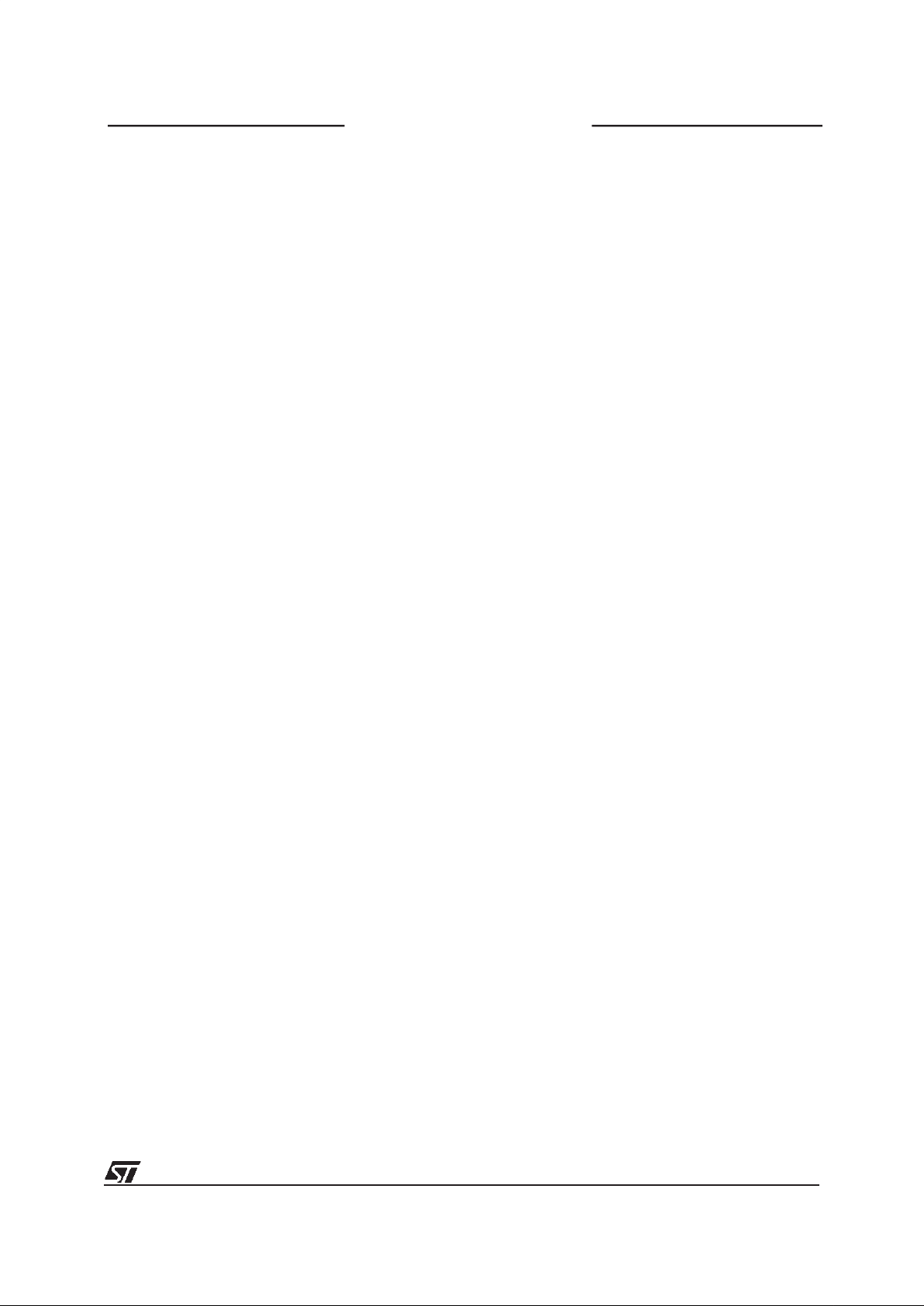

ST72101/ST72212/ST72213

1 GENERAL DESCRIPTION

1.1 INTRODUCTION

The ST72101, ST72213 and ST72212 HCMOS

Microcontroller Units are members of the ST7

family. These devices are based on an industrystandard 8-bit core and feature an enhanced

instruction set. They normally operate ata 16MHz

oscillator frequency. Under software control, the

ST72101, ST72213 and ST72212 may be placed

in either WAIT, SLOW or HALT modes, thus

reducing power consumption. The enhanced

instruction set and addressing modes afford real

programming potential. In addition to standard

8-bit data management, the ST72101, ST72213

and ST72212 feature true bit manipulation, 8x8

unsigned multiplication and indirect addressing

modes on the whole memory. The devices include

an on-chip oscillator, CPU, program memory

(ROM/OTP/EPROM versions), RAM, 22 I/O lines

and the following on-chip peripherals: Analog-toDigital Converter (ADC) with 6 multiplexed analog

inputs (ST72212 and ST72213 only), industry

standard synchronous SPI serial interface, digital

Watchdog, one or two independent 16-bit Timers,

one featuring an External Clock Input, and both

featuring Pulse Generator capabilities, 2 Input

Captures and 2 Output Compares.

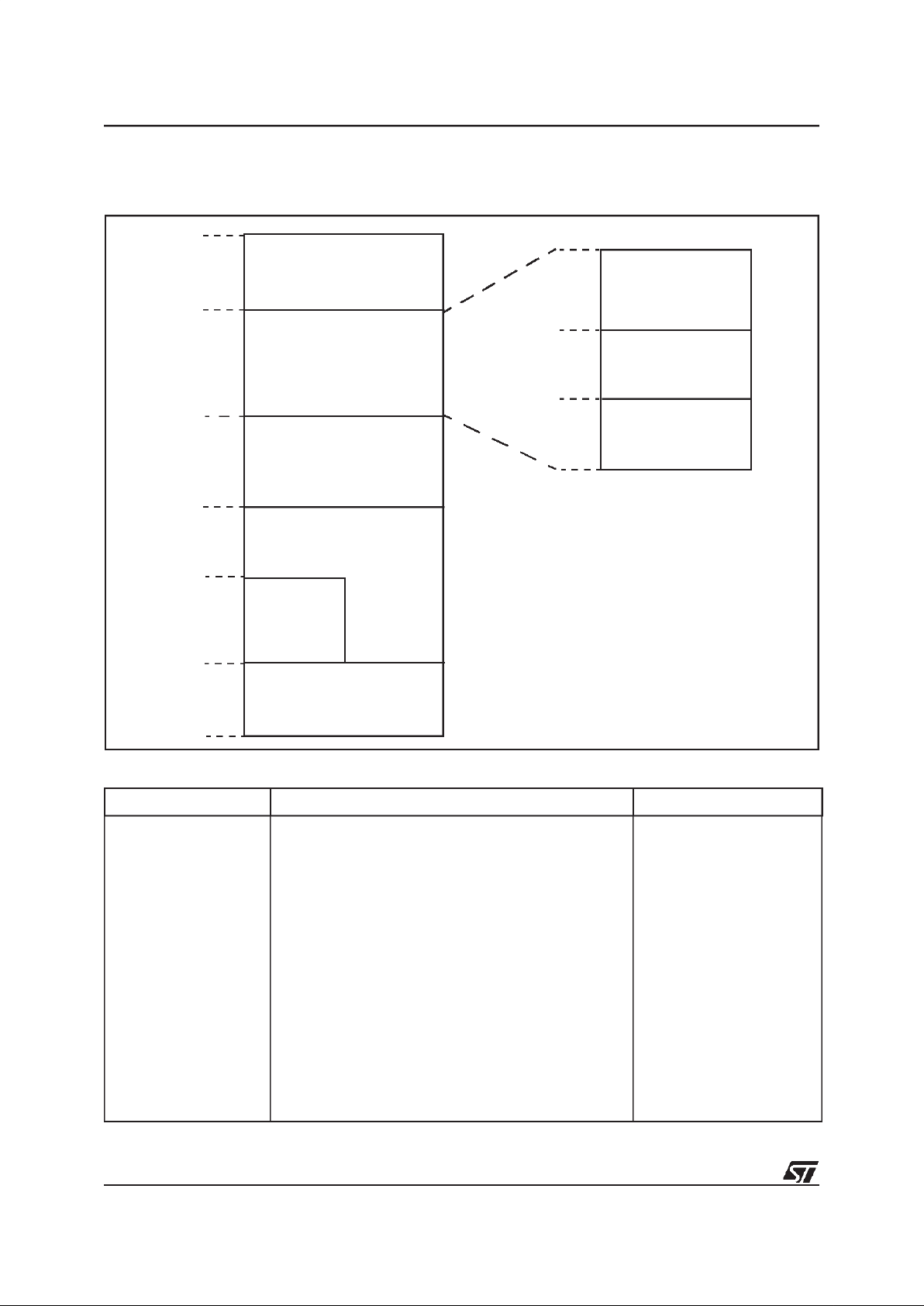

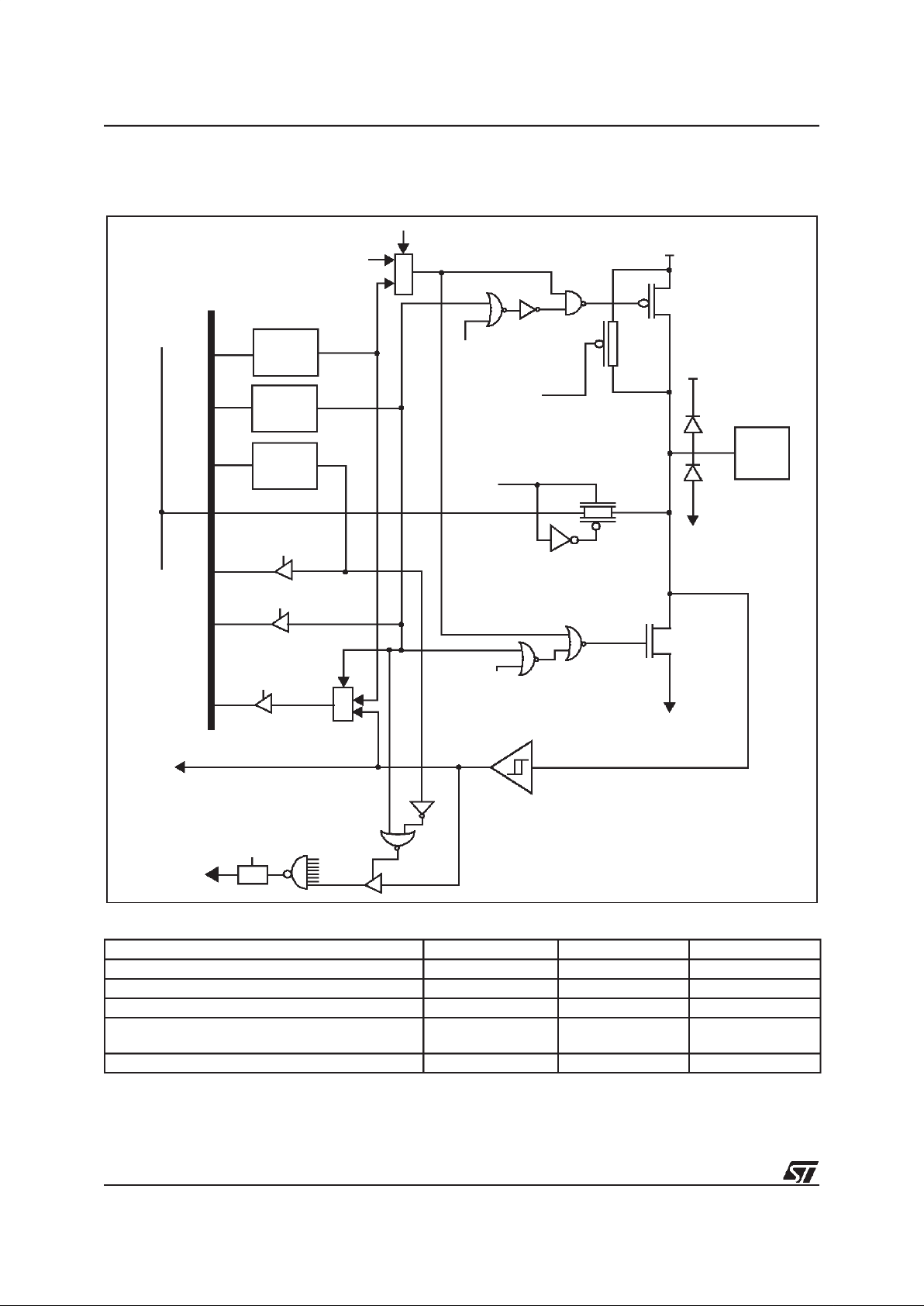

Figure 1. ST72101, ST72213 and ST72212 Block Diagram

8-BIT CORE

ALU

ADDRESSAND DATA BUS

OSCIN

OSCOUT

RESET

PORT B

TIMER A

PORT A

SPI

PORT C

8-BIT ADC

1)

WATCHDOG

PB0 -> PB7

(8 bits)

PC0 -> PC5

(6 bits)

OSC

Internal

CLOCK

CONTROL

RAM

(256 Bytes)

PA0 -> PA7

(8 bits)

V

SS

V

DD

POWER

SUPPLY

TIMER B

2)

1) ST72213 and ST72212 only

2) ST72212 only

PROGRAM

(4 - 8K Bytes)

MEMORY

4

Page 5

5/84

ST72101/ST72212/ST72213

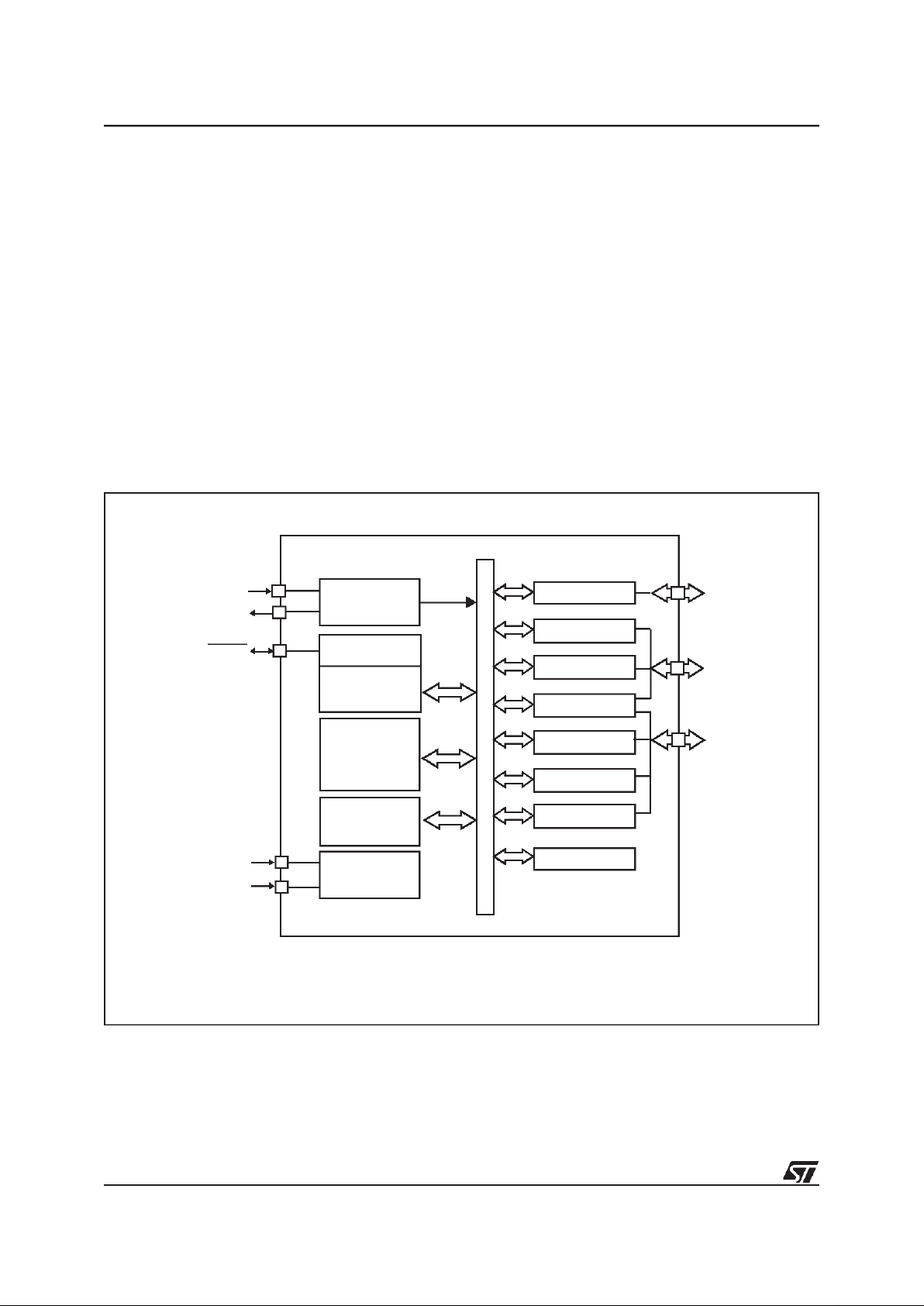

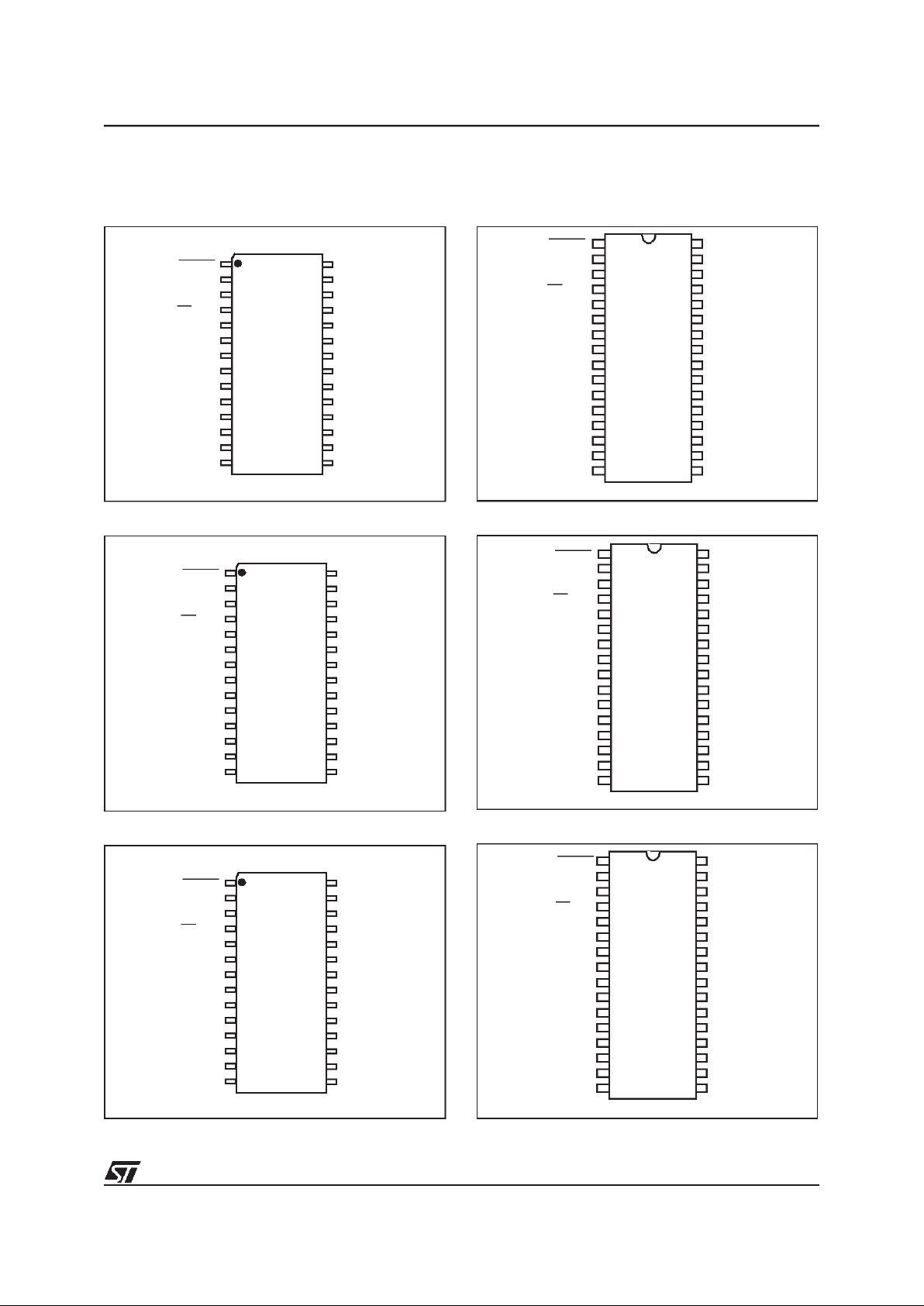

1.2 PIN DESCRIPTION

Figure 2. ST72212 Pinout (SO28)

Figure 3. ST72213 Pinout (SO28)

Figure 4. ST72101 Pinout (SO28)

Figure 5. ST72212 Pinout (SDIP32)

Figure 6. ST72213 Pinout (SDIP32)

Figure 7. ST72101 Pinout (SDIP32)

V

DD

V

SS

TEST/V

PP

1)

PA0

PA1

PA2

PA3

PA4

PA5

PA6

PA7

PC0/ICAP1_B/AIN0

PC1/OCMP1_B/AIN1

PC2/CLKOUT/AIN2

RESET

OSCIN

OSCOUT

SS/PB7

SCK/PB6

MISO/PB5

MOSI/PB4

OCMP2_A/PB3

ICAP2_A/PB2

OCMP1_A/PB1

ICAP1_A/PB0

AIN5/EXTCLK_A/PC5

AIN4/OCMP2_B/PC4

AIN3/ICAP2_B/PC3

15

16

17

18

19

20

28

27

26

25

24

23

22

21

1

2

3

4

5

6

7

8

9

10

11

12

13

14

1) VPPonEPROM/OTP only

V

DD

V

SS

TEST/V

PP

1)

PA0

PA1

PA2

PA3

PA4

PA5

PA6

PA7

PC0/AIN0

PC1/AIN1

PC2/CLKOUT/AIN2

RESET

OSCIN

OSCOUT

SS/PB7

SCK/PB6

MISO/PB5

MOSI/PB4

OCMP2_A/PB3

ICAP2_A/PB2

OCMP1_A/PB1

ICAP1_A/PB0

AIN5/EXTCLK_A/PC5

AIN4/PC4

AIN3/PC3

15

16

17

18

19

20

28

27

26

25

24

23

22

21

1

2

3

4

5

6

7

8

9

10

11

12

13

14

1) VPPon EPROM/OTPonly

V

DD

V

SS

TEST/V

PP

1)

PA0

PA1

PA2

PA3

PA4

PA5

PA6

PA7

PC0

PC1

PC2/CLKOUT

RESET

OSCIN

OSCOUT

SS/PB7

SCK/PB6

MISO/PB5

MOSI/PB4

OCMP2_A/PB3

ICAP2_A/PB2

OCMP1_A/PB1

ICAP1_A/PB0

EXTCLK_A/PC5

PC4

PC3

15

16

17

18

19

20

28

27

26

25

24

23

22

21

1

2

3

4

5

6

7

8

9

10

11

12

13

14

1) VPPon EPROM/OTP only

RESET

OSCIN

OSCOUT

SS/PB7

SCK/PB6

MISO/PB5

MOSI/PB4

OCMP2_A/PB3

ICAP2_A/PB2

OCMP1_A/PB1

ICAP1_A/PB0

AIN5/EXTCLK_A/PC5

AIN4/OCMP2_B/PC4

AIN3/ICAP2_B/PC3

V

DD

V

SS

TEST/V

PP

1)

PA0

PA1

PA2

PA3

PA4

PA5

PA6

PA7

PC0/ICAP1_B/AIN0

PC1/OCMP1_B/AIN1

PC2/CLKOUT/AIN2

NC

NC

NC

NC

28

27

26

25

24

23

22

21

20

19

18

17

16

15

1

2

3

4

5

6

7

8

9

10

11

12

13

14

29

30

31

32

1) VPPon EPROM/OTP only

RESET

OSCIN

OSCOUT

SS/PB7

SCK/PB6

MISO/PB5

MOSI/PB4

OCMP2_A/PB3

ICAP2_A/PB2

OCMP1_A/PB1

ICAP1_A/PB0

AIN5/EXTCLK_A/PC5

AIN4/PC4

AIN3/PC3

NC

NC

V

DD

V

SS

TEST/V

PP

1)

PA0

PA1

PA2

PA3

PA4

PA5

PA6

PA7

PC0/AIN0

PC1/AIN1

PC2/CLKOUT/AIN2

NC

NC

28

27

26

25

24

23

22

21

20

19

18

1716

15

1

2

3

4

5

6

7

8

9

10

11

12

13

14

29

30

31

32

1) VPPonEPROM/OTP only

V

DD

V

SS

TEST/V

PP

1)

PA0

PA1

PA2

PA3

PA4

PA5

PA6

PA7

PC0

PC1

PC2/CLKOUT

RESET

OSCIN

OSCOUT

SS/PB7

SCK/PB6

MISO/PB5

MOSI/PB4

OCMP2_A/PB3

ICAP2_A/PB2

OCMP1_A/PB1

ICAP1_A/PB0

EXTCLK_A/PC5

PC4

PC3

NC

NC

NC

NC

28

27

26

25

24

23

22

21

20

19

18

1716

15

1

2

3

4

5

6

7

8

9

10

11

12

13

14

29

30

31

32

1) VPPon EPROM/OTPonly

5

Page 6

6/84

ST72101/ST72212/ST72213

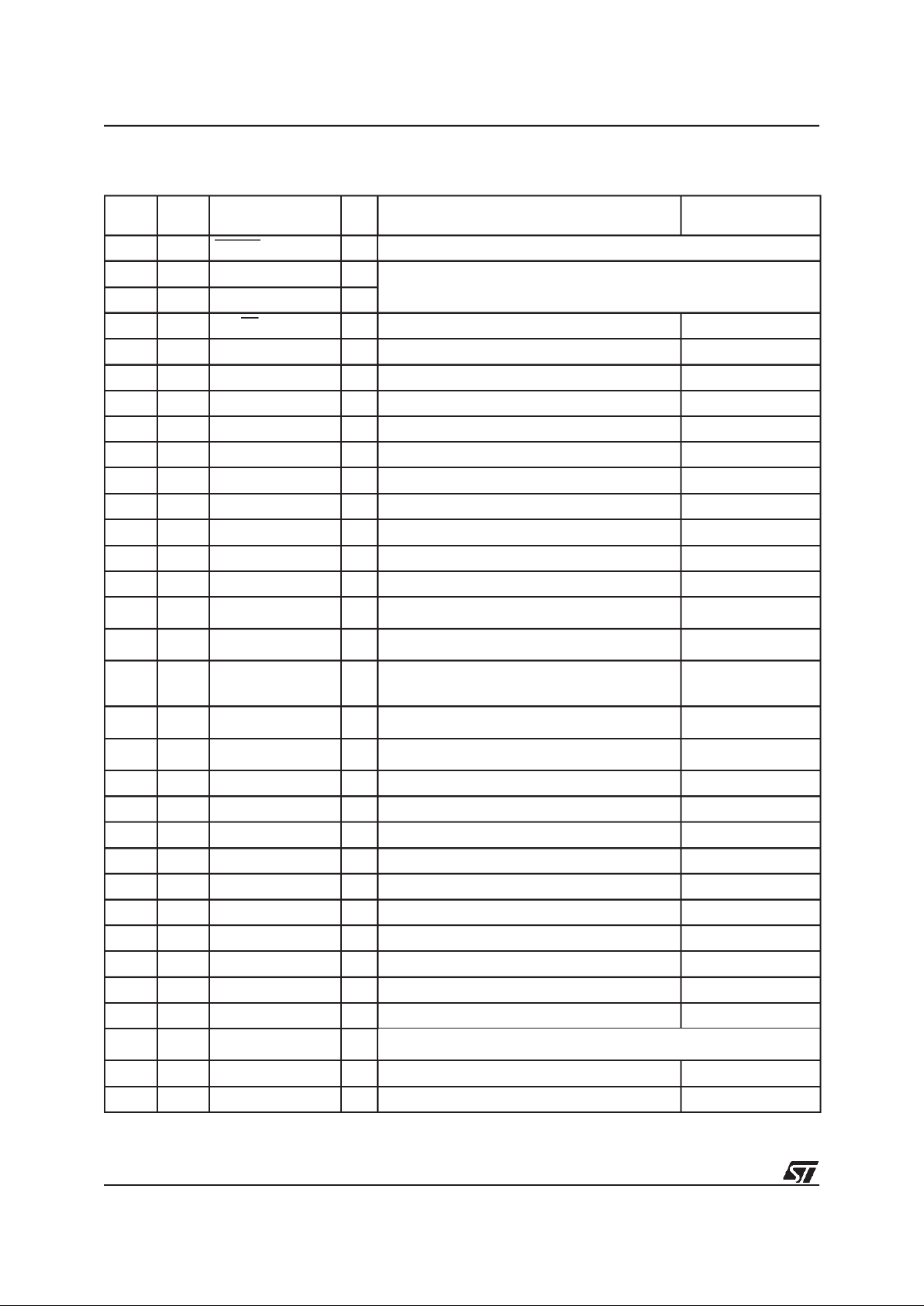

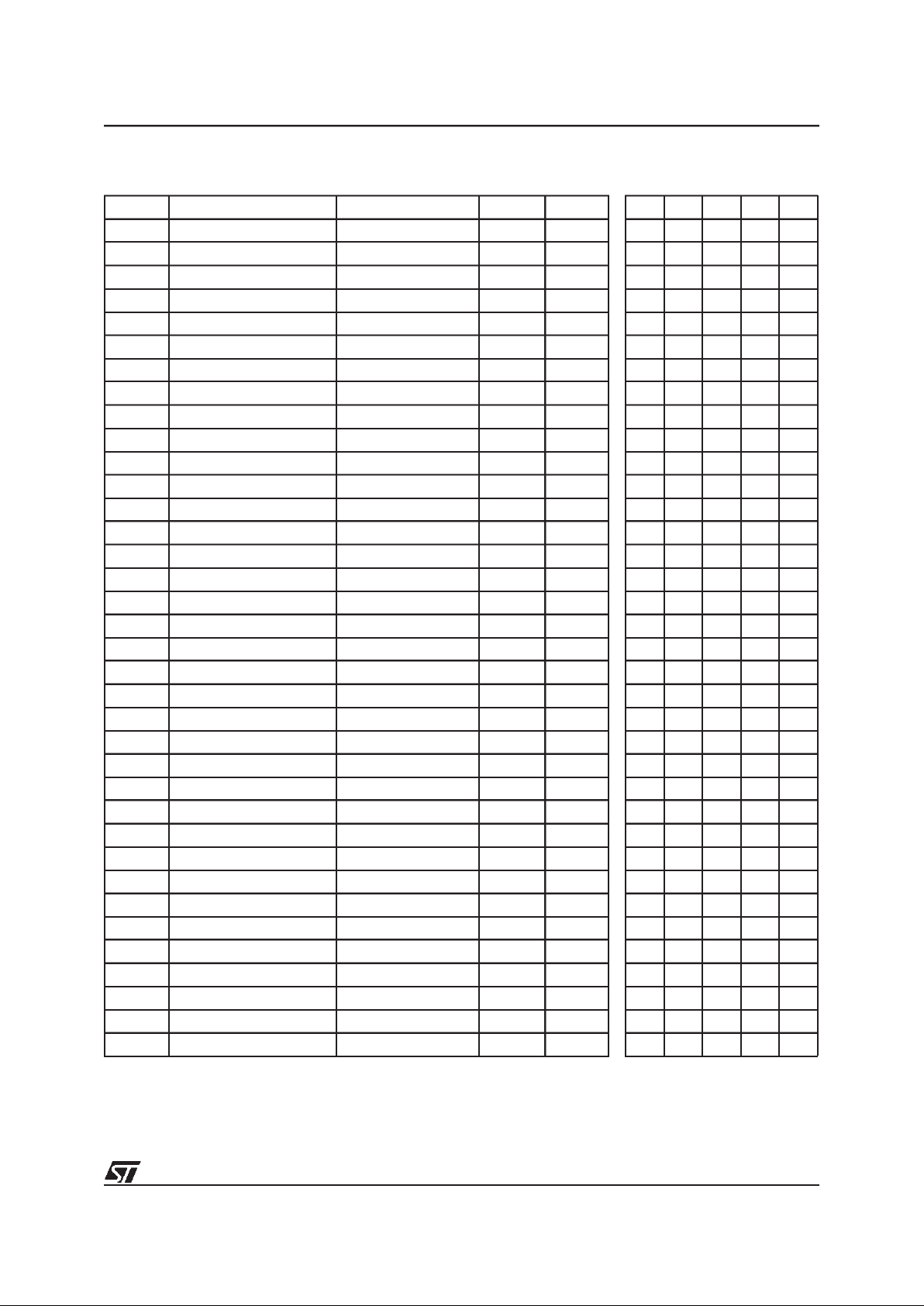

Table 1. ST72212 Pin Configuration

Note 1:VPPon EPROM/OTP only

Pin n°

SDIP32

Pin n °

SO28

Pin Name Type Description Remarks

1 1 RESET I/O Bidirectional. Active low. Top priority non maskable interrupt.

22OSCIN I

Input/Output Oscillator pin. These pins connect a parallel-resonant

crystal, or an external source to the on-chip oscillator.

3 3 OSCOUT O

4 4 PB7/SS I/O Port B7 or SPI Slave Select (active low) External Interrupt: EI1

5 5 PB6/SCK I/O Port B6 or SPI Serial Clock External Interrupt: EI1

6 6 PB5/MISO I/O Port B5 or SPI Master In/ Slave Out Data External Interrupt: EI1

7 7 PB4/MOSI I/O Port B4 or SPI Master Out / Slave In Data External Interrupt: EI1

8 NC Not Connected

9 NC Not Connected

10 8 PB3/OCMP2_A I/O Port B3 or TimerA Output Compare 2 External Interrupt: EI1

11 9 PB2/ICAP2_A I/O Port B2 or TimerA Input Capture 2 External Interrupt: EI1

12 10 PB1/OCMP1_A I/O Port B1 or TimerA Output Compare 1 External Interrupt: EI1

13 11 PB0/ICAP1_A I/O Port B0 or TimerA Input Capture 1 External Interrupt: EI1

14 12 PC5/EXTCLK_A/AIN5 I/O PortC5orTimerA InputClockorADCAnalog Input5 External Interrupt: EI1

15 13 PC4/OCMP2_B/AIN4 I/O

PortC4orTimerB OutputCompare2orADCAnalog

Input 4

External Interrupt: EI1

16 14 PC3 /IC A P2 _ B /AIN 3 I/O

Port C3 orTimerB InputCapture 2 orADC Analog

Input 3

External Interrupt: EI1

17 15 PC2/CLKOUT/AIN2 I/O

Port C2or InternalClockFrequency Outputor ADC

Analog Input 2. Clockout is driven by Bit 5 of the

miscellaneous register.

External Interrupt: EI1

18 16 PC1/OCMP1_B/AIN1 I/O

PortC1orTimerB OutputCompare1orADCAnalog

Input 1

External Interrupt: EI1

19 17 PC0 /IC A P1 _ B /AIN 0 I/O

Port C0 orTimerB InputCapture 1 orADC Analog

Input 0

External Interrupt: EI1

20 18 PA7 I/O Port A7, High Sink External Interrupt: EI0

21 19 PA6 I/O Port A6, High Sink External Interrupt: EI0

22 20 PA5 I/O Port A5, High Sink External Interrupt: EI0

23 21 PA4 I/O Port A4, High Sink External Interrupt: EI0

24 NC Not Connected

25 NC Not Connected

26 22 PA3 I/O Port A3, High Sink External Interrupt: EI0

27 23 PA2 I/O Port A2, High Sink External Interrupt: EI0

28 24 PA1 I/O Port A1, High Sink External Interrupt: EI0

29 25 PA0 I/O Port A0, High Sink External Interrupt: EI0

30 26 TEST/V

PP

(1)

I/S

Test mode pin (should be tied low in user mode). In the EPROM programming mode, this pin acts as the programming voltage input V

PP.

31 27 V

SS

S Ground

32 28 V

DD

S Main power supply

6

Page 7

7/84

ST72101/ST72212/ST72213

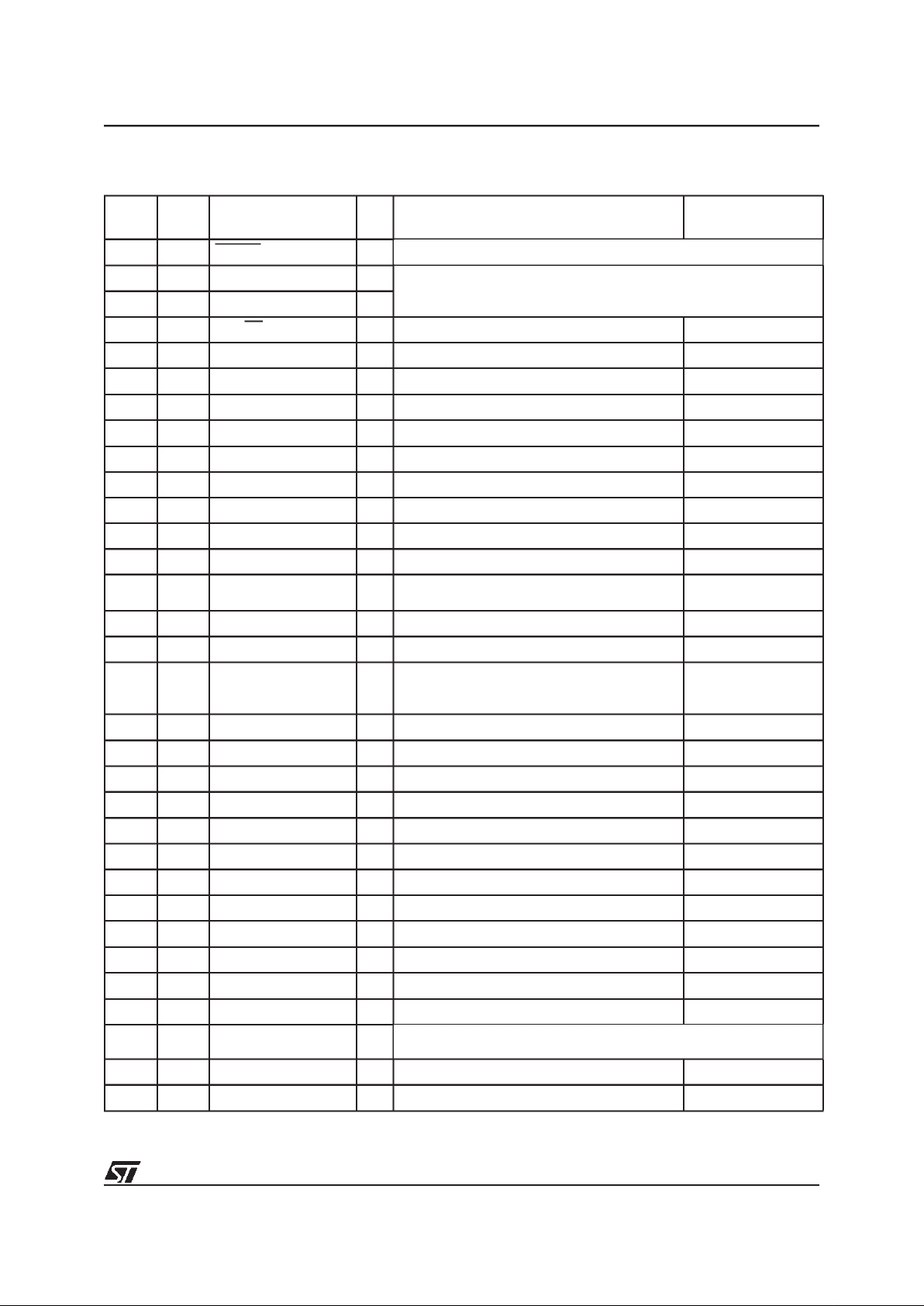

Table 2. ST72213 Pin Configuration

Note 1:VPPon EPROM/OTP only

Pin n°

SDIP32

Pin n°

SO28

Pin Name Type Description Remarks

1 1 RESET I/O

Bidirectional. Active low. Top priority non maskable interrupt.

2 2 OSCIN I

Input/Output Oscillator pin. These pins connect a parallel-resonant

crystal, oran external source to the on-chip oscillator.

3 3 OSCOUT O

4 4 PB7/SS I/O Port B7 orSPI Slave Select (active low) External Interrupt: EI1

5 5 PB6/SCK I/O Port B6 orSPI Serial Clock External Interrupt: EI1

6 6 PB5/MISO I/O Port B5 orSPI Master In/ Slave Out Data External Interrupt: EI1

7 7 PB4/MOSI I/O Port B4 orSPI Master Out / Slave In Data External Interrupt: EI1

8 NC Not Connected

9 NC Not Connected

10 8 PB3/OCMP2_A I/O Port B3 or TimerA Output Compare 2 External Interrupt: EI1

11 9 PB2/ICAP2_A I/O Port B2 orTimerA Input Capture 2 External Interrupt: EI1

12 10 PB1/OCMP1_A I/O Port B1 or TimerA Output Compare 1 External Interrupt: EI1

13 11 PB0/ICAP1_A I/O Port B0 orTimerA Input Capture 1 External Interrupt: EI1

14 12 PC5/EXTCLK_A/AIN5 I/O

Port C5 orTimerA Input Clock or ADC Analog

Input 5

External Interrupt: EI1

15 13 PC4/AIN4 I/O Port C4 or ADC Analog Input 4 External Interrupt: EI1

16 14 PC3/AIN3 I/O Port C3 or ADC Analog Input 3 External Interrupt: EI1

17 15 PC2/CLKOUT/AIN2 I/O

Port C2 orInternal Clock Frequency Output or

ADC Analog Input 2. Clockout is driven by Bit 5

of the miscellaneous register.

External Interrupt: EI1

18 16 PC1/AIN1 I/O Port C1 or ADC Analog Input 1 External Interrupt: EI1

19 17 PC0/AIN0 I/O Port C0 or ADC Analog Input 0 External Interrupt: EI1

20 18 PA7 I/O Port A7, High Sink External Interrupt: EI0

21 19 PA6 I/O Port A6, High Sink External Interrupt: EI0

22 20 PA5 I/O Port A5, High Sink External Interrupt: EI0

23 21 PA4 I/O Port A4, High Sink External Interrupt: EI0

24 NC Not Connected

25 NC Not Connected

26 22 PA3 I/O Port A3, High Sink External Interrupt: EI0

27 23 PA2 I/O Port A2, High Sink External Interrupt: EI0

28 24 PA1 I/O Port A1, High Sink External Interrupt: EI0

29 25 PA0 I/O Port A0, High Sink External Interrupt: EI0

30 26 TEST/V

PP

(1)

I/S

Test mode pin (should be tied low in user mode). In the EPROM programming mode, this pin acts asthe programming voltage input V

PP.

31 27 V

SS

S Ground

32 28 V

DD

S Main power supply

7

Page 8

8/84

ST72101/ST72212/ST72213

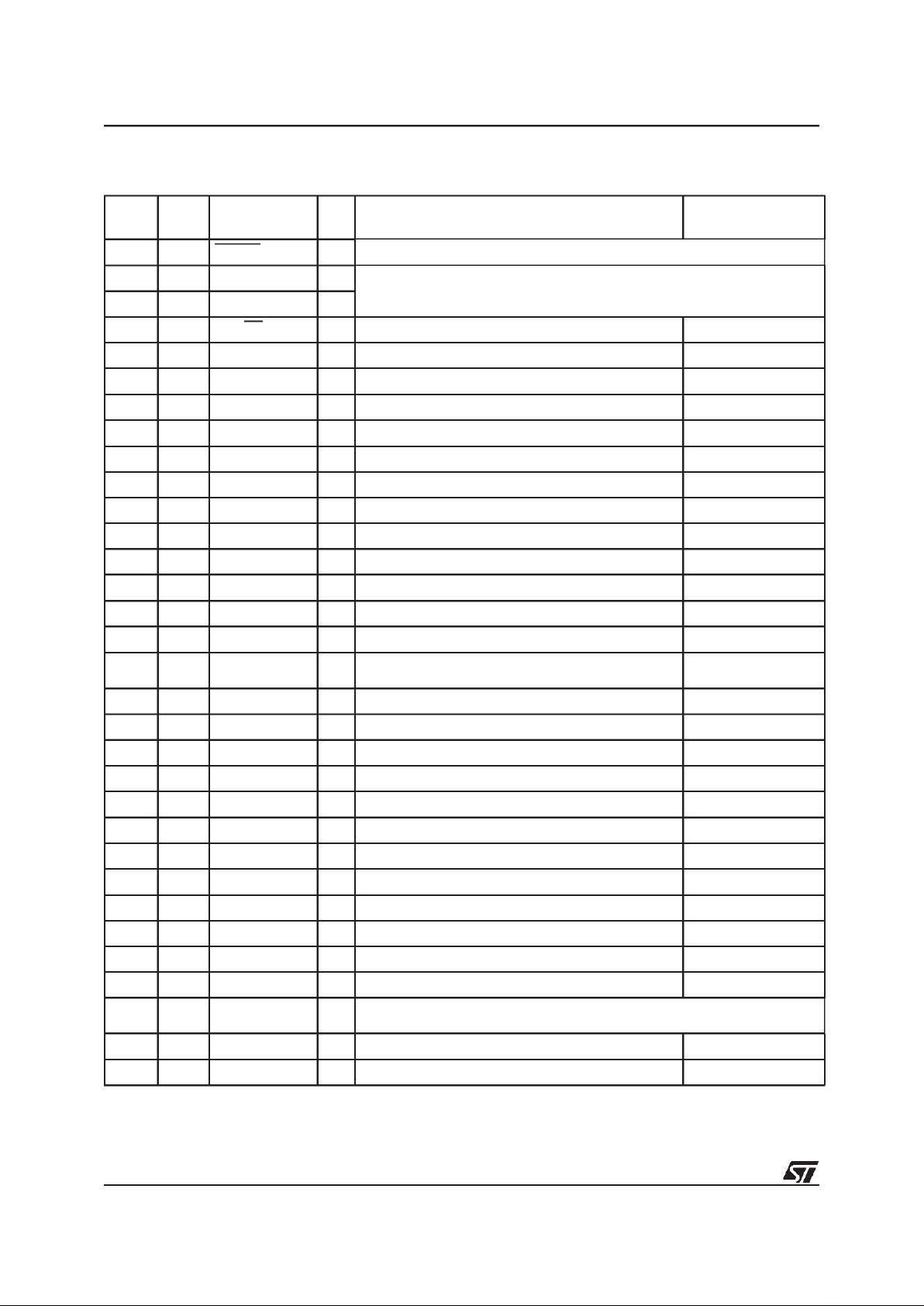

Table 3. ST72101 Pin Configuration

Pin n°

SDIP32

Pinn°

SO28

Pin Name Type Description Remarks

1 1 RESET I/O Bidirectional. Active low. Top priority non maskable interrupt.

2 2 OSCIN I

Input/Output Oscillator pin. These pins connect a parallel-resonant crystal, or

an external source to the on-chip oscillator.

3 3 OSCOUT O

4 4 PB7/SS I/O Port B7 orSPI Slave Select (active low) External Interrupt: EI1

5 5 PB6/SCK I/O Port B6 orSPI Serial Clock External Interrupt: EI1

6 6 PB5/MISO I/O Port B5 orSPI Master In/ Slave Out Data External Interrupt: EI1

7 7 PB4/MOSI I/O Port B4 orSPI Master Out / Slave In Data External Interrupt: EI1

8 NC Not Connected

9 NC Not Connected

10 8 PB3/OCMP2_A I/O Port B3 orTimerA Output Compare 2 External Interrupt: EI1

11 9 PB2/ICAP2_A I/O Port B2 orTimerA Input Capture 2 External Interrupt: EI1

12 10 PB1/OCMP1_A I/O Port B1 orTimerA Output Compare 1 External Interrupt: EI1

13 11 PB0/ICAP1_A I/O Port B0 orTimerA Input Capture 1 External Interrupt: EI1

14 12 PC5/EXTCLK_A I/O Port C5 or TimerA Input Clock External Interrupt: EI1

15 13 PC4 I/O Port C4 External Interrupt: EI1

16 14 PC3 I/O Port C3 External Interrupt: EI1

17 15 PC2/CLKOUT I/O

Port C2 or Internal Clock Frequency Output.Clockout

is driven by MCO bit of the miscellaneous register.

External Interrupt: EI1

18 16 PC1 I/O Port C1 External Interrupt: EI1

19 17 PC0 I/O Port C0 External Interrupt: EI1

20 18 PA7 I/O Port A7, High Sink External Interrupt: EI0

21 19 PA6 I/O Port A6, High Sink External Interrupt: EI0

22 20 PA5 I/O Port A5, High Sink External Interrupt: EI0

23 21 PA4 I/O Port A4, High Sink External Interrupt: EI0

24 NC Not Connected

25 NC Not Connected

26 22 PA3 I/O Port A3, High Sink External Interrupt: EI0

27 23 PA2 I/O Port A2, High Sink External Interrupt: EI0

28 24 PA1 I/O Port A1, High Sink External Interrupt: EI0

29 25 PA0 I/O Port A0, High Sink External Interrupt: EI0

30 26 TEST/V

PP

(1)

I/S

Test mode pin (should be tied low in user mode). In the EPROM programming

mode, this pin acts as the programming voltage input V

PP.

31 27 V

SS

S Ground

32 28 V

DD

S Main power supply

Note 1:V

PP

on EPROM/OTP only.

8

Page 9

9/84

ST72101/ST72212/ST72213

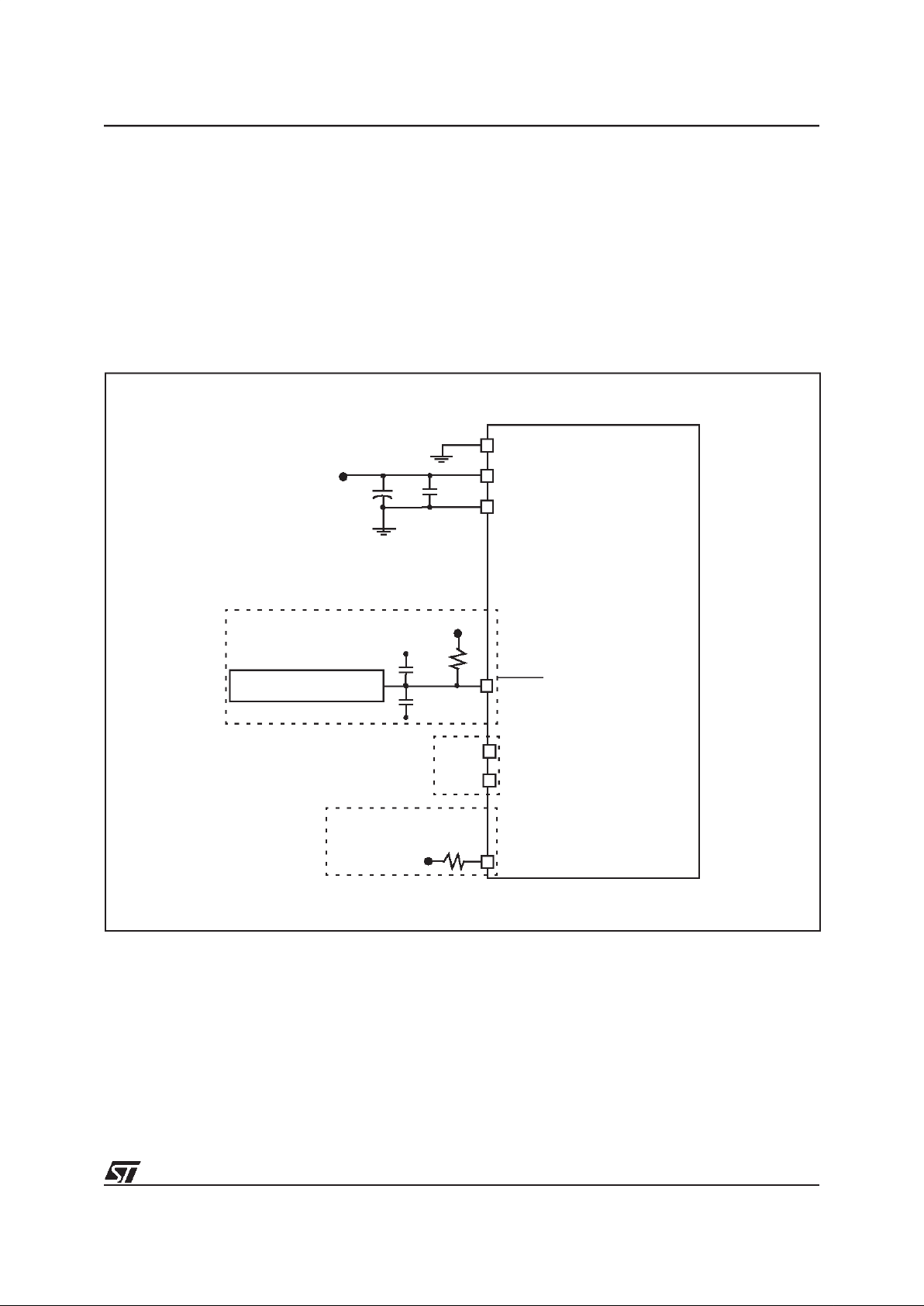

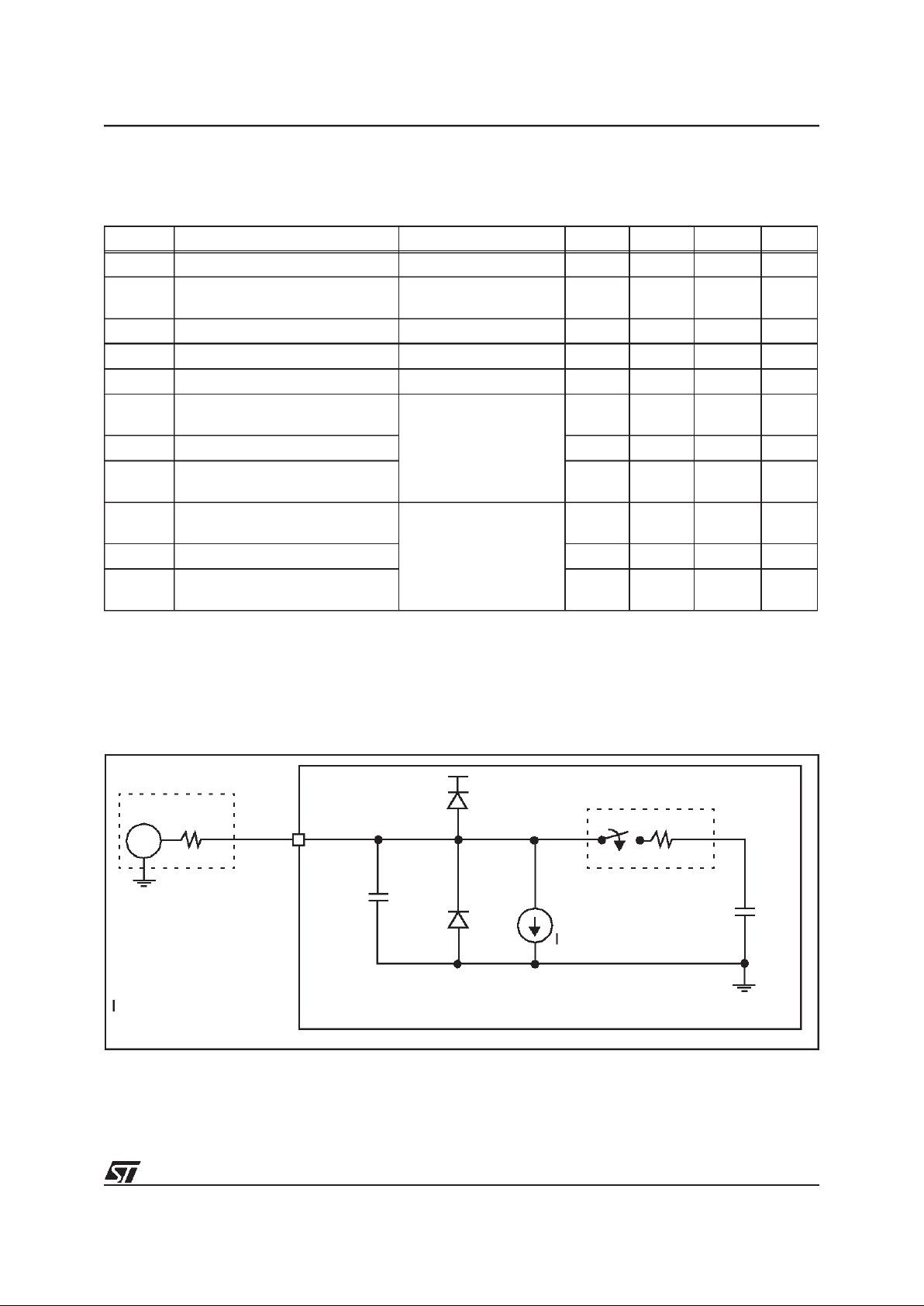

1.3 EXTERNAL CONNECTIONS

The following figure shows the recommended external connections for the device.

The VPPpin is only used for programming OTP

and EPROM devices and must betied to ground in

user mode.

The 10 nF and 0.1 µF decoupling capacitors on

the power supply lines are a suggested EMC performance/cost tradeoff.

The external reset network is intended to protect

the device against parasitic resets, especially in

noisy environments.

Unused I/Os should be tied high to avoid any unnecessary power consumption on floating lines.

An alternative solution is to program the unused

ports as inputs with pull-up.

Figure 8. Recommended External Connections

V

PP

V

DD

V

SS

OSCIN

OSCOUT

RESET

V

DD

0.1µF

+

See

Clocks

Section

V

DD

0.1µF

0.1µF

EXTERNAL RESET CIRCUIT

Or configure unused I/O ports

Unused I/O

10nF

4.7K

10K

by software as input with pull-up

V

DD

9

Page 10

10/84

ST72101/ST72212/ST72213

1.4 MEMORY MAP

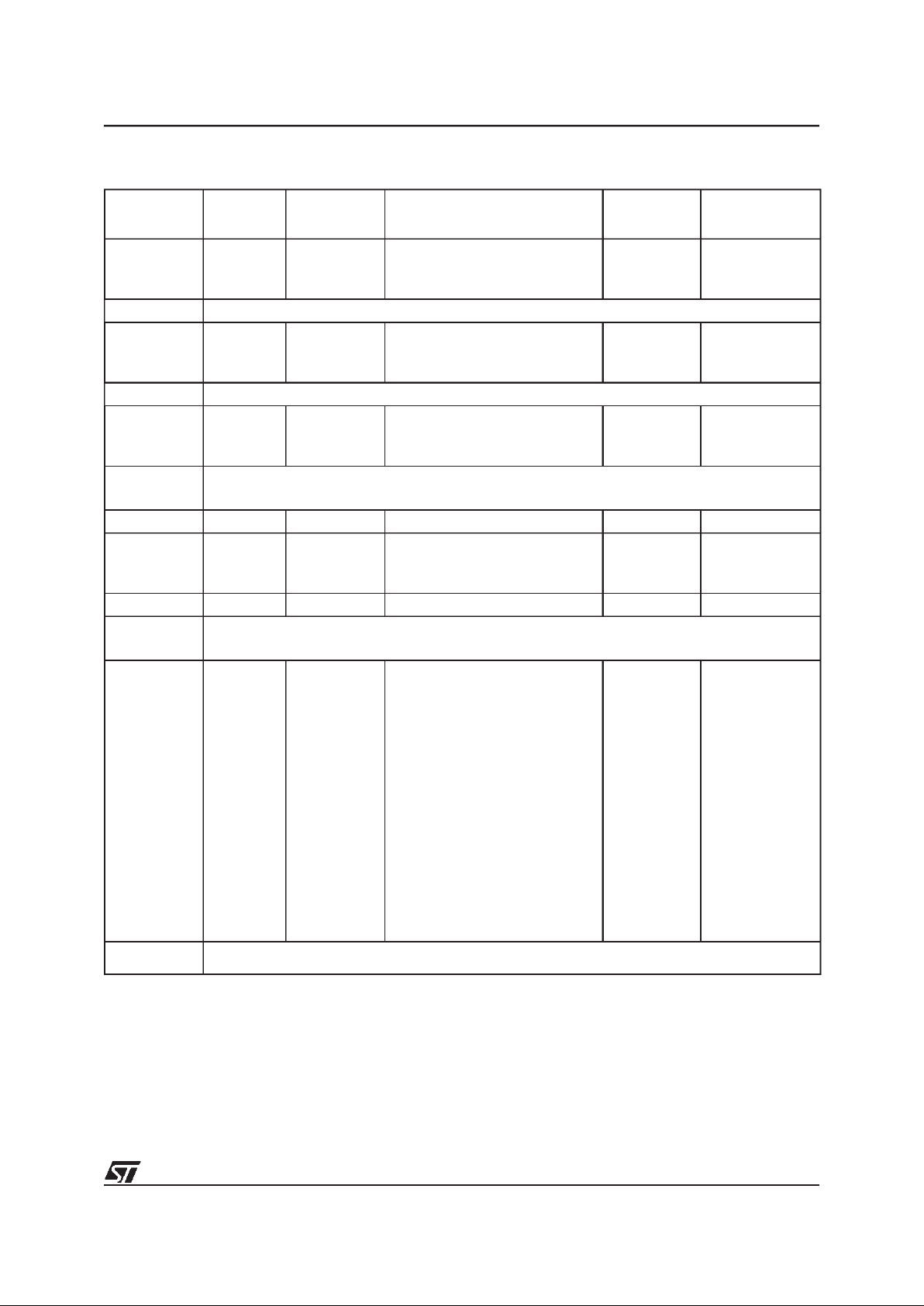

Figure 9. Memory Map

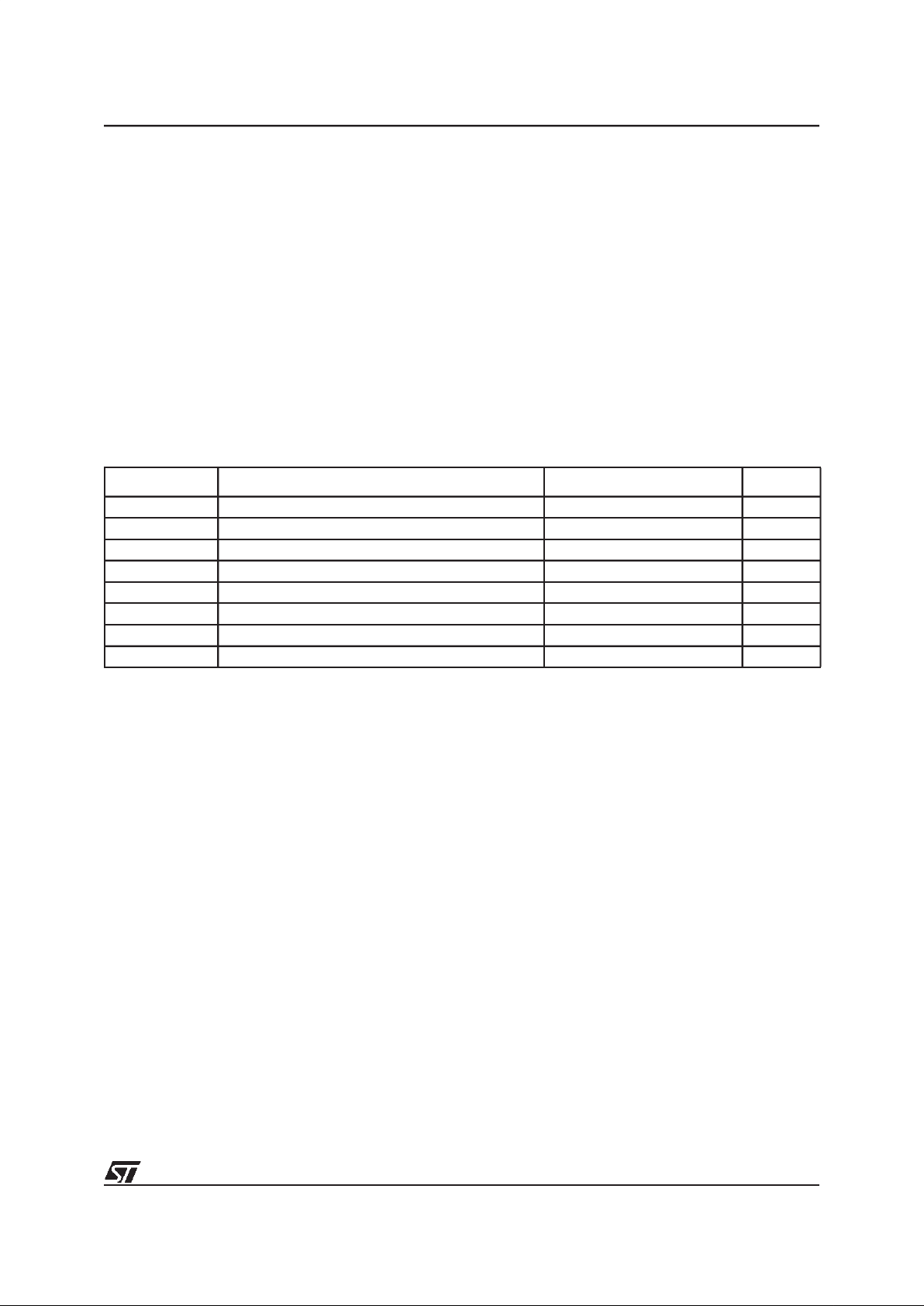

Table 4. Interrupt Vector Map

Vector Address Description Remarks

FFE0-FFE1h

FFE2-FFE3h

FFE4-FFE5h

FFE6-FFE7h

FFE8-FFE9h

FFEA-FFEBh

FFEC-FFEDh

FFEE-FFEFh

FFF0-FFF1h

FFF2-FFF3h

FFF4-FFF5h

FFF6-FFF7h

FFF8-FFF9h

FFFA-FFFBh

FFFC-FFFDh

FFFE-FFFFh

Not Used

Not Used

Not Used

Not Used

Not Used

Not Used

Not Used

TIMER B Interrupt Vector (ST72212 only)

Not Used

TIMER A Interrupt Vector

SPI Interrupt Vector

Not Used

External Interrupt Vector EI1

External Interrupt Vector EI0

TRAP (software) Interrupt Vector

RESET Vector

Internal Interrupt

Internal Interrupt

Internal Interrupt

External Interrupt

External Interrupt

CPU Interrupt

0000h

8K Bytes

Interrupt & Reset Vectors

HW Registers

017Fh

0080h

007Fh

DFFFh

Reserved

(see Table 5)

E000h

FFDFh

FFE0h

FFFFh

(see Table 4)

4K Bytes

F000h

256 Bytes RAM

Short Addressing

RAM (zero page)

16-bit Addressing

RAM

0100h

0140h

017Fh

0080h

00FFh

013Fh

64 Bytes Stack or

16-bit Addressing RAM

0180h

Program Memory

Program

Memory

10

Page 11

11/84

ST72101/ST72212/ST72213

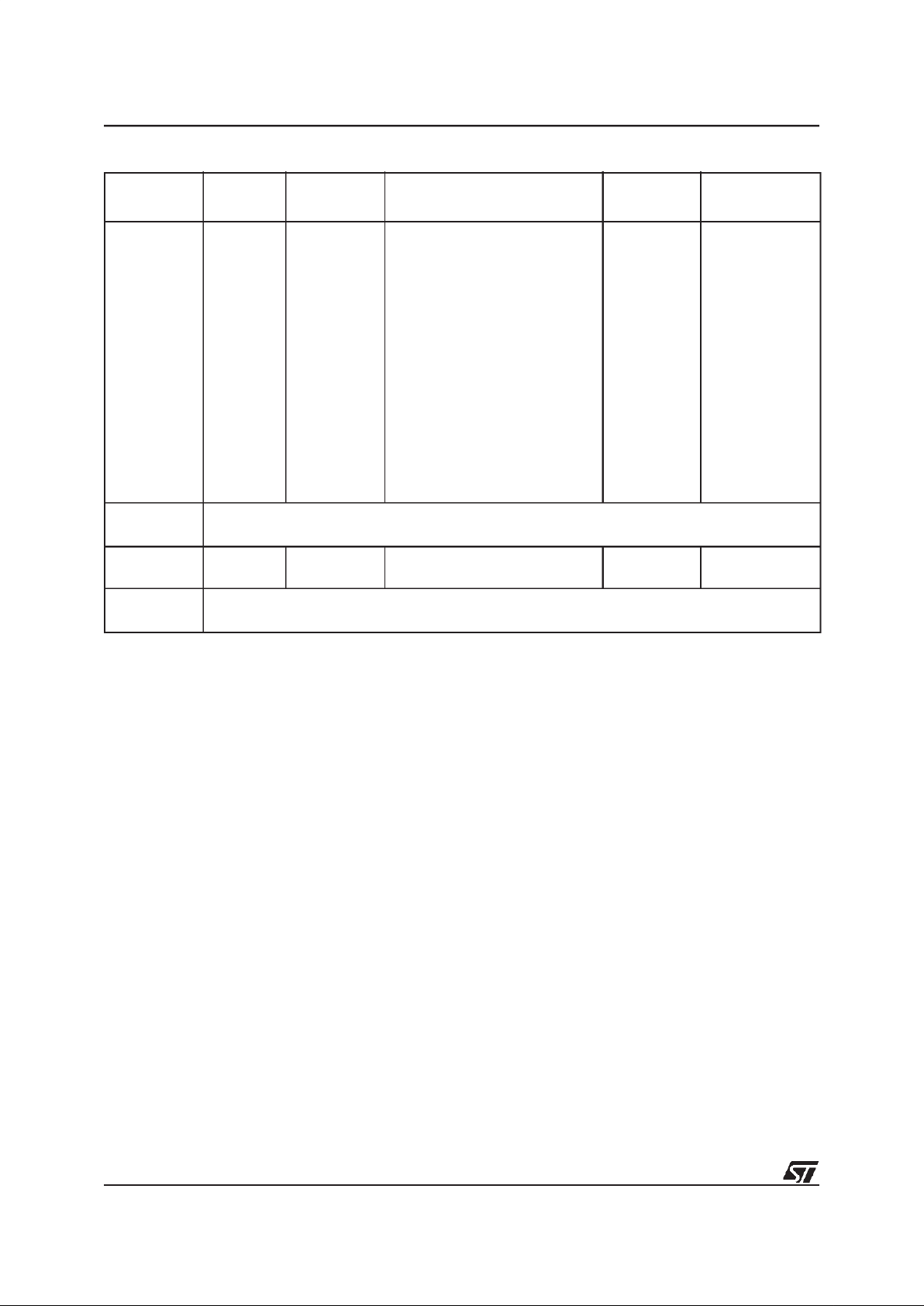

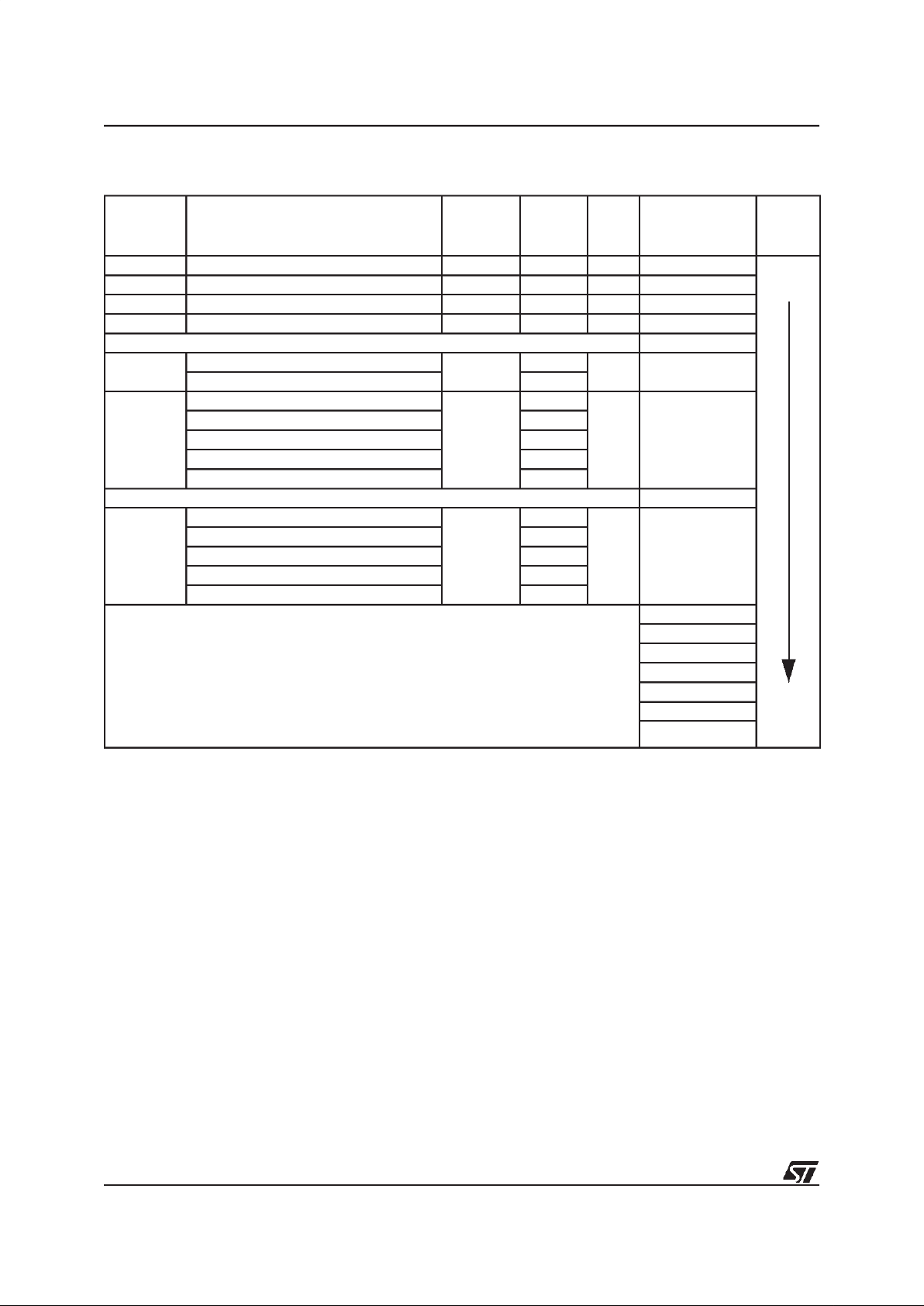

Table 5. Hardware Register Memory Map

Address

Block

Name

Register

Label

Register name Reset Status Remarks

0000h

0001h

0002h

Port C

PCDR

PCDDR

PCOR

Data Register

Data Direction Register

Option Register

00h

00h

00h

R/W

R/W

R/W

0003h Reserved Area (1 Byte)

0004h

0005h

0006h

Port B

PBDR

PBDDR

PBOR

Data Register

Data Direction Register

Option Register

00h

00h

00h

R/W

R/W

R/W

0007h Reserved Area (1 Byte)

0008h

0009h

000Ah

Port A

PADR

PADDR

PAOR

Data Register

Data Direction Register

Option Register

00h

00h

00h

R/W

R/W

R/W

000Bh to

001Fh

Reserved Area (21 Bytes)

0020h MISCR Miscellaneous Register 00h R/W

0021h

0022h

0023h

SPI

SPIDR

SPICR

SPISR

Data I/O Register

Control Register

Status Register

xxh

0xh

00h

R/W

R/W

Read Only

0024h WDG WDGCR Watchdog Control register 7Fh R/W

0025h to

0030h

Reserved Area (12 Bytes)

0031h

0032h

0033h

0034h-0035h

0036h-0037h

0038h-0039h

003Ah-003Bh

003Ch-003Dh

003Eh-003Fh

Timer A

TACR2

TACR1

TASR

TAIC1HR

TAIC1LR

TAOC1HR

TAOC1LR

TACHR

TACLR

TAACHR

TAACLR

TAIC2HR

TAIC2LR

TAOC2HR

TAOC2LR

Control Register2

Control Register1

Status Register

Input Capture1 High Register

Input Capture1 Low Register

Output Compare1 High Register

Output Compare1 Low Register

Counter High Register

Counter Low Register

Alternate Counter High Register

Alternate Counter Low Register

Input Capture2 High Register

Input Capture2 Low Register

Output Compare2 High Register

Output Compare2 Low Register

00h

00h

00h

xxh

xxh

80h

00h

FFh

FCh

FFh

FCh

xxh

xxh

80h

00h

R/W

R/W

Read Only

Read Only

Read Only

R/W

R/W

Read Only

Read Only

Read Only

Read Only

Read Only

Read Only

R/W

R/W

0040h Reserved Area (1 Byte)

11

Page 12

12/84

ST72101/ST72212/ST72213

Notes:

1. ST72212 only, reserved area for other devices.

2. ST72212 and ST72213 only, reserved otherwise.

0041h

0042h

0043h

0044h-0045h

0046h-0047h

0048h-0049h

004Ah-004Bh

004Ch-004Dh

004Eh-004Fh

Timer B

1)

TBCR2

TBCR1

TBSR

TBIC1HR

TBIC1LR

TBOC1HR

TBOC1LR

TBCHR

TBCLR

TBACHR

TBACLR

TBIC2HR

TBIC2LR

TBOC2HR

TBOC2LR

Control Register2

Control Register1

Status Register

Input Capture1 High Register

Input Capture1 Low Register

Output Compare1 High Register

Output Compare1 Low Register

Counter High Register

Counter Low Register

Alternate Counter High Register

Alternate Counter Low Register

Input Capture2 High Register

Input Capture2 Low Register

Output Compare2 High Register

Output Compare2 Low Register

00h

00h

00h

xxh

xxh

80h

00h

FFh

FCh

FFh

FCh

xxh

xxh

80h

00h

R/W

R/W

Read Only

Read Only

Read Only

R/W

R/W

Read Only

Read Only

Read Only

Read Only

Read Only

Read Only

R/W

R/W

0050h to

006Fh

Reserved Area (32 Bytes)

0070h

0071h

ADC

2)

ADCDR

ADCCSR

Data Register

Control/Status Register

00h

00h

Read Only

R/W

0072h to

007Fh

Reserved Area (14 Bytes)

Address

Block

Name

Register

Label

Register name Reset Status Remarks

12

Page 13

13/84

ST72101/ST72212/ST72213

2 CENTRAL PROCESSING UNIT

2.1 INTRODUCTION

This CPU hasa full 8-bit architecture andcontains

six internal registers allowing efficient 8-bit data

manipulation.

2.2 MAIN FEATURES

■ 63 basicinstructions

■ Fast 8-bit by 8-bit multiply

■ 17 main addressing modes (with indirect

addressing mode)

■ Two 8-bit index registers

■ 16-bit stackpointer

■ 8 MHzCPU internal frequency

■ Low power modes

■ Maskable hardware interrupts

■ Non-maskable software interrupt

2.3 CPU REGISTERS

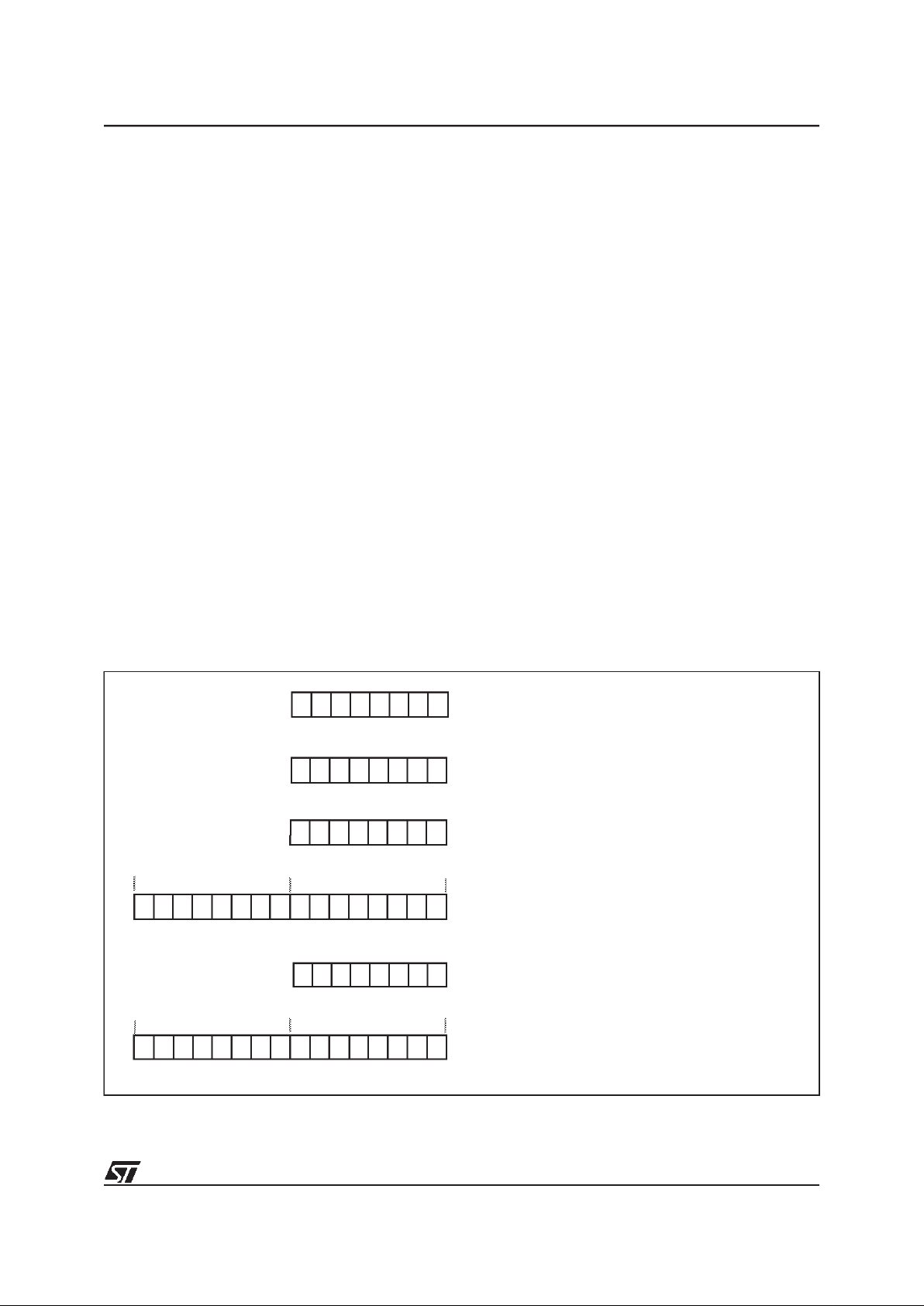

The 6 CPU registers shown in Figure 10 are not

present in thememory mapping and are accessed

by specificinstructions.

Accumulator (A)

The Accumulator is an 8-bit general purpose register used to hold operands and the results of the

arithmetic and logic calculations andto manipulate

data.

Index Registers (Xand Y)

In indexedaddressingmodes, these 8-bit registers

are used to create either effective addresses or

temporary storage areas for data manipulation.

(The Cross-Assembler generates a precede instruction (PRE) to indicate that the following instruction refers to the Y register.)

The Y register is notaffected by theinterrupt automatic procedures (notpushed toand popped from

the stack).

Program Counter (PC)

The program counteris a16-bit register containing

the address of the next instruction to be executed

by the CPU. It is made of two 8-bit registers PCL

(Program CounterLow whichis the LSB) and PCH

(Program Counter High which is the MSB).

Figure 10. CPU Registers

ACCUMULATOR

X INDEX REGISTER

Y INDEX REGISTER

STACK POINTER

CONDITION CODE REGISTER

PROGRAM COUNTER

70

1C11HINZ

RESET VALUE= RESET VECTOR @ FFFEh-FFFFh

70

70

70

0

7

15 8

PCH

PCL

15

87 0

RESET VALUE = STACKHIGHER ADDRESS

RESET VALUE =

1X11X1XX

RESET VALUE = XXh

RESET VALUE= XXh

RESET VALUE = XXh

X = Undefined Value

13

Page 14

14/84

ST72101/ST72212/ST72213

CENTRAL PROCESSING UNIT (Cont’d)

CONDITION CODE REGISTER (CC)

Read/Write

Reset Value: 111x1xxx

The 8-bit Condition Code register contains the interrupt mask and four flags representative of the

result of the instructionjust executed. This register

can also be handled by the PUSH and POP instructions.

These bits can be individually tested and/or controlled by specific instructions.

Bit 4 = H

Half carry

.

This bit isset byhardware when a carry occurs between bits 3 and 4 of the ALU during an ADD or

ADC instruction.Itis reset by hardware during the

same instructions.

0: No half carry has occurred.

1: A half carry has occurred.

This bit is tested using the JRH or JRNH instruction. The H bit is useful in BCD arithmetic subroutines.

Bit 3 = I

Interrupt mask

.

This bit is set by hardware when entering in interrupt or by software to disable all interrupts except

the TRAP software interrupt. This bit is cleared by

software.

0: Interrupts are enabled.

1: Interrupts are disabled.

This bit is controlled by the RIM, SIM and IRET instructions andis tested bythe JRM and JRNM instructions.

Note: Interrupts requested while I is set are

latched and can be processed when I is cleared.

By default an interrupt routine is not interruptable

because the I bit is set by hardware when you en-

ter it and resetby the IRET instruction at theend of

the interrupt routine. If the I bit is cleared by software inthe interrupt routine, pending interruptsare

serviced regardless of the priority levelof the current interrupt routine.

Bit 2 = N

Negative

.

This bit is set and cleared by hardware.It is representative of the result sign of the last arithmetic,

logical or data manipulation. It is a copy of the 7

th

bit of the result.

0:Theresult of the last operation is positiveor null.

1: The result of the last operation is negative

(i.e. the most significant bit is a logic 1).

This bit isaccessed by the JRMIand JRPL instructions.

Bit 1 = Z

Zero

.

This bit is set and clearedby hardware. Thisbit indicates that the result of the last arithmetic, logical

or data manipulation is zero.

0: The result of the last operation is different from

zero.

1: The result of the last operation is zero.

This bit is accessed by the JREQ and JRNE test

instructions.

Bit 0 = C

Carry/borrow.

This bit is set and cleared by hardware and software. It indicates an overflow or anunderflow has

occurred during the last arithmetic operation.

0: No overflowor underflow has occurred.

1: An overflow or underflow has occurred.

This bit is driven by the SCFand RCF instructions

and tested by theJRC andJRNC instructions.It is

also affected by the“bit test and branch”, shift and

rotate instructions.

70

111HINZC

14

Page 15

15/84

ST72101/ST72212/ST72213

CENTRAL PROCESSING UNIT (Cont’d)

Stack Pointer (SP)

Read/Write

Reset Value: 01 7Fh

The Stack Pointer is a 16-bit register which is always pointingto the next free location in the stack.

It isthen decremented after datahas been pushed

onto the stack and incremented before data is

popped from the stack (see Figure 11).

Since the stack is 64 bytes deep, the 10 most significant bits are forced by hardware. Following an

MCU Reset, or after a Reset Stack Pointer instruction (RSP), the Stack Pointer contains its reset value (the SP5 to SP0 bits are set) which is the stack

higher address.

The least significant byte of the Stack Pointer

(called S) can be directly accessed by a LD instruction.

Note: When the lower limit is exceeded, the Stack

Pointer wraps around tothe stackupper limit, without indicating the stack overflow. The previously

stored information is then overwritten and therefore lost.The stackalso wrapsin caseof anunderflow.

The stack is used to save the return address during a subroutine call and the CPU context during

an interrupt.Theuser may also directly manipulate

the stack by means of the PUSH and POP instructions. In the case ofan interrupt, the PCLis stored

at the first location pointed to by the SP. Then the

other registers are stored in the next locations as

shown in Figure 11.

– Whenan interrupt isreceived, the SP is decre-

mented and the context is pushed on the stack.

– Onreturn from interrupt, the SP is incremented

and thecontext is popped from the stack.

A subroutine call occupies twolocations and aninterrupt five locations in the stack area.

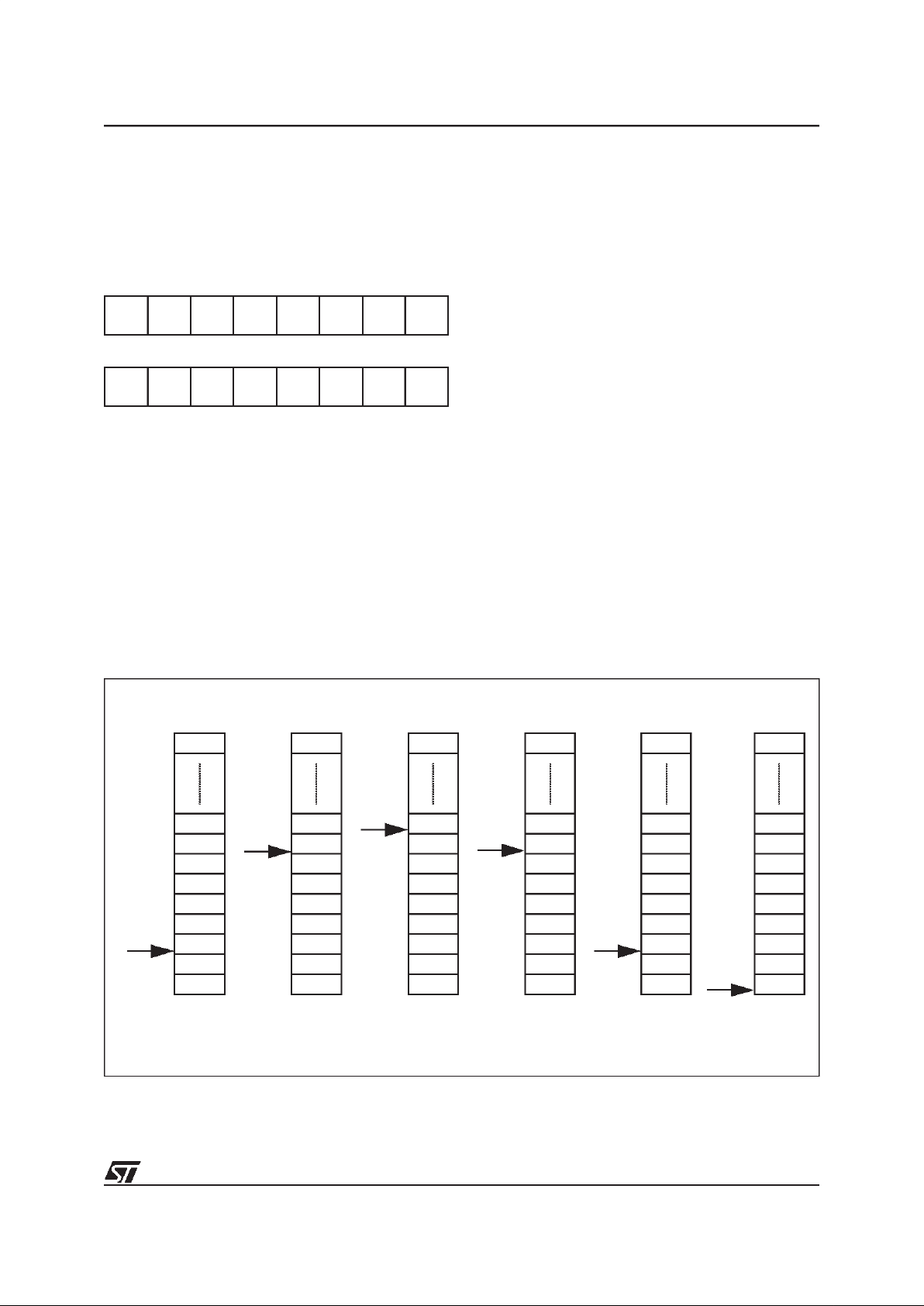

Figure 11. Stack Manipulation Example

15 8

00000001

70

0 1 SP5 SP4 SP3 SP2 SP1 SP0

PCH

PCL

SP

PCH

PCL

SP

PCL

PCH

X

A

CC

PCH

PCL

SP

PCL

PCH

X

A

CC

PCH

PCL

SP

PCL

PCH

X

A

CC

PCH

PCL

SP

SP

Y

CALL

Subroutine

Interrupt

Event

PUSH Y POP Y IRET

RET

or RSP

@ 017Fh

@ 0140h

Stack Lower Address = 0140h

Stack Higher Address =

017Fh

15

Page 16

16/84

ST72101/ST72212/ST72213

3 CLOCKS, RESET, INTERRUPTS & POWER SAVING MODES

3.1 CLOCK SYSTEM

3.1.1 General Description

The MCU accepts either a Crystal or Ceramicresonator, or an external clock signal to drive the internal oscillator. The internal clock (f

CPU

) is de-

rived fromthe external oscillator frequency (f

OSC).

The external Oscillator clock is first divided by 2,

and division factor of 32 can be applied if Slow

Mode is selected by settingthe SMS bit in the Miscellaneous Register. This reduces the frequency

of the f

CPU

; the clock signal is also routed to the

on-chip peripherals.

The internal oscillator is designed to operate with

an AT-cut parallel resonant quartz crystal resonator in the frequency range specified for f

osc

.The

circuit shown in Figure 13 is recommended when

using a crystal, and Table 6 lists the recommended capacitance and feedback resistance values.

The crystal and associated componentsshould be

mounted as close as possible to the input pins in

order to minimize output distortion and start-up

stabilisation time.

Use of an external CMOS oscillator is recommended when crystals outside the specified frequency ranges are to be used.

Table 6. Recommended Values for 16 MHz

Crystal Resonator (C0<7pF)

C0: parasitic shunt capacitance of the quartz crys-

tal.

R

SMAX

: equivalent serialresistor of the crystal (up-

er limit, see crystal specification).

C

OSCOUT,COSCIN

: maximum total capacitance on

OSCIN and OSCOUT, including the external capacitance plus the parasitic capacitance of the

board and the device.

Figure 12. External Clock Source Connections

Figure 13. Crystal/CeramicResonator

Figure 14. Clock Prescaler Block Diagram

R

SMAX

40 Ω 60 Ω 150 Ω

C

OSCIN

56pF 47pF 22pF

C

OSCOUT

56pF 47pF 22pF

OSCIN OSCOUT

EXTERNAL

CLOCK

NC

OSCIN OSCOUT

C

OSCIN

C

OSCOUT

OSCIN

OSCOUT

C

OSCIN

C

OSCOUT

%2 % 16

f

CPU

to CPU and

Peripherals

16

Page 17

17/84

ST72101/ST72212/ST72213

3.2 RESET

3.2.1 Introduction

There are three sources of Reset:

– RESET pin (externalsource)

– Power-On Reset (Internal source)

– WATCHDOG (Internal Source)

The Reset Service Routine vectoris located at ad-

dress FFFEh-FFFFh.

3.2.2 External Reset

The RESET pin is both an input and an open-drain

output with integrated pull-up resistor. When one

of the internal Reset sources is active, the Reset

pin is driven low , for a duration of t

RESET,

to reset

the whole application.

3.2.3 Reset Operation

The duration of the Reset state is a minimum of

4096 internal CPU Clock cycles. During the Reset

state, all I/Os take their reset value.

A Reset signal originating from an externalsource

must have a duration of at least t

PULSE

in order to

be recognised. This detection is asynchronous

and therefore the MCU can enter Reset state even

in Halt mode.

At the end of the Reset cycle, the MCU may be

held in the Reset state by an External Reset signal. The RESET pin may thus be used to ensure

VDDhas risen to a point where theMCU can operate correctly before the user program is run. Fol-

lowing a Reset event, or after exiting Halt mode, a

4096 CPU Clock cycle delay period is initiated in

order to allow the oscillator to stabilise and to ensure that recovery hastaken place from the Reset

state.

In the high state, the RESET pin is connected internally to a pull-up resistor (RON). This resistor

can be pulled low by external circuitry to reset the

device.

The RESET pin is an asynchronous signal which

plays a majorrole in EMS performance. In a noisy

environment, it is recommended to use the external connections shown in Figure8.

3.2.4 Power-on Reset

This circuit detects the ramping up of VDD, and

generates a pulse that is used to reset the application (at approximately VDD= 2V).

Power-On Reset is designed exclusively to cope

with power-up conditions, and should not be used

in order to attempt to detect a drop in the power

supply voltage.

Caution:

to re-initialize the Power-On Reset, the

power supply must fall below approximately 0.8V

(Vtn), prior to rising above 2V. If this condition is

not respected, on subsequent power-upthe Reset

pulse may not be generated. An external Reset

pulse may be required to correctly reactivate the

circuit.

Figure 15. Reset Block Diagram

INTERNAL

RESET

WATCHDOG RESET

OSCILLATOR

SIGNAL

COUNTER

RESET

TO ST7

RESET

POWER-ON RESET

V

DD

R

ON

17

Page 18

18/84

ST72101/ST72212/ST72213

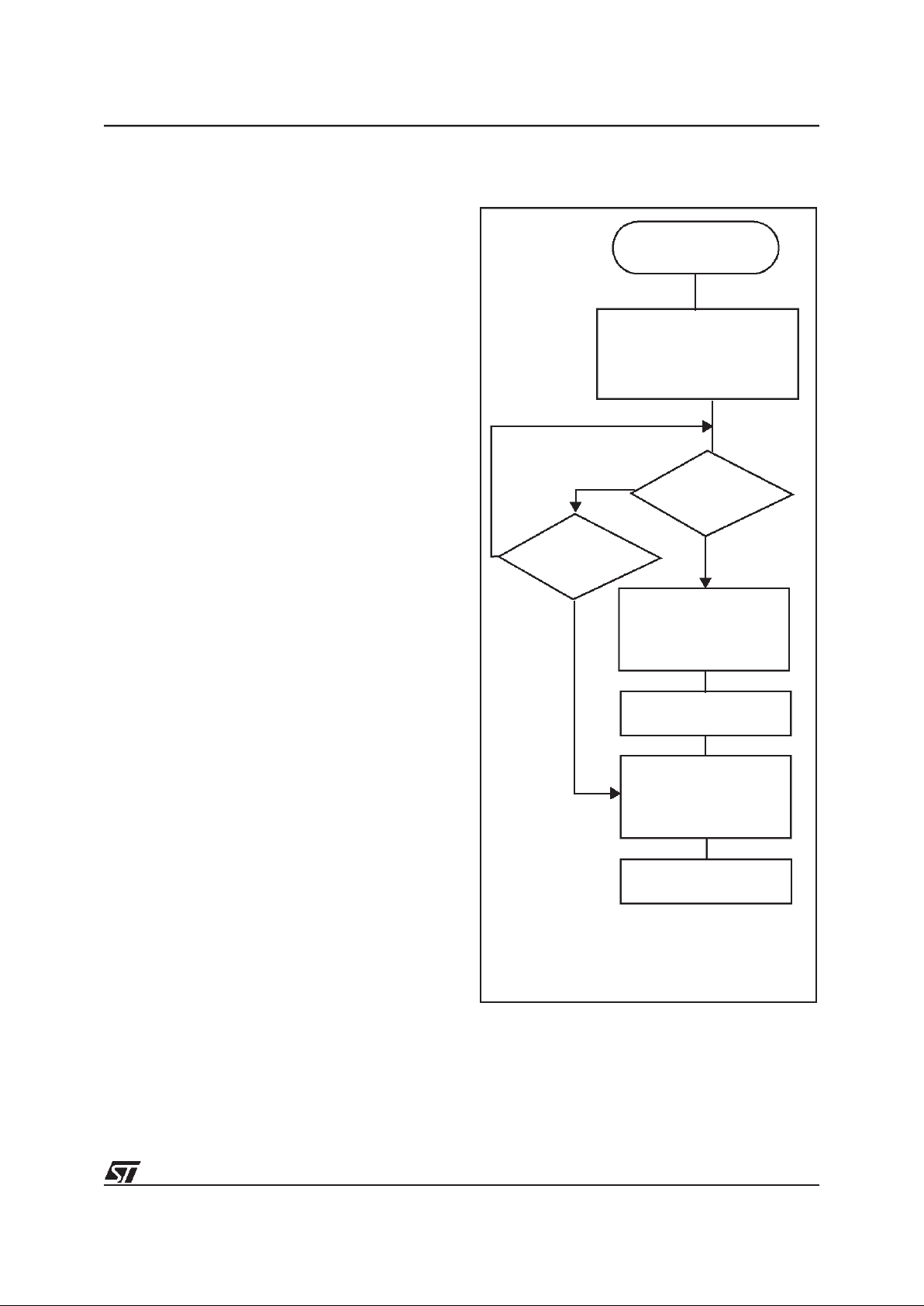

3.3 INTERRUPTS

The ST7 coremaybe interruptedby one of two different methods: maskable hardware interrupts as

listed in the Interrupt Mapping Table and a nonmaskable software interrupt (TRAP). The Interrupt

processing flowchartis shown in Figure16.

The maskable interrupts mustbe enabled clearing

the I bitin order to be serviced. However, disabled

interrupts may be latched and processed when

they are enabled (see external interrupts subsection).

When an interrupt has to be serviced:

– Normal processing is suspended at the end of

the current instruction execution.

– The PC, X, A and CC registersare saved onto

the stack.

– The I bit of the CC register is set to prevent addi-

tional interrupts.

– ThePC is thenloaded with theinterrupt vector of

the interrupt to service and the first instructionof

the interrupt serviceroutine is fetched(refer to

the Interrupt Mapping Table for vector addresses).

The interrupt service routine should finish with the

IRET instruction which causes the contents of the

saved registersto be recovered from thestack.

Note: As a consequence of the IRET instruction,

the I bit will be cleared and the main program will

resume.

Priority management

By default, a servicing interrupt can not be interrupted because the I bit is set by hardware entering in interrupt routine.

In the case several interrupts are simultaneously

pending, an hardware priority defines which one

will be serviced first (seethe Interrupt Mapping Table).

Non Maskable Software Interrupts

This interrupt is entered when the TRAP instruction is executed regardless of the state of theI bit.

It will be serviced according to the flowchart on

Figure 16.

Interrupts and Low power mode

All interrupts allowthe processorto leave the Wait

low power mode. Only external and specific mentioned interrupts allow the processor to leave the

Halt low power mode(referto the “Exit from HALT“

column in the Interrupt Mapping Table).

External Interrupts

External interrupt vectorscan be loaded in the PC

register if the corresponding external interrupt occurred and if the I bit is cleared. These interrupts

allow the processor to leave the Halt low power

mode.

The external interrupt polarity is selected through

the miscellaneous register or interrupt register (if

available).

External interrupt triggered on edge will be latched

and the interrupt request automatically cleared

upon entering the interrupt service routine.

If several input pins, connected to the same interrupt vector, are configured as interrupts, their signals are logically ANDed before entering theedge/

level detection block.

Warning: The type of sensitivity defined in the

Miscellaneous or Interrupt register (if available)

applies to the EI source. In case of an ANDed

source (as described on the I/O ports section), a

low level on an I/O pin configured as input with interrupt, masks the interrupt request even in case

of rising-edge sensitivity.

Peripheral Interrupts

Different peripheral interrupt flags in the status

register are able to cause an interrupt when they

are active if both:

– TheI bit of the CC register is cleared.

– Thecorresponding enablebit is set in thecontrol

register.

If any of these two conditions is false, theinterrupt

is latched and thus remains pending.

Clearing an interrupt request is done by:

– writing “0” to the corresponding bit in the status

register or

– anaccess to the status register while the flag is

set followed bya read or write of anassociated

register.

Note: the clearing sequence resets the internal

latch. A pending interrupt (i.e. waiting for being enabled) will therefore be lost ifthe clear sequence is

executed.

18

Page 19

19/84

ST72101/ST72212/ST72213

INTERRUPTS (Cont’d)

Figure 16. Interrupt Processing Flowchart

BIT I SET

Y

N

IRET

Y

N

FROM RESET

LOAD PC FROM INTERRUPT VECTOR

STACK PC, X, A, CC

SET I BIT

FETCH NEXT INSTRUCTION

EXECUTE INSTRUCTION

THIS CLEARS I BIT BY DEFAULT

RESTORE PC, X, A,CC FROM STACK

BIT I SET

Y

N

19

Page 20

20/84

ST72101/ST72212/ST72213

Table 7. Interrupt Mapping

Note 1: Timer B is available on ST72212 only.

Source

Block

Description

Register

Label

Flag

Exit

from

HALT

Vector

Address

Priority

Order

RESET Reset N/A N/A yes FFFEh-FFFFh

TRAP Software N/A N/A no FFFCh-FFFDh

EI0 External Interrupt PA0:PA7 N/A N/A yes FFFAh-FFFBh

EI1 External Interrupt PB0:PB7, PC0:PC5 N/A N/A yes FFF8h-FFF9h

Not Used FFF6h-FFF7h

SPI

Transfer Complete

SPISR

SPIF

no FFF4h-FFF5h

Mode Fault MODF

TIMER A

Input Capture 1

TASR

ICF1_A

no FFF2h-FFF3h

Output Compare 1 OCF1_A

Input Capture 2 ICF2_A

Output Compare 2 OCF2_A

Timer Overflow TOF_A

Not Used FFF0h-FFF1h

TIMER B

1)

Input Capture 1

TBSR

ICF1_B

no FFEEh-FFEFh

Output Compare 1 OCF1_B

Input Capture 2 ICF2_B

Output Compare 2 OCF2_B

Timer Overflow TOF_B

Not Used

FFECh-FFEDh

FFEAh-FFEBh

FFE8h-FFE9h

FFE6h-FFE7h

FFE4h-FFE5h

FFE2h-FFE3h

FFE0h-FFE1h

Highest

Priority

Priority

Lowest

20

Page 21

21/84

ST72101/ST72212/ST72213

3.4 POWER SAVING MODES

3.4.1 Introduction

There are threePower Saving modes. SlowMode

is selected by setting the relevant bits in the Miscellaneous register. Wait and Halt modes may be

entered usingthe WFI and HALT instructions.

3.4.2 Slow Mode

In Slow mode, the oscillator frequency can be divided by a value defined in the Miscellaneous

Register. The CPU and peripherals are clocked at

this lower frequency. Slow mode isused to reduce

power consumption, andenables the user to adapt

clock frequencyto available supply voltage.

3.4.3 Wait Mode

Wait mode places the MCU in a low power consumption mode by stoppingthe CPU. Allperipherals remain active. During Wait mode, the I bit (CC

Register) is cleared, so as to enable all interrupts.

All otherregisters and memory remain unchanged.

The MCU will remain in Wait mode until an Interrupt or Reset occurs, whereupon the Program

Counter branches to the starting address of the Interrupt orReset Service Routine.

The MCU will remain in Wait mode until a Reset or

an Interrupt occurs, causing it to wake up.

Refer to Figure 17 below.

Figure 17. WAIT Flow Chart

WFI INSTRUCTION

RESET

INTERRUPT

Y

N

N

Y

CPU CLOCK

OSCILLATOR

PERIPH. CLOCK

I-BIT

ON

ON

CLEARED

OFF

Note: Before servicing an interrupt, the CC register is

pushed on the stack. The I-Bit is set during the interrupt routine and cleared when the CC register is

popped.

4096 CPU CLOCK

FETCH RESET VECTOR

OR SERVICE INTERRUPT

CYCLES DELAY

CPU CLOCK

OSCILLATOR

PERIPH. CLOCK

I-BIT

ON

ON

SET

ON

CPU CLOCK

OSCILLATOR

PERIPH. CLOCK

I-BIT

ON

ON

SET

ON

21

Page 22

22/84

ST72101/ST72212/ST72213

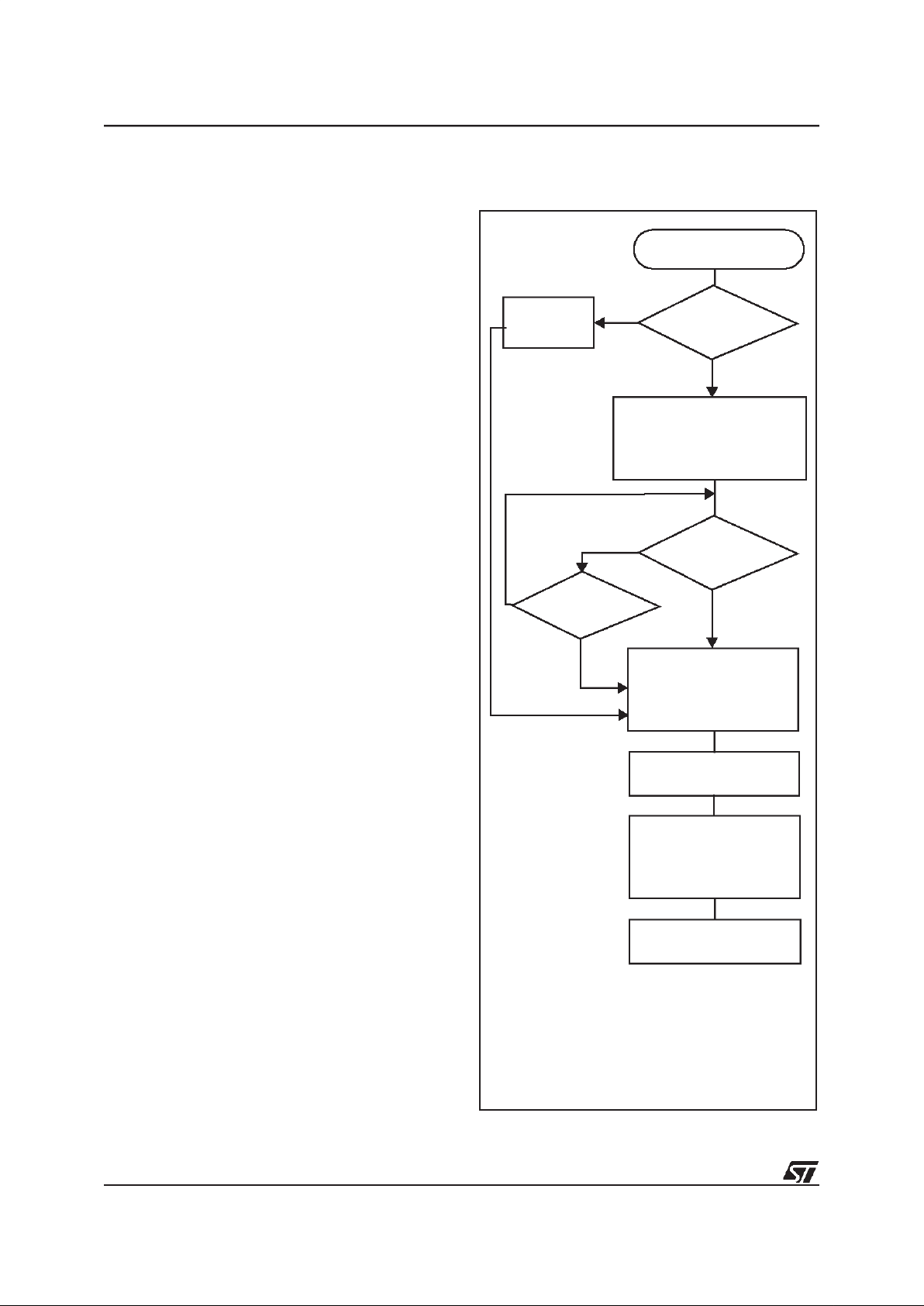

POWER SAVINGMODES (Cont’d)

3.4.4 Halt Mode

The Halt mode is the MCU lowest power consumption mode. The Halt mode is entered byexecuting theHALT instruction. The internal oscillator

is then turnedoff, causing allinternal processing to

be stopped, including the operation of the on-chip

peripherals. The Halt mode cannot be used when

the watchdog isenabled, ifthe HALT instruction is

executed while the watchdog system is enabled,a

watchdog reset is generatedthus resetting the entire MCU.

When entering Halt mode, the Ibit in the CC Register is clearedso as toenable ExternalInterrupts.

If an interrupt occurs, the CPU becomes active.

The MCU canexit theHalt mode upon reception of

an interrupt or a reset. Refer to the Interrupt Mapping Table. The oscillator is then turned on and a

stabilization time is provided beforereleasing CPU

operation. Thestabilization timeis 4096 CPU clock

cycles.

After the start up delay, the CPU continuesoperation byservicingthe interrupt whichwakes it up or

by fetching the reset vector if a reset wakes it up.

Figure 18. HALT Flow Chart

N

N

EXTERNAL

INTERRUPT

1)

RESET

HALT INSTRUCTION

4096 CPU CLOCK

FETCH RESET VECTOR

OR SERVICE INTERRUPT

CYCLES DELAY

CPU CLOCK

OSCILLATOR

PERIPH. CLOCK

2)

I-BIT

ON

OFF

SET

ON

CPU CLOCK

OSCILLATOR

PERIPH. CLOCK

I-BIT

OFF

OFF

CLEARED

OFF

Y

Y

WDG

ENABLED?

N

Y

RESET

WATCHDOG

1) or some specific interrupts

Note: Before servicing an interrupt, the CC register is

pushed on the stack. The I-Bit is set during the interrupt routine and cleared when the CC register is

popped.

CPU CLOCK

OSCILLATOR

PERIPH. CLOCK

I-BIT

ON

ON

SET

ON

2) if reset PERIPH. CLOCK = ON ;if interrupt

PERIPH. CLOCK = OFF

22

Page 23

23/84

ST72101/ST72212/ST72213

3.5 MISCELLANEOUS REGISTER

The Miscellaneous register allows to select the

SLOW operatingmode, the polarity of external interrupt requestsand to output the internal clock.

Register Address:0020h — Read/Write

Reset Value: 0000 0000 (00h)

Bit 7:6 = PEI[3:2]

External Interrupt EI1 Polarity

Option

.

These bits are set and cleared by software. They

determine which event on EI1 causes the external interrupt according to Table 8.

Table 8. EI1 External Interrupt Polarity Options

Note: Any modification of one of these twobits re-

sets the interrupt request related to this interrupt

vector.

Bit 5 = MCO

Main Clock Out

This bit isset andcleared by software. When set, it

enables the output of the Internal Clock on the

PC2 I/Oport.

0 -PC2 is a general purpose I/O port.

1 -MCO alternate function (f

CPU

is output on PC2

pin).

Bit 4:3 = PEI[1:0]

External Interrupt EI0 Polarity

Option

.

These bits are set and cleared by software. They

determine which event on EI0 causes the external interrupt according to Table 9.

Table 9. EI0 External Interrupt Polarity Options

Note: Any modification of oneof these two bits re-

sets the interrupt request related to this interrupt

vector.

Bit 1:2 = Unused, always read at 0.

Warning:

Software must write 1 to these bits for

compatibility with future products.

Bit 0 = SMS

Slow Mode Select

This bit is set andcleared by software.

0- Normal mode - f

CPU

= Oscillator frequency / 2

(Reset state)

1- Slow mode - f

CPU

= Oscillatorfrequency /32

70

PEI3 PEI2 MCO PEI1 PEI0 - - SMS

MODE PEI3 PEI2

Falling edge and low level

(Reset state)

00

Falling edge only 1 0

Rising edge only 0 1

Rising and falling edge 1 1

MODE PEI1 PEI0

Falling edge and low level

(Reset state)

00

Falling edge only 1 0

Rising edge only 0 1

Rising and falling edge 1 1

23

Page 24

24/84

ST72101/ST72212/ST72213

4 ON-CHIP PERIPHERALS

4.1 I/O PORTS

4.1.1 Introduction

The I/O ports offer different functional modes:

– transferof data through digital inputsand outputs

and forspecific pins:

– analog signal input (ADC)

– alternate signal input/output for the on-chip pe-

ripherals.

– external interrupt generation

An I/O port is composed of up to 8 pins. Each pin

can be programmedindependently as digital input

(with or without interrupt generation) or digital output.

4.1.2 Functional Description

Each portis associated to 2 main registers:

– Data Register (DR)

– Data Direction Register (DDR)

and someof them to an optional register:

– Option Register (OR)

Each I/Opin may beprogrammed using thecorre-

sponding register bits inDDR and ORregisters: bit

X corresponding to pin Xof the port.The same correspondence is used for the DR register.

The following description takes into account the

OR register, for specific ports whichdo not provide

this register refer to the I/O Port Implementation

Section 4.1.3. The generic I/O block diagram is

shown onFigure 20.

4.1.2.1 Input Modes

The input configuration isselected by clearing the

corresponding DDRregister bit.

In this case, reading the DR register returns the

digital value applied to the external I/O pin.

Different input modes can beselected by software

through theOR register.

Notes:

1. All the inputs are triggered by a Schmitt trigger.

2. When switching from input mode to output

mode, the DR register should be written first to

output the correct value as soon as the port is configured as an output.

Interrupt function

When an I/O is configured in Input with Interrupt,

an event on this I/O can generate an external Interrupt request to the CPU. Theinterrupt polarity is

given independently according to the description

mentioned in the Miscellaneous register or in the

interrupt register (where available).

Each pin can independently generate an Interrupt

request.

Each external interrupt vector is linked to a dedicated group of I/O port pins (see Interrupts section). If several input pins are configured as inputs

to the same interrupt vector, their signals are logically ANDed before entering the edge/level detection block. For this reason if one of the interrupt

pins is tied low, it masks the other ones.

4.1.2.2 Output Mode

The pin is configured in output mode bysetting the

corresponding DDR registerbit.

In this mode, writing “0” or “1” to the DR register

applies this digital value to the I/O pin through the

latch. Then reading the DR register returns the

previously stored value.

Note: In this mode, the interrupt function is disabled.

4.1.2.3 Digital Alternate Function

When an on-chipperipheral is configured to use a

pin, the alternate function is automatically selected. This alternate function takes priority over

standard I/O programming. When the signal is

coming from an on-chip peripheral, the I/O pin is

automatically configuredin output mode (push-pull

or open drain according to theperipheral).

When the signal is going to an on-chip peripheral,

the I/O pin has to be configured ininput mode. In

this case, the pin’s state is also digitally readable

by addressing the DR register.

Notes:

1. Input pull-up configuration can cause an unexpected value atthe input of the alternate peripheral input.

2. When the on-chip peripheral uses apin asinput

and output, this pin must be configured as an input

(DDR = 0).

Warning

: The alternate function must not be acti-

vated as long as the pin isconfigured as inputwith

interrupt, in order to avoid generating spurious interrupts.

24

Page 25

25/84

ST72101/ST72212/ST72213

I/O PORTS (Cont’d)

4.1.2.4 Analog Alternate Function

When the pin isused asan ADC input theI/O must

be configured as input, floating. The analog multiplexer (controlled by the ADC registers) switches

the analog voltage present on the selected pin to

the common analog rail which is connected to the

ADC input.

It isrecommended not to change the voltage level

or loading on any port pin while conversion is in

progress. Furthermore it is recommended not to

have clocking pins located close to a selected analog pin.

Warning

: The analog input voltage level must be

within the limits stated in the Absolute Maximum

Ratings.

4.1.3 I/O Port Implementation

The hardware implementation oneach I/O port depends on the settingsin theDDR andOR registers

and specific feature ofthe I/O portsuch as ADCInput (see Figure 20) or true open drain. Switching

these I/O ports from one state to another should

be done in a sequence that prevents unwanted

side effects. Recommended safetransitions areillustrated in Figure 19. Other transitions are potentially risky and should be avoided, since they are

likely to present unwanted side-effects such as

spurious interrupt generation.

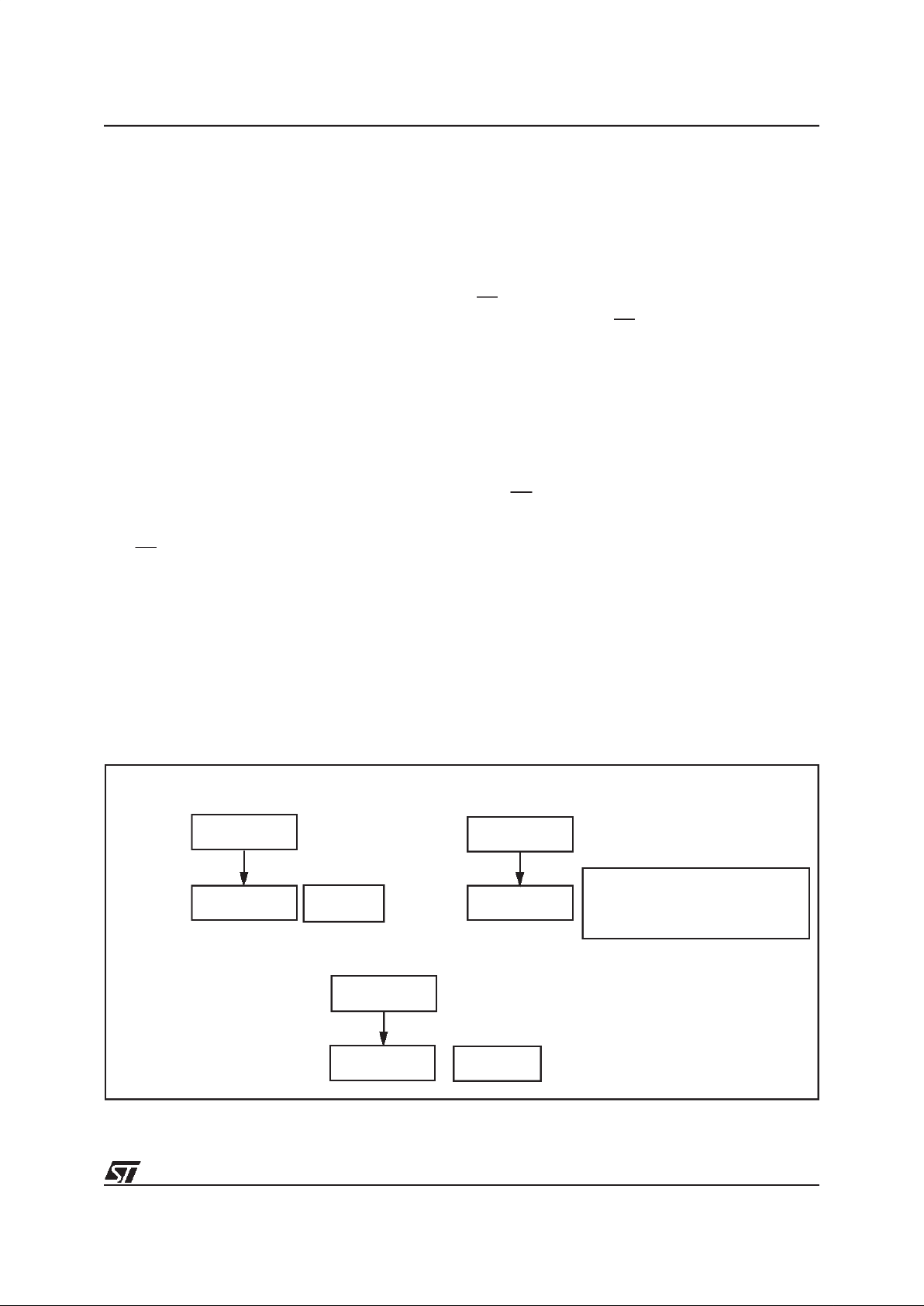

Figure 19. Recommended I/O State Transition Diagram

with interrupt

INPUT

OUTPUT

no interrupt

INPUT

push-pullopen-drain

OUTPUT

25

Page 26

26/84

ST72101/ST72212/ST72213

I/O PORTS (Cont’d)

Figure 20. I/O BlockDiagram

Table 10. Port Mode Configuration

Legend:

0 - present, not activated

1 - present and activated

Notes:

– No OR Register on some ports (see register map).

– ADC Switch on ports with analog alternate functions.

DR

DDR

LATCH

LATCH

DATA BUS

DR SEL

DDR SEL

V

DD

PAD

ANALOG

SWITCH

ANALOG ENABLE

(ADC)

M

U

X

ALTERNATE

ALTERNATE

ALTERNATE ENABLE

COMMON ANALOG RAIL

ALTERNATE

M

U

X

ALTERNATE INPUT

PULL-UP

OUTPUT

P-BUFFER

(S

EE TABLE BELOW)

N-BUFFER

1

0

1

0

OR

LATCH

ORSEL

FROM

OTHER

BITS

EXTERNAL

PULL-UP

CONDITION

ENABLE

ENABLE

GND

(S

EE TABLE BELOW)

(S

EE NOTE BELOW)

CMOS

SCHMITT TRIGGER

SOURCE (EIx)

INTERRUPT

POLARITY

SEL

GND

V

DD

DIODE

(SEE TABLEBELOW)

Configuration Mode Pull-up P-buffer V

DD

Diode

Floating 0 0 1

Pull-up 1 0 1

Push-pull 0 1 1

True Open Drain not present not present

not present in OTP

and EPROM devices

Open Drain (logic level) 0 0 1

26

Page 27

27/84

ST72101/ST72212/ST72213

Table 11. Port Configuration

*Reset State

Port Pin Name

Input (DDR = 0) Output (DDR = 1)

OR = 0 OR =1 OR = 0 OR = 1

Port A PA0:PA7 Floating* Floating with Interrupt

True Open Drain,

High Sink Capability

Reserved

Port B PB0:PB7 Floating* Pull-up with Interrupt Open Drain (Logic level) Push-pull

Port C PC0:PC5 Floating* Pull-up with Interrupt Open Drain (Logic level) Push-pull

27

Page 28

28/84

ST72101/ST72212/ST72213

I/O PORTS (Cont’d)

4.1.4 Register Description

4.1.4.1 Data registers

Port A Data Register (PADR)

Port B Data Register (PBDR)

Port C Data Register (PCDR)

Read/Write

Reset Value: 0000 0000 (00h)

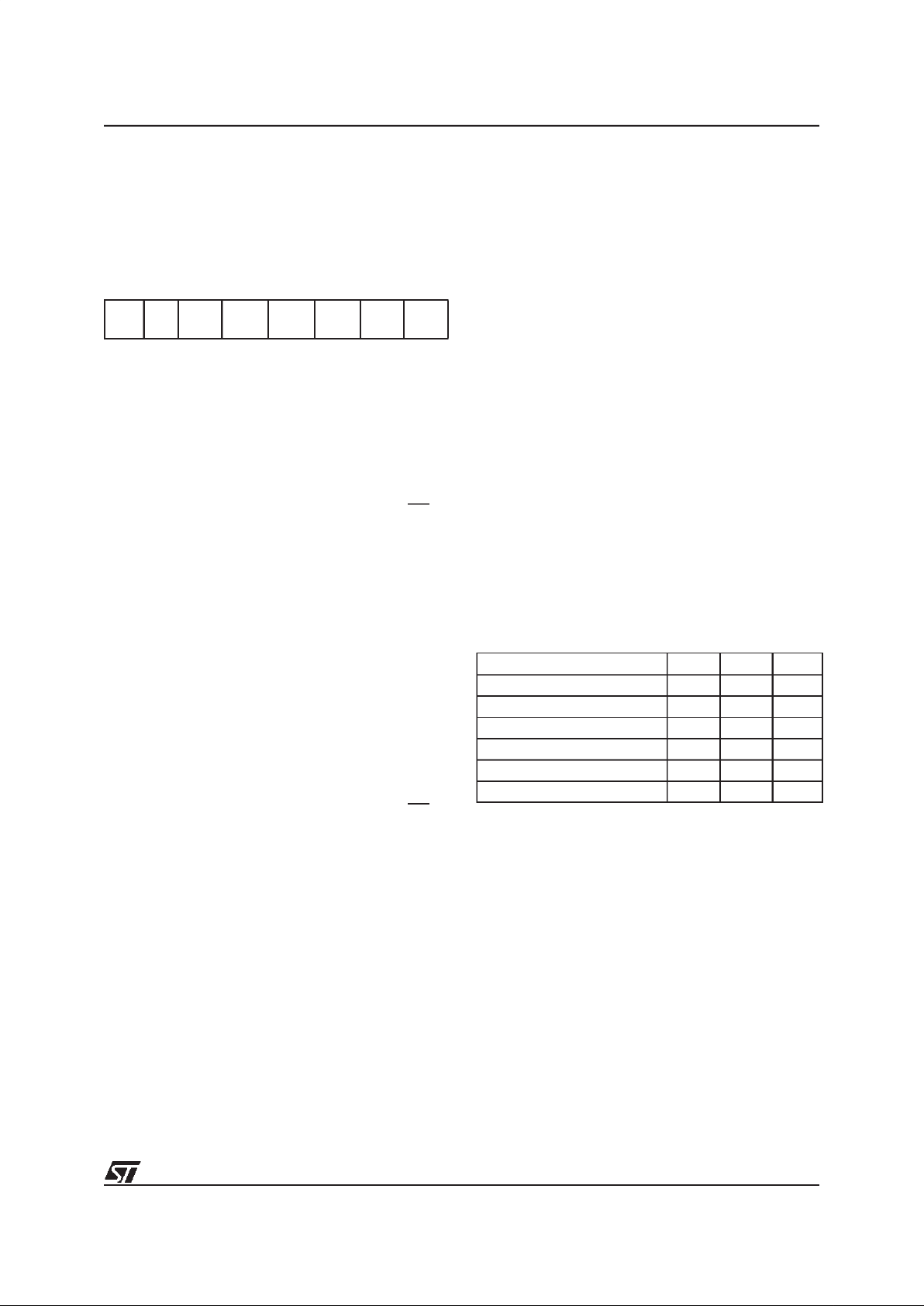

Bit 7:0 = D7-D0

Data Register 8 bits.

The DR register has a specific behaviour according to the selected input/output configuration. Writing the DR register is always taken in account

even if the pin is configured as an input. Reading

the DR register returns either theDR register latch

content (pin configuredas output) or the digital value applied to the I/O pin (pin configured as input).

4.1.4.2 Data direction registers

Port A Data Direction Register (PADDR)

Port B Data Direction Register (PBDDR)

Port C Data Direction Register (PCDDR)

Read/Write

Reset Value: 0000 0000 (00h) (input mode)

Bit 7:0 = DD7-DD0

Data Direction Register 8 bits.

The DDR register gives the input/output direction

configuration of the pins. Each bit is set and

cleared by software.

0: Input mode

1: Output mode

4.1.4.3 Option registers

Port A OptionRegister (PAOR)

Port B OptionRegister (PBOR)

Port C Option Register (PCOR)

Read/Write

Reset Value: 0000 0000 (00h) (nointerrupt)

Bit 7:0 = O7-O0

Option Register8 bits.

For specific I/O pins, thisregister is not implemented. In this case the DDR register is enough to select the I/O pin configuration.

The OR register allow to distinguish: in input mode

if the interrupt capability or the floating configuration is selected, in output mode if the push-pull or

open drain configuration is selected.

Each bit is set and clearedby software.

Input mode:

0: floating input

1: input interrupt with or without pull-up

Output mode (only for PB0:PB7, PC0:PC5):

0: output open drain (with P-Bufferinactivated)

1: output push-pull

Output mode (only for PA0:PA7):

0: output open drain

1: reserved

70

D7 D6 D5 D4 D3 D2 D1 D0

70

DD7 DD6 DD5 DD4 DD3 DD2 DD1 DD0

70

O7 O6 O5 O4 O3 O2 O1 O0

28

Page 29

29/84

ST72101/ST72212/ST72213

I/O PORTS (Cont’d)

Table 12. I/O Port RegisterMap and Reset Values

Address

(Hex.)

Register

Label

76543210

0000h

PCDR

Reset Value

D7

0

D6

0

D5

0

D4

0

D37

0

D2

0

D1

0

D0

0

0001h

PCDDR

Reset Value

DD7

0

DD6

0

DD5

0

DD4

0

DD3

0

DD2

0

DD1

0

DD0

0

0002h

PCOR

Reset Value

O7

0

O6

0

O5

0

O4

0

O3

0

O2

0

O1

0

O0

0

0004h

PBDR

Reset Value

D7

0

D6

0

D5

0

D4

0

D37

0

D2

0

D1

0

D0

0

0005h

PBDDR

Reset Value

DD7

0

DD6

0

DD5

0

DD4

0

DD3

0

DD2

0

DD1

0

DD0

0

0006h

PBOR

Reset Value

O7

0

O6

0

O5

0

O4

0

O3

0

O2

0

O1

0

O0

0

0008h

PADR

Reset Value

D7

0

D6

0

D5

0

D4

0

D37

0

D2

0

D1

0

D0

0

0009h

PADDR

Reset Value

DD7

0

DD6

0

DD5

0

DD4

0

DD3

0

DD2

0

DD1

0

DD0

0

000Ah

PAOR

Reset Value

O7

0

O6

0

O5

0

O4

0

O3

0

O2

0

O1

0

O0

0

29

Page 30

30/84

ST72101/ST72212/ST72213

4.2 WATCHDOG TIMER (WDG)

4.2.1 Introduction

The Watchdog timer is used to detect the occurrence of a software fault, usually generated by external interference or by unforeseen logical conditions, which causes the application program to

abandon its normal sequence. The Watchdog circuit generates an MCU reset on expiry of a programmed time period, unless theprogram refreshes the counter’s contents before the T6 bit becomes cleared.

4.2.2 Main Features

■ Programmable timer (64 increments of 12288

CPU cycles)

■ Programmablereset

■ Reset (if watchdog activated) after a HALT

instruction or whenthe T6 bit reaches zero

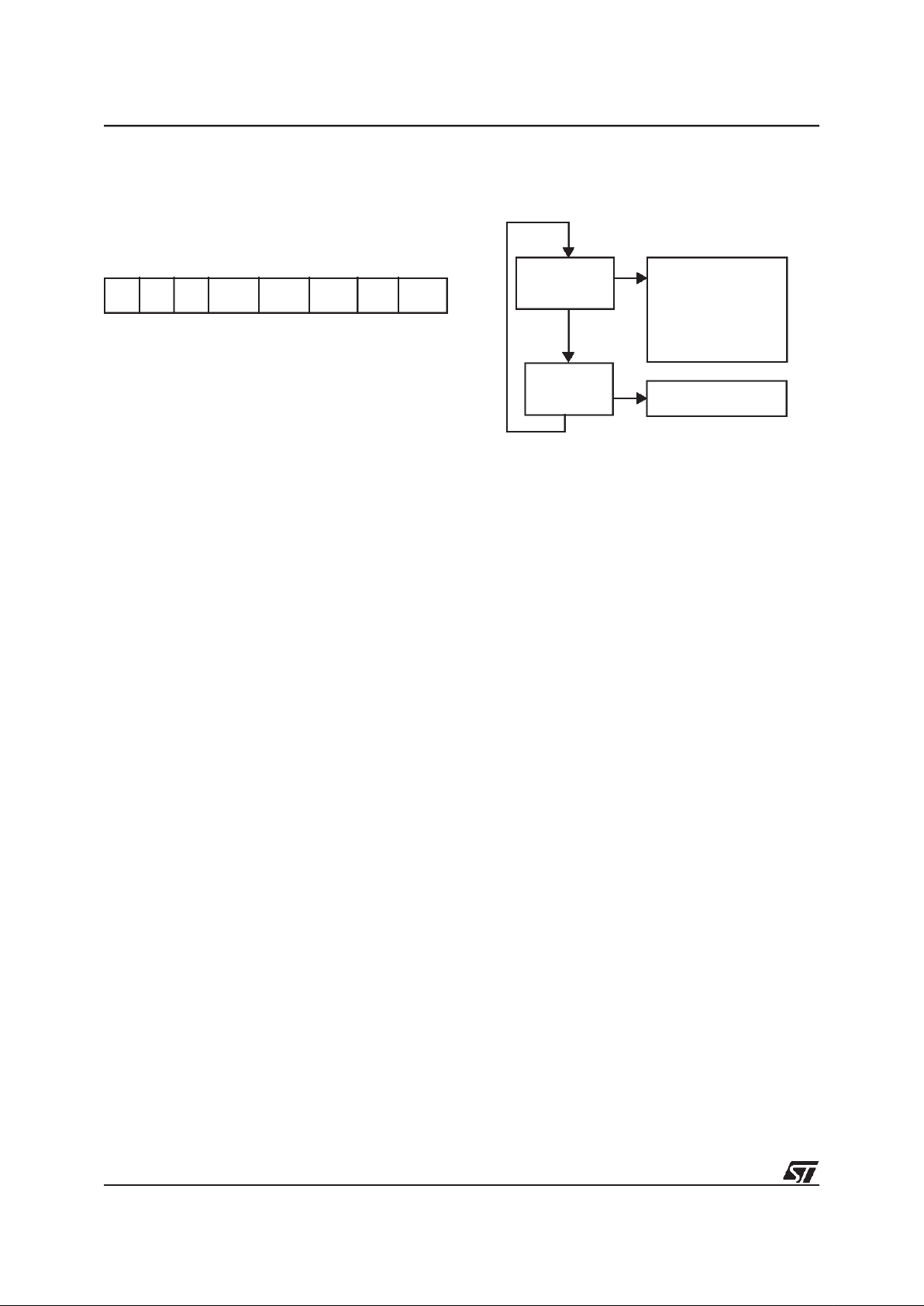

Figure 21. Watchdog Block Diagram

RESET

WDGA

7-BIT DOWNCOUNTER

f

CPU

T6 T0

CLOCK DIVIDER

WATCHDOG CONTROL REGISTER (CR)

÷12288

T1

T2

T3

T4

T5

30

Page 31

31/84

ST72101/ST72212/ST72213

WATCHDOG TIMER (Cont’d)

4.2.3 Functional Description

The counter value stored in the CR register (bits

T6:T0), is decremented every 12,288 machine cycles, and the length of the timeout period can be

programmed by the user in 64increments.

If the watchdog is activated (the WDGA bit is set)

and when the 7-bit timer (bits T6:T0) rolls over

from 40h to 3Fh (T6 becomes cleared), it initiates

a reset cycle pulling low the reset pin for typically

500ns.

The application program must write in theCR register at regular intervals during normal operation to

prevent an MCU reset. The value to be stored in

the CR register must be between FFh and C0h

(see Table 13):

– The WDGA bit is set (watchdog enabled)

– The T6 bit is set to prevent generating an imme-

diate reset

– TheT5:T0 bits containthenumber ofincrements

which represents the time delay before the

watchdog produces areset.

Table 13. Watchdog Timing (f

CPU

= 8MHz)

Notes: Following a reset, the watchdog is disa-

bled. Onceactivated it cannot be disabled, except

by areset.

The T6 bit can be used to generate a software reset (the WDGA bitis set and the T6 bit is cleared).

If the watchdog is activated, the HALT instruction

will generate a Reset.

4.2.4 Low Power Modes

4.2.5 Interrupts

None.

4.2.6 Register Description

CONTROL REGISTER (CR)

Read/Write

Reset Value: 0111 1111 (7Fh)

Bit 7 = WDGA

Activation bit

.

This bit is set by software and only cleared by

hardware after a reset. When WDGA = 1, the

watchdog can generatea reset.

0: Watchdog disabled

1: Watchdog enabled

Bit 6:0 = T[6:0]

7-bit timer (MSB to LSB).

These bits contain the decremented value. A reset

is produced when it rolls overfrom 40h to 3Fh(T6

becomes cleared).

Table 14. Watchdog Timer Register Map and Reset Values

CR Register

initial value

WDG timeout period

(ms)

Max FFh 98.304

Min C0h 1.536

Mode Description

WAIT No effect on Watchdog.

HALT

Immediate reset generation assoon as

the HALT instruction is executed ifthe

Watchdog is activated(WDGA bit is

set).

70

WDGA T6 T5 T4 T3 T2 T1 T0

Address

(Hex.)

Register

Label

76543210

0024h

WDGCR

Reset Value

WDGA

0

T6

1

T5

1

T4

1

T3

1

T2

1

T1

1

T0

1

31

Page 32

32/84

ST72101/ST72212/ST72213

4.3 16-BIT TIMER

4.3.1 Introduction

The timer consists of a 16-bit free-running counter

driven by a programmable prescaler.

It may be used for a variety of purposes, including

pulse length measurement of up to two input signals (

input capture

) orgeneration of upto two out-

put waveforms (

output compare

and

PWM

).

Pulse lengths and waveform periods can be modulated from a few microseconds to several milliseconds using the timer prescaler and the CPU

clock prescaler.

4.3.2 Main Features

■ Programmableprescaler:f

CPU

dividedby2,4or8.

■ Overflow statusflag and maskable interrupt

■ External clock input (must be at least 4 times

slower thantheCPUclockspeed)withthe choice

of activeedge

■ Output compare functions with

– 2 dedicated 16-bitregisters

– 2 dedicated programmablesignals

– 2 dedicated statusflags

– 1 dedicated maskableinterrupt

■ Input capturefunctions with

– 2 dedicated 16-bitregisters

– 2 dedicated active edge selection signals

– 2 dedicated statusflags

– 1 dedicated maskableinterrupt

■ Pulse widthmodulation mode (PWM)

■ One pulse mode

■ 5 alternatefunctionson I/Oports (ICAP1,ICAP2,

OCMP1, OCMP2, EXTCLK)*

The Block Diagram is shown in Figure 22.

*Note: Some external pins are not available on all

devices. Refer to the devicepin outdescription.

When reading an input signal which is not availa-

ble on an external pin, the value will always be ‘1’.

4.3.3 Functional Description

4.3.3.1 Counter

The principal block of the Programmable Timer is

a 16-bit free running increasing counter and itsassociated 16-bit registers:

Counter Registers

– Counter High Register (CHR) isthe most sig-

nificant byte (MSB).

– Counter Low Register (CLR) is the least sig-

nificant byte (LSB).

Alternate Counter Registers

– AlternateCounter HighRegister (ACHR) is the

most significant byte(MSB).

– AlternateCounter Low Register (ACLR) is the

least significant byte (LSB).

These two read-only 16-bit registers contain the

same value but with the differencethat reading the

ACLR register doesnot clear the TOF bit (overflow

flag), (see note at the end of paragraph titled16-bit

read sequence).

Writing in the CLRregister or ACLR register resets

the free running counter to the FFFCh value.

The timer clock depends on the clock control bits

of the CR2 register, as illustratedin Table 15. The

value in the counter register repeats every

131.072, 262.144 or 524.288 internal processorclock cycles depending on the CC1and CC0 bits.

32

Page 33

33/84

ST72101/ST72212/ST72213

16-BIT TIMER (Cont’d)

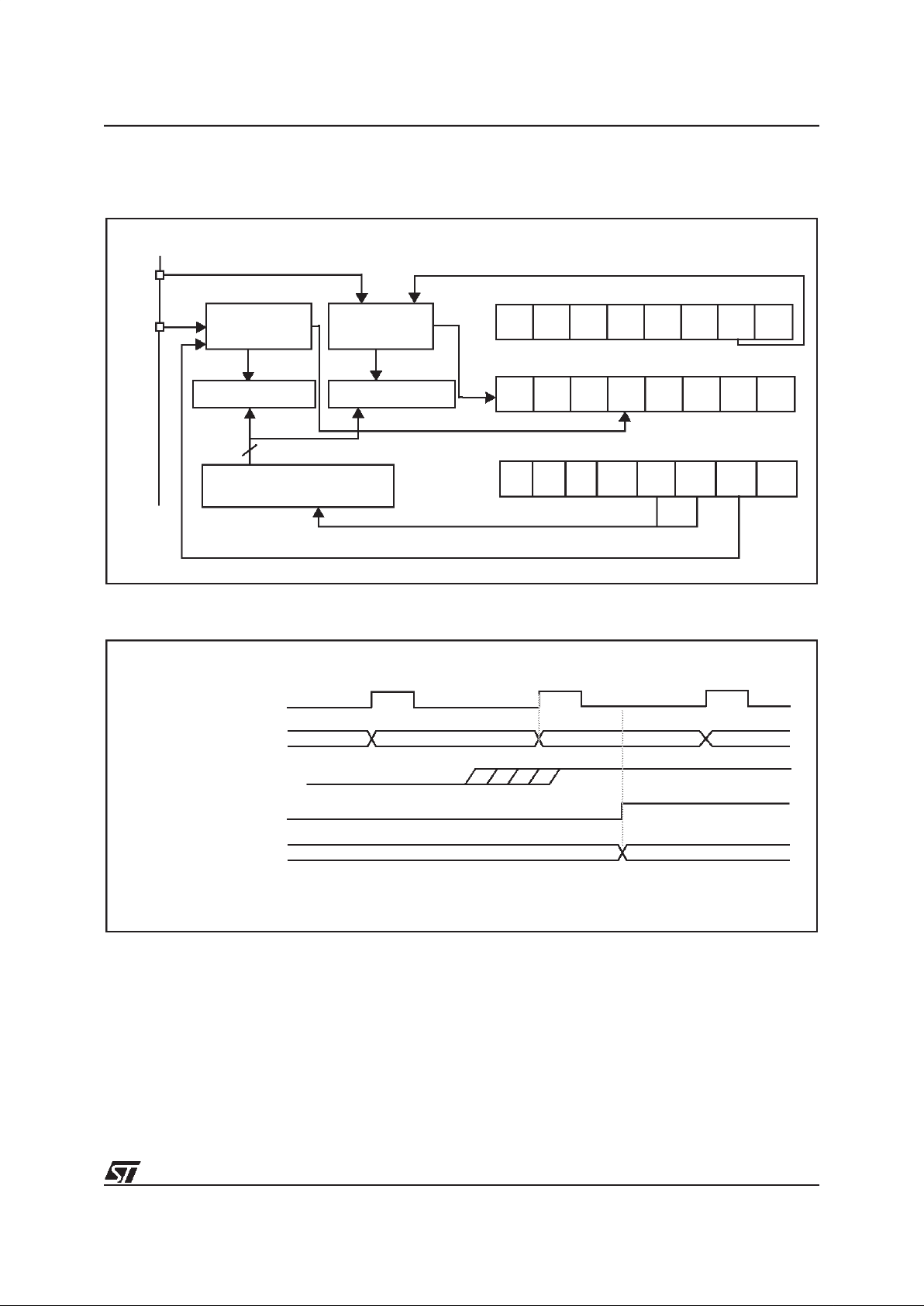

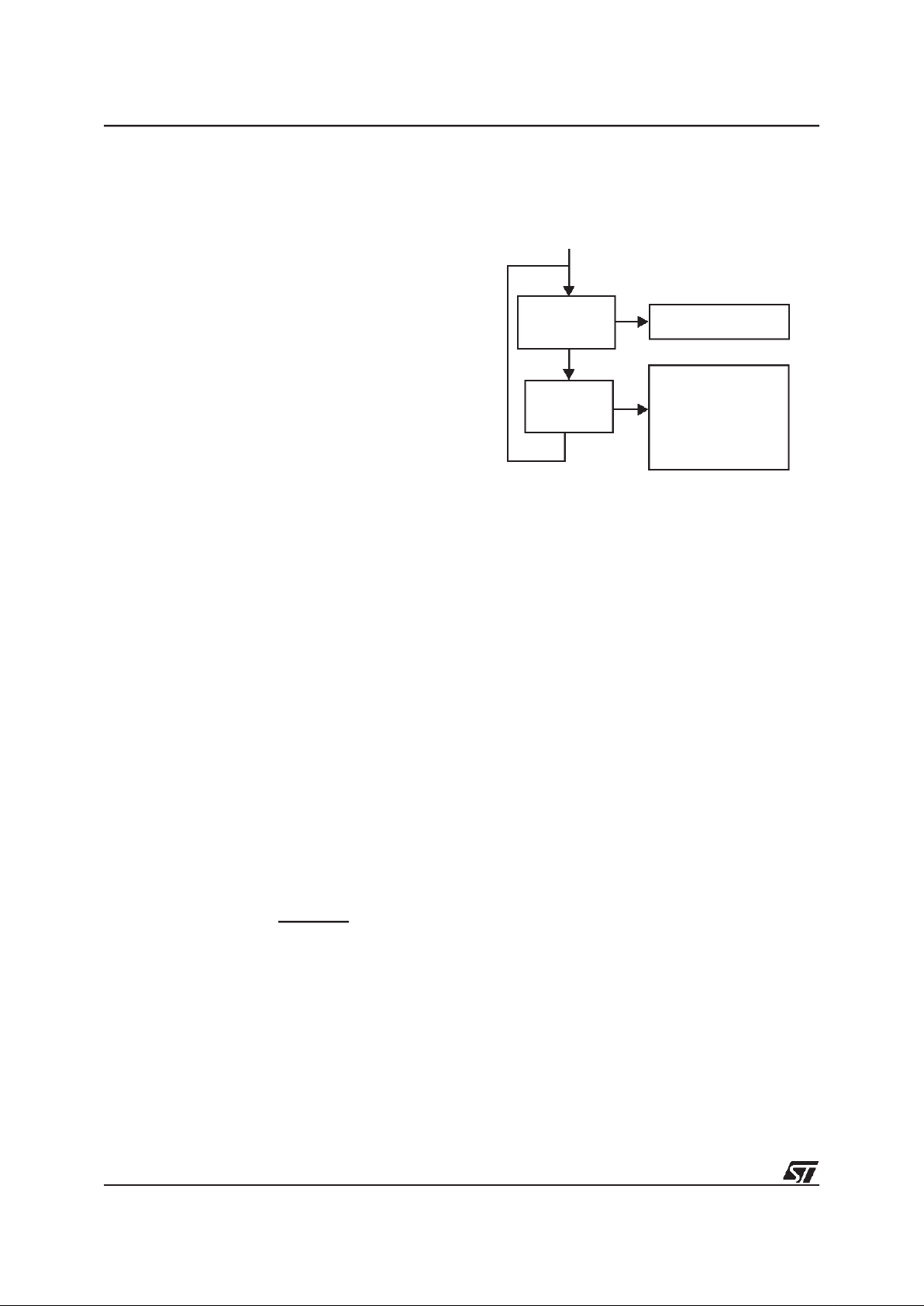

Figure 22. Timer Block Diagram

MCU-PERIPHERAL INTERFACE

COUNTER

ALTERNATE

REGISTER

OUTPUT

COMPARE

REGISTER

OUTPUT COMPARE

EDGE DETECT

OVERFLOW

DETECT

CIRCUIT

1/2

1/4

1/8

8-bit

buffer

ST7 INTERNAL BUS

LATCH1

OCMP1

ICAP1

EXTCLK

f

CPU

TIMER INTERRUPT

ICF2ICF1 000OCF2OCF1 TOF

PWMOC1E EXEDGIEDG2CC0CC1

OC2E

OPMFOLV2ICIE OLVL1IEDG1OLVL2FOLV1OCIE TOIE

ICAP2

LATCH2

OCMP2

8

8

8 low

16

8 high

16 16

16

16

CR1

CR2

SR

6

16

888

888

high

low

high

high

high

low

low

low

EXEDG

TIMER INTERNAL BUS

CIRCUIT1

EDGE DETECT

CIRCUIT2

CIRCUIT

1

OUTPUT

COMPARE

REGISTER

2

INPUT

CAPTURE

REGISTER

1

INPUT

CAPTURE

REGISTER

2

CC1 CC0

16 BIT

FREE RUNNING

COUNTER

33

Page 34

34/84

ST72101/ST72212/ST72213

16-BIT TIMER (Cont’d)

16-bit read sequence: (from either the Counter

Register orthe Alternate Counter Register).

The user must read the MSB first, then the LSB

value isbuffered automatically.

This buffered value remains unchanged until the

16-bit read sequence is completed, even if the

user readsthe MSB several times.

After a complete reading sequence, if only the

CLR register or ACLR register are read, they return the LSB of the count value at the time of the

read.

Whatever the timer mode used (input capture, output compare, one pulse mode or PWM mode) an

overflow occurs when the counter rolls over from

FFFFh to0000h then:

– The TOF bitof the SRregister is set.

– A timer interrupt is generated if:

– TOIE bit of the CR1 registeris set and

– I bit ofthe CC register is cleared.

If one of these conditions is false, the interrupt remains pending to be issued as soon as they are

both true.

Clearing the overflow interrupt request is done in

two steps:

1.Reading theSR registerwhile the TOF bit isset.

2.An access (read or write) to the CLR register.

Notes: The TOF bit is not cleared by accesses to

ACLR register. This feature allows simultaneous

use of the overflow function and reads of the free

running counter at random times (for example, to

measure elapsed time) without the risk ofclearing

the TOF biterroneously.

The timer is not affected byWAIT mode.

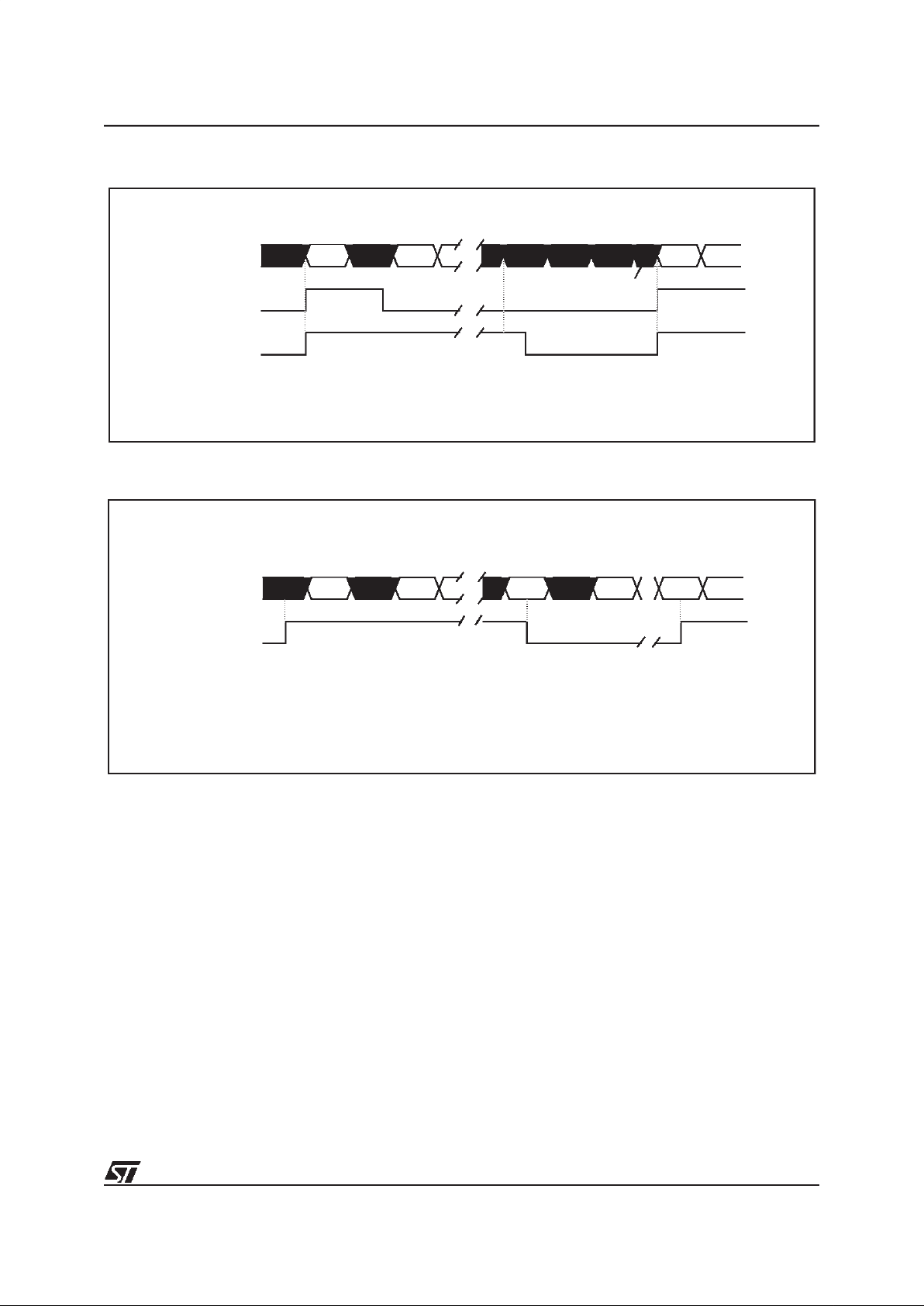

In HALT mode,the counter stops countinguntil the