Page 1

PROFESSIONAL DISC CAMCORDER

PDW-700

HD/SD SDI INPUT BOARD

CBK-HD01

ANALOG COMPOSITE INPUT BOARD

CBK-SC02

MAINTENANCE MANUAL

Volume 1 1st Edition (Revised 2)

Serial No. 10001 and Higher

Page 2

! WARNING

This manual is intended for qualified service personnel only.

To reduce the risk of electric shock, fire or injury, do not perform any servicing other than that

contained in the operating instructions unless you are qualified to do so. Refer all servicing to

qualified service personnel.

! WARNUNG

Die Anleitung ist nur für qualifiziertes Fachpersonal bestimmt.

Alle Wartungsarbeiten dürfen nur von qualifiziertem Fachpersonal ausgeführt werden. Um die

Gefahr eines elektrischen Schlages, Feuergefahr und Verletzungen zu vermeiden, sind bei

Wartungsarbeiten strikt die Angaben in der Anleitung zu befolgen. Andere als die angegeben

Wartungsarbeiten dürfen nur von Personen ausgeführt werden, die eine spezielle Befähigung

dazu besitzen.

! AVERTISSEMENT

Ce manual est destiné uniquement aux personnes compétentes en charge de l’entretien. Afin

de réduire les risques de décharge électrique, d’incendie ou de blessure n’effectuer que les

réparations indiquées dans le mode d’emploi à moins d’être qualifié pour en effectuer d’autres.

Pour toute réparation faire appel à une personne compétente uniquement.

PDW-700/V1 (E)

Page 3

CAUTION

Danger of explosion if battery is incorrectly replaced.

Replace only with the same or equivalent type

recommended by the manufacturer.

Dispose of used batteries according to the

manufacturer’s instructions.

ADVARSEL!

Lithiumbatteri-Eksplosionsfare ved fejlagtig

håndtering.

Udskiftning må kun ske med batteri

af samme fabrikat og type.

Levér det brugte batteri tilbage til leverandøren.

ADVARSEL

Lithiumbatteri - Eksplosjonsfare.

Ved utskifting benyttes kun batteri som

anbefalt av apparatfabrikanten.

Brukt batteri returneres

apparatleverandøren.

Vorsicht!

Explosionsgefahr bei unsachgemäßem Austausch

der Batterie.

Ersatz nur durch denselben oder einen vom

Hersteller empfohlenen ähnlichen Typ. Entsorgung

gebrauchter Batterien nach Angaben des

Herstellers.

ATTENTION

Il y a danger d’explosion s’il y a remplacement

incorrect de la batterie.

Remplacer uniquement avec une batterie du même

type ou d’un type équivalent recommandé par le

constructeur.

Mettre au rebut les batteries usagées conformément

aux instructions du fabricant.

VARNING

Explosionsfara vid felaktigt batteribyte.

Använd samma batterityp eller en likvärdig typ

som rekommenderas av apparattillverkaren.

Kassera använt batteri enligt gällande

föreskrifter.

VAROITUS

Paristo voi räjähtää jos se on virheellisesti

asennettu.

Vaihda paristo ainoastaan laitevalmistajan

suosittelemaan tyyppiin.

Hävitä käytetty paristo valmistajan ohjeiden

mukaisesti.

PDW-700/V1 (E)

1 (P)

Page 4

CLASS 1 LASER PRODUCT

LASER KLASSE 1 PRODUKT

LUOKAN 1 LASERLAITE

KLASS 1 LASER APPARAT

This Professional Disc Camcorder is classified

as a CLASS 1 LASER PRODUCT.

Laser Diode Properties

Wavelength: 400 to 410 nm

Emission duration: Continuous

Laser output power: 135 mW (max. of pulse peak),

65 mW (max. of CW)

Standard: IEC60825-1 (2001)

GEFAHR

Bei geöffnetem Laufwerk und beschädigter oder

deaktivierter Verriegelung tritt ein unsichtbarer

Laserstrahl aus. Direkter Kontakt mit dem

Laserstrahl ist unbedingt zu vermeiden.

This label is located

insidethe outside panel

of the unit.

CAUTION

The use of optical instruments with this product will

increase eye hazard.

Use of controls or adjustments or performance of

procedures other than those specified herein may result

in hazardous radiation exposure.

X-RAY RADIATION WARNING

Be sure that parts replacement in the high voltage block

and adjustments made to the high voltage circuits are

carried out precisely in accordance with the procedures

given in this manual.

For safety, do not connect the connector for peripheral

device wiring that might have excessive voltage to the

following port(s).

: Network connector

Follow the instructions for the above port(s).

2 (P)

PDW-700/V1 (E)

Page 5

Table of Contents

Manual Structure

Purpose of this manual ................................................................. 5

Related manuals ........................................................................... 5

1. Service Overview

1-1. Locations of Main Parts .................................................. 1-1

1-1-1. Locations of the Printed Wiring Boards ................ 1-1

1-1-2. Locations of Main Mechanical Parts ..................... 1-3

1-2. Circuit Description.......................................................... 1-4

1-2-1. Camera System ...................................................... 1-4

1-2-2. CCD Block ............................................................ 1-5

1-2-3. Video Signal System ............................................. 1-5

1-2-4. System Control ......................................................1-6

1-2-5. Digital Audio System .......................................... 1-12

1-2-6. Audio System ...................................................... 1-12

1-2-7. Audio DSP Operation Processing ....................... 1-14

1-2-8. Optical Drive System .......................................... 1-16

1-2-9. Power Supply Systems ........................................ 1-17

1-2-10. LCD System ........................................................ 1-18

1-2-11. Others .................................................................. 1-18

1-3. Matching Connectors .................................................... 1-20

1-4. Signal Inputs and Outputs ............................................. 1-20

1-5. On-Board Switch and LED Function ........................... 1-24

1-6. How to Take Out a Cartridge Manually ....................... 1-34

1-6-1. Taking Out a Cartridge at Power-off ................... 1-34

1-6-2. When You Cannot Take Out a Cartridge Even

If Pressing the EJECT Button at Power-on .........1-34

1-7. Removing/Installing ..................................................... 1-35

1-7-1. Removing Outside Panel .....................................1-35

1-7-2. Reinstalling Outside Panel .................................. 1-35

1-7-3. Inside Panel ......................................................... 1-35

1-7-4. Handle Assembly ................................................1-36

1-7-5. Front Panel .......................................................... 1-37

1-7-6. SW Guard Assembly ...........................................1-38

1-7-7. Shoulder Pad, Connector Cover .......................... 1-38

1-7-8. Connector Panel Assembly .................................1-39

1-7-9. Rear Panel Assembly .......................................... 1-40

1-7-10. Battery Connector ............................................... 1-40

1-8. Removing/Installing LCD Block .................................. 1-41

1-8-1. LCD Block .......................................................... 1-41

1-8-2. LCD Hinge .......................................................... 1-43

1-8-3. LCD Backlight and LCD Panel ........................... 1-44

1-9. Replacing the Flat Cables, Flexible Card

Wires/Boards ................................................................1-45

1-10. Service Tools/Measuring Equipment List .................... 1-46

1-10-1. Service Tools .......................................................1-46

1-10-2. Measuring Equipment ......................................... 1-47

1-11. Firmware/Software ....................................................... 1-48

1-11-1. EEPROM/FRAM List .........................................1-48

1-11-2. Firmware Update Using the USB Memory ......... 1-49

1-11-3. Software Option Registration Method

by Using USB Memory .......................................1-51

1-12. Other Overview ............................................................ 1-52

1-12-1. Notes on Handling Optical Block Assembly ...... 1-52

1-12-2. Standard Torque for Screws ................................1-53

1-12-3. Stop Washer ........................................................ 1-53

1-12-4. Description of CCD Block Number ....................1-54

1-12-5. Memory Backup Battery ..................................... 1-54

1-12-6. IC Link Replacement ..........................................1-54

1-12-7. Circuit Protection Element ..................................1-54

1-12-8. Precautions for Use of Condensation Sensor ...... 1-55

1-12-9. Precautions for the Battery Connector ................ 1-55

1-12-10. Notes on Repair Parts ..........................................1-55

1-12-11. Unleaded Solder .................................................. 1-55

2. XDCAM Web Site

2-1. XDCAM Web Site Overview ......................................... 2-1

2-2. Status Menu .................................................................... 2-3

2-2-1. Device Information ............................................... 2-3

2-2-2. Hours Meter ........................................................... 2-4

2-2-3. Software Version ................................................... 2-5

2-3. Disc Menu....................................................................... 2-7

2-3-1. Disc Properties ...................................................... 2-7

2-3-2. Thumbnails ............................................................2-7

2-4. Maintenance Menu ......................................................... 2-8

2-4-1. Software Update ....................................................2-8

2-4-2. Account ............................................................... 2-13

2-4-3. Network ...............................................................2-14

2-4-4. License Registration ............................................2-15

PDW-700/V1 (E)

1

Page 6

3. Error Messages

3-1. Error Messages Overview............................................... 3-1

3-2. Error Code List ............................................................... 3-2

3-2-1. Main Code and Sub Code ...................................... 3-2

3-2-2. Error 0X ................................................................. 3-3

3-2-3. Error 20 .................................................................3-4

3-2-4. Error 3X ................................................................. 3-5

3-2-5. Error 5X ................................................................. 3-5

3-2-6. Error 6X ................................................................. 3-5

3-2-7. Error 91 .................................................................3-6

3-2-8. Error 92 .................................................................3-7

3-2-9. Error 95 .................................................................3-7

4. Setup Menu

4-10-19. SKEW .................................................................. 4-97

4-10-20. SERVO_2 ............................................................ 4-97

4-10-21. ACCELERATION OFFSET ...............................4-98

4-10-22. ERROR LOGGER .............................................. 4-99

4-10-23. VERSION .......................................................... 4-100

4-10-24. SERIAL NO ...................................................... 4-100

4-10-25. CLEAR MEDIA LOG ......................................4-100

4-10-26. UPLOAD TO EEPROM ................................... 4-100

4-11. AUDIO A/D Error Correction .................................... 4-101

4-12. AUDIO D/A Error Correction .................................... 4-102

4-13. AUDIO LEVEL Volume Compensation ....................4-102

4-14. Adjusting Battery End Detection Voltage .................. 4-103

4-15. SERVICE SUPPORT Menu .......................................4-104

4-16. Setup Menu List .......................................................... 4-105

4-1. Setup Menus ................................................................... 4-1

4-1-1. Basic Operations of Setup Menus ......................... 4-1

4-1-2. How to Display the SERVICE Menu .................... 4-1

4-2. TOP Menu ...................................................................... 4-2

4-3. USER Menu .................................................................... 4-3

4-4. OPERATION Menu ....................................................... 4-4

4-5. PAINT Menu ................................................................ 4-27

4-6. MAINTENANCE Menu ............................................... 4-38

4-7. FILE Menu.................................................................... 4-56

4-8. DIAGNOSIS Menu ...................................................... 4-65

4-9. SERVICE Menu ........................................................... 4-69

4-10. Drive Maintenance ........................................................ 4-85

4-10-1. Basic Operation on Drive Maintenance

Menus .................................................................. 4-85

4-10-2. TEMPERATURE SENSOR ............................... 4-85

4-10-3. DEW SENSOR ................................................... 4-86

4-10-4. FAN MOTOR ..................................................... 4-86

4-10-5. ACCELERATION SENSOR ..............................4-87

4-10-6. LOADER ............................................................. 4-88

4-10-7. SLIDER-AUTO TEST ........................................4-91

4-10-8. IN-LIM TEST ..................................................... 4-91

4-10-9. OUT-LIM TEST ................................................. 4-92

4-10-10. SPINDLE MOTOR-AUTO TEST ...................... 4-92

4-10-11. FOCUS ACTUATOR ......................................... 4-93

4-10-12. TRACKING ACTUATOR ................................. 4-94

4-10-13. SA ACTUATOR ................................................. 4-94

4-10-14. LASER ................................................................ 4-95

4-10-15. ND FILTER ......................................................... 4-95

4-10-16. SKEW .................................................................. 4-96

4-10-17. LENS CLEANING ............................................. 4-97

4-10-18. SERVO_1 ............................................................4-97

5. File System

5-1. Structure of File System ................................................. 5-1

5-2. Data Structure .................................................................5-2

5-3. Operating the Files and the Data Flow ........................... 5-3

5-3-1. USER FILE ........................................................... 5-3

5-3-2. ALL FILE .............................................................. 5-5

5-3-3. REFERENCE FILE ............................................... 5-7

5-3-4. Other FILE (SCENE FILE and LENS FILE) ....... 5-9

5-3-5. SERVICE FILE ...................................................5-10

5-3-6. Other RESET ....................................................... 5-11

5-4. Special Items to Save .................................................... 5-12

5-4-1. White Gain .......................................................... 5-12

5-4-2. Master Gain .........................................................5-13

5-4-3. Shutter .................................................................5-13

6. Periodic Maintenance and Inspection

6-1. Periodic Check/Replacement Parts List.......................... 6-1

6-2. Cleaning .......................................................................... 6-2

6-2-1. General Information for the Use of Cleaning

Cloth ......................................................................6-2

6-2-2. Cleaning Loader Assembly ................................... 6-2

6-2-3. Cleaning Spindle Motor ........................................ 6-3

6-2-4. Cleaning Pickup Lens ............................................ 6-3

6-3. Cares after Using under Special Environment................ 6-4

6-4. Digital Hours Meter ........................................................6-5

6-4-1. Display Method and Reset Methods ..................... 6-5

6-5. Recommended Replacement Parts ................................. 6-6

6-6. Precautions for the Battery Connector ............................ 6-8

6-7. Precaution on Hanging Bracket of Handle .....................6-8

2

PDW-700/V1 (E)

Page 7

7. Replacement of Main Parts

7-1. Optical Drive Assembly ................................................. 7-1

7-1-1. Removing/Reinstalling Loader Assembly ............7-1

7-1-2. Removing/Reinstalling Drive Sub Assembly .......7-5

7-1-3. Replacing Cleaner Assembly ................................ 7-7

7-1-4. Replacing Loading Motor Assembly .................... 7-8

7-1-5. Replacing Optical Block Assembly ......................7-9

7-1-6. Replacing No.2/No.3 Gear Assemblies ............... 7-12

7-1-7. Replacing Seek Motor Assembly ........................7-14

7-1-8. Replacing Spindle Motor .................................... 7-15

7-1-9. Removing/Reinstalling Lock Release

Assembly .............................................................7-16

7-1-10. Removing/Reinstalling LD Motor ...................... 7-17

7-2. Removing/Reinstalling Mounted Circuit Board of the

Optical Drive ................................................................ 7-18

7-2-1. SE-709 Board ..................................................... 7-18

7-2-2. SE-857 Board ..................................................... 7-19

7-2-3. SE-858 Board ..................................................... 7-21

7-3. Replacing Fan Motor (Drive) ....................................... 7-23

7-4. Replacing Fan Motor (Rear) .........................................7-24

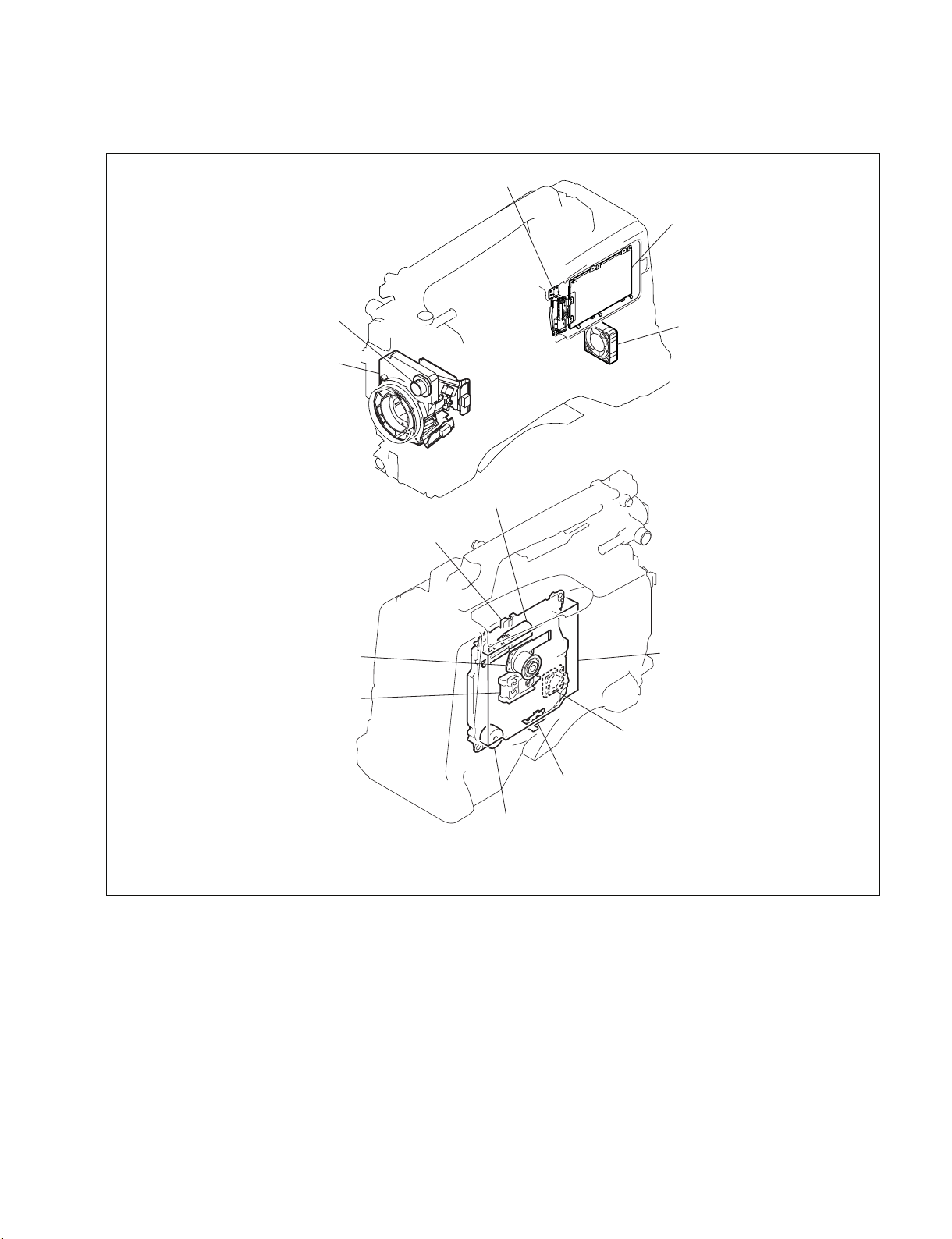

7-5. Removing/Reinstalling CCD Unit ................................ 7-25

7-5-1. Removing CCD Unit ...........................................7-25

7-5-2. Reinstalling CCD Unit ........................................ 7-26

7-6. Service Action After Replacing the CCD Unit............. 7-27

7-7. Removing/Installing Boards .........................................7-28

7-7-1. CN-2947 Board and TG-260 Board .................... 7-28

7-7-2. AT-177 Board and DCP-44 Board ......................7-28

7-7-3. DVP-45 Board and SY-355 Board ......................7-29

7-7-4. ENC-118 Board, HP-148 Board and

SW-1391 Board ...................................................7-29

7-7-5. FP-157 Board ...................................................... 7-30

7-7-6. CN-2946 Board and CN-3026 Board ..................7-31

7-7-7. KY-623 Board ..................................................... 7-32

7-7-8. CN-3025 Board and SW-1425 Board ................. 7-32

7-7-9. CN-3001 Board ................................................... 7-33

7-7-10. IO-235 Board ....................................................... 7-33

7-7-11. CI-37 Board .........................................................7-33

7-7-12. PS-731 Board ...................................................... 7-34

7-7-13. AXM-38 Board, CN-2948 Board,

SW-1352 Board and RM-216 Board ................... 7-34

7-7-14. MS-86 Board ....................................................... 7-34

7-7-15. CNB-25 Board and PS-708 Board ...................... 7-35

7-7-16. CN-3005 Board and SW-1426 Board ................. 7-35

7-7-17. DR-606 Board ..................................................... 7-36

7-7-18. RE-246 Board ...................................................... 7-37

7-7-19. RX-101 Board ..................................................... 7-37

7-7-20. MB-1111 Board ................................................... 7-38

7-8. Service Action After Replacing or Repairing

the Board ....................................................................... 7-39

7-8-1. Optical Block Assembly ...................................... 7-39

7-8-2. AT-177 Board .....................................................7-39

7-8-3. CN-3005 Board ................................................... 7-39

7-8-4. DCP-44 Board .....................................................7-39

7-8-5. SY-355 Board ...................................................... 7-40

7-8-6. FP-157 Board ...................................................... 7-40

7-8-7. DR-606 Board ..................................................... 7-40

7-8-8. SE-857 Board ...................................................... 7-40

8. Optical Drive Alignment

8-1. Optical Drive Alignment Overview................................ 8-1

8-1-1. Precautions ............................................................ 8-1

8-1-2. Fixtures .................................................................. 8-1

8-1-3. Preparations Before Adjustment ........................... 8-1

8-2. Procedures After Replacing the Optical Block

Assembly and the Board .................................................8-1

8-2-1. Adjustment After Replacing the Optical

Block Assembly .................................................... 8-1

8-2-2. Adjustment After Replacing the DR-606

Board ..................................................................... 8-1

8-2-3. Adjustment After Replacing the SE-857 Board ....8-1

8-3. Servo1 Automatic Adjustment ....................................... 8-2

8-4. Skew Adjustment ............................................................ 8-3

8-4-1. Tangential Skew Adjustment ................................ 8-3

8-4-2. Radial Skew Adjustment .......................................8-5

8-5. Servo2 Automatic Adjustment ....................................... 8-6

8-6. Clearing Media Log ........................................................ 8-6

8-7. After Adjustment ............................................................ 8-6

PDW-700/V1 (E)

3

Page 8

9. Electrical Alignment

9-1. Preparation ...................................................................... 9-1

9-1-1. Fixtures and Equipment ........................................9-1

9-1-2. Connection ............................................................9-1

9-1-3. Switch Setting before Adjustment ......................... 9-2

9-1-4. Notes on Adjustment .............................................9-2

9-1-5. Gray-Scale Chart and its Maintenance ..................9-3

9-2. Adjustment ...................................................................... 9-4

9-2-1. Confirming VCO CONT Frequency .....................9-4

9-2-2. Modulator Balance Adjustment ............................9-4

9-2-3. VA Gain Adjustment ............................................. 9-5

9-2-4. Black Shading Adjustment ....................................9-6

9-2-5. White Shading Adjustment ................................... 9-7

9-2-6. Black Set Adjustment ............................................9-8

9-2-7. Flare Adjustment ...................................................9-9

9-2-8. Auto Iris Adjustment ...........................................9-10

9-2-9. RPN Adjustment ................................................. 9-11

9-2-10. S/H DC Adjustment ............................................ 9-12

9-2-11. RPN Correction Procedure ..................................9-13

4

PDW-700/V1 (E)

Page 9

Purpose of this manual

Related manuals

Manual Structure

There are volume 1 and volume 2 in the Maintenance manual of PDW-700.

The maintenance manuals (volume 1, 2) are intended for use by trained system and

service engineers, and provides the information of maintenance and detailed service.

The following manuals are available in this model.

If this manual is required, please contact your local Sony Sales Office/Service

Center.

..

. Operation Manual (Supplied with the unit)

..

This manual is necessary for application and operation (and installation) of this

unit.

..

. Maintenance Manual

..

Volume 1: Describes about maintenance information, parts replacement, and

guideline for adjustment.

Part number: 9-968-417-03

Volume 2: Describes about block diagrams, schematic diagrams, board layouts

and detailed parts list required for parts-level service.

Part number: 9-968-435-03

..

. “Semiconductor Pin Assignments” CD-ROM

..

This “Semiconductor Pin Assignments” CD-ROM allows you to search for

semiconductors used in Broadcast and Professional equipment.

This manual contains a complete list of semiconductors and their ID Nos., and

thus should be used together with the CD-ROM.

Part number: 9-968-546-06

PDW-700/V1 (E)

5

Page 10

Page 11

Section 1

Service Overview

1-1. Locations of Main Parts

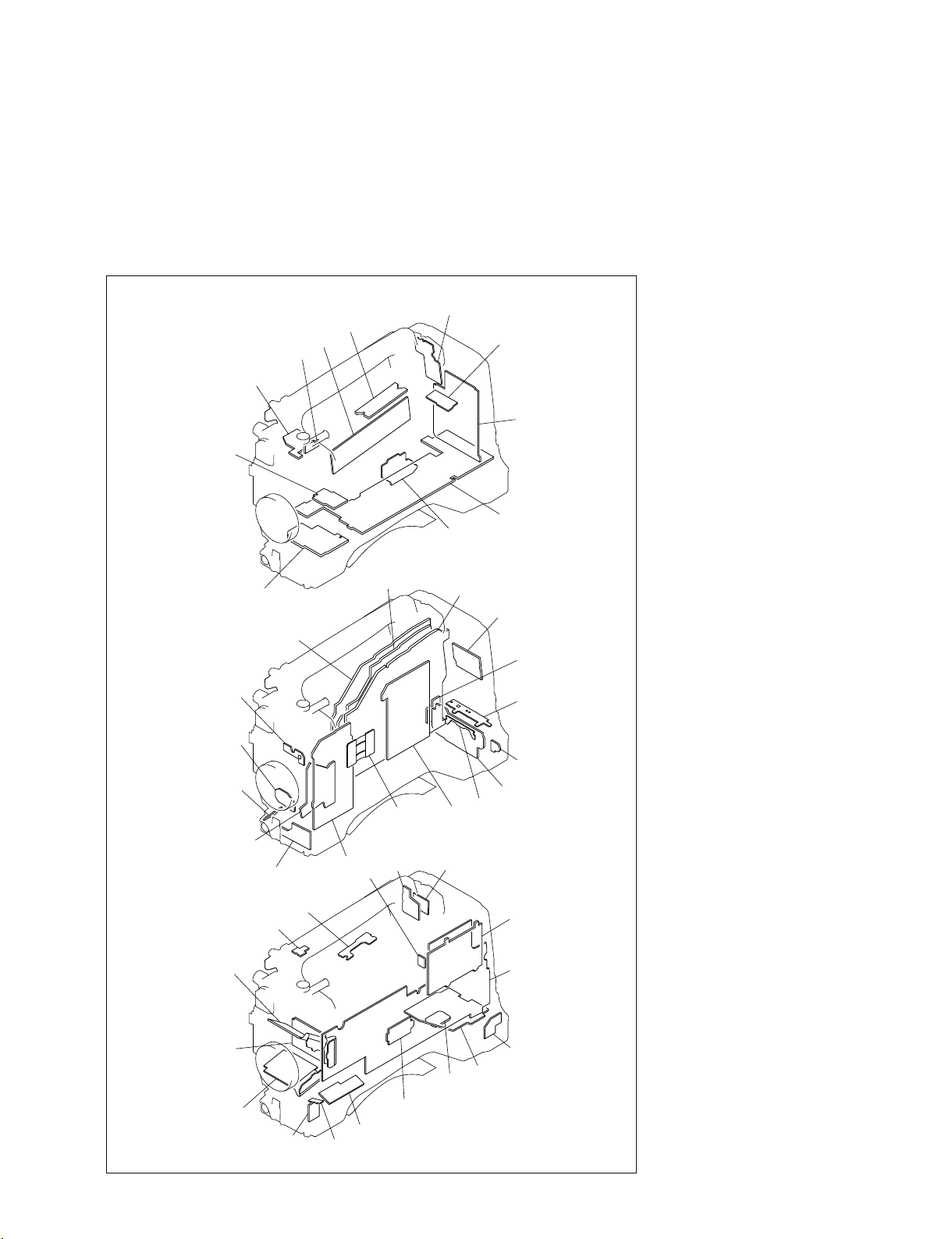

1-1-1. Locations of the Printed Wiring Boards

Main unit

@\

#/

@.

#'

7

9

@,

!;

8

@'

$=

#,

@/

!'

$[

$/

!\

!,

$\

@[

$-

![

$]

5

@]

#[

#;

1 AT-177

2 AXM-38

3 CI-37

4 CN-2946

5 CN-2947

$- SW-1391

$= SW-1425

$[ SW-1426

$] SY-355

$\ TG-260

6 CN-2948

#]

7 CN-3001

8 CN-3005

9 CN-3025

0 CN-3026

!- CNB-25

@=

@;

!= DCP-44

![ DET-45

!] DET-47

!=

3

!\ DR-606

!; DR-617

!' DVP-45

!, ENC-118

6

!. FP-157

@/ HP-148

#.

@- HP-149

@= IO-235

@[ KY-623

1

!]

#\

2

@] LED-444

@\ MA-162

@; MB-1111

@' MS-86

!/4

@, PA-342/342A

@. PA-343/343A

#/ PA-344

#-

#- PD-118

#= PS-708

!.

#[ PS-731

#] RE-246

#\ RM-216

#; RX-101

#' SE-924

#, SW-1249

#. SW-1352

#=

@-

!-

$/ SW-1385

PDW-700/V1 (E)

1-1

Page 12

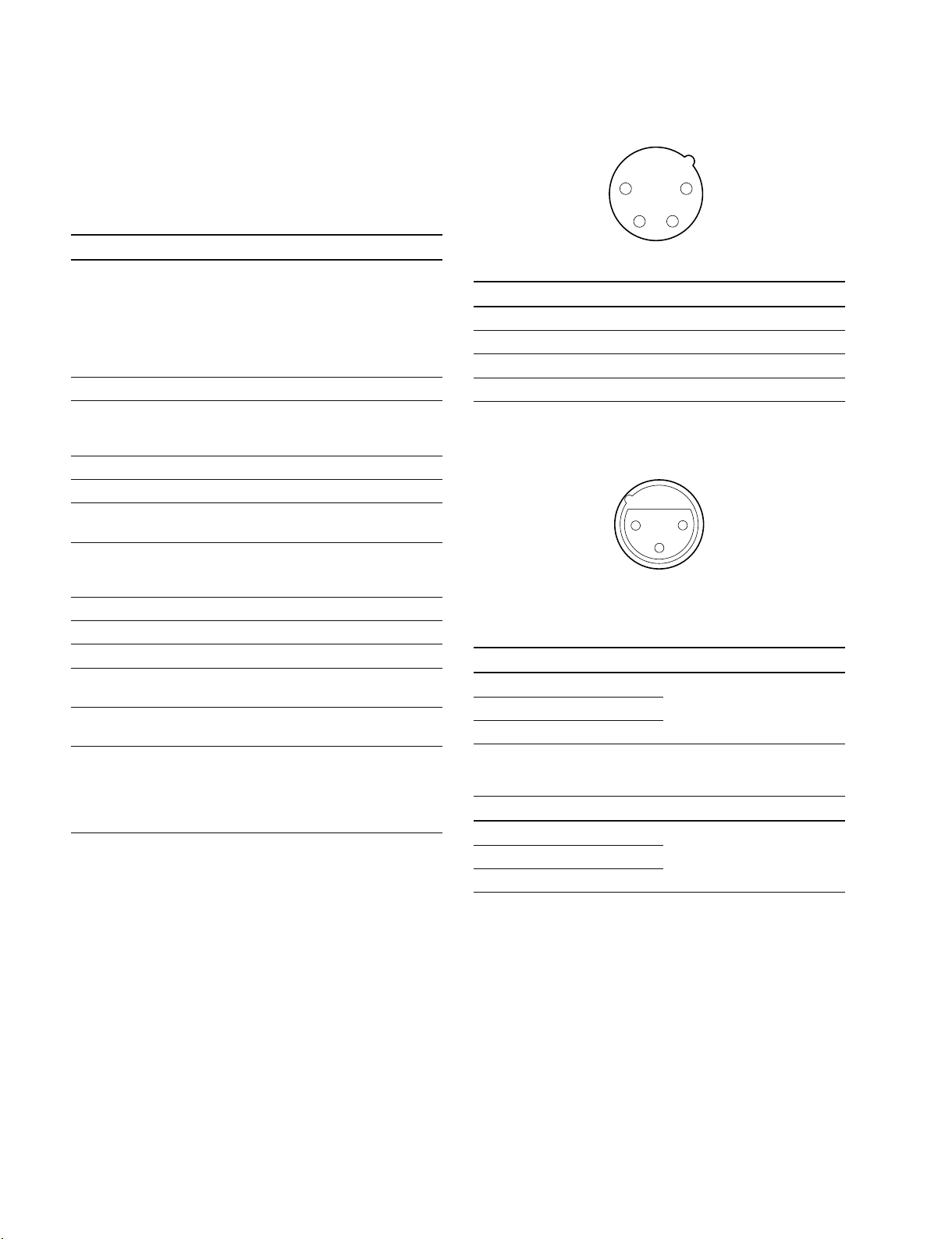

Optical drive

1 SE-709

2 SE-857

3 SE-858

4 SW-1125G

1

2

4

3

1-2

PDW-700/V1 (E)

Page 13

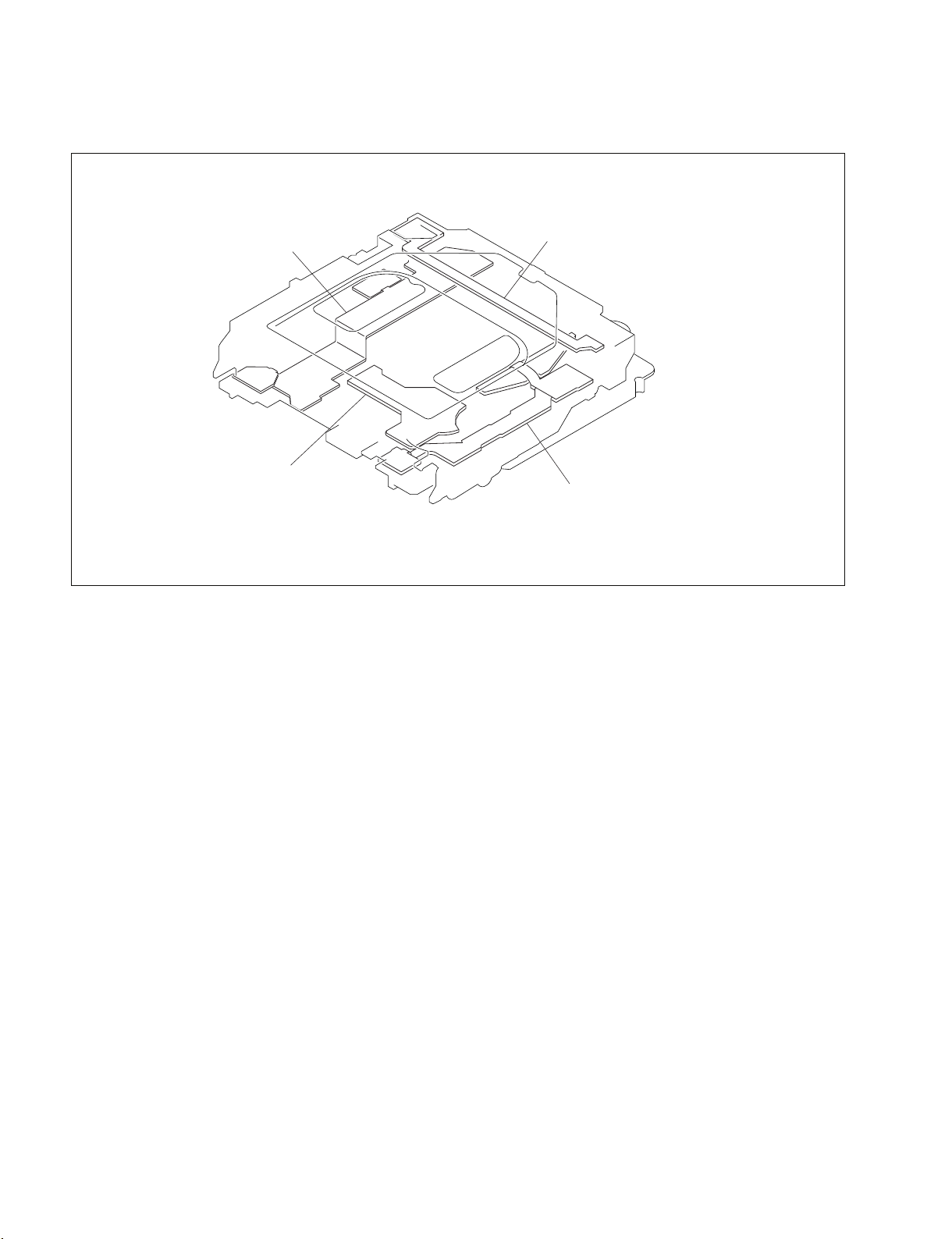

1-1-2. Locations of Main Mechanical Parts

3

4

2

1

1-2. Circuit Description

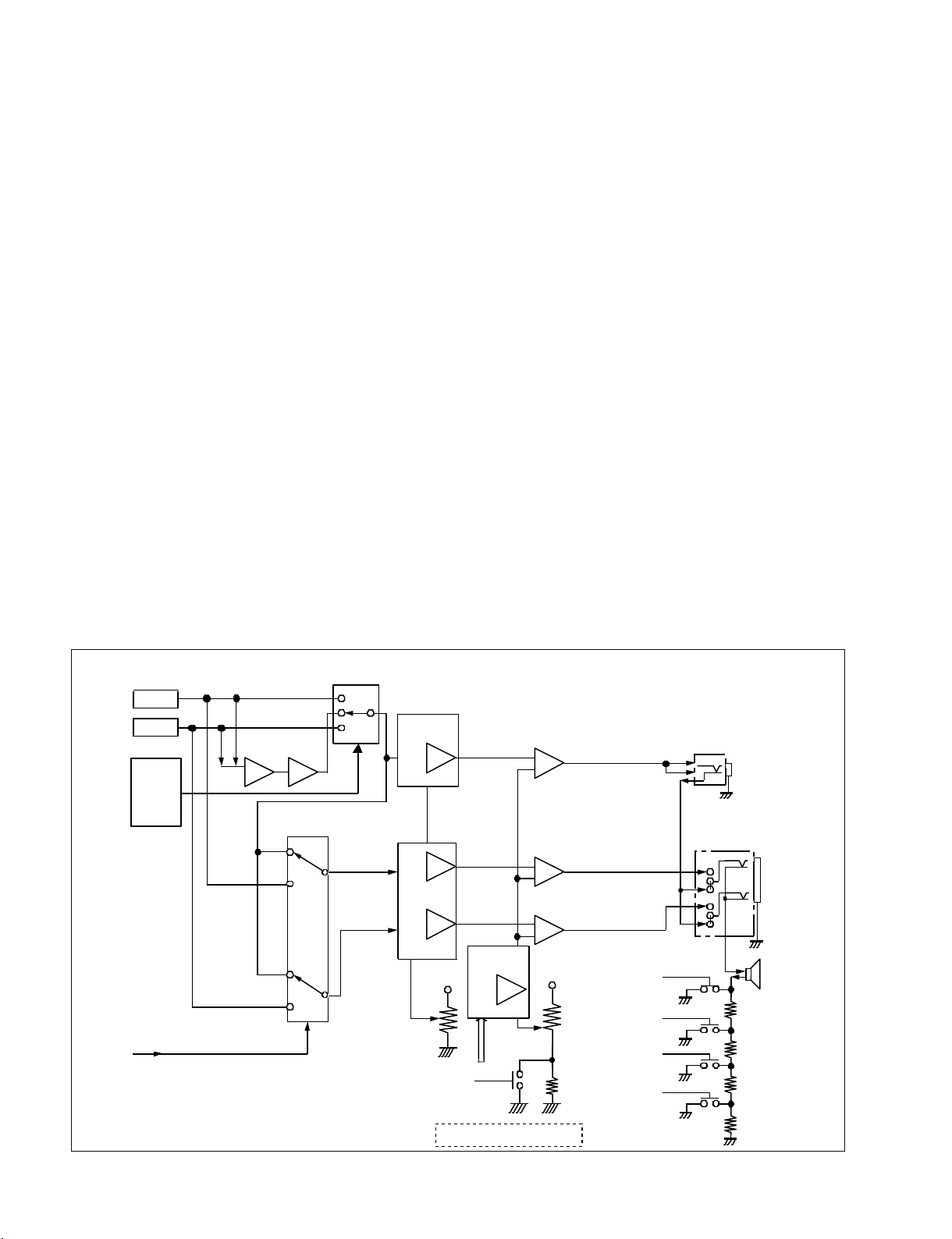

1-2-1. Camera System

AT-177 board

The AT-177 board is the microprocessor board that

controls the camera block.

DCP-44 board

The DCP-44 board consists of the block for A/D conversion

of the analog RGB signal from the PA-342/PA-342A/PA343/PA-343A/PA-344 board via the feedback clamp circuit,

the cam-era DSP block that performs the signal processing,

the dri-ver block that sends the analog signal that is D/A convert-ed to the outputs, and the I/F block to the AT-177 board.

1. Microprocessor peripherals

The CPU (IC209) uses SH2A (R5S7206), and the clock provides 32 MHz from an external source that is six multiplication in the CPU so that the clock runs on 192 MHz. The memory is composed of 64 MBit flash memory (IC302, IC303), 16

MBit SRAM (IC3056), and 1 MBit FRAM (IC308).

2. A/D input of the CPU

The A/D port equipped to the CPU is connected to the

following signal lines and monitored: CC position, ND

position, temperature, IRIS position of a camera lens,

ZOOM position, and mic volume level.

3. Internal communication

The serial communication includes intercommunication

with the BleConSh IC on the DCP-44 board, the writing

controls to the character generator IC, and

intercommunication with the disc.

The parallel communication is equipped with the 8-bit data

line, the total 11-bit address line (A0-A7, A14-A16),

control line clock, XRD, XWR, OE, DIR, CS, and

(QWERTY, ZXCV, TG).

In addition, the intercommunication is performed with

EEPROM on the DCP-44 board, the DAC and I/O port IC

for the video signal, and the I/O port IC on the FP-157

board with the I2C line that is installed directly to the CPU.

4. Memory stick circuit

The memory stick controller IC (IC610) is driven at 16

MHz, and the two-way communication and the clock

signal are directly connected from the connector (CN602)

to the memory stick connector of the MS-86 board via the

coaxial harness. This is compatible with the Memory Stick

PRO/DUO.

5. External communication

The 2 channel serial communication driver CXD9093R

(IC411) is equipped and performs external communication

with the remote control unit RM-B150/B750.

6. ROM jig connector (CN601)

The connector CN101 that can be connected to the jig for

writing the boot program (MS-86 board) is included.

1-4

After passing through the pre-filter (FL300 to FL302), the

analog RGB signal input from the PA-342/PA-342A/PA343/PA-343A/PA-344 board is converted to 74 MHz rate

14-bit digital RGB sign-al by the A/D converter (IC107 to

IC109), then input into the camera processor IC (IC600).

The camera signal processor IC (IC600) detects the

average value and the peak value of the camera video

signals that are required for the AUTO operations of the

camera such as AUTO black balance, AUTO white

balance, and AUTO iris control. The detected average

value and peak value are sent to the AT-microprocessor on

the AT-177 board. In addition to the above operations, the

25/30 PsF conversion function and the 1080 to 720

conversion function are realized by using the DDR

SDRAM (IC700 to 704).

After passing through white balance, white shading, and

flare correction, the camera main video signal performs the

Digital GAIN UP, then performs the Digital Noise

Reduction. Then, the matrix signal and the detail signal are

added to perform pedestal control, gamma correction, knee

correction, and white clip processing. After passing

through the selector circuit with which either the camera

main video signal or the color bar signal can be selected,

the selected signal is output from IC (IC600) to IC800.

The digital VBS signal and the digital Y signal for VF

supplied from the camera signal processor IC (IC800) are

converted into the analog VBS signal and analog VF signal

by the D/A converter* (IC1513, IC1524, IC1525). After

passing through the circuit with which either the camera

analog VBS signal or the VF Y can be selected, the

selected signal is output to the TEST OUT connector.

After passing through the circuit with which either the

GENLOCK IN connector input or the video signal can be

selected, the selected signal is output to the VF connector.

In addition, the sync separation circuit and the PLL circuit

to synchronize with the external input video of the GENLOCK IN connector are included.

The detected average value of the video signal detected in

the camera signal processor IC (IC600) and peak value are

loaded to the AT-microprocessor on the AT-177 board

through the 8-bit data bus.

PDW-700/V1 (E)

Page 15

At the same time, various control signals are controlled by

the AT-177 board via I/O Expander (IC3, IC4, IC67).

All volumes are controlled electronically, and the level

adjustment is adjusted from the menu.

are generated by IC8 and are sent to the DR-617 board.

These pulses are generated from the 74 MHz clock in

synchronization with the HD VD signal input from the

DCP-44 board. In addition, the TG-260 board has an

interface circuit with the optical filter.

The main functions of IC800 are the down-conversion HD

to SD, the conversion 720 to 1080 for VF output, and the

VF DETAIL generation processing digital ECN

processing.

The camera main signal of the SD system is output to IC1000.

After performing the multiplex and parallel-serial

conversion on the character signal, audio signal, and the

ancillary signal in IC1000, the HD signal and SD signal

output from IC800 pass through IC (IC1112, IC1113) and

are output to SDI1 and SDI2 connectors as the HD-SDI

and SD-SDI signals. After another system performs scaling

in IC1000 through the SDRAM (IC1309), the HD signal

output from IC800 passes through the D/A converter

(IC1518) and the video signal is sent to the LCD display.

The HD signal output from IC600 is sent to the recording

system (DVP-45 board) through multiple character signals

in IC1000. After the signal from the RX-105 board on the

SDI input option and the SDI signal from the 50-pin I/F are

selected internally in IC1000, the signals are separated into

the video signal, audio signal, and the ancillary signal, then

sent to the recording system (DVP-45 board).

* :The main functions of IC800 are the down-conversion HD to SD, the

conversion 720 to 1080 for VF output, and the VF DETAIL generation

processing digital ECN processing. The camera main output of the SD

system is output to IC1000.

1-2-2. CCD Block

PA-342/PA-342A/PA-343/PA-343A/PA-344 board

The CCD drive pulses that are supplied from the TG-260

board are amplified so that these pulses can drive the CCD

imagers directly (IC2: H Driver). On the other hand, the

CCD output signals are amplified approximately two times

and input to IC10. The video signal is drawn by the co-related dual sampling inside IC10 and GAIN UP of 0 to 12

dB is performed by the internal GAIN AMP. In addition,

the differences in the CCD sensitivity are adjusted by

adjusting GAIN. In addition to the above operations, the

temperature that is detected by the temperature sensor

(IC4) is converted to the voltage data and is sent to the AT177 board via the DCP-44 board.

TG-260 board

The pulses that drive the CCD imagers and the pulses that

are used for sample-and-hold of the CCD output signals

DR-617 board

The CCD drive pulses input from the TG-260 board and

the sample-and-hold pulse are latched and output to the

PA-342/PA-342A/PA-343/PA-343A/PA-344 boards. In

addition, the DR-617 board has the V driver of CCD.

The CCD V sub voltage and CCD sensitivity adjustment

data are recorded in the EEPROM (IC20).

1-2-3. Video Signal System

DVP-45 board

1. Baseband/Video signal processing system

<Recording system>

The component parallel digital video signal supplied from

the video circuit of the DCP-44 board is input to LVIS

(IC400) of the DVP-45 board.

Signal pre-processing such as the filtering and scaling is

performed in this system.

<Playback system>

The playback digital video data is loaded from LVIS

(IC400) and sent to the DCP-44 board via the MB board as

the component parallel digital video signal.

The component parallel digital video signal sent to the

DCP-44 board is distributed to each path of HD/SD-SDI,

VF, COLOR-LCD, and down-conversion and encoding to

the composite video signal are performed according to the

setting.

2. Video compression signal processing system

<Recording system>

The recording digital video signal that has undergone

signal processing on the DVP-45 board is sent to MPEG2VIDEO Codec (TORINO: IC1000, 1200, 1400) and

compressed to the MPEG-2 VIDEO format.

The compressed digital video data is sent to PIER G4

(IC1900) and written to PIER_SDRAM (IC1901 to IC1904).

The recording digital video signal is encoded to MPEG4VIDEO format in LVIS (IC400) at the same time and

generated as the Proxy video data.

The generated Proxy video data is sent to PIER G4

(IC1900) and written to PIER_SDRAM (IC1901 to IC1904).

PDW-700/V1 (E)

1-5

Page 16

The recording digital data via i.LINK/network is sent to

PIER G4 (IC1900) via the PCI bus and written to

PIER_SDRAM (IC1901 to IC1904).

While recording on a disc, the data in PIER_SDRAM

(IC1901 to IC1904) is sent to the DR-606 board via the

ATA interface.

<Playback system>

The playback video data and the Proxy video data are sent

to PIER G4 (IC1900) via the ATA interface and written to

PIER_SDRAM (IC1901 to IC1904).

The playback digital video data in PIER_SDRAM (IC1901

to IC1904) is sent to the MPEG2-VIDEO Codec (TORINO: IC1200, IC1400). Decode processing is performed

and then the data is sent to LVIS (IC400).

The playback Proxy video data in PIER_SDRAM (IC1901

to IC1904) is sent from PIER G4 (IC1900) to LVIS

(IC400) and decode processing is performed.

The Proxy video data is used as the video signal during the

search.

The playback video data in PIER_SDRAM (IC1901 to

IC1904) is provided to i.LINK/network via the PCI bus as

the MXF file data.

3. Sync signal system

Whether the status is on record or on playback, 74/27 MHz

clock, HD-F, HD-V, HD-H, HD-PB-F, SD-F, SD-V, and

SD-H that are always input from the DCP-44 board are the

reference signal.

Based on these reference clocks, the video sync timings

and system timings are generated.

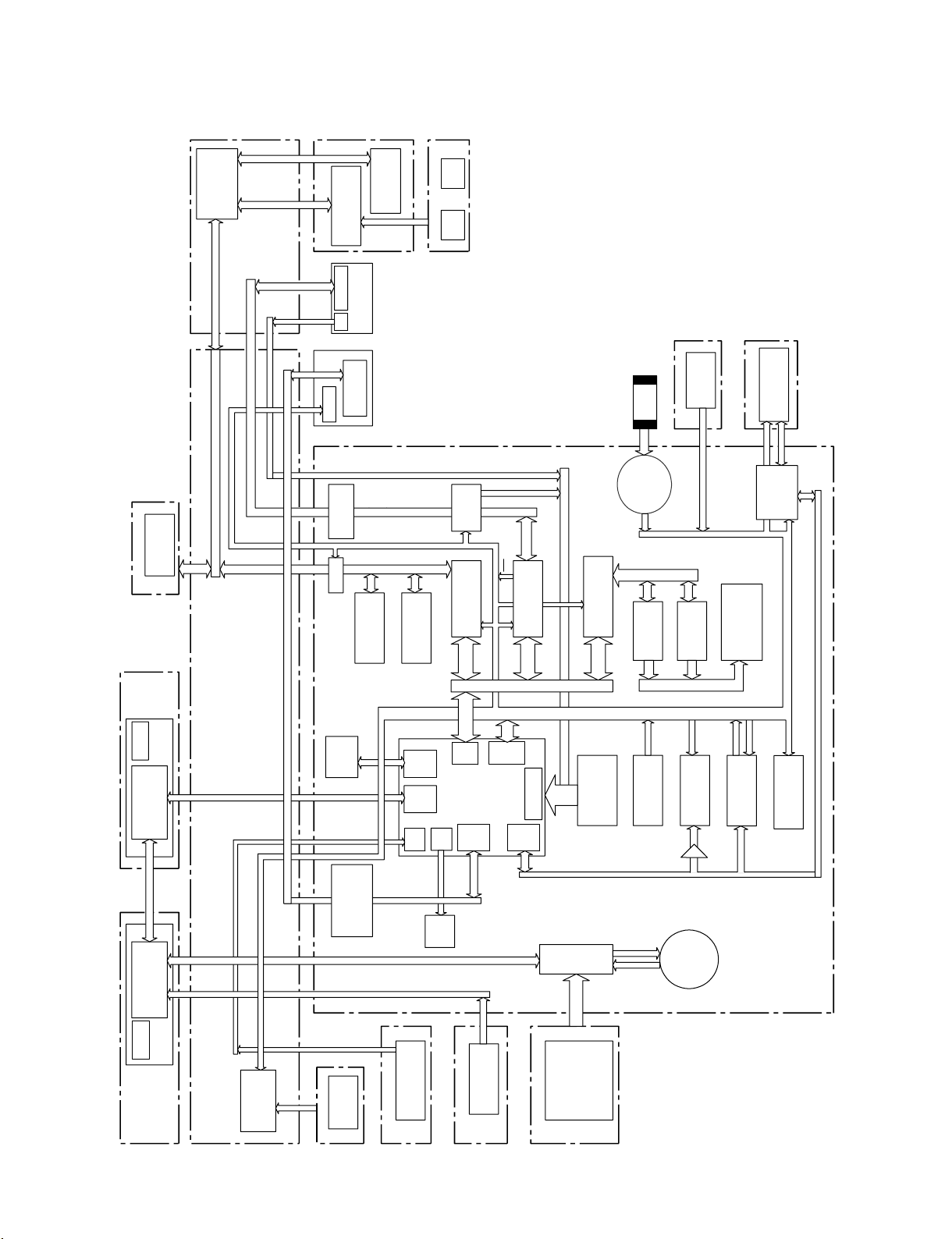

1-2-4. System Control

SY-355 board

1. Disc record/playback system control

The following functions are realized using the RISC

microprocessor (hereinafter refer to as CPU: IC 200) as the

CPU for the system control on the SY-355 board.

<PCI bus interface>

CPU is connected to PIER G4 (IC1900/DVP-45 board)/

FAM controller on the DVP-45 board and PCI-PCI Bridge

(IC900) via the PCI bus interface to receive and send data

with one another and perform control.

The PCI bus interface communicates with the following

devices by relaying through PIER G4 (IC1900/DVP-45

board).

. CAVA (IC200/DVP-45 board)

. MPEG2-VIDEO CODEC (IC1000, 1200, 1400/DVP-45

board)

. AUDIO REC/PB DSP (IC800, 801/DVP-45 board)/

AUDIO Low Resolution DSP (IC900/DVP-45 board)

. LVIS (IC400/DVP-45 board)

. Optical Drive (DR-606 board)

. AT microprocessor (AT-177 board)

. FP microprocessor (FP-157 board)

. Character generator (IC503/DCP-44 board)

. LTC generator/reader (PIER G4 (IC1900) built-in)

The PCI bus interface is connected to the Linux system on

the SY-355 board via the PCI-PCI Bridge (IC900/SY-355

board) and receives and sends data to the controllers.

<Memory controller>

. SDRAM (SY-355 board: IC201 to 204) control (32 bit x

64M word)

. Flash memory (IC505, IC506/SY-355 board) control (32

bit x 16 M word)

<Serial interface>

. EEPROM control saving the setting data

<External control bus (CPU LOCAL bus)>

. IN port/OUT port control

RESET signal output on each device, loading the switch

setting, and similar signals

.

CAVA/PIER G4/FAM/BRIDGE each FPGA

configuration

. FRAM (IC507/SY-355 board) control

2. Application device control system (Linux)

This is the system that uses RISC microprocessor

(hereinafter refer to as CPU: IC1300) on the SY-355 board

to control the device for the application. Linux is used as

the OS.

CPU and peripheral circuit configuration is almost same as

that of the system control.

<PCI bus interface>

The CPU exchanges data with the USB controller

(IC1500) via the PCI bus interface. In addition, the CPU

exchanges the data with the CPU of the system control via

the PCI-PCI Bridge (IC500/SY-355 board) on the same

bus.

<PCI BRIDGE (IC900)>

The functions of PCI BRIDGE are data relay of the PCI

bus and the I/F function to the OSD display controller on

the LVIS (IC400/DVP-45 board).

1-6

PDW-700/V1 (E)

Page 17

<USB HOST Controller (IC1500)>

USB HOST Controller exchanged data with the USB

devices such as the flash memory using the interface

compatible with the USB 2.0.

<Ether interface>

Ether interface controls the Ether PHY (IC1/CN-2946

board) and connects to the network via it.

FP-157 board

12. FP_CPU backup circuit

13. Backup lithium battery voltage measurement circuit

14. Independent operation of FP_CPU

15. REAR input control

16. REAR XLR automatic insertion detection circuit

control (DET-47 board and sensor holder)

17. Color LCD monitor drive control and switching/

rotation detection circuit

18. Nonvolatile memory control

19. Monochrome LCD display circuit with back light

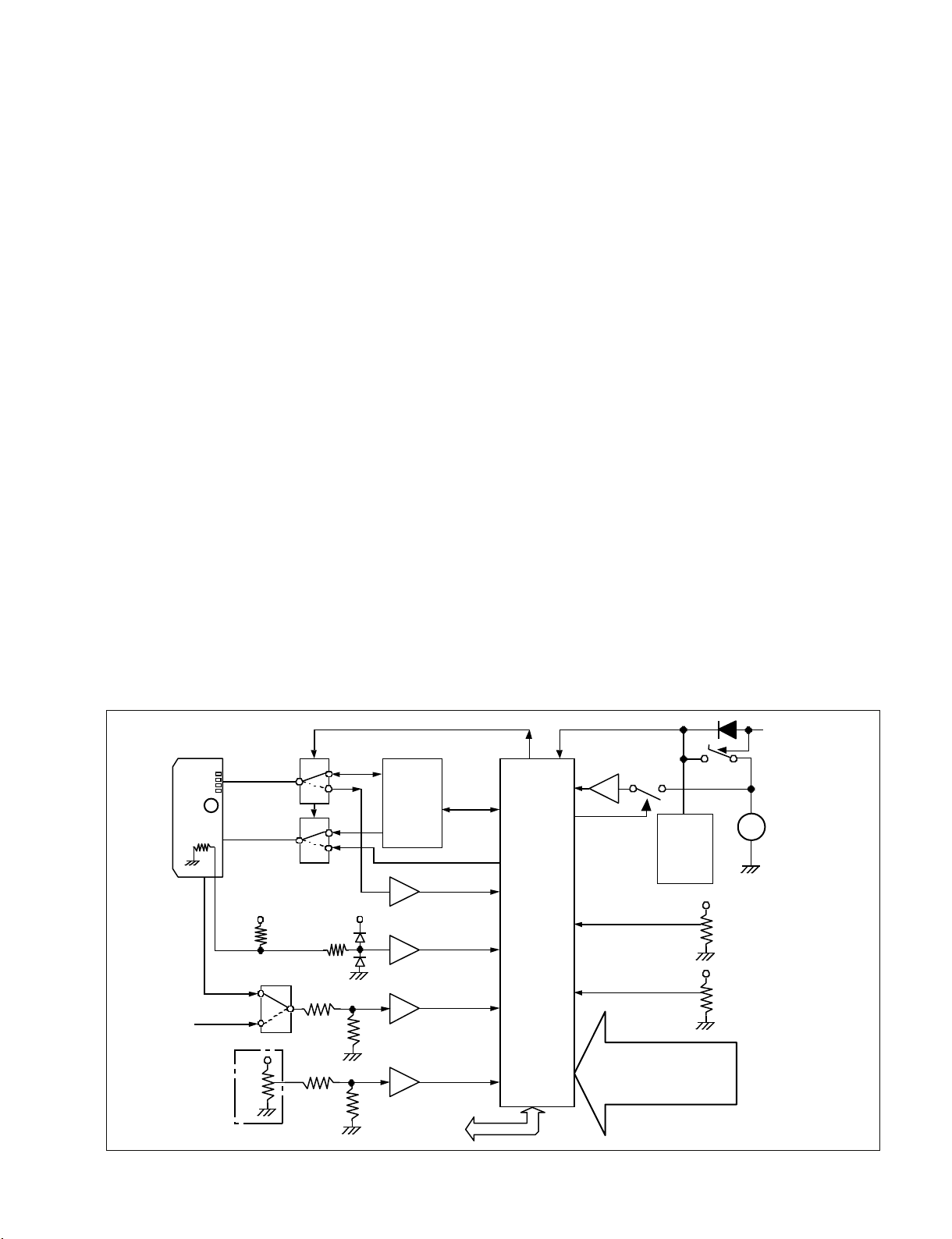

The FP-157 board has the FP_CPU (IC921) as the submicroprocessor and the hardware consists of the synchronous and asynchronous serial communication, I2C communication bus, and the 8-bit bus. The main function is

controlling the audio system.

Main functions

. Synchronous serial communication

The functions of synchronous serial communication are

the color LCD monitor setting, monochrome LCD

display, audio D/A setting, analog wireless communication, and the ITORON communication.

. Asynchronous serial communication

Digital wireless communication.

. I2C bus

The rear connector, detection such as PLAY/STOP key,

Info_BATTERY communication, Real Time Clock

communication, Serial EEPROM (Memory) communication, and I/O control communication make up the 3channel I2C bus.

. 8-bit bus

The 8-bit bus controls the serial communication bus

(SDA,SCL) of the 3-channel I2C bus controller (Parallel

bus to I2C_bus Controller).

. CPU I/O

The CPU I/O loads the A/D and controls the I/O port

terminal.

Main blocks

1. Audio mode control

2. AUDIO level indication

3. STOP/PLAY keys control

4. CTL/TC/UBIT control

5. Real Time Clock control

6. WARNING_LED control and alarm tone control

7. Wireless receiver (optional equipment) control

8. Software download function

9. Power supply voltage measuring circuit

10. Info-Battery communication circuit

11. POWER OFF soft control circuit

Description of each block

1. Audio mode control

Audio control is performed by receiving the audio mode

information and the menu setup information from the

ITORON (CPU) on the SY-355 board.

The switch information of the three positions is connected

to the AD terminal of the CPU and processed as the AD

signal of the three-valued data.

The audio is switched in the I2C bus PCA-9555 (I/O port:

IC923, 924).

2. AUDIO level indication

The digital signal applied on the DSP is converted to 16

bits and set in the register in DSP.

ITRON (CPU) reads and displays it on the color LCD

monitor. The peak hold time is approx. 1400 ms.

3. STOP/PLAY keys control

Each switch on the KY-623 board is connected to PCA9555 for I2C bus to read the ON/OFF information of the

switch and turn on the LED. The switch information is

transferred to ITORON (CPU).

At POWER-ON, the LED of EJECT, F REV, PLAY, F

FWD are turned on, initialized, and turned off.

4. CTL/TC/UBIT control

The switch information of the three positions is connected

to the AD terminal of the CPU and processed as the AD

signal of the three-valued data.

The ON/OFF information of the switches are transferred to

the ITRON (CPU) and displayed on the color LCD

monitor.

5. Real Time Clock control

The Real Time Clock IC (IC908:RX-8025NB) uses

nonadjustable clock for the I2C bus. The accuracy is ± 15

seconds per month. When the power is turned on, the

FP_CPU reads data and send it to ITRON (CPU)

The ITRON (CPU) sends the time data to the Camera CPU

PDW-700/V1 (E)

1-7

Page 18

of the AT-177 board. The viewfinder uses the time data for

displaying the time. The data for year, month, day, and

time of the clock can be changed using the menu.

The settings for year, month, day, and time are sent to the

FP_CPU and the year, month, day, and time are written to

the Real Time Clock IC.

6. WARNING_LED control and alarm tone control

The WARNING information is supplied from the ITRON

(CPU) that is used to turn on and off the WARNING LED

on the FP-157 board.

The 1 KHz square wave generated from the PWM generator circuit inside the FP_CPU alarm tone is used as the

alarm tone.

7. Wireless Receiver Control (Optional function)

This communication circuit can control both analog and

digital wireless receivers.

Analog wireless receivers use the conventional method of

synchronous serial communication (200 Bps).

(Interval time: 80 ms)

Digital wireless receivers use 38 KBps asynchronous serial

communication to handle large amounts of communication

data.

CH1&2

or

CH3&4

CH-1/3

CH-2/4

IC750

FP-CPU

(CH-1/3,

MIX,

CH-2/4)

FP-CPU(Head Phone Out:Streo/Mono)

MIX INV

Mono

CH-1/3

Streo

Mono

CH-2/4

Streo

CH-1/3

MIX

CH-2/4

IC704

TC74HC4052

IC705

TC74HC4052

SW

MONITOR-VR

FP_CPU (MIN ALARM VOL)

IC706

NJM-2172

VCA

+InA

OutA

_InA

Cont

OutB

+InB

_InB

VCA

OutA

+InA

_InA

Cont

RV700

ALARM SIGNAL(FP_CPU)

Audio Monitor Block

With a built-in wireless receiver, when FP_CPU is in the

POWER-ON state, the receiver type is determined and

information such as the transmission RF sensitivity is loaded. This data is transmitted to Camera CPU via ITRON

(CPU) and can be viewed on the viewfinder.

8. Software download function

FP_CPU has internal flash memory so the software can be

overwritten. Load the software in the memory stick into

the camera microcomputer and transmit the data through

ITRON (CPU) in the SY-335 board to the FP_CPU where

it is written.

9. Power voltage measurement circuit (batteries other

than the info battery)

Power voltage measurement circuit (IC839) outputs two

types of DC voltage from DA output of the FP_CPU and

switches voltage in the IC839 6-pin to switch between a

measurement range of +9 V to +14 V and +12 V to +17 V.

The voltage measurement is sent to ITRON (CPU) as the

voltage value. ITRON calculates the remaining battery

charge, creates voltage display data, and returns the data to

FP_CPU. FP_CPU displays the voltage display data on the

monochrome LCD. The voltage display data can be checked at the same time in the status menu for the color LCD.

IC708

NJM386

Final AMP

+

_

IC707

NJM-2172

IC706

+3 Vdc

+InA

_InA

Q707

When ALARM-VOL Position 0 %,

Alarm Level is about _38 dBu.

VCA

OutB

Cont

ALARM-VR

IC709

NJM386

Final AMP

+

_

IC710

NJM386

Final AMP

+

_

+3 Vdc

RV701

R761

FP_CPU

(SP ATT LEVEL:0dB)

FP_CPU

(SP ATT LEVEL:_3dB)

FP_CPU

(SP ATT LEVEL:_6dB)

FP_CPU

(SP ATT LEVEL:_9dB)

Front_EARPHONE

CN701

CN702

L

R

Q712

Q715

Q711

Q716

Q713

Q717

Q718

L

R

REAR_EARPHONE

with SW

SW

SW

CN703

MONITOR

SW-1

SP

SW-2

SW-3

SW-4

1-8

PDW-700/V1 (E)

Page 19

10. Info battery communication circuit.

This equipment supports batteries with SM Bus

specifications. The serial communication bus (SDA, SCL)

for IC916 (Parallel bus to I2C_bus Controller) connected

to the FP_CPU bus passes through IC927 and IC928

(switching switch) and connects to the serial terminal of

the info battery. The Serial Clock Rate is 88 KHz.

The battery type, remaining time, and other information is

loaded onto FP_CPU and transmitted to ITRON (CPU).

ITRON (CPU) calculates the remaining battery charge and

creates remaining charge display data, and transmits the

data to Camera CPU and FP_CPU. FP_CPU displays the

remaining charge display data on the monochrome LCD.

The remaining charge display data can be checked at the

same time in the status menu for the color LCD.

11. Power off software control circuit

FP_CPU detects the POWER-SW OFF information. When

power can be turned on, the "Power OFF" command is sent

from ITRON (CPU) and FP_CPU controls the power OFF

circuit on the CNB-25 board.

12. FP_CPU backup circuit

Even when power is turned off for FP_CPU, the data is

saved for the internal RAM and Real Time Clock (RX8025NB) through backup on a coin battery. By saving the

system data, FP_CPU can be started up quickly when the

power is turned on.

BATTERY

F

E

Battery

ID Register

+

Battery-in

DC-in

Front

Microphone

Volume

INFO_ BATT

_SDA

INFO_BATT

_SCL

+3 V

FET-SW

(CNB-25 board)

+5 V

SW

Battery

ID Data

IC927

IC928

I2C_BUS

A

B

A

B

UNREG+12 V

+3 V

IC916

PCA9564

SDA

SCL

IC914

IC838

IC839

IC7

8 bit

CPU_BUS

D7

:

D0

Voltage

measurement

Voltage

measurement

Voltage

measurement

Voltage

measurement

13. Backup lithium battery voltage measurement circuit

FP_CPU performs voltage measurement on the backup

lithium battery. When recharging is detected, the reducedvoltage information is send to ITRON (CPU).

(Measurement interval time: 60 s)

Current is prevented from running through FET-SW

(Q836) in order to prevent power from being lost during

measurement. Furthermore, reverse current above +3 V is

prevented with FET-SW (Q829), thus extending the life of

the lithium battery. The battery life is guaranteed for about

5 years.

14. FP_CPU independent operations

When the POWER-SW is set to power off, power is

supplied from the UNSW +12 V power circuit to display

the counter and other information on the monochrome

LCD. Power is supplied to each power regulator with

IC830 (hyposaturation regulator 8 V) and independent

operations can be performed. The operations can be turned

on or off from the menu.

15. REAR input control

The serial communication bus (SDA, SCL) for IC917

(Parallel bus to I2C_bus Controller) connected to the

FP_CPU bus sends control for the AXM-38 board through

the motherboard with IC202 (PCA-9555: I2C_I/O_PORT)

on the CNB-25 board and acquires the following

information: REAR_XLR automatic insertion detection

Port

D15

:

D8

HD64F2378

Port

AN11

AN14

AN13

AN10

IC921

CPU

Vcc

AN15

Port

AN8

AN9

AN0

AN1

AN2

AN3

AN4

AN5

AN6

AN7

Q836

IC844

FET-SW

(1 time/60 sec)

CLOCK 16 MHz

Voltage measurement

Voltage measurement

FRONT,REA,WRR-SW1,2,3,4

CTL,TC,U_BIT-SW

FREE,SET,REC_RUN-SW

PRESET,REGENE,CLOCK-SW

Monitor-SW

(3 digitize level)

+3 V

IC908

Real Time

Clock

RX-8025NB

+3 V

+3 V

CH-1

RV1

CH-2

RV2

+3 V

(IC805)

Q829

FET-SW

Lithium

Coin

Battery

+3 V

PDW-700/V1 (E)

SW-1425

to iTRON_CPU

Voltage Measurement Block Overview

1-9

Page 20

circuit control, microphone amplifier gain control, operational amplifier power control, and digital/analog input

switching switch information.

16. REAR XLR automatic insertion detection circuit

control (DET-47 board and sensor holder)

Combine the DET-47 board on the sensor holder and

connect with the harness to the AXM-38 board.

The infrared light emitter uses one LED that connects to

the CH1 and CH2 receivers positioned in the middle of the

sensor holder on the left and right sides. When “Detection

ON” is set from the menu and the XLR connector is

inserted into the 3P-XLR connector, the infrared light is

blocked, the output from the receivers changes from L to

H, and insertion is detected. At this time, CH1 and CH2

operate automatically and the XLR input on the REAR

area is selected. (CH3 and CH4 are not switched

automatically. ) Detection interval time is 200 ms.

17. Color LCD monitor drive control and opening/rotation

detection circuit

The CN108 connector is connected to the power supply

and the RGB signal for video, the passes through CN802 to

connect directly into the LCD driver.

FP_CPU and LCD driver are connected with synchronous

serial communication. During POWER_ON, parameters

such as brightness and contrast can be set. This information is saved in the LCD (PD-118 board) nonvolatile

memory and the FP-157 board IC913 (nonvolatile memory).

Rotation is detected by the rotation sensor switch in DET45 after passing through CN802.

Opening and closing is detected from the hole terminal

(H801) on the FP-157 board and the field intensity from

the permanent magnet (neodymium: Ne-FeB).

18. Nonvolatile memory control

IC907 on the FP-157 board is nonvolatile memory that

supports the I2C bus.

This memory stores system information such as the A/D

and D/A error compensation values and color LCD

settings. During POWER-ON, this information is sent to

ITRON (CPU) and the color LCD device.

19. Monochrome LCD display circuit with backlight

FP_CPU and IC806 (UPD7225GB) are connected by a 500

KHz serial communication port. IC806 is an LCD

controller/driver that is programmable with software.

ND800 displays the BATTERY value, DISC capacity,

time, and counter value on the monochrome LCD at three

hour intervals.

H_AMP12CH_ON

B1

Buffer

ATT

Buffer

ATT

Buffer

ATT

Buffer

ATT

H_AMP34CH_ON

ch1

ch2

AMP

AMP

ch3

ch4

AMP

B2

L_A/D_PD12CH_ON

DVP-45 board

PD

AK5383

AK5383

PD

L_A/D_PD34CH_ON

AK4382

FP-157 board

FIL

TER

AMP

MIX/CH1/CH2

MA-162 board

FrontMIC-1

FrontMIC-2

AMP

ch1

ch2

AMP

Monitor-OUT

STEREO

FP_H_AUOUT_ON FP_H_AUIN_ON

B3 B4

CNB-25 board

AXM-34 board

(-3,0,4 dB standard ATT)

MONO

RX-101 board

ch1

ch2

REAR-1

REAR-2

1-10

Audio Power Save Block

PDW-700/V1 (E)

Page 21

CPU

HD64F2378

8bit

I2C BUS (330KHz)

CONTROL-1

IC917(PAC9564)

8bit

I2C BUS (330KHz)

CONTROL-3

IC918(PAC9564)

PCA-9555-1

I/O OUT +5V

PCA-9555-2

I/O OUT +5V

I2C-BUS(+5V)

AUDIO-Control

SignalSelect

HeadRoomSelect

EEPROM

CAT24WC02

RealTimeClock

RX8025B

I2C-BUS(+3V)

BusSw

BUS

TxD4

RxD4

SCK4

Port

AD

AD

SIDE_VOL

Audio_IN_SW

RV1,2

SWITCS

Control

D/A Convertor

AK-4382A

B/W LCD

UPD-7225GB

TxD3

RxD3

SCK3

TxD2

RxD2

SCK2

TxD1

RxD1

SCK1

LCD

Position

DET-45

Info_Battery

PCA-9555-4

I/O IN&OUT

+3V

I2C-BUS(+3V)

Audio in Select Sw

Amp Gain Control

AXM-38

CNB-25

WRR-855

RX

101

BusSw

I2C-BUS(+3V)

COLOR-LCD

(CXD-3662R)

PD-118

CN-802

Terminal

(BOOT)

I2C-BUS

I2C-BUS(+5V)

CPU

iTRON

CPU

Camera

FP-157

DVP-45

DCP-44

MB -1111

SW-1425

FRONT_MIC_VOL

SW-1391

MENU

STBY/SAVE

OFF/ON-PAGE

LOW/M/HIGH

PREST A/B

DDC-BRA

PCA-9555-5

I/O OUT +3V

I2C-BUS(+3V)

Rotary SW

ENC-82

LED:ON/OFF

Auido_Mute

8bit

SDA,SCL

ID

I2C-BUS(+5V)

DA

Alarm

Tone

MOS-FET level

conversion 0/3V

Interface

KY-623

PCA-9555-3

I/O OUT +3V

INT

CCC-SW

TK60011CS8

(hall element)

SorN

Pole

Magnet

LCD

Open/Close

MIC

5P terminal

CN-3001

SW-1352

SW-1

SW-2

MIC-AMP

GAIN Control

MA-162

AT-177

SY-355

DET-47

XLR-DETCT

BusSw

SCK3,TxD3,

RxD3

8bit

PORT

I2C BUS (88KHz)

CONTROL-2

IC916(PAC9564)

I2C-BUS(+5V)

FET_SW

N_Channel

AntonSW

Audio System Control

PDW-700/V1 (E)

1-11

Page 22

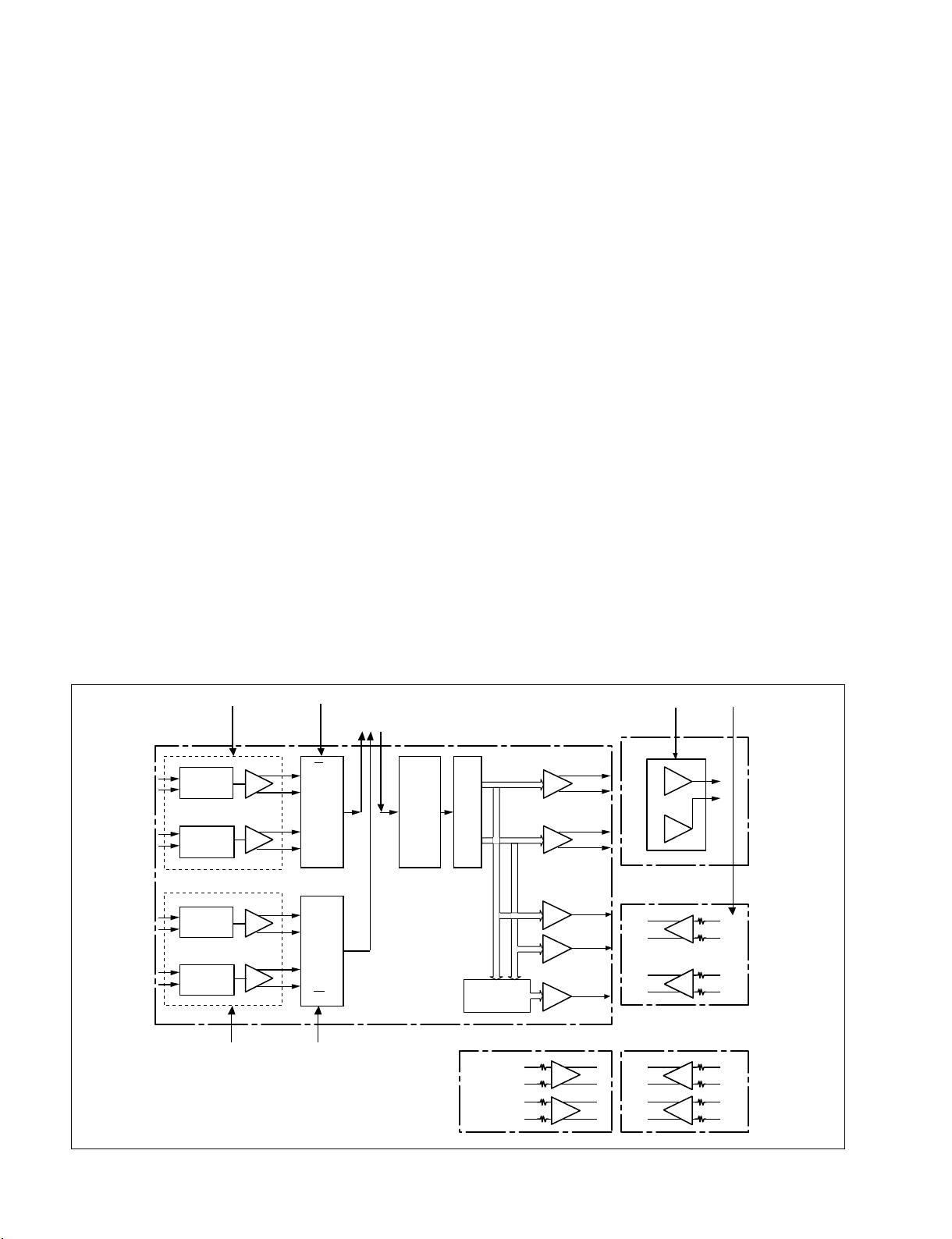

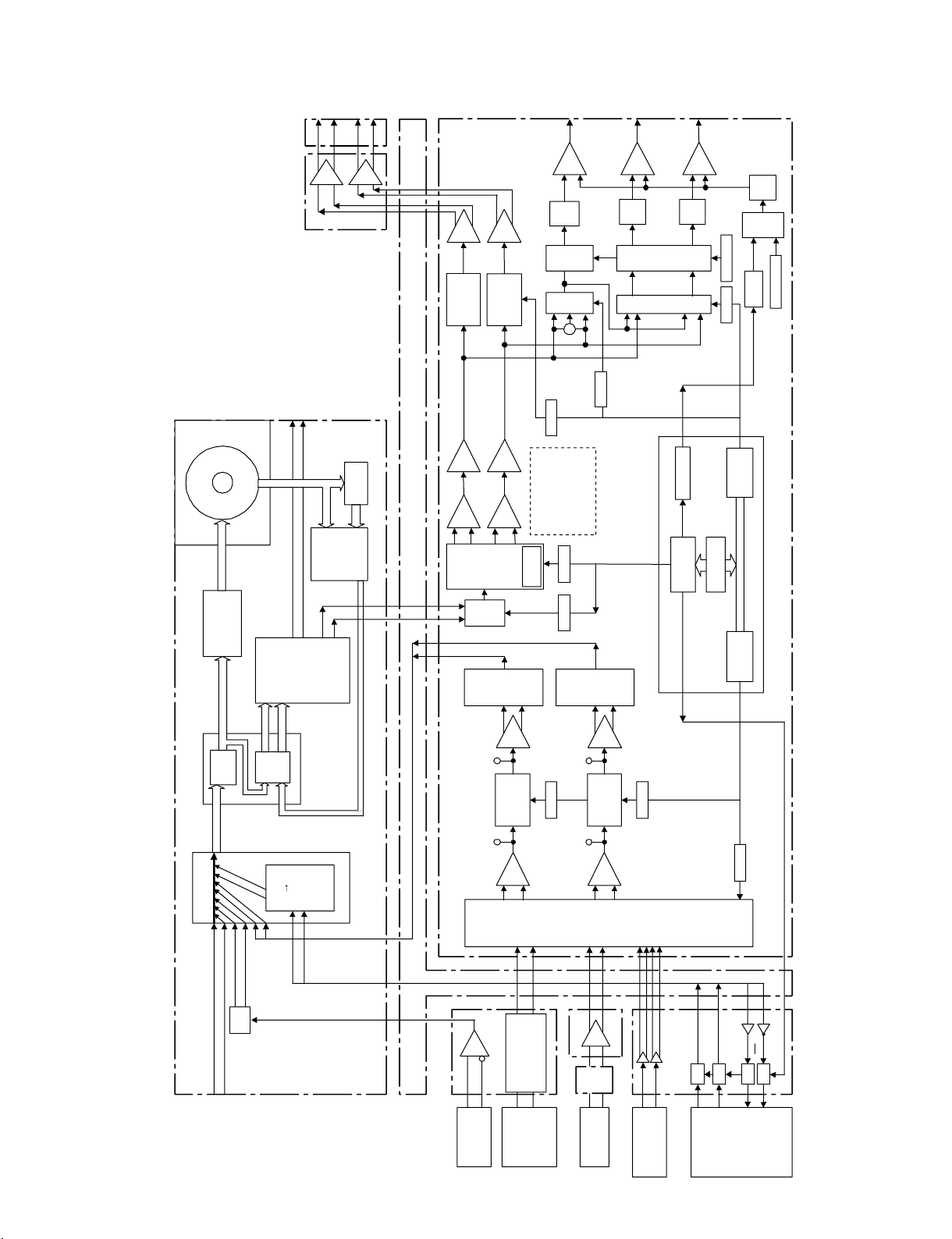

1-2-5. Digital Audio System

DVP-45 board

1. Audio signal processing system

<Recording system>

The analog audio signal input from the AUDIO IN

connector is converted into a serial digital audio signal

(two channels) with the AUDIO A/D converter on the FP157 board. The digital audio signal enters CAVA (IC200)

of the DVP-45 board through the MB-1111 board.

The serial digital audio signal (four channels) input from

the AES/EBU INPUT connector undergoes level

conversion in the AXM-38 board and is input into CAVA

(IC200) of the DVP-45 board. After the signal is decoded

in CAVA (IC200), it is synchronized and converted to the

same sampling rated as the recorded video signal with the

sampling rate converter (IC700, IC703).

Digital audio signals (eight channels) that include input

HD-SDI signal (when the option is attached) are decoded

with the DCP-44 board. Then, the signals are converted

into serial digital audio signals and entered into CAVA

(IC200) of the DVP-45 board via the MB-1111 board.

CAVA (IC200) selects the above entered digital audio

signal and sends it as the recorded audio data to AUDIO

REC DSP (IC800).

The recording digital audio data is sent to AUDIO Low

Resolution DSP (IC900) through CAVA (IC200), Proxy

audio data is generated in compressed A-Low format, and

the data is sent to PIER G4 (IC1900).

The above recording digital audio data and recording

compressed Proxy audio data are written PIER_SDRAM

(IC1901 to IC1904).

The recording digital data from the i.LINK/network is sent

to PIER G4 (IC1900) via the PCI bus and written to the

PIER_SDRAM (IC1901 to IC1904).

While recording to a disc, the data in PIER_SDRAM

(IC1901 to IC1904) is sent to the DR-606 board via the

ATA interface.

<Playback system>

The audio data and the Proxy audio data are sent to PIER

G4 (IC1900) via the ATA interface and written to the

PIER_SDRAM (IC1901 to IC1904).

The playback digital audio data in PIER_SDRAM (IC1901

to IC1904) is sent from PIER G4 (IC1900) to AUDIO PB

DSP (IC801), After performing signal processing such as

limiter, playback level control, and mute processing, the

signal is input to CAVA (IC200).

The audio data and Proxy audio data in PIER_SDRAM

(IC1901 to IC1904) is provided to i.LINK/network via the

PCI bus as the MXF file data.

<Playback system>

The playback digital audio signal that underwent playback

signal processing in AUDIO PB DSP (IC801) is entered

into CAVA (IC200), then separated and converted into the

serial digital audio signals for analog output systems and

digital output systems.

The analog output system serial digital audio signal is sent

to the AUDIO D/A converter in the FP-157 board via the

MB-1111 board. After it is converted into an analog audio

signal, the signal is output to the AUDIO OUT connector,

headphone, and monitor speaker.

The digital output system serial digital audio signal is sent

to the DCP-44 board via the MB-1111 board. The signal is

combined with the video signal in the DCP-44 board and

output as the HD/SD-SDI audio signal.

2. Digital signal processing system

<Recording system>

The recording audio data from CAVA (IC200) undergoes

signal processing such as recording level control, muting

process, and MIX/SWAP in AUDIO REC DSP (IC800),

and then it is sent to PIER G4 (IC1900) as recording digital

audio data.

3. Sync signal system

The reference signal is always the 24.576 MHz clock

entered from the DCP-44 board, whether recording or

playing back.

This reference clock is divided and timing signal for 256

FS, 64 FS and FS audio processing is generated.

1-2-6. Audio System

Block structure

Front microphone amp : MA-162 board

Input signal selector : FP-157 board

A/D circuit (CH1&2) : FP-157 board

A/D circuit (CH3&4) : FP-157 board

D/A circuit : FP-157 board

Final amp : CNB-25 board

Monitor amp : FP-157 board

Rear input : AXM-38 board

DPS operation processing : DVP-45 board

1-12

PDW-700/V1 (E)

Page 23

1. Front microphone amp

The front microphone amp on the MA-162 board comes

with a gain switch. (30 dB/20 dB/10 dB)

Gain switching can be performed from the menu.

(_60 dBu/_50 dBu/_40 dBu)

2. Input signal selector

The audio signal can be selected with the analog switch

(IC1 to IC4) based on the side panel switch information.

3. A/D circuit

A/D uses 24-bit AK-5383. The sampling frequency is 48

KHz.

The first has an ATT circuit for head room level adjustment.

performed with the operational amp with electronic

volume (NJM2172).

7. Rear input

The rear input is composed of the following: a switch for

Line In, AES/EBU, and MIC-IN; +48 V ON/OFF-SW;

automatic detection circuit (DET-47 board) for the 3-pin

input XLR connector; and the microphone amp (10 dB/20

dB/30 dB).

Gain switching can be performed from the menu.

(_60 dBu/_50 dBu/_40 dBu)

Line In input level setting can be switched to +4 dBu,

0 dBu, or _3 dBu with the slide switch on the AXM-38

board. (Open the inside panel.)

4. D/A circuit

D/A uses 24-bit AK-4382A. The sampling frequency is 48

KHz.

The latter has a differential LPF circuit and an output level

amp circuit.

5. Final amp

The final amp is located on the CNB-25 board and is

connected to the AXM-38 board with the connector-toconnector. The CH1 and CH2 output signals are output

from the 5-pin XLR connector.

The output level can be selected as _3 dBu, 0 dBu, or +4

dBu from the menu.

6. Monitor amp

Composed of the monaural amp for the front earphone and

stereo amp for the rear earphone, the volume control is

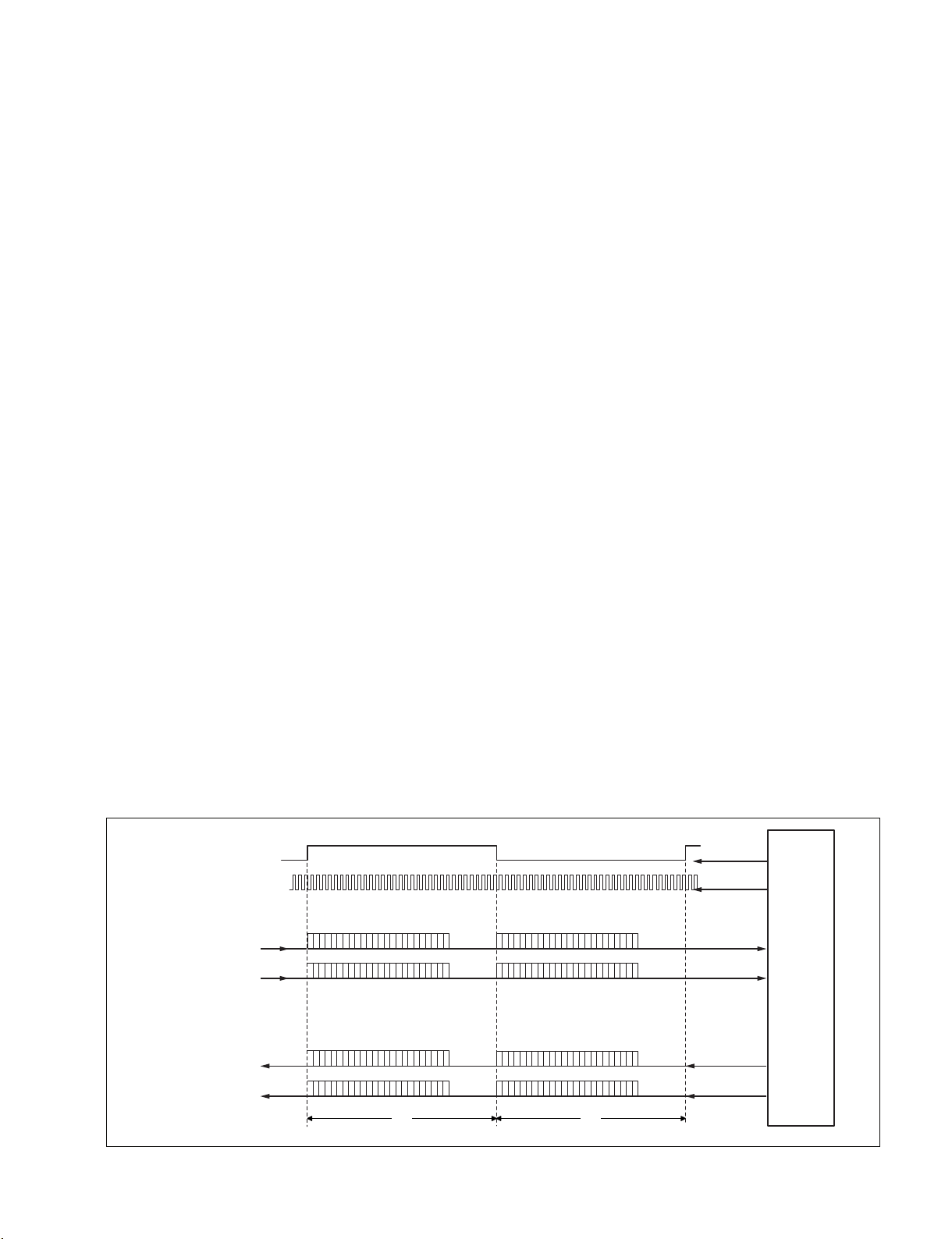

Fs

64Fs

Operation description

After the power to the device is turned on, each port in the

FP-157 board CPU is initialized, the necessary resistor data

is set, and MUTE is cancelled. (After approximately 3

seconds, the digital EE sound can be monitored.)

The front mic signal passes through the MA-162 board and

MB-1111 board before entering the input signal selector

(analog switch: IC1 to IC4) of the FP157 board.

The rear input signal passes through the AXM-38 board,

CNB-25 board, and MB-1111 board before entering the

input signal selector (analog switch: IC1 to IC4) of the FP157 board.

The information from the FRONT/REAR/WIRELSS

switch position can be obtained by loading the three

Fs

64Fs

A/D OUT CH3&4 (24bit)

A/D OUT CH1&2 (24bit)

(Left Justified,24bit Data)

D/A IN CH3&4 (24bit)

D/A IN CH1&2 (24bit)

(Left Justified,24bit Data)

PDW-700/V1 (E)

23

MSB

23 0

MSB

23 0

MSB

23 0

MSB

32bit

A/D & D/A Signal Format Diagram

0

23 0

MSB

CH3

23 0

MSB

CH1

23 0

MSB

CH3

23 0

MSB

CH1

32bit

CH4

CH2

CH4

CH2

AN34

AN12

DA34

DA12

DVP-45

1-13

Page 24

signals from the switch connected to each A/D terminal in

the FP_CPU (S1 to S4).

FP_CPU sends the switch position information to

ITORN_CPU of the SY-355 board, and then selects the

audio signal by receiving the audio mode information from

the ITORN_CPU.

The selected CH1 and CH2 system signals enter the

differential amp (IC5: balance-to-unbalance converter) and

pass through the head room level switching circuit and

balance-to-unbalance conversion amp for A/D. Then, the

signals are applied to the A/D converter IC (IC102: 24-bit).

The serial digital audio signal (2 channels) converted to

digital is entered to VAX (IC200) of the DVP-45 board via

the MB-1111 board

VAX (IC400) selects the entered digital audio signal and

sends it as the recorded audio data to AUDIO REC DSP

(IC800).

DSP for audio performs high-speed processing for

operations such as gain processing during manual

operations, AUTO processing, LIMITER processing, 67

Hz notch filter while using the front mic, LPF (15 KHz)

ON/OFF, internal SG, and audio level detection.

combined front and side volumes and sends the results to

DSP.

The D/A serial signal for playback passes through the

DVP-45 board and MB-1111 board and enters the digital

switch (IC461) of the FP-157 board. In the monitor CHSW, CH1&2 or CH3&4 is selected and applied to the 24bit D/A converter (IC453).

The D/A converter output passes through the differential

LPF, ATT balance-to-unbalance conversion amp (IC514),

and MB-1111 board. It is applied to the final amp (IC200,

IC201) of the CNB-25 board and output from the 5-pin

XLR connector (AXM-38 board).

The audio signal for the monitor passes from IC520/620

output through the monaural, mix, and stereo switching

switch (IC703, IC704). Then, the signal is applied to the

operation amp (NJM2172) with electronic volume.

The rear earphone can be switched between stereo and

mono from the menu.

The monitor speaker output level can be lowered from the

volume. Select one of the following for the ATT value: 0,

_3 dB, _6 dB, or _9 dB.

On the other hand, the front volume and side volume are

connected to the A/D terminal in the CPU and the volume

voltage is converted into digital with the internal 10-bit A/

D. After being converted into a multiplication value for

DSP, the signal is sent to ITORN_CPU.

ITORN_CPU performs operation processing on the

InPut

24dBu

20dBu

10dBu

+4dBu

+0dBu

_3dBu

_10dBu

_20dBu

_30dBu

_40dBu

_50dBu

_60dBu

_17dB

WireLess

_40dBu

_50dBu

_60dBu

_20dB

Max Input : _20dBu

Digital_WRR;

Reference OUT : _40dBFS

(DSP setting the same MIC

as specifications)

12dB:ATT 0dB

_24dB

Max Input : _10dBu

16dB:ATT 4dB

18dB:ATT 6dB

20dB:ATT 8dB

_20dBu

_30dBu

MIC

Max Input : 0dBu

HeadRoom

Tp-1

_21dBu

_31dBu

I2S-Format

_40dBFS

AK5383

40dB

30dB

Tp-101

_29dBu

_39dBu

HeadRoom : Get 30dBu

AK-5383 input : _23dBu

(X, Y terminal : _29dBu)

HeadRoom : Get 40dBu

AK-5383 input : _33dBu

(X, Y terminal : _39dBu)

LINE-IN;

MIC-IN;

24bit

A/D

_30dBFS

_40dBFS

DSP

(TMS320DA150GGU120)

_20dBFS

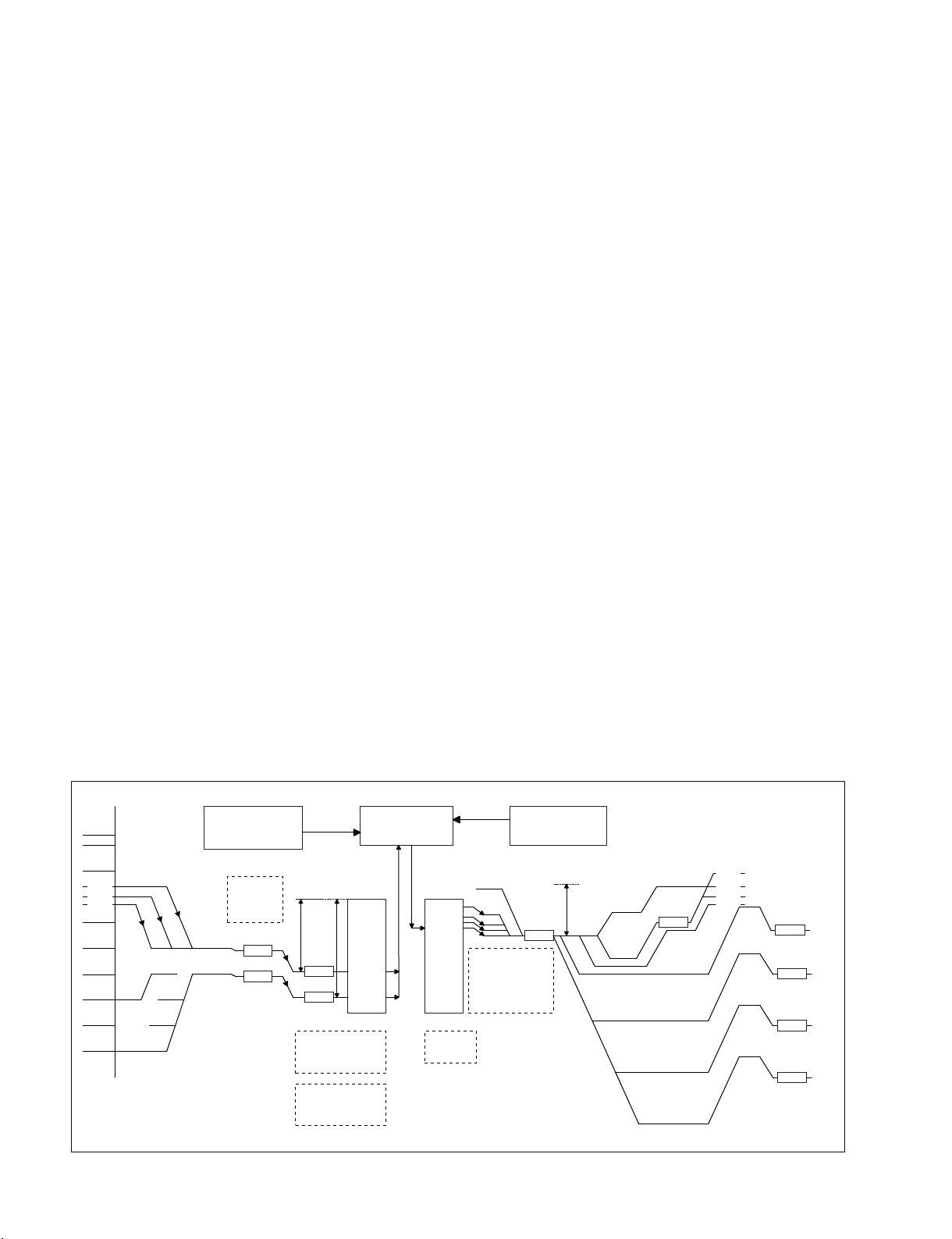

1-2-7. Audio DSP Operation Processing

Main functions

1. AUTO-AMP: Two to four types of characteristics can

be selected depending on each headroom.

_4dBu

_8dBu

_10dBu

_12dBu

AK4382A

24bit

D/A

AK-4382A

Max Output;

±

2.75Vp-p

_20dBFS

ALARM-TONE

CPU_OUT:2.7dBu

_3dB

HeadRoom

_12dB:ATT 8dB

_16dB:ATT 4dB

_18dB:ATT 2dB

_20dB:ATT 0dB

(Controled ATT of DAC)

AES/EBU;

Reference OUT : _20dBFS

+5dBu

_17.5dB

Tp-500

_15dBu

20dB

_33dB

_15dB

+9dB

_9dB

_12dB

VR_Max:_30dBu

VR_Max:_48dBu

ALARM_VR(Min):Faint_On

Tp-501

_10dBu

+14dB

ALARM_VR(Min):Faint_Off

+9dBu

+4dBu

+0dBu

_3dBu

+26dB

+26dB

+26dB

+26dB

_4dBu

_22dBu

XLR-OUT

(IN : +24dBu, Limiter-ON)

(IN : +4dBu, AGC-ON)

_13dBu

HeadPhone

(8Z loded)

_31dBu

ALARM (Max)

_62dBu

ALARM (Min)

Faint : On

_90dBu

ALARM (Min)

Faint : Off

1-14

Audio Level Chart

PDW-700/V1 (E)

Page 25

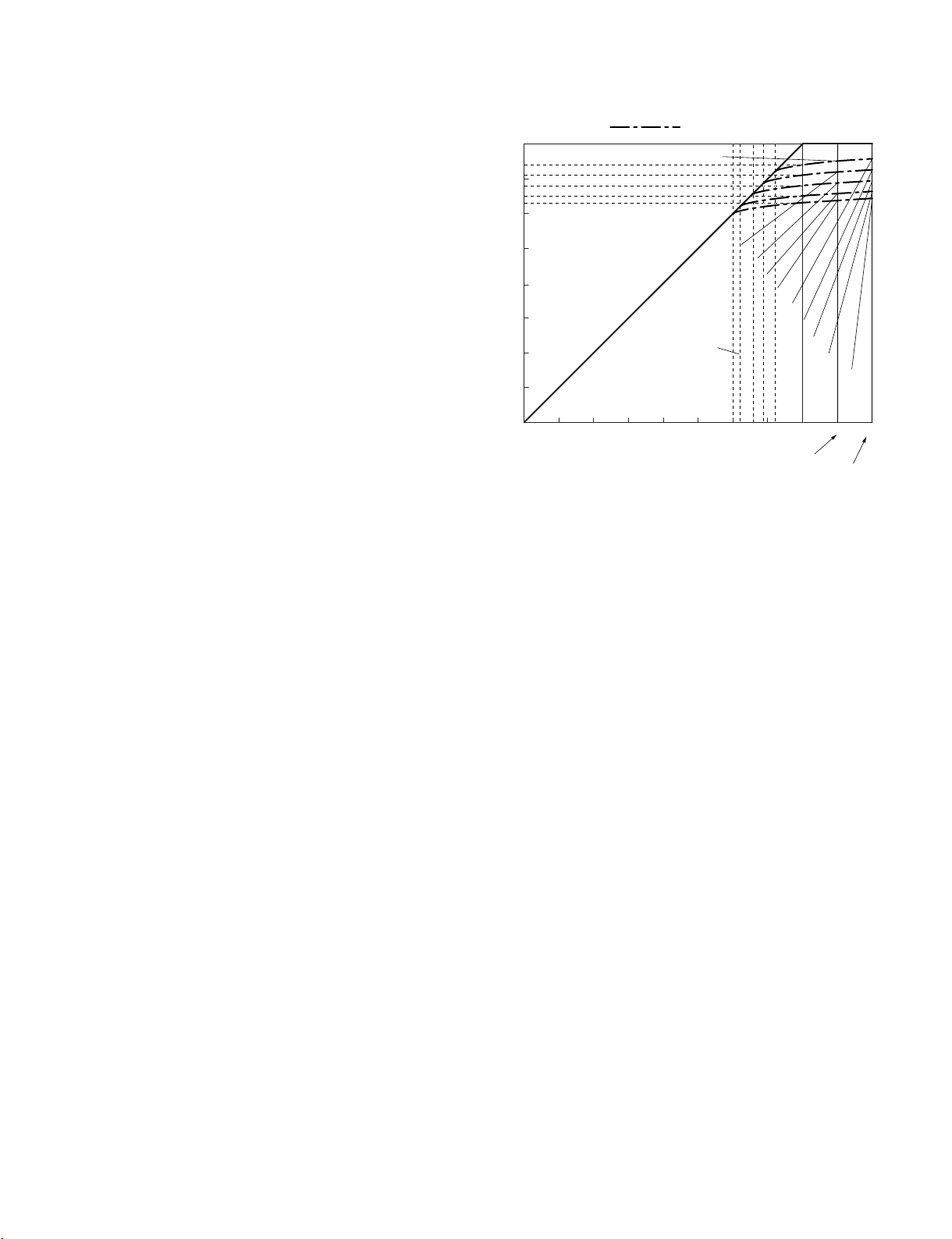

AGC/LIM SPECIFICATION

0

_

10

_

20

_

40

_

30

_

50

_

60

_

70

0 +10 +20

_

10

_

20

_

30

_

40

_

50

_

60

_

70

_6dBFS

_9dBFS

_15dBF S

_12dBF S

_17dBF S

INPUT [dBFS]

OUTOPUT [dBFS]

_8.1

dBFS

_11.4

dBFS

_14.6

dBFS

_17.9

dBFS

_20.0

dBFS

Output level at 0dBFS input.

Subthreshold level

_5.4dBFS max

_8.4dBFS max

_11.4dBFS max

_14.4dBFS max

_16.4dBFS max

_4.8dBFS max

_7.8dBFS max

_10.8dBFS max

_13.8dBFS max

_15.8dBFS max

0dBFS

Features of the AGC/LIM OFF.

: Features in common of the MIC/LINE input.

Max input level

of the LINE input.

Max input level

of the MIC input.

2. LIMITER characteristics: Two to four types of

characteristics can be selected depending on each

headroom.

3. OUT_PUT_LIMITER characteristics: Performs

LIMITER processing on the PB and EE_OUT. ON/

OFF.

4. Turns on and off the HPF (67 Hz) and LPF (15 KHz;

_24 dB). (Runs automatically during front

microphone selection)

5. Performs gain control when CH1 and CH2 are on

MANUAL status. (VR-MAX: +12 dB)

6. CH3 and CH4 turn on and off the AUTO operation.

7. Internal SG: Four types of 1 KHz/_12, _16, _18,

_20 dBFS.

8. Recording error correction: +0 to _2 dB (started from

the terminal)

9. Playback error correction: +0 to _2 dB (started from

the terminal)

10. INPUT delay amount: Performs delay processing to

match the VIDEO and AUDIO phases of each CH.

Description of each part

1. DIGITAL AUTO_AMP Processing

Selects the AUTO level from the menu.

AU AUTO SPEC : _6 dB/_9 dB/_12 dB/_15 dB/_17 dB

_6 dB : Linear operation until approx. _9 dBFS. Approx.

_6 dBFS at Max.

_9 dB : Linear operation until approx. _12 dBFS.

Approx. _9 dBFS at Max.

_12 dB : Linear operation until approx. _15 dBFS.

Approx. _12 dBFS at Max.

_15 dB : Linear operation until approx. _18 dBFS.

Approx. _15 dBFS at Max.

_17 dB : Linear operation until approx. _20 dBFS.

Approx. _17 dBFS at Max.

2. DIGITAL In Put LIMITER characteristics (only

during MANUAL)

Selects the LIMITER level from the menu.

AU AUTO SPEC : _6 dB/_9 dB /_12 dB/_15 dB/_17 dB

_6 dB : Linear operation until approx. _9 dBFS. Approx.

_9 dB : Linear operation until approx. _12 dBFS.

_12 dB : Linear operation until approx. _15 dBFS.

_15 dB : Linear operation until approx. _18 dBFS.

_17 dB : Linear operation until approx. _20 dBFS.

PDW-700/V1 (E)

_6 dBFS at Max.

Approx. _9 dBFS at Max.

Approx. _12 dBFS at Max.

Approx. _15 dBFS at Max.

Approx. _17 dBFS at Max.

3. DIGITAL Out Put LIMITER characteristics

Turn the LIMITER ON/OFF from the menu.

ON : Linear operation until approx. _12 dBFS, approx.

_11 dBFS (at Max.)

OFF : Turn off LIMITER at 0 dBFS.

4. Gain control during MANUAL

The A/D converted VR value is converted into a DSP

multiplication value at FP_CPU and synchronized with the

VIDEO1 frame, then handed over to the CPU to set in the

register of the DSP. The maximum variable for volume is

+12 dB. (_∞ to +12 dB)

5. Recording error correction

For error correction on the A/D converter for audio, the

multiplication value is corrected in the range +0 to _2 dB.

Starts from the terminal with the standard signal level

applied. (fully automatic)

6. Playback error correction

For error correction on the D/A converter for audio, the

multiplication value is corrected in the range +0 to _2 dB.

The correction is performed after the playback error

correction is completed. Starts from the terminal. (semiautomatic)

The internal SG is used as the standard signal, and the

inside panel for each LEVEL_VR is turned and fine-tuned.

1-15

Page 26

1-2-8. Optical Drive System

Recording System

Recording data sent from the DVP-45 board through the

ATA bus (Ultra ATA33) is sent to the Blu-ray Disc

Controller (BDC) IC300 on the DR-606 board.

The BDC performs signal processing to conform to

recording format, such as ATA interface, ECC coding and

17PP (Parity Preserve/Prohibit RMTR) modulation.

The recording data is converted to multi-pulse in the BDC,

and the multi-pulse data is sent through the flexible card

wire to the optical block to be written into the disc.

Playback System

• Data Playback System

The RF signal played back from the disc is sent from the

optical block to the Front End Processor (FEP) IC200 on

the DR-606 board where equalizing and asymmetry

correction are performed after the RF signal passes

through the AGC. After A/D conversion by the read

clock played back in the PLL, the signal is sent to the

BDC IC300.

In the BDC, the signal passes through the adaptive

digital filter, and Viterbi demodulation, 17PP demodulation, and ECC decoding are applied to the signal. Then

the signal is sent through the ATA bus to the DVP-45

board as played back data.

The tilt actuator is controlled for its angle against the

disc to be optimum based on the tilt adjustment result for

the jitter of the playback signal to be minimum and the

output of the angular velocity sensor.

The SA actuator position is controlled for the spherical

aberration to be optimum at the start-up adjustment when

the disc is inserted. The SA actuator for the double layer

disc is controlled to the optimum position every time to

jump the layer.

• Seek Motor

The seek motor controls the position of the optical block

so that the track to be recorded or played back is kept

within the object lens driving range.

• ND Filter

The transmission factor of the ND filter is selectable to

reduce the laser noise that occurs when the read power

light is emitted for the single layer disc.

• Spindle Motor