Sony LCX027AKB Datasheet

– 1 –

E98X21-PS

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

1.4cm (0.55-inch) NTSC/PAL Color LCD Panel

Description

The LCX027AKB is a 1.4cm diagonal active matrix

TFT-LCD panel addressed by polycrystalline silicon

super thin film transistors with built-in peripheral

driving circuit. This panel provides full-color

representation in NTSC/PAL mode. RGB dots are

arranged in a delta pattern featuring high picture

quality of no fixed color patterns, which is inherent in

vertical stripes and mosaic pattern arrangements.

Features

• The number of active dots: 180,000 (0.55-inch; 1.397cm in diagonal)

• Horizontal resolution: 400 TV lines

• High optical transmittance: 4.2% (typ.)

• High contrast ratio with normally white mode: 200 (typ.)

• Built-in H and V drivers (built-in input level conversion circuit, TTL drive possible)

• High quality picture representation with RGB delta arranged color filters

• Full-color representation

• NTSC/PAL compatible

• Right/left inverse display function

• 4:3 and 16:9 aspect switching function

Element Structure

• Dots

Total dots : 827 (H) × 228 (V) = 188,556

Active dots: 800 (H) × 225 (V) = 180,000

• Built-in peripheral driver using polycrystalline silicon super thin film transistors.

Applications

• Viewfinders

• Super compact liquid crystal monitors etc.

LCX027AKB

For the availability of this product, please contact the sales office.

– 2 –

LCX027AKB

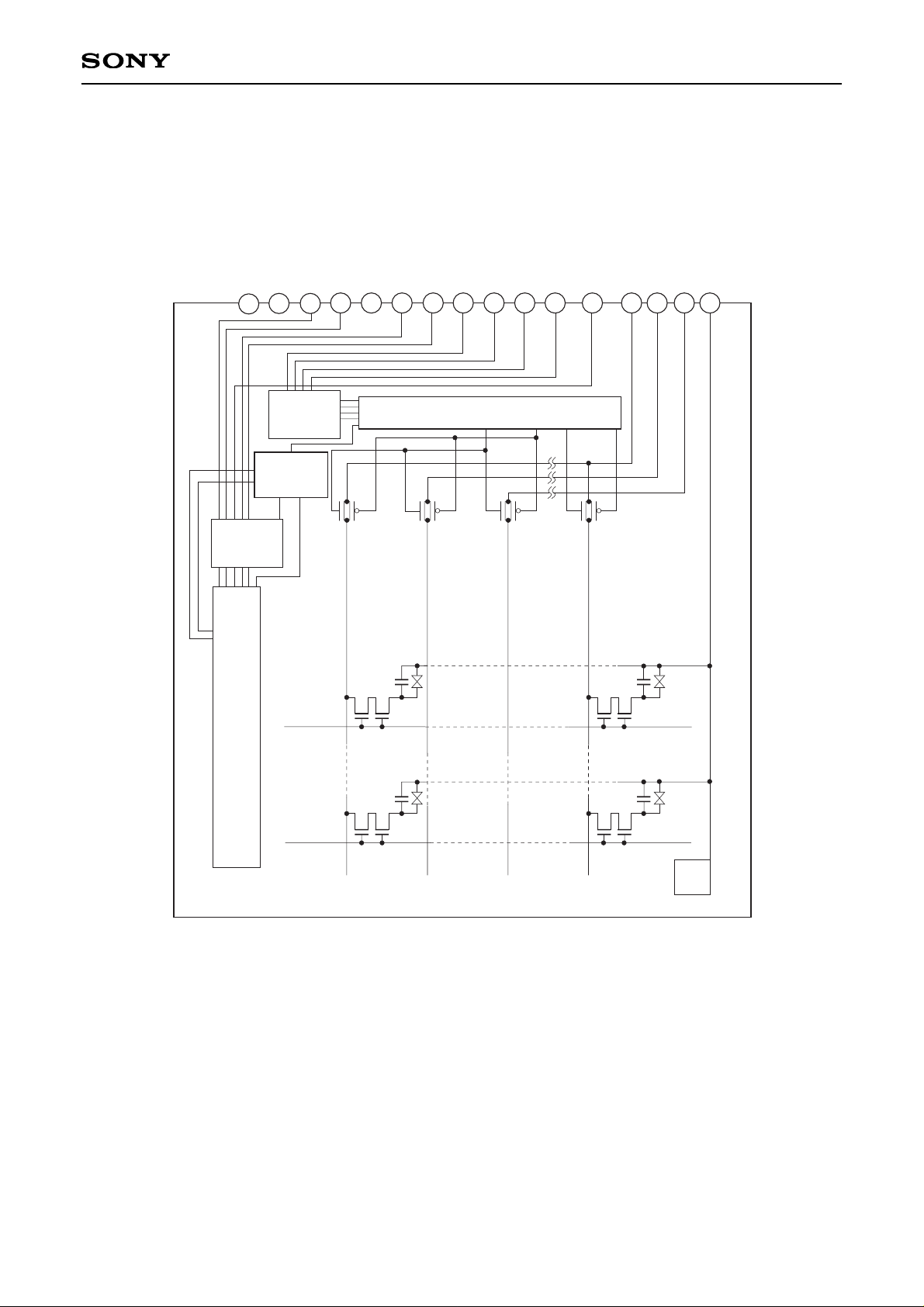

Block Diagram

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

H Shift Register

V Level

Conversion

Circuit

V Shift Register

CS LC

COM

Pad

V

DD

V

SS

VST

VCK

(NC)

EN

CLR

RGT

HST

HCK2

HCK1

BLK

BLUE

RED

GREEN

COM

Top/bottom

BLK Control

Circuit

H Level

Conversion

Circuit

– 3 –

LCX027AKB

Absolute Maximum Ratings (VSS = 0V)

• H and V driver supply voltages VDD –1.0 to +17 V

• H driver input pin voltage HST, HCK1, HCK2 –1.0 to +17 V

RGT

• V driver input pin voltage VST, VCK –1.0 to +17 V

CLR, EN, BLK

• Video signal input pin voltage GREEN, RED, BLUE –1.0 to +15 V

• Operating temperature Topr –10 to +70 °C

• Storage temperature Tstg –30 to +85 °C

Operating Conditions (VSS = 0V)

Supply voltage

VDD 11.4 to 12.6 V

Input pulse voltage (Vp-p of all input pins except video signal input pins)

Vin 2.6V (more than)

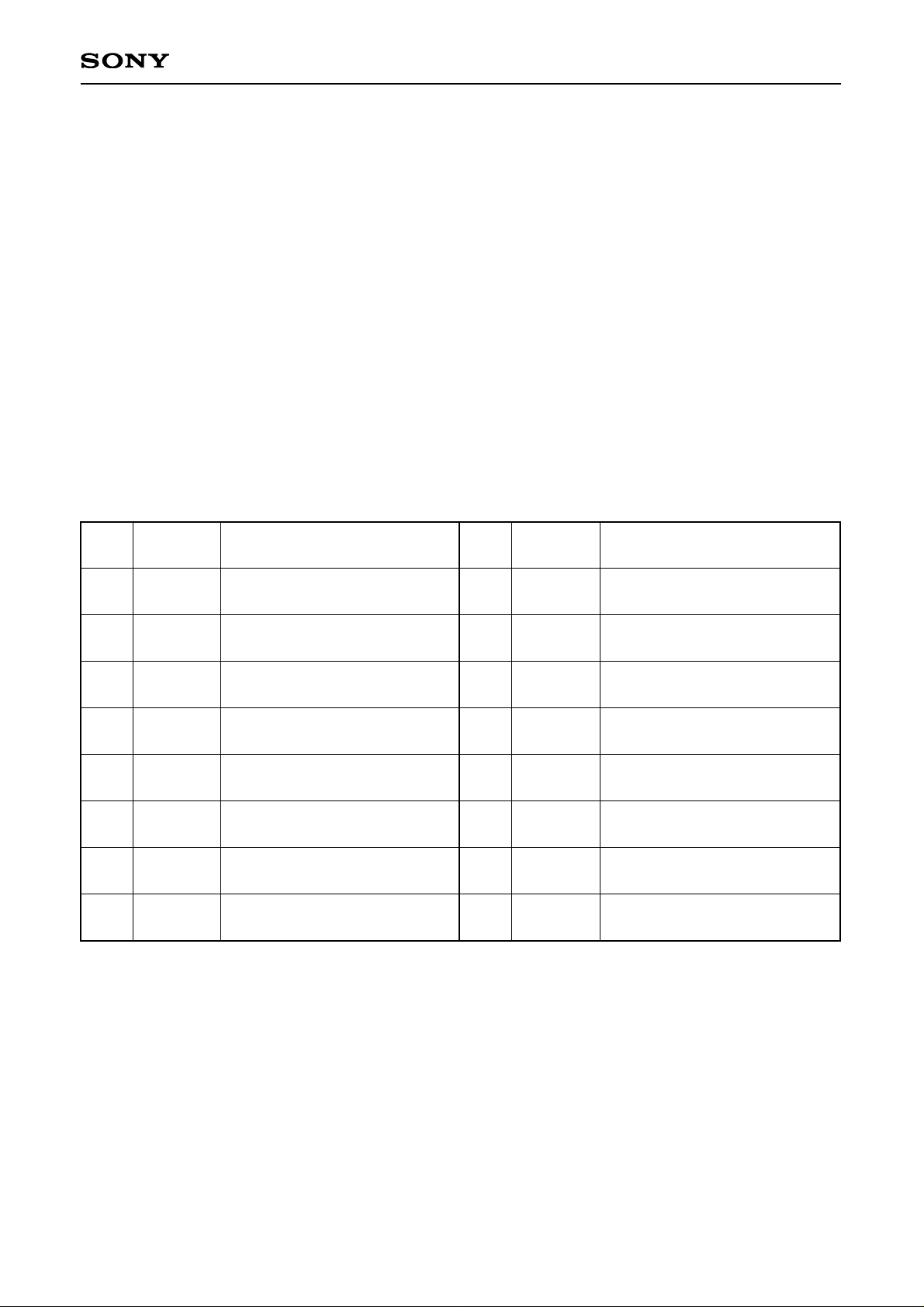

Pin Description

Pin

No.

1

2

3

4

5

6

7

8

COM

GREEN

RED

BLUE

BLK

HCK1

HCK2

HST

Common voltage of panel

Video signal (G) to panel

Video signal (R) to panel

Video signal (B) to panel

Top/bottom block display pulse

Clock pulse for H shift register

drive

Clock pulse for H shift register

drive

Start pulse for H shift register

drive

9

10

11

(12)

13

14

15

16

RGT

CLR

EN

(NC)

VCK

VST

Vss

VDD

Drive direction pulse for H shift

register (H: normal, L: reverse)

Improvement pulse for

uniformity

Enable pulse for gate selection

Not connected

Clock pulse for V shift register

drive

Start pulse for V shift register

drive

GND (H, V drivers)

Power supply for H and V drivers

Symbol Description

Pin

No.

Symbol Description

– 4 –

LCX027AKB

Input Equivalent Circuit

To prevent static charges, protective diodes are provided for each pin except the power supply. In addition,

protective resistors are added to all pins except video signal input. All pins are connected to Vss with a high

resistance of 1MΩ (typ.). The equivalent circuit of each input pin is shown below: (The resistor value: typ.)

(1) Video signal input

Input

V

DD

From H driver

Signal line

1MΩ

(2) HCK1, HCK2

VDD

250Ω

250Ω

250Ω

250Ω

Level conversion

circuit (2-phase

input)

HCK1

HCK2

1MΩ

1MΩ

(3) HST

Level conversion

circuit (singlephase input)

250Ω250Ω

V

DD

Input

1MΩ

(4) RGT, VST, CLR, EN, VCK, BLK

Level conversion

circuit (singlephase input)

2.5kΩ

2.5kΩ

V

DD

Input

1MΩ

(5) COM

Input

1MΩ

LC

VDD

– 5 –

LCX027AKB

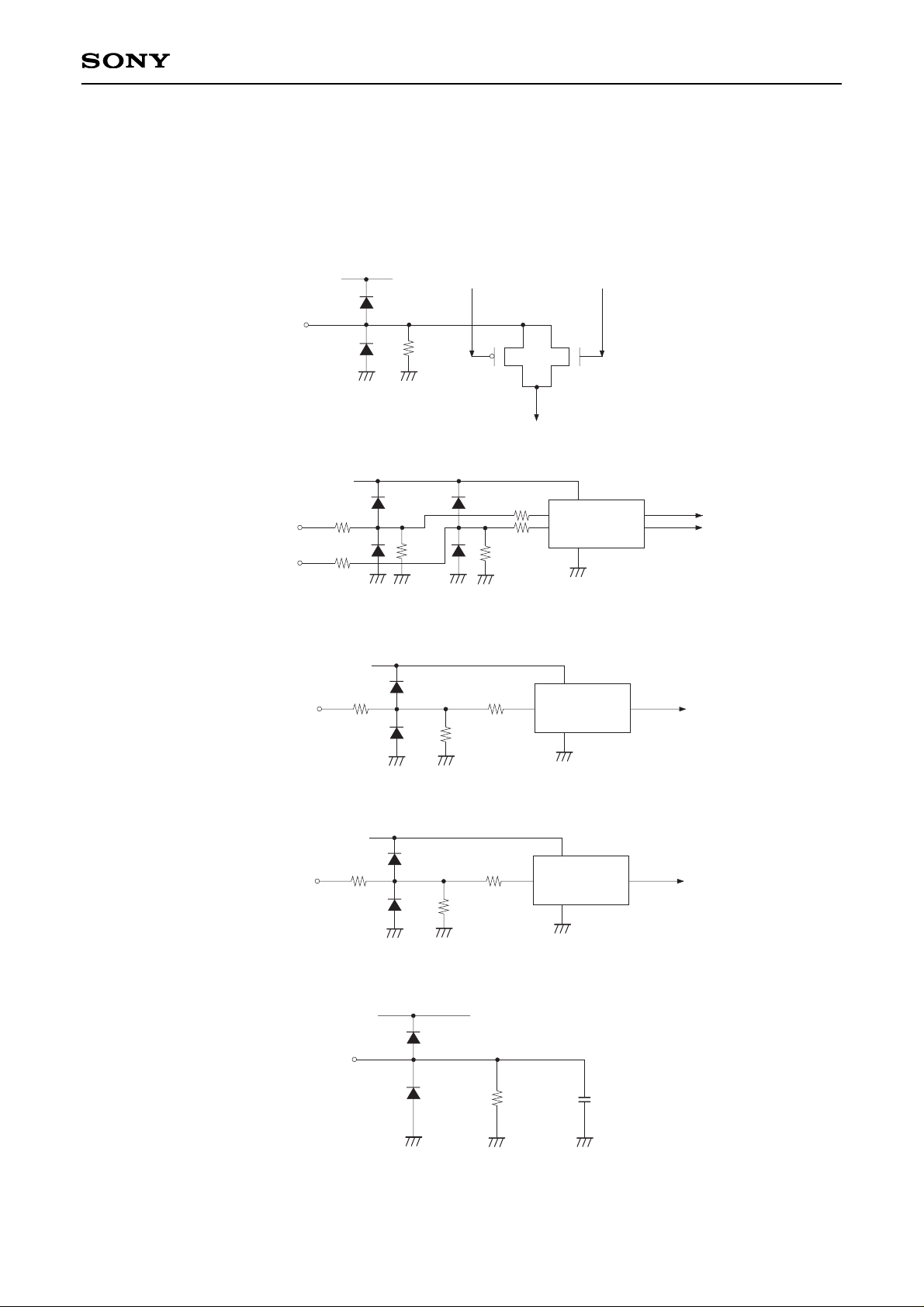

Level Conversion Circuit

The LCX027AKB has a built-in level conversion circuit in the clock input unit located inside the panel. The

circuit voltage is stepped up to VDD inside the panel. This level conversion circuit meets the specifications of a

3.0V power supply of the externally-driven IC.

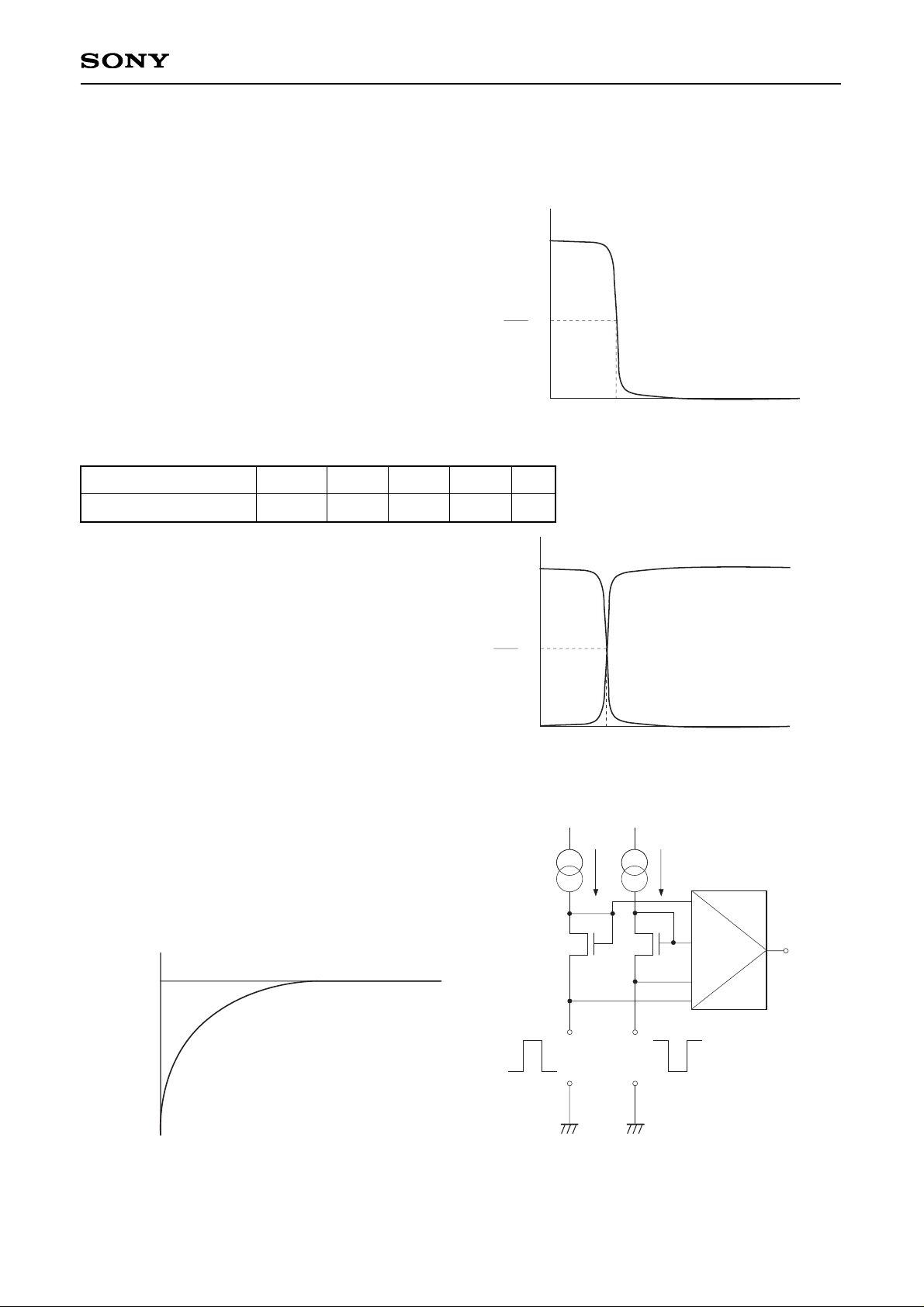

1. I/O characteristics of level conversion circuit

(For a single-phase input unit)

An example of the I/O voltage characteristics of a

level conversion circuit is shown in the figure to the

right. The input voltage value that becomes half the

output voltage (after voltage conversion) is defined

as Vth.

The Vth value varies depending on the VDD voltage.

The Vth values under standard conditions are

indicated in the table below. (HST, VST, EN, CLR,

RGT, VCK and BLK in the case of a single-phase input)

VDD = 12.0V

VDD

2

VDD

Vth

Input voltage [V]

Example of single-phase

I/O characteristics

Output voltage (inside panel)

Item

Vth voltage of circuit Vth 0.35 1.50 2.60 V

Symbol Min. Typ. Max. Unit

(For a differential input unit)

An example of I/O voltage characteristics of a level

conversion circuit for a differential input is shown in

the figure to the right. Although the characteristics,

including those of the Vth voltage, are basically the

same as those for a single-phased input, the twophased input phase is defined. (Refer to clock

timing conditions.)

VDD

2

VDD

Vth

Input voltage [V]

Example of differential I/O

characteristics

Output voltage (inside panel)

2. Current characteristics at the input pin of level conversion circuit

A slight pull-in current is generated at the input pin

of the level conversion circuit. (The equivalent

circuit is shown to the right.) The current volume

increases as the voltage at the input pin decreases,

and is maximized when the pin is grounded. (Refer

to electrical characteristics.)

VDD

output

HCK1

input

HCK2

input

Level conversion equivalent circuit

0

0

Max. value

Input pin voltage [V]

10

Pull-in current characteristics at the input pin

Input pin current

– 6 –

LCX027AKB

Input Signals

1. Input signal voltage conditions (VSS = 0V, VDD = 11.4 to 12.6V)

Item

H driver input voltage

(HST, HCK1, HCK2, RGT)

(Low)

(High)

(Low)

(High)

VHIL

VHIH

VVIL

VVIH

VVC

VCOM

–0.35

2.6

–0.35

2.6

5.8

VVC – 0.3

0.0

3.0

0.0

3.0

6.0

VVC – 0.15

0.35

3.5

0.35

3.5

6.2

VVC

V

V

V

V

V

V

V driver input voltage

(VST, VCK1, VCK2, CLR, EN)

Video signal center voltage

Common voltage of panel

Symbol Min. Typ. Max. Unit

Note) Video signal shall be symmetrical to VVC.

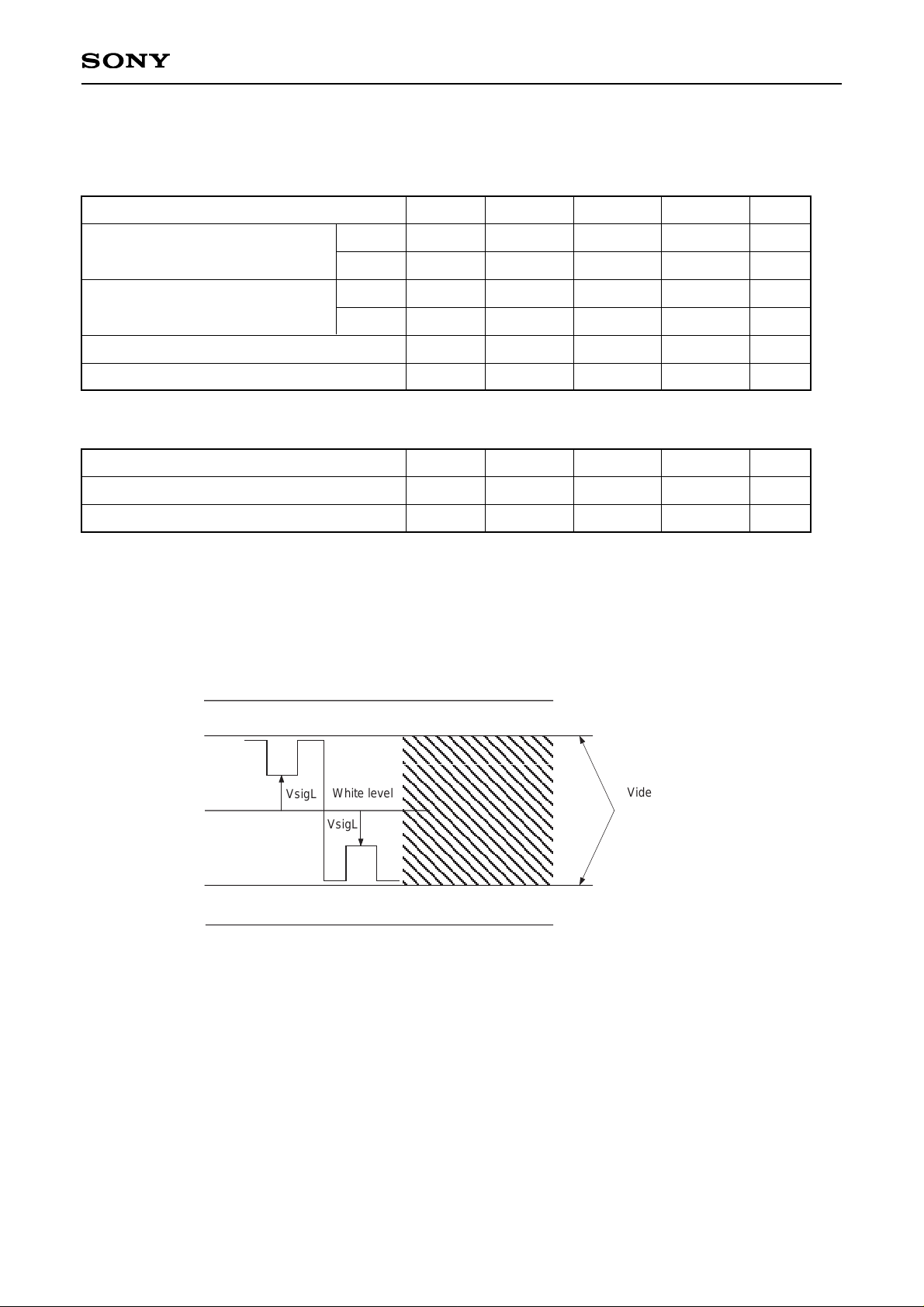

Supplement) Video signal input range is set within the range shown below for VDD and VSS.

Also, video signal white level is defined for VVC as shown below.

Item

Video signal input range

Video signal input white level

Vsig

VsigL

VSS + 1.3

0.5

VDD – 1.8 V

V

Symbol Min. Typ. Max. Unit

A

A

A

VsigL

White level

VsigL

Video signal input range

Max. VDD – 1.8 [V]

Min. VSS + 1.3 [V]

V

DD

VDD – 1.8

VVC

V

SS + 1.3

V

SS

AAA

AAA

AAA

– 7 –

LCX027AKB

Hst rise time

Hst fall time

Hst data set-up time

Hst data hold time

Hckn∗2rise time

Hckn∗2fall time

Hck1 fall to Hck2 rise time

Hck1 rise to Hck2 fall time

Clr rise time

Clr fall time

Clr pulse width

Clr fall to Hst rise time

Vck rise/fall to Clr fall time

Vst rise time

Vst fall time

Vst data set-up time

Vst data hold time

Vck rise time

Vck fall time

En rise time

En fall time

Vck rise/fall to En fall time

BLK rise time

BLK fall time

BLK pulse width

BLK fall to Clr fall time

trHst

tfHst

tdHst

thHst

trHckn

tfHckn

to1Hck

to2Hck

trClr

tfClr

twClr

toHst

thVck

trVst

tfVst

tdVst

thVst

trVck

tfVck

trEn

tfEn

tdVck

trBlk

tfBlk

twBlk

toClr

–100

–200

–15

–15

3400

1850

400

–50

–50

–100

600

60

–120

0

0

3500

1950

500

32

–32

0

1.0

700

30

30

100

–50

30

30

15

15

100

100

3600

2050

600

100

100

50

–20

100

100

100

100

100

100

100

800

ns

µs

ns

ms

ns

Item Symbol Min. Typ. Max. Unit

HST

HCK

CLR

VST

VCK

EN

BLK

∗3

∗2

Hckn means Hck1, Hck2. (fHckn = 2.75MHz, fVckn = 7.865kHz)

∗3

BLK pulse is used only for 16:9 mode. For 4:3 mode, connect to VSS.

2. Clock timing conditions (Ta = 25°C, Input voltage = 3.0V, VDD = 12.0V)

Loading...

Loading...