Page 1

CDX-C4900R/C5000R/C5000RX

SERVICE MANUAL

Ver 1.2 2001. 05

Photo: CDX-C5000R

• The tuner and CD sections have no adjustments.

SPECIFICATIONS

AEP Model

UK Model

Model Name Using Similar Mechanism NEW

CD Drive Mechanism Type MG-383Z-121//Q

Optical Pick-up Name KSS-720A

CD player section

Signal-to-noise ratio 90 dB

Frequency response 10 – 20,000 Hz

Wow and flutter Below measurable limit

Tuner section

FM

Tuning range 87.5 – 108.0 MHz

Aerial terminal External aerial connector

Intermediate frequency 10.7 MHz/450 kHz

Usable sensitivity 8 dBf

Selectivity 75 dB at 400 kHz

Signal-to-noise ratio 66 dB (stereo),

72 dB (mono)

Harmonic distortion at 1 kHz

0.6% (stereo),

0.3% (mono)

Separation 35 dB at 1 kHz

Frequency response 30 – 15,000 Hz

MW/LW

Tuning range MW: 531 – 1,602 kHz

LW: 153 – 279 kHz

Aerial terminal External aerial connector

Intermediate frequency 10.7 MHz/450 kHz

Sensitivity MW: 30 µV

LW : 40 µV

Power amplifier section

Outputs Speaker outputs

(sure seal connectors)

Speaker impedance 4 – 8 ohms

Maximum power output 50 W × 4 (at 4 ohms)

General

Outputs Audio outputs

Tone controls Bass ±9 dB at 100 Hz

Power requirements 12 V DC car battery

Dimensions Approx. 178 × 50 × 183 mm

Mounting dimension Approx. 182 × 53 × 162 mm

Mass Approx. 1.2 kg

Supplied accessories Parts for installation and

*1

Equipped with front and rear outputs:

CDX-C5000RX/C5000R only

Equipped with rear outputs: CDX-C4900R

*2

CDX-C5000RX/C5000R only

Design and specifications are subject to change without

notice.

Power aerial relay control

lead

Power amplifier control

lead

Telephone ATT control

lead

Treble ±9 dB at 10 kHz

(negative ground)

(w/h/d)

(w/h/d)

connections (1 set)

Front panel case (1)

*1

*2

9-870-070-12

2001E0400-1

© 2001. 5

FM/MW/LW COMPACT DISC PLAYER

Sony Corporation

e Vehicle Company

Shinagawa Tec Service Manual Production Group

1

Page 2

Ver 1.1 2000. 08

SERVICE NOTES

This product is classified as a CLASS 1 LASER PRODUCT.

This label is located on the bottom of the

chassis.

This label is located on the drive unit's internal

chassis.

When replacing the chassis (T) of mechanism deck which have

the “CAUTION LABEL” attached, please be sure to put a new

CAUTION LABEL (3-223-913-11) to the chassis (T).

NOTES ON HANDLING THE OPTICAL PICK-UP BLOCK

OR BASE UNIT

The laser diode in the optical pick-up block may suffer electrostatic

breakdown because of the potential difference generated by the

charged electrostatic load, etc. on clothing and the human body.

During repair, pay attention to electrostatic breakdown and also use

the procedure in the printed matter which is included in the repair

parts.

The flexible board is easily damaged and should be handled with

care.

NOTES ON LASER DIODE EMISSION CHECK

The laser beam on this model is concentrated so as to be focused on

the disc reflective surface by the objective lens in the optical pickup block. Therefore, when checking the laser diode emission, observe from more than 30 cm away from the objective lens.

Notes on Chip Component Replacement

• Never reuse a disconnected chip component.

• Notice that the minus side of a tantalum capacitor may be dam-

aged by heat.

TABLE OF CONTENTS

1. GENERAL

Location of controls................................................................. 3

Getting Started......................................................................... 3

Setting the clock ...................................................................... 3

CD Player CD/MD unit ........................................................... 4

Radio ....................................................................................... 5

RDS ......................................................................................... 6

Other Functions ....................................................................... 7

Connections ............................................................................. 8

2. DISASSEMBLY

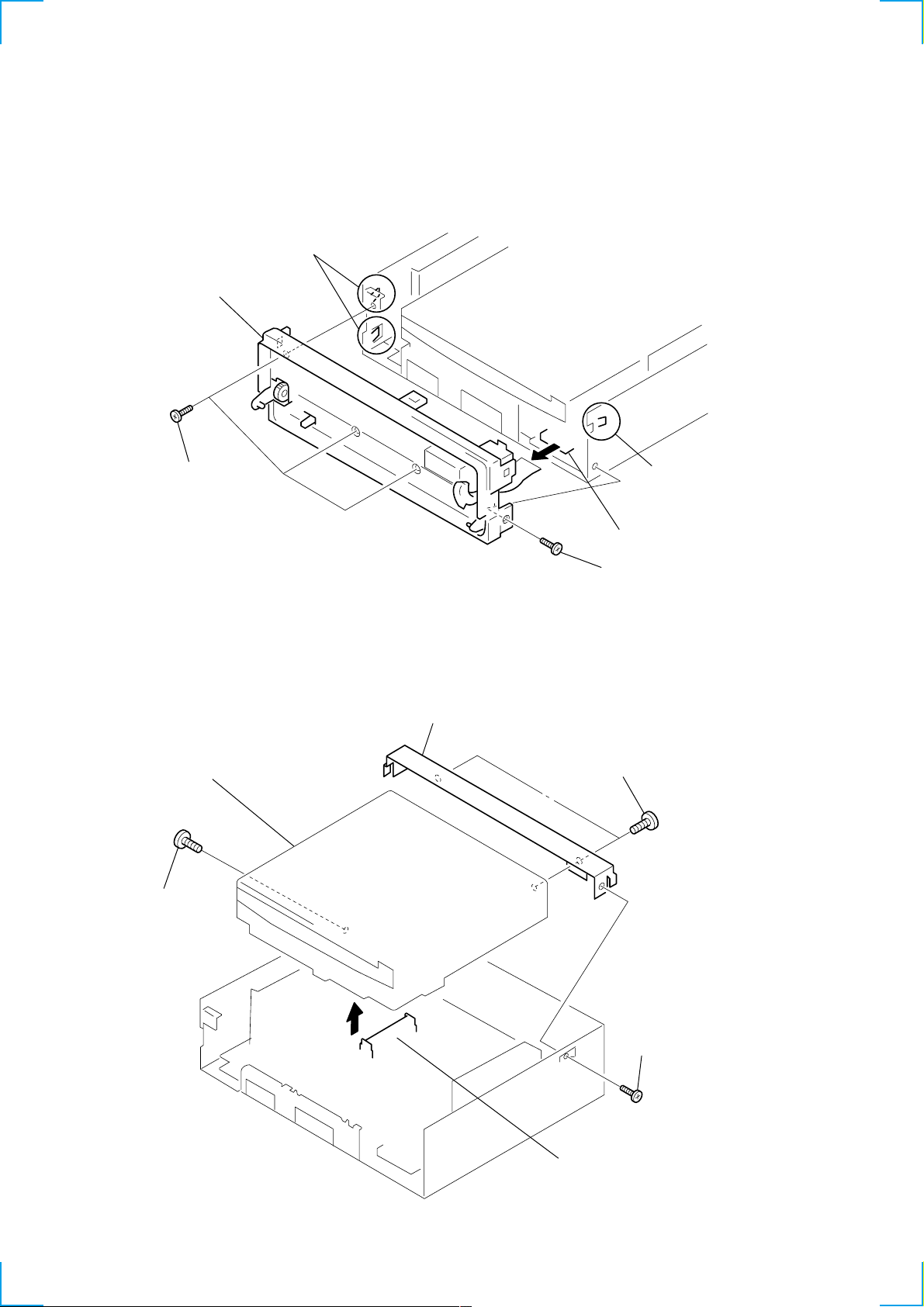

2-1. Sub Panel Assy.................................................................. 12

2-2. CD Mechanism Block ....................................................... 12

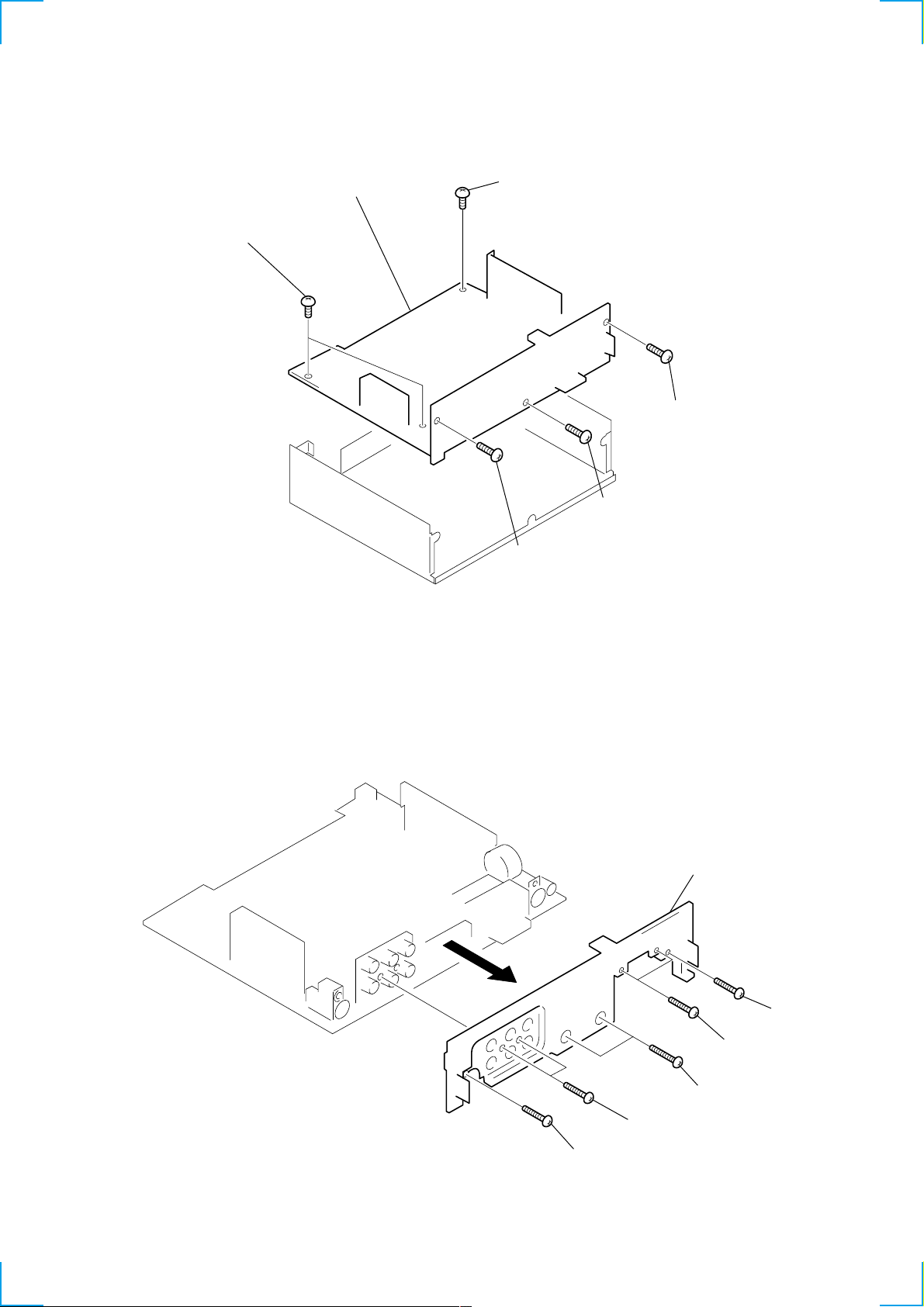

2-3. Main Board ....................................................................... 13

2-4. Heat Sink ........................................................................... 13

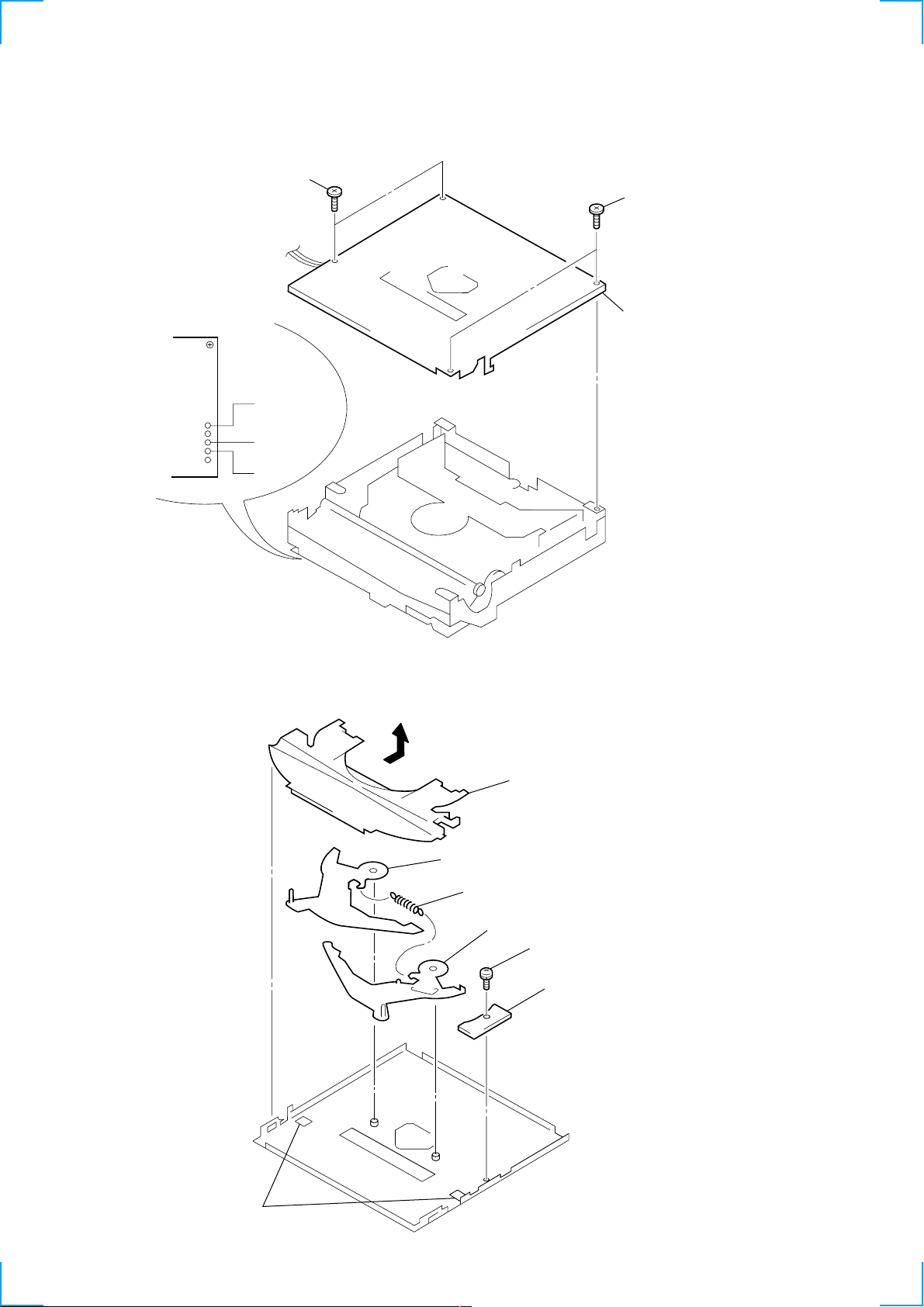

2-5. Chassis (T) Assy................................................................14

2-6. Lever Assy......................................................................... 14

2-7. Servo Board....................................................................... 15

2-8. ARM Roller Assy .............................................................. 15

2-9. Chassis (OP) Assy............................................................. 16

2-10. Optical Pick-up Block ....................................................... 16

3. DIAGRAMS

3-1. IC Pin Descriptions ........................................................... 17

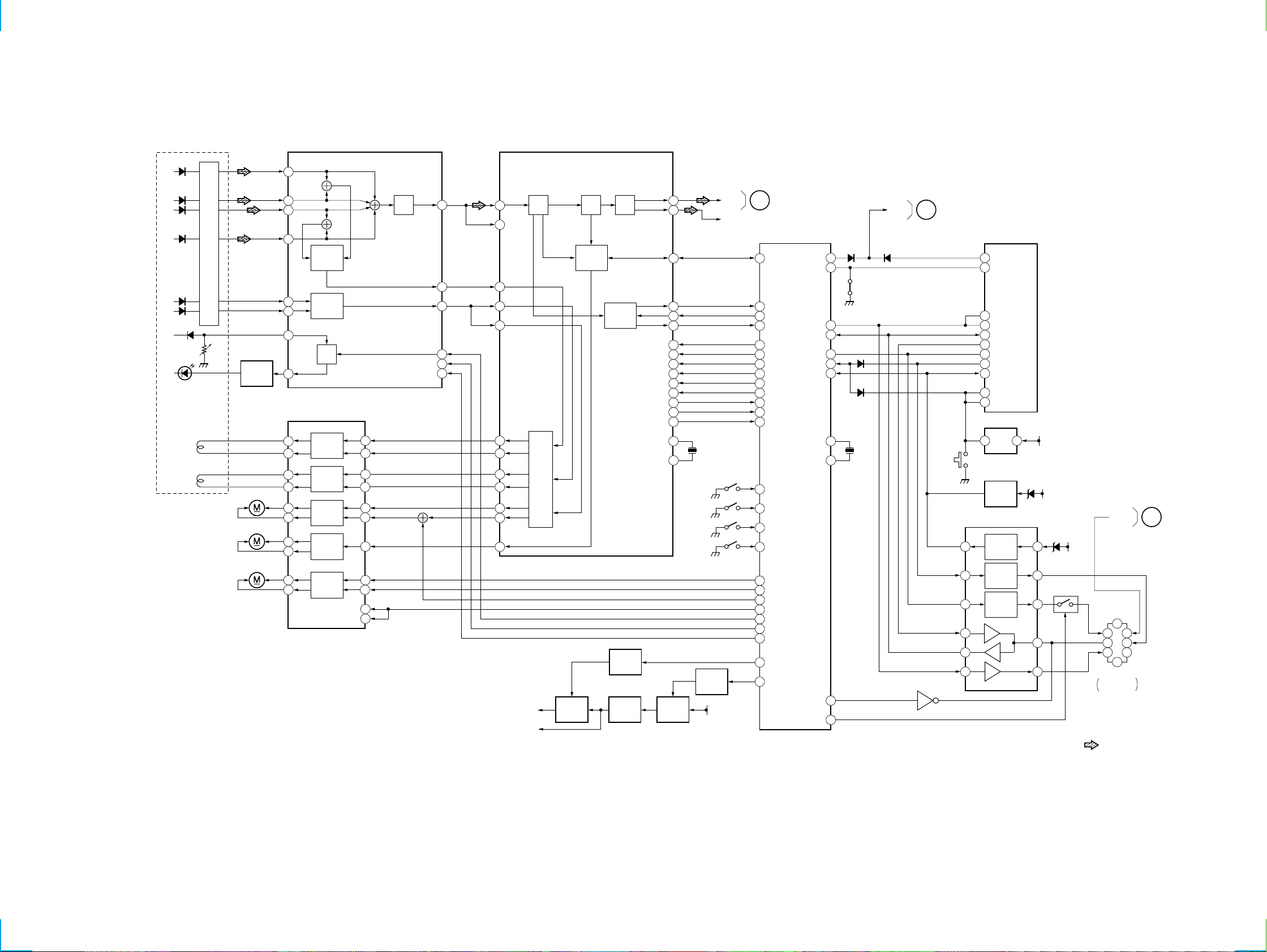

3-2. Block Diagram –CD Section–........................................... 23

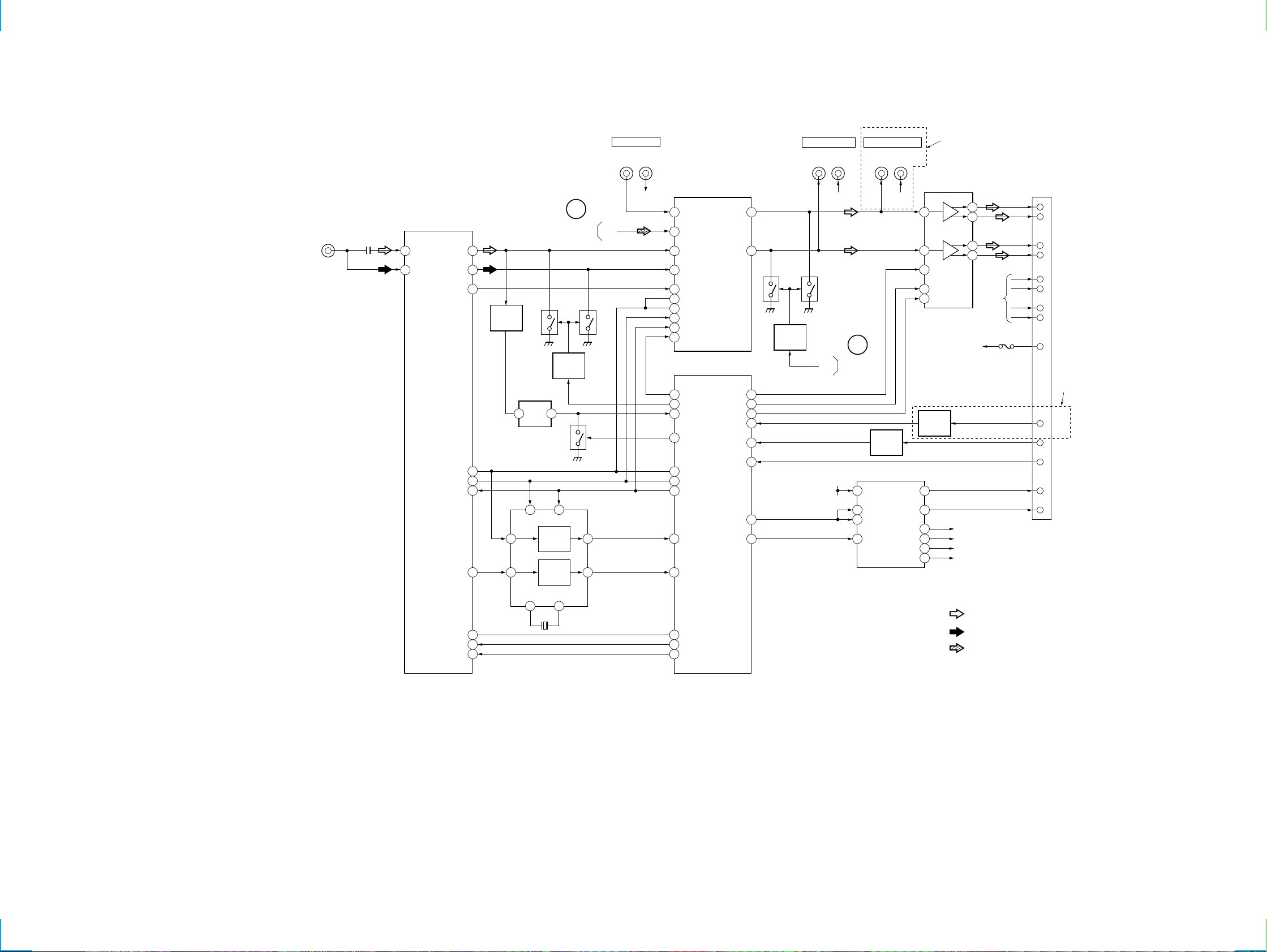

3-3. Block Diagram –Tuner Section–....................................... 24

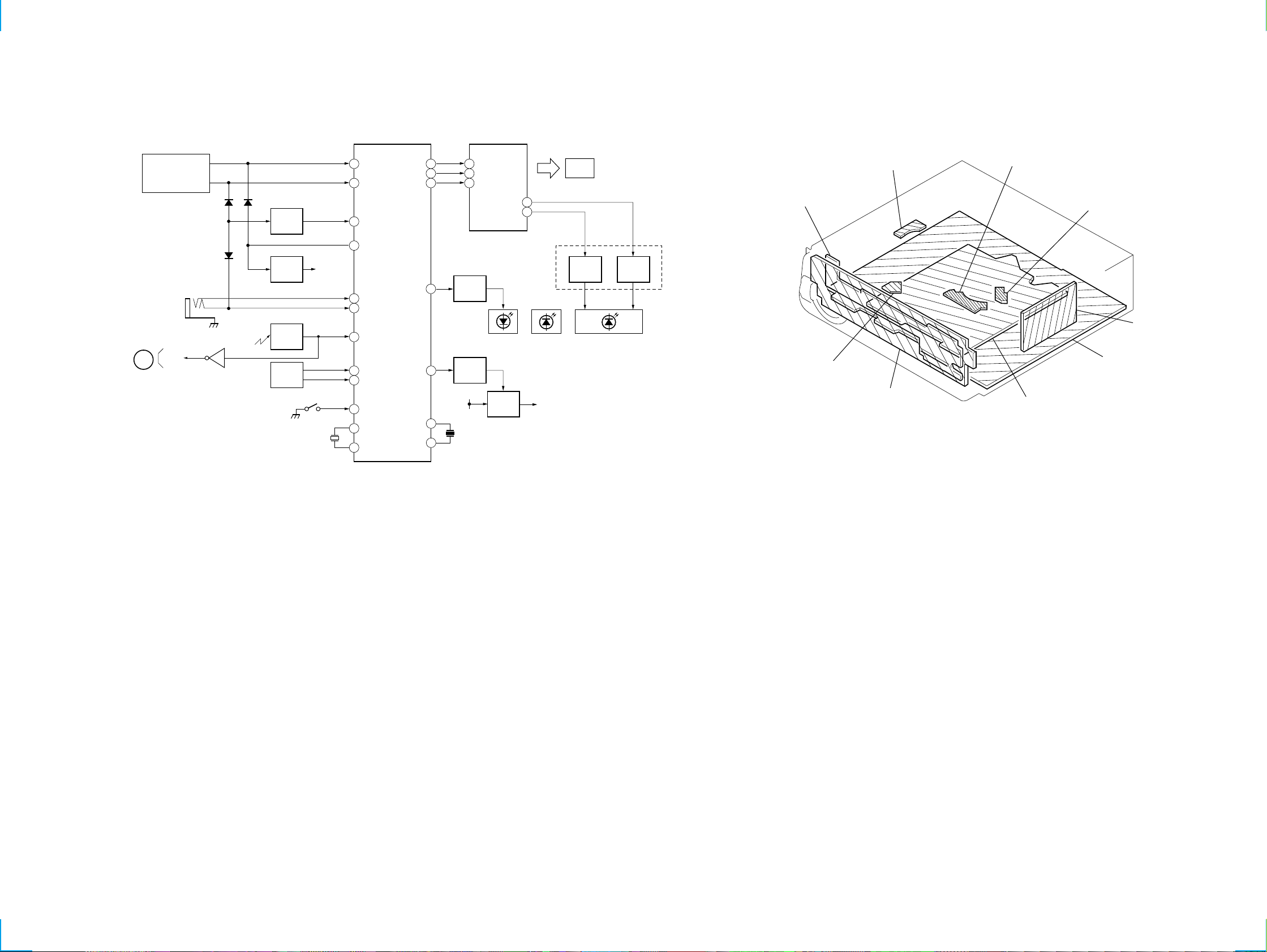

3-4. Block Diagram –Display Section–.................................... 25

3-5. Circuit Boards Location .................................................... 25

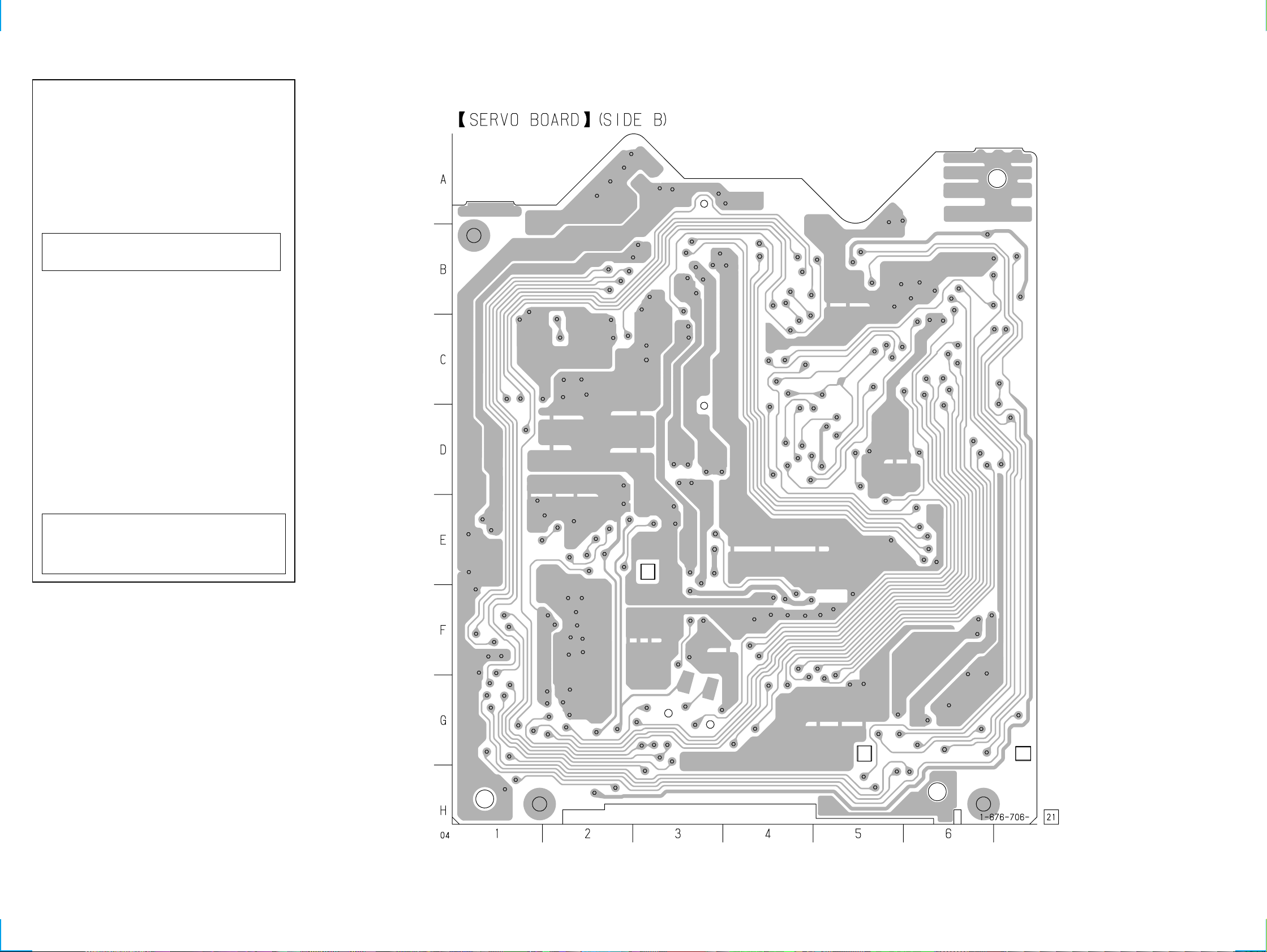

3-6. Printed Wiring Boards –CD Mechanism Section–............26

3-7. Schematic Diagram –CD Mechanism Section (1/2)– ....... 28

3-8. Schematic Diagram –CD Mechanism Section (2/2)– ....... 29

3-9. Printed Wiring Board –Main Section–.............................. 30

3-10. Schematic Diagram –Main Section (1/3)– ........................ 32

3-11. Schematic Diagram –Main Section (2/3)– ........................ 33

3-12. Schematic Diagram –Main Section (3/3)– ........................ 34

3-13. Schematic Diagram –Sub (CD) Section–.......................... 35

3-14. Printed Wiring Board –Sub (CD) Section–....................... 36

3-15. Printed Wiring Board –Key Section–................................ 37

3-16. Schematic Diagram –Key Section–................................... 38

4. EXPLODED VIEWS

4-1. Chassis Section ................................................................. 42

4-2. Front Panel Section ...........................................................43

4-3. CD Mechanism Section (1) ............................................... 44

4-4. CD Mechanism Section (2) ............................................... 45

4-5. CD Mechanism Section (3) ............................................... 46

SAFETY-RELATED COMPONENT WARNING!!

COMPONENTS IDENTIFIED BY MARK 0 OR DOTTED LINE

WITH MARK 0 ON THE SCHEMATIC DIAGRAMS AND IN

THE PARTS LIST ARE CRITICAL TO SAFE OPERATION.

REPLACE THESE COMPONENTS WITH SONY P ARTS WHOSE

PART NUMBERS APPEAR AS SHOWN IN THIS MANUAL OR

IN SUPPLEMENTS PUBLISHED BY SONY.

2

5. ELECTRICAL PARTS LIST ........................................ 47

Page 3

6

SECTION 2

DISASSEMBLY

Note : Follow the disassembly procedure in the numerical order given.

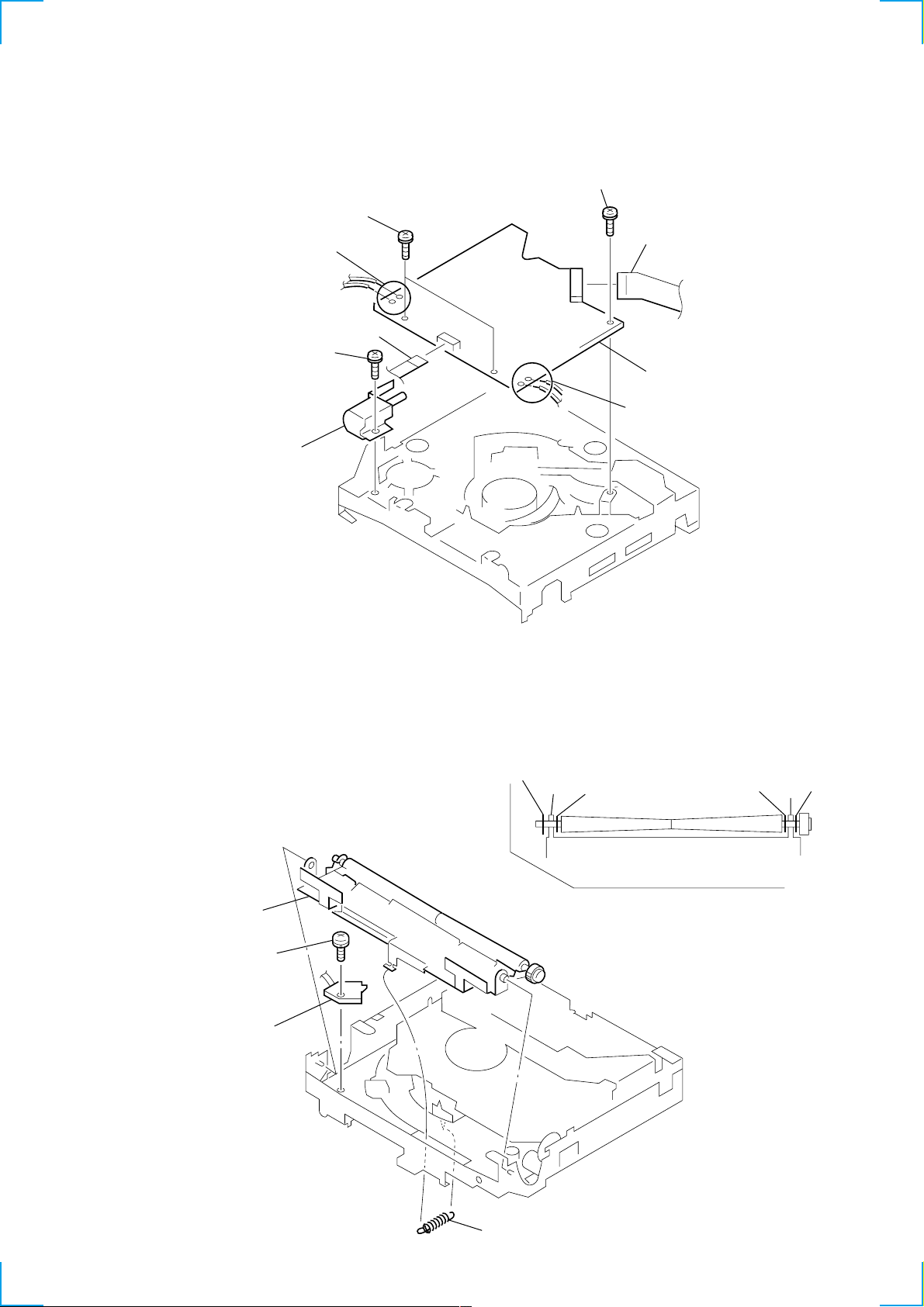

2-1. SUB PANEL ASSY

4 two claws

6 sub panel assy

2 PTT 2.6x8

2-2. CD MECHANISM BLOCK

5 CD mechanism block

2 PTT 2.6x6

3 claw

5 CN500

1 PTT 2.6x8

7 bracket (CD)

6 PTT 2.6x6

12

3

4 CN301

1 PTT 2.6x

Page 4

8

8

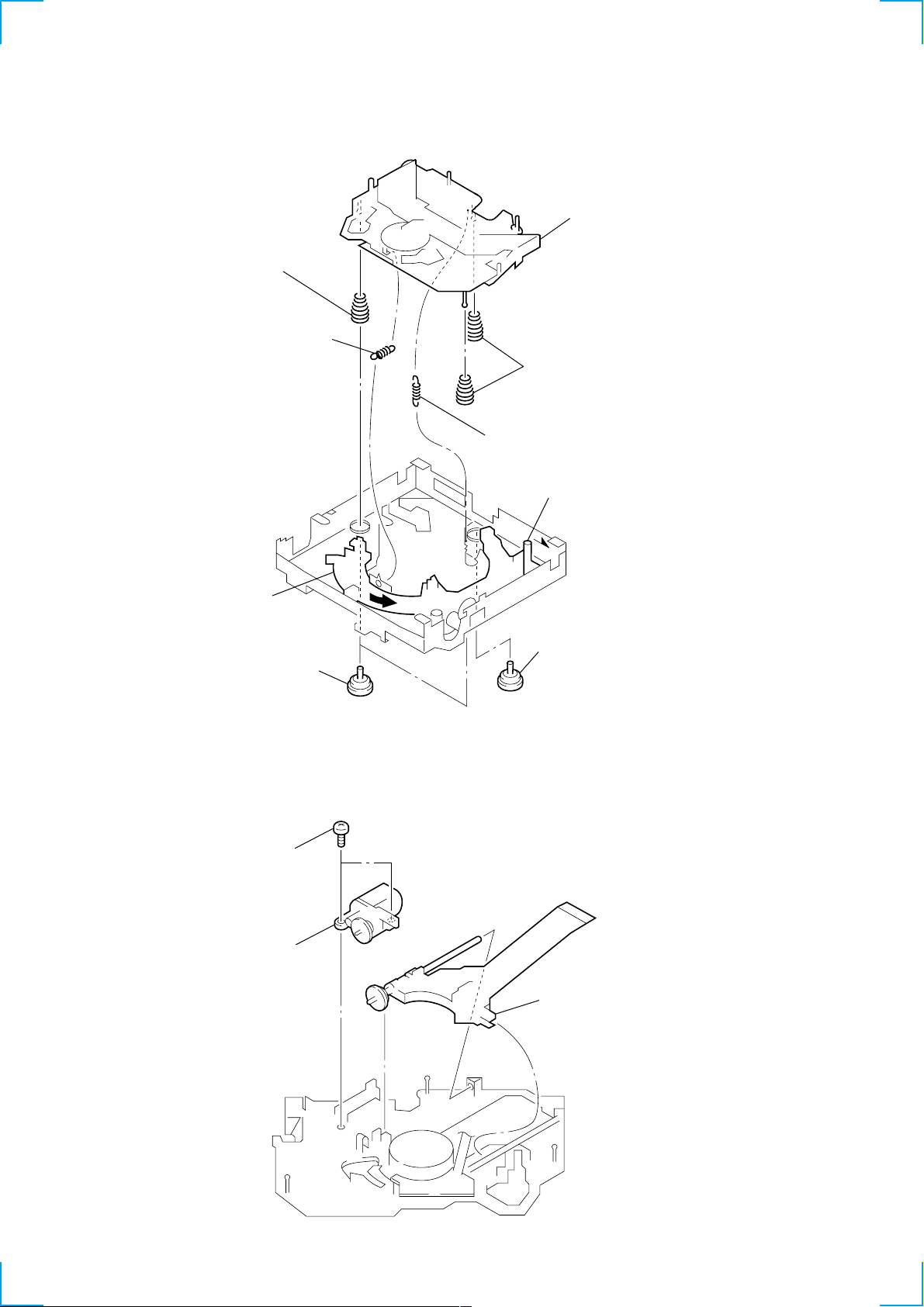

2-3. MAIN BOARD

6 MAIN board

5 ground point screws

(PTT 2.6x6)

4 ground point screw

(PTT 2.6x6)

3 PTT 2.6x

2 PTT 2.6x8

1 PTT 2.6x8

2-4. HEAT SINK

6 heat sink

5 PTT 2.6x

4 PTT 2.6x8

3 PTT 2.6x12

1 PTT 2.6x8

2 PTT 2.6x8

13

Page 5

2-5. CHASSIS (T) ASSY

2 P 2x3

3 P 2x3

2-6. LEVER ASSY

1 Unsolder the

lead wires.

4 chassis (T) assy

black

red

white

4 claws

5 guide (disc)

6 lever (R) assy

3 tension spring (LR)

7 lever (L) assy

1 PS 2x4

2 DISC IN SW board

14

Page 6

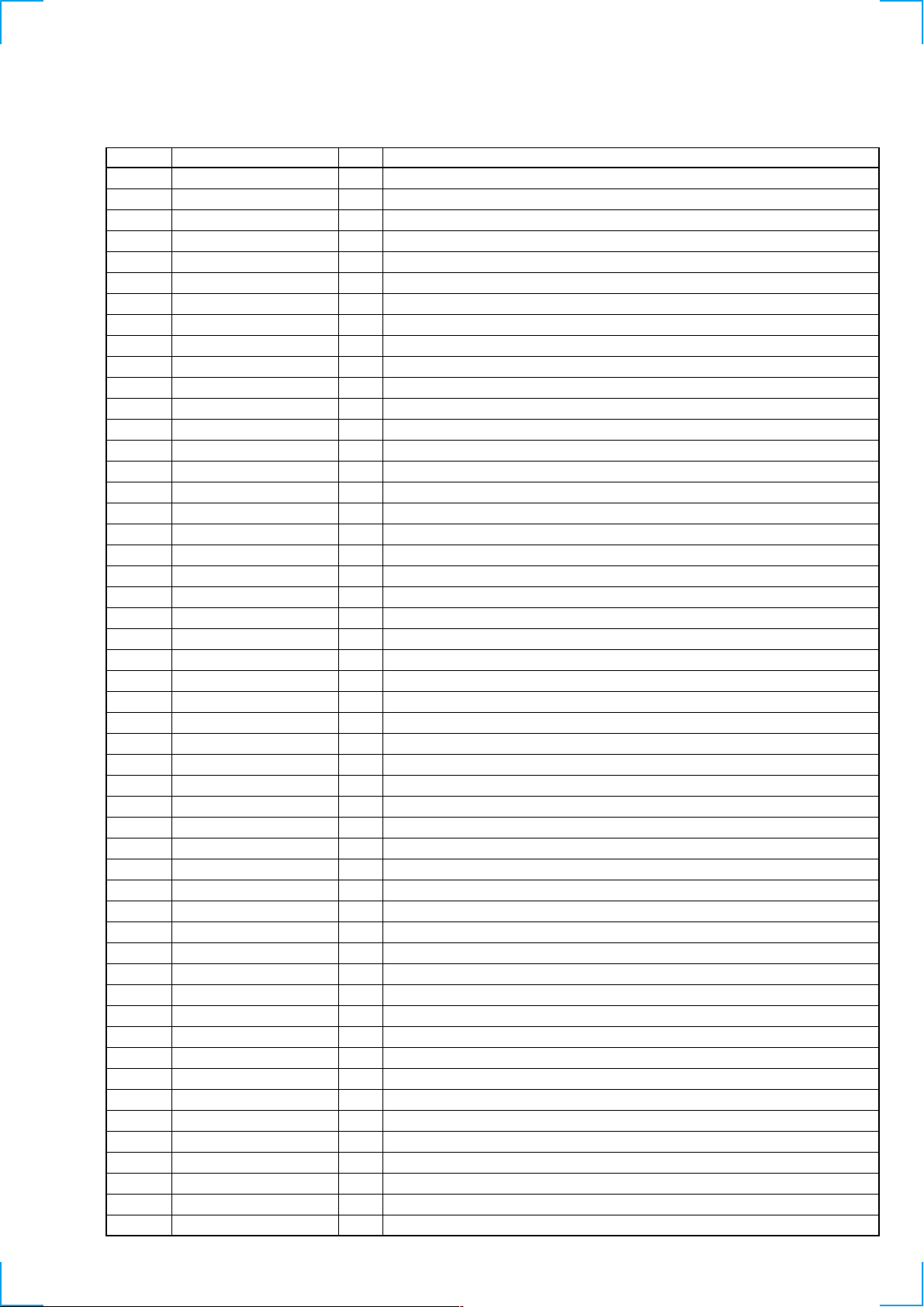

Fig. 1

3 PS 2x3

4 LOAD SW board

1 tension spring (RA)

2 arm roller assy

washer

arm

arm

washer

washer washer

2-7. SERVO BOARD

7 PS 2x4

8 PS 2x4

3 Removal the solders.

1 CN3

5 P 2x3

6 loading motor assy

(M903)

2 CN2

9 SERVO board

4 Removal the solders.

2-8. ARM ROLLER ASSY

• When installing, take note of the positions

arm (roller) and washers. (Fig. 1)

15

Page 7

2-9. CHASSIS (OP) ASSY

8 compression spring (FL)

1 tension spring (KF1)

7 chassis (OP) assy

9 compression spring (FL)

2 tension spring (KR1)

5 Fit lever (D) in the

direction of the arrow.

6 Turn loading ring in the

direction of the arrow.

4 damper (T)

2-10. OPTICAL PICK-UP BLOCK

1 P 2x3

2 sled motor assy

(M902)

3 damper (T)

3 optical pick-up block

16

Page 8

SECTION 3

DIAGRAMS

3-1. IC PIN DESCRIPTIONS

• IC501 CXD2598Q (DIGITAL SERVO, DIGITAL SIGNAL PROCESSOR) (SERVO BOARD)

Pin No. Pin Name I/O Pin Description

1 DVDD — Digital power supply pin

2 DVSS — Digital ground

3 SOUT O Servo brock serial data output (Not used.)

4 SOCK O Servo brock serial data read clock output (Not used.)

5 XOLT O Servo brock serial data latch output (Not used.)

6 SQSO O Sub Q 80 bit, PCM peak and level data output. CD TEXT data output

7 SQCK I Clock input from SQSO read output.

8 SCSY I Fixed at “L”.

9 SBSO O Serial output of sub-P to W. (Not used.)

10 EXCK I Clock input from SBSO read output. (Fixed at “L”)

11 XRST I System reset (“L”: Reset)

12 STSM I System mute input (Fixed at “L”)

13 DATA I Serial data input from CPU.

14 XLAT I Latch input from CPU. Latch serial data at the falling edge.

15 CLOK I Serial data transfer clock input from CPU.

16 SENS O SENS output for CPU.

17 SCLK I Clock input from SENS serial data read.

18 ATSK I/O Input/output for anti-shock.

19 WFCK O WFCK (Write Flame Clock) output (Not used.)

20 XUGF O XUGF output (Not used.)

21 XPCK O XPCK output (Not used.)

22 GFS O GFS output

23 C2PO O C2PO output (Not used.)

24 SCOR O “H” output at either detection, sub code sync S0 or S1.

25 C4M O 4.2336 MHz output (Not used.)

26 WDCK O Word clock input f=2Fs (Not used.)

27 COUT I/O Track number count signal input/output (Not used.)

28 MIRR I/O Mirror signal input/output (Not used.)

29 DVSS — Digital ground

30 DVDD — Digital power supply pin

31 DFCT I/O Diffect signal input/output (Not used.)

32 FOK I/O Focus OK signal output

33 PWM1 I External control input of spindle motor.

34 LOCK I/O Lock signal input/output

35 MDP O Servo control output of spindle motor.

36 SSTP I Disc most inner track detection signal input

37 FSTIO I/O 2/3 frequency division output of pins ih and ij. (Not used.)

38 SFDR O Sled drive output

39 SRDR O Sled drive output

40 TFDR O Tracking drive output

41 TRDR O Tracking drive output

42 FFDR O Focus drive output

43 FRDR O Focus drive output

44 DVDD — Digital power supply pin

45 DVSS — Digital ground

46 TEST I Test pin (Fixed at “L”)

47 TES1 I Test pin (Fixed at “L”)

48 XTSL I X’tal select input (“L”: 16.9344 MHz, “H”: 33.8688 MHz)

49 VC I Center voltage input

50 FE I Focus error signal input

51 SE I Sled error signal input

17

Page 9

Pin No. Pin Name I/O Pin Description

52 TE I Tracking error signal input

53 CE I Center servo analog input

54 RFDC I RF signal input

55 ADIO O Test pin (Not used.)

56 AVSSO — Analog ground

57 IGEN I Constant current input from OP amplifier.

58 AVDDO — Analog ground

59 ASYO O EFM full-swing output (“L”: VSS, “H”: VDD)

60 ASYI I Asymmetry comparate voltage input

61 RFAC I EFM signal input

62 AVSS3 — Analog ground

63 CLTV I VCO control voltage input from master.

64 FILO O Filter output for master PLL (slave=digital PLL)

65 FILI I Filter input from master PLL.

66 PCO O Charge pump output for master PLL.

67 AVDD3 — Analog power supply pin

68 BIAS I Asymmetry circuit constant current input

69 VCTL I VCO2 control input from wideband EFM PLL. (Not used.)

70 V16M O VCO2 oscillator output for wideband EFM PLL. (Not used.)

71 VPCO O Charge pump output for wideband EFM PLL. (Not used.)

72 DVSS — Digital ground

73 MD2 I Digital out ON/OFF control input (“L”: OFF, “H”: ON)

74 DOUT O Digital out output

75 ASYE I Asymmetry circuit ON/OFF input (“L”: OFF, “H”: ON)

76 DVDD — Digital power supply pin

77 LRCK O D/A interface LR clock output (f=Fs)

78 LRCKI I D/A interface LR clock input

79 PCMD O D/A interface serial data output (2’s COMP, MSB fast)

80 PCMD I D/A interface serial data input (2’s COMP, MSB fast)

81 BCK O D/A interface bit clock output

82 BCKI I D/A interface bit clock input

83 EMPH O Emphasis ON/OFF signal output

84 EMPHI I Emphasis ON/OFF signal input (“H”: ON, “L”: OFF)

85 XVDD — Power supply for master clock.

86 XTAI I X’tal oscillator input from master clock (16.9344 MHz).

87 XTAO O X’tal oscillator output for master clock (16.9344 MHz).

88 XVSS — Ground pin for master clock.

89 AVDD1 — Analog power supply pin

90 AOUT1 O Lch analog output

91 AIN1 I Lch OPAMP input

92 LOUT1 O Lch LINE output

93 AVSS1 — Analog ground

94 AVSS2 — Analog ground

95 LOUT2 O Rch LINE output

96 AIN2 I Rch OPAMP input

97 AOUT2 O Rch analog output

98 AVDD2 — Analog power supply pin

99 RMUT O Rch “0” detect Flug (Not used.)

100 LMUT O Lch “0” detect Flug (Not used.)

18

Page 10

• IC5 CXP84640-063Q (CD SYSTEM CONTROL) (SERVO BOARD)

Pin No. Pin Name I/O Pin Description

1 ITRPT — Not used in this set.

2, 3 ——Not used in this set.

4, 5 NCO — Not used in this set.

6 OPEN I Front panel open detection input

7 CLOSE O Front panel close control output

8 LINKOFF I Bus interface link input

9 NCO — Not used in this set.

10 D SW I Down switch input (SW4)

11 SSTP I Limit switch input (SW3)

12, 13 NCO — Not used in this set.

14, 15 ——Not used in this set.

16 EMPH O O De-emphasis ON/OFF control output

17 CDMON O CD mechanism deck power control output

18 CD ON O CD power control output

19 A MUT O System attenuate control output

20 LD ON O Laser power ON/OFF control output

21 CD RST O CD system reset output

22 HOLD O Hold switch output

23 AGC CONT O AGC control output

24 ——Not used in this set.

25 PH3 I Not used in this set.

26 TSTIN0 I Not used in this set.

27 TSTIN1 I Not used in this set.

28 TST.CLV I Not used in this set.

29 NCO — Not used in this set.

30 RESET I System reset input (“L”=Reset)

31 X IN I X’tal oscillator input from system clock. (10 MHz)

32 X OUT O X’tal oscillator output for system clock. (10 MHz)

33 GND — Analog ground

34 XT OUT O Not used in this set.

35 XT IN I Not used in this set.

36 AVSS — A/D converter ground

37 AVREF I A/D converter reference voltage input

38 TEP L I Not used in this set.

39 TEP H I Not used in this set.

40 SLED– I Sled drive input

41 PH2 I Not used in this set.

42 SEK/SMET I Fixed at “H” in this set.

43 GFS/MNT2 SEL I Fixed at “H” in this set.

44 SC-JIG ON/OFF I Fixed at “H” in this set.

45 SCLK O CD-TEXT data read clock output

46 LOCK I/O Lock signal input/output

47 ——Not used in this set.

48 SCK2 O Sub Q read clock output

49 SI2 I Sub Q 80 bit, PCM peak and level data 16 bit input.

50 ——Not used in this set.

51 BUS CLK I/O Bus system serial clock input/output

52 BUS SI I Bus system serial interface input

53 BUS SO O Bus system serial interface output

54 F OK I Focus OK signal input

55 GFS I GFS signal detection input

56 TEST MODE I Fixed at “H” in this set.

19

Page 11

Pin No. Pin Name I/O Pin Description

57 SENS I SENS signal input

58 ——Not used in this set.

59 ——Not used in this set.

60 BU.IN I Back-up power detection input

61 BUSON I Bus on control input

62 IN SW I Disc in switch input (SW1)

63 SELF SW I Self switch input (SW2)

64 SCOR O Sub-code sync output

65 CD-CKO O CD signal process serial clock input

66 LM LOD O Loading motor control output

67 CD DATA O CD signal process serial data output

68 CD-XLAT O CD signal process serial data latch output

69 LM-EJ O Loading motor control output

70 DRV-OE O Focus/tracking coil/sled motor control output

71 MD2 O Digital out ON/OFF control output (“L”: OFF, “H”: ON)

72 VDD — Power supply pin

73 NIH I Fixed at “H” in this set.

74 V/Z I Fixed at “H” in this set.

75 PH1 I Not used in this set.

76 ——Not used in this set.

77 DOUT-SEL I Fixed at “H” in this set.

78 – 80 ——Not used in this set.

20

Page 12

• IC501 MB90574PMT-G-266-BND (SYSTEM CONTROL) (MAIN BOARD)

Pin No. Pin Name I/O Pin Description

1 TUNON O Tuner power control output (+5 V)

2 ——Not used. (Open)

3 BUSON O SONY-BUS ON control output

4 – 6 ——Not used. (Open)

7 ILLON O Illumination power control output

8 VCC — Power supply pin (+5 V)

9 E2P SIO I/O E2P SONY-BUS serial data input/output

10 E2P CKO I/O E2P SONY-BUS serial clock input/output

11 SYSRST O SONY-BUS system reset output

12 DOORSW (WRITE OUT) I DOOR OPEN/CLOSE detection input (“L”: CLOSE, “H”: OPEN)

13 LCDSO (WRITE IN) O LCD serial data output

14 LCDCKO O LCD serial clock output

15 LCDCE O LCD chip enable output

16 BEEP O BEEP output

17 UNISI I SONY-BUS serial data input

18 UNISO O SONY-BUS serial data output

19 UNICKO O SONY-BUS serial clock output

20 UNICKI I SONY-BUS serial clock input

21 CD MD I CD/MD select input (“L”: CD, “H”: MD) (Fixed at “L” in this set)

22 FLASHW I Flash memory write mode detection input

23 ——Not used. (Open)

24 SIRCS I Remote commander (infrared ray reception) input

25 – 28 ——Not used. (Open)

29 DOORIND O DOOR indicator output

30 IFWIDTH O Not used in this set.

31 ——Not used. (Open)

32 NS MASK O Noise mask output

33 VSS — Ground

34 C — Condenser connection pin of power stabilization.

35 AD ON O Power control output for A/D converter.

36, 37 REIN0, 1 I Rotary encoder 0, 1 input

38 DVCC — D/A converter Vref pin (+5 V)

39 DVSS — D/A converter ground pin

40, 41 ——Not used. (Open)

42 AVCC — Analog power supply pin (+5 V)

43 AVRH — A/D converter Vref+ pin (+5 V)

44 AVRL — A/D converter Vref– pin

45 AVSS — Analog ground

46, 47 KEYIN0, 1 I Key 0, 1 input

48 RCIN0 I Rotary commander key input

49 DSTSEL I Destination setting input (Fixed at “L” in this set)

50 QUALITY I Noise detection input

51 FMAGC I FM AGC detection input

52 MPTH I Multi path detection input

53 VSM I Signal meter detection input

54 VCC — Power supply pin (+5 V)

55 RAMBU I RAM reset detection input

56 TUNATT O TUNER mute control output

57 VOLATT O Electric volume mute output

58 ATT O LINE mute output

59 AMPON O Power amplifier standby control output

60 AMPATT O Power amplifier mute control output

21

Page 13

Pin No. Pin Name I/O Pin Description

61 COLSW I

62 COLSEL I Illumination color select input (“L”: AMBER, “H”: GREEN) (Fixed at “L” in this set)

63 VSS — Ground

64 DAVN I Block synchronization detection input of RDS data.

65 FILE I Custom file setting input

66 TEXT I CD text setting input

67 NOSESW I Front panel attachment detection input

68, 69 ——Not used. (Open)

70 I2C SIO I/O I2C BUS serial data input/output

71 I2C CKO I/O I2C BUS serial clock input/output

72 ——Not used. (Open)

73 X1A — Low speed oscillation connecting pin (32.768 kHz)

74 X0A — Low speed oscillation connecting pin (32.768 kHz)

75 ——Not used. (Open)

76 KEYACK I Key acknowledge input

77 BUIN I Backup voltage detection input

78 ILLIN I Illumination (ILLIN) detection input (Fixed at “L” in this set)

79 TELATT I Telephone (TEL) detection input (Fixed at “L” in CDX-C4900R)

80 ——Not used. (Open)

81 TEST IN I Test mode setting input

82 ACC IN I Accessory power supply (ACC) detection input

83 ——Not used. (Open)

84 LOCKIN I MD LOCK detection input

85 RCIN1 I Rotary commander SHIFT input

86 HSTX I Hardware standby setting input

87 MD2 I Connect to VSS in this set.

88, 89 MD1, 0 I Connect to VCC in this set.

90 RSTX I Reset input

91 VSS — Ground

92 X0 — High speed oscillation connecting pin (3.68 MHz)

93 X1 — High speed oscillation connecting pin (3.68 MHz)

94 VCC — Power supply pin (+5 V)

95 – 97 ——Not used. (Open)

98 DIM SEL I

99 TAP CD I TAPE/CD select input (“L”: CD, “H”: TAPE) (Fixed at “L” in this set)

100 – 118 ——Not used. (Open)

119 VSS — Ground

120 PW ON O System power control output

Illumination color switch input (“L”: 2 colors, “H”: 1 color) (Fixed at “L” in

CDX-C4900R/C5000R, “H” in CDX-C5000RX)

Dimmer select input (“L”: With dimmer select, “H”: Without dimmer select)

(Fixed at “L” in this set)

22

Page 14

3-2. BLOCK DIAGRAM — CD SECTION —

CDX-C4900R/C5000R/C5000RX

PD

LD

TRACKING

04

OPTICAL PICKUP

KSS-720A

A

C

B

D

CONV.

E

F

FOCUS

COIL

COIL

I-V

M902

SLED

MOTOR

M901

SPINDLE

MOTOR

M903

LOADING

MOTOR

A

5

C

7

B

6

D

8

FOCUS

ERROR

E

11

TRACKING

F

ERROR

10

PD

4

LD

LD

DRIVE

Q101

TRACKING/FOCUS COIL DRIVE

SLED/SPINDLE/LOADING MOTOR DRIVE

10

11

12

13

AMP

LD

3

IC7

FOCUS

COIL

DRIVE

TRACKING

8

COIL

DRIVE

9

SLED

6

MOTOR

7

DRIVE

SPINDLE

MOTOR

DRIVE

LOADING

5

MOTOR

4

DRIVE

RF AMP, LD APC,

ERROR AMP

IC1

22

21

25

24

31

32

18

1

2

MUTE 1

34

MUTE 2

35

RFO RFAC

RF

EQ

FE

TE

LD ON

HOLD SW

AGC CONT

16

14

13

22

21

20

DIGITAL SERVO,

DIGITAL SIGNAL PROCESSOR

IC501

(Page 24)

Q706

(Page 24)

B

SW503

(RESET)

TUNER

SECTION

SYSTEM CONTROL

58

12

20

19

17

18

3

11

77

90

86

1 3

BUS INTERFACE

10 3

13 2

12

9

8

8

IC501 (1/3)

ATT

DOOR SW

UNI CKI

UNI CKO

UNI SI

UNI SO

BUS ON

SYS RST

BU IN

RSTX

HSTX

IC652

RESET

BATT (H)

CHECK

Q701

IC701

BATT (L)

CHECK

RESET

RESET

DATA

CLK

1

6

4

BU 5V

BATT

BATT

Q705

• Signal path

SIRCS

8

6

3

5

2

4

1

7

CN701

BUS

CONTROL IN

C

DISPLAY

SECTION

(Page 25)

LOUT1

LOUT2

LOCK

SQSO

SQCK

SCOR

XRST

DATA

XLAT

SCLK

CLOK

SENS

XTALI

XTALO

MD2

GFS

FOK

92

95

34

6

7

24

73

11

13

14

17

15

16

22

32

86

87

11V REG

Q361

SW4

(LIMIT)

SW1

(DISC IN)

SW3

(LOAD IN)

SW2

(SELF)

RFDC

FE

TE

SE

FFDR

FRDR

TFDR

TRDR

SFDR

SRDR

MDP

CD 5V

CD 6V

EFM

DEM

SERVO

CTL

61

54

50

52

51

42

43

40

41

38

39

35

5V REG

Q364

D/A

I/F

DIGITAL

CLV

D/A

CONV.

SUB

CODE

PROCESS

POWER

CONT

Q365

6V REG

Q362

X2

16MHz

POWER

CONT

Q363

CD L

R-CH

BATT

TUNER

A

SECTION

CD SYSTEM CONTROL

LOCK

46

SI2

49

SCK2

48

SCOR

64

MD2

71

CD RST

21

CD DATA

67

CD XLAT

68

SCLK

45

CD CKO

65

SENS

57

GFS

55

FOK

54

SSTP

11

D SW

10

IN SW

64

SELF SW

63

LM EJ

69

LM LOD

66

SLED –

40

DRIVE ON

70

LD ON

20

HOLD

22

AGC CONT

23

CD ON

18

CDM ON

17

IC5

A MUT

OPEN

BUS CLK

BUS SI

BUS ON

RESET

BU IN

X IN

X OUT

BUS SO

LNK OFF

19

51

52

61

30

60

31

32

53

6

8

(KEY BOARD)

X1

10MHz

ATT

:CD

23 23

Page 15

CDX-C4900R/C5000R/C5000RX

3-3. BLOCK DIAGRAM — TUNER SECTION —

J1

(ANTENNA)

TUNER UNIT

TU1

ANTFM MPX

2 10

AM DET

ANTAM

1

IF AM

S-METER

I2C SDA

I2C SCL

RDS DET

CNJ151–1, –2

BUS AUDIO IN

–1

–2

L

R

ELECTRONIC VOLUME

IC151

A

CD

CDL

Q121

MUTE

RDS DECODER

IC51

8

Q111

MUTE

IC90

NOISE

DET

9

SECTION

MUTE

CONT

Q90

NOISE ON

10

MULTI

PATH

DET

RDS/RDBS

DEM/DEC

Q131

(Page 23)

8

19

BUFFER

Q1

5 1

14

12

13

SDA SCA

LV IN

20 2

9

MPX

16

R-CH

FDIL OUT LF

3 30

SEL

1

MPX

13

AM

11

AM IF

12

LEVEL

14

MPIN

15

SDA

20

SCL

21

SM

18

SYSTEM CONTROL

VOL ATT

57

TUN ATT

56

QUALITY

50

NS MASK

32

VSM

53

I2C SIO

70

I2C CKO

71

MPTH

52

DAVN

64

IC501 (2/3)

AMP MUTE

OUT LR

BEEP

AMP ON

TEL ATT

ACC IN

TEST IN

TU ON

PW ON

29

MUTE

16

59

60

79

82

81

1

120

Q181

MUTE

CONT

Q621, 622

CNJ151–3, –4

AUDIO OUT REAR

–3L–4

R

R-CH

Q171

MUTE

ATT

SECTION

(Page 23)

BATT

CNJ151–5, –6

AUDIO OUT FRONT

–5L–6

R

-CH

R

B

CD

ACC

CHECK

Q661

POWER SUPPLY

IC671

7 6

VCC AMP +B

2

3

4

8.7V ON

5.6V ON

STB

ANT +B

BU+B BU 5V

COM 8V

TU 5.6V

TU 8.7V

POWER AMP

12

11

AUX IN

16

STAND BY

4

MUTE

22

TEL

ATT

Q571

8

5

9

10

11

C5000R/C5000RX

IC611

5

3

9

8

BATT

COM 8V

TU 5.6V

TU 8.7V

R-CH

F901

CN601

1

9

2

10

4

12

3

11

16

13

7

15

5

6

FL+

FL–

RL+

RL–

FR+

FR–

RR+

RR–

BATT

C5000R/C5000RX

ATT

ACC

TEST

AMP R

ANT R

OSCO OSCI

4 5

FM AGC

E2PROM SDA

E2PROM SCL

04

4

17

18

X51

4.332MHz

51

9

10

FM AGC

E2P SIO

E2P CKO

• Signal path

:FM

:MW

:CD

2424

Page 16

t

CDX-C4900R/C5000R/C5000RX

3-4. BLOCK DIAGRAM — DISPLAY SECTION —

KEY MATRIX

LSW901-917

S901-904

LSW801

KEY

ACTIVE

Q651

CD

SECTION

(Page 23)

C

04

J501

(REMOTE IN)

SIRCS

Q704

ACTIVE

IC951

RECEIVE

ROTARY

ENCODER

RE901

SW504

(NOSE DET)

KEY

Q652

IR

KEY ACT

X502

32.768kHz

SYSTEM CONTROL

IC501 (3/3)

KEY IN0 DATA

46 13

KEY IN1

KEY ACK

76

AD ON

35

RC IN1

85

RC IN0

48

SIRCS

24

RE IN0

36

RE IN1

37

NOSE SW

67

XOA

73

XIA

74

LCD SO

LCD CKO

LCD CE

DOOR IND

ILL ON

14

1547

DOOR IND

29

POWER

7

BATT

XO

92

XI

3.68MHz

93

LCD DRIVE

IC901

64

CL

63

CE

62

GREEN

2

AMBER

1

C4900R/

C5000R

DRIVE

Q551

LED801-803 LED910-915 LSW901-917

CONT

Q633

X501

+10V REG

Q631

ILL +B

LCD901

AMBER

DRIVE

Q901

LED901-904

GREEN

DRIVE

Q902

3-5. CIRCUIT BOARDS LOCATION

DISC IN SW board

SUB (CD) board

LOAD SW board

KEY board

SUB board

LIMIT SW board

tuner uni

(TU1)

MAIN board

SERVO board

25 25

Page 17

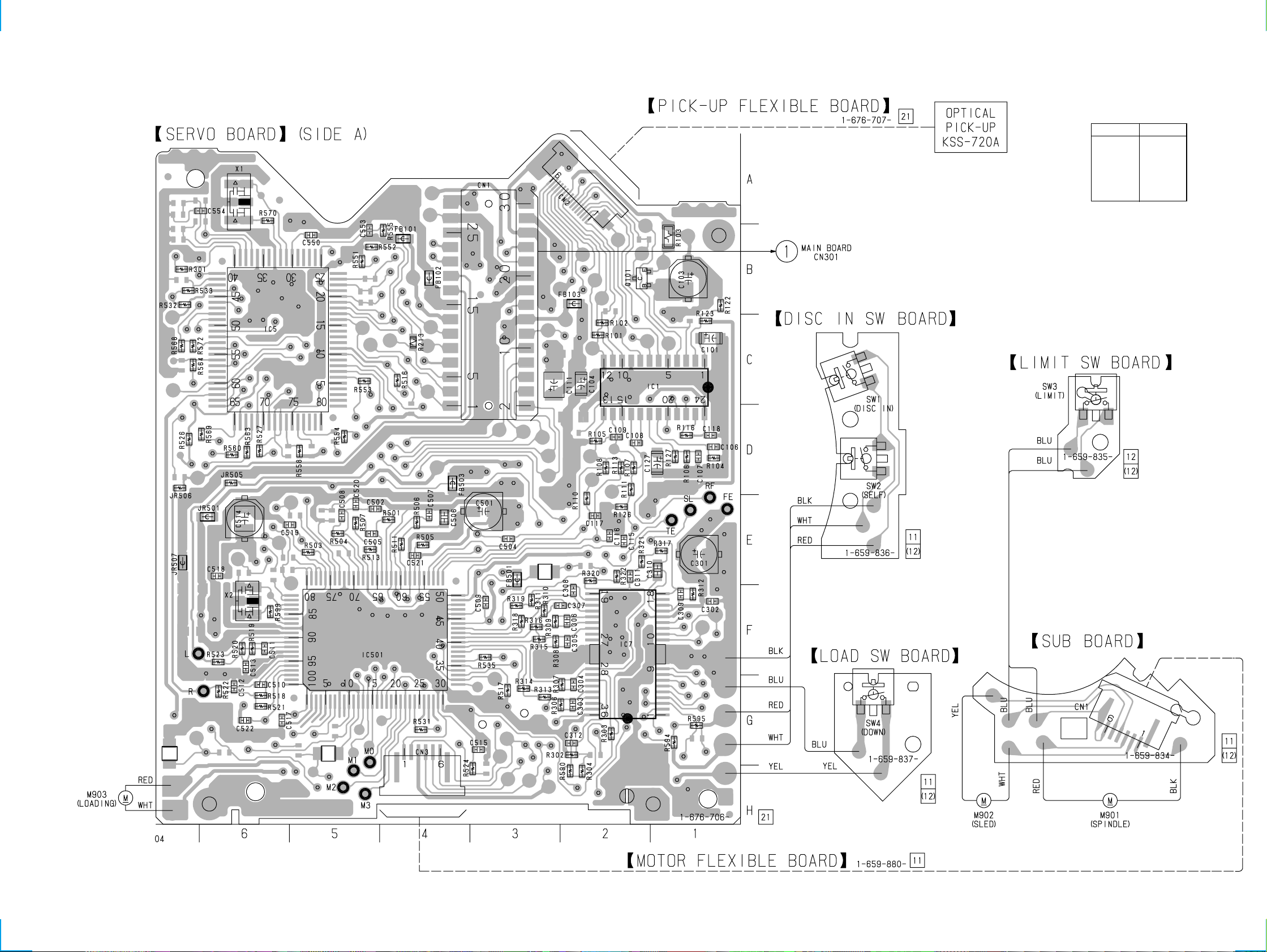

CDX-C4900R/C5000R/C5000RX

THIS NOTE IS COMMON FOR PRINTED WIRING

BOARDS AND SCHEMATIC DIAGRAMS.

(In addition to this, the necessary note is

printed in each block.)

for schematic diagram:

• All capacitors are in µF unless otherwise noted. pF: µµF

50 WV or less are not indicated except for electrolytics

and tantalums.

• All resistors are in Ω and 1/

specified.

• % : indicates tolerance.

f

•

• C : panel designation.

Note: The components identified by mark 0 or dotted line

• U : B+ Line.

• Power voltage is dc 14.4V and fed with regulated dc power

• Voltages are tak en with a V OM (Input impedance 10 MΩ).

• Waveforms are taken with a oscilloscope.

• Circled numbers refer to waveforms.

• Signal path.

: internal component.

with mark 0 are critical for safety.

Replace only with part number specified.

supply from ACC and BATT cords.

Voltage variations may be noted due to normal produc-

tion tolerances.

Voltage variations may be noted due to normal produc-

tion tolerances.

F : FM

f : MW

J : CD

4

W or less unless otherwise

3-6. PRINTED WIRING BOARDS — CD MECHANISM SECTION —

for printed wiring boards:

• X : parts extracted from the component side.

• Y : parts extracted from the conductor side.

• x : parts mounted on the conductor side.

a

•

• b : Pattern from the side which enables seeing.

Caution:

Pattern face side: Parts on the pattern face side seen from the

(Side B) pattern face are indicated.

Parts face side: Parts on the parts face side seen from the

(Side A) parts face are indicated.

: Through hole.

(The other layer’s patterns are not indicated.)

2626

Page 18

(Page 31)

CDX-C4900R/C5000R/C5000RX

• Semiconductor

Location

Ref. No. Location

IC1 C-1

IC5 C-6

IC7 F-2

IC501 F-5

Q101 B-2

27 27

Page 19

CDX-C4900R/C5000R/C5000RX

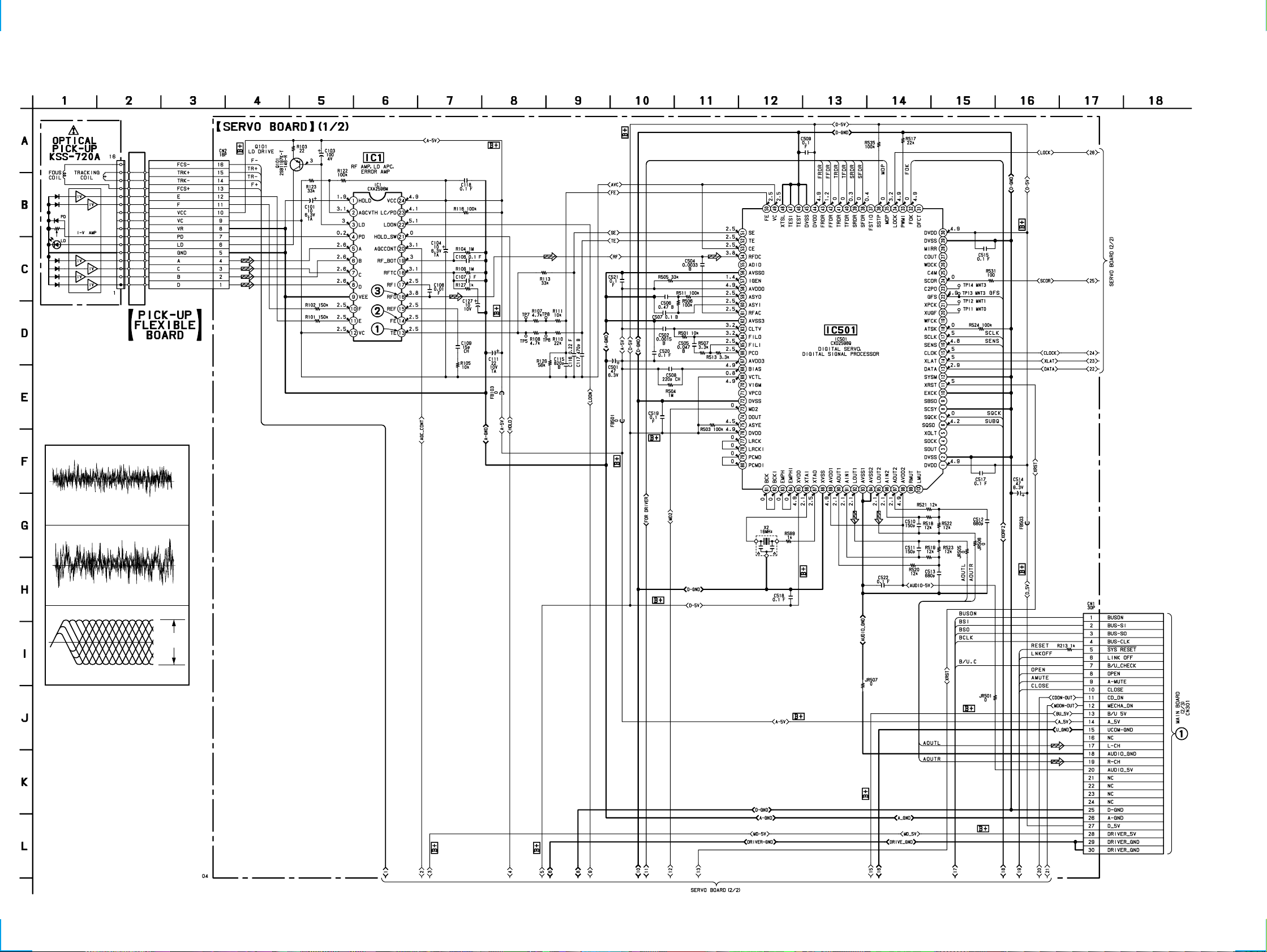

3-7. SCHEMATIC DIAGRAM — CD MECHANISM SECTION (1/2) — • Refer to page 39 for IC Block Diagrams.

(Page 29)

• Waveforms (MODE:PLAY)

1

0V

Approx. 200mVp-p

qd

(TE)

IC1

2

0V

Approx. 620mVp-p

qf

(FE)

IC1

3

1.2Vp-p

qh

(RFO)

IC1

(Page 33)

Note:

• Voltage and waveforms are dc

with respect to ground

under no-signal conditions.

no mark : CD PLAY

(Page 29)

2828

Page 20

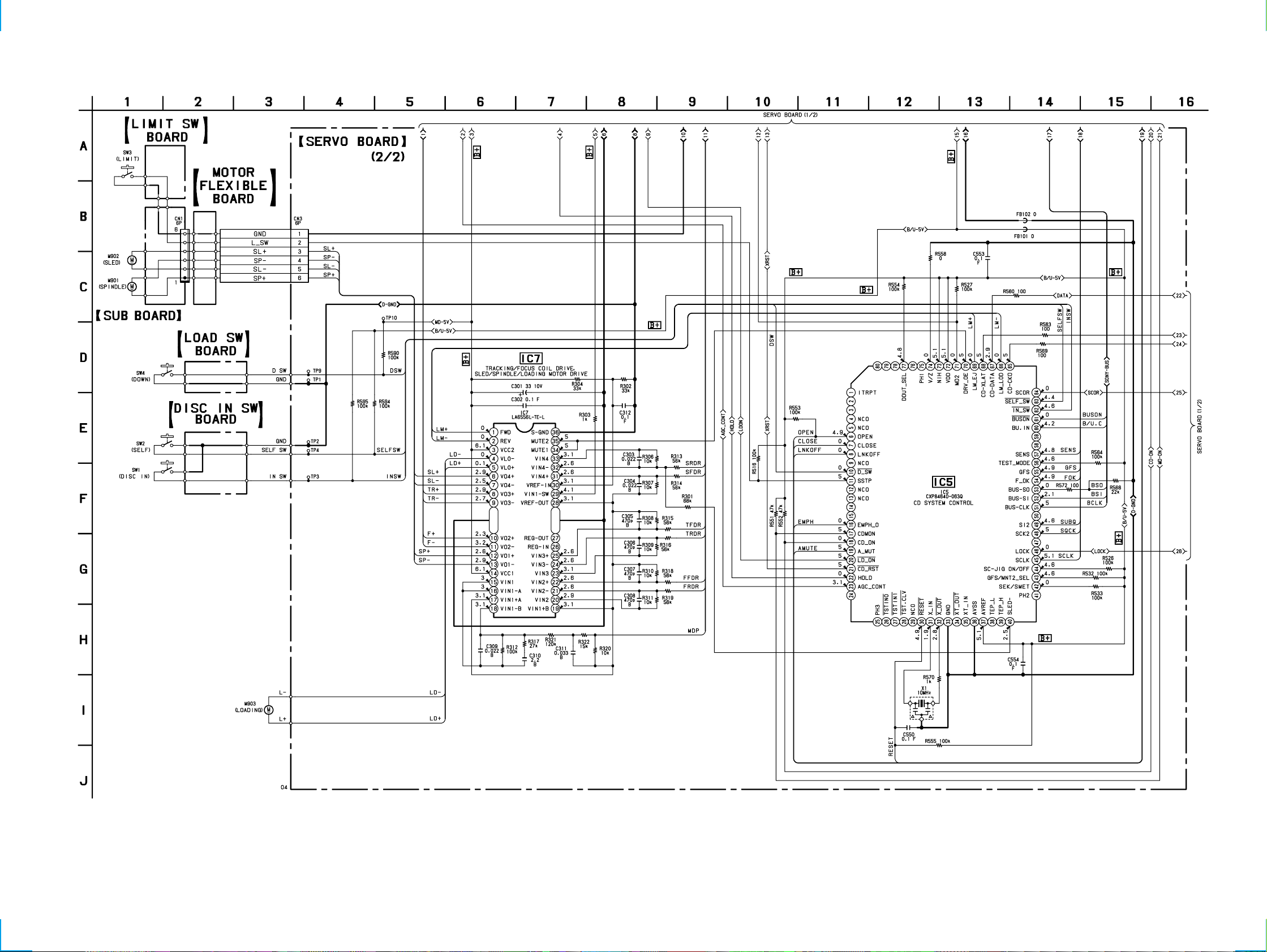

3-8. SCHEMATIC DIAGRAM — CD MECHANISM SECTION (2/2) — • Refer to page 40 for IC Block Diagrams.

CDX-C4900R/C5000R/C5000RX

(Page 28)

(Page 28)

29 29

Note:

• Voltage is dc with respect to ground under no-signal

conditions.

no mark : CD PLAY

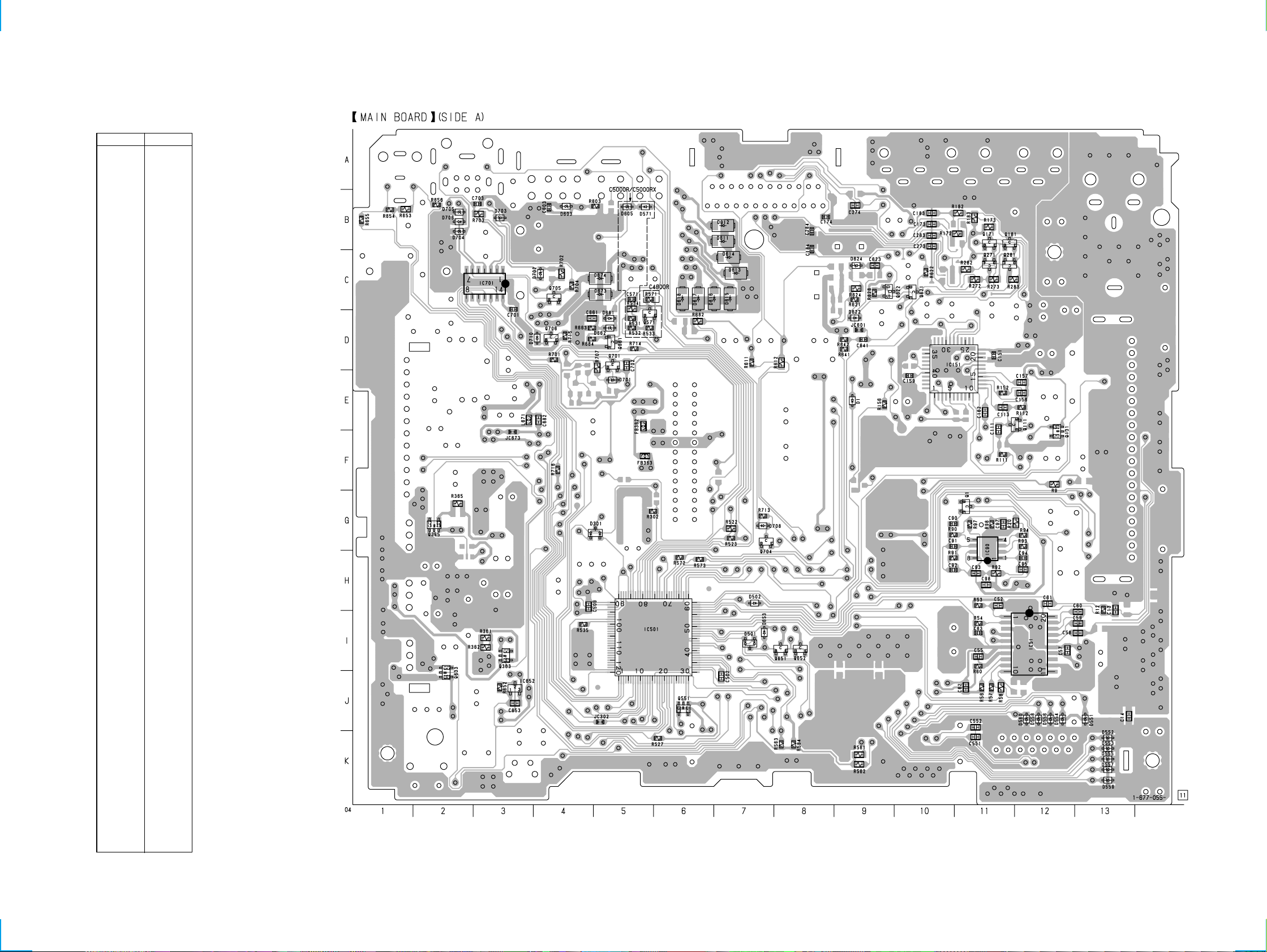

Page 21

CDX-C4900R/C5000R/C5000RX

• Semiconductor

Location (Side A)

Ref. No. Location

D1 E-9

D301 G-4

D501 I-7

D502 H-7

D551 J-13

D552 K-13

D553 K-13

D554 J-12

D555 K-13

D556 J-12

D557 K-13

D558 J-12

D559 K-13

D560 J-12

D571 B-5

D603 B-4

D605 B-5

D611 B-7

D612 B-7

D613 C-7

D614 B-7

D615 C-7

D616 C-7

D617 C-6

D618 C-6

D622 D-9

D624 C-9

D653 I-7

D661 D-5

D662 D-5

D673 C-5

D674 C-5

D701 E-5

D702 C-4

D703 B-3

D704 B-2

D705 B-2

D706 B-2

D708 D-7

D710 D-4

3-9. PRINTED WIRING BOARD — MAIN SECTION —

IC51 I-12

IC90 H-11

IC151 D-11

IC501 I-6

IC652 J-3

IC701 C-3

Q1 G-11

Q111 E-12

Q131 F-12

Q171 B-11

Q181 B-12

Q271 C-11

Q281 C-12

Q363 I-3

Q365 G-2

Q551 J-6

Q571 D-6

Q621 C-10

Q622 C-9

Q633 J-2

Q651 I-8

Q652 I-8

Q661 D-5

Q701 E-5

Q704 G-7

Q705 C-4

Q706 D-4

3030

Page 22

CDX-C4900R/C5000R/C5000RX

(Page 27)

• Semiconductor

Location (Side B)

Ref. No. Location

D2 E-7

D90 H-12

D91 H-11

D92 D-12

D131 F-12

D302 G-8

D361 I-2

D362 G-2

D363 G-3

D561 K-11

D562 K-11

D601 C-3

D602 B-4

D604 A-5

D621 B-10

D631 J-2

D671 B-5

D672 C-5

D675 I-4

D676 I-4

D677 I-4

D709 G-5

D901 K-12

D902 K-13

(Page 36)

IC611 B-7

IC671 E-1

Q90 D-11

Q121 E-12

Q361 H-1

Q362 G-1

Q364 G-2

Q631 J-2

31 31

Page 23

CDX-C4900R/C5000R/C5000RX

3-10. SCHEMATIC DIAGRAM — MAIN SECTION (1/3) — • Refer to page 39 for IC Block Diagrams.

(Page 33) (Page 34)

3232

Note:

• Voltage is dc with respect to ground under no-signal

(detuned) condition.

no mark : FM

( ) : MW

Page 24

3-11. SCHEMATIC DIAGRAM — MAIN SECTION (2/3) —

CDX-C4900R/C5000R/C5000RX

(Page 32)

(Page 28)

(Page 34)

33 33

Note:

• Voltage is dc with respect to ground under no-signal

(detuned) condition.

no mark : FM

( ) : MW

< > : CD PLAY

Page 25

CDX-C4900R/C5000R/C5000RX

3-12. SCHEMATIC DIAGRAM — MAIN SECTION (3/3) — • Refer to page 39 for IC Block Diagrams.

(Page 32)

(Page 33)

(Page 35)

Note:

• Voltage is dc with respect to ground under no-signal

(detuned) condition.

no mark : FM

( ) : MW

< > : CD PLAY

3434

Page 26

3-13. SCHEMATIC DIAGRAM — SUB (CD) SECTION —

(Page 34)

CDX-C4900R/C5000R/C5000RX

(Page 38)

35 35

Page 27

CDX-C4900R/C5000R/C5000RX

3-14. PRINTED WIRING BOARD — SUB (CD) SECTION —

(Page 31)

WHT

(Page 37)

3636

Page 28

3-15. PRINTED WIRING BOARD — KEY SECTION —

CDX-C4900R/C5000R/C5000RX

• Semiconductor

Location

Ref. No. Location

(D901) A-11

(D902) B-10

(D903) B-10

(D904) B-10

(D951) C-4

(D952) B-6

(IC901) B-8

IC951 C-5

LED901 A-2

LED902 C-2

LED903 C-4

LED904 A-4

LED910 B-12

LED911 B-12

LED912 A-12

LED913 B-5

LED914 B-5

LED915 B-5

(Q901) A-3

(Q902) A-3

( ) : SIDE B

37 37

(Page 36)

Page 29

CDX-C4900R/C5000R/C5000RX

3-16. SCHEMATIC DIAGRAM — KEY SECTION —

(Page 35)

Note:

• Voltage is dc with respect to ground under no-signal

(detuned) condition.

no mark : FM

3838

Page 30

8

7

6

5

1

2

3

4

2CH

1CH

VCC

OUT2

–IN2

+IN2

OUT1

–IN1

+IN1

VEE

• IC Block Diagrams

IC1 CXA2596M

APC PD AMP

HOLD

1 24

VEE

AGCVTH

2

VEE

1.25V

VREF

LD

3

PD

4

A

5

B

6

C

7

D

8

VEE

VEE

9

VC

F

10

+

–

+

–

+

–

–

+

VC

VCC

+

–

+

–

VC

+

–

+

–

+

–

RF SUMMING AMP RF EQ AMP

VC

VC

VC

+

–

VEE

ERROR AMP

APC LD AMP

VCC

+

–

FOCUS

+

–

23

22

21

20

19

18

17

16

15

VCC

LC/PD

LD ON

HOLD SW

AGCCONT

RF BOT

RFTC

RF I

RFO

RFE

IC90 BA4558F-E2

IC701 BA8270F

BUS ON

1

2

RST

BATT

3

4

CLK

5

VREF

6

DATA

GND

7 8

BUS ON

SWITCH

RESET

SWITCH

BATTERY

SWITCH

14

13

12

11

10

9

VCC

RST

BUS ON

CLK IN

BU IN

DATA IN

DATA OUT

VCC

+

–

VC

VC BUFFER

–

+

+

–

VCC

VEE

VC

VC

–

+

TRACKING

ERROR AMP

E

11

VC

VC

12

VC

FE

14

TE

13

IC51 SAA6588T-V2-118

6

VSSD

17

CLOCK

DATA

7

VDDD

VREF

MPX

SIGNAL QUALITY

DECODER

445

INTERFACE

REGISTER

8

DAVN

VSSA

15

POWER SUPPLY

& RESET

LVIN

20

MULTI

PATH

DETECTOR

CLOCKED

COMPARATOR

RDS/RDBS

DEMODULATOR

TEST

CONTROL

2

1

MRO

3

MPTH

19

TCON

18

BAND-PASS FILTER

OSCILLATOR

& CLOCK

4 5

OSCO

57kHz

8th ORDER

RDS/RDBS

DECODER

OSCI

SCOUT

CIN

VDDA

14

CLOCK

DATA

IIC BUS SLAVE

TRANSCEIVER

9 10

1316

SDA

AFIN

DETECTOR

SCL

PAUSE

MAD

PSWN

11

12

39

Page 31

IC7 LA6556L-TE-L

FWD

REV

VCC2

VL0–

VL0+

VO4+

VO4–

VO3+

VO3–

VO2+

VO2–

MUTE2

MUTE1

VIN1/VREF SW

5V REG

+

–

GND

+

–

–

+

36

S-GND

35

MUTE2

34

MUTE1

VIN4

33

VIN4–

32

VIN4+

31

VREF-IN

30

VIN1 (VREF)-SW

29

VREF-OUT (CH1)

28

REG-OUT

27

REG-IN

26

1

INPUT

2

3

4

5

6

7

8

9

10

11

OUTPUT

CONTROL

LEVEL

SHIFT

LEVEL

SHIFT

–

+

LEVEL

SHIFT

CH2-CH4 OUTPUT

ON/OFF

CH1 OUTPUT

ON/OFF

–

+

VO1+

12

VO1–

13

VCC1

14

VIN1

15

VIN1–A

16

AMP-A

–

VIN1+A

VIN1–B

+

17

–

18

+

IC671 BA4908-V3

AMP-B

LEVEL

SHIFT

–

+

REGULATOR

VIN3+

25

–

+

–

+

+

–

VIN3–

24

VIN3

23

VIN2+

22

+

–

VIN2–

21

20

VIN2

19

VIN1 +B

40

OVER VOLTAGE

PROTECT

–

+

2 3

4

1

NC

STB

MODE2

MODE1

5 6 7 8 9

ANT

VCC

VDD

AMP

COM

–

+

10

AM

–

+

11

FM

–

+

12

GND

Page 32

IC151 TDA7402TR

ACINLR

ACINLR

ACINRR

OUTLF

33

OUTLR

28 2730 2932 31

OUTRF

OUTRR

OUTSWL

OUTSWR

26 25 24 23

OUTSSL

OUTSSR

ACINLF

SWINR

SWINL

AC OUTR

AC OUTL

VREF

MUX

MD1 (SE4L)

MD1G (SE4R)

MD2

MD2G

MONO

FADER

MIXER

MIXING

SUBWOOFER

+PHASE

CONTROL

SECOND SOURCE

LOUDNESS

IN GAIN

MUTE

SELECTOR

II

C-BUS

DIGITAL

CONTROL

BEEP

HIGH OUT

S & H

LP

DEMODULATOR

+STEREO ADJUST

+STEREO BLAND

PILOT

CANCELLATION

LP

PIL, DET

PLL

QUAL.

MALTI

PATH

DETECTOR

MONO

FADER

34

35

36

37

38

LP

HP

BASS

39

40

41

42

43

44

TRABLE

VOLUME

SOFT MUTE

LOUDNESS COMPANDER

IN GAIN

+ AUTO

ZERO

MAIN SOURCE

SELECTOR

OUTPUT CONTROL

VOICE

BANDPASS

INPUT MULTIPLEXER

MONO

FADER

SELECTOR

SUPPLY

D/A

PULSE

FORMER

AM/FM

NOISE

BLANKER

22

21

20

19

18

17

16

15

14

13

12

VDD

SCL

SDA

GND

MUTE

QUAL

MP OUT

MP IN

LEVEL

MPX

AMIF

1 2 3 4 5 6 7 8 9 10 11

CD L

CD R

SE2L

SE2R

AUX L

AUX R

FD2L+

FD2L–

FD2R+

FD2R–

AM

41

Page 33

NOTE:

• The mechanical parts with no reference

number in the exploded views are not supplied.

• Items marked “*” are not stocked since

they are seldom required for routine service.

Some delay should be anticipated

when ordering these items.

• -XX and -X mean standardized parts, so

they may have some difference from the

original one.

4-1. CHASSIS SECTION

#6

8

SECTION 4

EXPLODED VIEWS

• Color Indication of Appearance Parts

Example :

KNOB, BALANCE (WHITE) ... (RED)

• Accessories and packing materials and

hardware (# mark) list are given in

the last of this parts list.

9

MG-383Z-121//Q

11

15

R

Parts Color Cabinet’s Color

R

10

#4

14

13

12

The components identified by

mark 0 or dotted line with mark.

0 are critical for safety.

Replace only with part number

specified.

#2

#1

#1

#1

#3

#1

#1

#1

#1

4

3

2

1

5

7

#1

#5

#1

#5

#5

18

Ref. No. Part No. Description Remark

1 X-3378-512-1 PANEL ASSY, SUB

2 3-040-990-01 BUTTON (EJECT)

* 3 1-677-056-11 SUB (CD) BOARD

4 X-3376-699-2 GEAR ASSY

5 3-030-909-02 DAMPER, OIL

#1

TU1

#4

16

19

F901

11

#2

6

20

#2

17

Ref. No. Part No. Description Remark

* 12 A-3326-196-A MAIN BOARD, COMPLETE (C5000R)

* 12 A-3326-198-A MAIN BOARD, COMPLETE (C4900R)

* 12 A-3326-210-A MAIN BOARD, COMPLETE (C5000RX)

* 13 3-040-998-01 BRACKET (IC)

* 14 3-040-996-51 HEAT SINK (4P) (C4900R)

6 X-3377-621-2 LOCK ASSY

7 3-713-786-51 SCREW +P 2X3

* 8 3-040-995-01 COVER

9 1-776-527-51 CORD (WITH CONNECTOR) (ISO) (POWER)

9 1-776-527-61 CORD (WITH CONNECTOR) (ISO) (POWER)

(C5000R/C5000RX)

* 10 3-041-012-01 BRACKET (CD)

11 3-376-464-11 SCREW (+PTT 2.6X6), GROUND POINT

42

(C4900R)

14 3-040-996-61 HEAT SINK (6P) (C5000R/C5000RX)

* 15 3-041-011-01 HEAT SINK (REG)

* 16 3-045-878-01 PLATE (TU), GROUND

* 17 3-040-994-11 CHASSIS

18 3-047-812-01 SCREW (LOCK)

* 19 3-045-877-01 CUSHION (TU)

* 20 3-045-828-01 PLATE, INSULATED

F901 1-532-877-11 FUSE (BLADE TYPE) (AUTO FUSE) 10A

TU1 A-3220-738-A TUNER UNIT (TUX-020)

Page 34

4-2. FRONT PANEL SECTION

#12

#12

54

#12

not supplied

(KEY board)

53

67

66

65

LCD901

52

51

51 3-040-980-01 BUTTON (SOURCE)

52 3-040-981-01 KNOB (VOL)

* 53 3-040-992-01 HOLDER (LCD)

54 X-3378-398-1 PANEL ASSY, FRONT BACK

55 X-3378-517-1 SUB ASSY, PANEL (C4900R)

64

63

61

62

59

58

55

Ref. No. Part No. Description RemarkRef. No. Part No. Description Remark

60 3-041-010-01 BUTTON (1-6/M)

61 3-041-003-01 BUTTON (LIST/ENTER)

62 3-040-987-01 BUTTON (OFF)

63 3-040-986-01 BUTTON (MENU/SOUND)

* 64 3-040-997-01 PLATE (LCD), GROUND

60

57

56

55 X-3378-518-1 SUB ASSY, PANEL (C5000R)

55 X-3378-591-1 SUB ASSY, PANEL (C5000RX)

56 3-041-006-01 BUTTON (AF/TA)

57 3-041-005-11 BUTTON (D)

58 3-040-989-01 BUTTON (OPEN)

59 3-037-267-01 SPRING (OPEN)

65 1-694-660-11 CONDUCTIVE BOARD, CONNECTION

* 66 3-041-371-02 SHEET (REFLECTOR)

* 67 3-040-993-01 PLATE (LCD), LIGHT GUIDE

LCD901 1-803-906-11 DISPLAY PANEL, LIQUID CRYSTAL

(C4900R/C5000R)

LCD901 1-803-906-31 DISPLAY PANEL, LIQUID CRYSTAL (C5000RX)

43

Page 35

4-3. CD MECHANISM SECTION (1)

(MG-383Z-121//Q)

102

104

101

#8

#8

103

107

109

C

#7

110

105

106

112

111

C

#7

#7

M903

#9

108

#8

Ref. No. Part No. Description Remark Ref. No. Part No. Description Remark

* 101 1-659-836-11 DISC IN SW BOARD

* 102 A-3315-034-A CHASSIS (T) ASSY

103 3-931-909-01 SPRING (LR), TENSION

104 X-3371-501-1 LEVER (L) ASSY

105 3-338-737-01 SCREW (2X3), +PS

* 106 1-659-837-11 LOAD SW BOARD

107 X-3371-502-1 LEVER (R) ASSY

* 108 3-039-629-01 BRACKET (MOTOR)

109 3-013-388-02 GUIDE (DISC)

110 A-3315-040-A ROLLER ASSY, ARM

* 111 A-3326-231-A SERVO BOARD, COMPLETE

112 3-047-477-01 SPRING (RA2), TENSION

M903 A-3315-039-A MOTOR SUB ASSY, LD (LOADING)

44

Page 36

4-4. CD MECHANISM SECTION (2)

(MG-383Z-121//Q)

155

157

158

162

163

154

D

160

155

165

151

156

157

166

167

153

164

161

D

159

152

152

152

Ref. No. Part No. Description Remark Ref. No. Part No. Description Remark

151 X-3378-956-1 ARM ASSY, CHUCKING

152 3-931-897-61 DAMPER (T)

153 3-039-627-01 LEVER (D)

154 3-040-165-01 RETAINER (DISC)

155 3-018-272-01 WASHER

156 3-931-895-01 SPRING (CH), TENSION

157 3-931-898-01 SPRING (FL), COMPRESSION

158 3-032-483-02 SPRING (KF1), TENSION

159 A-3307-471-A OVERALL ASSY, CHASSIS (M)

160 3-931-883-01 SPRING (TR), TENSION

161 3-931-881-01 LEVER (LOCK)

162 3-931-882-02 GEAR (MDL)

163 3-007-537-11 WHEEL (U), WORM

164 3-032-484-01 SPRING (KR1), TENSION

165 3-014-727-01 WHEEL (LW), WORM

166 3-039-626-01 LEVER (TR)

167 3-025-418-21 RING, LOADING

45

Page 37

4-5. CD MECHANISM SECTION (3)

(MG-383Z-121//Q)

207

201

M901

202

M902

208

203

205

#10

206

209

210

#8

204

213

212

Ref. No. Part No. Description Remark Ref. No. Part No. Description Remark

201 X-3378-598-1 CHASSIS (OP) ASSY (INCLUDING M901)

202 3-043-494-01 SPRING (SL), TORSION

203 3-040-170-01 BASE (DRIVING)

204 3-040-419-01 GEAR (MIDWAY)

* 205 1-659-835-12 LIMIT SW BOARD

* 208 1-659-834-11 SUB BOARD

0 210 8-820-103-03 PICK-UP, OPTICAL KSS-720A/K1RP

211

#8

The components identified by

mark 0 or dotted line with mark.

0 are critical for safety.

Replace only with part number

specified.

209 3-909-607-01 SCREW

211 3-931-834-01 SPRING (FEED), PLATE

212 1-676-707-21 PICK-UP FLEXIBLE BOARD

206 3-338-737-01 SCREW (2X3), +PS

207 1-659-880-11 MOTOR FLEXIBLE BOARD

46

213 A-3291-669-A SHAFT (FEED) ASSY

M902 A-3291-674-A MOTOR ASSY, SLED (SLED)

Page 38

SECTION 5

ELECTRICAL PARTS LIST

NOTE:

• Due to standardization, replacements in

the parts list may be different from the

parts specified in the diagrams or the

components used on the set.

• -XX and -X mean standardized parts, so

they may have some difference from the

original one.

• RESISTORS

All resistors are in ohms.

METAL:Metal-film resistor.

METAL OXIDE: Metal oxide-film resistor.

F:nonflammable

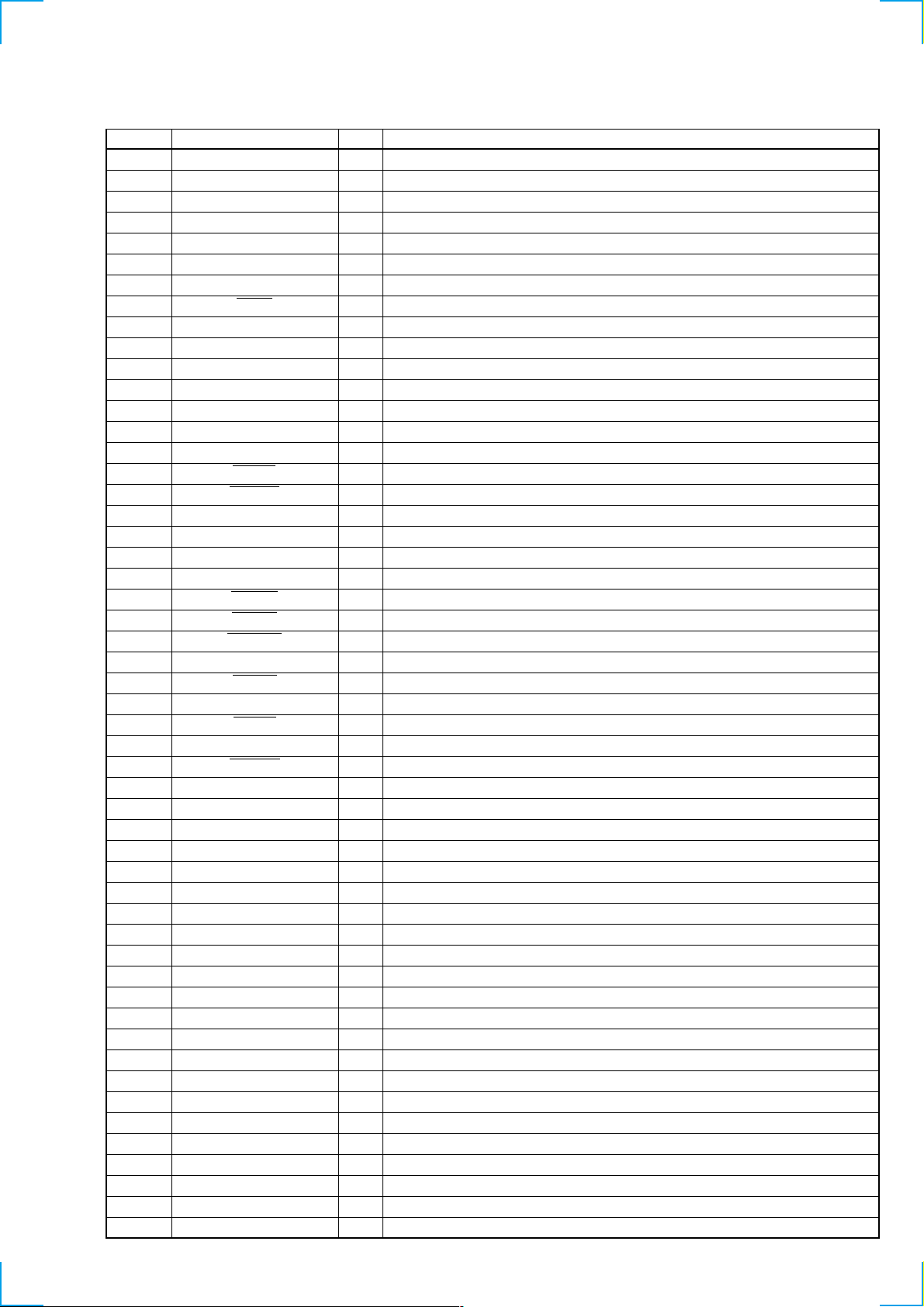

Ref. No. Part No. Description Remark Ref. No. Part No. Description Remark

* 1-659-836-11 DISC IN SW BOARD

****************

< SWITCH >

SW1 1-572-288-21 SWITCH, PUSH (DISC IN)

SW2 1-572-288-21 SWITCH, PUSH (SELF)

*************************************************************

KEY BOARD

**********

1-694-660-11 CONDUCTIVE BOARD, CONNECTION

* 3-040-992-01 HOLDER (LCD)

* 3-040-993-01 PLATE (LCD), LIGHT GUIDE

* 3-040-997-01 PLATE (LCD), GROUND

* 3-041-371-02 SHEET (REFLECTOR)

< CAPACITOR >

C951 1-164-004-11 CERAMIC CHIP 0.1uF 10% 25V

C952 1-163-037-11 CERAMIC CHIP 0.022uF 10% 25V

C953 1-163-251-11 CERAMIC CHIP 100PF 5% 50V

C954 1-164-004-11 CERAMIC CHIP 0.1uF 10% 25V

C955 1-164-004-11 CERAMIC CHIP 0.1uF 10% 25V

C956 1-164-489-11 CERAMIC CHIP 0.22uF 10% 16V

< CONNECTOR >

CN901 1-794-065-21 PLUG, CONNECTOR 14P

• Items marked “*” are not stocked since

they are seldom required for routine service.

Some delay should be anticipated

when ordering these items.

• SEMICONDUCTORS

In each case, u : µ, for example:

uA.. : µA.. uPA.. : µPA..

uPB.. : µPB.. uPC.. : µPC.. uPD.. : µPD..

• CAPACITORS

uF : µF

• COILS

uH : µH

LED901 8-719-061-16 LED CL-190SR-CD-T (C5000RX)

LED901 8-719-078-15 LED CL-165Y/PG-D-T (C4900R/C5000R)

LED902 8-719-061-16 LED CL-190SR-CD-T (C5000RX)

LED902 8-719-078-15 LED CL-165Y/PG-D-T (C4900R/C5000R)

LED903 8-719-061-16 LED CL-190SR-CD-T (C5000RX)

LED903 8-719-078-15 LED CL-165Y/PG-D-T (C4900R/C5000R)

LED904 8-719-061-16 LED CL-190SR-CD-T (C5000RX)

LED904 8-719-078-15 LED CL-165Y/PG-D-T (C4900R/C5000R)

LED910 8-719-078-19 LED LWA673-R1S2

LED911 8-719-078-19 LED LWA673-R1S2

LED912 8-719-078-19 LED LWA673-R1S2

LED913 8-719-078-19 LED LWA673-R1S2

LED914 8-719-078-19 LED LWA673-R1S2

LED915 8-719-078-19 LED LWA673-R1S2

LSW901 1-771-610-11 SWITCH, TACTILE (WITH LED) (OFF)

LSW901 1-771-883-21 SWITCH, TACTILE (WITH LED) (OFF)

LSW902 1-762-620-21 SWITCH, KEY BOARD (WITH LED) (SOURCE)

LSW902 1-771-476-11 SWITCH, KEY BOARD (WITH LED) (SOURCE)

LSW903 1-762-620-21 SWITCH, KEY BOARD (WITH LED) (SOUND)

DISC IN SW

The components identified by

mark 0 or dotted line with mark.

0 are critical for safety.

Replace only with part number

specified.

When indicating parts by reference

number, please include the board.

• Abbreviation

G : German model

< DIODE >

< SWITCH >

KEY

(C4900R/C5000R)

(C5000RX)

(C4900R/C5000R)

(C5000RX)

(C4900R/C5000R)

< DIODE >

D901 8-719-158-49 DIODE UDZ-TE-17-12B

D902 8-719-056-82 DIODE UDZ-TE-17-6.2B

D903 8-719-056-82 DIODE UDZ-TE-17-6.2B

D904 8-719-056-82 DIODE UDZ-TE-17-6.2B

D951 8-719-976-99 DIODE UDZ-TE-17-5.1B

D952 8-719-976-99 DIODE UDZ-TE-17-5.1B

< IC >

IC901 8-759-366-34 IC LC75824E

IC951 8-749-012-25 IC RS-170-TU

< LIQUID CRYSTAL DISPLAY >

LCD901 1-803-906-11 DISPLAY PANEL, LIQUID CRYSTAL

(C4900R/C5000R)

LCD901 1-803-906-31 DISPLAY PANEL, LIQUID CRYSTAL (C5000RX)

LSW903 1-771-476-11 SWITCH, KEY BOARD (WITH LED) (SOUND)

(C5000RX)

LSW904 1-762-620-21 SWITCH, KEY BOARD (WITH LED) (MENU)

(C4900R/C5000R)

LSW904 1-771-476-11 SWITCH, KEY BOARD (WITH LED) (MENU)

(C5000RX)

LSW905 1-762-620-21 SWITCH, KEY BOARD (WITH LED) (DSPL/PTY)

(C4900R/C5000R)

LSW905 1-771-476-11 SWITCH, KEY BOARD (WITH LED) (DSPL/PTY)

(C5000RX)

LSW906 1-762-620-21 SWITCH, KEY BOARD (WITH LED) (LIST)

(C4900R/C5000R)

LSW906 1-771-476-11 SWITCH, KEY BOARD (WITH LED) (LIST)

(C5000RX)

LSW907 1-762-620-21 SWITCH, KEY BOARD (WITH LED) (ENTER)

(C4900R/C5000R)

LSW907 1-771-476-11 SWITCH, KEY BOARD (WITH LED) (ENTER)

(C5000RX)

LSW908 1-771-610-11 SWITCH, TACTILE (WITH LED) (MODE)

(C4900R/C5000R)

47

Page 39

KEY

Ref. No. Part No. Description Remark Ref. No. Part No. Description Remark

LSW908 1-771-883-21 SWITCH, TACTILE (WITH LED) (MODE)

(C5000RX)

LSW909 1-762-737-11 SWITCH, KEY BOARD (WITH LED) (D-BASS)

LSW910 1-762-620-21 SWITCH, KEY BOARD (WITH LED) (TA)

(C4900R/C5000R)

LSW910 1-771-476-11 SWITCH, KEY BOARD (WITH LED) (TA)

(C5000RX)

LSW911 1-762-620-21 SWITCH, KEY BOARD (WITH LED) (AF)

(C4900R/C5000R)

LSW911 1-771-476-11 SWITCH, KEY BOARD (WITH LED) (AF)

(C5000RX)

LSW912 1-771-610-11 SWITCH, TACTILE (WITH LED) (6)

(C4900R/C5000R)

LSW912 1-771-883-21 SWITCH, TACTILE (WITH LED) (6) (C5000RX)

LSW913 1-771-610-11 SWITCH, TACTILE (WITH LED) (5)

(C4900R/C5000R)

LSW913 1-771-883-21 SWITCH, TACTILE (WITH LED) (5) (C5000RX)

LSW914 1-771-610-11 SWITCH, TACTILE (WITH LED) (4)

(C4900R/C5000R)

LSW914 1-771-883-21 SWITCH, TACTILE (WITH LED) (4) (C5000RX)

LSW915 1-771-610-11 SWITCH, TACTILE (WITH LED) (3)

(C4900R/C5000R)

LSW915 1-771-883-21 SWITCH, TACTILE (WITH LED) (3) (C5000RX)

LSW916 1-771-610-11 SWITCH, TACTILE (WITH LED) (2)

(C4900R/C5000R)

LSW916 1-771-883-21 SWITCH, TACTILE (WITH LED) (2) (C5000RX)

LSW917 1-771-610-11 SWITCH, TACTILE (WITH LED) (1)

(C4900R/C5000R)

LSW917 1-771-883-21 SWITCH, TACTILE (WITH LED) (1) (C5000RX)

< TRANSISTOR >

Q901 8-729-904-75 TRANSISTOR DTD114EK-T-146

(C4900R/C5000R)

Q902 8-729-904-75 TRANSISTOR DTD114EK-T-146

(C4900R/C5000R)

< RESISTOR >

R901 1-216-647-11 METAL CHIP 680 0.5% 1/10W

R902 1-216-647-11 METAL CHIP 680 0.5% 1/10W

R903 1-216-647-11 METAL CHIP 680 0.5% 1/10W

R904 1-216-651-11 METAL CHIP 1K 0.5% 1/10W

R905 1-216-655-11 METAL CHIP 1.5K 0.5% 1/10W

R906 1-216-655-11 METAL CHIP 1.5K 0.5% 1/10W

R907 1-216-659-11 METAL CHIP 2.2K 0.5% 1/10W

R908 1-216-663-11 METAL CHIP 3.3K 0.5% 1/10W

R909 1-216-667-11 METAL CHIP 4.7K 0.5% 1/10W

R910 1-216-671-11 METAL CHIP 6.8K 0.5% 1/10W

R911 1-208-806-11 RES-CHIP 10K 2% 1/10W

R912 1-216-647-11 METAL CHIP 680 0.5% 1/10W

R913 1-216-647-11 METAL CHIP 680 0.5% 1/10W

R914 1-216-647-11 METAL CHIP 680 0.5% 1/10W

R915 1-216-651-11 METAL CHIP 1K 0.5% 1/10W

R916 1-216-655-11 METAL CHIP 1.5K 0.5% 1/10W

R917 1-216-655-11 METAL CHIP 1.5K 0.5% 1/10W

R918 1-216-659-11 METAL CHIP 2.2K 0.5% 1/10W

R919 1-216-663-11 METAL CHIP 3.3K 0.5% 1/10W

R920 1-216-667-11 METAL CHIP 4.7K 0.5% 1/10W

R921 1-216-810-11 METAL CHIP 120 5% 1/16W

(C5000RX)

R921 1-216-811-11 METAL CHIP 150 5% 1/16W

(C4900R/C5000R)

R922 1-216-807-11 METAL CHIP 68 5% 1/16W

(C4900R/C5000R)

R923 1-216-811-11 METAL CHIP 150 5% 1/16W

(C4900R/C5000R)

R923 1-216-812-11 METAL CHIP 180 5% 1/16W

(C5000RX)

R924 1-216-807-11 METAL CHIP 68 5% 1/16W

(C4900R/C5000R)

R925 1-216-029-00 METAL CHIP 150 5% 1/10W

(C4900R/C5000R)

R925 1-216-031-00 METAL CHIP 180 5% 1/10W

(C5000RX)

R926 1-216-807-11 METAL CHIP 68 5% 1/16W

(C4900R/C5000R)

R927 1-216-029-00 METAL CHIP 150 5% 1/10W

(C4900R/C5000R)

R927 1-216-031-00 METAL CHIP 180 5% 1/10W

(C5000RX)

R928 1-216-807-11 METAL CHIP 68 5% 1/16W

(C4900R/C5000R)

R931 1-216-813-11 METAL CHIP 220 5% 1/16W

R932 1-216-813-11 METAL CHIP 220 5% 1/16W

R933 1-216-812-11 METAL CHIP 180 5% 1/16W

(C4900R/C5000R)

R933 1-216-813-11 METAL CHIP 220 5% 1/16W

(C5000RX)

R934 1-216-808-11 METAL CHIP 82 5% 1/16W

(C4900R/C5000R)

R938 1-216-809-11 METAL CHIP 100 5% 1/16W

R939 1-216-821-11 METAL CHIP 1K 5% 1/16W

(C5000RX)

R951 1-216-819-11 METAL CHIP 680 5% 1/16W

R952 1-216-057-00 METAL CHIP 2.2K 5% 1/10W

R953 1-216-857-11 METAL CHIP 1M 5% 1/16W

R954 1-216-049-11 RES-CHIP 1K 5% 1/10W

R955 1-216-049-11 RES-CHIP 1K 5% 1/10W

R956 1-216-821-11 METAL CHIP 1K 5% 1/16W

R957 1-216-851-11 METAL CHIP 330K 5% 1/16W

R958 1-216-033-00 METAL CHIP 220 5% 1/10W

R970 1-216-815-11 METAL CHIP 330 5% 1/16W

R971 1-216-815-11 METAL CHIP 330 5% 1/16W

R972 1-216-864-11 METAL CHIP 0 5% 1/16W

R973 1-216-815-11 METAL CHIP 330 5% 1/16W

R975 1-216-815-11 METAL CHIP 330 5% 1/16W

R976 1-216-815-11 METAL CHIP 330 5% 1/16W

R977 1-216-815-11 METAL CHIP 330 5% 1/16W

R980 1-216-864-11 METAL CHIP 0 5% 1/16W

R999 1-216-864-11 METAL CHIP 0 5% 1/16W

(C5000RX)

48

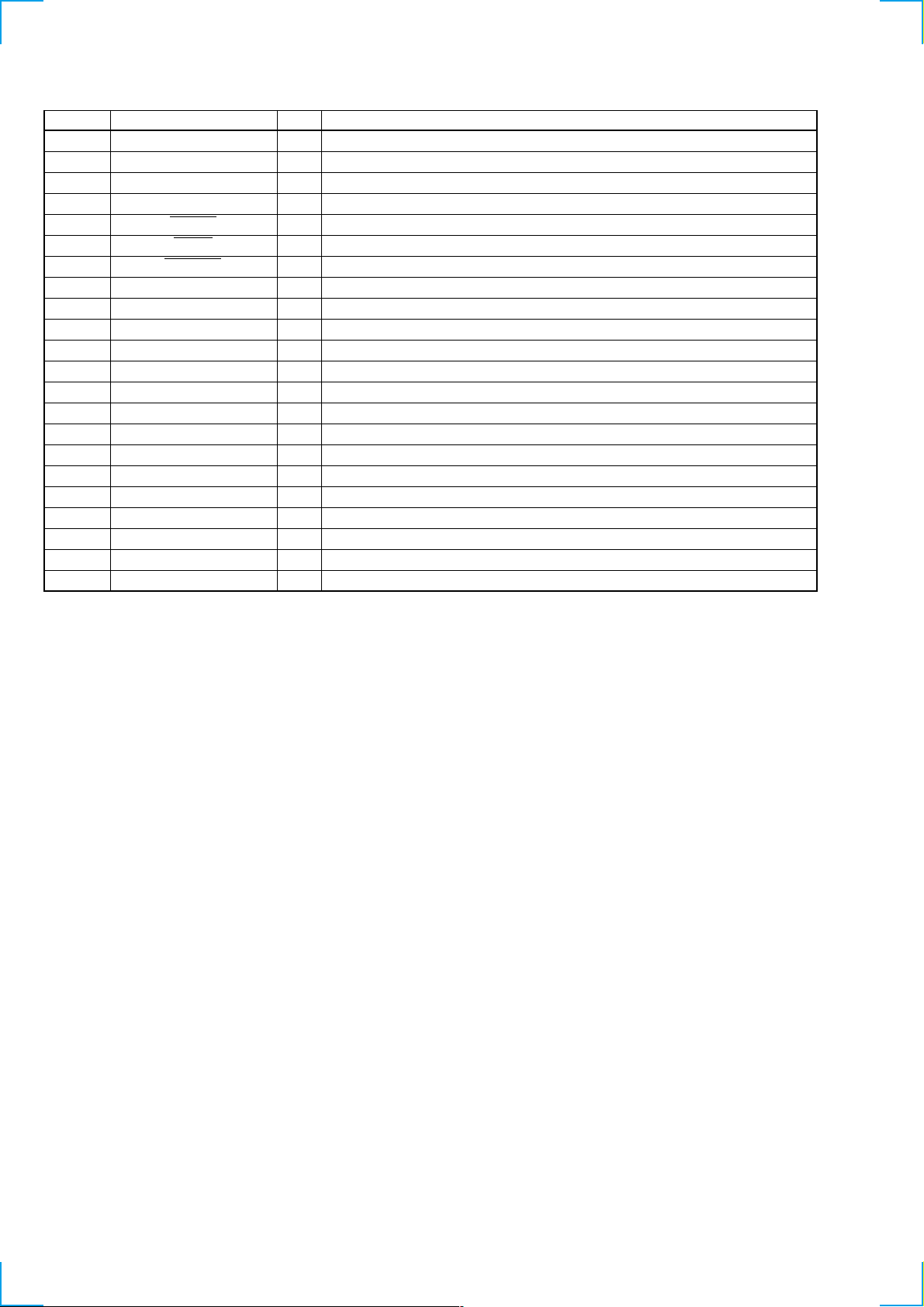

Page 40

KEY

Ref. No. Part No. Description Remark Ref. No. Part No. Description Remark

< ROTARY ENCODER >

RE901 1-475-014-12 ENCODER, ROTARY

< SWITCH >

C60 1-163-135-00 CERAMIC CHIP 560PF 5% 50V

C61 1-164-161-11 CERAMIC CHIP 0.0022uF 10% 100V

C62 1-163-009-11 CERAMIC CHIP 0.001uF 10% 50V

C63 1-164-315-11 CERAMIC CHIP 470PF 5% 50V

C90 1-162-964-11 CERAMIC CHIP 0.001uF 10% 50V

MAINLIMIT SW LOAD SW

S901 1-771-884-21 SWITCH, TACTILE (WITH LED) (SEEK/AMS

. m –)

S902 1-771-884-21 SWITCH, TACTILE (WITH LED) (DISC/PRST +)

S903 1-771-884-21 SWITCH, TACTILE (WITH LED) (SEEK/AMS

> M +)

S904 1-771-884-21 SWITCH, TACTILE (WITH LED) (DISC/PRST –)

*************************************************************

* 1-659-835-12 LIMIT SW BOARD

***************

< SWITCH >

SW3 1-572-688-11 SWITCH, PUSH (1 KEY) (LIMIT)

*************************************************************

* 1-659-837-11 LOAD SW BOARD

***************

< SWITCH >

SW4 1-572-288-21 SWITCH, PUSH (DOWN)

*************************************************************

* A-3326-196-A MAIN BOARD, COMPLETE (C5000R)

* A-3326-198-A MAIN BOARD, COMPLETE (C4900R)

* A-3326-210-A MAIN BOARD, COMPLETE (C5000RX)

*********************

* 3-040-996-51 HEAT SINK (4P) (C4900R)

3-040-996-61 HEAT SINK (6P) (C5000R/C5000RX)

* 3-040-998-01 BRACKET (IC)

* 3-041-011-01 HEAT SINK (REG)

7-685-647-11 SCREW BVTP 3X10 TYPE 2 N-S

7-685-793-09 SCREW +PTT 2.6X8 (S)

7-685-795-09 SCREW +PTT 2.6X12 (S)

< CAPACITOR >

C1 1-163-233-11 CERAMIC CHIP 18PF 5% 50V

C3 1-124-584-00 ELECT 100uF 20% 10V

C4 1-164-004-11 CERAMIC CHIP 0.1uF 10% 25V

C6 1-164-004-11 CERAMIC CHIP 0.1uF 10% 25V

C7 1-124-589-11 ELECT 47uF 20% 16V

C13 1-163-017-00 CERAMIC CHIP 0.0047uF 5% 50V

C14 1-163-021-11 CERAMIC CHIP 0.01uF 10% 50V

C52 1-164-004-11 CERAMIC CHIP 0.1uF 10% 25V

C53 1-163-229-11 CERAMIC CHIP 12PF 5% 50V

C54 1-163-229-11 CERAMIC CHIP 12PF 5% 50V

C55 1-164-004-11 CERAMIC CHIP 0.1uF 10% 25V

C56 1-124-589-11 ELECT 47uF 20% 16V

C57 1-164-004-11 CERAMIC CHIP 0.1uF 10% 25V

C58 1-163-263-11 CERAMIC CHIP 330PF 5% 50V

C59 1-164-505-11 CERAMIC CHIP 2.2uF 16V

C91 1-162-964-11 CERAMIC CHIP 0.001uF 10% 50V

C92 1-162-964-11 CERAMIC CHIP 0.001uF 10% 50V

C93 1-163-133-00 CERAMIC CHIP 470PF 5% 50V

C94 1-162-915-11 CERAMIC CHIP 10PF 0.5PF 50V

C95 1-107-823-11 CERAMIC CHIP 0.47uF 10% 16V

C96 1-163-809-11 CERAMIC CHIP 0.047uF 10% 25V

C97 1-164-004-11 CERAMIC CHIP 0.1uF 10% 25V

C98 1-164-004-11 CERAMIC CHIP 0.1uF 10% 25V

C101 1-126-160-11 ELECT 1uF 20% 50V

C110 1-163-251-11 CERAMIC CHIP 100PF 5% 50V

C111 1-109-982-11 CERAMIC CHIP 1uF 10% 10V

C113 1-109-982-11 CERAMIC CHIP 1uF 10% 10V

C121 1-164-004-11 CERAMIC CHIP 0.1uF 10% 25V

C122 1-163-037-11 CERAMIC CHIP 0.022uF 10% 25V

C123 1-163-037-11 CERAMIC CHIP 0.022uF 10% 25V

C131 1-124-233-11 ELECT 10uF 20% 16V

C141 1-163-251-11 CERAMIC CHIP 100PF 5% 50V

C142 1-126-160-11 ELECT 1uF 20% 50V

C151 1-162-970-11 CERAMIC CHIP 0.01uF 10% 25V

C152 1-124-584-00 ELECT 100uF 20% 10V

C153 1-163-009-11 CERAMIC CHIP 0.001uF 10% 50V

C156 1-163-017-00 CERAMIC CHIP 0.0047uF 5% 50V

C157 1-107-823-11 CERAMIC CHIP 0.47uF 10% 16V

C159 1-162-970-11 CERAMIC CHIP 0.01uF 10% 25V

C161 1-124-233-11 ELECT 10uF 20% 16V

C162 1-164-489-11 CERAMIC CHIP 0.22uF 10% 16V

C171 1-126-163-11 ELECT 4.7uF 20% 50V

C172 1-163-251-11 CERAMIC CHIP 100PF 5% 50V

(C5000R/C5000RX)

C173 1-164-489-11 CERAMIC CHIP 0.22uF 10% 16V

C174 1-162-919-11 CERAMIC CHIP 22PF 5% 50V

C181 1-126-163-11 ELECT 4.7uF 20% 50V

C182 1-163-251-11 CERAMIC CHIP 100PF 5% 50V

C183 1-164-489-11 CERAMIC CHIP 0.22uF 10% 16V

C184 1-162-919-11 CERAMIC CHIP 22PF 5% 50V

C191 1-216-295-00 SHORT 0

C192 1-216-295-00 SHORT 0

C193 1-216-295-00 SHORT 0

C201 1-126-160-11 ELECT 1uF 20% 50V

C210 1-163-251-11 CERAMIC CHIP 100PF 5% 50V

C241 1-163-251-11 CERAMIC CHIP 100PF 5% 50V

C242 1-126-160-11 ELECT 1uF 20% 50V

C271 1-126-163-11 ELECT 4.7uF 20% 50V

C272 1-163-251-11 CERAMIC CHIP 100PF 5% 50V

(C5000R/C5000RX)

C273 1-164-489-11 CERAMIC CHIP 0.22uF 10% 16V

C274 1-162-919-11 CERAMIC CHIP 22PF 5% 50V

C281 1-126-163-11 ELECT 4.7uF 20% 50V

49

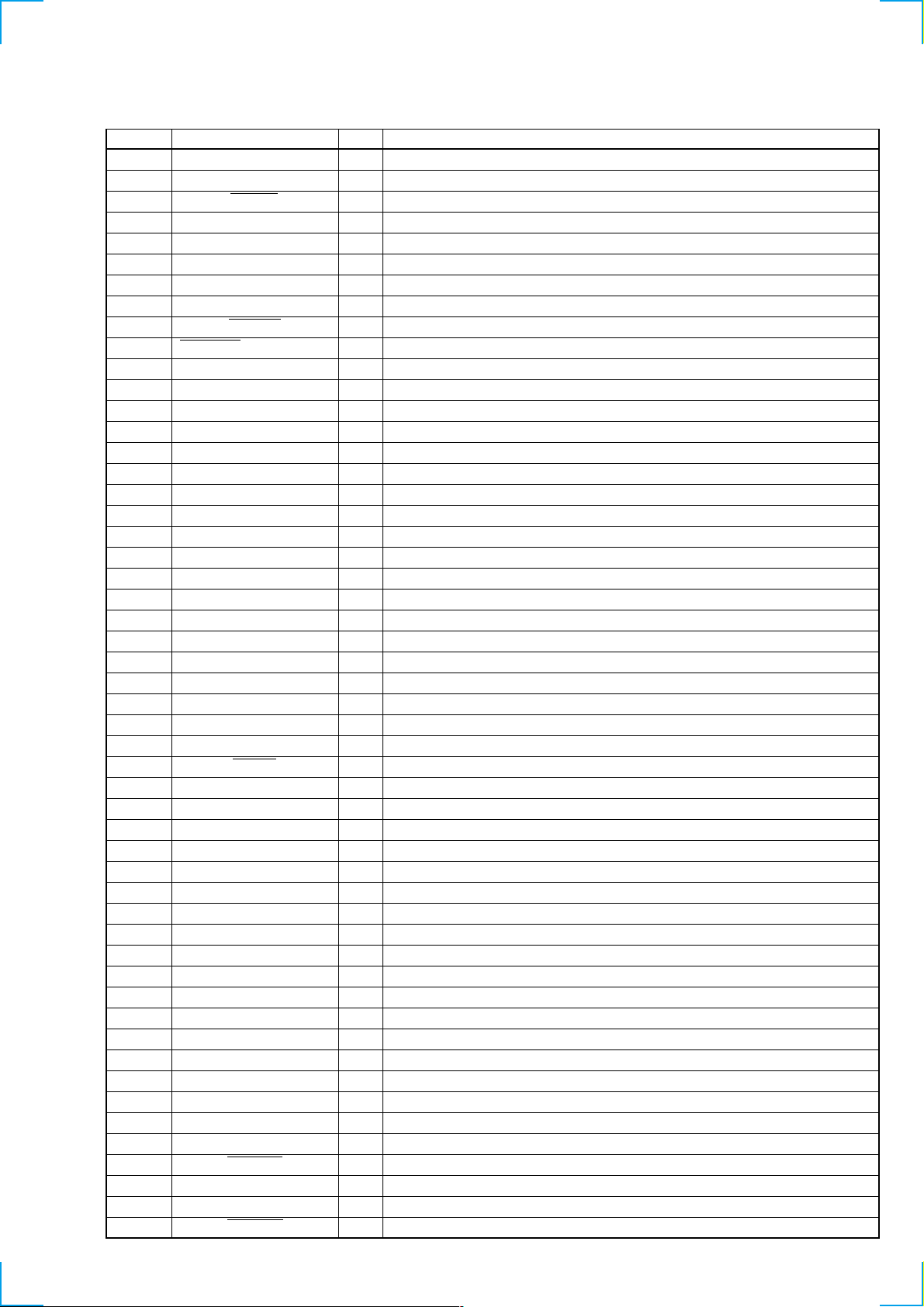

Page 41

MAIN

Ref. No. Part No. Description Remark Ref. No. Part No. Description Remark

C282 1-163-251-11 CERAMIC CHIP 100PF 5% 50V

C283 1-164-489-11 CERAMIC CHIP 0.22uF 10% 16V

C284 1-162-919-11 CERAMIC CHIP 22PF 5% 50V

C361 1-164-004-11 CERAMIC CHIP 0.1uF 10% 25V

C362 1-126-157-11 ELECT 10uF 20% 16V

C673 1-126-157-11 ELECT 10uF 20% 16V

C674 1-124-233-11 ELECT 10uF 20% 16V

C675 1-124-233-11 ELECT 10uF 20% 16V

C676 1-126-157-11 ELECT 10uF 20% 16V

C682 1-163-021-11 CERAMIC CHIP 0.01uF 10% 50V

C363 1-164-004-11 CERAMIC CHIP 0.1uF 10% 25V

C364 1-126-157-11 ELECT 10uF 20% 16V

C365 1-164-004-11 CERAMIC CHIP 0.1uF 10% 25V

C366 1-124-233-11 ELECT 10uF 20% 16V

C367 1-109-982-11 CERAMIC CHIP 1uF 10% 10V

C368 1-109-982-11 CERAMIC CHIP 1uF 10% 10V

C369 1-163-021-11 CERAMIC CHIP 0.01uF 10% 50V

C370 1-163-021-11 CERAMIC CHIP 0.01uF 10% 50V

C371 1-163-021-11 CERAMIC CHIP 0.01uF 10% 50V

C372 1-163-021-11 CERAMIC CHIP 0.01uF 10% 50V

C373 1-163-021-11 CERAMIC CHIP 0.01uF 10% 50V

C374 1-124-584-00 ELECT 100uF 20% 10V

C375 1-124-584-00 ELECT 100uF 20% 10V

C502 1-164-004-11 CERAMIC CHIP 0.1uF 10% 25V

C503 1-164-004-11 CERAMIC CHIP 0.1uF 10% 25V

C504 1-164-004-11 CERAMIC CHIP 0.1uF 10% 25V

C505 1-164-004-11 CERAMIC CHIP 0.1uF 10% 25V

C506 1-163-233-11 CERAMIC CHIP 18PF 5% 50V

C507 1-163-102-00 CERAMIC CHIP 24PF 5% 50V

C509 1-163-021-11 CERAMIC CHIP 0.01uF 10% 50V

C510 1-124-584-00 ELECT 100uF 20% 10V

C511 1-164-004-11 CERAMIC CHIP 0.1uF 10% 25V

C512 1-163-133-00 CERAMIC CHIP 470PF 5% 50V

C513 1-163-259-11 CERAMIC CHIP 220PF 5% 50V

C551 1-164-222-11 CERAMIC CHIP 0.22uF 25V

C552 1-164-222-11 CERAMIC CHIP 0.22uF 25V

C571 1-162-927-11 CERAMIC CHIP 100PF 5% 50V

(C5000R/C5000RX)

C600 1-164-489-11 CERAMIC CHIP 0.22uF 10% 16V

C601 1-135-473-21 ELECT 3300uF 20% 16V

C602 1-163-251-11 CERAMIC CHIP 100PF 5% 50V

C603 1-162-927-11 CERAMIC CHIP 100PF 5% 50V

C611 1-126-160-11 ELECT 1uF 20% 50V

C612 1-126-160-11 ELECT 1uF 20% 50V

C614 1-126-157-11 ELECT 10uF 20% 16V

C616 1-107-823-11 CERAMIC CHIP 0.47uF 10% 16V

C617 1-136-165-00 MYLAR 0.1uF 5% 50V

C621 1-124-589-11 ELECT 47uF 20% 16V

C623 1-109-982-11 CERAMIC CHIP 1uF 10% 10V

C631 1-164-222-11 CERAMIC CHIP 0.22uF 25V

C632 1-164-222-11 CERAMIC CHIP 0.22uF 25V

C641 1-162-964-11 CERAMIC CHIP 0.001uF 10% 50V

C653 1-163-021-11 CERAMIC CHIP 0.01uF 10% 50V

C654 1-125-710-11 DOUBLE LAYERS 0.1F 5.5V

C655 1-124-584-00 ELECT 100uF 20% 10V

C661 1-109-982-11 CERAMIC CHIP 1uF 10% 10V

C671 1-126-157-11 ELECT 10uF 20% 16V

C672 1-126-157-11 ELECT 10uF 20% 16V

C701 1-162-970-11 CERAMIC CHIP 0.01uF 10% 25V

C702 1-164-004-11 CERAMIC CHIP 0.1uF 10% 25V

C703 1-164-227-11 CERAMIC CHIP 0.022uF 10% 25V

C704 1-165-319-11 CERAMIC CHIP 0.1uF 50V

C705 1-126-935-11 ELECT 470uF 20% 16V

< CONNECTOR >

CN301 1-764-617-12 PIN, CONNECTOR (PC BOARD) 30P

CN500 1-784-456-11 CONNECTOR, FFC/FPC 14P

CN601 1-774-701-11 PIN, CONNECTOR 16P

CN701 1-580-907-31 PLUG, CONNECTOR (BUS CONTROL IN)

< JACK >

CNJ151 1-774-699-12 JACK, PIN 4P (BUS AUDIO IN,

AUDIO OUT REAR) (C4900R)

CNJ151 1-774-700-11 JACK, PIN 6P (BUS AUDIO IN,

AUDIO OUT REAR,AUDIO OUT FRONT)

(C5000R/C5000RX)

< DIODE >

D1 8-719-073-01 DIODE MA111-TX

D2 8-719-067-56 DIODE MA112-TX

D90 8-719-073-01 DIODE MA111-TX

D91 8-719-073-01 DIODE MA111-TX

D92 8-719-976-99 DIODE UDZ-TE-17-5.1B

D131 8-719-422-12 DIODE UDZ-TE-17-3.9B

D301 8-719-914-44 DIODE DAP202K-T-146

D302 8-719-073-01 DIODE MA111-TX

D361 8-719-035-98 DIODE MA4110-M(TA)

D362 8-719-017-62 DIODE MA8068-L-TX

D363 8-719-158-15 DIODE UDZ-TE-17-5.6B

D501 8-719-914-44 DIODE DAP202K-T-146

D502 8-719-073-01 DIODE MA111-TX

D551 8-719-158-49 DIODE UDZ-TE-17-12B

D552 8-719-056-82 DIODE UDZ-TE-17-6.2B

D553 8-719-056-82 DIODE UDZ-TE-17-6.2B

D554 8-719-056-82 DIODE UDZ-TE-17-6.2B

D555 8-719-056-82 DIODE UDZ-TE-17-6.2B

D556 8-719-056-82 DIODE UDZ-TE-17-6.2B

D557 8-719-056-82 DIODE UDZ-TE-17-6.2B

D558 8-719-056-82 DIODE UDZ-TE-17-6.2B

D559 8-719-056-82 DIODE UDZ-TE-17-6.2B

D560 8-719-056-82 DIODE UDZ-TE-17-6.2B

D561 8-719-056-93 DIODE UDZ-TE-17-18B

D562 8-719-056-82 DIODE UDZ-TE-17-6.2B

D571 8-719-073-01 DIODE MA111-TX (C5000R/C5000RX)

D601 8-719-049-38 DIODE 1N5404TU

D602 8-719-056-93 DIODE UDZ-TE-17-18B

D603 8-719-056-93 DIODE UDZ-TE-17-18B

50

Page 42

MAIN

Ref. No. Part No. Description Remark Ref. No. Part No. Description Remark

D604 8-719-056-82 DIODE UDZ-TE-17-6.2B

D605 8-719-056-93 DIODE UDZ-TE-17-18B (C5000R/C5000RX)

D611 8-719-079-55 DIODE PTZ-TE25-22

D612 8-719-079-55 DIODE PTZ-TE25-22

D613 8-719-079-55 DIODE PTZ-TE25-22

D614 8-719-079-55 DIODE PTZ-TE25-22

D615 8-719-079-55 DIODE PTZ-TE25-22

D616 8-719-079-55 DIODE PTZ-TE25-22

D617 8-719-079-55 DIODE PTZ-TE25-22

D618 8-719-079-55 DIODE PTZ-TE25-22

D621 8-719-422-12 DIODE UDZ-TE-17-3.9B

D622 8-719-073-01 DIODE MA111-TX

D624 8-719-158-15 DIODE UDZ-TE-17-5.6B

D631 8-719-158-49 DIODE UDZ-TE-17-12B

D653 8-719-073-01 DIODE MA111-TX

D661 8-719-073-01 DIODE MA111-TX

D662 8-719-420-14 DIODE MA8082-M(TX)

D671 8-719-053-18 DIODE 1SR154-400TE-25

D672 8-719-053-18 DIODE 1SR154-400TE-25

D673 8-719-053-18 DIODE 1SR154-400TE-25

D674 8-719-053-18 DIODE 1SR154-400TE-25

D675 8-719-067-56 DIODE MA112-TX

D676 8-719-073-01 DIODE MA111-TX

D677 8-719-073-01 DIODE MA111-TX

D701 8-719-978-69 DIODE UDZ-TE-17-16B

D702 8-719-017-62 DIODE MA8068-L-TX

D703 8-719-056-82 DIODE UDZ-TE-17-6.2B

D704 8-719-056-93 DIODE UDZ-TE-17-18B

D705 8-719-056-93 DIODE UDZ-TE-17-18B

D706 8-719-072-70 DIODE MA2ZD14001S0

J1 1-764-808-21 JACK (ANTENNA)

J501 1-566-822-41 JACK (REMOTE IN)

JC1 1-216-296-00 SHORT 0

JC2 1-216-296-00 SHORT 0

JC4 1-216-296-00 SHORT 0

JC5 1-216-296-00 SHORT 0

JC16 1-216-295-00 SHORT 0

JC31 1-216-295-00 SHORT 0

JC50 1-216-295-00 SHORT 0

JC53 1-216-295-00 SHORT 0

JC90 1-216-295-00 SHORT 0

JC191 1-216-295-00 SHORT 0

JC192 1-216-295-00 SHORT 0

JC193 1-216-295-00 SHORT 0

JC194 1-216-295-00 SHORT 0

JC302 1-216-864-11 METAL CHIP 0 5% 1/16W

JC502 1-216-295-00 SHORT 0

JC601 1-216-864-11 METAL CHIP 0 5% 1/16W

JC671 1-216-295-00 SHORT 0

JC673 1-216-864-11 METAL CHIP 0 5% 1/16W

L601 1-419-476-11 COIL, CHOKE (2000)

L671 1-410-989-11 INDUCTOR CHIP 0.47uH

< JACK >

< JUMPER RESISTOR >

< COIL >

< TRANSISTOR >

D708 8-719-073-01 DIODE MA111-TX

D709 8-719-073-01 DIODE MA111-TX

D710 8-719-073-01 DIODE MA111-TX

D901 8-719-109-97 DIODE RD6.8ESB2

D902 8-719-109-97 DIODE RD6.8ESB2

< FERRITE BEAD >

FB361 1-414-233-22 FERRITE BEAD INDUCTOR

FB362 1-414-233-22 FERRITE BEAD INDUCTOR

FB363 1-414-233-22 FERRITE BEAD INDUCTOR

FB501 1-414-233-22 FERRITE BEAD INDUCTOR

< IC >

IC51 8-759-650-68 IC SAA6588T/V2-118

IC90 8-759-909-71 IC BA4558F-E2

IC151 8-759-653-27 IC TDA7402TR

IC501 8-759-663-56 IC MB90574PMT-G-266-BND

IC611 8-759-663-88 IC TA8268H

IC652 8-759-574-61 IC XC61AN4302MR

IC671 8-759-661-47 IC BA4908-V3

IC701 8-759-449-89 IC BA8270F-E2

Q1 8-729-120-28 TRANSISTOR 2SC2412K-T-146-QR

Q90 8-729-900-53 TRANSISTOR DTC114EKA-T146

Q111 8-729-920-21 TRANSISTOR DTC314TK-T-146

Q121 8-729-920-21 TRANSISTOR DTC314TK-T-146

Q131 8-729-921-25 TRANSISTOR FMC2-T148

Q171 8-729-920-21 TRANSISTOR DTC314TK-T-146

Q181 8-729-920-21 TRANSISTOR DTC314TK-T-146

Q271 8-729-920-21 TRANSISTOR DTC314TK-T-146

Q281 8-729-920-21 TRANSISTOR DTC314TK-T-146

Q361 8-729-019-00 TRANSISTOR 2SD2394-G

Q362 8-729-019-00 TRANSISTOR 2SD2394-G

Q363 8-729-921-25 TRANSISTOR FMC2-T148

Q364 8-729-015-11 TRANSISTOR 2SD1802FAST-TL

Q365 8-729-921-25 TRANSISTOR FMC2-T148

Q551 8-729-921-25 TRANSISTOR FMC2-T148

Q571 8-729-120-28 TRANSISTOR 2SC2412K-T-146-QR

(C5000R/C5000RX)

Q621 8-729-027-23 TRANSISTOR DTA114EKA-T146

Q622 8-729-021-94 FET 2SK1657-T1B

Q631 8-729-423-99 TRANSISTOR 2SD2137-OP-TA

Q633 8-729-921-25 TRANSISTOR FMC2-T148

Q651 8-729-027-23 TRANSISTOR DTA114EKA-T146

Q652 8-729-027-23 TRANSISTOR DTA114EKA-T146

51

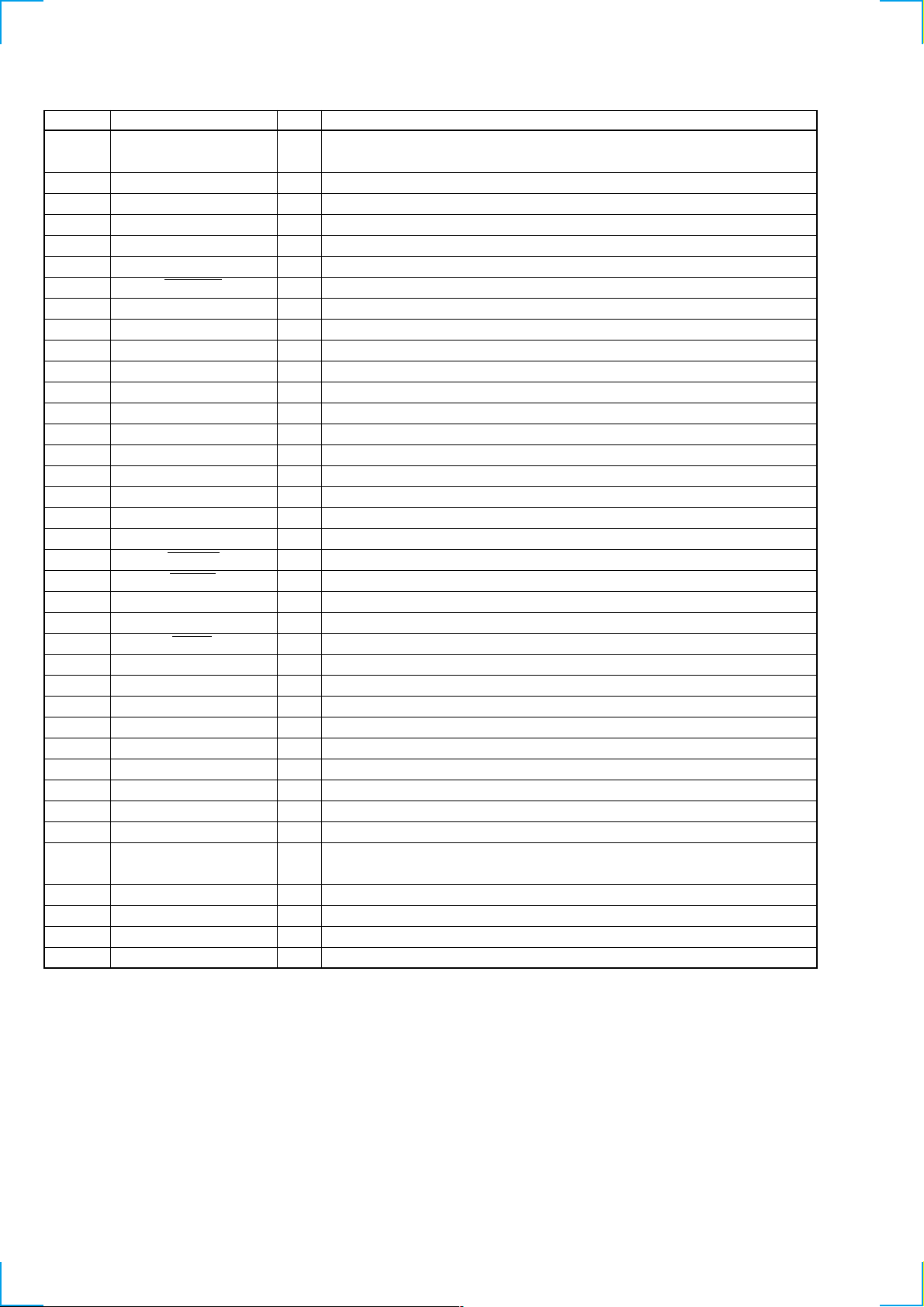

Page 43

MAIN

Ref. No. Part No. Description Remark Ref. No. Part No. Description Remark

Q661 8-729-120-28 TRANSISTOR 2SC2412K-T-146-QR

Q701 8-729-900-53 TRANSISTOR DTC114EKA-T146

Q704 8-729-027-23 TRANSISTOR DTA114EKA-T146

Q705 8-729-027-23 TRANSISTOR DTA114EKA-T146

Q706 8-729-120-28 TRANSISTOR 2SC2412K-T-146-QR

R241 1-216-025-11 RES-CHIP 100 5% 1/10W

R242 1-216-073-00 METAL CHIP 10K 5% 1/10W

R271 1-216-033-00 METAL CHIP 220 5% 1/10W

R272 1-216-081-00 METAL CHIP 22K 5% 1/10W

R273 1-216-089-11 RES-CHIP 47K 5% 1/10W

< RESISTOR >

R1 1-216-295-00 SHORT 0

R4 1-216-025-11 RES-CHIP 100 5% 1/10W

R5 1-216-025-11 RES-CHIP 100 5% 1/10W

R6 1-216-025-11 RES-CHIP 100 5% 1/10W

R7 1-216-025-11 RES-CHIP 100 5% 1/10W

R8 1-216-295-00 SHORT 0

R9 1-216-041-00 METAL CHIP 470 5% 1/10W

R12 1-216-837-11 METAL CHIP 22K 5% 1/16W

R20 1-216-057-00 METAL CHIP 2.2K 5% 1/10W

R53 1-216-853-11 METAL CHIP 470K 5% 1/16W

R54 1-216-821-11 METAL CHIP 1K 5% 1/16W

R55 1-216-061-00 METAL CHIP 3.3K 5% 1/10W

R56 1-216-817-11 METAL CHIP 470 5% 1/16W

R57 1-216-809-11 METAL CHIP 100 5% 1/16W

R58 1-216-025-11 RES-CHIP 100 5% 1/10W

R59 1-216-001-00 METAL CHIP 10 5% 1/10W

R60 1-216-797-11 METAL CHIP 10 5% 1/16W

R90 1-216-825-11 METAL CHIP 2.2K 5% 1/16W

R91 1-216-825-11 METAL CHIP 2.2K 5% 1/16W

R92 1-216-025-11 RES-CHIP 100 5% 1/10W

R93 1-216-845-11 METAL CHIP 100K 5% 1/16W

R94 1-216-829-11 METAL CHIP 4.7K 5% 1/16W

R95 1-216-121-11 RES-CHIP 1M 5% 1/10W

R96 1-216-025-11 RES-CHIP 100 5% 1/10W

R97 1-216-833-11 RES-CHIP 10K 5% 1/16W

R98 1-216-833-11 RES-CHIP 10K 5% 1/16W

R108 1-216-057-00 METAL CHIP 2.2K 5% 1/10W

R111 1-216-864-11 METAL CHIP 0 5% 1/16W

R112 1-216-841-11 METAL CHIP 47K 5% 1/16W

R121 1-216-049-11 RES-CHIP 1K 5% 1/10W

R122 1-216-085-00 METAL CHIP 33K 5% 1/10W

R131 1-216-037-00 METAL CHIP 330 5% 1/10W

R132 1-216-045-00 METAL CHIP 680 5% 1/10W

R141 1-216-025-11 RES-CHIP 100 5% 1/10W

R142 1-216-073-00 METAL CHIP 10K 5% 1/10W

R152 1-216-841-11 METAL CHIP 47K 5% 1/16W

R153 1-216-025-11 RES-CHIP 100 5% 1/10W

R154 1-216-025-11 RES-CHIP 100 5% 1/10W

R156 1-216-809-11 METAL CHIP 100 5% 1/16W

R171 1-216-033-00 METAL CHIP 220 5% 1/10W

R172 1-216-081-00 METAL CHIP 22K 5% 1/10W

R173 1-216-089-11 RES-CHIP 47K 5% 1/10W

R181 1-216-033-00 METAL CHIP 220 5% 1/10W

R182 1-216-081-00 METAL CHIP 22K 5% 1/10W

R183 1-216-089-11 RES-CHIP 47K 5% 1/10W

R208 1-216-057-00 METAL CHIP 2.2K 5% 1/10W

R281 1-216-033-00 METAL CHIP 220 5% 1/10W

R282 1-216-081-00 METAL CHIP 22K 5% 1/10W

R283 1-216-089-11 RES-CHIP 47K 5% 1/10W

R302 1-216-845-11 METAL CHIP 100K 5% 1/16W

R361 1-216-041-00 METAL CHIP 470 5% 1/10W

R362 1-216-041-00 METAL CHIP 470 5% 1/10W

R363 1-216-041-00 METAL CHIP 470 5% 1/10W

R364 1-216-041-00 METAL CHIP 470 5% 1/10W

R365 1-216-041-00 METAL CHIP 470 5% 1/10W

R504 1-216-057-00 METAL CHIP 2.2K 5% 1/10W

R505 1-216-057-00 METAL CHIP 2.2K 5% 1/10W

R506 1-216-057-00 METAL CHIP 2.2K 5% 1/10W

R507 1-216-073-00 METAL CHIP 10K 5% 1/10W

R509 1-216-097-11 RES-CHIP 100K 5% 1/10W

(C5000RX)

R510 1-216-097-11 RES-CHIP 100K 5% 1/10W

(C4900R/C5000R)

R520 1-216-097-11 RES-CHIP 100K 5% 1/10W

R522 1-216-097-11 RES-CHIP 100K 5% 1/10W

R523 1-216-845-11 METAL CHIP 100K 5% 1/16W

R524 1-216-073-00 METAL CHIP 10K 5% 1/10W

R525 1-216-073-00 METAL CHIP 10K 5% 1/10W

R527 1-216-845-11 METAL CHIP 100K 5% 1/16W

R529 1-216-049-11 RES-CHIP 1K 5% 1/10W

R531 1-216-839-11 METAL CHIP 33K 5% 1/16W

(C5000R/C5000RX)

R532 1-216-833-11 RES-CHIP 10K 5% 1/16W

(C5000R/C5000RX)