Page 1

Introduction

The Pocket Guide CPU 922/CPU 928/CPU 928B/

CPU 948

Order No. 6ES5 997-3UA22

is included with this manual.

1

SIMATIC S5

S5-155U

CPU 948

Programming Guide

Order No. 6ES5 998-3PR21

Release 03

User Program

Program Execution

Operating Sta tuses and Pr ogram

Execution Levels

Interrupt and Error Diagnosis

Integrated Special Functions

Extended Data Block DX 0

Memory Assignment and

Memory Organization

2

3

4

5

6

7

8

Memory Access Using

Absolute Addresses

Multiprocessor Mode and

Communication in the S5-155U

PG Interfaces and

Functions

Appendix

Further Reading

List of Abbreviations,

List of Key Words,

List of Tables and Figures

9

10

11

12

13

14

C79000-H8576-C848-03

Page 2

Copyright

Copyright © Siemens AG 1993 All Rights Reserved

The reprod uction , transm issio n or use of th is doc ument or it s conten ts is no t permitt ed witho ut expr ess

written authority.

Offenders wi ll b e li able for dama ges. Al l ri ghts , in clud ing righ ts c reat ed b y pa tent grant or regi stra tion of a

utility mod el or de sign, ar e reserv ed.

Disclaimer of liability

We have chec ked th e conten ts of this manual for agree ment wit h the hard ware an d softwar e descri bed.

Since dev iation s cann ot be prec luded en tirely , we cann ot guara ntee ful l agreem ent. How ever, the data in

this manual are reviewed regularly and any necessary corrections included in subsequent editions. Suggestions for improvement are welcomed.

Technica l da ta s ubje ct t o ch ange.

Safety-relate d guidelines

This manu al c onta ins noti ces whi ch y ou s houl d obse rve to e nsur e yo ur ow n pers on al s afet y, as wel l

as to protec t the prod uct and co nnec ted equi pment. Th ese noti ces ar e highli ghted in the manu al by

a warning tri angle and ar e marked as follow s accord ing to the level of da nger:

Warning

indicat es that de ath, sev ere pers onal injury or substan tial pro perty da mage ca n result

if proper precautions are not taken.

!

Caution

indicat es t hat m inor p erso nal inju ry o r prop erty dama ge c an r esul t if p rope r

precautions are not taken.

!

Only qualif ied pers onne l should be allo wed to in stall an d work on this equi pment. Q ualifi ed perso ns

are defined as persons who are authorized to commission, to ground and to tag equipment, systems

and circui ts in ac cordan ce with establi shed s afety pr actice s and st andard s.

Siemens Aktiengesellschaft

6ES5 998-3PR21

EWK Elektronikwerk Karlsruhe

Printed in the Federal Republic of Germany

Page 3

How to Use this Manual

Scope

This programming guide describes the following versions of the

CPU 948 and its system software:

Versions of the CPU 948

•• CPU 948-1 with 640 Kbytes of user memory,

Order no . 6ES5 948-3UA11, from vers ion A03

•• CPU 948-2 with 1 664 Kbytes of user memory,

Order no . 6ES5 948-3UA21, from version A03

CPU 948 Programming Guide

C79000-H8576-C848-03

0 - 1

Page 4

How to Use this Manual

Overview of the Chapters

Chapter 1

Chapter 2

Chapter 3

This informs you about the area s of app lica tion of the S5-1 55U

programmable controller with the CPU 948 and its device structur e.

It explains the typical mode of operation of the CPU and illustrates

how a CPU program i s str uc tured.

The chapter also conta ins sugge stions a bout ho w to tackle

programming an d whic h ch ar ac teristics of the CPU 948 are impor tan t

for programming.

If you have already worke d with the CPU 946/94 7 an d want to know

the differences betwe en these CPUs and the CPU 948 you will find

this information in this chapter.

This explains the components of a STE P 5 user pr ogra m an d how the

program can be structured.

This is intended for readers who do not yet have muc h expe rie nc e of

using the STEP 5 programm ing la ngua ge . It therefore deal s with the

basics of STEP 5 programming and ex pla ins the STEP 5 operations in

detail (with examples).

Experience d re ad er s who may find that the information about specific

operations in the pocke t guid e i s inade qu ate , ca n use Sec tion 3.5 as a

reference section.

Chapter 4

Chapter 5

0 - 2 C79000-H8576-C848-03

This provides an overvie w of the mod es and progr am exe cu tion levels

of the CPU 948. It provides you with detailed information about

various start-up modes and the associated organization blocks in

which you can program your routines for differrent start-up situations.

The chapter also explains th e dif fe re nc es betwe en the pr ogram

execution levels "cyc lic proc essing" , "tim e-controlled processing" and

"interrupt-driven processing" and whic h blo cks are available for your

user program.

This informs you about errors to be avo ide d whe n pla nning and

writing your STEP 5 programs.

The chapter tells you about the help you can obta in fr om the syste m

program for diagnosing errors and which reactions can be expected

and informs you ab ou t the blocks in which you can prog ram reactions

to certain errors.

The chapter also explains the CPU 948 self-test.

CPU 948 Programming Guide

Page 5

How to Use this Manual

Chapter 6

Chapter 7

Chapter 8

Chapter 9

This covers the special functions integrated in the system program. It

tells you how to use the special functions and how to call and assign

parameters to the special func tion OBs. The chapte r also ex pla ins how

to recognize and deal with er ro rs in the pr ocessin g of a specia l

function.

This describes the use of data blo ck DX 0 and its structur e. The

chapter infor ms you of the significance of the variou s DX 0

parameters. Based on examples, you will lear n how to create data

block DX 0 or how to assign the parameters in a screen form.

This is a reference section for experienced system users. It provides

information about the me mo ry organ ization of the CPU 948 and

certain system data words whic h conta in information that can be

called up by the user.

This is also for experienced system user s. The cha pte r ex pla ins how to

address data in certain memory areas using absolute addresses.

Chapter 10

Chapter 11

Chapter 12

This explains when the multipro ce ssor mode ca n be used an d how

data can be exchanged between the CPUs and CPs. The chapter

provides information ab out pro gram ming for multiprocessor operatio n.

The remainder of the ch ap ter provid es detailed information and

application examples for exchanging larger amounts of data in the

multiprocessor mode (multiprocessor communication).

This tells you how to connect your CPU to a PG and the functions

provided by the PG software to test your STEP 5 prog ra m.

This contains the Appendix with tec hn ica l data (e. g. typical operation

execution times, system runtimes, memory capacity) of the CPU 948.

CPU 948 Programming Guide

C79000-H8576-C848-03

0 - 3

Page 6

How to Use this Manual

Chapter 13

Chapter 14

This lists documentation for further reading.

This is intended to help you find themes quickly and contains a list of

abbreviations and a list of keywords as well as lists of all the

numbered tables and figu re s.

CPU 948 Programming Guide

0 - 4 C79000-H8576-C848-03

Page 7

Conventions used in the text

To provide you with an over vie w of the con ten t s of the pages, the

manual uses the following conventions in addition to a 2nd and 3rd

order of titles:

How to Use this Manual

Entries in the margin

Fourth order entries

Notes

Instructions

Entries in the margin are ke ywords printed in italics on the left-h an d

edge of a page. They provide inform atio n ab out the co nte nts of on e or

more paragraphs on the page.

Fourth order entrie s ar e no t numbe red but appear in the margin in bold

face and identify a lon ge r se ctio n of text.

The following conventions are also used.

Note

Important information is indicated in this format.

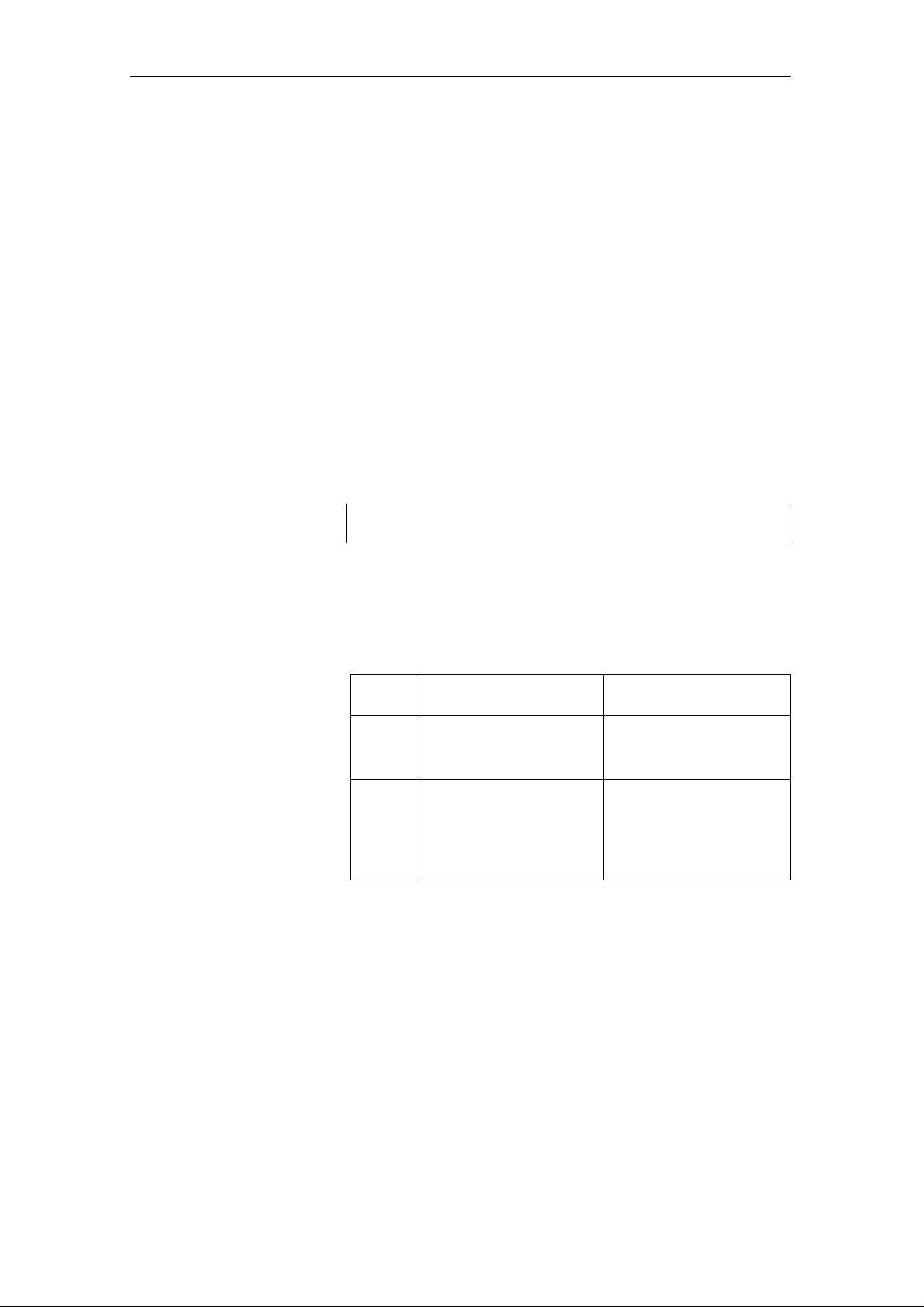

Instructions (often a seque nc e of operations to be performed) ar e

represented in tables, e.g.

Step Action Result

CPU 948 Programming Guide

C79000-H8576-C848-03

1 Switch the mode selector

from RUN to STOP.

2 Hold the reset switch in t he

OVERALL RESET position;

at the same time, switch the

mode selector from STOP to

RUN and back to STOP.

The CPU is in the stop

mode. The STOP LED is lit

continuously.

An OVERALL RESET is

requested. The STOP LED

flashes quickly.

0 - 5

Page 8

How to Use this Manual

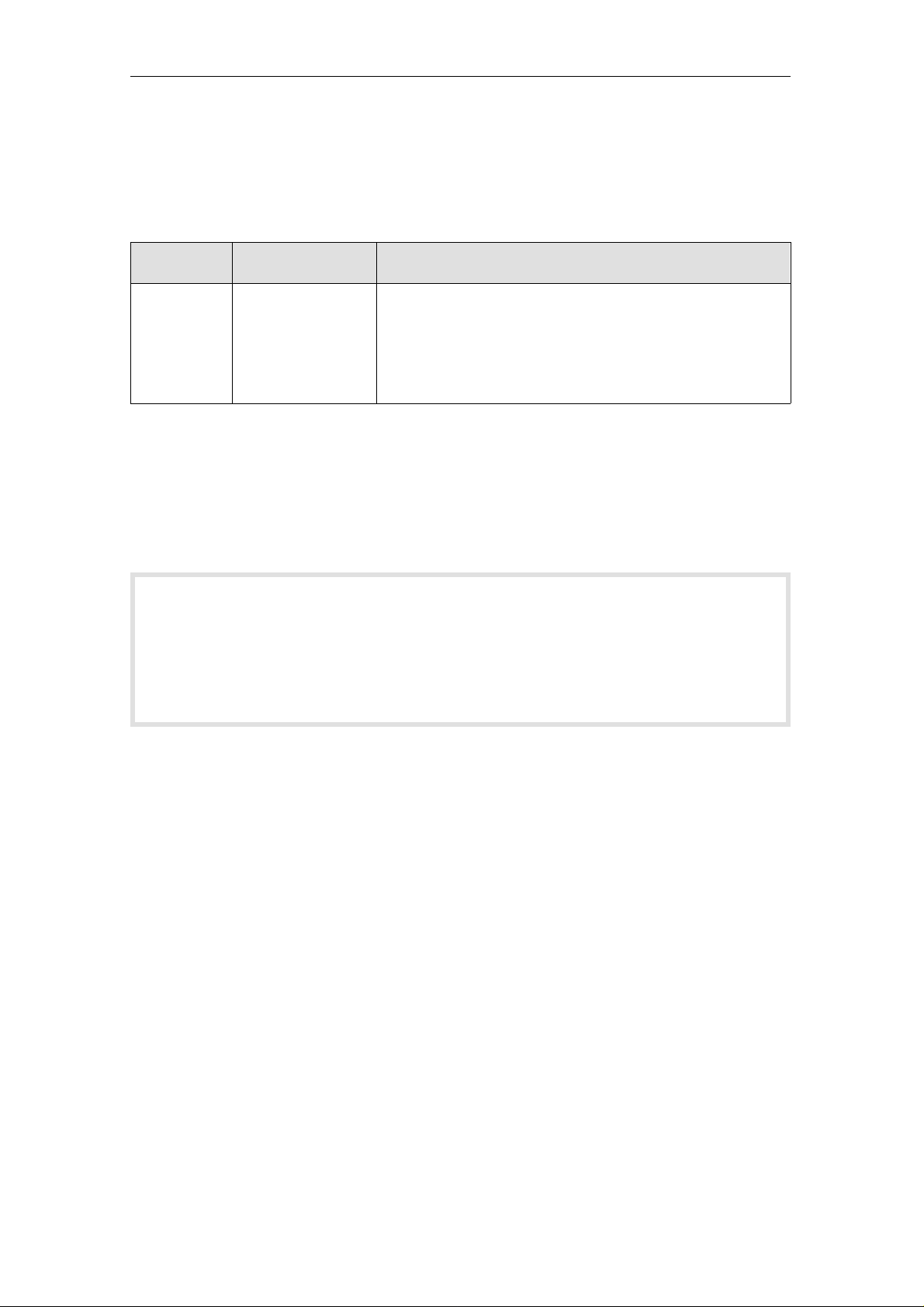

Reference tables

Specific informatio n you ma y requ ire at any time is contained in

numbered tables as shown in the fo llowin g ex am ple and can be foun d

in the list of tables (refer to Chapter 14).

Table 3-2 Binary logic operations

Operation Operand Function

A

O

I 0.0 to 12 7.7

......

Examples

AND logic operation with scan for signal state "1"

OR logic operation with scan for signal sta te "1 "

of an input in the PII

........

Examples, some of which cover several pages, are highlighted by a gray

frame. When the examples cover more than one page this is clearly

indicated.

Example 1: Call ing a n d ass i gning par a meters to a fun c tion b lock i n the

methods of representation STL and LAD/CSF in a program block

Method of representation STL

......

CPU 948 Programming Guide

0 - 6 C79000-H8576-C848-03

Page 9

Contents

Contents

1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

1.1 Area of Application for the S5-155U with the CPU 948 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

1.2 Typical Mode of Operation of a CPU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

1.3 Th e Programs in a CPU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8

1.4 Which Operands are available to the User Program?. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-12

1.5 How much Memory is available for the User Program? . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-15

1.6 How to Tackle Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-16

1.7 Programming Tools . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-19

1.8 What is New with the CPU 948? . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 -20

1.8.1 CPU 948, Version A01. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-20

1.8.2 CPU 948, Version A02 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-23

1.8.3 CPU 948, Version A03 and higher . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-23

1.9 Converting User Programs of the C PU 928B for the CPU 948. . . . . . . . . . . . . . . . . . . . . . . . . . 1-24

2 User Program . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

2.1 STEP 5 P rogrammi ng Language . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2- 4

2.1.1 The LAD, CSF, STL Methods of Representation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-4

2.1.2 Structured Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5

2.1.3 STEP 5 Operations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-6

2.1.4 Number Representation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8

2.1.5 STEP 5 Blocks and Storing them in Memory. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-12

2.2 Program, Organization and Sequence Blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-16

2.2.1 Organization Blocks as User Interfaces. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-18

2.2.2 Organization Blocks for Special Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-22

2.3 Function Blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-23

2.3.1 Structure of Function Blocks. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-24

CPU 948 Programming Guide

C79000-J8576-C848-03

i

Page 10

2.3.2 Programming Function Blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-26

2.3.3 Calling Function Blocks and Assigning Parameters to them . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-28

2.3.4 Special Function Blocks. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-33

2.4 Data Blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-35

2.4.1 Creating Data Blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-37

2.4.2 Opening Data Blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-38

2.4.3 Special Data Blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-41

3 Program Execution. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3- 3

3.1 Principle of Program Execution. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4

3.2 Program Organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5

3.3 Storing Progra m and Data Blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-10

3.4 Processing the User Program. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 -11

3.4.1 Definition of Terms used in Program Execution. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-12

3.5 STEP 5 Operations with Examples . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-15

3.5.1 Basic Operations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 -19

3.5.2 Programming Examples in the STL, LAD and CSF Methods of Representation. . . . . . . . . . . . 3-34

3.5.3 Supplementary Operations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-49

3.5.4 Executive Operations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 -59

3.5.5 Semaphore Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-75

4 Operating Statuses and Program Execution Levels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

4.1 Introduction and Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-4

4.2 Program Execution Levels. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7

4.3 STOP Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-12

4.3.1 SOFT STOP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-12

4.3.2 HARD STOP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-16

4.3.3 OVERALL RES ET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-17

4.4 START-UP Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 -19

4.4.1 MANUAL and AUTOMATIC COLD RESTART . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-20

4.4.2 MANUAL and AUTOMATIC WARM RESTART . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-21

4.4.3 Comparison between COLD RESTART and WARM RESTART . . . . . . . . . . . . . . . . . . . . . . . . 4-24

4.4.4 RETENTIVE COLD RESTART. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-25

4.4.5 Comparison of COLD R ESTART and RETENTIVE COLD RESTART . . . . . . . . . . . . . . . . . . 4-26

4.4.6 User Interfaces for Start-Up. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-27

4.4.7 Extended AUTOMATIC WARM RESTART with the CPU 948 (HOT RESTART). . . . . . . . . . 4-30

4.4.8 Interruptions during START-UP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-31

4.5 RUN Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-33

4.5.1 Cyclic Program Execution. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-34

4.5.2 Specifying Time and Interrupt-Driven Program Execution . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-36

4.5.3 Time-Controlled Program Execution. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-37

4.5.4 Interrupt-Driven Program Execution. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 -45

CPU 948 Programming Guide

ii C79000-J8576-C848-03

Page 11

5 Interrupt and Error Diagnostics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

5.1 Frequent Errors in the U ser Program . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

5.2 Error Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-5

5.3 Procedure for Error Analysis . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-8

5.4 Control Bits and Interrupt Stack . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 -9

5.4.1 Control Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-10

5.4.2 ISTACK Co ntent . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-14

5.4.3 Example of Error Diagnosis using the ISTACK. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-19

5.5 Error Handling Using Organization Blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-20

5.6 Causes of Error and Reactions of the CPU. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-23

5.6.1 OB 19: C alling a Logic Block That Is Not Loaded (KB) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 -24

5.6.2 OB 19: C alling a Data Block That Is Not Loaded (KDB). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-24

5.6.3 OB 23/24, OB 28/29:Timeout Error (QVZ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-25

5.6.4 OB 25: Addressing Error (ADF) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-26

5.6.5 OB 26: Cycle Time Exceeded Error (ZYK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-27

5.6.6 OB 27: (Substitution Error SUF). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-28

5.6.7 OB 30: Parity Error and Timeout Error in the User Memory (PARE) . . . . . . . . . . . . . . . . . . . . 5-28

5.6.8 OB 32: Load and Transfer Error (TRAF) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2 9

5.6.9 OB 33: C ollision of Timed Interrupts Error (WEFES/WEFEH) . . . . . . . . . . . . . . . . . . . . . . . . . 5-30

5.6.10 OB 34: Error with G DB/GX DX (FEDBX) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-32

5.6.11 OB 35: Communication Errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5 -32

5.6.12 OB 36: Error in Self-test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-33

5.7 Self-Test . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3 4

5.7.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-34

5.7.2 Description of the Test Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-35

5.7.3 Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-37

5.7.4 Error Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-38

6 Integrated Special Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

6.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4

6.2 OB 121: Set/Read System Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-7

6.3 OB 122: "Disable Interrupts" On/Off . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-11

6.4 OB 124: Delete STEP 5 Blocks. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-13

6.5 OB 125: Generate STEP 5 Blocks. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-16

6.6 OB 12 6: Define, Transfer Process Images . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-19

6.7 OB 129: Battery State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-24

6.8 OB 131: Delete ACCUs 1, 2, 3 and 4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-25

6.9 OB 132/133: Roll-Up ACCU/Roll-Down ACCU. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-27

6.10 OB 141: "Disable Single Cyclic Timed Interrupts" On/Off. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-29

6.11 OB 142: "Delay All Interrupts" On/Off . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-32

CPU 948 Programming Guide

C79000-J8576-C848-03

iii

Page 12

6.12 OB 143: "Delay Single Cyclic Timed Interrupts" On/Off . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-35

6.13 OB 150: Set/Read System Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-38

6.14 OB 151: Set/Read Time for Clock-Controlled Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-43

6.15 OB 153: Set/Read Time for Delayed Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-50

6.16 OB 180: Variable Data Block Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-53

6.17 OB 181: Test Data Blocks (DB/DX) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-57

6.18 OB 182: Copy Data A rea. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-59

6.19 OB 202 to 205: Multiprocessor Communication . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-62

6.20 OB 222: Restart Cycle Monitoring Time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-63

6.21 OB 223: Comp are St art-Up Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 -64

6.22 OB 254/255: Copy/Duplicate Data Blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-65

7 Extended Data Block DX 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-3

7.1 Application. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-4

7.2 St ructure of DX 0. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-5

7.2.1 Example of In put in DX 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-7

7.3 Parameters for DX 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-8

7.4 Examples of Parameter Assignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-12

7.4.1 STEP 5 Programmi ng . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-12

7.4.2 Parameter Assignment using the PG Screen Form . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-14

8 Memory Assignment and Memory Organization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-3

8.1 St ructure of the Memor y Area. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8- 4

8.2 Memory Assignment in the CPU 948 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-5

8.2.1 Memory Assignment for the System R AM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-6

8.2.2 Memory Assignment for the Peripherals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-8

8.3 User Memory Organization in the CPU 948. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-10

8.3.1 Block Headers in User Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-12

8.3.2 Block Address List in Data Block DB 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-13

8.3.3 RI/RJ Area . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-14

8.3.4 RS/RT Area. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 -15

8.3.5 Bit Assignment of the System Data Words. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-18

8.3.6 Addressable System Data Area . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-42

CPU 948 Programming Guide

iv C79000-J8576-C848-03

Page 13

9 Memory Access Using Absolute Addresses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-3

9.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-4

9.2 Memory Access via Address in ACCU 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-8

9.2.1 LIR/TIR: Loading to or Transferring from a 16-Bit Memory Area Indirectly . . . . . . . . . . . . . . . 9-9

9.2.2 Examples of Access to DW > 255 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-15

9.2.3 LDI/TDI: Loading to or Transferring from a 32-Bit Memory Area I ndirectly . . . . . . . . . . . . . . 9-17

9.3 Transferring Memory Blocks. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-19

9.4 Operations with the Base Address Register (BR Register) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-22

9.4.1 Operations for Transfer between Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-23

9.4.2 Accessing the Local Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-24

9.4.3 Accessing the Global Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-25

9.4.4 Accessing the Dual-Port RAM Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-29

10 Multiprocessor Mode and Communication in the S5-155U . . . . . . . . . . . . . . . . . . . . . . . . . . 10-3

10.1 Multiprocessor Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-4

10.1.1 When to use the Multiprocessor Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-4

10.1.2 What Communications Mechanisms are Available?. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 0-4

10.1.3 Exchanging Data via IPC Flags. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-5

10.1.4 Exchanging Data via Handling Blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-8

10.1.5 What needs to be Programmed for the Multiprocessor Mode? . . . . . . . . . . . . . . . . . . . . . . . . . . 10-9

10.1.6 How to Create Data Block DB 1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 0-9

10.1.7 Starting up in the Multiprocessor Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-13

10.1.8 Test Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 0-14

10.2 Multiprocessor Communication. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-15

10.2.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-15

10.2.2 How the Transmitter and Receiver are Identified . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-16

10.2.3 Why Data is Buffered . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-17

10.2.4 How the Buffer is Processed and Ma naged . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-18

10.2.5 System Start-Up . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-21

10.2.6 Calling Communication OBs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-22

10.2.7 How to Assign Parameters to Communication OBs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-23

10.2.8 How to Evaluate the Output Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-24

10.3 Runtimes of the Communication OBs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-31

10.4 INITIALIZE Function (OB 200). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-33

10.4.1 Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-33

10.4.2 Call Parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-35

10.4.3 Input Parame ters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-35

10.4.4 Outp ut Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-38

10.5 SEND Function (OB 202) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-40

10.5.1 Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-40

10.5.2 Call Parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-40

10.5.3 Input Parame ters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-40

10.5.4 Outp ut Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-42

CPU 948 Programming Guide

C79000-J8576-C848-03

v

Page 14

10.6 SEND TEST Function (OB 203) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-45

10.6.1 Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-45

10.6.2 Call Parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-45

10.6.3 Input Parame ters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-45

10.6.4 Outp ut Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-45

10.7 RECEIVE Function (OB 204). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-47

10.7.1 Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-47

10.7.2 Call Parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-47

10.7.3 Input Parame ters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-47

10.7.4 Outp ut Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-48

10.8 RECEIVE TEST Function (OB 205) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-51

10.8.1 Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-51

10.8.2 Call Parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-51

10.8.3 Input Parame ters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-51

10.8.4 Outp ut Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-51

10.9 Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-53

10.9.1 Calling the Special Function OB using Function Blocks. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-53

10.9.2 Transferring Data Blocks. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-60

10.9.3 Extending the IPCFlag Area . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-66

11 PG Interfaces and Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-3

11.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-4

11.2 PG Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-5

11.2.1 Info . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-6

11.2.2 Installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-7

11.2.3 Progr am Test. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-8

11.3 Serial Link PG - PLC via 1st or 2nd Serial Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-16

11.4 Parallel Operation of Two Serial PG Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-17

11.4.1 Installation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-19

11.4.2 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-19

11.4.3 Sequence in Certain Operating Situations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-21

11.5 PG Functions via the S5 Bus. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-26

11.5.1 Application . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-26

11.5.2 How the PG Functions Work via the S5 Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-28

11.5.3 Installation a nd Getting Started . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-30

11.5.4 Condition Codes Indicating Problems. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-34

CPU 948 Programming Guide

vi C79000-J8576-C848-03

Page 15

12 Appendix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-3

Appendix 1: Jumper Settings f or System Interrupts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 - 4

Appendix 2: Inserting and Removing the PG Submodule. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 - 5

Appendix 3: Technical Data of the C PU 948, CPU 946/947 and C PU 928B. . . . . . . . . . . . . . . . . . . . 12 - 7

Appendix 4: Results IDs of some of the Special Function OBs in ACCU 1 . . . . . . . . . . . . . . . . . . . 12 - 10

Byte IDs in ACCU-1-LL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 - 10

Word IDs in ACCU-1-L. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 - 12

13 Further Reading. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 - 3

14 Indexes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 - 1

List of Abbreviations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 - 3

List of Key Words . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 - 5

List of Tables and Figures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 - 11

List of Tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 - 11

List of Figures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 - 17

CPU 948 Programming Guide

C79000-J8576-C848-03

vii

Page 16

Introduction

Contents of Chapter 1

1.1 Area of Application for the S5-155U with the CPU 948 . . . . . . . . . . . . . . . . . . . . . . . . 1 - 4

1.2 Typical Mode of Operation of a CPU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 - 6

1.3 Th e Programs in a CPU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 - 8

System program . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 - 8

User program . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 - 10

1.4 Which Operands are available to the User Program? . . . . . . . . . . . . . . . . . . . . . . . . . . 1 - 12

1.5 How much Memory is available for the User Program? . . . . . . . . . . . . . . . . . . . . . . . 1 - 15

1.6 How to Tackle Programming? . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 - 16

1

1.7 Programming Tools. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 - 19

1.8 What is New with the CPU 948?. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 - 20

1.8.1 CPU 948, Version A01 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 - 20

1.8.2 CPU 948, Version A02 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 - 23

1.8.3 CPU 948, Ve rsion A03 and Higher . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 - 23

1.9 Converting User Programs of the C PU 928B for the CPU 948 . . . . . . . . . . . . . . . . . . 1 - 24

CPU 948 Programming Guide

C79000-D8576-C848-03

1 - 1

Page 17

1

1Introduction

Aims of the manual

Contents of Chapter 1

This manual is intended to provide spec ialized information about

programming the CPU 948 for users who alrea dy have ba sic

knowledge of programm ing PLCs an d want to use the CPU 948 in the

S5-155U programmable controller. If you do not yet have this basic

knowledge, we strongly ad vise you rea d the docum entation

introducing the progr am min g lan gu ag e STE P 5 /3/ or take part in a

course at our training center. SIEMENS provides comprehensive

training for SIMATIC S5. For more detailed information, contact your

local SIEMENS office.

Chapter 1 explains how to use the manua l and dea ls with the ar ea s of

application of the S5-155U programmable controller with the

CPU 948 and its structure.

The chapter explains the typical mode of operation of a CPU and the

structure of the CPU program.

You will also find a few suggestions abou t how to tac kle

programming and will learn som e of the fe atu re s of the CPU 948

which are important for programming.

If you have already worke d with the CPU 946/94 7 an d would like to

know the differences betwee n the se modules an d the CPU 948, refer

to Section 1.8.

Chapter 1 also informs you about dif ferences between versio ns A01

and A02 of the CPU 948 and explains points you should rem em be r

when convertin g "928B" p rogr am s f or the CPU 94 8.

CPU 948 Programming Guide

C79000-D8576-C848-03

1 - 3

Page 18

Area of Application for the S5-155U with the CPU 948

1.1 Area of Application for the S5-155U with the CPU 948

SIMATIC S5 family

Suitability

The S5-155U programmable controller belongs to the family of

SIMATIC S5 programmable co ntr olle rs. With the CPU 948, it is the

most powerful multiprocessor unit for process automation (open and

closed loop control, signalling, monitoring, logging).

Owing to its modularity and high perfo rm an ce , it can be used for

medium to extremely larg e co ntr ol syste ms as well as fo r comp lex

automation tasks at the plant and process supervision level.

The S5-155U with the CPU 948 is particular ly suita ble for the

following:

•• Tasks requiring fast bit and word-oriented processing and fast reaction

times, i.e. with extremely fast open and closed loop controls.

Examples of this are fast processes in mechanical engineering

(bottling plant, packing machines or similar systems) and in the

automobile industry.

•• Tasks requiring an extremely hig h storag e capacity and fast acces s

times, e.g. in the automob ile ind ustr y, proce ss a nd plan t

engineerin g.

•• Tasks requiring fast commun ica tion with othe r CPUs installed in

the PLC and operating in the multip rocessor mode and with CP

modules (e.g. when connec ted to bus systems, host computers, for

visualization, operation and monitoring).

•• Complex tasks which can be handled efficiently and clearly using

the high level languages C and SCL.

CPU 948 Programming Guide

1 - 4 C79000-D8576-C848-03

Page 19

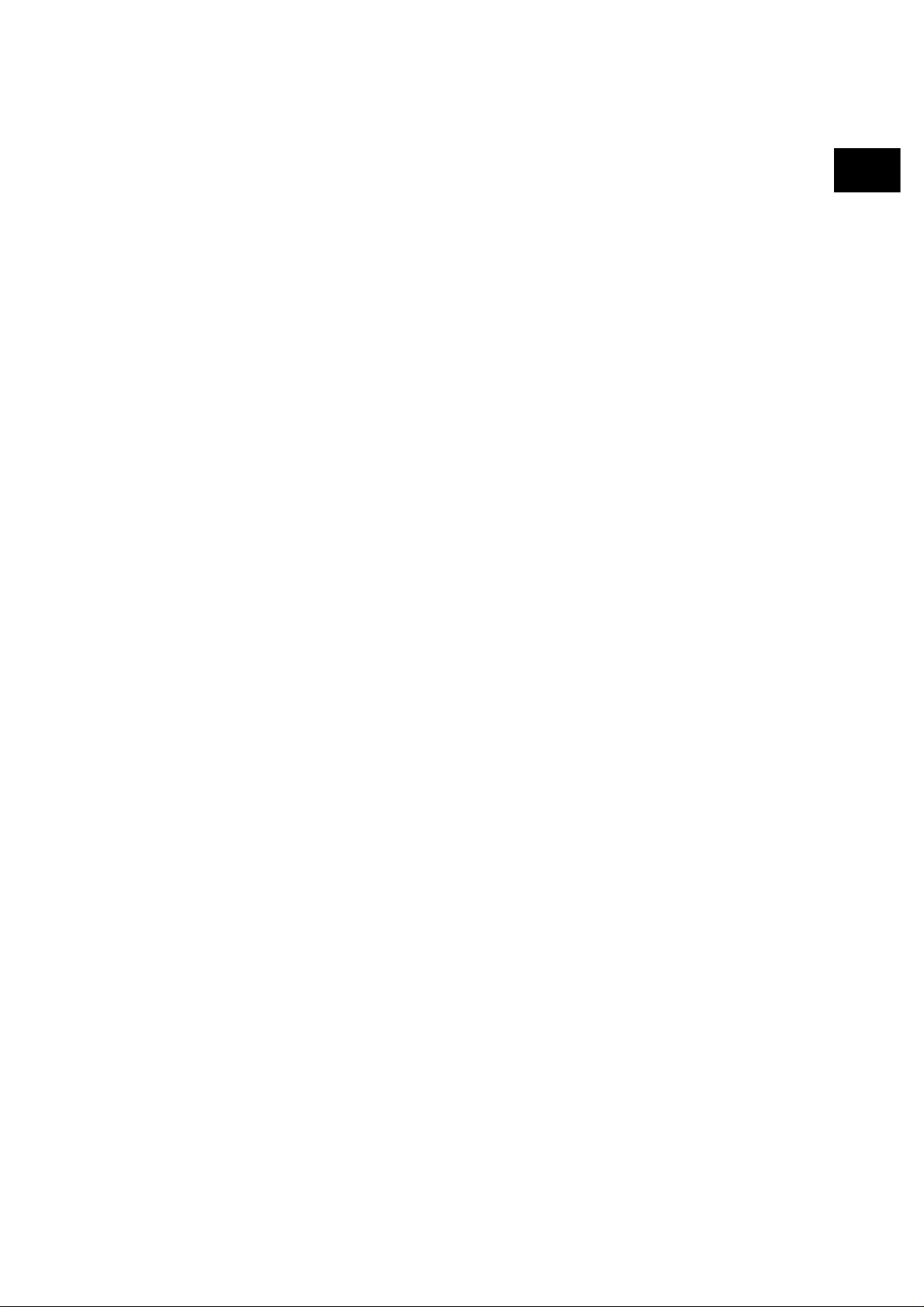

Area of Application for the S5-155U with the CPU 948

Example of application

PG 770

System management Data base/

Service system

Control room

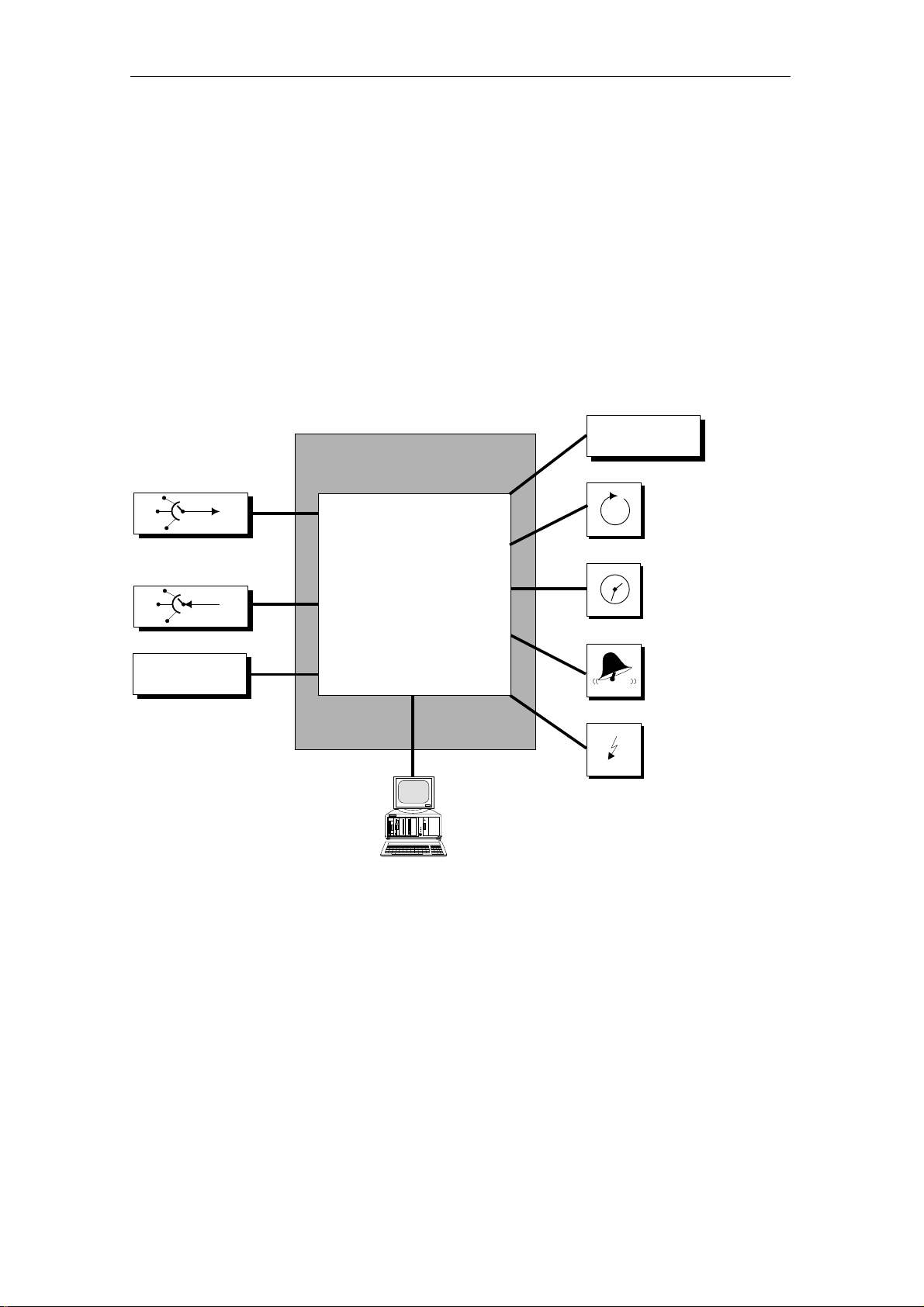

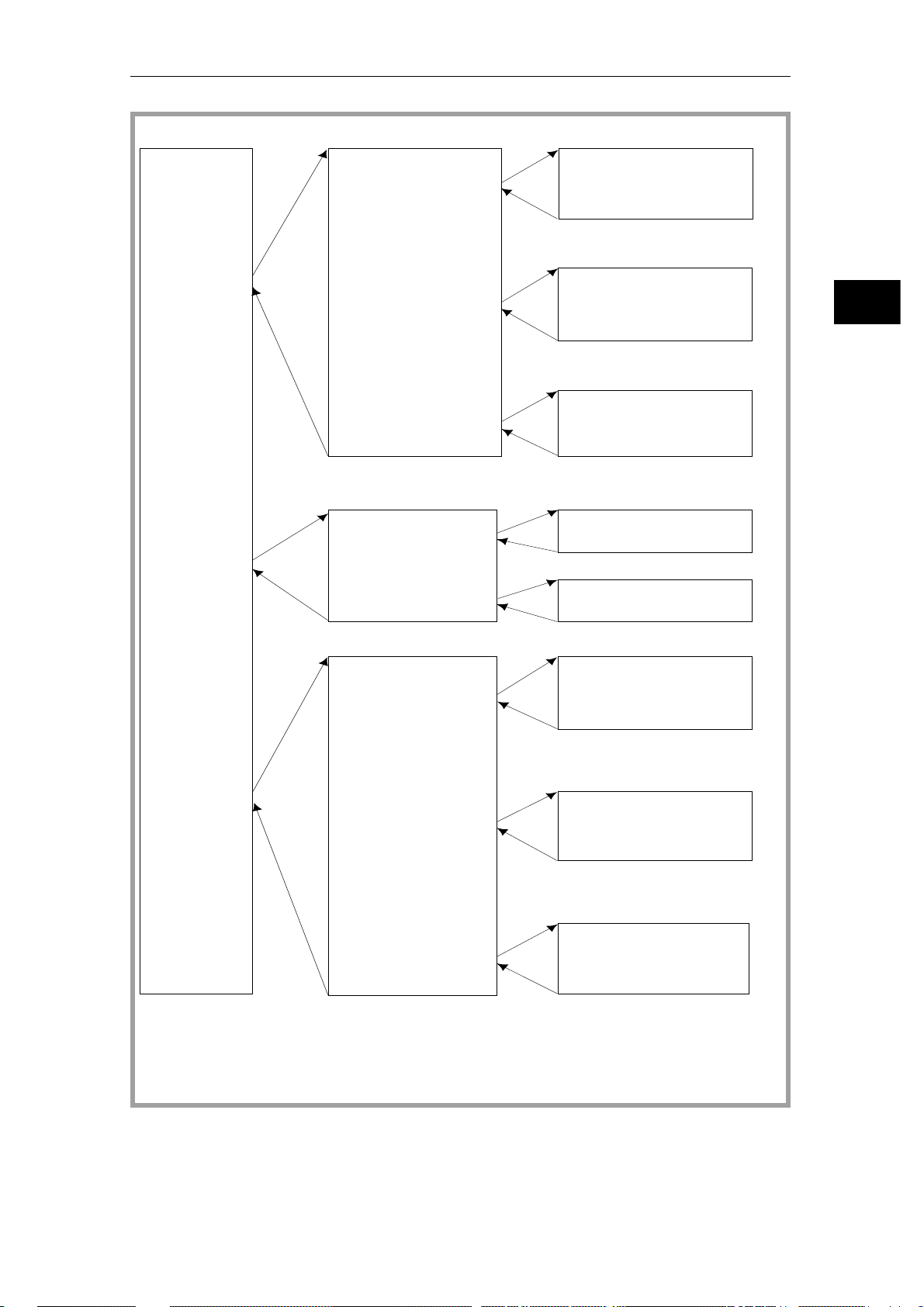

Fig. 1-1 illustrates the use of the S5-155 U progr am ma ble controller in

a cement w orks.

PG 770

logging

PG 770 PG 770

Quarry,

Raw meal silo,

Crusher,

Raw mill

Coal mill,

Kiln

PG 770

Cement

mills,

Dispatch

SINEC H1 bus

1

Process data control

Operation and monitoring (COROS)

S5-155U

Crusher,

Test station,

Limestone

store

S5-155U

Raw mill

Raw meal

silos

S5-155U S5-155U S5-155U S5-155U

Coal mill

Dryer

Heat

exchanger

Rotary

kiln

Clinker cooler

Clinker transport

Dust collector

Telephone

system

Central

control room

Fig. 1-1 Example of application of the S5-155U with the CPU 948

S5-155U

Cement mills

Distribution

PG 770

Process

data

editing

CPU 948 Programming Guide

C79000-D8576-C848-03

1 - 5

Page 20

.1

Typical Mode of Operation of a CPU

1.2 Typical Mode of Operation of a CPU

Mode of operation of a CPU

The following modes of operation are possib le in a CPU:

1. 2. 3.

Cyclic processing

Cyclic processing

This is the main part of all activities in the CPU. As the name alre ad y

says, the same operatio ns are re pe ate d in an endless cy cle .

Time-controlled processing

Interrupt-driven processing

Phase Sequence

All the input modules assigned to the

1

CPU are scanned by the system

program and the values read in are

stored in the proce ss imag e of the

inputs (PII).

The values contained in the PII are

2

processed by the user program and the

values to be output are entered in the

process image of the outpu ts ( PIQ) .

The values containe d in the proce s s

3

image of the outputs are output by the

system program to the output modules

assigned to the CPU.

Cyclic processing can be divided into thr ee main phases, as follows:

CPU

Read in process image

of the inputs

Evaluate input signals,

set output signals

&

I1.5

I1.6

I1.4

I1.3

Output process image

of the outputs

1

=

&

Q3.1

Process

Input I 1.3

Input I 1.4

Input I 1.5

Output Q 2.0

Output Q 3

Output Q 4.7

CPU 948 Programming Guide

1 - 6 C79000-D8576-C848-03

Page 21

Typical Mode of Operation of a CPU

Time-controlled processing

Interrupt-driven processing

Processing according to

priority

In addition to the cyclic processing, time- co ntr olle d processing is also

available for processes requiring control signals at constant intervals,

e.g. non-time critical mo nito rin g func tion s per fo rm ed every seco nd.

1

If the reaction to a particular process signal must be particularly fast, this

should be handled with interrupt-driven processing. With, for example,

a system interrupt, triggered via an interrupt generating module, you

can activate a special processing section within your program.

The types of processing listed above are handle d by the CPU

according to the ir prio rit y.

Since a fast reaction is required to a time or interrupt event, the CPU

interrupts cyclic processing to handle a time or interru pt ev ent. Cy clic

processing theref or e ha s the lowe st prio rity.

Whether or not the time-co ntr olle d proc essin g is mor e imp or tan t than

the interrupt controlled processing depends, among other things, on

the particular task . For this rea son, the priority of time and

interrupt-drive n proc essing on the CPU 948 can be selected.

CPU 948 Programming Guide

C79000-D8576-C848-03

1 - 7

Page 22

g

The Programs in a CPU

1.3 The Programs in a CPU

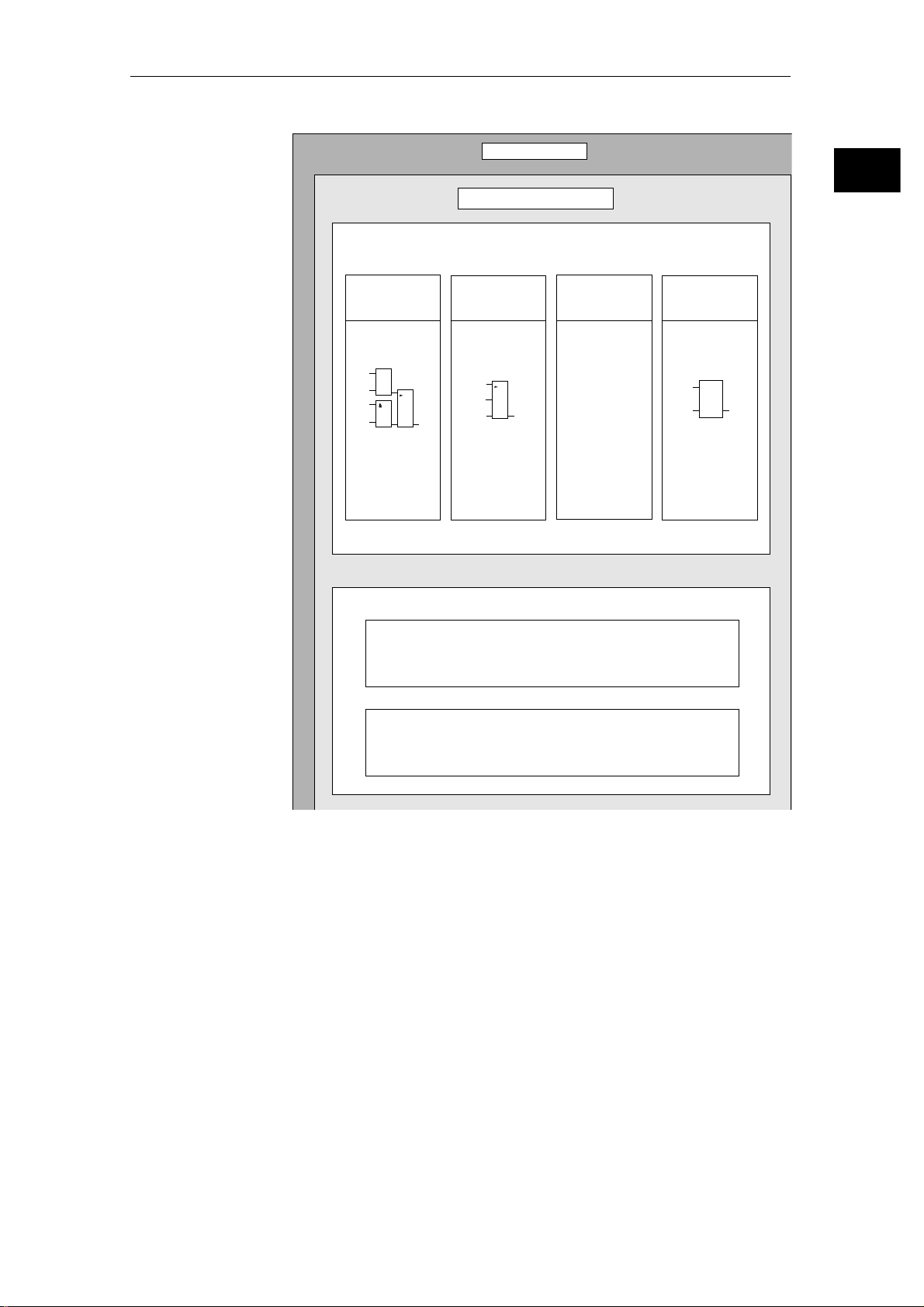

The program existing on every CPU is divided into the fo llowin g:

•• the system program

and

•• the user program.

System program

Update process image

of the inputs

Output process image

of the outputs

Manage memory

The system program organizes all the functions and sequences of the

CPU which do not involve a specific control task (refer to Fig. 1-2).

System

program

Communication with

the PG

Execute start-up

Call

user

processin

(interfaces)

Handle errors

Fig. 1-2 Tasks of the system program

1 - 8 C79000-D8576-C848-03

CPU 948 Programming Guide

Page 23

The Programs in a CPU

Tasks

User interfaces

The tasks include the follo wing :

1)

•• cold and warm restart,

•• updating the process image of the inp uts an d outpu tting the

process image of the outputs,

•• calling the cyclic, time- co ntr olle d an d inte rrup t-d riv en progr am s,

•• detection and handling of erro rs,

•• memory management,

•• communication with the programme r (PG) .

As the user, you can influenc e the rea ctio n of the CPU to partic ula r

situations and errors via spec ial inte rf ac es to the system progr am .

1

Storing the system program

System program defaults

Modifying the defaults

After switching on the power supp ly to the PLC (POWER UP) the

system program is read fro m the EP ROM to the internal operating

system RAM.

The following chapters, except for Chapter 7, describe the default

system reaction to process events or errors. Depending on the

defaults, the CPU changes to the stop mode if an oper atio n code err or

occurs and the error or ga niz atio n blo ck is not loaded .

You can modify the system resp onse by assign ing par am ete rs fo r the

data block DX 0.

Chapter 7 describes the system response following modification.

1)

When operating with several CPUs (multiprocessing) further tasks are involved.

CPU 948 Programming Guide

C79000-D8576-C848-03

1 - 9

Page 24

The Programs in a CPU

User program

Tasks

The user program contains all the functions required for processing a

specific control task . In gen er al ter ms, these functions can be

assigned to the interfac e pr ovided by the system program for the

various types of processing, as follows:

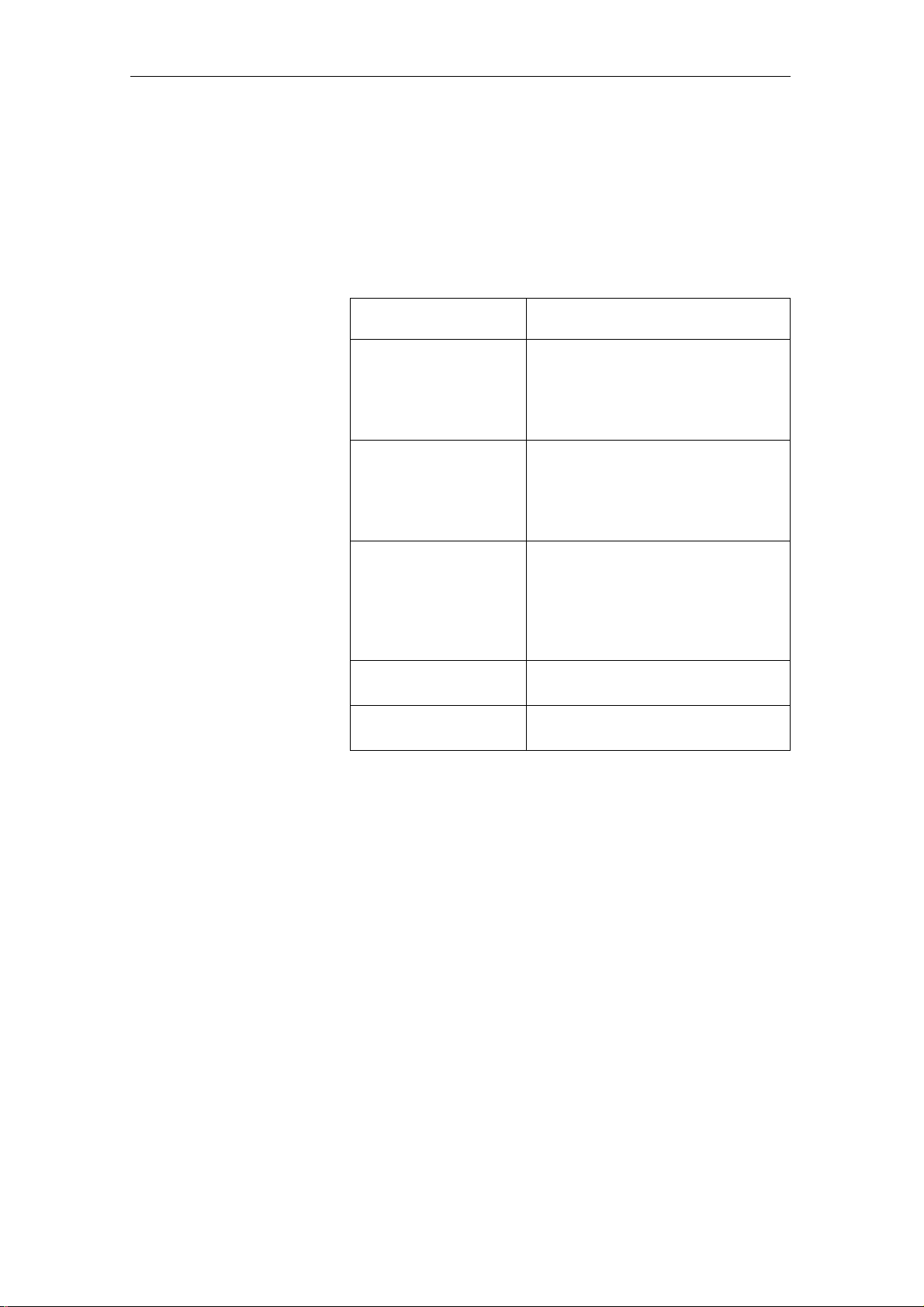

Type of processing Task

Cold and warm restart To provide the conditio ns un de r whic h

the other processing functions can start

from a defined status following a cold or

warm restart of the contro l system (e. g.

assigning specific values to signa ls).

Cyclic processing Constantly repeated signal processing

(e.g. logic operatio ns on binary signa ls,

reading in and analyzing analog values,

specifying binar y sign als fo r output,

outputting analog values).

Time-controlled proc essin g Special, time-dependent processing with

the following time conditions:

- faster than the average cycle,

- at a time interval greater than the

average cycle time,

- at a specified point in time.

Interrupt-driven proc essin g Special, fast reactions to certain proc ess

signals.

Error reaction Handling pr oblem s within the normal

sequence of the program.

CPU 948 Programming Guide

1 - 10 C79000-D8576-C848-03

Page 25

The Programs in a CPU

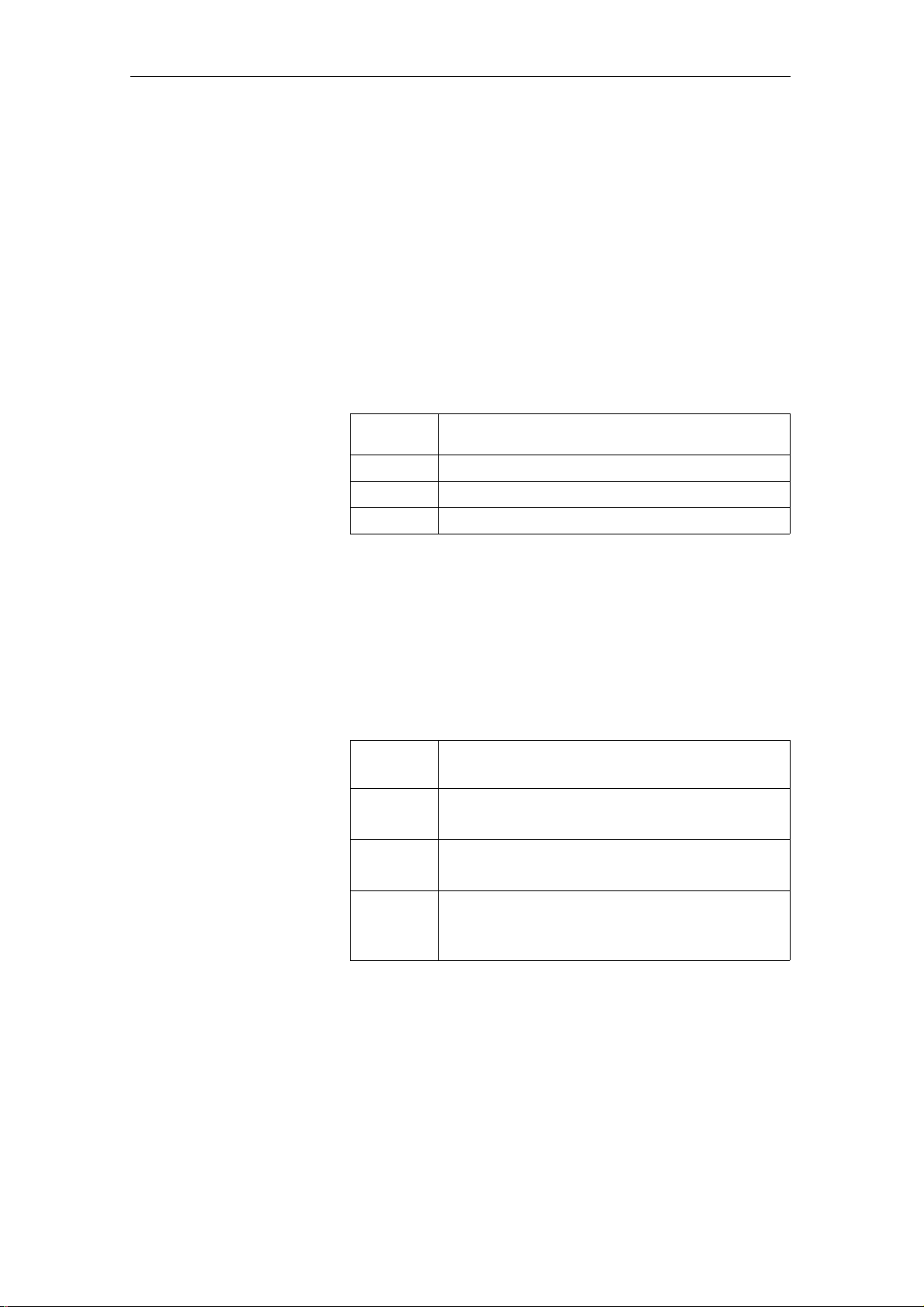

Structure

Organization

blocks

OB

STEP 5

operations

&

I1.5

I1.6

I1.4

&

I1.3

User memory

1

User program

Code blocks

Program

blocks

PB

STEP 5

operations

F 50.1

1

1

=

Q3.1

F 50.2

F 50.3

=

Q5.3

Function

blocks

FB/FX

STEP 5

operations

FB 8

SEGMENT 1

NAME :TRANS

0005 :L IB 3

0006 :T FW 200

0007 :C DB 5

0008 :DO FW 200

0009 :L DW 0

000A :T QW 6

000B :BE

Sequence

blocks

SB

STEP 5

operations

F1.7

S

I2.6

RQ

I1.3

Fig. 1-3 Structure of a STEP 5 user program

Storing the user program

Interfaces to the

system program

Data blocks

DB

static or dynamic data

(bits, bytes, words, double words)

DX

static or dynamic data

(bits, bytes, words, double words)

1: KH = 0101;

2: KF = +120;

3: KS = xy;

4: KY = 4.5;

5: KG =

6: KM =

7:

1: KH = FFFF;

2: KH = FFFF;

3: KH = FFFF;

4: KH = FFFF;

5: KH = FFFF;

6: KH = FFFF;

7:

After programming the user program, you must load it in the user

memory of the CPU 948 (directly fro m the PG) or via a memor y ca rd

whose contents are copied to the user memory by an OVERALL

RESET of the CPU.

Organization blocks are ava ilab le as inte rf ac es to the system program

for the special types of processin g.

CPU 948 Programming Guide

C79000-D8576-C848-03

1 - 11

Page 26

Which Operands are available to the User Program?

1.4 Which Operands are available to the User Program?

The CPU 948 provides the follo wing ope ra nd are as fo r pr ogramming:

•• process image and I/Os

•• flags (F flags and S flags)

•• timers/counters

•• data blocks

Process image of the inputs

and outputs PII/PIQ

Characteristics Size

I/O area (P area)

Extended I/O area (O area)

The user program can ac ce ss the fo llowin g da ta typ es

in the process image ex tre mely quickly:

- single bits,

- bytes,

- words,

- double words

Characteristics Size

The user program can ac ce ss the I/O mo dules dir ectly

via the S5 bus.

The following data types are po ssible :

- bytes,

- words.

Characteristics Size

128 bytes

each for

inputs and

outputs

256 bytes

each for

inputs and

outputs

The user program can ac ce ss the I/O mo dules dir ectly

via the S5 bus.

The following data types are po ssible :

- bytes,

- words.

CPU 948 Programming Guide

1 - 12 C79000-D8576-C848-03

256 bytes

each for

inputs and

outputs

Page 27

F flags

Which Operands are available to the User Program?

Characteristics Size

The flag area is a memory area which the user

program can access extremely quickly with certa in

operations.

The flag area should be used ideally for working data

required often.

The following data types can be accessed:

- single bits,

- bytes,

- words,

- double words.

Single flag bytes can be used as interpr ocesso r

communication flags (IPC flags) to exchange data

between the CPUs in the multiproce ssor mode (refer

to Chapter 10). IPC flags ar e up dated by the system

program at the end of the cycle via a buffer in the

coordinator or CP/IP.

2048 bits

1

S flags (extended flag area)

Characteristics Size

The CPU 948 also contains an addition al fla g ar ea , the

S flag area. The user program ca n also acc ess this ar ea

extremely quickly as with the F flags.

S flags cannot however by used as actual operands

with function block calls nor as IPC flags for data

exchange between the CPUs. The bit test oper atio ns of

the CPU 948 can also not be used with the S flags.

These flags can only be used with the PG system

software "S5-DOS" from version 3.0 upwards or

"S5-DOS/MT" from version 1.0 upwar ds.

32 768 bits

CPU 948 Programming Guide

C79000-D8576-C848-03

1 - 13

Page 28

Which Operands are available to the User Program?

Timers (T)

Characteristics Size

Counters (C)

Data words in the current data

block

The user program loads timer cells with a time value

between 10 ms and 9990 s and by means of a start

operation, decrements the timer from this value at the

preselected intervals until it reaches the value zero.

Characteristics Size

The user program loads co unter cells with a start value

(max. 999) and then increm en t s o r de crements th em.

Characteristics Size

256 timer

cells

256

counters

A data block contains constants and/or variables in the

byte, word or double word format. With STEP 5

operations, you can always access the "current" data

block (refer to Section 2.4.2).

The following data types can be accessed:

- single bits,

- bytes,

- words,

- double words.

1)

In data blocks with a length greater than 256 words, you can only access data

words with the numbers > 255 with operations for absolute memory access

(refer to Chapter 9).

256

words

1)

CPU 948 Programming Guide

1 - 14 C79000-D8576-C848-03

Page 29

How much Memory is available for the User Program?

1.5 How much Memory is available for the User Program?

For storing logic and data bloc ks, the CPU 948 only ha s the use r

memory in the internal RAM.

The CPU 948 is available with two versions of the user memory:

•• Version 1: with 640 Kbytes,

•• Version 2: with 1,664 Kbytes.

1

CPU 948 Programming Guide

C79000-D8576-C848-03

1 - 15

Page 30

How to Tackle Programming

1.6 How to Tackle Programming

If you are an experienced user, you have probably found the most

suitable method fo r cr ea ting programs for yourse lf an d you ca n skip

this section.

Less experienced reade rs will find tips for desig ning, program min g,

testing and starting up your STEP 5 program.

Implementation stages

Recursive procedure

Stage 1

The implementa tion of the STEP 5 co ntr ol pr og ra m can be divided

into three stages:

Stage Activity

1 Determining the tec hn olo gic al task

2 Designing the program

3 Creating, testing and starting the program

In practice, you will recognize that certain steps must be repeate d

(recursive proced ur e) , e. g. when you rea lize that more signals are

required to improve the handling of the task.

Determining the tec hn olo gic al task :

Stage Activity

1 Create a general block diagram outlining the co ntr ol

tasks of your process.

2 Create a list of the input and output sign als re quired

for the task.

3 Improve the block diagram by assigning the signals

and any particular time conditio ns an d/or counter

statuses to the individual blocks.

CPU 948 Programming Guide

1 - 16 C79000-D8576-C848-03

Page 31

How to Tackle Programming

Stage 2

Designing the program

1

Stage Activity

1 Based on the improved bloc k dia gr am , decide on the

types of processing required of your program (cyclic

processing, time-contr olle d proc essin g etc.) and selec t

the OBs required for this.

2 Divide the types of processin g into tech no log ica l

and/or functional units.

3 Check whether the units can be assign ed to a progr am

or function block and select the blocks you requir e

(PB x, FB y etc.)

4 Find out which timers, counters an d da ta or resu l ts

memory you require.

5 Specify the tasks for each of the propo sed logic bloc ks

and the data for flags and data bloc ks whic h ma y be

required. Create flow dia gr am s for the log ic blocks.

Notes on the scope of

cyclic processing

When deciding on the types of proc essin g, kee p the follo wing

conditions in mind:

•• The cycle must run through quickly enough. The process statuses

must not change more quickly than the CPU can rea ct. Other wise

the process can get out of control.

•• The maximum reaction time should be taken as twice the cyc le

time.

The cycle time is determined by the cy clic proce ssing of the

system program and the type and scope of the use r progra m. It is

often not constant, since the cyclic user program may be

interrupted when time and inte rr upt-driven program sectio ns ar e

called.

CPU 948 Programming Guide

C79000-D8576-C848-03

1 - 17

Page 32

How to Tackle Programming

Stage 3

Creating, testing and startin g up the pr ogram:

Stage Activity

1 Decide on the type of repr ese ntation for the logic

blocks (LAD, CSF or STL, refer to Chapter 2).

Remember that function blocks can only be cre ate d in

the STL method of represen tation.

2 Program all logic and data bloc ks (p lea se re fe r to yo ur

STEP 5 manual).

3 Start up the blocks one after the other (you may have

to program a differe nt OB fo r ea ch indiv idu al step, to

call the logic blocks):

1a: load the block(s)

1b: test the block(s)

(For more detailed info rmation please refer to your

STEP 5 manual and Chapter 11).

4 When you are certain that all the logic bloc ks ru n

correctly and all the data can be correc tly ca lculated

and stored, you can start up your whole progr am .

Note on test strategies

When you actually start up your progr am for the fir st tim e in genu ine

process operation, i.e. with real input an d more impo rta ntly output

signals, is a decision that must be left up to yourself or to a team of

experts.

The more complex the proc ess, the gr ea ter the risk and ther ef ore the

greater the care re qu ire d whe n starting up.

CPU 948 Programming Guide

1 - 18 C79000-D8576-C848-03

Page 33

1.7 Programming Tools

Programming Tools

Suitable PGs

Suitable software

The following program me rs ar e av aila ble for creating your user

program, PG 685, PG 710, PG 730, PG 750 and PG 770. You can

check on the performance and cha ra cte ristic s of the se devic es in the

catalog ST 59 /9/.

Note

If you wish to use the full range of performa nce of the CPU 948

in your automation softwar e, (pa rtic ula rly the DX 0 screen, the

"Output ISTACK" screen, the displa y with the "memor y

configuration" func tion and the PG functions via the backplane

bus) you require the PG system sof twar e "STEP 5/ST" from

version 6.3 upwards or "STEP 5/MT" from version 6.0 upwards

plus the "Delta diskette CPU 948" and a PG 7xx.

You can crea t e user programs for SIMATIC S5 programmable

controllers as follows:

•• In the STEP 5 programming language,

Here you require the STE P 5 pro gramming package alo ng with the

system software STEP 5/ST or STEP 5/MT (descr iptio n, refer to

/3/ in Further Reading ),

1

or

•• In a higher programming language :

If you are familiar with programming in higher programming

languages, you can also formulate your STEP 5 program for the

CPU 948 as follows:

- SCL (refer to /12/ in Furth er Rea din g, the S CL com pile r i s

contained in the PG software "S5-DOS/MT" from version 6

upwards.)

or

- C with S5 C compiler (refer to /13/ in Further Reading).

You can also create programs for sequence control systems in a

graphic representation using the GRAPH 5 programming package

(description, refer to /4/ in Further Reading).

Depending on the task, you can also inc or porate "off-the-peg"

standard function bloc ks in yo ur user progr am . Th e pe rf or ma nce and

characteristics of the se blocks are described in the ca talog ST 57 /11/.

CPU 948 Programming Guide

C79000-D8576-C848-03

1 - 19

Page 34

What is New with the CPU 948?

1.8 What is New with the CPU 948?

1.8.1

CPU 948, Version A01 Compared with the CPU 946/947, the CPU 948 versio n A01 has new

characteristics and functions an d signific an t improvem ents in

performance.

Faster processing

Larger user memory

Memory Card

The CPU 948 is between three and five times fa ster than the CPU

946/947. The exact execution times can be found in your Pocket

Guide /1/.

CPU 948

only RAM (integrated)

640 Kbytes or 1664 Kbytes in

internal RAM integrated in the

CPU 948, for logic and data

blocks.

RAM or EPROM cartridges

Max. 896 Kbytes, of which 128

Kbytes fixed as RAM plus

additional 6 RAM or EPROM

cartridges, each with 128 Kbyte s

in 355 memory modules.

CPU 946/947

CPU 948 CPU 946/947

SIMATIC Memory Card (Flash

EPROM), 256 Kbytes to

2 Mbytes;

the memory card is programmed

on the PG and its contents loaded

in the user memory (inte rnal

RAM) following an OVERALL

RESET.

1 - 20 C79000-D8576-C848-03

SIMATIC memory c ar tridges

RAM or EPROM, max. 128

Kbytes;

data blocks can be copied to the

DB RAM from EPROM

(OB 254/255).

CPU 948 Programming Guide

Page 35

What is New with the CPU 948?

Interruptability at block or

operation boundaries

Expansion of

time-controlled program

processing

With a CPU 948, there is no longer a distinctio n betwee n 150/155U

modes. This means the following chan ge s compa re d with the CPU

946/947:

CPU 948 CPU 946/947

- Processing system interrupts:

possible with interrupts at the

operation or block boundaries

- Multiprocessor mode:

interrupts possible at the

operation or block boundaries.

Apart from the familiar cyclic time d inte rrup ts at fixe d interv als, the

following new interrupts are also proc esse d:

•• delayed interrupt (OB 6),

•• clock-controlle d inte rr up t (OB 9).

Both interrupts are only possible when "process interrupts via IB 0 =

off" is set in DX 0.

- Processing systems interrupts:

only possible with interrupts

at operation boundarie s.

- Multiprocessor mode:

only possible with interrupts

at operation boundarie s.

1

Expansion of PG

communication

New special functions

•• Second PG serial interfac e via plug -in PG submo dule.

•• PG functions via SINEC H1 and para llel ba ck pla ne bus.

•• Delete ACCU 1 to ACCU 4 (OB 131)

Roll-up ACCU (OB 132)

Roll-down ACCU (OB 133)

•• Enable/disable "bloc k sing le time d interr upts" ( OB 141)

Enable/disable "delay all inter rupts" (OB 142 )

Enable/disable "delay single timed interrupts" (OB 143)

•• Read/set system time, compatible with CPU 928B (OB 150),

•• Assign parameters for cloc k- co ntr olle d inte rr upt ( OB 9), (OB 151 )

•• Assign parameters for dela yed inte rr upt (OB 6), (OB 153)

•• Restart cycle monitoring time (OB 222)

CPU 948 Programming Guide

C79000-D8576-C848-03

1 - 21

Page 36

What is New with the CPU 948?

Self test functions

OB 0

WHAT IS TESTED? WHEN?

The user memory In OVERALL RESET

The BASP signal

In STOP

(disable command output)

The hardware clock In COLD RESTART

The cycle time monitorin g In START-UP

The address lines Cyclically in RUN

The code of the system program

Cyclically in RUN

(checksum )

The code of the STEP 5 logic

Cyclically in RUN

blocks in the user memory

(checksum)

The test functions can be activ ated individually, they are per fo rmed in

"time slices".

New HDBs for the CPU 948

CPU 948 CPU 946/947

With the PG functions,

BSTACK, ISTACK and DIR,

only the operating syste m

organization block OB 0 is

displayed.

With the PG functions,

BSTACK, ISTACK and DIR, all

the operating system

organization bloc ks > OB 40 are

displayed.

"New" handling block s (HDBs) are req uir ed for the CPU 948. T he

HDBs of the CPU 946/947 cannot be used in the CPU 948.

The HDBs for the CPU 948 are those for the S5-135U (CPU 922,

CPU 928, CPU 928B), and can be obtained under the following order

numbers:

6ES5 842-xCB01 ("HDBs for the CPU 922, 928, 928B and CPU 948")

where:

x = 8 stands for the operating system S5-DOS (PCP/M)

x = 7 stands for the operating system MS-DOS, S5/DOS-MT.

CPU 948 Programming Guide

1 - 22 C79000-D8576-C848-03

Page 37

1.8.2 CPU 948, Version A02

What is New with the CPU 948?

The CPU 948, version A02, provide s you with new fe atu re s and

functions compared with the CPU 948, version A01:

1

Communication via the

second serial interface

Software protection

New special function OBs

As with the CPU 928B, the following communication s optio ns ar e

available via the second ser ial inte rf ac e:

•• RK 512,

•• data transmission with procedure 3964/3964R,

•• open drivers,

•• SINEC L1.

For more detailed info rmation, see the communicatio ns manual

(Further Reading /14/).

You can protect your user progr am from re ad and write access using a

password (see Chapter 8, RS 120).

The following special func tion OBs are availab le (see Chapter 6):

•• OB 129: Battery state

•• OB 181: Test data blocks DB/DX

1.8.3 CPU 948, Version A03 and Higher

•• OB 182: Copy data areas

Special function OB 180: Variable data block access.

CPU 948 Programming Guide

C79000-D8576-C848-03

1 - 23

Page 38

Converting User Programs of the CPU 928B for the CPU 948

1.9 Converting User Programs of the CPU 928B for the CPU 948

The following section inf or ms you ab out the po ints you sho uld

remember when you convert user programs written for the CPU 928B

for use on the CPU 948.

Operations

Operations CPU 928B CPU 948

IA/RA (disable/enable

interrupts)

LIR/TIR 16 bit long addresses are used. 20 bit long addresses are used .

Block transfer operation TNB

Block transfer operation TNW

All process interrupts are disa ble d or

enabled

16 bit long addresses are used. The operation does not exist.

- 16 bit long addresses are used.

- Block transfer s from the 8-bit to the

In the following opera tion s, no te the diff erences in the exec utio n an d

handling (among other things the different mem ory utiliz atio n) .

Only the process interru pts via inpu t

byte IB 0 are disabled or enabled.

Instead of these operations, use the

special function OBs OB 122 or

OB 142.

Adaptation is necessary.

Use TNW for block transfer from the

8-bit to the 8-bit area.

- 20 bit long addresses are used.

Adaptation is necessary.

- only block transfers from the

8-bit area and vice versa are

possible.

8-bit to the 8-bit area and from the

16-bit to the 16-bit areas possible

with TNW.

- for the block tra nsf er from

the 8-bit to the 16-bit area use

the operation TXB,

- for the block tra nsf er from

the 16-bit to the 8-bit area use

the operation TXW.

(TXB and TXW do not exist on

a CPU 928B)

All operations with the

BR register

1 - 24 C79000-D8576-C848-03

The BR register is 20 bits wide. The BR register is 32 bits wide.

Adaptation is necessary.

CPU 948 Programming Guide

Page 39

Timer processing

FB 0 as cycle block

Converting User Programs of the CPU 928B for the CPU 948

CPU 928B CPU 948

The timers are updated during

start-up.

CPU 928B CPU 948

The timers are only updated in

the RUN mode

(Reason: compatibility with

CPU 946/947)

1

Default priorities

Data block DB 0

(block address list)

If no cycle block OB 1 exists, the

system program calls FB 0

cyclically, provided it is loaded.

CPU 928B CPU 948

Process interrupts have higher

priority than timed interrupts.

CPU 928B CPU 948

The block address list contains

the direct start addresses of the

blocks.

Only OB 1 can be used for cyclic

processing. If you have

programmed FB 0, create an

OB 1 in which FB 0 is called.

Timed interrupts have pr ior ity

over process interrupts via IB 0

or system interrupts. You can

change the priority with the

parameters in DX 0.

The block address list contains

the segment addresses of the

blocks. To obtain the start

address of a block, its segment

address must be shifted 4 bits to

the left.

CPU 948 Programming Guide

C79000-D8576-C848-03

1 - 25

Page 40

Converting User Programs of the CPU 928B for the CPU 948

Data block DX 0

Using the RT area

Organization blocks

Error OBs

You must create a new DX 0 data block (see Chapter 7), since the

DX 0 for the CPU 928B has a different structure and settings.