Sharp LH5496D-20, LH5496D-15, LH5496-65, LH5496-50, LH5496-35 Datasheet

...

LH5496/96H

CMOS 512 × 9 FIFO

FEATURES

•• Fast Access Times :

15 */20/25/35/50/65/ 80 ns

•• Full CMOS Dual Port Memor y Arr ay

•• Fully Async hronous Read and Write

•• Expandable-in Width and Depth

•• Full, Half-F ull, and Empty Status Flags

•• Read Retransmit Capability

•• TTL Compatible I/O

•• Packages:

28-Pin, 300-mil PDIP

28-Pin, 600-mil PDIP

32-Pin PLCC

•• Pin an d Fu nct io n all y C omp at ibl e wi th I DT 72 01

FUNCTIONAL DESCRIPTION

The LH5496/ 96H are dual por t memor ies with inter nal

addressing to implement a First-In, First-Out algorithm.

Through an advanc ed dual por t archit ecture, they provide

fully asynchr onous read/wr ite ope ration. Empty, Full, and

Half-Full status flags are provided to prevent data overflow and underflow . In addition, interna l logic provides for

unlimited expansion in bot h word size and depth.

Read and write operations automatically access sequential locat ions in memory in that data is read out in the

same order that it was written, that is on a First-In,

First-O ut basis. Since the addr ess s equen ce is internally

predefined, no external address info rmation is required

for the oper ation of this dev ice. A nint h data bit is pro vided

for parity or contro l inform at ion oft en needed in comm unication applicat ions.

Empty, Full, and Half-Full status flags monitor the

extent to which data has been writt en int o the FIFO, and

prevent improper operations (i.e., Read if the FIFO is

empty, or Write if the FIFO is full). A retransmit feature

resets the Read address pointer to i ts initial position,

thereby allowing repetitive readout of the same data.

Expansion In and Expansion Out pins implement an

expansion scheme that allows individual FIFOs to be

cascaded to greater depth without incurring additional

latency ( bubblet hrough) delays .

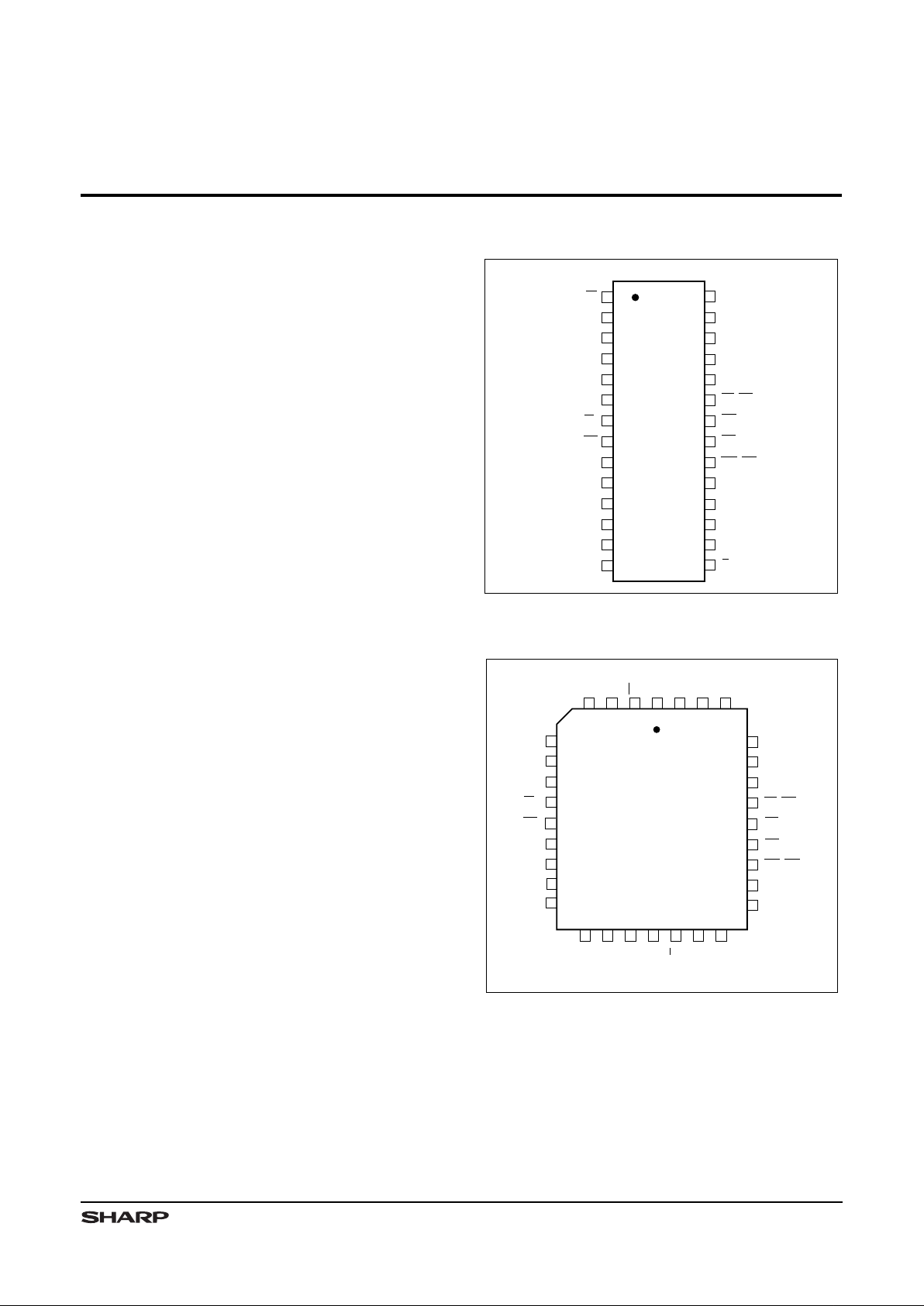

PIN CONNECTIONS

5496-1D

1

2

3

4

5

6

7

8

9

10

11

12

13

14

W

D

8

D

3

D

2

D

1

D

0

XI

FF

Q

0

V

SS

28

27

26

25

24

23

22

21

20

19

18

17

16

15

V

CC

D

4

FL/RT

RS

EF

XO/HF

R

Q

1

Q

2

Q

3

Q

8

D

6

D

5

D

7

Q

7

Q

6

Q

5

Q

4

28-PIN PDIP TOP VIEW

Figur e 1. Pin Connections for PDIP Packages

5

6

7

8

9

10

D

2

D

1

D

0

XI

FF

Q

0

11Q

1

2

3

4

32

31

30

29

28

27

26

25

24

D

6

D

7

NC

EF

D3D

8

W

NC

V

CC

D

4

D

5

14

15

16

20

19

18

17

FL/RT

RS

23

XO/HF

22

Q

7

21

Q

6

12NC

13Q

2

1

Q3Q

8

V

SS

NC

R

Q

4

Q

5

5496-2D

32-PIN PLCC TOP VIEW

Figure 2. Pin Connections for PLCC Package

* LH5496 only.

1

PIN DESCRIPTIONS

PIN PIN TYPE * DESCRIPTION

D0 – D

8

I

Input Data Bus

Q0 – Q

8 O/Z

Output Dat a Bu s

W

I

Write Request

R

I

Read Request

EF

O

Empty Flag

FF

O

Full Flag

* I = Input, O = Output, Z = High-Impedance, V = Power Volta ge Level

PIN PIN TYPE * DESCRIPTION

XO/HF

O

Expansion Out/Half-Full Flag

XI

I

Expansion In

FL/RT

I

First Load/ Retransmit

RS

I

Reset

V

CC

V

Positive Power Supply

V

SS

V

Ground

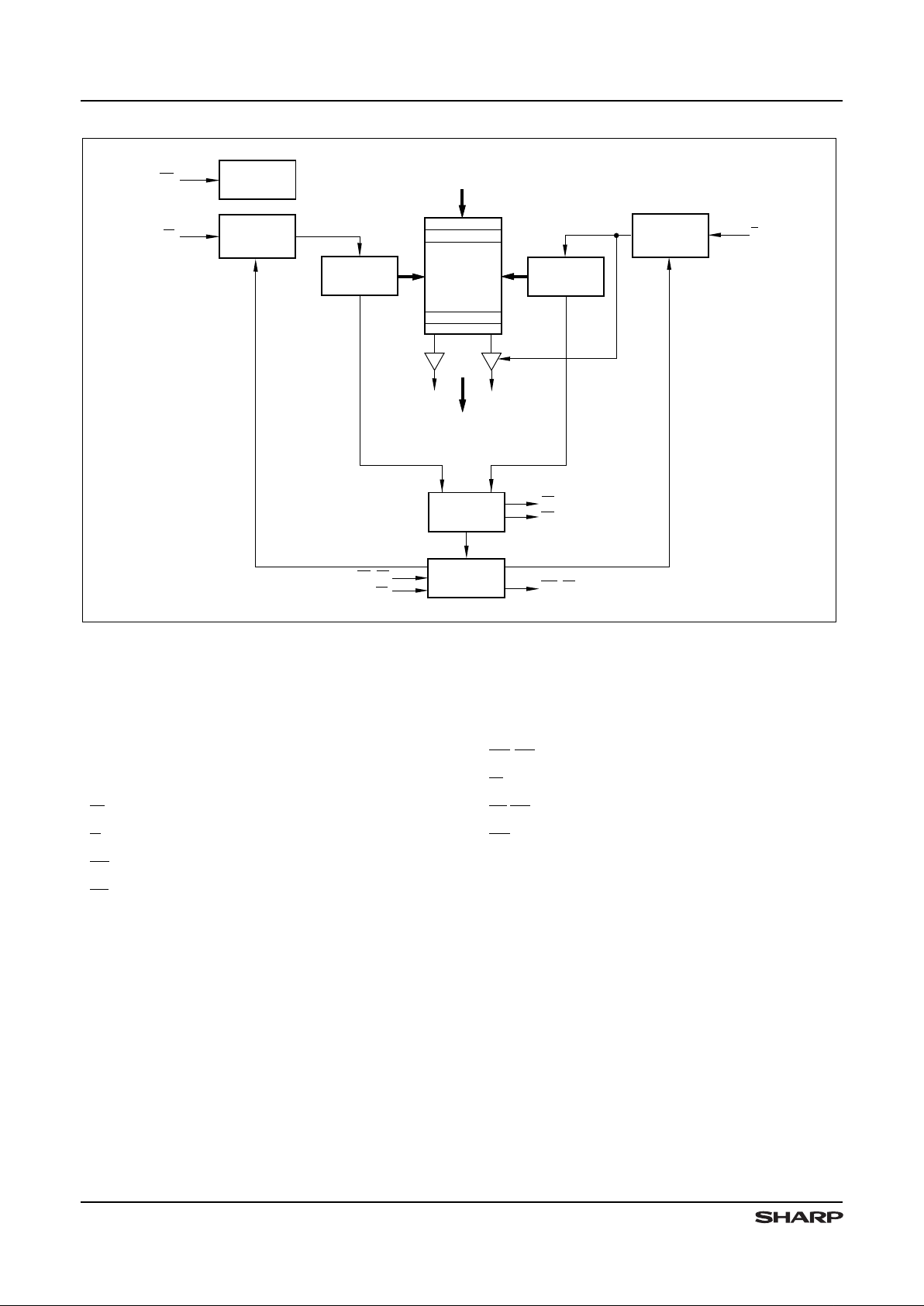

DATA OUTPUTS

Q

0

- Q

8

FLAG

LOGIC

WRITE

POINTER

READ

POINTER

DATA INPUTS

D

0

- D

8

DUAL-PORT

RAM

ARRAY

512 x 9

EF

FF

. . .

5496-3

INPUT

PORT

CONTROL

R

W

RESET

LOGIC

RS

OUTPUT

PORT

CONTROL

EXPANSION

LOGIC

XO/HF

XI

FL/RT

Figure 3. LH5496/96H Block Diagram

LH5496/96H CMOS 512 × 9 FIFO

2

ABSOLUTE MAXIMUM RATINGS

1

PARAMETER RATING

Supply Volt age t o VSS Potential –0.5 V to 7 V

Signal Pin Voltage to VSS Potential

3

–0.5 V to VCC + 0.5 V (not to exceed 7 V)

DC Output Current

2

±50 mA

Storage T e mperature Range –65oC to 150oC

Power Dissipation (Package Limit) 1.0 W

DC Voltag e Applied T o Outpu ts In High-Z State –0.5 V to Vcc + 0.5 V (not to exceed 7 V)

NOTES:

1. Stresses greater than those listed under ‘Absolute Maximum Ratings’ may cause permanent damage to the device.

This is a device stress rating for transient conditions only. Functional operatio n at these or any other conditions above

those indicated in the ‘Operating Range’ of this specification is not implied. Exposure to absolute maximum rating

conditi ons for extended periods may affect reliability.

2. Outputs should not be shorted for more than 30 seconds. No more than one output should be shorted at any time.

3. Negative undershoots of 1.5 V in amplitude ar e permitted for up to 10 ns once per cycle.

OPERATING RANGE

SYMBOL PARAMETER MIN MAX UNIT

T

A

T emperat ure, Ambient, LH5496

070

o

C

T

A

T emperature, Ambient, LH5496H

–40 85

o

C

V

CC

Supply Voltage

4.5 5.5 V

V

SS

Supply Voltage

00V

VILLogic ‘0 ’ Input V oltag e

1

–0.5 0.8 V

V

IH

Logic ‘1 ’ Input V oltag e

2.0 VCC + 0.5 V

NOTE:

1. Negative undershoots of 1.5 V in amplitude ar e permitted for up to 10 ns once per cycle.

DC ELECTRICAL C HARACTERISTICS (O ver Operat ing Range)

SYMBOL PARAMETER TEST CO NDITIONS MIN MAX UNIT

I

LI

Inpu t Leakage Cur rent VCC = 5.5 V, VIN = 0 V to V

CC

–10 10

µA

I

LO

Output Leakage Current

R ≥ VIH, 0 V ≤ V

OUT

≤ V

CC

–10 10

µA

V

OH

Output High Voltage IOH = –2.0 mA

2.4 V

V

OL

Output Low Voltage IOL = 8.0 mA

0.4 V

I

CC

Aver age Supply Cur rent

1

Measu red at f = 40 MHz

100 mA

I

CC2

A ver age Sta ndby Cur re nt

1

All Inputs = V

IH

15 mA

I

CC3

Power Down Current

1

All Inputs = VCC – 0.2 V

5mA

NOTE:

1. ICC, I

CC2

, and I

CC3

are dependent upon actual output loading and cycle rates. Specified values are with outputs open.

CMOS 512 × 9 FIFO LH5496/96H

3

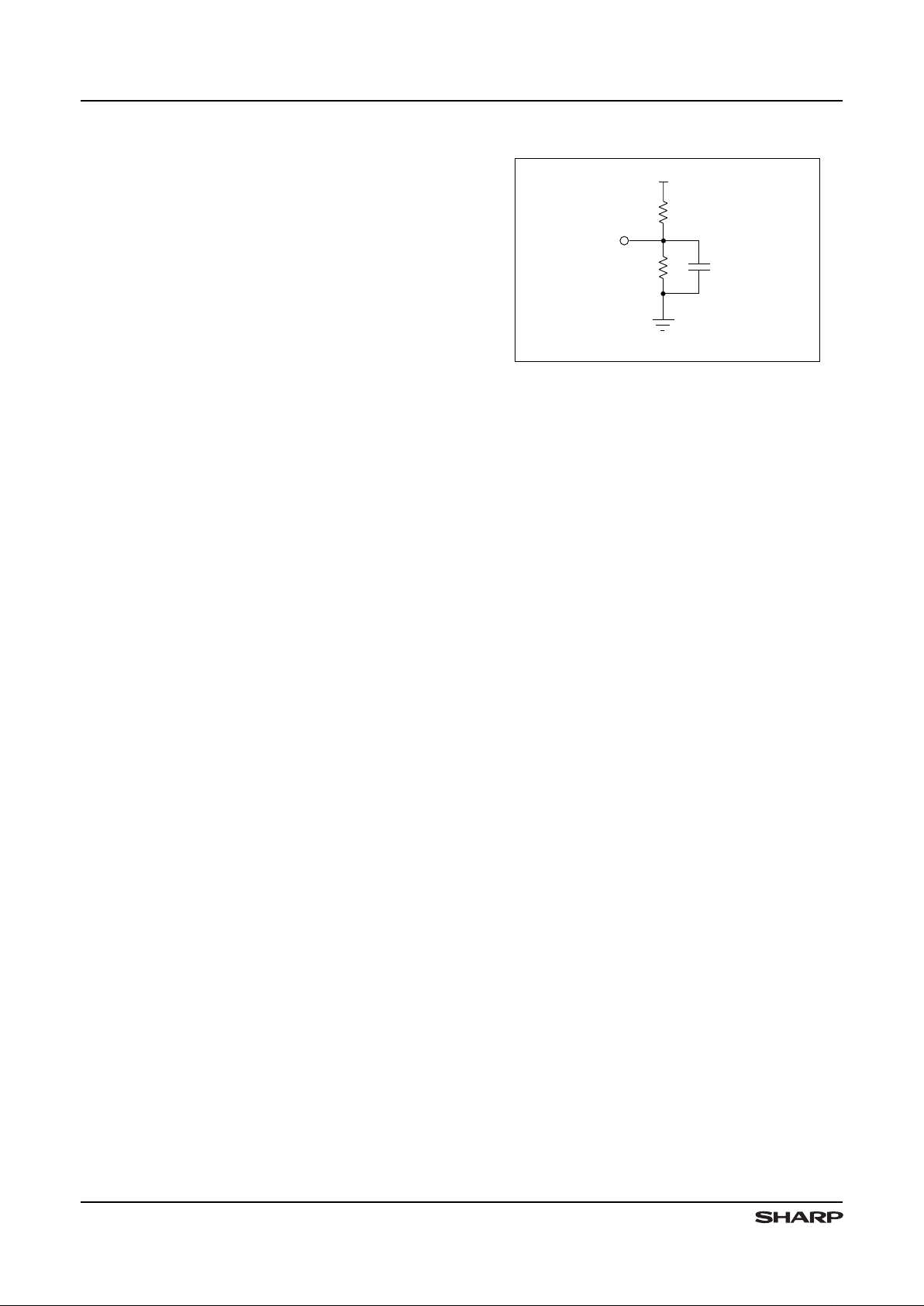

AC TE ST C O NDI T IO N S

PARAMETER RAT IN G

Input Pulse Levels

VSS to 3 V

Input Rise and Fall Times (10% to 90%)

5 ns

Input Tim ing Ref ere nce Lev els

1.5 V

Output Refer ence Le vels

1.5 V

Output L oad, Timing Test s

Figure 4

CAP ACI TANCE

1,2

PARAMETER RATING

CIN (Input Capacitance)

5 pF

C

OUT

(Output Capacitance)

7 pF

NOTES:

1. Sample tested only.

2. Capacitances are maximum values at 25oC measured at 1.0 MHz

with VIN = 0 V.

5496-4

DEVICE

UNDER

TEST

+5 V

30 pF

1.1 k Ω

680 Ω

INCLUDES JIG & SCOPE CAPACITANCES

*

*

Figure 4. Output Load C ircuit

LH5496/96H CMOS 512 × 9 FIFO

4

AC ELECTRICAL CHARACTERISTICS 1 (Over Operat ing Range)

SYMBOL PARAMETER

tA = 15 ns 2tA = 20 ns tA = 25 ns tA = 35 ns tA = 50 ns tA = 65 ns tA = 80 ns

UNIT

MIN MAX MIN MAX MIN MAX MIN MAX MIN MAX MIN

MAX

MIN MAX

READ CYCLE TIMING

t

RC

Read Cycle Time 25 – 30 – 35 – 45 – 65 – 80 – 100 – ns

t

A

Access T im e – 15 – 20 – 25 – 35 – 50 – 65 – 80 ns

t

RR

Read Recover Time 10 – 10 – 10 – 10 – 15 – 15 – 15 – ns

t

RPW

Read Pulse Width

3

15 – 20 – 25 – 35 – 50 – 65 – 80 – ns

t

RLZ

Data Bus Active from Read LOW 45 – 5– 5–5– 5– 5–10– ns

t

WLZ

Data Bus Acti ve fro m Wri te

HIGH

4,5

10 – 10 – 10 – 10 – 10 – 10 – 20 – ns

t

DV

Data Valid from Read Pulse HIGH

5 – 5– 5–5– 5– 5–5 –ns

t

RHZ

Data Bus High-Z from Read

HIGH

4

– 15 – 15 – 15 – 15 – 20 – 30 – 30 ns

WRITE CYCLE TIMING

t

WC

Write Cycle Time 25 – 30 – 35 – 45 – 65 – 80 – 100 – ns

t

WPW

Write Pulse Width

3

15 – 20 – 25 – 35 – 50 – 65 – 80 – ns

t

WR

Write Recovery Time 10 – 10 – 10 – 10 – 15 – 15 – 15 – ns

t

DS

Data Setup Time 10 – 10 – 10 – 15 – 20 – 20 – 20 – ns

t

DH

Data Hold Time 0 – 0 – 0 – 0 – 0 – 5 – 5 – ns

RES ET TIMING

t

RSC

Reset Cycl e Ti me 25 – 30 – 35 – 45 – 65 – 80 – 100 – ns

t

RS

Reset Puls e Width

3

15 – 20 – 25 – 35 – 50 – 65 – 80 – ns

t

RSR

Reset Reco very Ti me 10 – 10 – 10 – 10 – 15 – 15 – 15 – ns

t

RRSS

Read HIGH to RS HIGH 15 – 20 – 25 – 35 – 50 – 65 – 80 – ns

t

WRSS

Write HIGH to RS HIGH 15 – 20 – 25 – 35 – 50 – 65 – 80 – ns

RETRANSMIT TIMING

t

RTC

Retransmit Cycle Time

25 – 30 – 35 – 45 – 65 – 80 – 100 – ns

t

RT

Retransmit Pulse Width

3

15 – 20 – 25 – 35 – 50 – 65 – 80 – ns

t

RTR

Retransmit Recovery Time 10 – 10 – 10 – 10 – 15 – 15 – 15 – ns

FLAG TIMING

t

EFL

Reset LOW to Empt y Flag LOW – 25 – 30 – 35 – 45 – 65 – 80 – 100 ns

t

HFH,FFH

Reset LOW to Half -Fu ll and Full

Flags HIGH

– 25 – 30 – 35 – 45 – 65 – 80 – 100 ns

t

REF

Read LOW to Empty Flag LOW – 20 – 25 – 25 – 35 – 45 – 60 – 60 ns

t

RFF

Read HIGH to Full Flag HIGH – 20 – 25 – 25 – 35 – 45 – 60 – 60 ns

t

WEF

Write HIGH to Empty Flag HIGH – 20 – 25 – 25 – 35 – 45 – 60 – 60 ns

t

WFF

Write LOW to Full Flag LOW – 20 – 25 – 25 – 35 – 45 – 60 – 60 ns

t

WHF

Write LOW to Half-Full Flag LOW

– 25 – 30 – 35 – 45 – 65 – 80 – 100 ns

t

RHF

Read HIGH to Half -Fu ll Flag HIG H – 25 – 30 – 35 – 45 – 65 – 80 – 100 ns

EXPANSION TIMING

t

XOL

Expansion Out LOW – 18 – 20 – 25 – 35 – 50 – 65 – 80 ns

t

XOH

Expansion Out HIGH – 18 – 20 – 25 – 35 – 50 – 65 – 80 ns

t

XI

Expansion In Pulse Width 15 – 20 – 25 – 35 – 50 – 65 – 80 – ns

t

XIR

Expansi on In Reco very Tim e 10 – 10 – 10 – 10 – 10 – 10 – 10 – ns

t

XIS

Expansi on in Setu p Ti me 7 – 10 – 10 – 15 – 15 – 15 – 15 – ns

NOTES :

1. LH5496 only.

2. A ll timing measurements performed at ‘AC Test Condition’ levels.

CMOS 512 × 9 FIFO LH5496/96H

5

Loading...

Loading...