Sharp LH5164AVHT, LH5164AVHN Datasheet

LH5164AVH

CMOS 6 4K (8 K × 8) S tatic RA M

FEATURES

•• 8,192 × 8 bit orga niza ti on

•• Access time: 200 ns (MAX.)

•• Supply curre nt (MAX.):

Operating : 90 mW

29 mW (t

RC

, tWC = 1 µs)

Standb y: 3.6 µW (MAX.) @ 70°C

10.8 µW (MAX.) @ 85°C

Data reten tion:

0.6 µW (V

CC

= 3 V, tA = 25°C)

•• Low voltag e ope ration : 3.3 V ±0.3 V

•• Fully-static operatio n

•• TTL compatible I/O

•• Three-state outputs

•• Packages:

28-pi n , 450 -mil S OP

28-pi n , 8 × 13 mm

2

TSOP (Type I)

DESCRIPTION

The LH5164AVH is a static RAM organized as

8,192 × 8 bits. It is fabricated using silicon-gate CMOS

process technology.

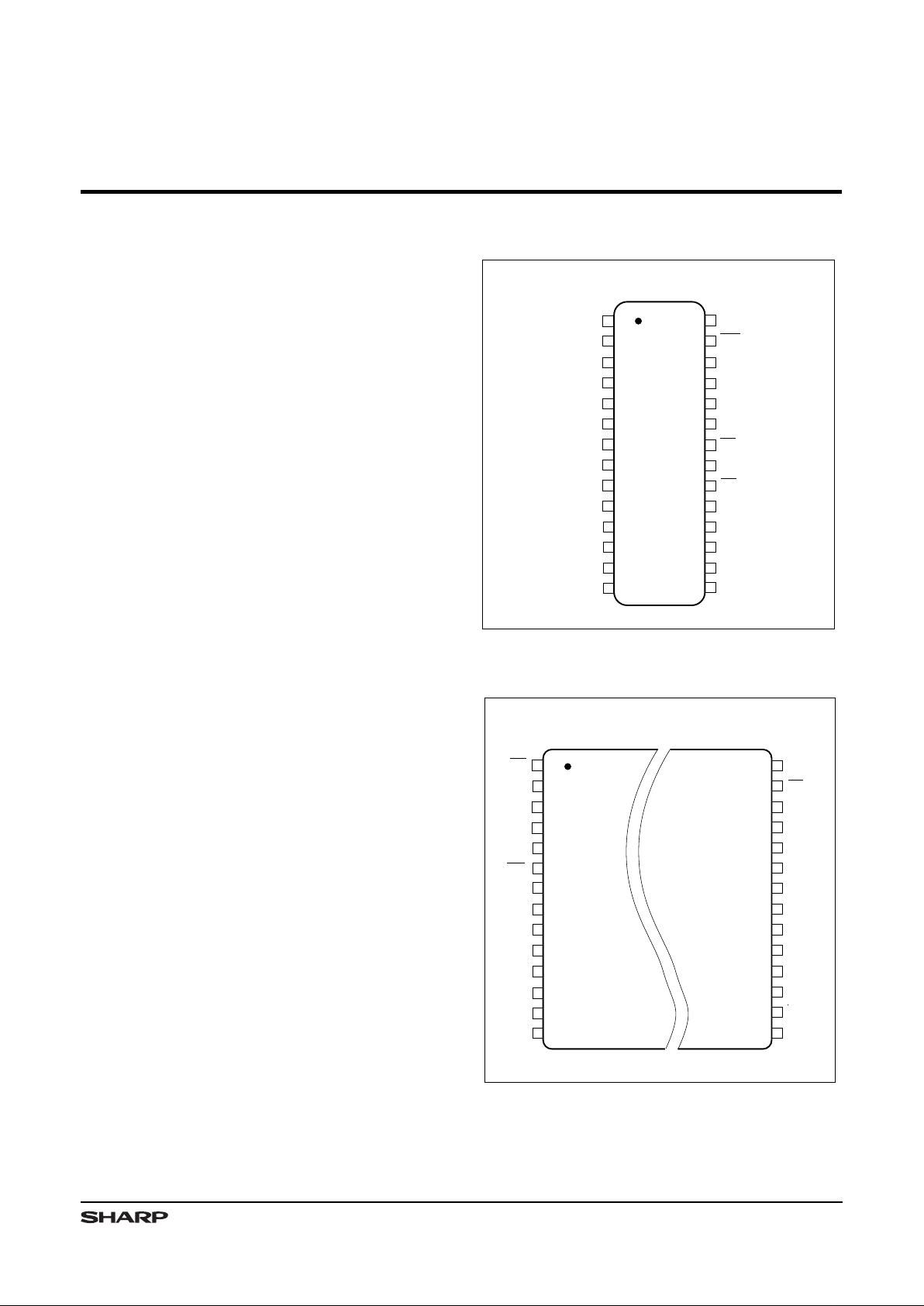

PIN CONNECTIONS

1

2

3

4

7

8

A

2

A

5

26

25

24

23

22

21

18

15

A

7

A

6

5

6

A

3

A

4

20

19

A

12

GND

A

8

A

11

A

10

CE

1

9

10

11

28

27

WE

A

1

V

CC

12

17

16

A

0

I/O

1

A

9

13

14

NC

OE

I/O

2

I/O

3

I/O

7

I/O

6

I/O

5

I/O

4

I/O

8

CE

2

5164AVH-1

TOP VIEW

28-PIN SOP

Figure 1. Pin Connections for SOP Package

2

3

4

5

6

9

10

7

8

A

11

11

1

28

27

26

25

22

21

24

23

20

19

A

10

28-PIN TSOP (Type I)

12

13

14

17

16

18

15

OE

A

8

A

9

CE

2

WE

A

12

NC

I/O

3

I/O

2

A

1

I/O

8

CE

1

I/O

6

I/O

7

GND

I/O

5

I/O

4

I/O

1

A

0

5164AVH-2

V

CC

A

7

A

6

A

5

A

4

A

3

A

2

TOP VIEW

Figure 2. Pin Connect ions for TSOP Package

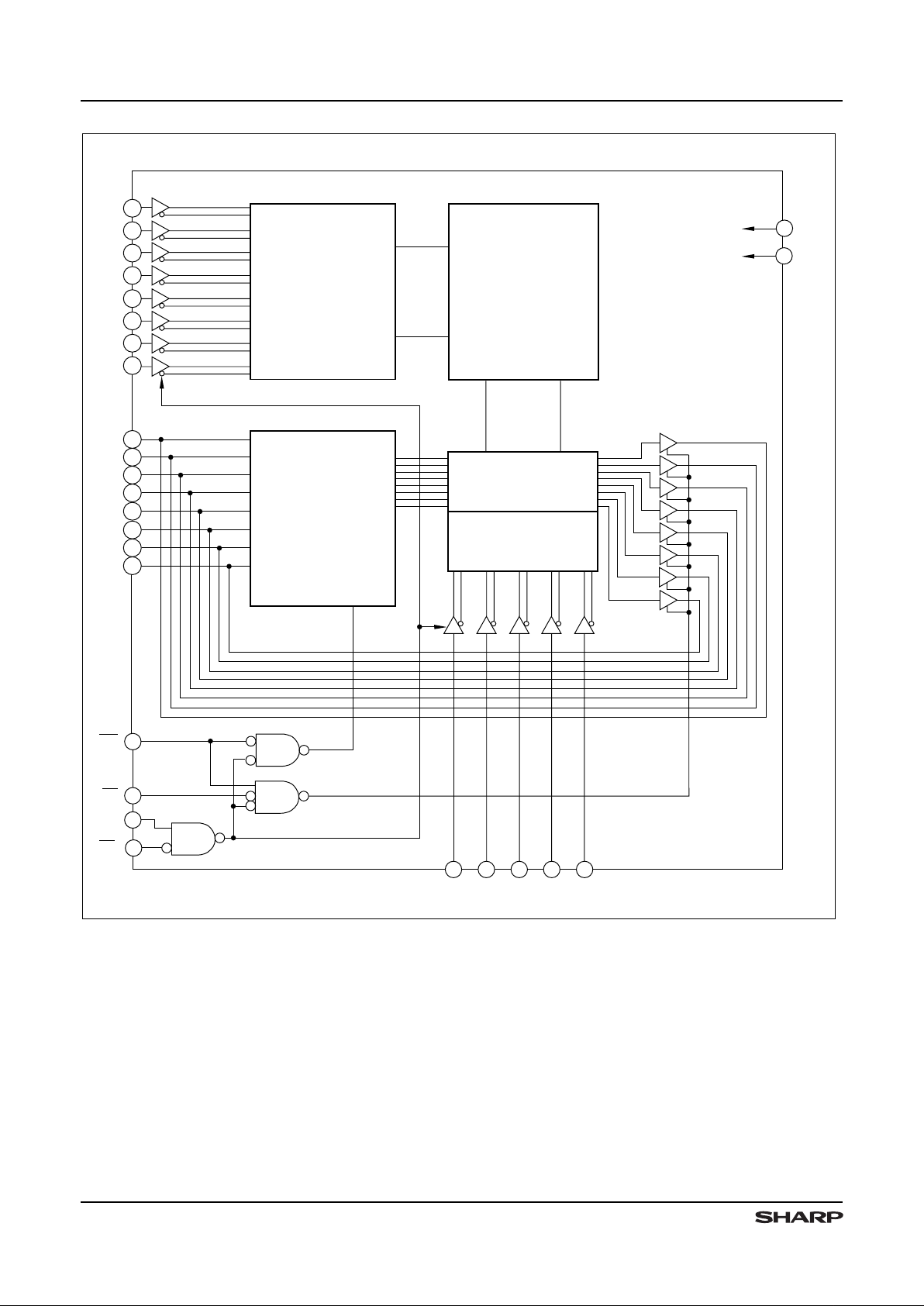

1

I/O

8

A

5

A

4

A

3

11

15

18

5164AVH-3

MEMORY

ARRAY

(256 x 256)

13

17

12

16

A

6

WE

A

7

A

12

27

A

8

COLUMN I/O

CIRCUITS

COLUMN SELECT

V

CC

GND

OE

I/O

7

I/O

6

I/O

5

I/O

4

I/O

3

I/O

2

I/O

1

22

19

8

A

2A1A0A11

23

9

10

28

14

A

9

CE

1

20

26

CE

2

INPUT

DATA

CONTROL

A

10

21

ROW

SELECT

5

6

7

4

3

2

25

24

NOTE: Pin numbers apply to the 28-pin SOP.

Figure 3. LH5164AVH Block Diagram

PIN DESCRIPTI ON

SIGNA L PIN N AME

A0 - A

12

Addre ss inputs

CE1/CE

2

Chip Ena ble in put

WE Write E na ble inp ut

OE Outpu t E nab le inp ut

SIGNAL PIN NAM E

I/O1 - I/O

8

Data i npu ts and ou tpu ts

V

CC

Power sup ply

GND Ground

NC No connec tion

LH5164AVH CMOS 64K (8 K × 8) Static RAM

2

TRUTH TABLE

CE

1

CE

2

WE OE MODE I/O1 - I/O

8

SUPPLY CU RRENT NOTE

HXXX

Standby High-Z Standby (I

SB

)1

XLXX

L H L X Write Data input Operating (ICC)1

L H H L Read Data output Operating (I

CC

)

L H H H Output disable High-Z Operating (I

CC

)

NOTE:

1. X = H or L

ABSOLUTE MAXIMUM RATINGS

PARAMETER SYMBOL RATING UNIT NOTE

Suppl y v olt age

V

CC

–0.3 to +7.0 V 1

Input vol tage V

IN

–0.3 to VCC +0.3 V 1, 2

Operating temperature Topr –40 to +85 °C

Storag e t emp era ture

Tstg –65 to +150 °C

NOTES:

1. The maximum applicable voltage on any pin with respect to GND.

2.

V

IN

(MIN.) = –3. 0 V for pu lse widt h ≤ 50 ns.

RECOMMENDED OPERATING CON DITIONS (TA = –40°C to +85°C)

PARAMETE R SYMB OL MIN. TYP. MAX. UNIT N OTE

Suppl y v olt age V

CC

3.0 3.3 3.6 V

Input vol tage

V

IH

VCC – 0.5 VCC + 0.3 V

V

IL

–0.3 0.2 V 1

NOTE:

1.

V

IL

(MIN.) = –3. 0 V for p ulse w idt h ≤50 ns.

DC CHARACTERISTICS 1 (TA = –40°C to +85°C, VCC = 3.3 V ±0.3 V)

PARAMETER SYMBOL CONDITIONS MIN. MAX. UNIT NOTE

Input lea kage

curren t

I

LI

VIN = 0 V to V

CC

–1.0 1.0

µA

Output le aka ge

curren t

I

LO

CE1 = VIH or CE2 = VIL or

OE = VIH or WE = V

IL

V

I/O

= 0 to V

CC

–1.0 1.0 µA

Operat ing su ppl y

curren t

I

CC

CE1 = 0.2 V, VIN = 0.2 V, or

V

CC

– 0.2 V

CE

2

= VCC – 0.2 V,

Outputs open

t

CYCLE

=

200 ns

25

mA

t

CYCLE

=

1.0 µs

8

Standb y c urr ent

I

SB

CE2 ≤ 0.2 V or

CE1 ≥ VCC – 0.2 V

T

A

≤ +70° C

1.0

µA

1

T

A

≤ +85°C

3.0

I

SB1

CE1 = V

IH or CE2

= V

IL

5mA

Output vo lta ge

V

OL

IOL = 500 µA

0.4 V

V

OH

IOH = –500 µ A

V

CC

–

0.5

V

NOTE:

1.

CE

2

should be ≥ VCC – 0.2 V or ≤ 0. 2 V when CE1 ≥ V

CC

– 0.2 V.

CMOS 64K (8K × 8) Static RAM LH5164AVH

3

Loading...

Loading...