Sharp LH5116HD-10, LH5116H-10, LH5116H, LH5116, LH5116N-10 Datasheet

...

LH5116/H

CMOS 1 6K (2 K × 8) S tatic RA M

FEATURES

•• 2,048 × 8 bit orga niza ti on

•• Access time: 100 ns (MAX.)

•• Power consu mption :

Operating : 22 0 mW (MAX.)

Standb y: 5.5 µW (MAX.)

•• Single +5 V p owe r su ppl y

•• Fully-static operatio n

•• TTL compatible I/O

•• Three-state outputs

•• Wide temp erature ra nge a vail able

LH5 116H: -40 to +8 5°C

•• Packa ges:

24-pi n , 600 -mil DIP

24-pi n , 300 -mil SK-DIP

24-pi n , 450 -mil S OP

DESCRIPTION

The LH51 16/H are static RAM s organized as 2,048 × 8

bits. It is fabri cated using silicon-gate C MOS process

technology. It features high speed access in read m ode

using output enable (tOE).

PIN CONNECTIONS

24-PIN DIP

24-PIN SK-DIP

24-PIN SOP

A

A

A

A

A

A

A

I/O

I/O

I/O

GND

Vcc

1

7

2

6

3

5

4

4

5

3

6

2

A

7

1

8

0

9

1

10

2

11

3

12

24

23

22

20

19

18

17

16

15

14

13

21

A

A

WE

OE

A

CE

I/O

I/O

I/O

I/O

I/O

TOP VIEW

8

9

10

8

7

6

5

4

5116-1

Figure 1. Pin Connections for DIP, SK-DIP,

and SOP Packages

1

LH5116/H CMOS 16K (2K × 8) Static RAM

8

A

0

3

A

A

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

5

A

2

6

A

1

7

23

A

8

A

22

9

19

10

9

1

10

2

11

3

13

4

14

5

15

6

16

7

17

8

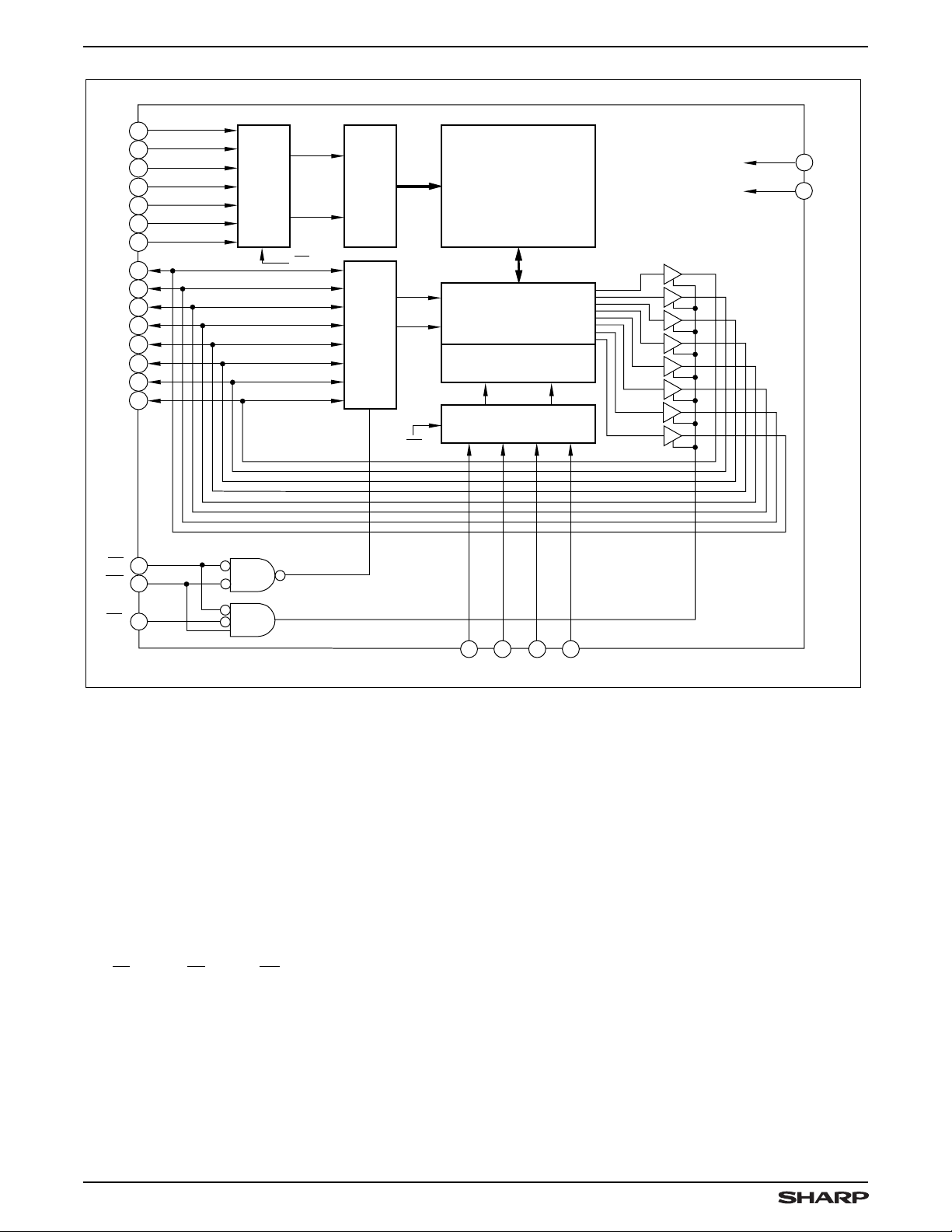

BUFFERS

ROW ADDRESS

CE

ROW DECODERS

DATA CONTROL

MEMORY CELL

ARRAY

(128 x128)

COLUMN

I/O CIRCUIT

COLUMN DECODERS

COLUMN ADDRESS

BUFFERS

CE

24

12

V

CC

GND

CE

18

21

WE

20

OE

5

4

A

4A3A2A1

6

Figure 2. LH5116/H Block Diagram

PIN DESCRIPTION

SIGNA L PIN N AME

A0 - A

10

Addre ss input

CE Ch ip Ena ble in put

OE Ou tpu t E nab le inp ut

WE Wri te E na ble inp ut

SIGNAL PIN NAME

I/O1 - I/O

V

GND Ground

TRUTH TABLE

CE OE WE MODE I/O1 - I/O

L X L Write D

L L H Read D

IN

OUT

H X X Deselect High-Z Standby (I

L H X Outputs disable High-Z Operating (I

NOTE:

1. X = H or L

SUPPLY CURRENT NOTE

8

7

Data i npu t/o utp ut

8

CC

Power sup ply

Operating (ICC) 1

Operating (ICC)

)1

SB

)1

CC

5116-2

2

CMOS 16K (2K × 8) Static RAM LH5116/H

ABSOLUTE MAXIMUM RATINGS

PARAMETER SYMBOL RATING UNIT NOTE

Suppl y v olt age

Input vol tage V

V

CC

IN

Operat ing te mpe ratu re Topr

Storage temperature Tstg -55 to +150

NOTES:

1. The maximum applicable voltage on any pin with respect to GND.

2. Applied to the LH5116/D/NA

3. Applied to the LH5116H/HD/HN

-0.3 to +7.0 V 1

-0.3 to VCC + 0.3 V 1

0 to +70

-40 to +85 3

°C

°C

2

RECOMMENDED OPERATING CONDITIONS

PARAMETER SYMBOL MIN. TYP . MAX. UNIT

Suppl y v olt age V

Input vol tage

NOTE:

1.

T

= 0 to 7 0°C (LH5116/D/NA), TA = -40 to +85 °C (LH5116H/HD/HN)

A

CC

V

IH

V

IL

4.5 5.0 5.5 V

2.2 VCC + 0.3 V

-0.3 0.8 V

1

DC CHARACTERISTICS 1 (VCC = 5 V ±10%)

PARAMETER SYMBOL CONDITIONS MIN. TYP. MAX. UNIT NOTE

Output ‘L OW’ v olta ge V

Output ‘H IGH ’ vol tage V

Input lea kag e c urr ent

Output le aka ge cur ren t I

Operat ing cu rre nt

Standb y c urr ent I

NOTES:

1.

T

= 0 to 7 0°C (LH5116/D/NA), TA = -40 to +85 °C (LH5116H/HD/HN)

A

CE = 0 V; all other input pins = 0 V to V

2.

3. CE = VIL; all other input pins = VIL to V

4.

T

= 25°C

A

OL

OH

I

LI

LO

I

CC1

I

CC2

SB

All other input pins = 0 V to V

CC

IH

IOL = 2.1 mA 0.4 V

IOH = -1.0 mA 2.4 V

VIN = 0 V to V

CE = VIH, V

= 0 V to V

I/O

CC

CC

Outputs open (OE = VCC)2530mA2

Outputs open (OE = VIH)3040mA3

CE ≥ V

CC

- 0.2 V

-1.0 1.0 µA

-1.0 1.0

CC

µA

1.0

0.2 4

µA

AC CHARACTERISTICS

1

(1) READ CYCLE (VCC = 5 V ±10%)

PARAMETER SYMBOL MIN. TYP. MAX. UNIT NOTE

Read c yc le t ime t

Addres s a cc ess ti me t

Chip e nab le acc es s ti me t

Chip e nab le Low to ou tpu t in Lo w-Z t

Output en abl e a cce ss tim e t

Output en abl e L ow to o utp ut in Low -Z t

Chip d isa ble to ou tpu t i n Hi gh- Z t

Output disable to outp ut in High-Z t

Output ho ld time t

NOTES:

1.

T

= 0 to 7 0°C (LH5116/NA/D). TA = -40 to 8 5°C (LH5116H/HD/HN).

A

2.

Active output to high-impedance and high-impedance to output active tests specified for a ±200 mV transition

from steady state levels into the test load.

RC

AA

ACE

CLZ

OE

OLZ

CHZ

OHZ

OH

100 ns

100 ns

100 ns

10 ns 2

40 ns

10 ns 2

040ns2

040ns2

10 ns

3

Loading...

Loading...