Page 1

TopPage

LC-37D90U

SERVICE MANUAL

No. S56S8LC37D90U

LCD COLOR TELEVISION

In the interests of user-safety (Required by safety regulations in some countries) the set should

be restored to its original condition and only parts identical to those specified should be used.

CONTENTS

SAFETY PRECAUTION

CHAPTER 1. SPECIFICATIONS

CHAPTER 2. OPERATION MANUAL

CHAPTER 3. DIMENSIONS

CHAPTER 4. REMOVING OF MAJOR PARTS

CHAPTER 5. ADJUSTMENT

CHAPTER 6. TROUBLE SHOOTING TABLE

CHAPTER 7. OVERALL WIRING/BLOCK DIAGRAM

CHAPTER 8. SCHEMATIC DIAGRAM

MODEL

LC-37D90U

CHAPTER 9. PRINTED WIRING BOARD ASSEMBLIES

Parts Guide

Parts marked with " " are important for maintaining the safety of the set. Be sure to replace these parts with specified ones for maintaining the

safety and performance of the set.

This document has been published to be used for

after sales service only.

The contents are subject to change without notice.

Page 2

LC-37D90U

SAFETY PRECAUTION

IMPORTANT SERVICE SAFETY PRE-

CAUTION.........................................................i

PRECAUTIONS A PRENDRE LORS DE

LA REPARATION............................................ ii

PRECAUTIONS FOR USING LEAD-

FREE SOLDER.............................................. iii

CHAPTER 1. SPECIFICATIONS

[1] SPECIFICATIONS ...................................... 1-1

CHAPTER 2. OPERATION MANUAL

[1] OPERATION MANUAL ............................... 2-1

CHAPTER 3. DIMENSIONS

[1] DIMENSIONS ............................................. 3-1

CHAPTER 4. REMOVING OF MAJOR PARTS

[1] REMOVING OF MAJOR PARTS ................ 4-1

CONTENTS

CHAPTER 5. ADJUSTMENT

[1] ADJUSTMENT PROCEDURE.................... 5-1

[2] MAJOR IC INFORMATIONS .................... 5-17

CHAPTER 6. TROUBLE SHOOTING TABLE

[1] TROUBLE SHOOTING TABLE................... 6-1

CHAPTER 7. OVERALL WIRING/BLOCK DIAGRAM

[1] OVERALL WIRING DIAGRAM ................... 7-1

[2] SYSTEM BLOCK DIAGRAM ...................... 7-3

[3] MAIN BLOCK DIAGRAM ............................ 7-5

[4] POWER BLOCK DIAGRAM ....................... 7-7

CHAPTER 8. SCHEMATIC DIAGRAM

[1] DESCRIPTION OF SCHEMATIC DIA-

GRAM ......................................................... 8-1

[2] R/C, LED Unit ............................................. 8-2

[3] IF Unit ......................................................... 8-3

[4] MAIN Unit.................................................... 8-7

[5] KEY Unit ................................................... 8-53

[6] SPEAKER TERMINAL-L Unit ................... 8-54

[7] SPEAKER TERMINAL-R Unit................... 8-54

CHAPTER 9. PRINTED WIRING BOARD ASSEMBLIES

[1] IF Unit ......................................................... 9-1

[2] MAIN Unit.................................................... 9-3

[3] R/C, LED Unit ............................................9-11

[4] KEY Unit ....................................................9-11

[5] SPEAKER TERMINAL-L Unit ................... 9-12

[6] SPEAKER TERMINAL-R Unit................... 9-12

Parts Guide

Page 3

LC-37D90U

LC-37D90U

SAFETY PRECAUTION

Service Manual

IMPORTANT SERVICE SAFETY PRECAUTION

Service work should be performed only by qualified service technicians who are thoroughly familiar with all safety checks and the

servicing guidelines which follow:

WARNING

1. For continued safety, no modification of any circuit should be

attempted.

2. Disconnect AC power before servicing.

CAUTION: FOR CONTINUED

PROTECTION AGAINST A RISK OF

FIRE REPLACE ONLY WITH SAME

TYPE FUSE.

AV

F701 (125V 8A),

F4701, F5701 (250V 3A ~ 115

O

C)

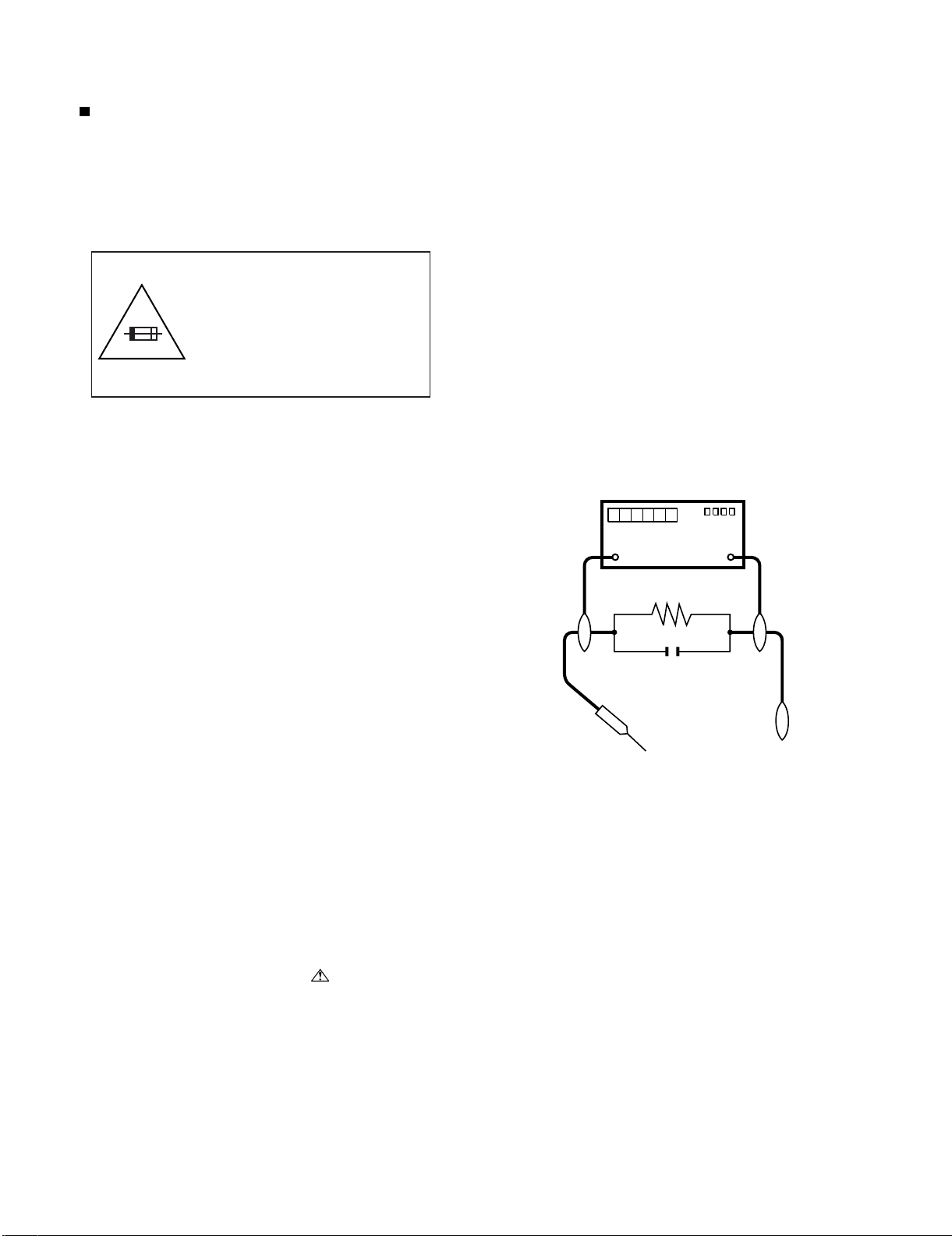

• Use an AC voltmeter having with 5000 ohm per volt, or higher, sensitivity or measure the AC voltage drop across the resistor.

• Connect the resistor connection to all exposed metal parts having a

return to the chassis (antenna, metal cabinet, screw heads, knobs

and control shafts, escutcheon, etc.) and measure the AC voltage

drop across the resistor.

All checks must be repeated with the AC cord plug connection

reversed. (If necessary, a nonpolarized adaptor plug must be used

only for the purpose of completing these checks.)

Any reading of 0.75 Vrms (this corresponds to 0.5 mA rms AC.) or

more is excessive and indicates a potential shock hazard which

must be corrected before returning the monitor to the owner.

DVM

BEFORE RETURNING THE RECEIVER (Fire &

Shock Hazard)

Before returning the receiver to the user, perform the following

safety checks:

3. Inspect all lead dress to make certain that leads are not pinched,

and check that hardware is not lodged between the chassis and

other metal parts in the receiver.

4. Inspect all protective devices such as non-metallic control knobs,

insulation materials, cabinet backs, adjustment and compartment

covers or shields, isolation resistor-capacitor networks, mechanical

insulators, etc.

5. To be sure that no shock hazard exists, check for leakage current in

the following manner.

• Plug the AC cord directly into a 120 volt AC outlet.

• Using two clip leads, connect a 1.5k ohm, 10 watt resistor paralleled by a 0.15µF capacitor in series with all exposed metal cabinet

parts and a known earth ground, such as electrical conduit or electrical ground connected to an earth ground.

///////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

TO EXPOSED

METAL PARTS

AC SCALE

1.5k ohm

10W

0.15µF

TEST PROBE

CONNECT TO

KNOWN EARTH

GROUND

SAFETY NOTICE

Many electrical and mechanical parts in LCD color television have

special safety-related characteristics.

These characteristics are often not evident from visual inspection, nor

can protection afforded by them be necessarily increased by using

replacement components rated for higher voltage, wattage, etc.

Replacement parts which have these special safety characteristics are

identified in this manual; electrical components having such features

are identified by " " and shaded areas in the Replacement Parts List

and Schematic Diagrams.

///////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

For continued protection, replacement parts must be identical to those

used in the original circuit.

The use of a substitute replacement parts which do not have the same

safety characteristics as the factory recommended replacement parts

shown in this service manual, may create shock, fire or other hazards.

i

Page 4

LC-37D90U

PRECAUTIONS A PRENDRE LORS DE LA REPARATION

Ne peut effectuer la réparation qu' un technicien spécialisé qui s'est parfaitement accoutumé à toute vérification de sécurité et aux

conseils suivants.

AVERTISSEMENT

6. N'entreprendre aucune modification de tout circuit. C'est dangereux.

7. Débrancher le récepteur avant toute réparation.

PRECAUTION:POURLA

PROTECTION CONTINUE

CONTRE LES RISQUES

D'INCENDIE, REMPLACER LE

FUSIBLE

AV

F701 (125V 8A),

F4701, F5701 (250V 3A ~ 115

O

C)

VERIFICATIONS CONTRE L'INCEN-DIE ET LE

CHOC ELECTRIQUE

Avant de rendre le récepteur à l'utilisateur, effectuer les vérifications suivantes.

8. Inspecter tous les faisceaux de câbles pour s'assurer que les fils ne

soient pas pincés ou qu'un outil ne soit pas placé entre le châssis

et les autres pièces métalliques du récepteur.

9. Inspecter tous les dispositifs de protection comme les boutons de

commande non-métalliques, les isolants, le dos du coffret, les couvercles ou blindages de réglage et de compartiment, les réseaux

de résistancecapacité, les isolateurs mécaniques, etc.

10.S'assurer qu'il n'y ait pas de danger d'électrocution en vérifiant la

fuite de courant, de la facon suivante:

• Brancher le cordon d'alimentation directem-ent à une prise de courant de 120V. (Ne pas utiliser de transformateur d'isolation pour cet

essai).

• A l'aide de deux fils à pinces, brancher une résistance de 1.5 kΩ 10

watts en parallèle avec un condensateur de 0.15µF en série avec

toutes les pièces métalliques exposées du coffret et une terre connue comme une conduite électrique ou une prise de terre branchée

à la terre.

• Utiliser un voltmètre CA d'une sensibilité d'au moins 5000Ω/V pour

mesurer la chute de tension en travers de la résistance.

• Toucher avec la sonde d'essai les pièces métalliques exposées qui

présentent une voie de retour au châssis (antenne, coffret métallique, tête des vis, arbres de commande et des boutons, écusson,

etc.) et mesurer la chute de tension CA en-travers de la résistance.

Toutes les vérifications doivent être refaites après avoir inversé la

fiche du cordon d'alimentation. (Si nécessaire, une prise d'adpatation non polarisée peut être utilisée dans le but de terminer ces

vérifications.)

La tension de pointe mesurèe ne doit pas dépasser 0.75V (correspondante au courant CA de pointe de 0.5mA).

Dans le cas contraire, il y a une possibilité de choc électrique qui

doit être supprimée avant de réndre le recepteur au client.

DVM

ECHELLE CA

1.5k ohm

10W

µ

F

0.15

SONDE D'ESSAI

AUX PIECES

METALLIQUES

EXPOSEES

///////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

BRANCHER A UNE

TERRE CONNUE

AVIS POUR LA SECURITE

De nombreuses pièces, électriques et mécaniques, dans les téléviseur

ACL présentent des caractéristiques spéciales relatives à la sécurité,

qui ne sont souvent pas évidentes à vue. Le degré de protection ne

peut pas être nécessairement augmentée en utilisant des pièces de

remplacement étalonnées pour haute tension, puissance, etc.

Les pièces de remplacement qui présentent ces caractéristiques sont

identifiées dans ce manuel; les pièces électriques qui présentent ces

particularités sont identifiées par la marque " " et hachurées dans la

liste des pièces de remplacement et les diagrammes schématiques.

///////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

Pour assurer la protection, ces pièces doivent être identiques à celles

utilisées dans le circuit d'origine. L'utilisation de pièces qui n'ont pas

les mêmes caractéristiques que les pièces recommandées par l'usine,

indiquées dans ce manuel, peut provoquer des électrocutions, incendies, radiations X ou autres accidents.

ii

Page 5

LC-37D90U

PRECAUTIONS FOR USING LEAD-FREE SOLDER

Employing lead-free solder

• "PWBs" of this model employs lead-free solder. The LF symbol indicates lead-free solder, and is attached on the PWBs and service manuals. The

alphabetical character following LF shows the type of lead-free solder.

Example:

Indicates lead-free solder of tin, silver and copper. Indicates lead-free solder of tin, silver and copper.

Using lead-free wire solder

• When fixing the PWB soldered with the lead-free solder, apply lead-free wire solder. Repairing with conventional lead wire solder may cause damage or accident due to cracks.

As the melting point of lead-free solder (Sn-Ag-Cu) is higher than the lead wire solder by 40 °C, we recommend you to use a dedicated soldering

bit, if you are not familiar with how to obtain lead-free wire solder or soldering bit, contact our service station or service branch in your area.

Soldering

• As the melting point of lead-free solder (Sn-Ag-Cu) is about 220 °C which is higher than the conventional lead solder by 40 °C, and as it has poor

solder wettability, you may be apt to keep the soldering bit in contact with the PWB for extended period of time. However, Since the land may be

peeled off or the maximum heat-resistance temperature of parts may be exceeded, remove the bit from the PWB as soon as you confirm the

steady soldering condition.

Lead-free solder contains more tin, and the end of the soldering bit may be easily corroded. Make sure to turn on and off the power of the bit as

required.

If a different type of solder stays on the tip of the soldering bit, it is alloyed with lead-free solder. Clean the bit after every use of it.

When the tip of the soldering bit is blackened during use, file it with steel wool or fine sandpaper.

• Be careful when replacing parts with polarity indication on the PWB silk.

Lead-free wire solder for servicing

Part No, Description Code

ZHNDAi123250E J φ0.3mm 250g(1roll) BL

ZHNDAi126500E J φ0.6mm 500g(1roll) BK

ZHNDAi12801KE J φ1.0mm 1kg(1roll) BM

iii

Page 6

LC-37D90U

LC-37D90U

CHAPTER 1. SPECIFICATIONS

[1] SPECIFICATIONS

Item Model: LC-37D90U

Service Manual

LCD panel

Number of dots

TV-standard

TV

Function

Receiving

Channel

Audio multiplex

Audio out

Terminals

Rear

VHF/UHF

CATV

Digital Terrestrial

Broadcast (8VSB)

Digital cable*

(64/256 QAM)

INPUT 1

INPUT 2

INPUT 3

INPUT 4

INPUT 5

Air ANTENNA

Cable ANTENNA

i.LINK

DIGITAL AUDIO OUTPUT

37" Advanced Super View & BLACK TFT LCD

6,220,800 dots (1920 1080 3 dots)

American TV Standard ATSC/NTSC System

VHF 2-13ch, UHF 14-69ch

1-135ch (non-scrambled channel only)

2-69ch

1-135ch (non-scrambled channel only)

BTSC System

10W 2

AV in, COMPONENT in

AV in, S-VIDEO in

HDMI in with HDCP

Audio in, HDMI in with HDCP

Audio in, DVI-I in with HDCP

75 Unbalance, F Type for VHF/UHF/Digital Air in 1

75 Unbalance, F Type for CATV/Digital Cable in 1

IEEE1394 2 with DTCP (Compatible with DTVLink)

Optical Digital audio output 1 (PCM/Dolby Digital)

OUTPUT

OSD language

Power Requirement

Power Consumption

w/o stand

Weight

with stand

Dimension

(W H D)

w/o stand

with stand

Accessories

Operating temperature

Audio out

English/French/Spanish

AC 120 V, 60 Hz

230 W

50.7 lbs./23.0 kg

62.9 lbs./28.5 kg

5

/8269/

36

5

/82845/

36

64

64

413/16inch

121/16inch

Remote control unit ( 1), AC cord ( 1), "AAA" size battery ( 2), Cable clamp ( 1),

Cable tie ( 1), Operation manual ( 1)

32°F to 104°F (0°C to 40°C)

* Emergency alert messages via Cable are unreceivable.

• As part of policy of continuous improvement, SHARP reserves the right to make design and specification changes for product

improvement without prior notice. The performance specification figures indicated are nominal values of production units.

There may be some deviations from these values in individual units.

1 – 1

Page 7

LC-37D90U

CHAPTER 2. OPERATION MANUAL

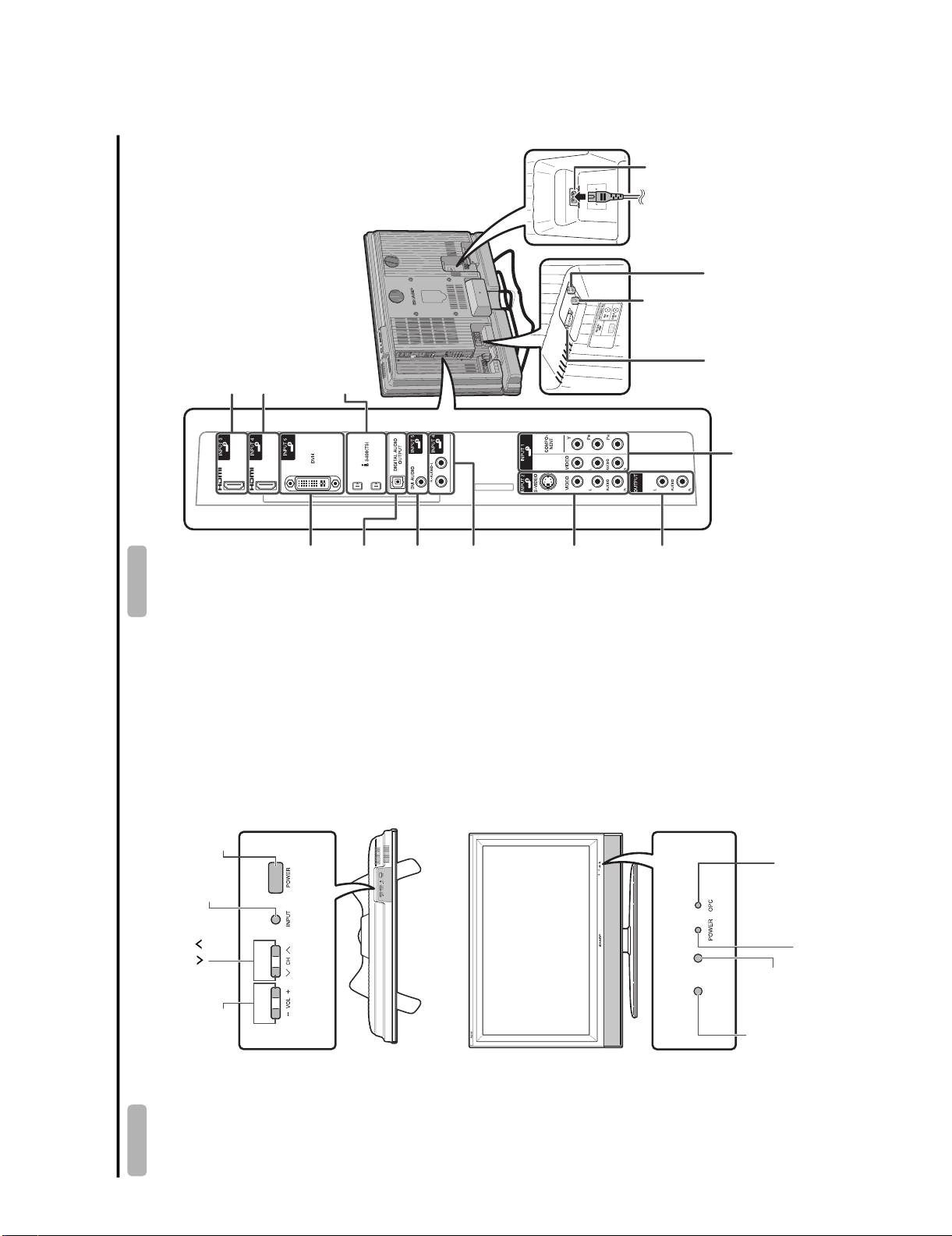

[1] OPERATION MANUAL

HDMI terminal(INPUT3)

HDMI terminal(INPUT4)

i.LINK terminals

LC-37D90U

Service Manual

AC INPUT terminal

AIR IN terminal

CABLE IN terminal

RS-232C terminal

Part names

INPUT button

POWER button

(INPUT5)

DVI terminal

OUTPUT

DIGITAL AUDIO

terminal

terminal

DVI AUDIO

INPUT1 terminals

terminals

(INPUT5)

(INPUT4)

AUDIO input

INPUT2

terminals

terminals

AUDIO OUTPUT

OPC indicator*

TV (Front) TV (Rear)

Part names

Channel buttons

(CH /)

+

-

VOL /)

Volume buttons (

2 – 1

Remote control sensor

OPC sensor*

POWER

indicator**

Page 8

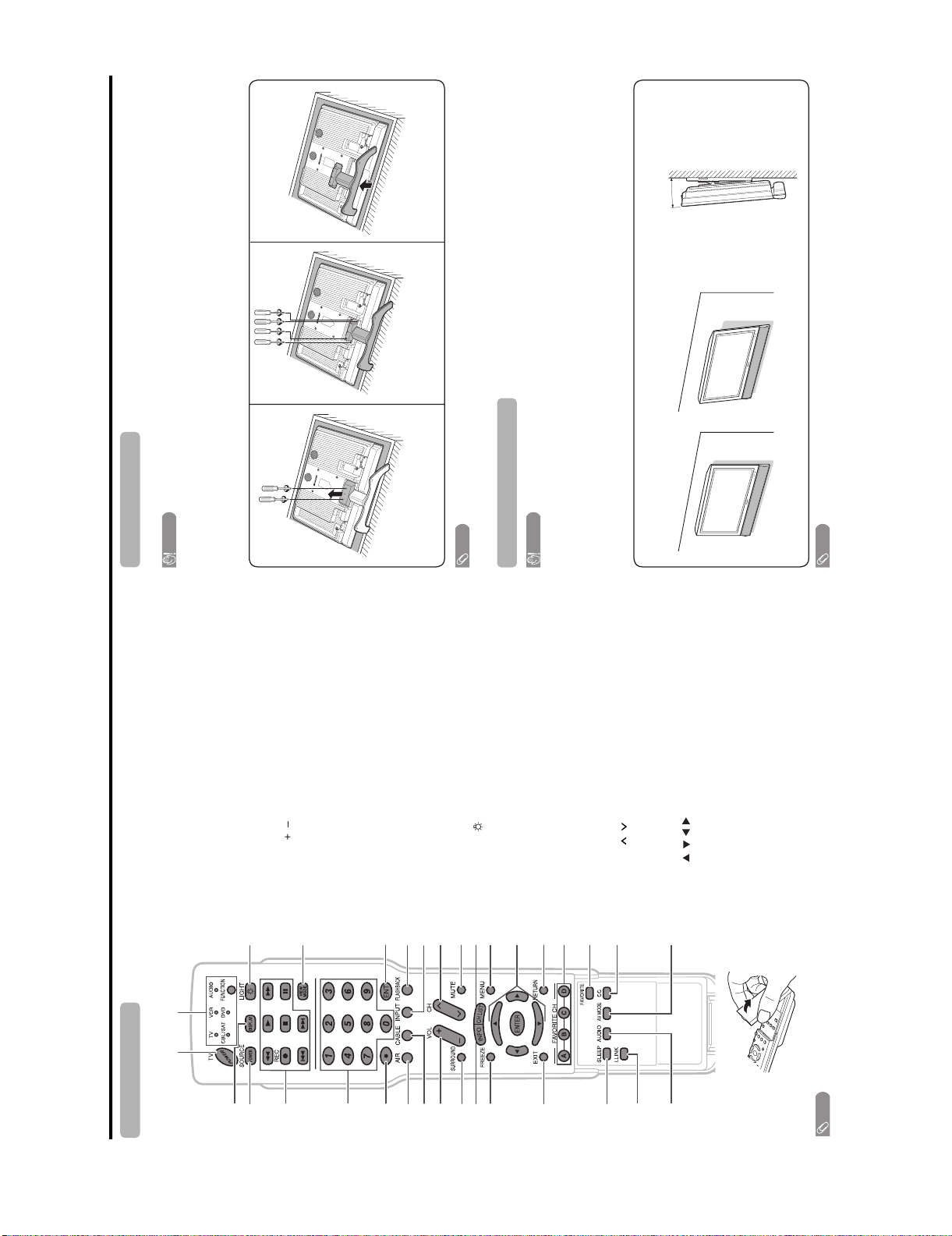

LC-37D90U

0° or 5°

Detach the stand from the TV.

(Hold the stand so it will not drop from

Unfasten the four screws used to

the edge of the base area.)

secure the stand in place.

About setting the TV angle

Angular mounting

3

CAUTION

Appendix

Before detaching (or attaching) stand, unplug the AC cord from the AC INPUT terminal.

standby mode.

1 TV POWER: Switches the TV power on or enters

2 DISPLAY: Displaysthe channel information.

• Do not remove the stand from the TV unless using an optional wall mount bracket to mount it.

3 SOURCE POWER: Turns the power of the external

Before attaching/detaching stand

equipment on and off.

damaged.

• Before performing work make sure to turn off the TV.

• Before performing work spread cushioning over the base area to lay the TV on. This will prevent it from being

the external equipment.

5 0–9:Sets the channel.

4 External equipment operational buttons: Operates

the stand in place.

SAT, VCR,DVD and AUDIO operation. Indicator lights up

17 FUNCTION: Switches the remote control for TV, CBL/

for the current mode.

23

NOTE

* To enter the code registration mode, you need to press

24

• To attach the stand, perform the above steps in reverse order.

time.

FUNCTION and DISPLAY at the same

18 LIGHT : When pressed all buttons on the remote

25

14 SLEEP: Sets the sleep timer.

15 i.LINK: Displays the i.LINK control panel.

20

Unfasten the screws used to secure

multi-channel audio broadcasts.

16 AUDIO: Selects the MTS/SAP or the audio mode during

21

12

normal screen.

6 • (DOT):

7AIR:Receives air signal.

18

8 CABLE: Receives cable signal.

9VOL/:Sets the volume.

10 SURROUND: Selects Surround settings.

19

11 INFO: Displays the program information screen.

13 EXIT: Turns off the menu screen.

12 FREEZE: Sets the still image. Press again to return to

control unit will light. The lighting will turn off if no

Setting the TV on the wall

operations are performed within about 5 seconds. This

button is used for performing operations in low-light

CAUTION

• Installing the TV requires special skill that should only be performed by quali-ed service personnel. Customers

situations.

19 VIEW MODE: Selects the screen size.

20 ENT: Jumps to a channel after selecting with the 0–9

28

27

should not attempt to do the work themselves. SHARP bears no responsibility for improper mounting or

mounting that results in accident or injury.

buttons.

21 FLASHBACK:Returns to the previous channel or

29

Using an optional bracket to mount the TV

external input mode.

• You can ask a quali-ed service professional about using an optional AN-37AG2 bracket to mount the TV to the

2, INPUT 3, INPUT 4, INPUT 5, i.LINK)

22 INPUT: Selects a TV input source. (TV, INPUT1, INPUT

30

wall.

• Carefully read the instructions that come with the bracket before beginning work.

23 CH / : Selects the channel.

31

Hangingonthewall

24 MUTE: Mutes the sound.

25 CH LIST: Displays the channel list screen.

AN-37AG2 wall mount bracket. (See the bracket instructions for details.)

26 MENU: Displays the menu screen.

27 ////ENTER: Selects a desired item on the

screen.

28 RETURN: Returns to the previous menu screen.

29 FAVORITE CH

A, B, C, D: Selects four preset favorite channels in four

different categories.

While watching, you can toggle the selected channels by

pressing A, B, C and D

30 FAVORITE:Registers favorite channels.

Vertical mounting

31 CC: Displays c aptio ns fr om a c losed- capt ion sourc e.

NOTE

STANDARD,MOVIE,GAME, USER,DYNAMIC(Fixed),

32 AV MODE: Selects an audio or video setting. (AVmode:

• Detach the cable clamp on the rear of the TV when using the optional mount bracket.

DYNAMIC.PC mode: STANDARD,MOVIE,GAME,

USER,DYNAMIC (Fixed),DYNAMIC, PC.)

Remote control unit Removing the stand

Part names

117

3

2

4

5

6

7228

9

102611

12

13

14

15

16 32

NOTE

• When using the remote control unit, point it at the TV.

2 – 2

Page 9

Possible Solution

PC

31.5 kHz

31.5 kHz

37.9 kHz

37.5 kHz

35.1 kHz

37.9 kHz

48.1 kHz

46.9kHz

48.4 kHz

56.5 kHz

60.0 kHz

64.0 kHz

47.7kHz

75.0 kHz

34.9 kHz

49.7 kHz

60.2 kHz

640 x 480

720 x 400

VGA

800 x 600SVGA

XGA 1024 x 768

WXGA

SXGA 1280 x 1024

1360 x 768

UXGA* 1600 x 1200

VGA 640 x 480

MAC13"

XGA 1024 x 768MAC19"

SVGA 832 x 624MAC16"

70 Hz

60 Hz

72 Hz

75Hz

56 Hz

60 Hz

72 Hz

75 Hz

60 Hz

70 Hz

75 Hz

60 Hz

60 Hz

60 Hz

67 Hz

75 Hz

75 Hz

OOOOOOOOOOOOO

Error code

setup.

• Check the antenna cable. Check that the antenna is correctly

E202

E203 • Check the broadcast time in the program guide.

Possible Solution

• Displayed when you have selected a device that is not compatible with the TV, or

that does not have DTLA copy protection technology installed.

Check the connection, and re-connect the cable if necessary.

• Displayed when a problem is experienced with a connection using i.LINK cable.

i.LINK connected device. To operate the selected device from the TV, you will first

• Displayed when the device you have selected is already being used by another

have to override control from the other device.

LC-37D90U

VESA StandardResolution

Vertical Frequency

Horizontal Frequency

Appendix

The example of an error

message displayed on a screen

The error message about reception of broadcast

Possible Solution

• Check if you pressed TV POWER on the remote control unit. If the

• No broadcast now.

• Failed to receive broadcast.

indicator on the TV does not light up, press POWER on the TV.

• Is the AC cord disconnected?

• Has the power been turned on?

The cautions about i.LINK

operation. In this case, operate the unit after fi-rst turning on the power of the TV or

unplugging the AC cord and replugging it in after 1 or 2 minutes.

• External influences such as lightning, static electricity, may cause improper

Caution sentence

• Record/Playback may fail on the

, ) aligned?

+

FUNCTION set correctly? Set it to the TV setting position.

•Isthe

• Are batteries inserted with polarity (

selected model.

• Are batteries worn out? (Replace with new batteries.)

• Are you using it under strong or fluorescent lighting?

connection was found. Refer to

• Wrong connection or no i.LINK

Is a fluorescent light illuminated near the remote control sensor?

•

Operation Manual on connection.

• The selected model is disabled to

• Is the image position correct?

• Are screen mode adjustments such as picture size made correctly?

record/play. Check that no other

model is used.

• Adjust the picture tone.

• Is the room too bright? The picture may look dark in a room that is too bright.

• Check the input signal setting.

PC compatibility chart

• Is the sleep timer set?

PC/MAC

• Check the power control settings.

• The unit's internal temperature has increased.

Remove any objects blocking vent or clean.

• Is connection to other components correct?

• Is correct input signal source selected after connection?

• Is the correct input selected?

• Is picture adjustment correct?

• Is "On" selected in "Audio Only"?

• Is a non-compatible signal being input?

• Is the volume too low?

• Is "Variable" selected in "Output Select"?

Apple and Macintosh are registered trademarks of Apple

Computer, Inc.

DDC is a registered trademark of Video Electronics

Standards Association.

Power Management is a registered trademark of Sun

Microsystems, Inc.

VGA and XGA are registered trademarks of International

*Digital input only.

++

Business Machines Co., Inc.

Problem

Troubleshooting Troubleshooting-Digital broadcasting

Appendix

• No power

• Unit cannot be operated.

operate.

• Remote control unit does not

screen.

• Picture is cut off/with sidebar

misalignment

• Strange color, light color, or color

• Power is suddenly turned off.

2 – 3

• No picture

• No sound

__

When the unit is used in a low temperature space (e.g. room, office), the picture may leave trails or appear slightly delayed.

This is not a malfunction, and the unit will recover when the temperature returns to normal.•Do not leave the unit in a hot or cold location. Also, do not leave the unit in a location exposed to direct sunlight or near a

heater, as this may cause the cabinet to deform and the Liquid Crystal panel to malfunction.

Cautions regarding use in high and low temperature environments

Storage temperature: 4°F to 140°F ( 20°C to 60°C)

•

Page 10

LC-37D90U

CONTROL CONTENTS

Effective only when the StandbyMode is set to "Mode1".

It input-switches by the toggle.(It is the same as an input change key)

It input-switches to TV. (Achannel remains as it is. (Last memory))

It input-switches to INPUT1~INPUT5.

It input-switches to i.LINK.

An input change is alsoincluded.

Although it can choose now,it is toggle operation in inside.

Only available when DVI ANALOGis being input.

Only available when DVI ANALOGis being input.

Although it can choose now,it is toggle operation in inside.

An input change is includedif it is not TV display.

In Air, 2–69ch is effective.

In Cable, 1–135ch is effective.

If it is not TVdisplay, it will input-switch to TV. (same function as CH )

If it is not TVdisplay, it will input-switch to TV. (same function as CH )

DIGITAL Cable (One-Part numbers, 5-digit,more than 10,000)

Toggle operation of a closedcaption.

AIR CABLE AIR(Toggle)ACSL 0_ __

_

+

DIGITAL Air (Two-Part numbers, 2-digitplus 2-digit)(0101-9999)

DIGITAL Cable (Two-Part numbers, 3-digitplus 3-digit)

DIGITAL Cable (Two-Part numbers, 3-digitplus 3-digit)

Front half of DIGITAL CABLECHANNEL NO. (Designate major channel)

Rear half of DIGITAL CABLECHANNEL NO. (Designate minor channel)

DIGITAL Cable (One-Part numbers, 5-digit,less than 10,000)

Appendix

Response code format

OK

Normal response

Return code (0DH)

ERR

Problem response (communication error or incorrect command)

Return code (0DH)

(Toggle)

Input terminal number (1–5)

Power Off

Power On1___

___

_

_______________

_______________

*

x

x

0

PARAMETER

ITGD

ITVD

IAVD

POWR

TV

INPUT1-5

CONTROL ITEM COMMAND

INPUT SELECTION A TOGGLE

POWER SETTING It shifts to standby.

Command table

• Commands not indicated here are not guaranteed to operate.

AUTO

VIDEO

COMPONENT

DIGITAL

ANALOG

(Toggle)

STANDARD

INP5

INPUT 5

MOVIE

12345

0

AVMD

AVMODE SELECTION

AUTO

___________

05612

INP1

LINKx___

i.LINK

INPUT 1

INPUT SELECTION B

GAME

USER

DYNAMIC (Fixed)

DYNAMIC

_

_

_

6

Volume(0–60)

AVmode. ( 10)

PC mode. (0–180)

PC

_____

_

_

*****

*

_

*****

*

___

*

*****

7

VOLM

HPOS

H-POSITIONH-POSITION

VOLUME

POSITION

AVmode. ( 20)

PC mode. (0–100)

Only PC mode. (0–180)

*

*

S

VPO

CLCK

V-POSITION

CLOCK

Only PC mode. (0–40)

(Toggle) [AV]

Side Bar [AV]

S.Stretch [AV]

Zoom [AV]

Stretch [AV]

_________

_________

_________

012345678

E

PHS

WIDE

PHASE

VIEWMODE

Normal [PC]

Zoom [PC]

(Toggle)

Stretch [PC]

Dot by Dot [AV] [PC]

On

Off

OFF

OFF TIMER – 30 MIN.

Full Screen [AV]9___

(Toggle)OnOff

___

___

___

1

MUT E0

The channel number of TV

(Toggle)

_

_

_

_

_

_

_

0

2

Ax___

U

ACS

ACH

(1–135)

OFF TIMER – 60 MIN.

OFF TIMER – 90 MIN.

OFF TIMER – 120 MIN.4___

_

_

_

_

_

*

___

_

_

*

___

_

_

*

112

2

3

0

M

OFT

H

DCC

DIRECT

(ANALOG)

CHANNEL

P** **

DA2

DIRECT

(0-999)

U** *_

DC2

(DIGITAL)

CHANNEL

The channel number of TV 1

The channel number of TV 1

(0-6383)

_

_

_

x

1****

DC1

CHUPCHDW

CH UP

_

_

_

x

CH DOWN

(Toggle)

AIR1___

CABLE2___

_

_

_

x

CLCP

(0-999)

(0-9999)

L***_

DC2

DC1 0 * * * *

X

NOTE

Surround

SLEEP TIMER

MUTE

AUDIO SELECTION

CHANNEL

Air/Cable SELECT

CC

• If an underbar (_) appears in the parameter column, enter a space.

• If an asterisk (*) appears, enter a value in the range indicated in brackets under CONTROL CONTENTS.

• As long as that from which the parameter ( ) in the table is a numerical value, it may write anything.

RS-232C port specifications

PC Control of the TV

Appendix

• When a program is set, the TV can be controlled from the PC using the RS-232C terminal. The input signal

(PC/AV) can be selected, the volume can be adjusted and various other adjustments and settings can be made,

enabling automatic programmed playing.

NOTE

connections.

• Attach an RS-232C cable cross-type (commercially available) to the supplied Din/D-Sub RS-232C for the

• This operation system should be used by a person who is accustomed to using computers.

Communication conditions

Set the RS-232C communication settings on the PC to match the TV's communication conditions.

The TV's communication settings are as follows:

9,600 bps

Baud rate:

8bits

Data length:

None

Parity bit:

1bit

Stop bit:

None

Flow control:

Communication procedure

Send the control commands from the PC via the RS-232C connector.

The TV operates according to the received command and sends a response message to the PC.

2 – 4

Do not send multiple commands at the same time. Wait until the PC receives the OK response before sending the

next command.

+

Eight ASCII codes CR

Command format

Command 4-digits: Command. The text of four characters.

Parameter 4-digits: Parameter 0 – 9, x, blank, ?

C1 C2 C3 C4 P1 P2 P3 P4

Command 4-digits Parameter 4-digits Return code

Input the parameter values, aligning left, and fill with blank(s) for the remainder. (Be sure that 4 values are input for

the parameter.)

When the input parameter is not within an adjustable range, "ERR" returns. (Refer to "Response code format".)

Parameter

0

Any numerical value can replace the "x" on the table.

30

0055

100

0009

_

?

When "?" is input for some commands, the present setting value responds.

????

Page 11

LC-37D90U

Setup

Picture

Picture

Menu items for TV/INPUT 1/INPUT 2 Menu items for HDMI/DVI

Basic adjustment settings

OPC

Backlight

OPC

Backlight

Contrast

Brightness

Color

Contrast

Brightness

Color

Tint

Sharpness

Advanced

Tint

Sharpness

Advanced

Color Temp.

Black

Monochrome

Color Temp.

Black

3D-Y/C

Audio

Film Mode

Range of OPC

Monochrome

Film Mode

Range of OPC

Audio

Treble

Bass

Treble

Balance

Surround

Bass

Balance

Power Control

Surround

Setup

Input Skip

Input Signal

Auto Sync.

Input Label

Fine Sync.

Position

Picture Flip

No Signal Off

No Operation Off

Power Control

EZ Setup

No Signal Off

No Operation Off

CH Setup

Standby Mode

Antenna Setup-DIGITAL

Input Skip

Input Label

Parental CTRL

Position

Language

Reset

Picture Flip

Standby Mode

Language

Reset

Option

Option

Audio Only

Digital Noise Reduction

Input Select

Audio Only

HDMI Setup

Output Select

Quick Shoot

Digital Noise Reduction

Input Select

Output Select

Quick Shoot

Digital Setup

Color System

Caption Setup

Program Title Display

Favorite CH

i.LINK Setup

Digital Setup

Audio Setup

i.LINK Setup

2 – 5

Page 12

LC-37D90U

LC-37D90U

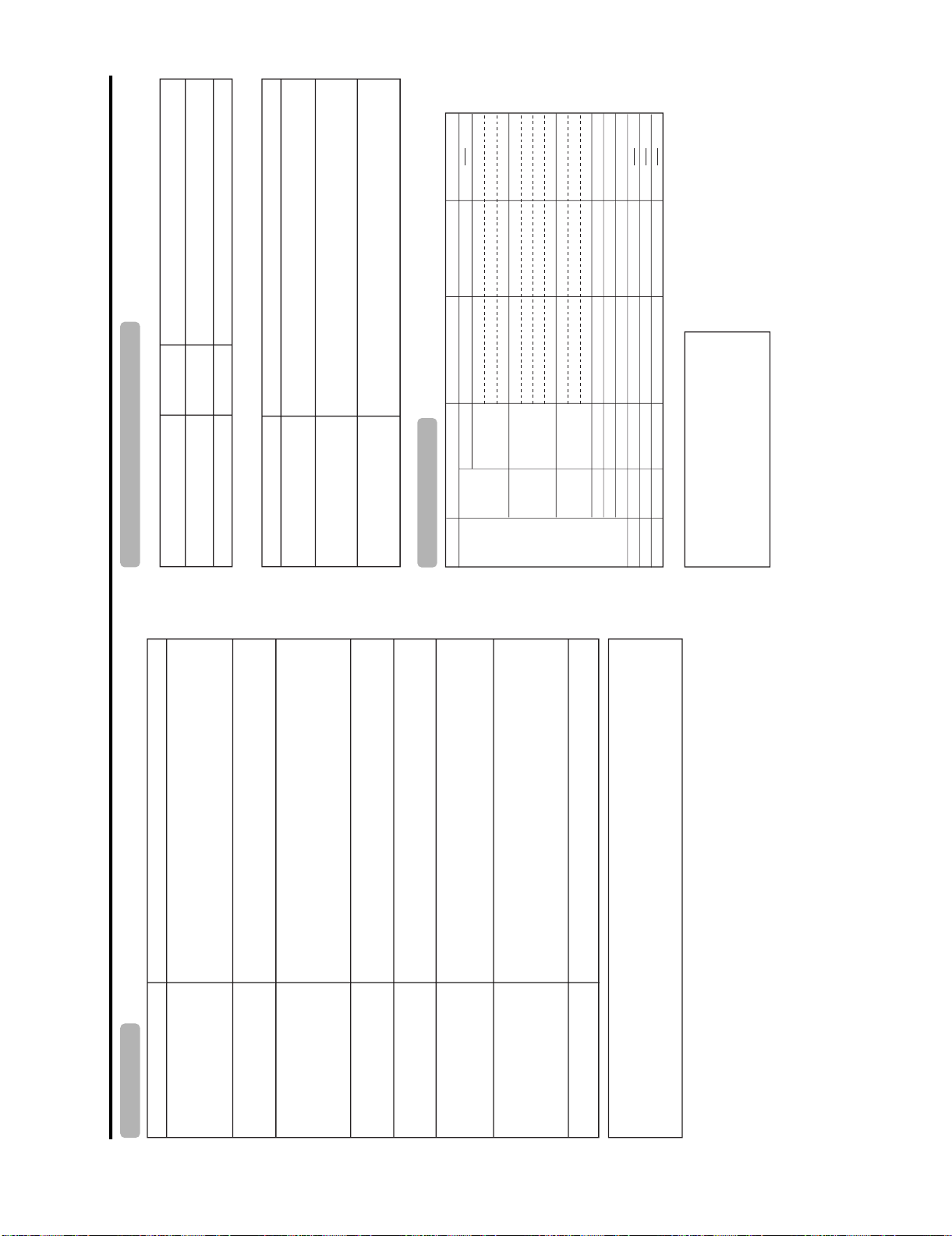

CHAPTER 3. DIMENSIONS

[1] DIMENSIONS

3225/64(

27

26

36

822.6)

/64(671)

5

/8(

930)

Service Manual

Unit: inch/(mm)

4

(

104)

13

3

32

/

4

(

122)

16

/

729)

(

64

/

45

28

200)

(

8

/

7

7

664)

(

64

/

9

26

63)

(

64

/

31

2

100)

(

64

/

61

3

585)

(

32

/

1

23

77/8(

200)

463.8)

(

64

/

17

18

439)

(

32

/

9

17

12

1

/16(

306)

3 – 1

Page 13

LC-37D90U

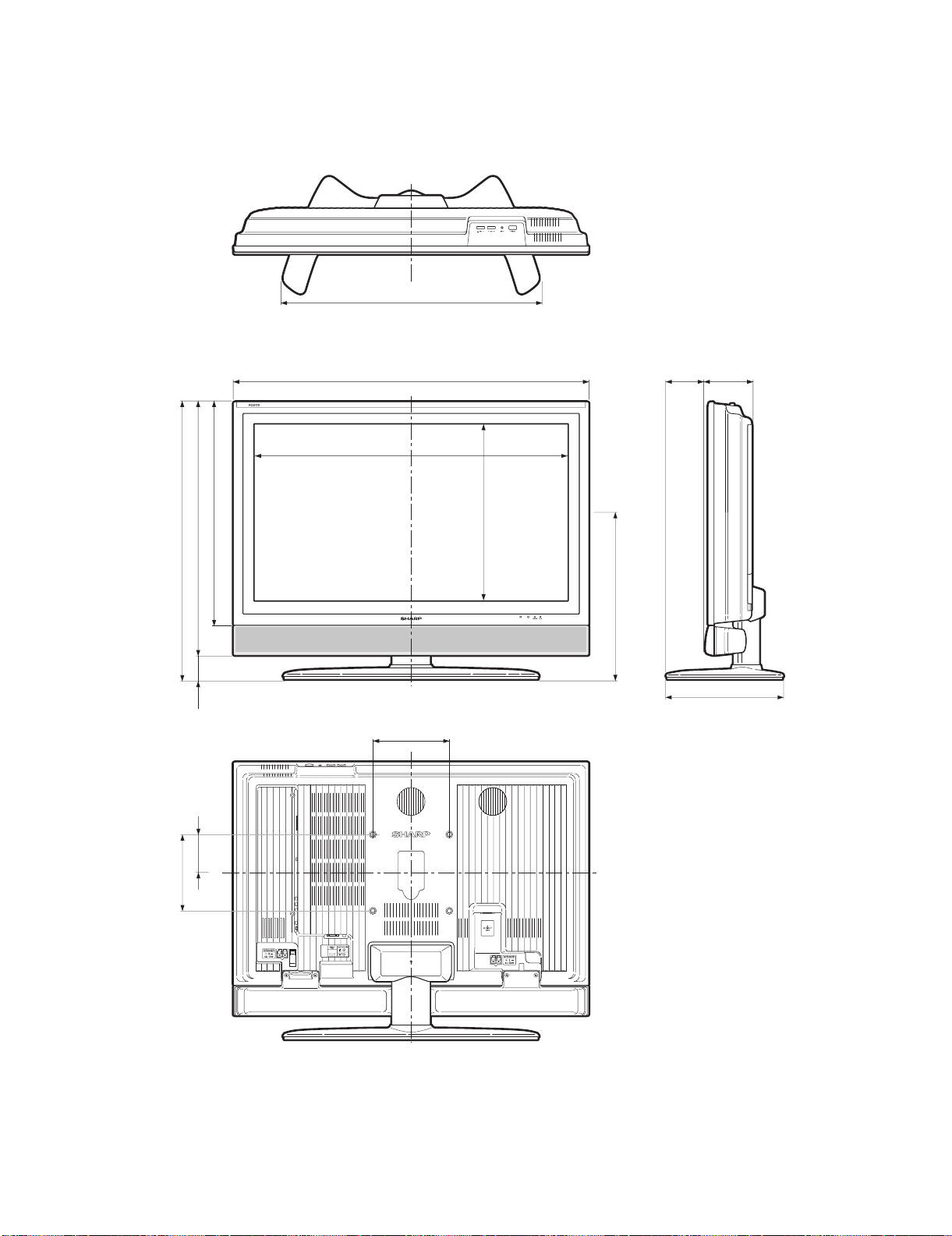

CHAPTER 4. REMOVING OF MAJOR PARTS

Service Manual

[1] REMOVING OF MAJOR PARTS

1. Detach the SD Card Cover.

2. Remove the 2 lock screws and detach the Stand Cover.

3. Remove the 4 lock screws and detach the Stand.

4. Remove the SP Wire (L)(R). Remove the 4 lock screws and detach the Speaker Box.

5. Remove the 13 lock screws, 6 lock screws, 4 lock screws and detach the Rear Cabinet.

Front Cabinet

5

1

SD Card Cover

LC-37D90U

5

SP Wire (R)

4

5

Rear Cabinet

3

SP Wire (L)

2

Stand Cover

Stand

4

Speaker Box

4 – 1

Page 14

LC-37D90U

6. Remove the Stand Bottom Cover.

7. Disconnect the [FB] connector. Remove the 2 lock screws and detach the Fan Angle C Ass’y.

8. Remove the 4 lock screws and detach the SUS Angle (L)(R).

9. Remove the 5 lock screws and detach the Stand Fixing Angle.

10.Remove the 6 lock screws and detach the Main Shield.

10

Main Shield

SUS Angle (R)

8

7

SUS Angle (L)

Fan Angle C Ass'y

8

11.Disconnect all the connectors from all the PWBs.

Stand Fixing Angle

Stand Bottom Cover

9

4 – 2

Page 15

12.Remove the 3 lock screws and detach the Fan Angle L Ass’y.

13.Remove the 2 lock screws and detach the SP (L) PWB.

14.Remove the 3 lock screws and detach the SP Fixing Angle (L).

15.Remove the 2 lock screws and detach the SP (R) PWB.

16.Remove the 3 lock screws and detach the SP Fixing Angle (R).

17.Remove the 2 lock screws and detach the R/C, LED PWB.

18.Remove the 2 lock screws and detach the Top Control Cover.

19.Remove the 3 lock screws and detach the KEY PWB.

20.Remove the 4 lock screws and detach the Try Chassis.

18

Top Control Cover

KEY PWB

19

LC-37D90U

20

Try Chassis

12

Fan Angle L Ass'y

17

R/C, LED PWB

SP Fixing Angle (R)

16

SP (R) PWB

15

16

14

SP (L) PWB

SP Fixing Angle (L)

14

13

4 – 3

Page 16

LC-37D90U

21.Remove the 9 lock screws and detach the Jack Angle Long.

22.Remove the 6 lock screws and detach the POWER PWB.

23.Remove the 6 lock screws and detach the IF PWB.

24.Remove the 5 lock screws and detach the MAIN PWB Radiator and MAIN PWB.

24

MAIN PWB Radiator

MAIN PWB

21

21

22

POWER PWB

21

Jack Angle Long

23

IF PWB

25.Remove the 2 lock screws from the Panel Fixing Angle (C), the 2 lock screws from the Panel Fixing Angle (L)(R) and detach the LCD Panel Ass'y.

26.Remove the 3 lock screws and detach the Panel Fixing Angle (C).

27.Remove the 4 lock screws and detach the Panel Fixing Angle (L)(R).

Panel Fixing Angle (C)

27

Panel Fixing

Angle (R)

25

25

26

27

25

Panel Fixing

Angle (L)

4 – 4

Page 17

LC-37D90U

LC-37D90U

CHAPTER 5. ADJUSTMENT

Service Manual

[1] ADJUSTMENT PROCEDURE

The adjustment values are set to the optimum conditions at the factory before shipping. If a value should become improper or an adjustment is

required due to part replacement, make an adjustment according to the following procedure.

1. After replacement of any PWB unit and/or IC for repair, please note the following.

When replacing the following units, make sure to prepare the new units loaded with updated software.

MAIN Unit: DKEYDD743FM21

2. Upgrading of each microprocessor software

CAUTION: Never “POWER OFF” the unit when software upgrade is ongoing.

Otherwise the system may be damaged beyond recovery.

2.1. Software version upgrade

The model employs the following software.

•Main software

• Monitor microprocessor software

The main software and the monitor microprocessor software can be upgraded by using a general-purpose SD memory card.

The followings are the procedures for upgrading, explained separately for each of the main software, the monitor microprocessor software.

2.2. Main software version upgrade

2.2.1 Get ready before you start

• SD memory card of 32MB or higher capacity

• PC running on Windows 98/98SE/ME/2000/XP operating system

• SD memory card reader/writer with USB connectivity

• SD memory card formatting software

(Downloadable at http://panasonic.jp/support/audio/sd/download/sd_formatter_e.html)

2.2.2 Preparations

To upgrade the main software, it is necessary to get ready the SD card for version upgrade before you start. Follow the steps below and create the SD

card for version upgrade.

1. Insert the SD card into the SD card reader/writer. Start the SD card formatting software. Click [Format]. (When you have the drive options, select

the drive where the SD card is inserted before you proceed.)

5 – 1

Page 18

LC-37D90U

2. When the formatting is over, the following window appears. Click [OK].

3. Click [Exit] to finish the formatting.

NOTE: When you are done, take out the SD card once to make sure it is finished, and then insert it again.

4. Copy the binary image file OLYMAxxx.SDC (named temporarily) for version upgrade to the root directory (folder) of the SD card drive.

NOTE: In the SD card drive, do not store other folders or unrelated files, or more than one binary image files for version upgrade.

Now the SD card for version upgrade is ready.

2.2.3 Upgrading the software

1. Turn off the AC power (Unplug the AC power cord).

2. Insert the upgrading SD card (prepared as instructed above) into the service slot.

NOTE: Be careful not to insert the SD card in the wrong way. Otherwise the card may come into the set and fail to come out.

3. Turn on the AC power (Plug in the AC power cord).

4. A couple to dozen seconds after the set starts, the upgrade screen below shows up.

5 – 2

Page 19

LC-37D90U

5. If any of the procedures fails, the following upgrade failure screen shows up. For the failing procedure, the “NG” marking turns red.

NOTE: In such case, try to upgrade the software again. If it still fails, the hardware may be in trouble.

6. When all the procedures are complete, the following upgrade success screen shows up. The new software version can be confirmed on screen.

The version number appears when each item has been successfully upgraded. Finally the main version number appears on screen.

7. Turn off the AC power (Unplug the AC power cord). Take out the upgrading SD card.

8. Now the software has been upgraded.

NOTE: Then get the set started and call the process adjustment screen 1/27 to check the main software version.

CAUTION: 1) Do not take out and put in the SD memory card during formatting.

2) With the SD formatted, all the data stored on the medium will be deleted.

3) Do not start the SD formatting with the memory card’s WRITE PROTECT switch still on.

4) If the SD memory card format software does not recognize the SD memory card, take out and put in the SD memory card again, and

click the “UPDATE” button.

5) After checking the performance, use the set under its interface environment.

6) The SD formatting is impossible on drives that are not recognized “REMOVABLE”.

2.3. Upgrading the monitor microprocessor software

2.3.1 Kit

Have the above “Upgrading the main software” kit or equivalent at hand.

2.3.2 Preparations

As discussed in “Upgrading the main software” earlier, create the SD card for upgrading the monitor microprocessor software. For this SD card, use

the monitor microprocessor upgrading binary image file.

2.3.3 Upgrading procedure

To follow the monitor microprocessor software upgrading, the monitor screen upgrade progress indicator and the flashing power LED indicator can be

used.

1. Turn off the AC power (Unplug the AC power cord).

2. Insert the upgrading SD card (prepared as instructed above) into the service slot at the back of the set. Insert the SD card with its logo-printed face

upward (visible). Be careful not to insert the SD card in the wrong way. Otherwise the card may come into the set and fail to come out.

3. Turn on the AC power (Plug in the AC power cord).

CAUTION: Now the monitor microprocessor software starts getting upgraded. Be very careful not to turn off the power while the software is being

upgraded. Otherwise the software will fail to upgrade itself and the set will fail to get started.

5 – 3

Page 20

LC-37D90U

4. A couple to dozen seconds after the set starts, the upgrade screen below shows up. The upgrade progress is indicated on screen. The power LED

indicator goes out once and then starts flashing in blue. (It takes 2-3 minutes to get the monitor microprocessor software upgraded.)

5. If the procedure fails, the following upgrade failure screen shows up and the “NG” marking turns red. The power LED indicator fails to start flashing

in blue. Even if the usual screen reappears in several seconds, do the procedure from Step “1” again.

NOTE: In case of failure, try to upgrade the software again. If it still fails, the hardware may be in trouble.

6. When the procedure is complete, the following upgrade success screen shows up. The new software version can be confirmed on screen. The

upgrade success can also be confirmed when the power LED indicator and the OPC LED indicator start flashing alternately in blue and green,

respectively. Double-check the upgrading and turn off the AC power (Unplug the AC power cord). Take out the upgrading SD card. Now the software has been upgraded.

Finally get the set started and call the process adjustment screen 1/27 to check the monitor microprocessor software version.

5 – 4

Page 21

LC-37D90U

3. Entering and exiting the adjustment process mode

1) Before entering the adjustment process mode, the AV position RESET in the video adjustment menu.

2) While holding down the “VOL (–)” and "INPUT" keys at a time, plug in the AC cord of the main unit to turn on the power.

The letter “<K>” appears on the screen.

3) Next, hold down the “VOL (–)” and “CH ( )” keys at a time.

(The "VOL (–)" and "CH ( )" keys should be pressed and held until the display appears.)

Multiple lines of blue characters appearing on the display indicate that the unit is now in the adjustment process mode.

When you fail to enter the adjustment process mode (the display is the same as normal startup), retry the procedure.

4) To exit the adjustment process mode after the adjustment is done, unplug the AC cord from the outlet to make a forced shutdown. (When the

power was turned off with the remote controller, once unplug the AC cord and plug it again. In this case, wait 10 seconds or so before plugging.)

CAUTION: Use due care in handling the information described here lest your users should know how to enter the adjustment process mode. If the

4. Remote controller key operation and description of display in adjustment process mode

1) Key operation

Remote controller key Main unit key Function

CH ( / ) CH ( / )

VOL (+/–) VOL (+/–) Changing a selected item setting (+1/ –1)

Cursor (UP/DOWN) ————— Turing a page (PREVIOUS/NEXT)

Cursor (LEFT/RIGHT) ————— Changing a selected line setting (+10/ –10)

INPUT ————— Input switching (toggle switching)

ENTER ————— Executing a function

2) Description of display

settings are tampered in this mode, unrecoverable system damage may result.

Moving an item (line) by one (UP/DOWN)

(TUNER→INPUT1→INPUT2→INPUT3→INPUT4→INPUT5)

*Input mode is switched automatically when relevant adjustment is started so far as the necessary input signal is available.

(1) Current page/ (5) (6) LCD Panel size/Speaker type

Total pages

1/27 [INFO] INPUT5 AUTO USA 37_UNDER

MAIN Version 0.95 ( U 2006/02/02 1)

BOOT Version OLYM0.92

Monitor Version 0.88

EQ DATA CHECKSUM ROM (8) Parameters

TEMPAERATURE 7B

LAMP ERROR 0

NORMAL STANDBY CAUSE

ERROR STANDBY CAUSE 1) 0 2) 0 3) 0

(2) Current page title

(3) Current selected input

(4) Current color system

0

00H 00M 00H 00M 00H 00M

4) 0 5) 0

00H 00M 00H 00M

Destination

(7) Adjustment

process menu

header

5 – 5

Page 22

LC-37D90U

5. List of adjustment process mode menu

The character string in brackets [ ] will appear as a page title in the adjustment process menu header.

Page Line Item Description Remarks (adjustment detail, etc.)

1 [INFO]

1 MAIN Version Main software version

2BOOT Version

3 Monitor Version Monitor software version

4 EQ DATA CHECKSUM Audio data checksum

5 TEMPERATURE CPU temperature

6 LAMP ERROR Number of termination due to lamp error

7 NORMAL STANDBY CAUSE Refer to *1 under the list for details

8 ERROR STANDBY CAUSE Refer to *2 under the list for details

2 [INIT]

1 INDUSTRY INIT (Cause)

2 INDUSTRY INIT Initialization to factory settings .

3 HOTELMODE Hotel mode

4 Center Acutime Accumulated main operation time

5 RESET Reset

6 BacklightAcutime Accumulated monitor operation time

7 RESET Reset

8 LAMP ERROR RESET Reset LAMP ERROR

9 VIC XPOS X-coordinate setting for VIC READ

10 VIC YPOS Y-coordinate setting for VIC READ

11 VIC COLOR Collected color data setting for VIC READ

12 VIC SIGNAL TYPE Signal type setting for VIC READ

13 VIC READ Picture level acquisition function Level appears in green on the upper right.

3 [N358MAIN]

1 N358 ALL ADJ CVBS and TUNER signal level adjustment

2 N358 MAIN ADJ CVBS signal level adjustment

3 TUNER DAC ADJ TUNER signal level adjustment

4 N358 MAIN CONTRAST CVBS and TUNER contrast adjustment values

5 TUNER A DAC TUNER adjustment value

4 [TUNER TEST]

1 TUNER VCHIP TEST(69ch) Tuning test and VCHIP test (69 ch)

2 TUNER VCHIP TEST(7ch) Tuning test and VCHIP test (7 ch)

3 TUNER VCHIP TEST(10ch) Tuning test and VCHIP test (10 ch)

4 TUNER VCHIP TEST(15ch) Tuning test and VCHIP test (15 ch)

5 [COMP15KMAIN]

1 COMP15K MAIN ADJ Component 15K picture level adjustment (main)

2 COMP15K MAIN CONTRAST Contrast adjustment value

3 COMP15K MAIN Cb GAIN Cb GAIN adjustment value

4 COMP15K MAIN Cr GAIN Cr GAIN adjustment value

5 COMP15K Y OFFSET Y OFFSET adjustment value

6 COMP15K Cb GAIN Cb OFFSET adjustment value

7 COMP15K Cr GAIN Cr OFFSET adjustment value

6 [HDTV]

1 HDTV ADJ Component Hi-Vision picture level adjustment

2 CONTRAST Contrast adjustment value

3 Cb GAIN Cb GAIN adjustment value

4 Cr GAIN Cr GAIN adjustment value

5 HDTV Y OFFSET Y OFFSET adjustment value

6 HDTV Cb OFFSET Cb OFFSET adjustment value

7 HDTV Cr OFFSET Cr OFFSET adjustment value

7 [DVI ANALOG]

1 DVI ANALOG ADJ DVI ANALOG adjustment

2 R CUTOFF R CUTOFF adjustment value

3 G CUTOFF G CUTOFF adjustment value

4 B CUTOFF B CUTOFF adjustment value

5 R DRIVE R DRIVE adjustment value

6 G DRIVE G DRIVE adjustment value

7 B DRIVE B DRIVE adjustment value

5 – 6

Page 23

LC-37D90U

Page Line Item Description Remarks (adjustment detail, etc.)

8 [M GAMMA IN]

1 MONITOR GAMMA IN 1 Standard value 1(LEV60050) Adjustment gradation setting.

2 MONITOR GAMMA IN 2 Standard value 2(LEV60066)

3 MONITOR GAMMA IN 3 Standard value 3(LEV60116)

4 MONITOR GAMMA IN 4 Standard value 4(LEV60144)

5 MONITOR GAMMA IN 5 Standard value 5(LEV60200)

6 MONITOR GAMMA IN 6 Standard value 6(LEV60236)

7 GAMMA WRITE WB adjustment data writing

8 GAMMA RESET WB adjustment data reading

9 [M GAMMA R1]

1 MONITOR GAMMA R 1 WB adjustment Point 1, R adjustment value Parameter for six-point adjustment

2 MONITOR GAMMA G 1 WB adjustment Point 1, G adjustment value

3 MONITOR GAMMA B 1 WB adjustment Point 1, B adjustment value

4 MONITOR GAMMA R 2 WB adjustment Point 2, R adjustment value

5 MONITOR GAMMA G 2 WB adjustment Point 2, G adjustment value

6 MONITOR GAMMA B 2 WB adjustment Point 2, B adjustment value

7 MONITOR GAMMA R 3 WB adjustment Point 3, R adjustment value

8 MONITOR GAMMA G 3 WB adjustment Point 3, G adjustment value

9 MONITOR GAMMA B 3 WB adjustment Point 3, B adjustment value

10 GAMMA WRITE WB adjustment data writing

11 GAMMA RESET WB adjustment data reading

10 [M GAMMA R4]

1 MONITOR GAMMA R 4 WB adjustment Point 4, R adjustment value Parameter for six-point adjustment

2 MONITOR GAMMA G 4 WB adjustment Point 4, G adjustment value

3 MONITOR GAMMA B 4 WB adjustment Point 4, B adjustment value

4 MONITOR GAMMA R 5 WB adjustment Point 5, R adjustment value

5 MONITOR GAMMA G 5 WB adjustment Point 5, G adjustment value

6 MONITOR GAMMA B 5 WB adjustment Point 5, B adjustment value

7 MONITOR GAMMA R 6 WB adjustment Point 6, R adjustment value

8 MONITOR GAMMA G 6 WB adjustment Point 6, G adjustment value

9 MONITOR GAMMA B 6 WB adjustment Point 6, B adjustment value

10 GAMMA WRITE WB adjustment data writing

11 GAMMA RESET WB adjustment data reading

11 [SOUND 1]

1 AUDIO SELECT

2 INPUT_TRIM_SP

3 INPUT_TRIM_HP

4 CLIPPER_LEVEL

5ANGLE

6 MASTER_VOLUME

7 SCART_PRESCALE

8 FM_AM_PRESCALE

9 I2S1_PRESCALE

10 SCART1_VOLUME

11 SCART2_VOLUME

12 [SOUND 2]

1 AIN1_ADC_VOLUME

2 AIN2_ADC_VOLUME

3 AIN3_ADC_VOLUME

4 AIN4_ADC_VOLUME

5 AIN5_ADC_VOLUME

6 AIN6_ADC_VOLUME

5 – 7

Page 24

LC-37D90U

Page Line Item Description Remarks (adjustment detail, etc.)

13 [SOUND 3]

1 SUB_VOLUME_SURROUND

2SUB_VOLUME_FLAT

3 SUB_VOLUME_EQ

4 SUB_VOLUME_HP

5 SUB_VOLUME_HP_CENTERSP

6 SUB_VOLUME_CENTERSP_EQ

7 SUB_VOLUME_CENTERSP_FLAT

8 BBE_HF_ADJUST

9 BBE_LEVEL

10 BBE_MACH3_F0

11 BBE_MACH3_Q

12 BBE_MACH3_GAIN

14 [SOUND 4]

1EQ_MODE

2 PEQ1_F0

3 PEQ1_Q

4 PEQ1_GAIN

5 PEQ2_F0

6 PEQ2_Q

7 PEQ2_GAIN

8 PEQ3_F0

9 PEQ3_Q

10 PEQ3_GAIN

11 PEQ4_F0

12 PEQ4_Q

13 PEQ4_GAIN

15 [SOUND 5]

1 PEQ5_F0

2 PEQ5_Q

3 PEQ5_GAIN

4 EALA_GAIN

16 [M OPC1]

1 BRIGHTNESS DA0

2 BRIGHTNESS DA1

3 BRIGHTNESS DA2

4 BRIGHTNESS DA3

5 BRIGHTNESS DA4

6 BRIGHTNESS DA5

7 BRIGHTNESS DA6

8 BRIGHTNESS DA7

9 BRIGHTNESS DA8

10 BRIGHTNESS DA9

11 BRIGHTNESS DA10

12 BRIGHTNESS DA11

17 [M OPC2]

1 BRIGHTNESS DA12

2 BRIGHTNESS DA13

3 BRIGHTNESS DA14

4 BRIGHTNESS DA15

5 BRIGHTNESS DA16

6 BRIGHTNESS DA17

7 BRIGHTNESS DA18

8 BRIGHTNESS DA19

9 BRIGHTNESS DA20

10 BRIGHTNESS DA21

11 BRIGHTNESS DA22

5 – 8

Page 25

LC-37D90U

Page Line Item Description Remarks (adjustment detail, etc.)

18 [M OPC3]

1 BRIGHTNESS DA23

2 BRIGHTNESS DA24

3 BRIGHTNESS DA25

4 BRIGHTNESS DA26

5 BRIGHTNESS DA27

6 BRIGHTNESS DA28

7 BRIGHTNESS DA29

8 BRIGHTNESS DA30

9 BRIGHTNESS DA31

10 BRIGHTNESS DA32

19 [M ADL1]

1 OPC33 ADLEVEL 0

2 OPC33 ADLEVEL 1

3 OPC33 ADLEVEL 2

4 OPC33 ADLEVEL 3

5 OPC33 ADLEVEL 4

6 OPC33 ADLEVEL 5

7 OPC33 ADLEVEL 6

8 OPC33 ADLEVEL 7

9 OPC33 ADLEVEL 8

10 OPC33 ADLEVEL 9

11 OPC33 ADLEVEL 10

12 OPC33 ADLEVEL 11

20 [M ADL2]

1 OPC33 ADLEVEL 12

2 OPC33 ADLEVEL 13

3 OPC33 ADLEVEL 14

4 OPC33 ADLEVEL 15

5 OPC33 ADLEVEL 16

6 OPC33 ADLEVEL 17

7 OPC33 ADLEVEL 18

8 OPC33 ADLEVEL 19

9 OPC33 ADLEVEL 20

10 OPC33 ADLEVEL 21

11 OPC33 ADLEVEL 22

21 [M ADL3]

1 OPC33 ADLEVEL 23

2 OPC33 ADLEVEL 24

3 OPC33 ADLEVEL 25

4 OPC33 ADLEVEL 26

5 OPC33 ADLEVEL 27

6 OPC33 ADLEVEL 28

7 OPC33 ADLEVEL 29

8 OPC33 ADLEVEL 30

9 OPC33 ADLEVEL 31

22 [M V6THE]

1V6 OS THERMO 1

2V6 OS THERMO 2

3V6 OS THERMO 3

4V6 OS THERMO 4

5V6 OS THERMO 5

6V6 OS THERMO 6

7V6 OS THERMO 7

23 [M V5THE]

1V5 OS THERMO 1

2V5 OS THERMO 2

3V5 OS THERMO 3

4V5 OS THERMO 4

5V5 OS THERMO 5

6V5 OS THERMO 6

7V5 OS THERMO 7

5 – 9

Page 26

LC-37D90U

Page Line Item Description Remarks (adjustment detail, etc.)

24 [M EEP SET]

1 MONITOR TIME OUT

2 MONITOR MAX TEMP

3 MONITOR STANDBY CAUSE

25 [M TESTPTRN]

1 LCD TEST PATTERN

26 [MEMORY CLR]

1 KEY LOCK(1217)

2 KOUTEI AREA ALL CLEAR

3 A MODE AREA CLEAR

4 BACKUP AREA CLEAR

5 B MODE AREA CLEAR

6EXECUTION

27 [ETC]

1 EEP SAVE Writing setting values to EEPROM.

2 EEP RECOVER Reading setting values from EEPROM.

3 STANDBY CAUSE RESET Reset stand by cause.

*1 Details of P1.7(NORMAL STANDBY CAUSE)

6 No operation off in the cause of “no operation off”

7 No signal off in the cause of “no signal off”

8 PC power management mode 1 in the cause of “Standby mode MODE1”

9 PC power management mode 2 in the cause of “Standby mode MODE2”

A Off timer in the cause of “SLEEP timer”

C Command from RS232C in the cause of command by RS-232C

*2 Details of P1.8(ERROR STANDBY CAUSE)

5 Prolonged unspecified-signal input in PC mode in the cause of continuous “out of range”, PC input mode

13 Temperature error in the cause of abnormal temperature

16 Monitor trouble detected in the cause of abnormal monitor mode

17 Fan lock in the cause of fan lock

6. Special features

* STANDBY CAUSE (Page 1/27)

Display of a cause (code) of the last standby

The cause of the last standby is recorded in EEPROM whenever possible.

Checking this code will be useful in finding a problem when you repair the troubled set.

* EEP SAVE (Page 27/27)

Storage of EEP adjustment value

* EEP RECOVER (Page 27/27)

Retrieval of EEP adjustment value from storage area

7. Video signal adjustment procedure

*Adjustment process mode menu is listed in section 5.

7.1. Signal check

Signal generator level adjustment check (Adjustment to the specified level)

• Composite signal : 0.714Vp-p ± 0.02Vp-p (Pedestal to white level)

• 15K component signal : Y level : 0.714Vp-p ± 0.02Vp-p (Pedestal to white level)

PB, PR level : 0.7Vp-p ± 0.02Vp-p

• 33K component signal : Y level : 0.7Vp-p ± 0.02Vp-p (Pedestal to white level)

PB, PR level : 0.7Vp-p ± 0.02Vp-p

• DVI-I (analog RGB) signal : RGB level : 0.7Vp-p ± 0.02Vp-p (Pedestal to white level)

7.2. Entering the adjustment process mode

Enter the adjustment process mode according to the steps described in section 3.

5 – 10

Page 27

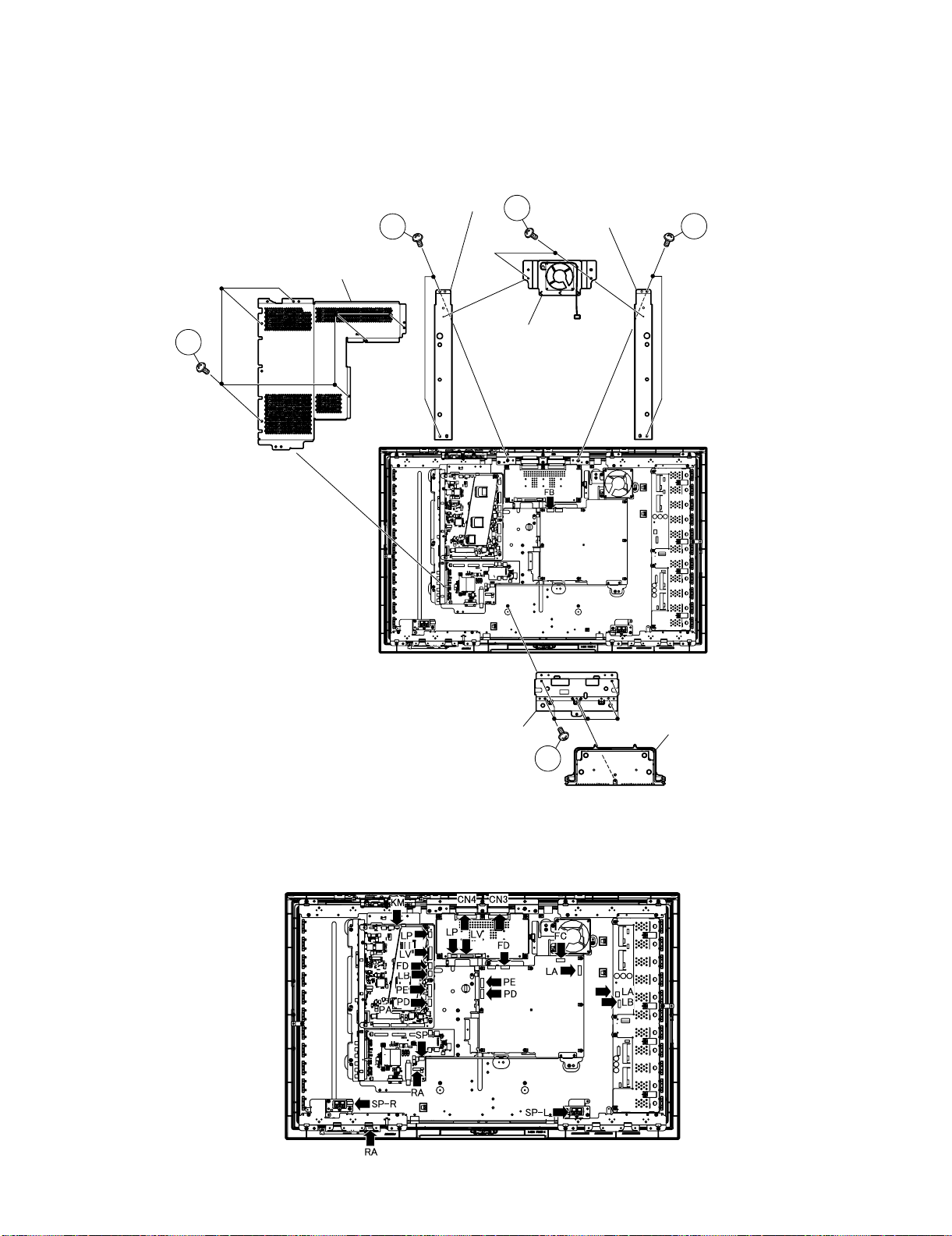

7.3. N358 composite signal adjustment (Tuner)

Adjustment item Adjustment conditions Adjustment procedure

1 Adjustment N358 signal Feed the PAL split field color bar signal (75% color saturation) to VIDEO

1 input. Feed the RF signal (by use of US-10ch) to TUNER-A.

[Video input signal] [US-10CH]

100% white 100% white

2 Auto adjustment

performance

Page 3/27 Bring the cursor on [•N358 ALL ADJ] and press [ENTER].

[•N358 ALL ADJ FINISH] appears when finished.

7.4. Component 15K signal adjustment

Adjustment item Adjustment conditions Adjustment procedure

1 Adjustment 480i signal Feed the 100% color bar signal to INPUT 1 component input.

LC-37D90U

100% white

2 Auto adjustment

performance

Page 5/27 Bring the cursor on [•COMP 15K ALL ADJ] and press [ENTER].

[•COMP 15K ALL ADJ FINISH] appears when finished.

7.5. Component 33K signal adjustment

Adjustment item Adjustment conditions Adjustment procedure

1 Adjustment 1080i signal Feed the 100% color bar signal to INPUT 1 component input.

100% white

2 Auto adjustment

performance

Page 6/27 Bring the cursor on [•HDTV ADJ] and press [ENTER].

[•HDTV ADJ FINISH] appears when finished.

7.6. DVI-I (analog) signal adjustment

Adjustment item Adjustment conditions Adjustment procedure

1 Adjustment DVI-I (analog)

XGA (1024 x 768)

60Hz

H,V SYNC

Feed the 100% white 1/2 window pattern signal to DVI-I (analog) input.

1/4

1/2

1/4

5 – 11

1/4

1/2

100% White

0% Black

1/4

Page 28

LC-37D90U

Adjustment item Adjustment conditions Adjustment procedure

2 Auto adjustment

performance

8. Adjustment of white balance

8.1. White balance adjustment

Adjustment item Adjustment conditions Adjustment procedure

1 Adjustment 1) Apply the following settings to the set.

2 Auto adjustment

performance

Page 7/27 Bring the cursor on [•DVI ANALOG] and press [ENTER].

[•DVI ANALOG ADJ FINISH] appears when finished.

AV MODE: [DYNAMIC]

Aging Time: 60 Min.

Backlight: +16

2) Connect a white balance jig and the set.

Optical measuring machine: [Minolta CA-210]

PC

RS-232C communication cable

3) Use an RS-232C command to display the screen for multipoint adjustment.

•Multipoint adjustment mode (MSET0001)

•Adjustment value initialization (MSET0004)

•Standard value 6 (LEV60232)

•Standard value 5 (LEV50200)

•Standard value 4 (LEV40164)

•Standard value 3 (LEV30132)

•Standard value 2 (LEV20088)

•Standard value 1 (LEV10048)

•Write setting (MSET0003)

[Adjustment]

1) Enter the monitor adjustment process mode.

2) Set the specified gradation for standard value 6. Set the strongest

color as the fixed color and adjust RGB by reducing to the standard

value.

3) Set the specified gradation for standard value 5. Set the correction

value of G [(default of standard value 5) x (G of standard value 6) /

(default of standard value 6)] and adjust RB to the standard value.

4) Set the specified gradation for standard value 4. Set the correction

value of G [(default of standard value 4) x (G of standard value 6) /

(default of standard value 6)] and adjust RB to the standard value.

5) Set the specified gradation for standard value 3. Set the correction

value of G [(default of standard value 3) x (G of standard value 6) /

(default of standard value 6)] and adjust RB to the standard value.

6) Set the specified gradation for standard value 2. Set the correction

value of G [(default of standard value 2) x (G of standard value 6) /

(default of standard value 6)] and adjust RB to the standard value.

7) Set the specified gradation for standard value 1. Set the correction

value of G [(default of standard value 1) x (G of standard value 6) /

(default of standard value 6)] and adjust RB to the standard value.

8) Write the adjustment values with MSET0003 command and turn off

AC power.

[Adjustment values]

Optical measuring machine: [Minolta CA-210] (Focus on the center of the screen.)

Level Standard value Adjustment value Tolerance

Standard value 6 232 x = 0.272 ±0.001 ±0.0020

y = 0.272 ±0.001 ±0.0020

Standard value 5 200 x = 0.272 ±0.001 ±0.0020

y = 0.272 ±0.001 ±0.0020

Standard value 4 164 x = 0.272 ±0.001 ±0.0020

y = 0.272 ±0.001 ±0.0020

Standard value 3 132 x = 0.272 ±0.001 ±0.0020

y = 0.272 ±0.001 ±0.0020

Standard value 2 88 x = 0.272 ±0.002 ±0.004

y = 0.272 ±0.002 ±0.004

Standard value 1 48 x = 0.272 ±0.002 ±0.004

y = 0.272 ±0.002 ±0.004

5 – 12

Page 29

LC-37D90U

Level Standard value Adjustment value Tolerance

Note Set the following before adjustment.

AV MODE: [DYNAMIC]

Monochrome: ON

Aging Time: 60 Min.

8.2. Adjusting procedure by use of [RS-232C]

1. Get ready the PC with COM port (RS-232C) running on Windows 95/98/ME/2000/XP operating system, as well as the RS-232C cross cable.

2. Start the unit with the RS-232C cable connected.

3. Start the terminal software. (The freeware readily available on the Internet will do.)

4. Make the following settings.

Baud rate 9,600 bps

Data LENGTH 8 bit

Parity bit None

Stop bit 1 bit

Flow control None

5. If the settings are correct, the terminal software indicates “ERR” against pressing of the “ENTER” key.

6. After the settings are done correctly, it is possible to make an adjustment by typing in the command shown in the table below and pressing the

“ENTER” key on the keyboard.

7. Command entry is successful if the terminal software indicates “OK” when the “ENTER” is pressed. If “ERR” is shown, retry to enter the command.

8. Send the process mode switching command to switch from the RS232C operation mode to the process mode.

KRSW0001: “ERR” is returned.

KKT10037: When “OK” is returned, the process mode becomes active. When “ERR”, start over from KRSW0001.

9. Send each adjustment command.

5 – 13

Page 30

LC-37D90U

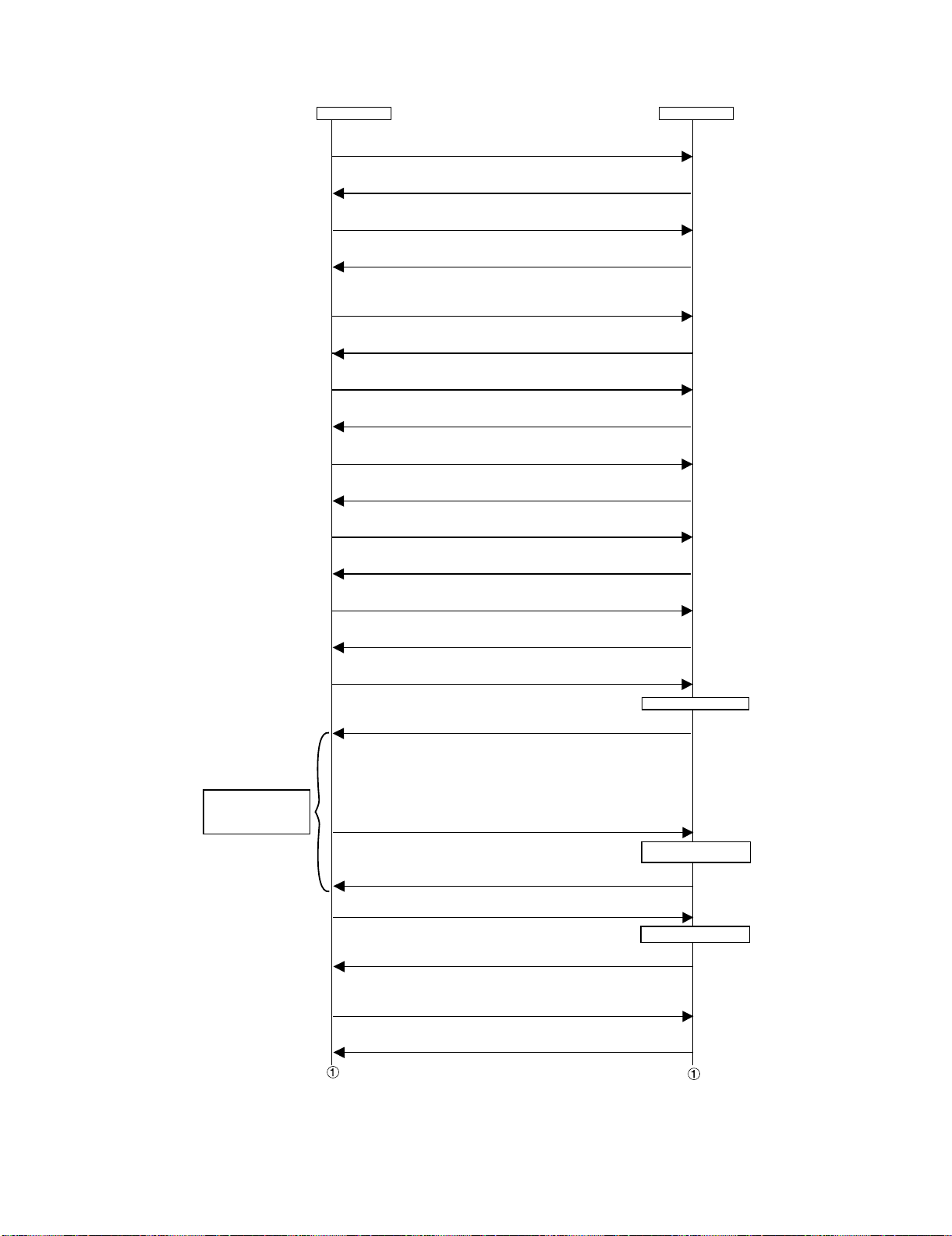

8.3. White balance adjustment sequence

Adjustment is available in any input or position. There is no specific order to adjust high and low, either.

Repeat until values are

properly

adjusted.

PC

Activate process command (STEP1).

KRSW0001

Command is accepted.

ERR

Activate process command (STEP2).

KKT10037

Process command is

activated.

OK

Remote control

disable command

KYOF0000

Setting is complete.

OK

Inhibit command for the OSD display

OSDS0001

Setting is complete.

OK

Set the light level to +12 using dimmer control command.

SBSL0016

Setting is complete.

OK

Set the multipoint adjustment mode.

MSET0001

The mode is set.

OK

Initialize adjustment values.

MSET0004

Initialization is done.

OK

Adjustment gradation setting (Standard value 6 = 236 gradation)

LEV60232

Adjustment value is set.

Adjust RGB to the target xy values.

MG6GXXXX

MG6BXXXX

MG6RXXXX

* XXXX indicates adjustment values between 0000 - 1023 (4 digit decimal

number with zero fill).

*

In order to adjust by reducing the value, set the strongest color as the fixed color.

* Default adjustment value of RGB is the parameter value of LEV6 command

multiplied by 4.

Adjustment gradation setting (Standard value 5 = 200 gradation)

LEV50200

Correct G value.

MG5GXXXX

When G is changed at adjustment gradation setting (standard value 6 = 236 gradation), calculate the ratio of the

change and set the following value to XXXX: (the value set with LEV5) x 4 x (the ratio).

OK

Adjustment values are set.

OK

Adjustment value is set.

OK

Adjustment value is set.

OK

Pattern display

Reflecting adjustment

values to images

Pattern display

Set

5 – 14

Page 31

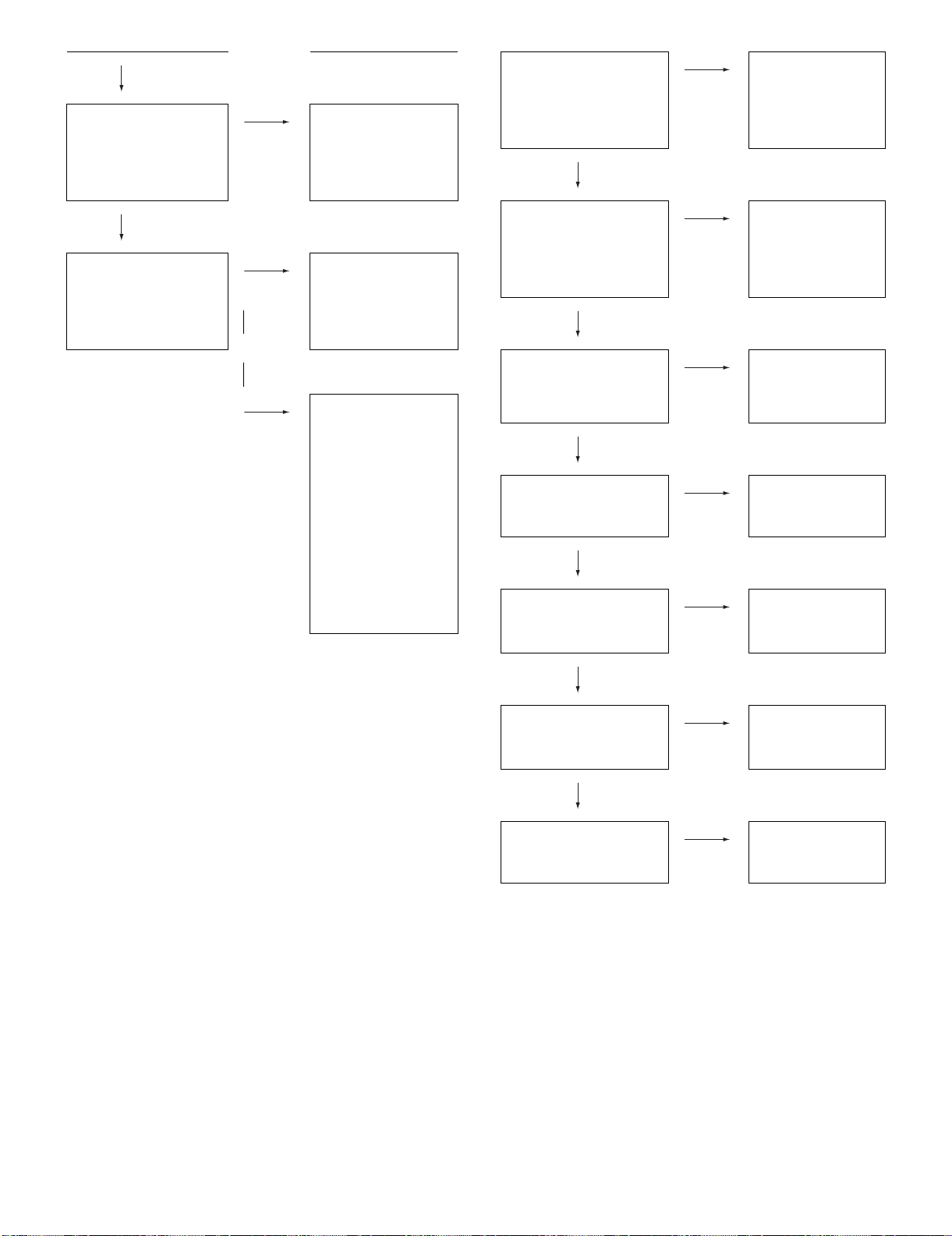

Repeat until values are

properly adjusted.

Start of measurement

Adjust RB to the target xy values.

MG5RXXXX

MG5BXXXX

* XXXX indicates adjustment values between 0000 - 1023 (4 digit decimal number with zero fill).

* G is fixed.

* Default adjustment value of RGB is the parameter value of LEV5 command multiplied by 4.

Adjustment values are set.

Adjustment gradation setting (Standard value 4 = 144 gradation)

LEV40164

OK

Reflecting adjustment values to

images

LC-37D90U

Repeat until values are

properly adjusted.

Repeat until values are

properly adjusted.

Adjustment value is set.

Correct G value.

MG4GXXXX

When G is changed at adjustment gradation setting (standard value 6 = 236 gradation), calculate

the ratio of the change and set the following value to XXXX: (the value set with LEV4) x 4 x (the ratio).

Start of measurement

Adjust RB to the target xy values.

MG4RXXXX

MG4BXXXX

* XXXX indicates adjustment values between 0000 - 1023 (4 digit decimal number with zero fill).

* G is fixed.

* Default adjustment value of RGB is the parameter value of LEV4 command multiplied by 4.

Adjustment gradation setting (Standard value 3 = 116 gradation)

LEV30132

Correct G value.

MG3GXXXX

When G is changed at adjustment gradation setting (standard value 6 = 236 gradation), calculate

the ratio of the change and set the following value to XXXX: (the value set with LEV3) x 4 x (the ratio).

Start of measurement

Adjust RB to the target xy values.

MG3RXXXX

MG3BXXXX

* XXXX indicates adjustment values between 0000 - 1023 (4 digit decimal number with zero fill).

* G is fixed.

* Default adjustment value of RGB is the parameter value of LEV3 command multiplied by 4.

OK

Adjustment value is set.

OK

Reflecting adjustment values to

Adjustment values are set.

OK

Adjustment value is set.

OK

Adjustment value is set.

OK

Pattern display

images

Pattern display

Reflecting adjustment values to

Adjustment values are set.

OK

Adjustment gradation setting (Standard value 2 = 66 gradation)

LEV20088

Adjustment value is set.

Correct G value

MG2GXXXX

When G is changed at adjustment gradation setting (standard value 6 = 236 gradation), calculate

the ratio of the change and set the following value to XXXX: (the value set with LEV2) x 4 x (the ratio).

OK

Adjustment value is set.

OK

Pattern display

5 – 15

images

Page 32

LC-37D90U

Repeat until values are

properly adjusted.

Repeat until values are

properly adjusted.

Start of measurement

Adjust RB to the target xy values.

MG2RXXXX

MG2BXXXX

* XXXX indicates adjustment values between 0000 - 1023 (4 digit decimal number with zero fill).

* G is fixed.

* Default adjustment value of RGB is the parameter value of LEV2 command multiplied by 4.

Reflecting adjustment values to

Adjustment values are set.

OK

Adjustment gradation setting (Standard value 1 = 50 gradation)

LEV10048

Adjustment value is set.

OK

Correct G value.

MG1GXXXX

When G is changed at adjustment gradation setting (standard value 6 = 236 gradation), calculate

the ratio of the change and set the following value to XXXX: (the value set with LEV1) x 4 x (the ratio).

Adjustment value is set.

OK

Start of measurement

Adjust RB to the target xy values.

MG1RXXXX

MG1BXXXX

* XXXX indicates adjustment values between 0000 - 1023 (4 digit decimal number with zero fill).

* G is fixed.

* Default adjustment value of RGB is the parameter value of LEV1 command multiplied by 4.

Reflecting adjustment values to

Adjustment values are set.

OK

Save adjustment values.

MSET0003

Adjustment values are saved.

OK

Completion of adjustment

Turn off AC power

images

Pattern display

images

9. Initialization to factory settings

CAUTION: When initialization is performed, all user setting data including the channel settings are initialized. Be cautious when making this adjust-

ment.

(The adjustments done in the adjustment process mode are not initialized.)

Adjustment item Adjustment conditions Adjustment procedure

1 Initialization It turns off with AC power

supply.

After the adjustment, cancel the adjustment process mode.

To exit the adjustment process mode, unplug the AC power cable from the outlet to make a

forced shutdown. (When the power was turned off with the remote controller, once unplug the

power cable and plug it again. In this case, wait 10 seconds or so before plugging.)

Enter the adjustment process mode.

Bring the cursor on to [INDUSTRY INIT] in page 2/27.

Set to [ON] using [VOL] key, and press [ENTER] to execute the initialization.

When the version number screen shows up on the green background and “SUCCESS”

gets displayed at the top on screen, it means the procedure has been successfully carried out.

(If an error occurs, “ERROR” is displayed on the red background.)

•Turn off the AC power.

*Never shut off the power during the initialization process.

The following settings are initialized in this adjustment.

1) User setting

2) Channel data (e.g. broadcast frequencies)

3) Password data

4) Operation time

5) Auto installation flag

6) V-CHIP block setting

5 – 16

Page 33

LC-37D90U

[2] MAJOR IC INFORMATIONS

1. MAJOR IC INFORMATIONS

1.1. IC501 (MM1630CQ)

This I2C bus-controlled video switch is designed to switch between one-system color difference (component) signal, one-system S video signal and

two-system composite signal.

The analog video signal from the INPUT-1 or INPUT-2 input terminal is fed into this IC for selection. The video output signal from this IC flows through

a low-pass filter into the video signal processing circuit IC3301 (IXB723WJ).

1.2. IC2701 (VHiTA2024++-1Y)

The Class-T type digital audio power amplifier TA2024 gives maximum continuous output of 10 W/ch.

1.3. IC1401 (VHiAN5832SA-1Y)

The AN5832SA is an I2C bus-controlled, US-standard analog TV sound multiplexing demodulator IC. It has the following functions built in: SIF

demodulation, STEREO demodulation, SAP demodulation, dbx noise reduction, and audio AGC.

1.4. IC1403 (VHiAK4683EQ-1Q)

This IC provides for 2-channel A/D and 4-channel D/A (192-kHz sampling).

The built-in digital audio interfaces DIR (Digital Interface Receiver) and DIT (Digital Interface Transmitter) (192 kHz compatible, 6 inputs/1 output) are

compatible with the AES3, IEC60958, S/PDIF, and EIAJ CP1201 standards. Both the DIR and DIT can handle 192-kHz sampling and 24-bit data. The

DIR is also equipped with 6-channel input selector that detects not just PCM data but also Dolby Digital and other non-PCM data.

1.5. IC1406 (VHiNJU26111-1Q)

The 24-bit, DSP core, digital audio processor has the Circle Surround II 5.1, TruSurround XT, Tru Bass, Focus, and Mono-To-Stereo functions. The

Circle Surround II 5.1 feature converts matrix-encoded stereo signals to theater-like 5.1-channel sounds. Un-matrix-encoded signals are also converted to effects-rich 5.1-channel output. The TruSurround XT feature creates three-dimensional sounds, richer than stereo signals.

1.6. IC1507 (VHiTMDS341+-1Y)

The TMDS341 single-chip IC is provided with multiple switching function, in which up to 3 DVI/HDMI ports can be selected for a single display input

terminal.

This 3-port device is also equipped with signal conditioning function and switching function. Each of the ports supports 4-channel TMDS signal, one

hot plug detection, and I2C interface. Each of the 4 TMDS channels, in turn, provides maximum 1.65-Gbps signal transmission rate, fixed 8-dB input

equalization, and enable/disable 3-dB output deemphasis function.

On this IC, the INPUT-3/4 HDMI port and the INPUT-5 DVI port are switched.

1.7. IC1508 (VHiSii9011L-1Q)

The TMDS receiver IC decodes differential serial-transmitted signal to parallel signal. Compatible with the HDCP system, encrypted signals can also

be received.

This IC responds to the INPUT-3/4 HDMI (High-Definition Multimedia Interface) and the INPUT-5 DVI (Digital Visual Interface) selected by IC507.

1.8. IC2002 (RH-iXB345WJZZQ)

The monitor microprocessor is intended to communicate with the main microprocessor and to operate the system. It also controls power of the entire

system.

1.9. IC3301 (RH-iXB723WJQZQ)

This video processor consists of an LSI system-on-chip device. For high-precision data processing, it is equipped with a high-precision 166-MHz, 10bit A/D converter.

For processing analog video signals, this IC supports the NTSC-compatible high-performance multi-format 2D/3D digital Y/C separation video

decoder as well as the video format conversion engine. It provides for 10-bit video signal processing.

1.10. IC3501/3502 (RH-iXB375WJZZQ)

These ICs are 128-Mbit GDDR SDRAM (Graphic Double Data Rate Synchronous DRAM), providing a memory for image processing and buffering

OSD data.

5 – 17

Page 34

LC-37D90U

1.11. IC8101 (RH-iXB281WJZZQ)

This LSI with MPEG-2 system decoder performs back-end processing for digital broadcasting. It is equipped with a CPU (processor core: AM33-3),

descrambler (DES), transport stream de-multiplexer, video decoder (MPEG-2 MP@HL compatible), graphic processor, audio decoder (AC3 compatible), and an NTSC video encoder.

After receiving transport stream from the tuner, the LSI decrypts pay-TV broadcasts with the descrambler. Then using the de-multiplexer, it separates