Page 1

LC-32SH25E

SERVICE MANUAL

No. SX8T4LC32SH25

LCD COLOUR TELEVISION

MODELS

In the interests of user-safety (Required by safety regulations in some countries) the set should be restored to its original condition and only parts identical to those specified should be used.

SAFETY PRECAUTION

IMPORTANT SERVICE SAFETY PRE-

CAUTION ................................................. ... ........2

Precautions for using lead-free solder ......….......3

CHAPTER 1. OPERATION MANUAL

[1] SPECIFICATIONS ..................................................4

[2] OPERATION MANUAL ...........................................5

[3] DIMENSIONS .......................................................10

CHAPTER 2. REMOVING OF MAJOR PARTS

[1] REMOVING OF MAJOR PARTS ..........................11

CHAPTER 3. ADJUSTMENT PROCEDURE

[1] ADJUSTMENT PROCEDURE .............................16

[2] SERVICE MODE ..................................................21

[3]

SOFTWARE UPGRADE PROCEDURE...............22

CHAPTER 4. TROUBLESHOOTING TABLE

[1] TROUBLESHOOTING TABLE..............................26

CHAPTER 5. MAJOR IC INFORMATIONS

[1] MAJOR IC INFORMATIONS.................................39

CHAPTER 6. BLOCK DIAGRAM/WIRING DIAGRAM

[1] VIDEO & AUDIO BLOCK DIAGRAM ...................59

Parts marked with " " are important for maintaining the safety of the set. Be sure to replace these parts with specified ones for maintaining the

safety and performance of the set.

CONTENTS

[2] POWER MANAGEMENT BLOCK DIAGRAM ......60

[3] I2C and RS232 BLOCK DIAGRAM .......................61

[4] WIRING DIAGRAM ...............................................62

CHAPTER 7. PRINTED WIRING BOARD

[1] MAIN UNIT PRINTED WIRING BOARD ...............63

[2] POWER UNIT PRINTED WIRING BOARD ..........65

[3] KEY UNIT PRINTED WIRING BOARD .................67

[4] IR UNIT PRINTED WIRING BOARD ....................68

CHAPTER 8. SCHEMATIC DIAGRAM

[1] MAIN SCHEMATIC DIAGRAM ............................69

[2] POWER SCHEMATIC DIAGRAM .......................83

[3] KEY SCHEMATIC DIAGRAM .............................84

[4] IR SCHEMATIC DIAGRAM .................................85

CHAPTER 9. Parts Guide

[1] SPARE PARTS LIST.............................................86

[2] CABINET PARTS ................................................108

[3] SUPPLIED ACCESSOORIES..............................110

[4] PACKING PARTS................................................111

LC-32SH25E

This document has been published to be used for

after sales service only.

The contents are subject to change without notice.

1

Page 2

LC-32SH25E

SAFETY PRECAUTION

IMPORTANT SERVICE SAFETY PRECAUTION

■ Service work should be performed only by qualified service technicians who are thoroughly familiar with all safety checks and the

servicing guidelines which follow:

■ WARNING

1. For continued safety, no modification of any circuit should be

attempted.

2. Disconnect AC power before servicing.

CAUTION:

FOR CONTINUED PROTECTION AGAINST A

RISK OF FIRE REPLACE ONLY WITH SAME

TYPE FUSE.

42" F901 (T6.3AH/250V)

26"/32" F901 (T5AH/250V)

■

BEFORE RETURNING THE RECEIVER

(Fire & Shock Hazard)

Before returning the receiver to the user, perform the following

safety checks:

3. Inspect all lead dress to make certain that leads are not pinched,

and check that hardware is not lodged between the chassis and

other metal parts in the receiver.

4. Inspect all protective devices such as non-metallic control knobs,

insulation materials, cabinet backs, adjustment and compartment

covers or shields, isolation resistor-capacitor networks, mechanical

insulators, etc.

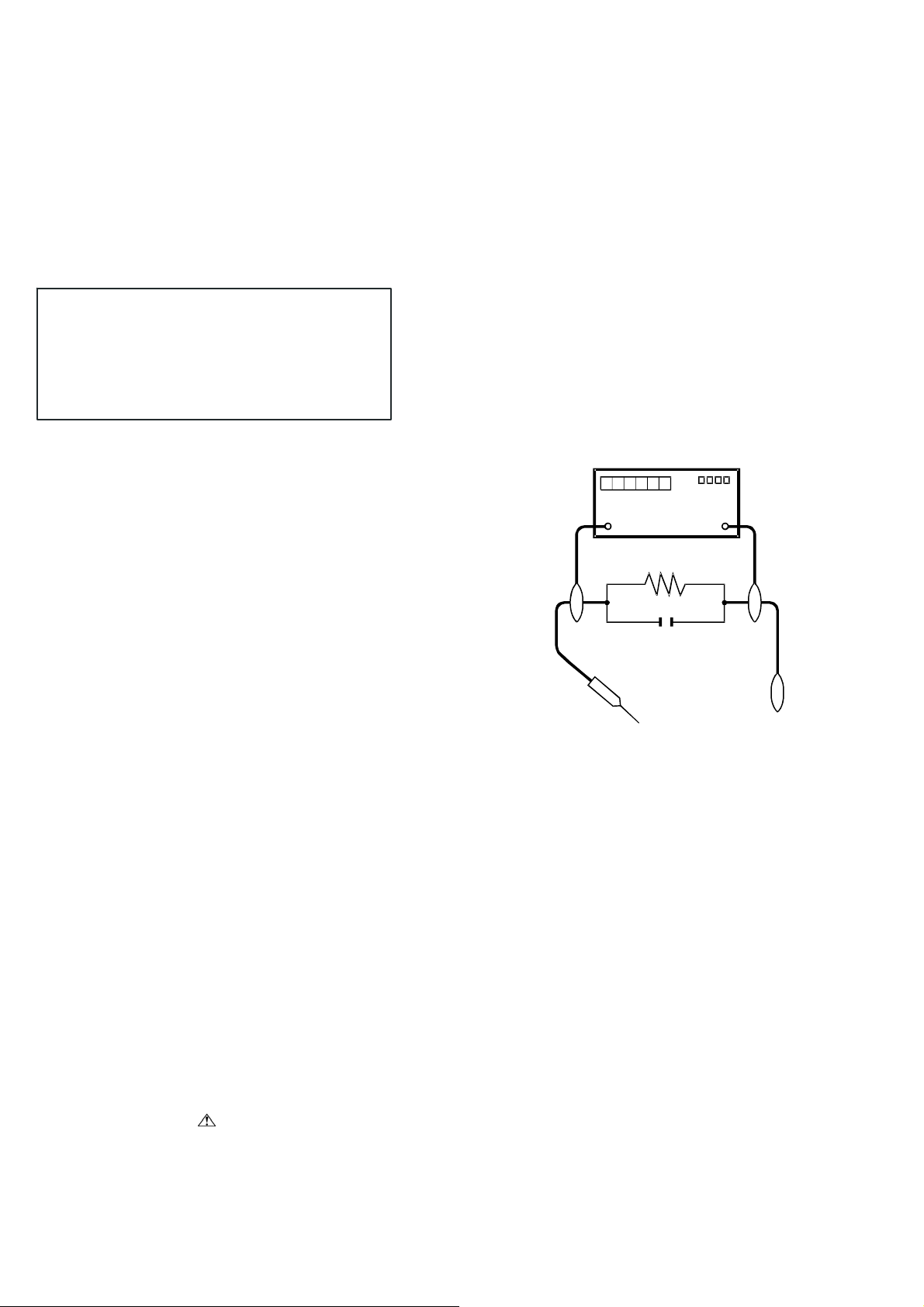

5. To be sure that no shock hazard exists, check for leakage current in

the following manner.

• Plug the AC cord directly into a 220~240 volt AC outlet.

• Using two clip leads, connect a 1.5k ohm, 10 watt resistor paralleled

by a 0.15µF capacitor in series with all exposed metal cabinet

parts and a known earth ground, such as electrical conduit or

electrical ground connected to an earth ground.

//////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

SAFETY NOTICE

Many electrical and mechanical parts in LCD color television have

special safety-related characteristics.

These characteristics are often not evident from visual inspection,

nor

can protection afforded by them be necessarily increased by using

replacement components rated for higher voltage, wattage, etc.

Replacement parts which have these special safety characteristics

are identified in this manual; electrical components having such

features are identified by “ ” and shaded areas in the Replacement

Parts List and Schematic Diagrams.

//////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

• Use an AC voltmeter having with 5000 ohm per volt, or higher, sensitivity or measure the AC voltage drop across the resistor.

• Connect the resistor connection to all exposed metal parts having a

return to the chassis (antenna, metal cabinet, screw heads, knobs

and control shafts, escutcheon, etc.) and measure the AC voltage

drop across the resistor.

All checks must be repeated with the AC cord plug connection

reversed. (If necessary, a nonpolarized adaptor plug must be used

only for the purpose of completing these checks.)

Any reading of 1.05 V peak (this corresponds to 0.7 mA peak AC.)

or more is excessive and indicates a potential shock hazard which

must be corrected before returning the monitor to the owner.

DVM

AC SCALE

1.5k ohm

10W

0.15 µF

TEST PROBE

TO EXPOSED

METAL PARTS

CONNECT TO KNOWN

EARTH GROUND

For continued protection, replacement parts must be identical to those

used in the original circuit.

The use of a substitute replacement parts which do not have the same

safety characteristics as the factory recommended replacement parts

shown in this service manual, may create shock, fire or other hazards.

2

Page 3

LC-32SH25E

Precautions for using lead-free solder

Using lead-free wire solder

• When fixing the PWB soldered with the lead-free solder, apply lead-free wire solder. Repairing with conventional lead wire solder may cause

damage or accident due to cracks.

As the melting point of lead-free solder (Sn-Ag-Cu) is higher than the lead wire solder by 40 °C, we recommend you to use a dedicated soldering

bit, if you are not familiar with how to obtain lead-free wire solder or soldering bit, contact our service station or service branch in your area.

Soldering

• As the melting point of lead-free solder (Sn-Ag-Cu) is about 220 °C which is higher than the conventional lead solder by 40 °C, and as it has

poor solder wettability, you may be apt to keep the soldering bit in contact with the PWB for extended period of time. However, Since the land

may be peeled off or the maximum heat-resistance temperature of parts may be exceeded, remove the bit from the PWB as soon as you

confirm the steady soldering condition.

Lead-free solder contains more tin, and the end of the soldering bit may be easily corroded. Make sure to turn on and off the power of the bit as

required.

If a different type of solder stays on the tip of the soldering bit, it is alloyed with lead-free solder. Clean the bit after every use of it.

When the tip of the soldering bit is blackened during use, file it with steel wool or fine sandpaper.

• Be careful when replacing parts with polarity indication on the PWB silk.

3

Page 4

LC-32SH25E

CHAPTER 1. OPERATION MANUAL

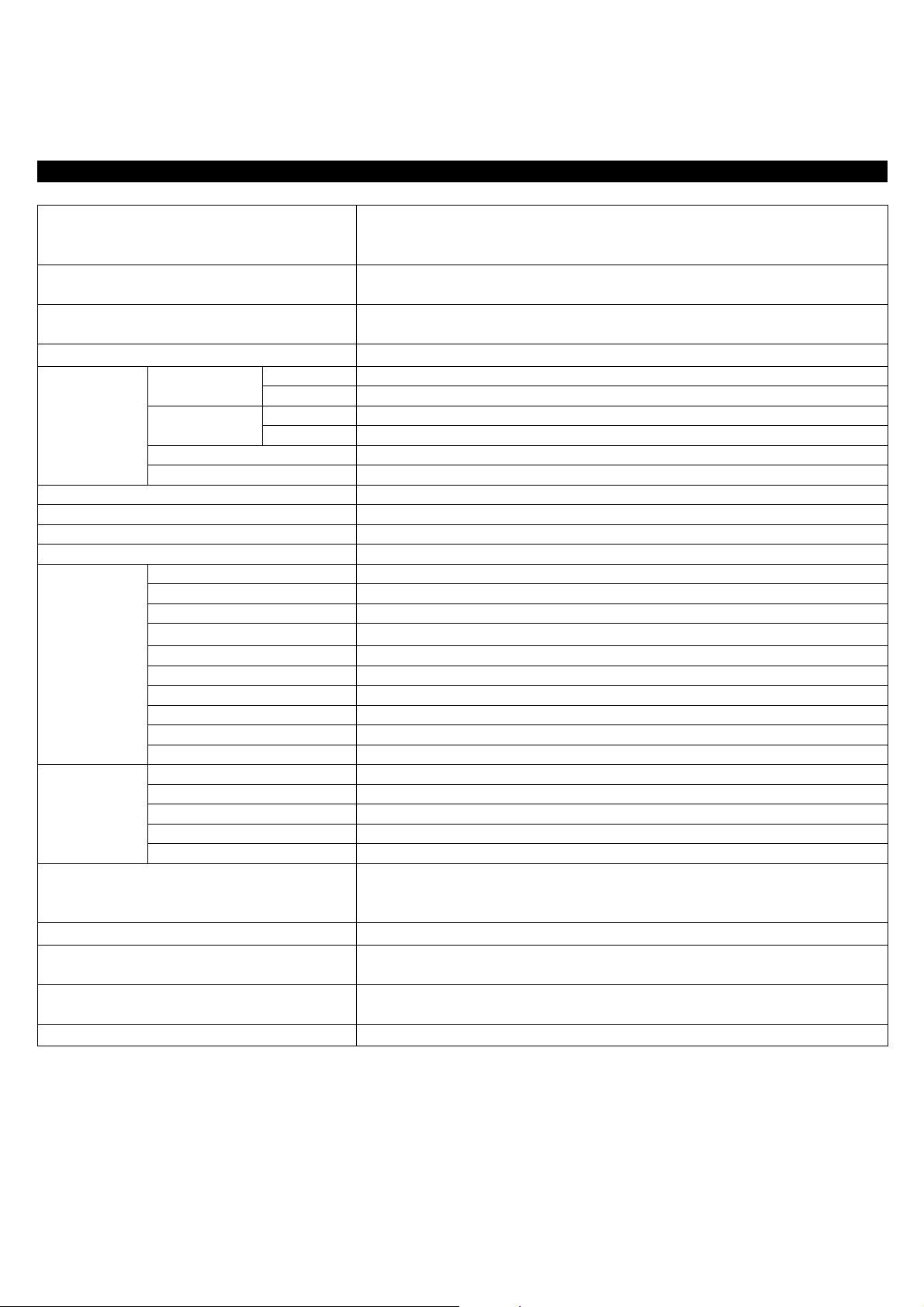

[1] SPECIFICATIONS

Specification

Item

LCD panel 32” diagonal

Number of dots

Video Colour System

TV-Standard

TV Function

Backlight life 60,000 hours (at Backlight Standard position)

Viewing angles H : 176° V : 176°

Audio amplifier 5W X 2

Speaker (100 mm X 30 mm) X 2

Rear

Side

OSD language

Power Requirement

Power Consumption

Receiving

Channel

TV-Tuning System Auto Preset 999 ch, Auto Label, Auto Sort

STEREO/BILINGUAL NICAM/A2

Antenna

RS-232C D-Sub 3 pin male connector

SCART 1 SCART (AV input, Y/C input, RGB input, TV output-analogue only)

SCART 2 SCART (AV input, Y/C input, monitor output (analogue source - RF, SCART 1, SIDE AV) )

PC IN VGA pin (AV input), Ø 3.5mm jack (Audio output)

Component Y/Pb(Cb)/Pr(Cr), RCA pin (L/R)

SPDIF Digital audio output

AUDIO OUT RCA pin (L/R)

HDMI 1

HDMI 2

C. I. (Common Interface) EN50221, R206001

Headphones Ø 3.5mm jack (Audio output)

AV IN RCA pin (AV input) , RCA pin (L/R), S-VIDEO (Y/C input)

USB

HDMI 3

Analogue

Digital

VHF/UHF ATV : IRA-E69, DVB-T : E5-E69

CATV S-band, S1–S41ch

32” LCD Colour TV

Model: LC-32SH25E

3,147,264 dots

(1366 X 768 X 3 dots)

PAL/SECAM/NTSC 3.58/NTSC 4.43/PAL 60

CCIR (B/G, I, D/K, L/L’)

DVB-T (2K/8K OFDM)

UHF/VHF 75 Ω

For service use only

Bulgarian, Croatian, Czech, Danish, Dutch, English, Finnish, French, German, Greek, Hungarian,

Italian, Norwegian, Polish, Portuguese, Romanian, Russian, Serbian, Slovak, Slovene, Spanish,

Swedish, Turkish

AC 220–240 V, 50 Hz

150 W (Standby<1W)

(Method IEC60107)

,

Weight

Operating temperature 0°C to + 40°C

• As a part of policy of continuous improvement, SHARP reserves the righ t to make design and specification changes for product improvement

without prior notice. The performance specification figures indicated are nominal values of production units. There may be some deviations

from these values in individual units.

10.7 kg (Without stand),

12.5 kg (With stand)

4

Page 5

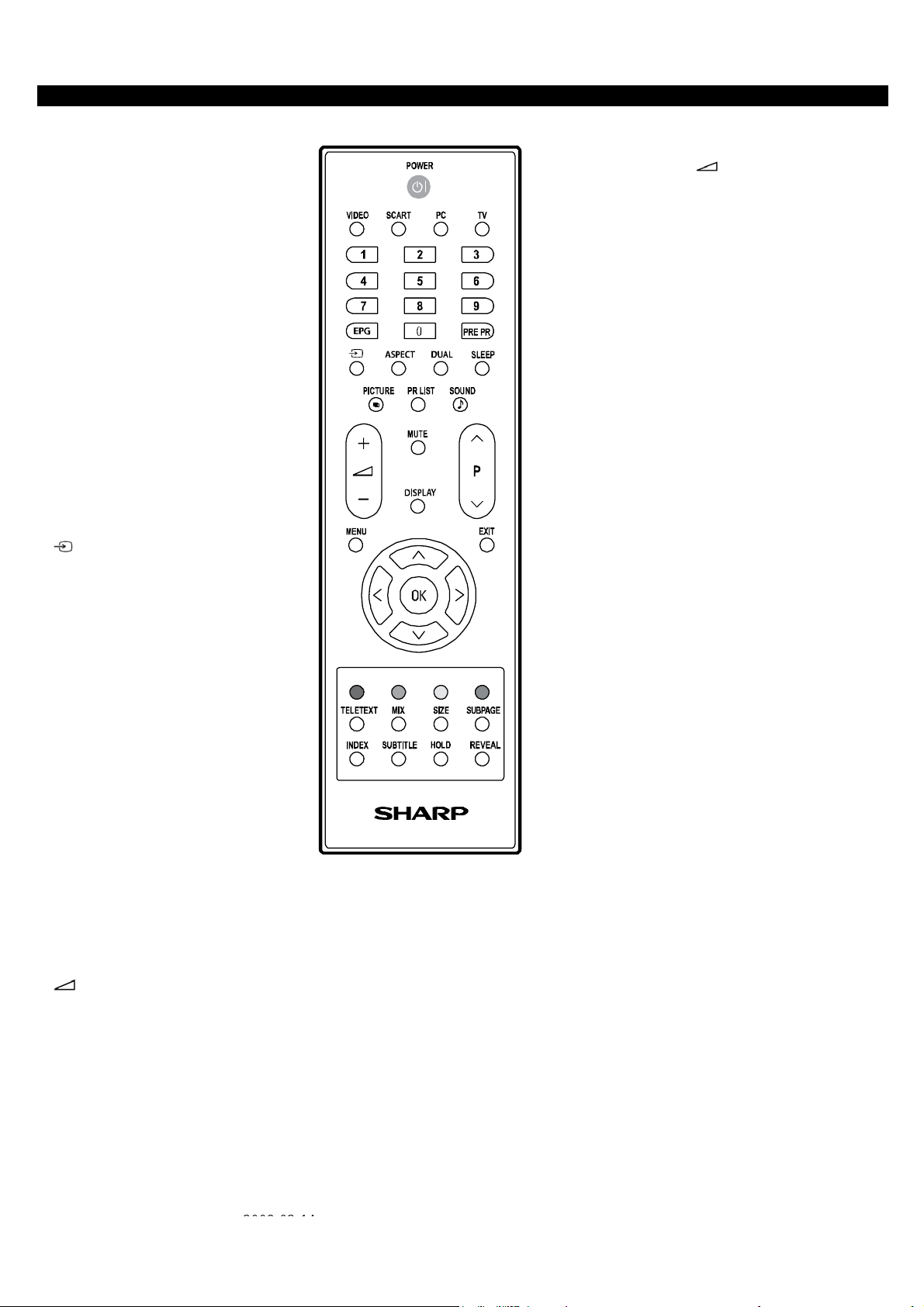

[2] OPERATION MANUAL

Remote control unit

POWER

Press to turn the LCD TV on or enter

standby mode.

VIDEO

Press this key you could select YPbPr, Side

AV, HDMI 1, HDMI 2, HDMI 3.

SCART

Press this key you could select

SCART 1, SCART 2.

PC

Press to direct to the PC mode.

TV

Press to direct to the TV mode.

0-9 DIGIT BUTTONS

To select a TV channel directly.

EPG

Press this button to display electronic

program guide in TV mode.

PRE PR

To display the previous selected TV channel.

(INPUT SOURCE)

Select an input source.

ASPECT

Change the aspect ratio; please refer to

Picture format section.

DUAL

Select MONO, STEREO, DUAL 1 and DUAL

2 for ATV channel. Select Audio language for

DTV channel.

SLEEP

Press to turn the LCD TV off within an

amount of time. (5-180 minutes.)

PICTURE

Press to set the LCD TV to a predefined

picture setting.

User / Cinema / Sport / Vivid / Hi-Bright

PR LIST

Press to display a list of channels. Then

press Red button to select the Digital or

Analogue channel list.

SOUND

Press to set the LCD TV to a predefined

sound setting.

Off / Rock / Pop / Live / Dance / Techno /

Classic / Soft

(+/-)

Press to adjust the volume.

P(∧/

)

∨

Press to select the channel.

LC-32SH25E

MUTE

Press to toggle audio on and off.

You can also press (+/-) VOL to

restore the previous volume level.

DISPLAY

Press to display the current signal

status, including input source/

channel audio mode.

MENU

Press to activate the LCD TV OSD.

Press again to exit the LCD TV

OSD.

EXIT

Press to exit LCD TV OSD.

OK

Press to activate a setting.

<>

∧∨

Press ∧∨<>

to navigate and confirm your selection.

R/G/Y/B (Colour Button)

Press buttons to select the pictures with

various colours of text. Different channels

display different functions.•

TELETEXT

Press this button to activate Teletext. Press

again to turn off Teletext.

MIX

Press this button to activate Teletext with TV.

SIZE

Press this button to change the font size: Full

screen, Top half and Bottom half.

SUBPAGE

To select the subpage when the current page

contains subpage(s).

INDEX

Press this button to return to page 100 or the

index page; and then press 0 to 9. The teletext

page will be numbered and added to the page

you select or the secondary item.

SUBTITLE

For DTV, press it to select subtitle setting.

off / on / on during mute

For ATV, please activate Teletext to select

subtitle page.

HOLD

Press this button to stop the scrolling of pages.

The text decoder stops receiving data.

REVEAL

Reveal hidden information such as answers to

a quiz.

2008-03-14

5

Page 6

LC-32SH25E

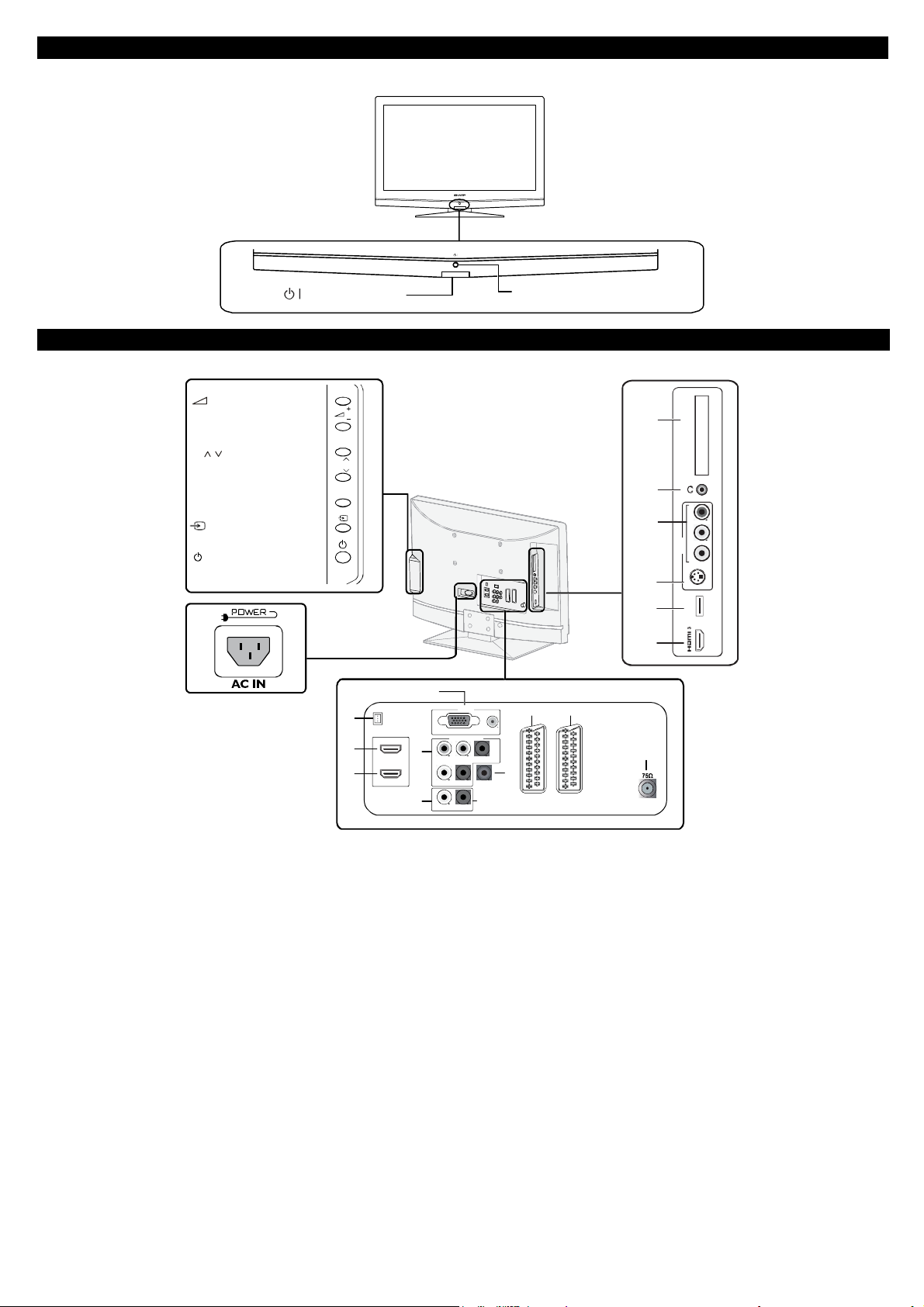

TV (Front view)

TV (Rear view)

(+/-)

Volume buttons

P

( )

/

Programme [channel] buttons

MENU

button

(INPUT SOURCE) bu tton

(Power) button

1

1 Power connector

2 SERVICE socket

3 HDMI 1

4 HDMI 2

5 PC IN (VGA/AUDIO)

6 Component Video and L/R Audio input

7 SPDIF Output (Digital audio out)

8 AV L/R Audio Output

9 SCART 1 (CVBS Tuner out)

10 SCART 2 (CVBS Monitor out)

11 Tuner Input

12 COMMON INTERFACE slot

13 Earphone Output

14 Composite ( AV IN, AV/LR)

15 S-Video

16 SERVICE socket(For LC-32SH25E)

17 HDMI 3

(Standby/On) indicator

P

MENU

2

3

4

SERVICE

HDMI1

HDMI2

5

6

YPbPr

LRSPDIF OUT

8

L

PC IN

VGA

COMPONENT

R

6

AUDIO

7

AUDIO OU T

Remote control sensor

9

10

SCART1 SCART2

12

13

14

15

16

17

11

Page 7

Preparation

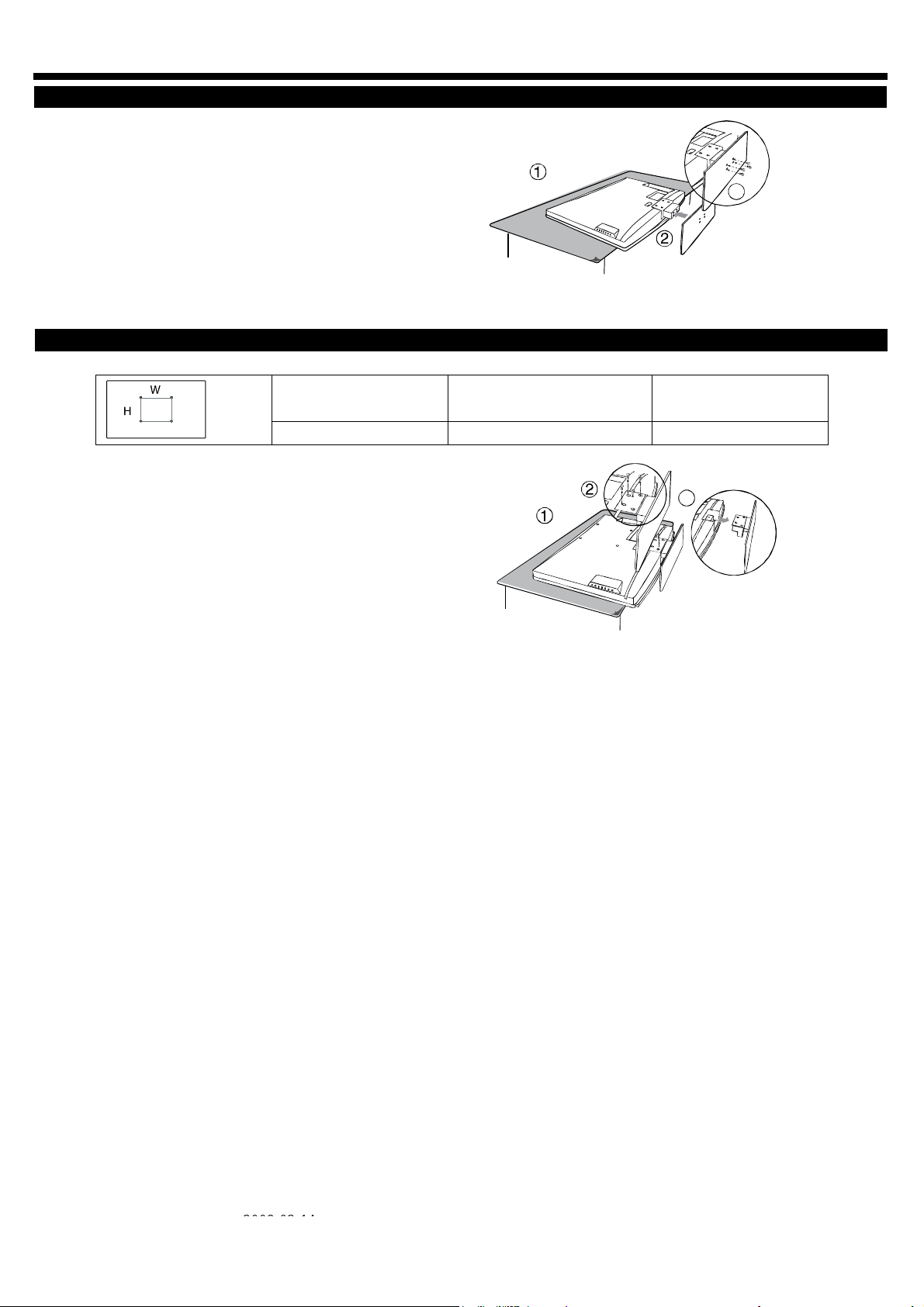

Mount the TV Stand

1. Put the TV face down on a safe surface that

is covered by a soft and smooth cloth.

2. Adjust the TV stand to the base column.

3. Fasten 4 screws.

Wall mounting

LC-32SH25E

3

TV screen size

( inches)

1. Put the TV face down on a safe surface that is

covered by a soft and smooth cloth.

2. Unscrew the 4 bolts that fasten the base

column to the TV by using a cross-head

screwdriver. (not supplide)

3. Detach the stand from the bottom of the TV.

32” 200 x 200 mm Metric 6 x 10 mm

VESA-compatible wall bracket

(millimeters) (W x H)

Screw type

3

2008-03-14

7

Page 8

LC-32SH25E

preparation

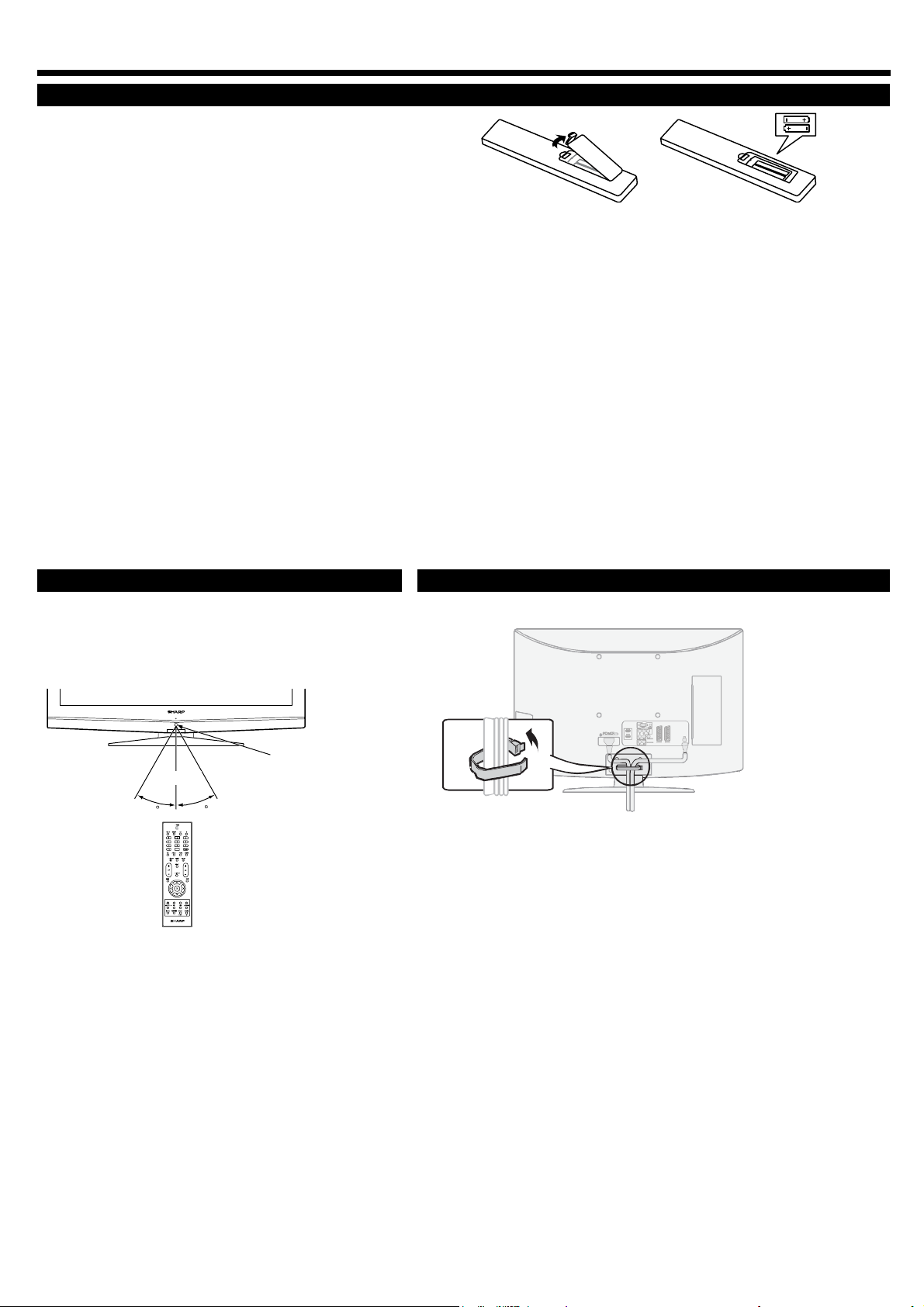

Installation of batteries

1. insert two AAA batteries into Remote control.

Make sure (+) and (-) are facing the proper

direction.

2. Replace the cover.

NOTE

• If the remote control will not to be used for a long

time, remove the batteries to avoid remote control damage.

CAUTION

Improper use of batteries can result in chemical leakage or explosion. Be sure to follow the instructions below.

• Do not mix batteries of different types. Different types of batteries have different characteristics.

• Do not mix old and new batteries. Mixing old and new batteries can shorten the life of new batteries or cause

chemical leakage in old batteries.

• Remove batteries as soon as they have worn out. Chemicals that leak from batteries can cause a rash. If you find

any chemical leakage, wipe thoroughly with a cloth.

• The batteries supplied with this product may have a shorter life expectancy due to storage conditions.

• If you will not be using the remote control unit for an extended period of time, remove the batteries from it.

Note on disposing batteries:

The batteries provided contain no harmful materials such as cadmium, lead or mercury.

Regulations concerning used batteries stipulate that batteries may no longer be thrown out with the household

Rubbish. Deposit any used batteries free of charge into the designated collection containers set up at commercial

Businesses.

Using the remote control unit Bundling the cables

Use the remote control unit by pointing it towards the

remote control sensor. Objects between the remote

control unit and sensor may prevent proper operation.

5m

30

Remote control sensor

30

8

Page 9

LC-32SH25E

Appendix

troubleshooting

problem possible Solution

No picture 1. Connect power cord correctly.

2. Turn on power.

3. Connect signal cable correctly.

4. Press any button on the LCD TV.

Abnormal colours Connect signal cable correctly.

Twisted picture 1. Connect signal cable correctly.

2. Please use compatible signal.

Picture too dark Adjust brightness and contrast.

Audio only, no images 1. Please check if input signal is connected correctly.

Picture only, no audio 1. Connect signal cable correctly.

Cannot use remote control 1. Please change battery.

Cannot receive sufficient channels

through antenna

No colours Please adjust the colour setup

Blinking picture accompanied by ghost

image

Broken lines or segments

Certain TV channels are blocked (Hope to

acquire some channels)

Overlapping images or ghost images Please use multi-directional outdoor antenna. (If your TV is subject to the influence of nearby mountains or

Cannot use a function If the item you choose turns gray, that item cannot be selected.

Cannot receive programs Please use the Update scan method to add the channels not included in memory.

1. When a lamp in LCD panel is broken and the

protector circuit in inverter operates and we

tune on the this set, LED keep red? or Green?

2. Service man only change the lamp in LCD

panel?

Cautions regarding use in high and low temperature environments

• When the unit is used in a low temperature space (e.g. room, office), the picture may leave trails or appear slightly delayed. This

is not a malfunction, and the unit will recover when the temperature returns to normal.

• Do not leave the unit in a hot or cold location. Also, do not leave the unit in a location exposed to direct sunlight or near a

heater, as this may cause the cabinet to deform and the LCD panel to malfunction.

• Storage temperature: +5°C to +35°C.

information on the software license for this product

Software composition

The software included in this product is comprised of various software components whose individual copyrights are held by SHARP or by third parties.

Software developed by SHarp and open source software

The copyrights for the software components and various relevant documents included with this product that were developed or written by SHARP are

owned by SHARP and are protected by the Copyright Act, international treaties, and other relevant laws. This product also makes use of freely

distributed software and software components whose copyrights are held by third parties. These include software components covered by a GNU

General Public License (hereafter GPL), a GNU Lesser General Public License (hereafter LGPL) or other license Agreement.

obtaining source code

Some of the open source software licensors require the distributor to provide the source code with the executable software components. GPL and

LGPL include similar requirements. For information on obtaining the source code for the open source software and for obtaining the GPL, LGPL, and

other license agreement information, visit the following website:

2. TV-RF signal must not be lower than 50dB.

2. Adjust volume to proper level.

3. Connect audio signal cable correctly.

4. TV-RF signal must not be lower than 50dB.

2. Turn off power for 10 seconds; and then restart power.

Please use the Channel scan function to increase the number of channels not included in memory.

1. Check the connection of antenna/signal cable.

2. Check if channel is in play mode.

3. Press signal source and change input mode.

Adjust antenna.

Keep the TV away from noise sources, such as automobiles, neon lights, and hair dryers.

Please use the Update scan method to add the channels not included in memory

buildings).

1. If the lamp(s) is(are) broken, panel inverter will not kick on the lamps, so TV set phenomena will be "no picture

on display."

But the TV system is still working, that is the RC can also control LED.

When AC power on, the LED will keep last status and when use RC DC power on, the LED will keep green light.

2. The failed panel should be sent back to Panel maker (CMO) via RMA process.

Panel maker (CMO) will not rework the lamps at customer's side since the repaired panel should be checked

through regular inspection flow to secure the quality.

http://www.sharp-eu.com/gpl/

We are unable to answer any questions about the source code for the open source software. The source code for the software components whose

copyrights are held by SHARP is not distributed.

acknowledgements

The following open source software components are included in this product:

•linuxkernel•modutils•glibc•zlib•libpng

2008-03-14

9

Page 10

LC-32SH25E

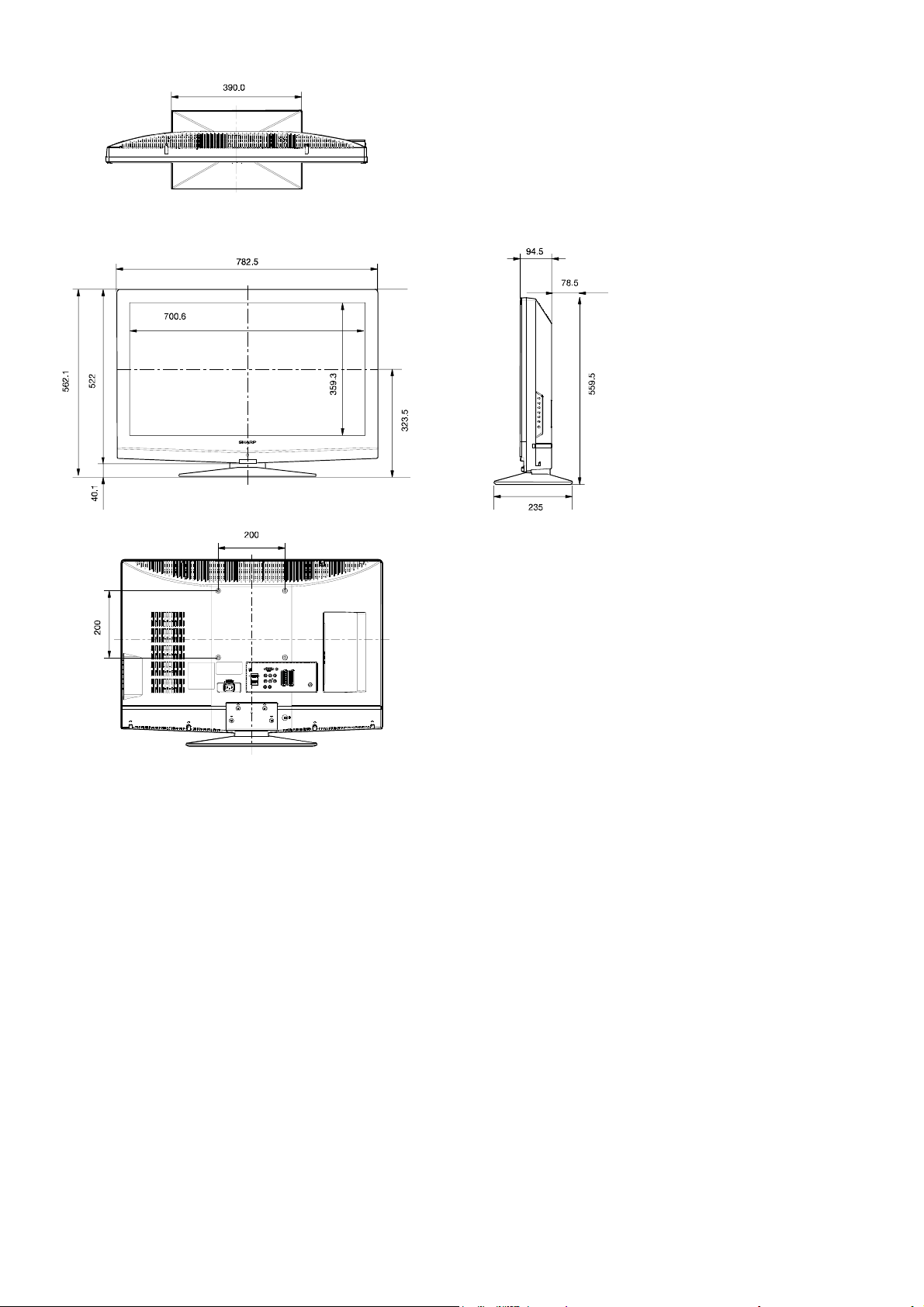

[3] DIMENSIONS

10

Page 11

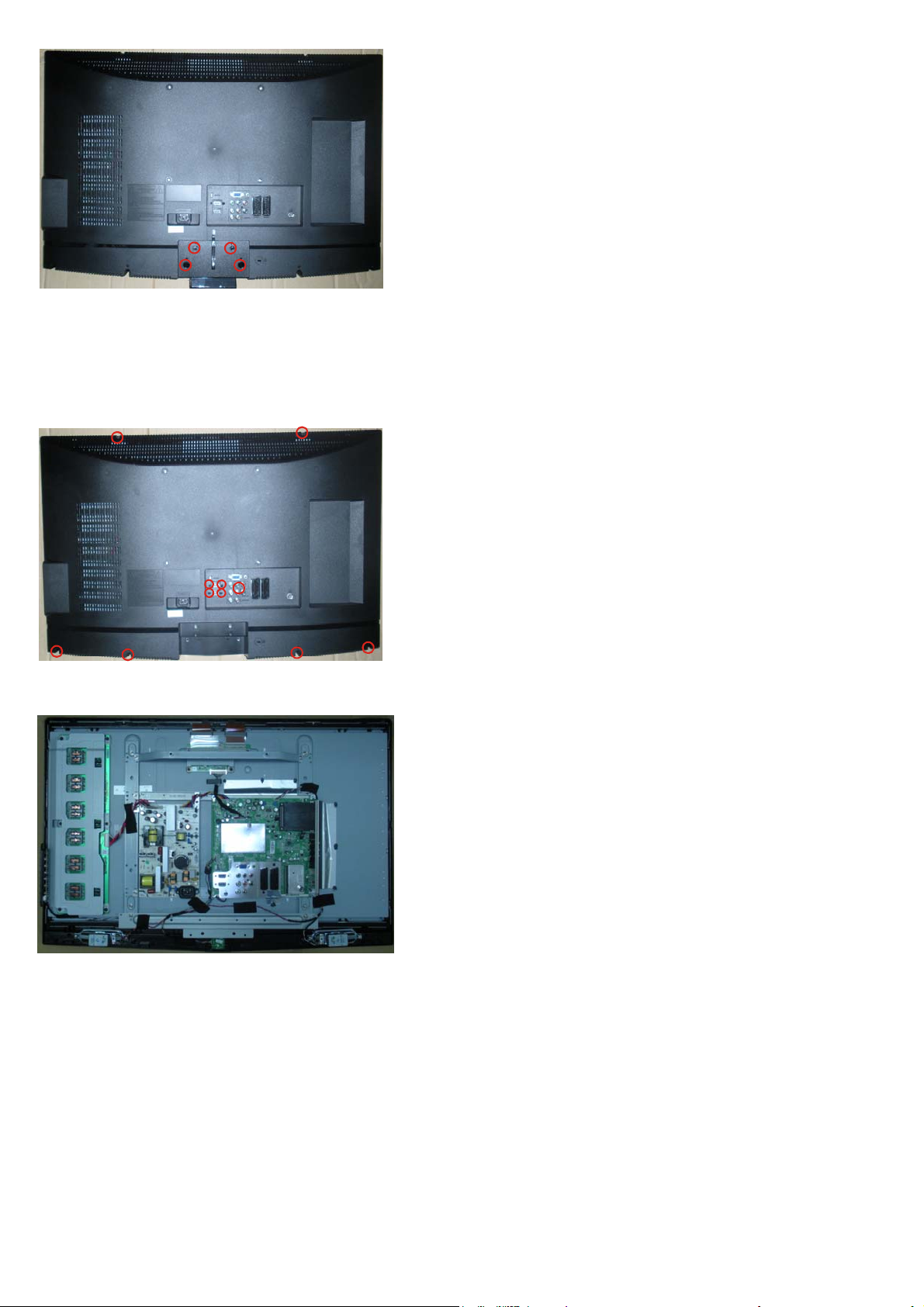

CHAPTER 2. REMOVING OF MAJOR PARTS

[2] REMOVING OF MAJOR PARTS(LC-32SH25)

1. Assy/Panel Removal

Notes: Please put your machine on soft material to avoid to scrape panel when you disassemble it.

Front view

Fig.1

Back view

LC-32SH25E

Fig.2

Step 1. Remove the Base Assy.

1. Remove the base as Fig.3.

Remove the 4 screws as Fig.3 and pull out the base as Fig.4

Fig.3

2008-03-14

11

Page 12

LC-32SH25E

Fig.4

2. Remove the 4 screws. Detach the BASE STAND as Fig.5.

Step 2. Remove the REAR COVER Assy.

1. Remove the 11 screws. Detach the REAR COVER as Fig.5.

Fig.5

Step 3. Remove the Main, Power, IR, Key board and the Speakers.

Fig.6

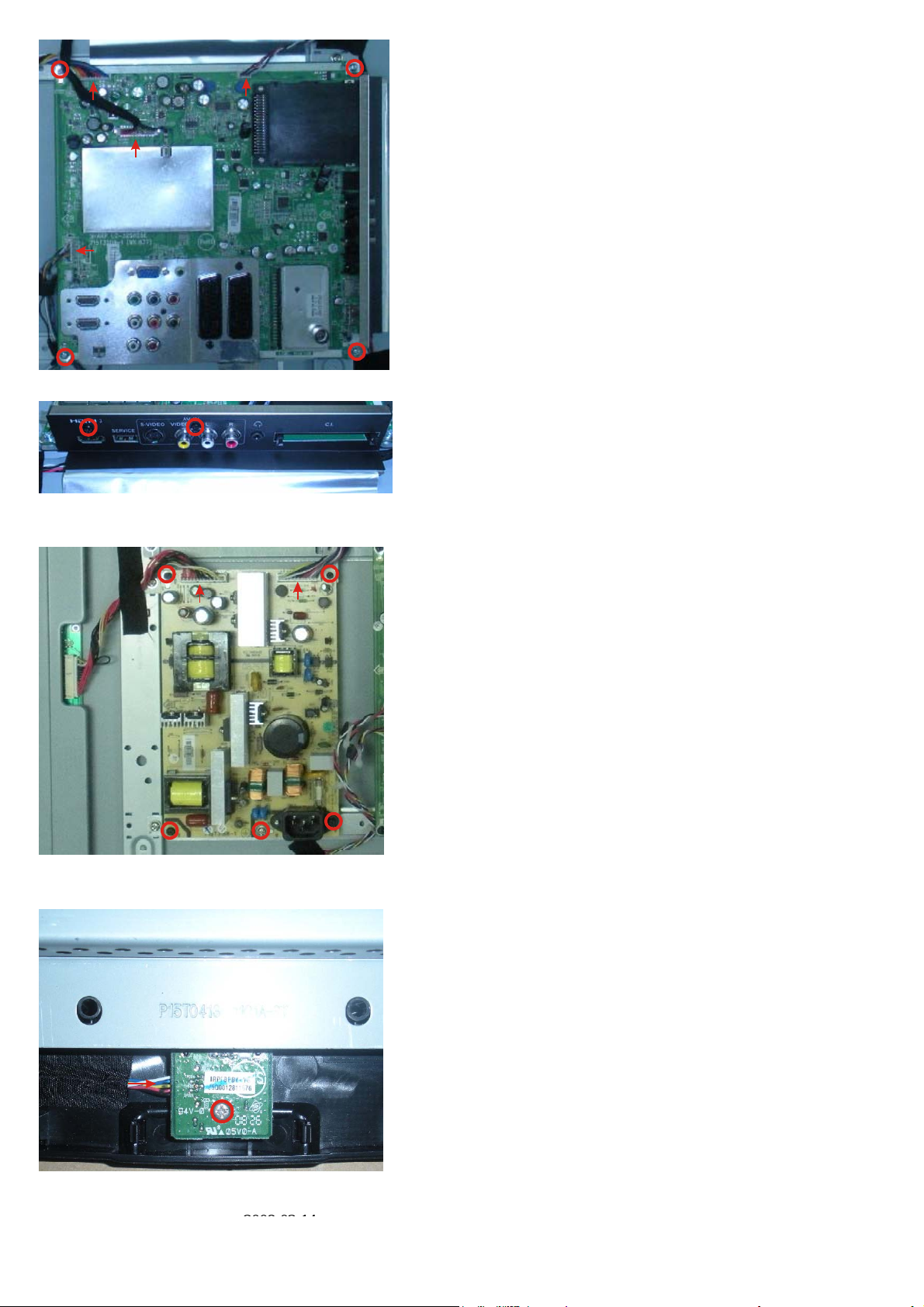

1. Remove the 6 screws and disconnect 4 cables. Detach the Main board as Fig.7 and Fig.8.

12

Page 13

Fig.7

LC-32SH25E

Fig.8

2. Remove the 5 screws and disconnect 2 cables. Detach the Power board as Fig.9.

Fig.9

3. Remove the 1 screw and disconnect 1 cable. Detach the IR board as Fig.10.

Fig.10

4. Disconnect 1 cable. Detach the Key board as Fig.11.

2008-03-14

13

Page 14

LC-32SH25E

Fig.11

5. Remove the 4 screws and disconnect 4 cables. Detach the Speakers as Fig.12 and Fig.13.

Fig.12 Fig.13

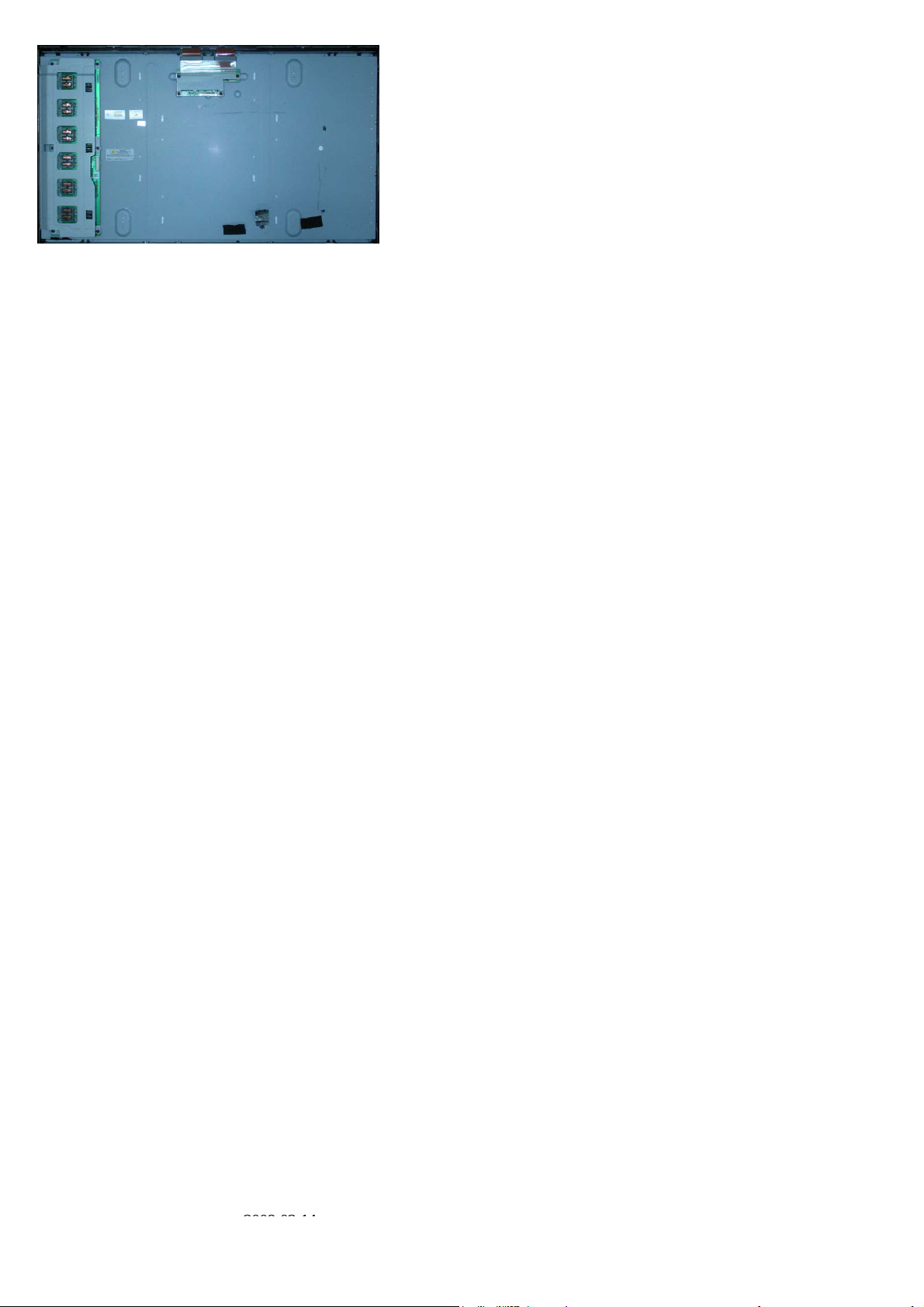

Step 4. Remove the Metal Frame.

1. Remove the 6 screws and disconnect 2 cables. Detach the Metal Frame as Fig.14.

Fig.14

Step 5. Remove the Bezel Assy.

1. Remove the Bezel Assy as Fig.15

Fig.15

2. The below picture is panel as Fig.16.

14

Page 15

Fig.16

2. Set Re-assembly

To re-assemble the whole set, execute all processes in reverse order.

Notes:

a. While re-assembling, make sure that all cables are placed and connected in their original position.

b. Pay special attention not to damage the EMC foams at the SSB shielding. Check that EMC foams are put

correctly on their places.

LC-32SH25E

2008-03-14

15

Page 16

LC-32SH25E

CHAPTER 3. ADJUSTMENT PROCEDURE

PROCEDURE

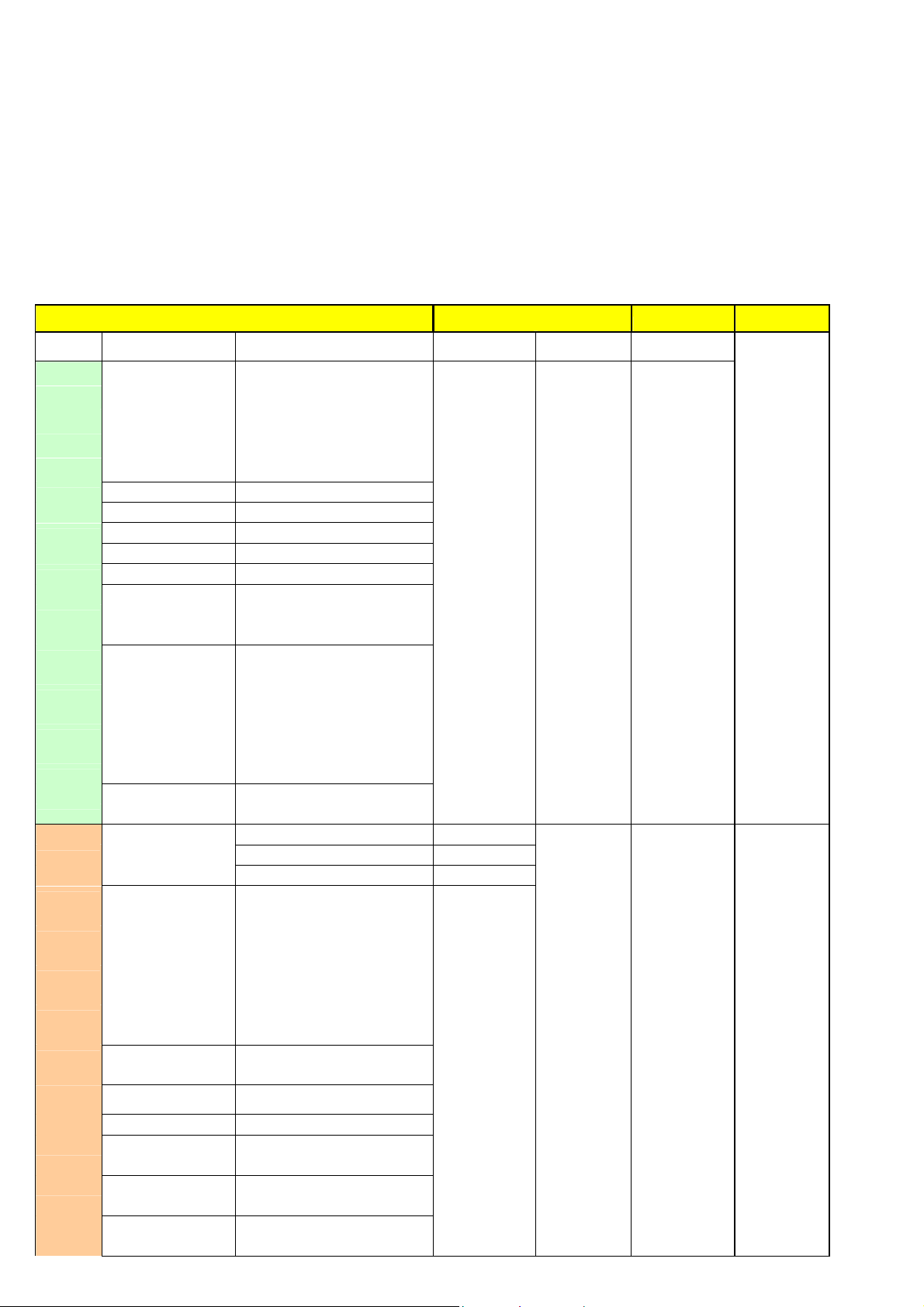

[1] ADJUSTMENT PROCEDURE

1. OSD Menu

OSD tree - As following

• TV

Digital Europe OSD tree-TV Remark

OSD Layer

1 2 3 4 5 6

Picture

Contrast slider

Brightness slider

Color slider

Sharpness slider

Tint

Color temperature

Cool

Picture format Automatic

Noise Reduction Off

On

Sound

Virtual surround Off

On

Dual I-II Dual I

Dual II

Mono/Stereo Mono

Stereo

Auto volume leveling Off

On

Smart Picture

Settings

Sound mode

Volume-visually

impaired

Audio language

User

Cinema

Sport

Vivid

Hi-bright

slider

Normal

Warm

Super zoom

4:3

Movie expand 14:9

Movie expand 16:9

Wide screen

Subtitle zoom

Bass slider

Treble slider

Balance slider

Off

Rock

Pop

Live

Dance

Techno

Classic

Soft

slider

Broadcsted list of audio languages

16

Page 17

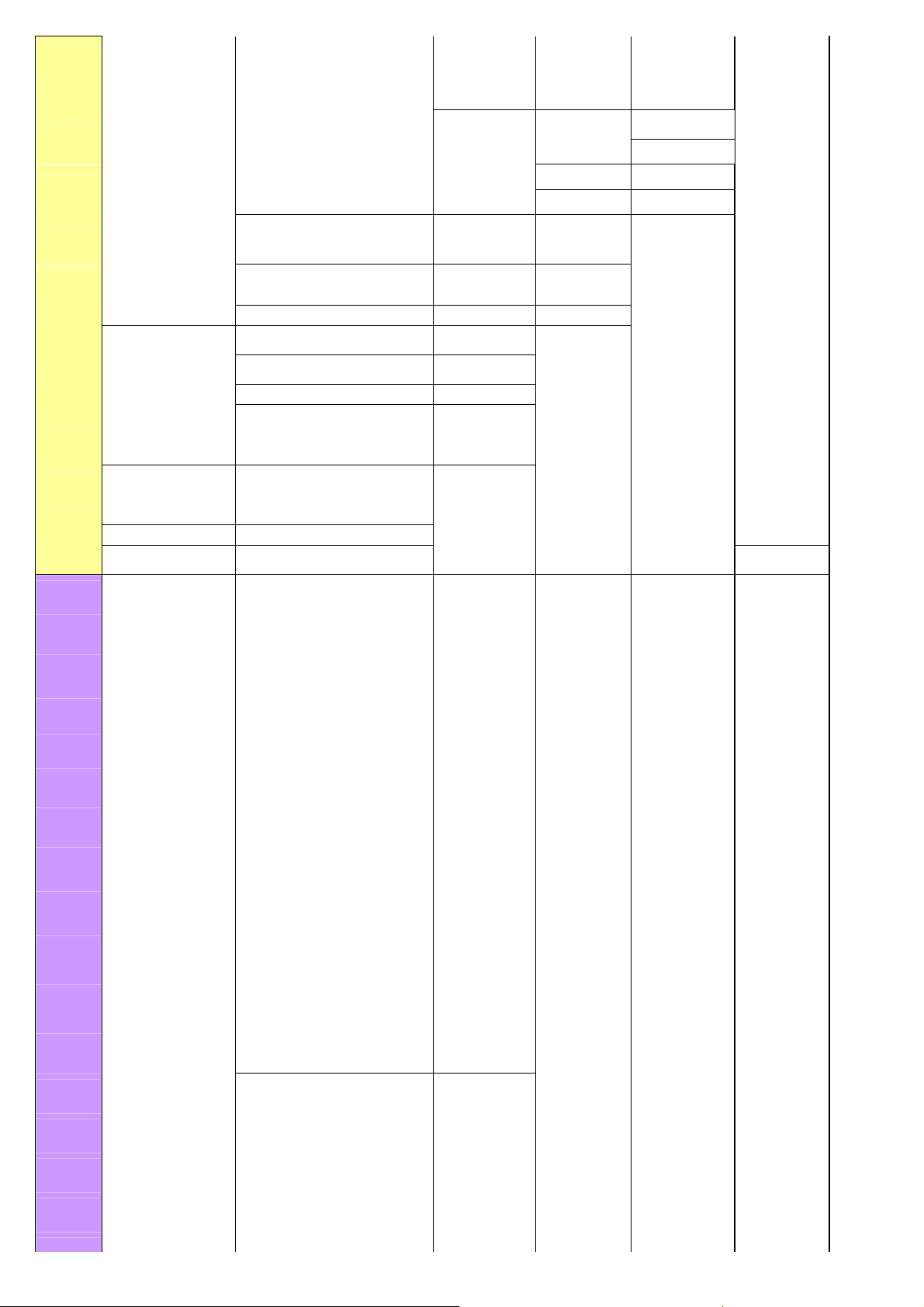

Features Timer

Stop time Timer Off

On

Sleeptimer slider

Auto lock Lock program

Change code

Clear all Start now

Parental rating None

Age 4~18

X-rated(Spain)

Subtitle Off

On

On during mute

Subtitle language Broadcsted list of audio languages

Common interface

Installation

Preferred audio language Basque

Bulgarian

Catalan

Croatian

Czech

Danish

Dutch

English

Finnish

Language

Clock

Start time

Menu language Български

Česky

Dansk

Deutsch

English

Hrvatski

Italiano

magyar

Nederlands

Norsk

Polski

Română

Svenska

Türkçe

Time zone

Time

Timer Off

On

(Channel

number…)

Please enter your

current PIN.

Ελληνικά

Español

Français

Português

Русский

Slovenský

Slovenščina

Srpski

Suomi

GMT +x:xx

GMT -x:xx

As broadcaster

Auto

synchronization

Date

Time

On

Off

20xx/xx/xx

xx:xx:xx

2008-03-14

(When CAM

inserted)

LC-32SH25E

17

Page 18

LC-32SH25E

French

Gaelic

Galician

German

Greek

Hungarian

Italian

Norwegian

Polish

Portuguese

Romanian

Russian

Serbian

Slovak

Slovenian

Spanish

Swedish

Turkish

Welsh

Preferred subtitle language Basque

Bulgarian

Catalan

Croatian

Czech

Danish

Dutch

English

Finnish

French

Gaelic

Galician

German

Greek

Hungarian

Italian

Norwegian

Polish

Portuguese

Romanian

Russian

Serbian

Slovak

Slovenian

Spanish

Swedish

Turkish

Welsh

Hearing impaired Off

On

Audio description Off

On

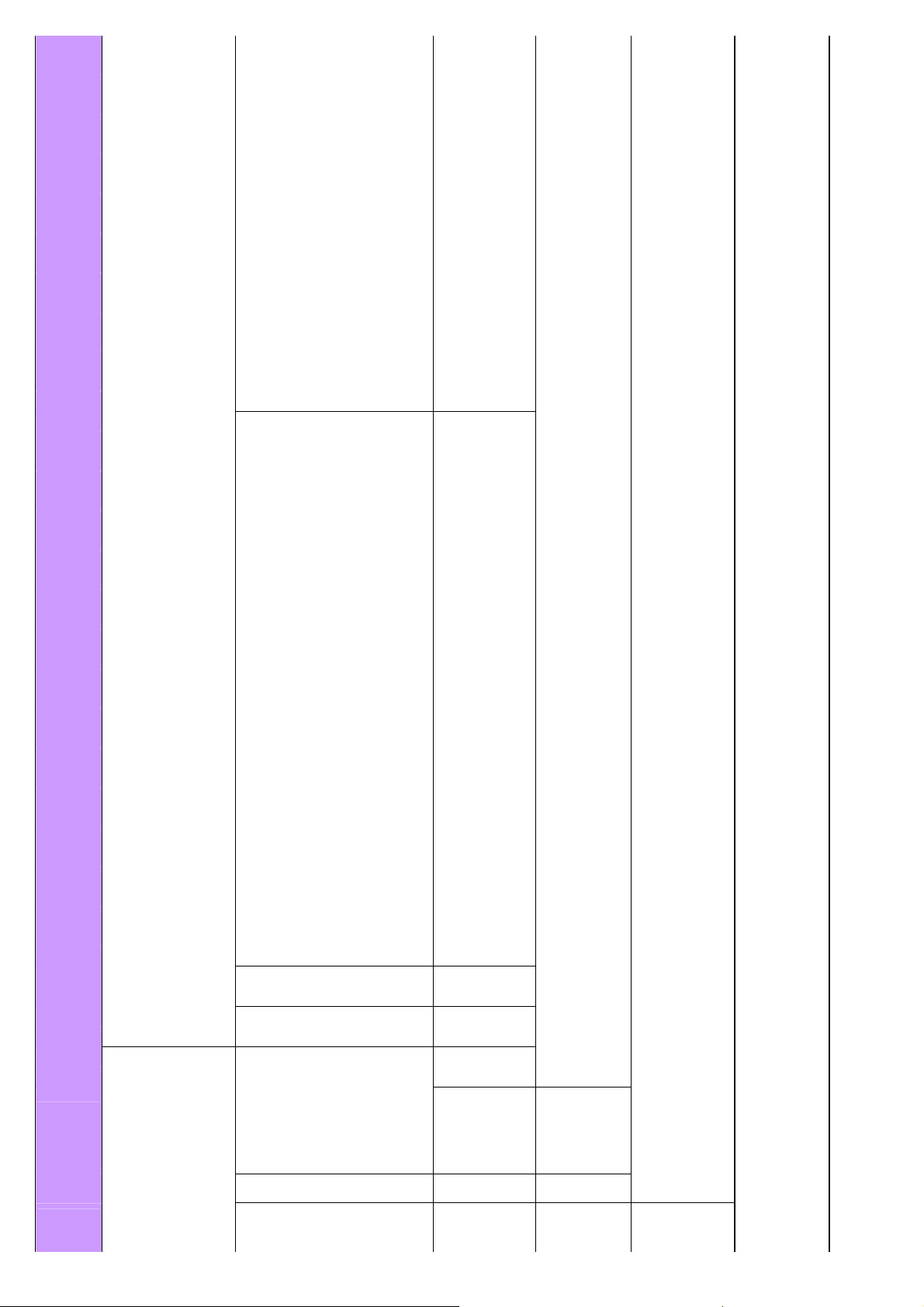

Country France

Channel installation Automatic installation Start now

Installation update Start now

Digital: Test reception 000.00 MHz Start Network name:

Status:

scanning…

Digital channels

found:

Analoguel

channels found:

Status:

scanning…

Signal

quality:Good/Poor

18

Page 19

Signal strength:

Analog: Manual installation System West EU

East EU

UK

France

Search 000 MHz

Fine tune 000.00 MHz

Rearrange

Source labels

SCART 1 DVD

SCART 2 Blu-ray

PC HDD/DVDR

HDMI 1 HD rec.

HDMI 2 Game

HDMI 3 VCR

PC

Digital STB

HD dig STB

Other

Decoder (Channel numbers…)

Current software info

Factory reset Start now

YPbPr

Side AV No label

Store current

channel Store

Store as new

channel Store

(Channel

numbers…)

Rename,reshuffle

• PC

LC-32SH25E

Digital Europe OSD tree-PC Remark

OSD Layer

1 2 3 4 5

Picture Contrast slider

Brightness slider

Colour Temperature Normal

Warm

Cool

Picture format

Sound Incredible surround Off

On

Picture

adjustment

Factory

reset Start now

Auto adjust

Manual adjust

Clock

Horizontal

Vertical

4:3

Wide screen

Start

Phase slider

slider

slider

slider

2008-03-14

19

Page 20

LC-32SH25E

2. Picture check

1) WHITE-D adjustment

General set-up :

Equipment Requirements: Minolta CA-210 or Equivalent Color analyzer Chroma 2250 or equivalent PC signal generator

input requirements:

Input Signal Type : PC VGA signal

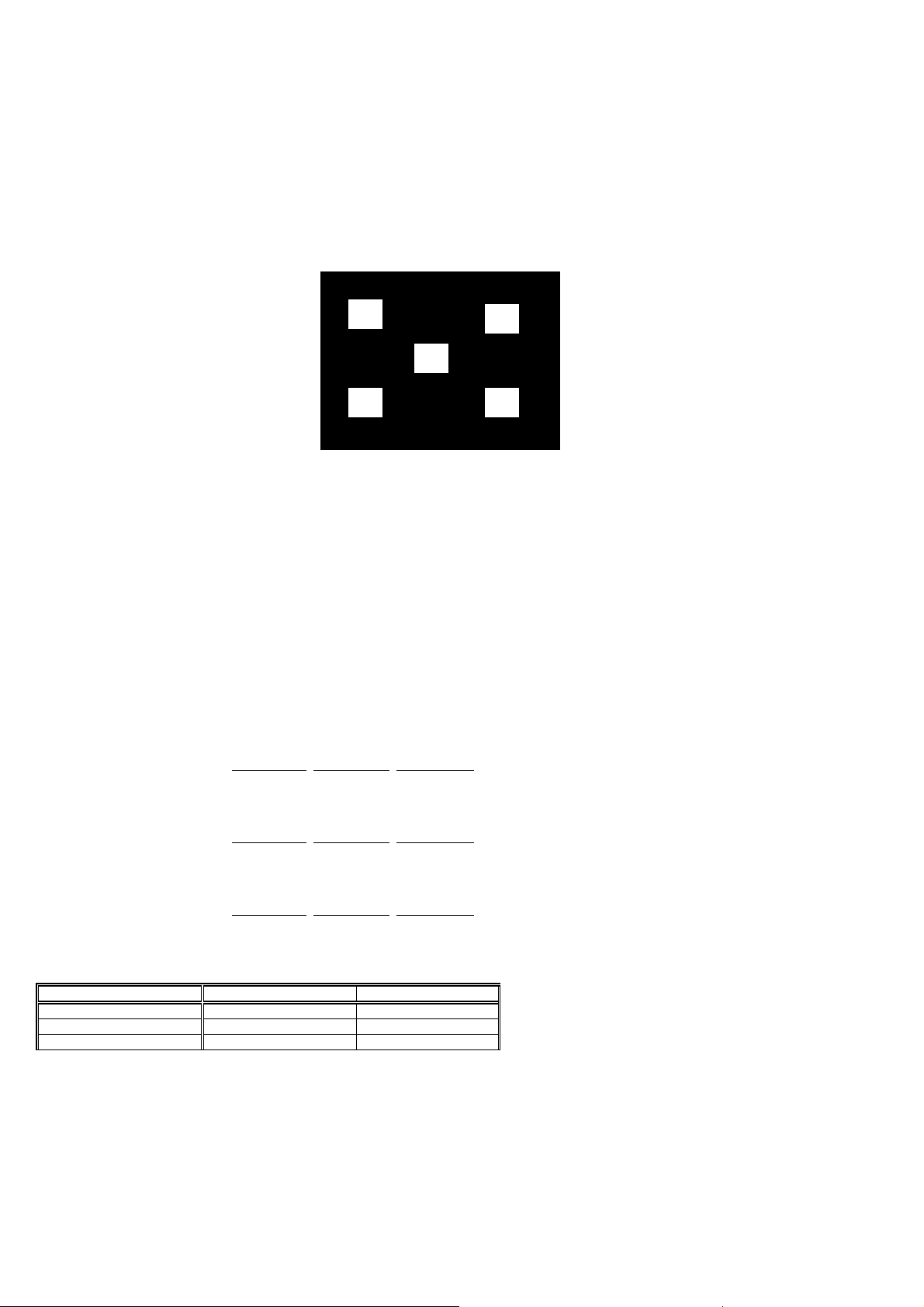

1280 X 1024/60Hz PC mode with ”5 white block” pattern. (see pattern-1)

Input Signal Strength : 0.7 Vp-p linear voltage.

Input Injection Point : PC D-SUB input

Pattern-1

Alignment method:

Initial Set-up:

1>. Select source as “PC”.

2>. Set Contrast = 50 (Sharp) and Brightness=50 (Sharp) , at normal menu mode.

3>. Apply “5 white block”(pattern-1) pattern b y VGA pattern generator.

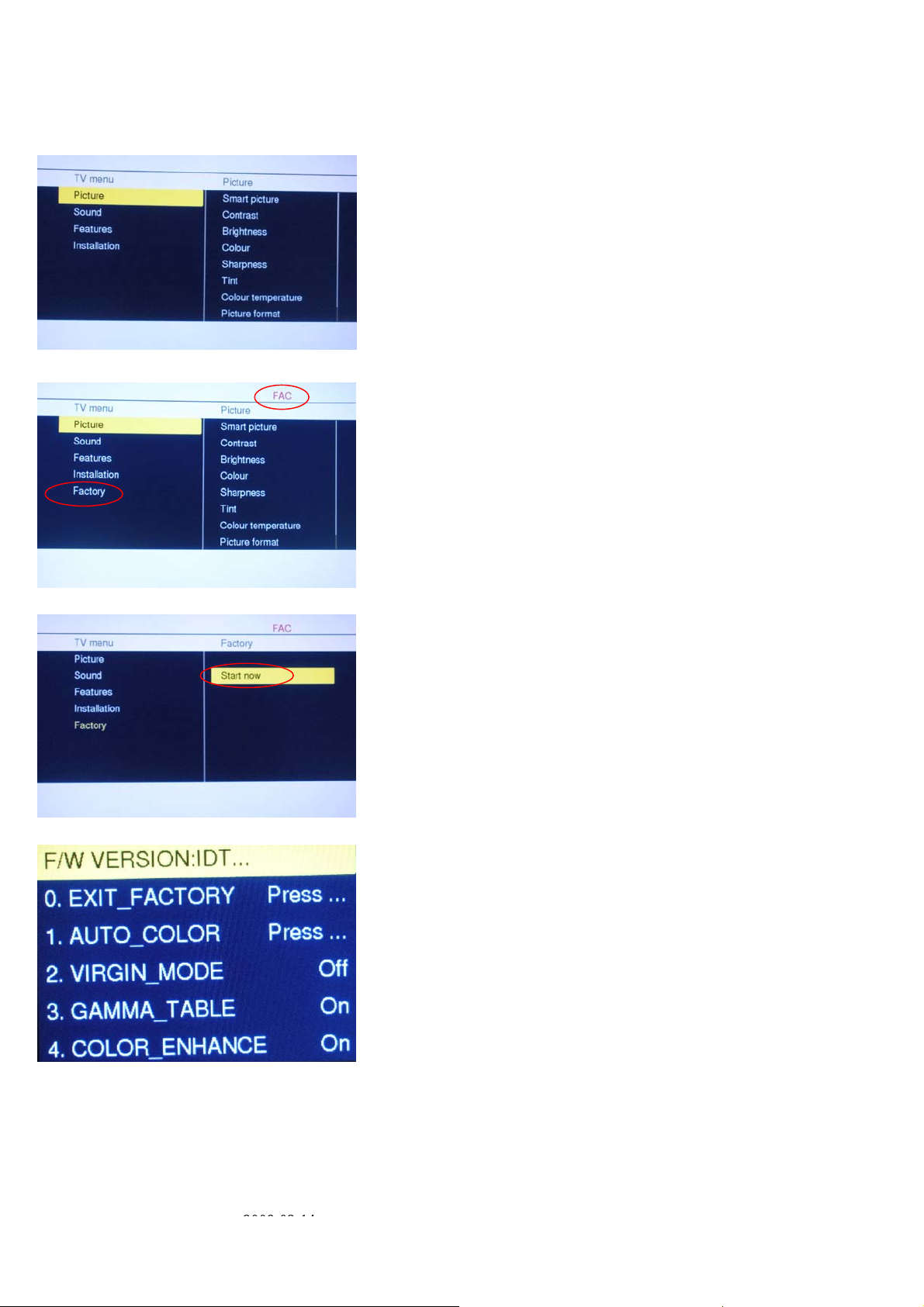

4>. Enter factory mode menu: press MENU + Numeric keys “062596” + MENU key (FAC mode menu). Then select “Factory” item.

Alignment:

1>. At FAC mode menu, select AUTO_COLOR item. Then press “OK” key to adjust ADC_GAIN_R, ADC_GAIN_G, ADC_GAIN_B and ADC_OFFSET_R,

ADC_OFFSET_G, ADC_OFFSET_B. Then store those values to NVM.

2>. Apply Flat80 pattern (80% white pattern).

3>. Set color temperature to “NORMAL”.

4>. At FAC mode menu, adjust the CLR TEMP R

store those values to NVM

5>. Set color temperature to “COOL”.

6>. At FAC mode menu, adjust the CLR TEMP R

those values to NVM

7>. Set color temperature to “WARM”.

8>. At FAC mode menu, adjust the CLR TEMP R

those values to NVM

Color temperature Normal/Warm/Cool (x, y) co-ordinates specification:

Picture Mode x y

Normal (9000oK) 0.289±0.003 0.291±0.003

Cool (12000oK) 0.272±0.003 0.277±0.003

Warm (6500oK) 0.314±0.003 0.319±0.003

Table 5: Reading with Minolta CA-210.

Note:

1>. Use Minolta CA-210 for color coordinates and luminance check.

2>. Befor adjusting,all colour analyzers (CA-210) should be coordinates with a same reference TV set.

3>. Luminance > 400 cd/m

2

in the center of the screen when Brightness control at 100; Contrast control at 100 for Sharp 32” panels.

, CLR TEMP G, CLR TEMP B values to meet “NORMAL” color coordinates specification below. Then

, CLR TEMP G, CLR TEMP B values to meet “COOL” color coordinates specification below. Then store

, CLR TEMP G, CLR TEMP B values to meet “WARM” color coordinates specification below. Then store

20

Page 21

LC-32SH25E

[2] SERVICE MODE

Enter factory mode menu: press MENU + Numeric keys “062596” + MENU key (FAC mode menu).Then select “Factory”

item.

2008-03-14

21

Page 22

LC-32SH25E

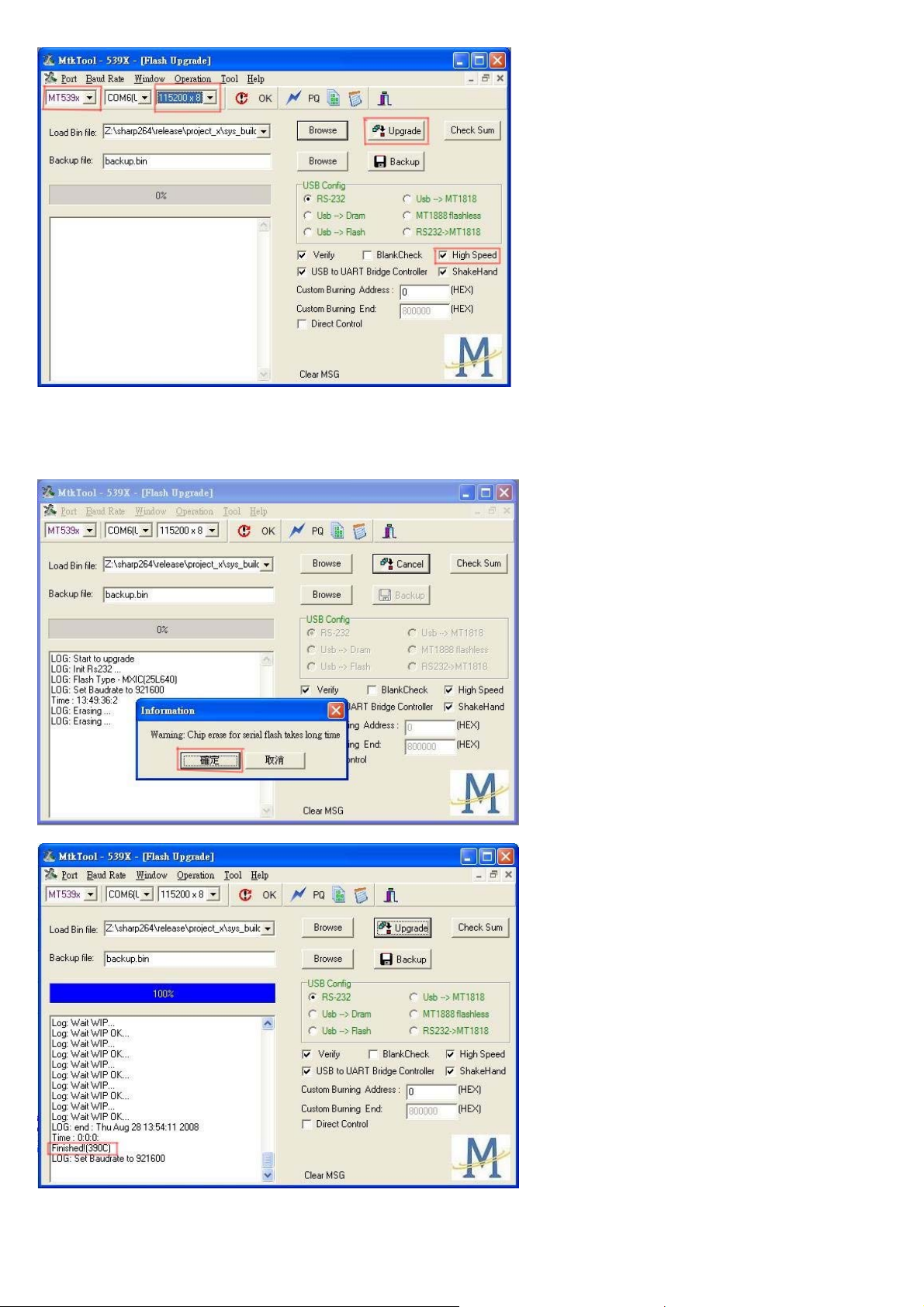

[3] SOFTWARE UPGRADE PROCEDURE

Environment Setup

Before you start to write the code, we suggest you setup the environment first. This chapter lists the setup requirements and guides you to setup and test

your development environment.

1.1 Connect to ISP Board to upgrade the software firmware.

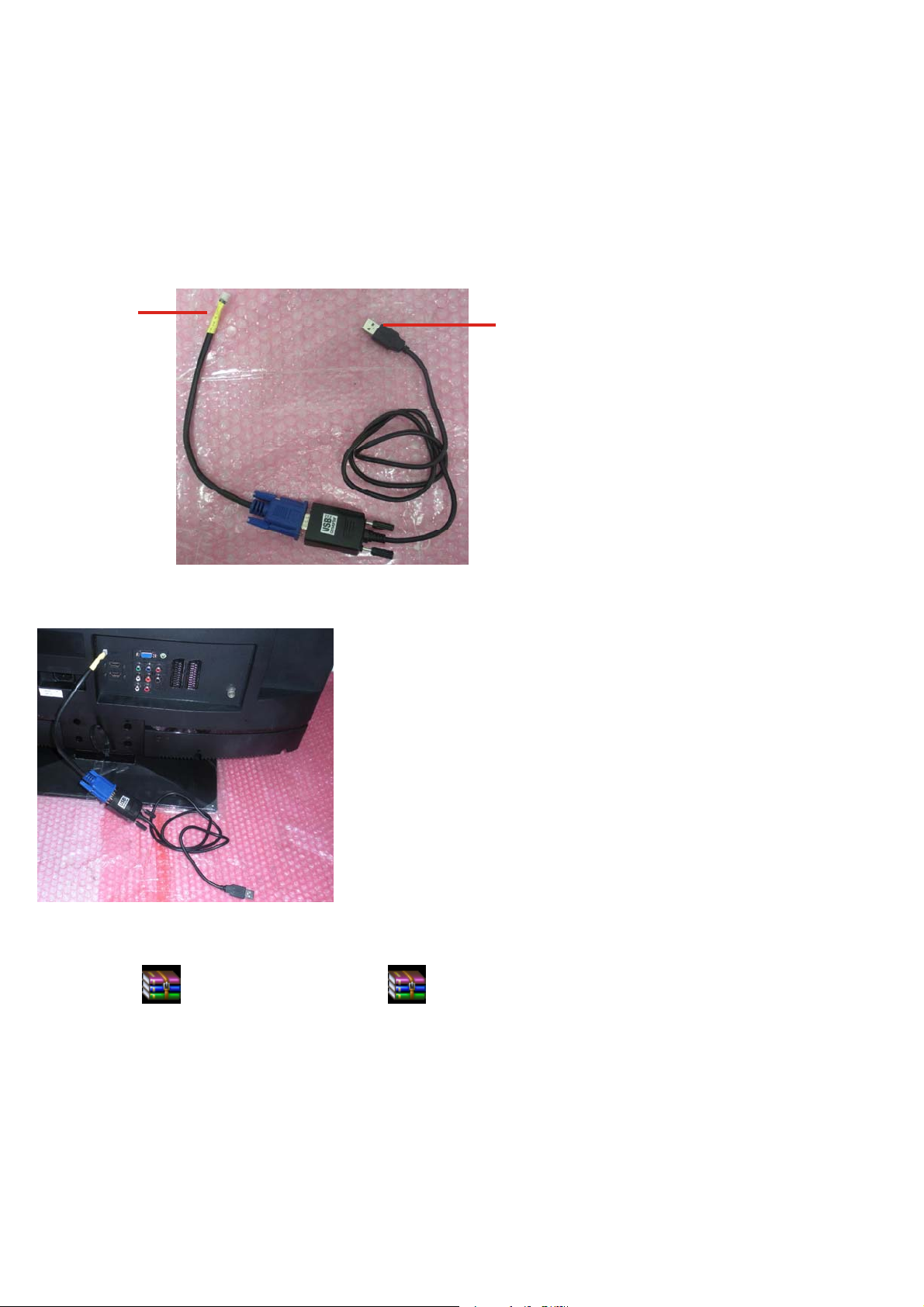

Use USB port connecting PC & MT536x Board via ISP board(Code number: 9JR9900000099(715G537XL2)).

To P C U S B port

Example: PC Connected to system board service port ( From USB to RS232).

To system board

service port

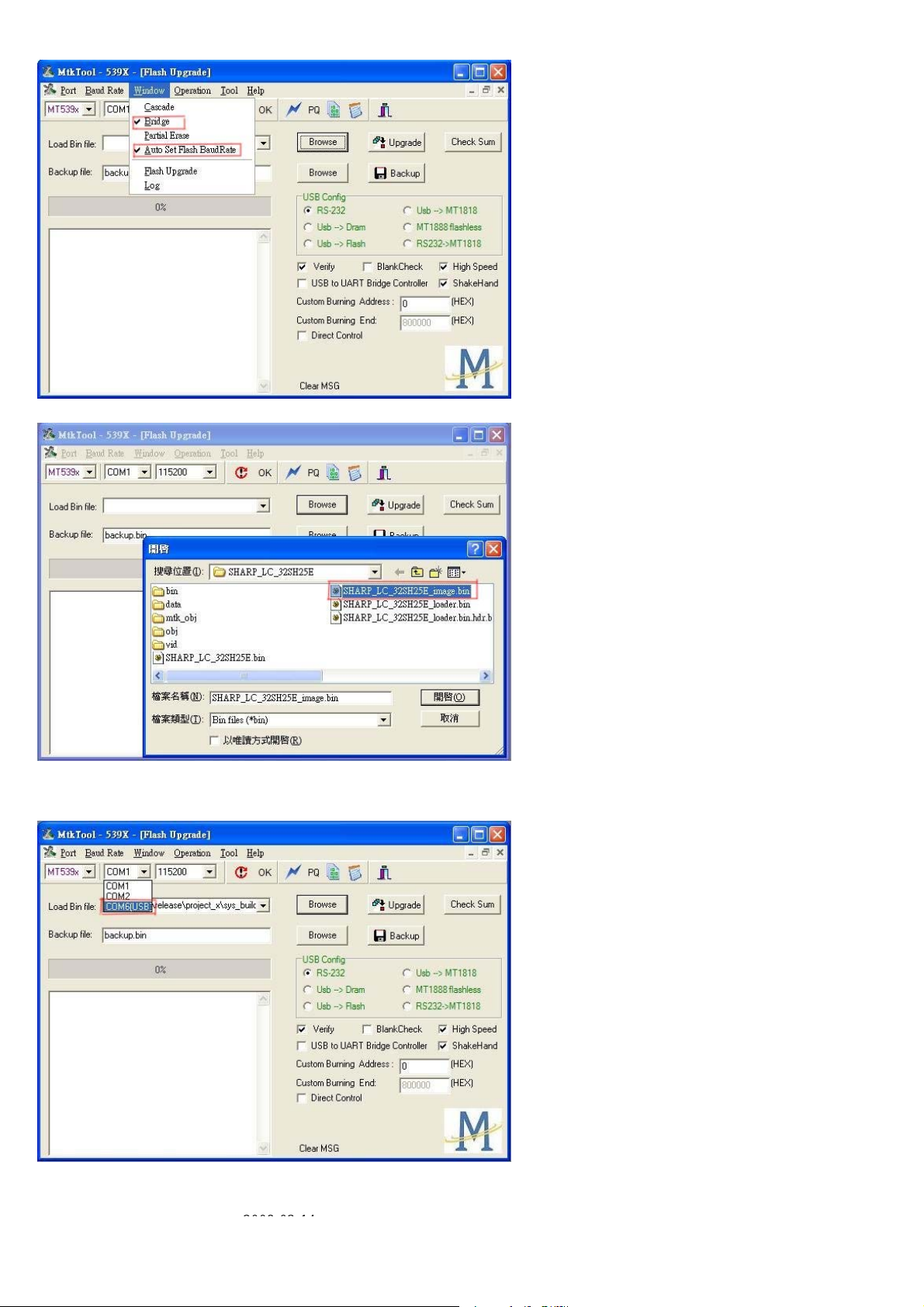

1. Unzip USB2COM Driver.zip to C:\

PL-2303 Driver Installer.rar

I. PL-2303 Driver Installer.exe

II. Double click exe file to install driver

2. Use MTK_Tools to download .bin file. (Ex: SHARP_LC_32SH25E__Vxx.xx_image.bin)

3. Make sure the Type “MTK539X” && “USB Baud Rate 115200x8” && Load the correct “bin” file.

Detailed operation sequence listed as follows.

Load .bin file on the Linux system or on the local Windows file system(Ex: SHARP_LC_32SH25E__Vxx.xx_image.bin) & Set Bridge & Auto Set Flash

BaudRate.

mtktool_mt5391.rar

22

Page 23

BaudRate.

LC-32SH25E

4. Set COM port resource that used by USB Port.

5. Set Baud rate 115200x8 & High speed item Enable. & MT539x.

2008-03-14

23

Page 24

LC-32SH25E

6. Push “Upgrade” button. (Waiting for “Finished!” message.)

Press “確定” button

7. Mainboard Power Off Æ On.

24

Page 25

1.2 Connect to TV USB port to upgrade the software firmware

Please follow the following step to upgrade the firmware.

1. Copy the software firmware (*.pkg) to USB Disk.

2. Modify the pkg’s filename to “upgrade.pkg”

3. Insert the USB Disk to TV USB port.

LC-32SH25E

4. TV AC power off -> AC power on

5. TV will upgrade by itself after detect the USB disk condition and the content of the pkg file.

Note: TV’s Green LED will flash during upgrade process

6. After finish upgrade process, TV will reboot by itself.

7. Remove USB disk from TV.

8. Check the software version is correct or not.

(Menu / setup / Current software info)

2008-03-14

25

Page 26

LC-32SH25E

A

p

f

A

CHAPTER 4. TROUBLESHOOTING TABLE

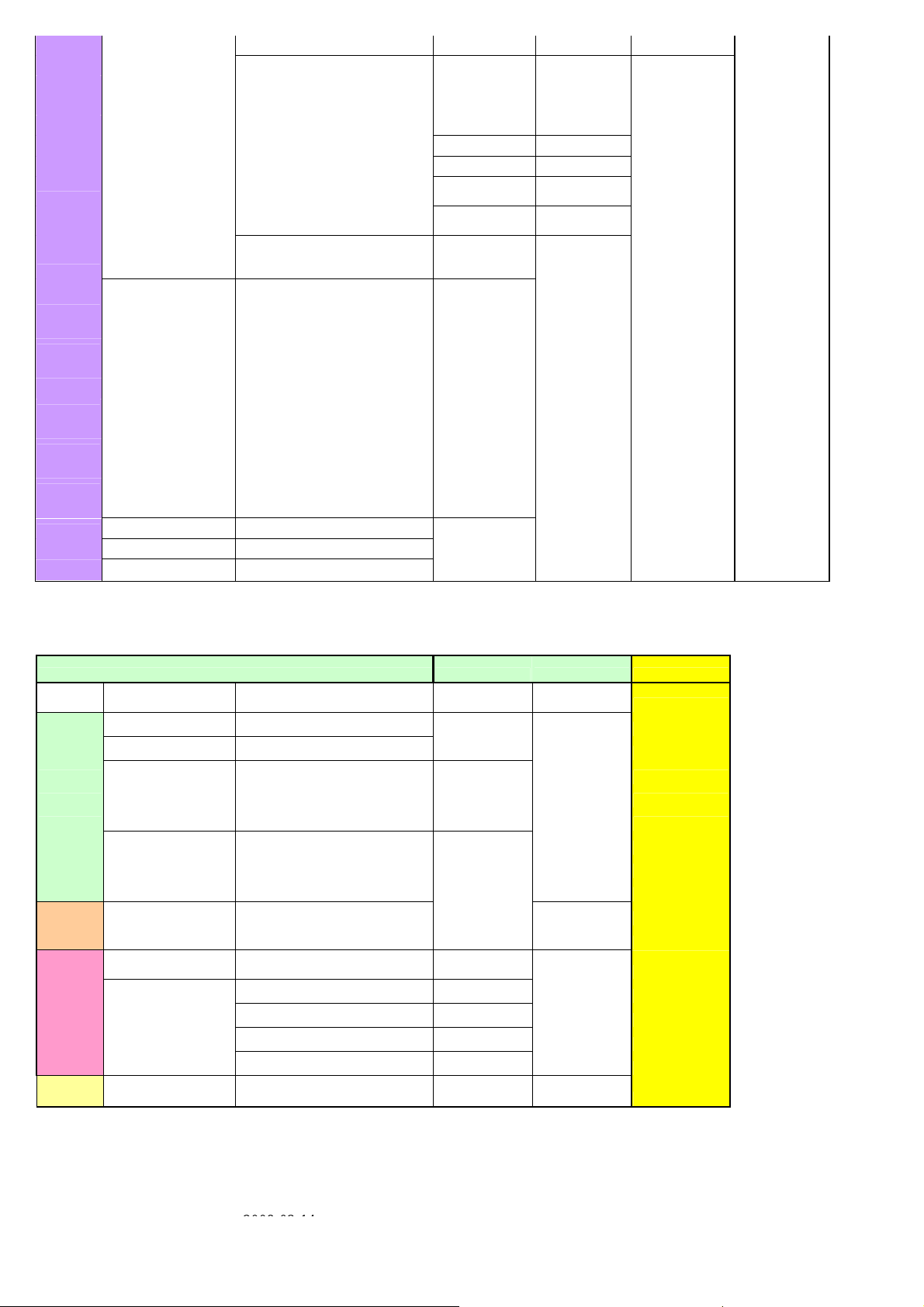

[1] TROUBLESHOOTING TABLE

Power unit operation check.

↓

re the power cord and harness in the unit properly connected?

LINE_FILTER_UNIT: ↓ YES

Is F901 normal?

POWER_UNIT

Is BD901 (+320V) output? (Set the main power SW to OFF.)

* When power on/off switch is on ‧‧‧ About +400V

↓YES

↓YES

Is a voltage of +5V applied to pin (11,12) of connector (CN902)?

(Set the main power SW to OFF.)

↓YES

re +24V output as for the power on/off switch when it is on?

↓YES

Similarly, is +12V output as for the power on/off switch when it is

on?

NO

NO

NO

NO

NO

NO

Connect the power cord and harness properl y, and turn on the

ower.

LINE_FILTER_UNIT:

Isn't L901,L902,RV901,C903,C904,C901,C902, etc. out o

order? Moreover, whether the short-circuit with the

circumference circuit is checked.

POWER_UNIT:

BD901, RV902, IC951, etc. out of order?

Moreover, whether the short-circuit with the circumference circuit

is checked.

Does the PFC circuit operate normally?

(L906, Q901, D902, D903, IC901 and etc. And, the circuit around

the protection circuit etc. is checked.)

Does the switching circuit operate normally?

Check circuit around the primary side (T901, IC931, Q931,

ZD981, ZD930, D980, D981, ZD981, etc.), t he secondary side

(D935, L980, etc.), the AC_DET circuit (ZD982, IC932, IC982,

Q992, Q993, etc.), and the protection circuit.

Does the inverter circuit operate normally?

Check circuit around the primary side (T902,Q951,Q952,IC951,

D951,D952, etc.), the secondary side (D955, L971, ZD967,

IC952, IC953, etc.), the STANDBY circuit (Q988, etc.), and the

protection circuit.

Check +12V circuit of D956, L931, etc.

26

Page 27

The sound is not emitted from the speaker though the picture has come out.

↓

No sound output in all modes?

TEREMINAL UNIT: ↓

Is the audio signal output of pin (H26) (AL0) and pin (H25) (AR0) of

IC U400 normal?

NO

↓YES

Is the audio signal output of pin (17) (PGA2OUTL) and pin (18)

(PGA2OUTR) of IC U605 normal?

NO

↓YES

Is audio signal input to pin (2)(L), pin (14)(R) of IC U600 (AMP)?

NO

↓YES

Is MUTE circuit [AMP_MUTE_LINE, POWERUP_LINE] normal?

NO

↓YES

Is the audio signal output of pin (3, 4) (L-ch) and pin (1, 2) (R-ch) of

CN600 (AOUDIO-CONNECTOR) normal?

NO

↓YES

Check Speaker Box (right and left) and wire harness.

No sound (during the reception of TV(ANALOG) broadcasting)

↓

Does not the sound go out though the picture has come out when UHF/VHF is received?

TEREMINAL UNIT: ↓

Is the SIF signal output from pin (11) of TUNER (TU200)?

NO

↓YES

Is the SIF signal sent to pin (AB25) and pin (AB26) of IC U400?

NO

↓YES

Refer to “No sound output in all modes”.

2008-03-14

27

LC-32SH25E

Check IC U400 and its peripheral circuits.

Check IC U605 and its peripheral circuits.

Check the line between IC U605 and IC U600.

Check the AMP_MUTE_LINE and POWERUP_LINE. (Q600,

etc.)

Check IC U600 and its peripheral circuits.

Check the tuner and its peripheral circuits. Replace as required.

Check IC U400 its peripheral circuits.

Page 28

LC-32SH25E

f

f

No sound (during the reception of TV (DIGITAL) broadcasting)

↓

Does not the sound go out though the picture has come out when DTV is received?

MAIN UNIT: ↓

Is the DIF signal output from pin (17) and pin (19) of TUNER

(TU200)?

NO

↓YES

Is the DIF signal sent to pin (R25) and pin (T25) of IC U400?

NO

↓YES

Refer to “No sound output in all modes”.

No sound from external input devices (1)

↓

Does not the sound of the audio signal input to SCART1 go out?

Does not the sound of the audio signal input to SCART2 go out?

TEREMINAL UNIT: ↓

Is the audio signal properly sent to pin (6) (SCT1_AUL_IN) and pin

(2) (SCT1_AUR_IN) of SCART1(CN500)?

Is the audio signal properly sent to pin (6) (SCT2_AUL_IN) and pin

(2) (SCT2_AUR_IN) of SCART2(CN501)?

NO

NO

↓YES

Is the audio signal properly sent to pin (44) (SC1_LIN) and pin ( 43)

(SC1_RIN) of IC U605?

Is the audio signal properly sent to pin (46) (SC2_LIN) and pin ( 45)

(SC2_RIN) of IC U605?

NO

NO

↓YES

Refer to “No sound output in all modes”.

No sound from external input devices (2)

↓

Does not the sound of the audio signal input to AV1(Component) go out?

MAIN UNIT: ↓

Is the audio signal properly sent to pin (2) (AV1_AudioLIN) and pin

(4)(AV1_AudioRIN) of CN553?

NO

↓YES

Is the audio signal properly sent to pin (50) (AV1_LIN) and pin (49)

(AV1_RIN) of IC U605?

NO

↓YES

Refer to “No sound output in all modes”.

Check the tuner and its peripheral circuits. Replace as required.

Check IC U400 its peripheral circuits.

Check the setting of an external input device that connects o

CN500.

Check the setting of an external input device that connects o

CN501.

Check the line between CN500 and IC U605.

Check the line between CN501 and IC U605.

Check the connection to CN553 and the external input device.

Check the line between CN553 and IC U605.

28

Page 29

(

No sound from external input devices (3)

↓

Does not the sound of the audio signal input to AV3(Composite/Y/C) go out?

MAIN UNIT: ↓

Is the audio signal properly sent to pin (4) (AV3_AudioLIN) and pin

(6) (AV3_AudioRIN) of CN650?

↓YES

Is the audio signal properly sent to pin (52) (SIDE_LIN) and pin (51)

(SIDE_RIN) of IC U605?

↓YES

Refer to “No sound output in all modes”.

No sound from external input devices (4)

↓

Does not the sound of the audio signal input to VGA go out?

MAIN UNIT: ↓

Is the audio signal properly sent to pin (2) (VGA_AudioLI N) and pin

(3) (VGA_AudioRIN) of CN555?

↓YES

Is the audio signal properly sent to pin (48) (VGA_LIN) an d pin (47)

VGA_RIN) of IC U605?

↓YES

Refer to “No sound output in all modes”.

No sound from external input devices (5)

↓

Does not the sound of the audio signal input to HDMI1/2/3 go out?

↓

Is picture of the signal input from HDMI1/2/3 displayed?

↓YES

Refer to “No sound output in all modes”.

NO

NO

NO

NO

NO

LC-32SH25E

Check the connection to CN650 and the external input device.

Check the line between CN650 and IC U605.

Check the connection to CN555 and the external input device.

Check the line between CN555 and IC U605.

Refer to “Does not the picture of the HDMI signal input to

HDMI1/2/3 go out?”.

2008-03-14

29

Page 30

LC-32SH25E

The audio signal is not output (1)

↓

The audio signal of UHF/VHF is not output from SCART1.

TEREMINAL UNIT: ↓

Is audio signal output from IC U602 sent to pin (3)(SCT1_AULOUT) and pin(1)(SCT1_AUR-OUT) of SCART1(CN500)?

↓NO

Is audio signal output from IC U400 sent to pin (2)(LRCLK) and pin

(3)(DIN) and pin (4)(BCLK) and pin(13)(MCLK) of IC U602?

↓NO

Check IC U400 and its peripheral circuits.

The audio signal is not output (2)

↓

The audio signal of UHF/VHF/MONITOR is not output from SCART2.

TEREMINAL UNIT: ↓

Is audio signal output from IC U605 sent to

pin(3)(SCT2_AUL_OUT) and pin(1)(SCT2_AUR_OUT) of

↓NO

Is the audio signal output from IC U400 pin(K26) (AL2) and pin(J24)

(AR2) sent to pin(26)(INPUT1L) and pin(25)(INPUT1R) of IC U605?

↓NO

Check IC U400 and its peripheral circuits.

The audio signal is not output (3)

↓

No audio signal output from LINE_AUDIO_OUTPUT terminal.

TEREMINAL UNIT: ↓

Is audio signal output from IC U605 sent to pin(2)(L_OUT) and pin

(4)(R_OUT) of LINE_AUDIO_OUT connector(CN556)?

↓NO

Is the audio signal output from IC U400 pin(K26) (AL2) and pin(J24)

(AR2) sent to pin(26)(INPUT1L) and pin(25)(INPUT1R) of IC U605?

↓NO

Check IC U400 and its peripheral circuits.

YES

YES

YES

YES

YES

YES

Check the connection to SCART1 and external devices.

Check the line between IC U400 and IC U602.

Check the connection to SCART2 and external devices.

Check the line between IC U400 and IC U605.

Check the connection to LINE_AUDIO_OUT and external

devices.

Check the line between IC U400 and IC U605.

30

Page 31

f

The audio signal is not output (4)

↓

No audio signal output from SPDIF_OUTPUT terminal.

TEREMINAL UNIT: ↓

Is ASPDIF audio signal output from pin (E26) of IC U400 to pin (6)

of connector CN553?

↓NO

Check IC U400 and its peripheral circuits.

The audio signal is not output (5)

↓

No sound from HEADPHONE_OUTPUT terminal.

MINI AV_UNIT: ↓

Is the HPDET signal input into pin (AA5) of IC U400 from pin (7) o

a headphone terminal (CN602)?

↓YES

Is the audio signal output from IC U605 to pin(2) (HPOU TL) a nd pi n

(3) (HPOUTR) of headphone terminal CN602?

↓YES

Is the audio signal output from IC U400 pin(J26)(AL1) and pin(J25)

(AR1) sent to pin(24)(INPUT0L) and pin(23)(INPUT0R) of IC U605?

↓YES

Check IC U400 and its peripheral circuits.

YES

NO

NO

NO

LC-32SH25E

Check the connection to SPDIF_OUT and external devices.

Check the connection to CN602 and external headphone is plug

in well.

Check the line between IC U605 and CN602.

Check the line between IC U400 and IC U605.

2008-03-14

31

Page 32

LC-32SH25E

No picture on the display (1)

↓

The picture doesn't appear in all modes.

MAIN UNIT: ↓

Is LVDS signal output from 1st_channel and 2nd_channel of IC U400 in each mode?

(A0N/A0P),(A1N/A1P),(A2N/A2P),(A3N/A3P),(CLK1N/CLK1P)

↓NO

YES

Is the above-mentioned LVDS signals output to connector CN750?

NO

↓YES

Is LCD controller's control signal normal?

NO

PANEL_UNIT:

Similarly, is the LVDS signal input to connector of the panel

↓YES

NO

↓YES

Check the panel module.

No picture on the display (2)

↓

Does not the picture come out when VHF/UHF is received?

TERMINAL UNIT: ↓

Is TUNER_CVBS signal output from pin (21) of TUNER (TU200)?

NO

MAIN_UNIT: ↓YES

Is picture signal input from pin (21) of TUNER (TU200) to pin

(AB24) of IC U400?

NO

↓YES

Refer to “The picture doesn't appear in all modes.”

Check IC U400 and its peripheral control circuits.

Check the line between IC U400 and CN750.

Control signals BRIGHT_ADJ, INVERTER_ON_OFF,

PANEL_VCC_ON/OFF, and it peels off and whether normality is

checked.

Wire harness is checked.

Check whether I2C is normally accessed between TU200 and IC

U400.

Check the line between IC U400 and TU200.

32

Page 33

No picture on the display (3)

↓

Does not the picture come out when DTV is received?

TERMINAL UNIT: ↓

Is the voltage of regulation for a TUNER circuit and the power

supply terminal of IC U400 supplied?

↓YES

Is IF signal output from pin (17), (19) of TUNER (TU200) to pin

(R25), pin (T25) of IC U400 ?

↓YES

Is MPEG data (TS0INDATA0, TS0INSYNC, TS0INCLK,

TS0INVALID) from IC U400 are output to pin (9), pin (7), pin (6), pin

(8) of a IC U401?

MAIN_UNIT: ↓YES

Do X300 (60.00MHz)/ X400 (27MHz) oscillate?

↓YES

Is MPEG data (TS_DATAO, TS_CKO, TS_VALIDO, TS_SYNCO)

from IC U401 are output to pin (B21/A21/B20/C21) of a IC U400?

↓YES

Refer to “The picture doesn't appear in all modes.”

LC-32SH25E

NO

NO

NO

NO

NO

Each power supply circuit is checked.

Check the tuner, IC U400 and their peripher al circuits. Replace

as required.

is communication control carried out between pin (6)(SCL),

pin(9)(SDA), of TU200, and pin(F24)(TUNER_SCL1), pin

(F25)(TUNER_SDA1), of IC U400?

Check X300/ X400 and its peripheral circuits.

Is the control signal between IC U401 and IC U400 normal?

(RESET_CI, etc.).

2008-03-14

33

Page 34

LC-32SH25E

f

f

f

<External input SCART1, SCART2>No picture on the display (4)

↓

Does not the picture of the CVBS signal input to SCART1 go out?

Does not the picture of the CVBS signal input to SCART2 go out?

TERMINAL UNIT: ↓

Is CVBS signal sent to pin (20) of SCART1 (CN500)?

Is CVBS signal sent to pin (20) of SCART2 (CN501)?

MAIN_UNIT:

Is CVBS signal sent to pin (AE24) of IC U400?

Is CVBS signal sent to pin (AE26) of IC U400?

Refer to “The picture doesn't appear in all modes.”

↓YES

↓YES

<External input SCART1>No pict u re on the di sp lay (5)

↓

Does not the picture of the R/G/B video signal input to SCART1 go out?

TERMINAL UNIT: ↓

Is RGB signal sent to pin (15)/R, (11)/G, (7)/B, of SCART1

(CN500)?

MAIN_UNIT: ↓YES

Is RGB signal sent to pin (AF24)/R, (AD24)/G, (AD23)/B of IC

U400?

Refer to “The picture doesn't appear in all modes.”

↓YES

NO

NO

NO

NO

NO

NO

Check the setting of an external input device that connects o

CN500.

Check the setting of an external input device that connects o

CN501.

Check the line between IC U400 and CN500.

Check the line between IC U400 and CN501.

Check the setting of an external input device that connects o

CN500.

Check the line between IC U400 and CN500.

34

Page 35

f

f

f

f

<External input SCART1, SCART2>No picture on the display (6)

↓

Does not the picture of the Y/C signal input to SCART1 go out?

Does not the picture of the Y/C signal input to SCART2 go out?

TERMINAL UNIT: ↓

Is Y/C signal sent to pin (20) and (15) of SCART1 (CN500)?

Is Y/C signal sent to pin (20) and (15) of SCART2 (CN501)?

MAIN_UNIT:

Is Y/C signal sent to pin (AE24)/Y, (AF25)/C of IC U400?

Is Y/C signal sent to pin (AE26)/Y, (AE25)/C of IC U400?

Refer to “The picture doesn't appear in all modes.”

↓YES

↓YES

<External input AV3(Composite)>No picture on the display (7)

NO

NO

NO

NO

↓

Does not the picture of the composite video signal input to AV3(Composite) go out?

TERMINAL UNIT: ↓

Is CVBS signal sent to pin (2) of AV3 (CN650) ?

NO

MAIN_UNIT: ↓YES

Is CVBS signal sent to pin (AC24) of IC U400?

Refer to “The picture doesn't appear in all modes.”

↓YES

<External input AV3(Y/C)>No picture on the display (8)

NO

↓

Does not the picture of the Y/C video signal input to AV3(Y/C) go out?

TERMINAL UNIT: ↓

Is Y/C signal sent to pin (8)/Y, (7)/C of AV3 (CN650) ?

NO

MAIN_UNIT: ↓YES

Is Y/C signal sent to pin (AD26)/Y, (AD25)/C of IC U400?

Refer to “The picture doesn't appear in all modes.”

↓YES

NO

LC-32SH25E

Check the setting of an external input device that connects o

CN500.

Check the setting of an external input device that connects o

CN501.

Check the line between IC U400 and CN500.

Check the line between IC U400 and CN501.

Check the setting of an external input device that connects o

CN650.

Check the line between IC U400 and CN650.

Check the setting of an external input device that connects o

CN650.

Check the line between IC U400 and CN650.

2008-03-14

35

Page 36

LC-32SH25E

A

, (

A

A

<External input HDMI1>No picture on the display (9)

↓

Does not the picture of the HDMI signal input to HDMI1 go out?

MINI AV_UNIT: ↓

Is the HOT_PLUG detection function of pin (19) of a HDMI terminal

(CN702) normal?

YES

re EDID data pin (6)(SCL) of IC U708 (EEPROM), pin (5)(SDA)

accessed, and is it read from pin (15), pin (16) of a HDMI

terminal(CN702)?

Is TMDS signal input into pin (AF10, AE10)/RX2±, (AF9, AE9)/RX1

AF8, AE8)/RX0±, (AF7, AE7)/RXC± of IC U400?

±

Refer to “The picture doesn't appear in all modes.”

YES

↓YES

<External input HDMI2>No picture on the display (10)

↓

Does not the picture of the HDMI signal input to HDMI2 go out?

MINI AV_UNIT: ↓

Is the HOT_PLUG detection function of pin (19) of a HDMI terminal

(CN700) normal?

YES

re EDID data pin (6)(SCL) of IC U701 (EEPROM), pin (5)(SDA)

accessed, and is it read from pin (15), (16) of a HDMI

terminal(CN700)?

Is TMDS signal input into pin(AF14, AE14)/RX2±, (AF13,

E13)/RX1±, (AF12, AE12)/RX0±, (AF11, AE11)/RXC± of IC U400?

Refer to “The picture doesn't appear in all modes.”

YES

↓YES

NO

NO

NO

NO

NO

NO

Check the line between pin (AC4) of IC U400 and CN702.

↓

Check the connection and setup with the external HDMI devices.

Is access possible in the re-writing or exchange of EDID data of

IC U708?

↓NO

Check CN702, IC U708 and peripheral circuits.

Check the line between IC U400 and CN702.

Check the line between pin (AA6) of IC U400 and CN700.

↓

Check the connection and setup with the external HDMI devices.

Is access possible in the re-writing or exchange of EDID data of

IC U701?

↓NO

Check CN700, IC U701 and peripheral circuits.

Check the line between IC U400 and CN700.

36

Page 37

A

A

f

f

f

A

f

<External input HDMI3>No picture on the display (11)

↓

Does not the picture of the HDMI signal input to HDMI3 go out?

MINI AV_UNIT: ↓

Is the HOT_PLUG detection function of pin (19) of a HDMI terminal

(CN701) normal?

NO

Check the line between pin (AB5) of IC U400 and CN701.

Check the connection and setup with the external HDMI devices.

YES

re EDID data pin (6)(SCL) of IC U700 (EEPROM), pin (5)(SDA)

accessed, and is it read from pin (15), (16) of a HDMI

terminal(CN701)?

Is TMDS signal input into pin (AF18, AE18)/RX2±, (AF17,

E17)/RX1±, (AF16, AE16)/RX0±, (AF15, AE15)/RXC± of IC U400?

Refer to “The picture doesn't appear in all modes.”

YES

↓YES

<External input VGA>No picture on the display (12)

NO

NO

Is access possible in the re-writing or exchange of EDID data of

IC U700?

Check CN701, IC U700 and peripheral circuits.

Check the line between IC U400 and CN701.

↓

Does not the picture of the PC IN(ANALOG) video signal input to VGA(15pin-D-SUB terminal) go out?

TERMINAL_UNIT: ↓

Is R/G/B/H/V signal sent to pin (1)/R, (2)/G, (3)/B, (14 )/H, (13)/V o

VGA (CN554)?

MAIN_UNIT: ↓YES

Is R/G/B/H/V signal sent to pin (AE20)/R, (AE19)/G, (AD19)/B,

(AC18)/H, (AB18)/V of IC U400?

Refer to “The picture doesn't appear in all modes.”

↓YES

<External input AV1(Component)>No picture on the display (13)

NO

NO

Check the setting of an external input device that connects o

CN554.

Check the line between IC U400 and CN554.

↓

Does not the picture of the component video signal input to Component go out?

TERMINAL_UNIT: ↓

Is Component Y/Pb/Pr signal sent to pin (2)/Y, (4)/Pb, (6)/Pr o

V1(CN552) ?

MAIN_UNIT: ↓YES

Is Component Y/Pb/Pr signal sent to pin (AE21)/Y, (AD22)/Pb,

(AF22)/Pr of IC U400?

Refer to “The picture doesn't appear in all modes.”

↓YES

NO

NO

Check the setting of an external input device that connects o

CN552.

Check the line between IC U400 and CN552.

LC-32SH25E

↓

↓NO

2008-03-14

37

Page 38

LC-32SH25E

f

p

)

f

p

)

< During external connec t ion > No pi ctu r e o n the mo ni to r (1)

↓

No picture appears on SCART1 - connected monitor during the tuner (U/V) reception.

↓

Checklist:

1) Is the Signal Type (item) in MENU-Option-Input Select equal to Signal Type of an external device? …Set it to “CVBS”, “Y/C”, “RGB”, “AUTO”.

2) Is ANT-CABLE disconnected or connected improperly? …Connect it correctly as per the operation manual.

3) The picture is sent to the monitor in a CVBS signal if the source during display is ATV, CVBS or Y/C of SCART1-2, AV3.

When sent by component, etc., that signal is not sent to the monitor.

4) When the monitor picture is not sent and is not displayed on the monitor, refer to “No picture” for each terminal.

5) The video output from SCART1 is not the monitor output (output of the picture now watching).

The

icture of the last selected TV channel is always sent to SCART1. (Specification

TERMINAL_UNIT:

Is CVBS signal output into pin (19) of CN500 (SCART1)?

↓NO

Is TUNER_CVBS signal output into pin (21) of CN500 (SCART1)?

Refer to “The picture doesn't appear in all modes.”

↓

↓NO

YES

YES

Check the setting of an external input device that connects o

CN500.

Check the line between CN500 and TU200.

< During external connec t ion > No pi ctu r e o n the mo ni to r (2)

SCART2: ↓

No picture from SCART1 appears on SCART2-connected monitor.

NOTE: Normally, if the screen during display is sent to SCART2, no picture is sent to SCART2.

↓

Checklist:

1) Is the Signal Type (item) in MENU-Option-Input Select equal to Signal Type of an external device? …Set it to “CVBS”, “Y/C”, “AUTO”.

2) The picture is sent to the monitor in a CVBS signal if the source during display is TV, CVBS or Y/C of SCART1-2, AV3.

When sent by component, etc., that signal is not sent to the monitor.

3) When the monitor picture is not sent and is not displayed on the monitor, refer to “No picture” for each terminal.

4) The video output from SCART1 is not the monitor output (output of the picture now watching).

The

TERMINAL_UNIT:

Is CVBS signal output into pin (19) of CN501 (SCART2)?

↓NO

Is CVBS signal output from pin (A13) of IC U400 into pin (19) of

CN501 (SCART2)?

Refer to “The picture doesn't appear in all modes.”

icture of the last selected TV channel is always sent to SCART1. (Specification

↓

YES

YES

↓NO

Check the setting of an external input device that connects o

CN501.

Check the line between CN501 and IC U400.

38

Page 39

LC-32SH25E

CHAPTER 5. MAJOR IC INFORMATIONS

[1] MAJOR IC INFORMATIONS

1. MAJOR IC INFORMATIONS

1.1. U400 (MT5362CHG/A)

GENERAL DESCRIPTION

The MediaTek MT5362CHG/A family consists of a DTV(DVB-T) front-end demodulator, a backend decoder and a TV controller and offers high

integration for advanced applications. It combines a transport de-multiplexer, a high definition video decoder, an AC3 audio decoder, an dual-link LVDS

transmitter, and an NTSC/PAL/SECAM TV decoder with a 3D comb filter(NTSC/PAL). The MT5362CHG/A enables consumer electronics manufactures to

build high quality, low cost and feature-rich DTV.

World-Leading Audio/Video Technology: The MT5362CHG/A supports most Full-HD video decoder standards including H.264, MPEG4, MPEG2 and

JPEG. The MT5362CHG/A also supports MediaTek MDDi

to the TV decoder recovers great details for still pictures. The special color processing technology provides natural, deep colors and true studio quality

video. Also, the MT5362CHG/A family has built-in high resolution and high-quality audio codec.

Rich Features for High Value Products: The MT5362CHG/A family enables true single-chip experience. It integrates high-quality HDMI1.3, high speed

VGA ADC, dual-channel LVDS, USB2.0 receiver and multi-media decoder

Reliable DVB-T Receiving capability: MT5362CHG/A family supports DVB-T demodulation function. Excellent adjacent and co-channel rejection

capability grants customers never miss any wonderful stream. Professional error-concealment provides stable, smooth and mosaic-free video quality.

Key Features:

1. DVB-T demodulator

2. A transport demultiplexer

3. A multi-standard video decoder

4. An AC3/MPEG2 audio decoder

5. HDMI1.3 receiver

6. Audio codec

Note: All packages are lead free

General Feature List

□ Host CPU

· ARM 926EJS

· 16K I-Cache and 16K D-Cache

· 8K Instruction TCM

· JTAG ICE interface

· Watch Dog timers

· Build-in CPI analyzer and Cache Hit Rate Meter

□ Transport Demultiplexer

· Supports a serial or parallel transport stream input

· Supports ATSC, DVB, MPEG-2 transport stream input

· Supports DES/3-DES/DVB/AES de-scramblers

· Up to 8-PID even/odd keys for descrambling

· Support 32 PID filters and 32 section filters

· Support micro-processor section filtering

· Support hardware CRC-32 check

· Support PCR recovery function

· Support a micro-processor for stream process and MPEG start code detection

· Support DVB CA

· Support simple trick play (Playback / Pause /Fast Forward (upto x32)) through USB or Flash

□ MPEG2 Decoder

· MPEG MP@ML, MP@HL and MPEG-1 video standards

· Support de-blocking filter

□ MPEG1 Decoder

□ MPEG4.2 Decoder

· ASP@15 (720P)

□ H.264 (MPEG4.10) HD Decoder (AVC)

· MP@L4.1, HP@L4.1, BP@L3 (baseline) video standard

□ Still Image decoding

· JPEG (base-line or progressive)

□ De-mosquito engine

· 2D/3D for all AV inputs

□ 2D Graphics

· Support multiple color modes

· Point, horizontal/vertical line primitive drawings

2008-03-14

TM

de-interlace solution to reach very smooth picture quality for motions. A 3D comb filter added

39

Page 40

LC-32SH25E

· Rectangle fill and gradient fill functions

· Bitblt with transparent options

· Alpha blending and alpha composition Bitblt

· Stretch Bitblt

· Font rendering by color expansion

· YCbCr to RGB color space conversion

□ Image Resizer

· Support 2/4/8bpp index format, 16bpp/32bpp direct color format.

· Support 420/422 video format.

· Support 420/422/444 JPEG format.

· Arbitrary ratio vertical/horizontal scaling of video, from 1/128X to 128X

· Simple DMA.

□ OSD Plane

·Two linking list OSDs with multiple color mode and one of them has scaler

□ Video Plane

· Support video capture and over scan.

· Flesh tone management

· Gamma correction

· Color Transient Improvement (CTI)

· 2D Peaking

· Saturation/hue adjustment

· Brightness and contrast adjustment

· Black and White level extender

· Adaptive Luma/Chroma management

· Automatic detect film or video source

· 3:2/2:2 pull down source detection

· Support maximum 1920 width motion-adaptive de-interlace.

· Support excellent low angle image processing.

· Arbitrary ratio vertical/horizontal scaling of video, from 1/32X to 32X

· Advanced non-linear panorama scaling.

· Programmable zoom viewer

· Progressive scan output

· Support alpha blending

· Dithering processing for flat panel display

· Frame rate conversion.

· Support FHD panel and VGA dot-to-dot

· Support PIP/POP, (dual de-interlace, one HD and one SD)

□ LVDS

· Support 6/8/10-bit one – channel or 6/8-bit dual-channel LVDS transmitter, 2-link LVDS up-to 175 MHz

· Built-in spread spectrum for EMI performance

· Programmable panel timing output

□ CVBS In

· On-chip 54 MHz 10-bit video ADC

· Support PAL (B,G,D,H,M,N,I,Nc), NTSC,

· NTSC-4.43, SECAM

· Macrovision detection

· NTSC/PAL support 3D/2D comb filter

· Built-in motion-adaptive 3D Noise Reduction

· VBI data slicer for CC/TT decoding

· Support 2-S-Video.

· Max. Support 4-channel CVBS.

· Support SCART connector

□ VGA In

· Support VGA input up to UXGA 162 MHz

· Support full VESA standards

□ Component Video In

· Support two component video inputs

· Support 480i / 480p / 576i / 576p / 720p / 1080i / 1080p

□ Audio ADC

· 2 channel on chip Audio ADC

□ Audio digital input

· 1 bit I2S audio input

□ HDMI Receiver

· HDMI1.3, data rate can be up to 2.25 GHz

· EIA/CEA-861B

· CEC

40

Page 41

LC-32SH25E

□ Video bypass (for EU application)

· TVbypass

· CVBS Monitor (any AV input)

□ TV audio demodulator

· Support BTSC / EIA-J / A2 / NICAM / PAL FM /

· SECAM world-wide formats

· Standard automatic detection

· Stereo demodulation, SAP demodulation

· Mode selection (Main/SAP/Stereo)

□ Audio DAC

· 6 on-chip audio DACs (3-pair) support R/L channel and subwoofer outputs

□ DRAM Controller

· 32-bit DDR1/2 interface

· Support 8MB to 128 MB DDR DRAM devices

· Support DDR1-400, DDR1-500, DDR2-667 DDR2-800

□ Audio DSP

· Support Dolby Digital AC-3 decoding (ATSC)

· MPEG-1 layer I/II decoding (DVB)

· Dolby Prologic II

· Support WMA / HE-AAC / DTS / ADPCM /

· LPCM

· Audio output: 7.1ch + 2ch (down mix)

· Pink noise and white noise generator

· Equalizer

· Bass management

· 3D surround processing with virtual surround

· Audio and video lip synchronization

· Support reverberation

· Automatic volume control

· Support 5-bit (10-channel) main audio I

· Support 1-bit (2-channel) aux audio I

□ S/PDIF interface

· One SPDIF input

· One SPDIF out

□ Digital TV(DVB-T) Demodulator

· COFDM(Coded Orthogonal Frequency Division Multiplex) channel demodulator for DVB-T receiver

· ETSI 300 744 & Nordig Unified compliant

· Excellent performance for SFN(Single Frequency Network) & Indoor reception

· Support 2K, 8K modes

· Support QPSK,16,64 QAM constellations

· 1/4,1/8,1/16,1/32 Guard interval

· Support hierarchical & non-hierarchical modes

· Accept 6,7,8 MHz channel bandwidth

· Automatic mode detection

· Full-digital timing/frequency with wide acquisition range

· Support triple offset

· Excellent adjacent Channel interference (ACI) rejection capability

· Excellent Co-Channel interference(CCI) rejection capability

· Fast channel lock time

□ Analog TV IF Demodulator

· Support PAL/SECAM standard

· Accept IF frequency at 38.25 MHz

· Full digital AGC control and carrier recovery

□ Peripherals

· Each of the MT5362CHG/A has one built-in UART with Tx and Rx FIFO. It has hardware flow control and high speed data transferring.

· The MT5362CHG/A family has three basic serial interfaces; one is for the tuner, one is the master for general purpose, the other is the slave for

HDMI EDID data.

· Three PWMs

· While NAND Flash is disabled, the MT5362CHG/A support MS/MS-PRO, SD/MMC, and SDHC card reader.

· IR blaster and receiver

· Real-time clock and watchdog controller

· The MT5362CHG/A includes 2-link USB2.0/1.1 (support external hub) for USB mass storage class device.

· Built-in uP in standby module

· SDIO interface (for DSG, WiFi or UWB)

· Support two serial flash or one serial and one NAND

· Support five-input low-speed ADC.

2008-03-14

2

S output interface: each of these channels is up to 24-bit resolution.

2

S output I/F: each of these channels is up to 24-bit resolution.

41

Page 42

LC-32SH25E

· Support boundary scan (JTAG)

□ IC Outline

· MT5362CHG/A is 27x27 mm BGA Package

· 3.3V/1.0V and 1.8V for DDR2

1.2. U103, U104 (L5985 VFQFPN8)

Description

The L5985 is a step down switching regulator with 2.5A current limited embedded power MOSFET, so it is able to deliver up to 2A DC current to the load

depending on the application condition.

The input voltage can range from 2.9V to 18V, while the output voltage can be set starting from 0.6V to V

. Having a minimum input voltage of 2.9V, the

IN

device is suitable for buses staring from for 3.3V bus.

Requiring a minimum set of external components, the device includes an internal 250KHz switching frequency oscillator that can be externally adjusted up

to 1MHz.

The QFN package with exposed pad allows reducing the R

down to approximately 60°C/W.

thJA

Features

· 2A DC output current

· 2.9V to 18V input voltage

· Output voltage adjustable from 0.6V

· 250KHz switching frequency, programmable up to 1MHz

·Internal Soft-start and Inhibit

· Low dropout operation: 100% duty cycle

· Voltage feed-forward

· Zero load current operation

· Over current and thermal protection

· VQFN3x3-8L package

Applications

· Consumer:

STB, DVD, DVD recorder, car audio, LCD TV and monitors

· Industrial:

Chargers, car battery, PLD, PLA, FPGA

· Networking: XDSL, modems, DC-DC modules

· Computer:

Optical storage, hard disk drive, printers, audio/graphic cards

1.3. U351, U352 (HYB18TC512160B2F-25 TFBGA84)

Features

The 512-Mbit Double-Data-Rate-Two SDRAM offers the following key features:

· 1.8 V ± 0.1 V Power Supply

· 1.8 V ± 0.1 V (SSTL_18) compatible I/O

· DRAM organizations with 8, 16 data in/outputs

· Double Data Rate architecture:

- two data transfers per clock cycle

- four internal banks for concurrent operation

· Programmable CAS Latency: 3, 4, 5 and 6

· Programmable Burst Length: 4 and 8

· Differential clock inputs (CK and CK)

· Bi-directional, differential data strobes (DQS and DQS) are transmitted / received with data. Edge aligned with read data and center-aligned with write

data.

· DLL aligns DQ and DQS transitions with clock

· DQS can be disabled for single-ended data strobe operation

· Commands entered on each positive clock edge, data and data mask are referenced to both edges of DQS

· Data masks (DM) for write data

· Posted CAS by programmable additive latency for better command and data bus efficiency

· Off-Chip-Driver impedance adjustment (OCD) and On-Die-Termination (ODT) for better signal quality.

· Auto-Precharge operation for read and write bursts

· Auto-Refresh, Self-Refresh and power saving Power-Down modes

· Average Refresh Period 7.8 µs at a T

lower than 85 °C, 3.9 µs between 85 °C and 95 °C

CASE

· Programmable self refresh rate via EMRS2 setting

· Programmable partial array refresh via EMRS2 settings

· DCC enabling via EMRS2 setting

· Full and reduced Strength Data-Output Drivers

· 1K page size for x8, 2KB page size for x16

· Packages: PG-TFBGA-84, PG-TFBGA-60

· RoHS Compliant Products

1

)

· All Speed grades faster than DDR2-400 comply with DDR2-400 timing specifications when run at a clock rate of 200 MHz.

42

Page 43

LC-32SH25E

1.4. U600 (TDA8933BTW HTSSOP32)

General description

The TDA8933B is a high-efficiency class D amplifier with low power dissipation.

The continuous-time output power is 2 × 10 W in a stereo half-bridge application (R

to the low power dissipation the device can be used without any external heat sink when playing music. Due to the implementation of thermal foldback(TF)

the device remains operating with considerable music output power without the need for an external heat sink, even for high supply voltages and/or lower

load impedances.

The device has two full differential inputs driving two independent outputs. It can be used in a mono full-bridge configuration (Bridge-Tied Load(BTL)) or as

stereo half-bridge configuration (Single-Ended(SE)).

Features

· Operating voltage from 10 V to 36 V asymmetrical or ±5 V to ±18 V symmetrical

· Mono bridge-tied load (full-bridge) or stereo single-ended (half-bridge) application

· Application without heat sink using thermally enhanced small-outline package

· High efficiency and low-power dissipation

· Thermal foldback to avoid audio holes

· Current limiting to avoid audio holes

· Full short-circuit proof across load and to supply lines (using advanced current protection)

· Switchable internal or external oscillator (master-slave setting)

· No pop noise

· Full differential inputs

Applications

· Flat-panel television sets

· Flat-panel monitor sets

· Multimedia systems

· Wireless speakers

· Mini/micro systems

· Home sound sets

= 8 Ω) or 1 × 20 W in a mono full-bridge application (RL =16 Ω). Due

L

1.5. U602 (WM8521H9GED/RV SOIC-14)

DESCRIPTION

The WM8521 is a 96kHz stereo DAC with an integrated output op-amp stage, designed to generate a 2.0Vrms output signal directly, so reducing external

component requirements in digital audio applications.

WM8521 comes into two variants WM8521HC and WM8521H9 which offers different line drive output capabilities. WM8521HC outputs 2Vrms at 12V

supply, while WM8521H9 outputs 2.0Vrms at 9V supply. WM8521HC/H9 are designed for cost sensitive consumer digital audio applications requiring

2Vrms line output.

A 24-bit multi-bit sigma delta DAC is used with oversampling digital interpolation filters. Digital audio input word lengths from 16-32 bits and sampling rates

from 8kHz to 96kHz are supported.

The audio interface supports I

The devices are controlled via a hardware interface which provides access to features including de-emphasis, mute and data formats. These devices are

pin equivalent and are available in a 14-pin SOIC package.

FEATURES

· Audio Performance

- DAC SNR 98dB (‘A’ weighted @ 48kHz)

- THD -81dB (‘A’ weighted @ 48kHz)

· DAC Sampling Frequency: 8kHz – 96kHz

· Pin Selectable Audio Data Interface Format

2

S, 16-bit Right Justified or 16bit DSP

- I

· 2.0 Vrms output at 12V or 9V supply

· 8.2V to 13.2V Analogue, 2.7V to 3.6 Digital Supply

· 14-pin SOIC Package

APPLICATIONS

· Consumer digital audio applications requiring 2 Vrms output

- DVD Players

- Digital TV

- Digital Set Top Boxes

- A/V Receivers

2

S, Right Justified and DSP digital audio formats.

2008-03-14

1.6. U401 (MT8295AE LQFP-128)

43

Page 44

LC-32SH25E

FEATURES

■ PCMCIA/CI Interface

· Single slot PC Card interface

· Single slot CI interface

· 512 byte embedded buffer

■ Host Interface

· NAND flash interface

· Interrupt capability

· 3.3V logic levels

■ Transport Stream Interface

· MPEG2 compliant TS

· One parallel or two serial TS interface from demodulator

· Serial TS interface to MPEG2 decoder

· Parallel TS interface from/to CAM

· Supports serial to parallel TS conversion

· Supports parallel to serial TS conversion

■ Miscellaneous

· 27 MHz crystal

· 60 MHz clock input

· Integrated PLL

· 3.3/1.8V process

· 5V compatible I/Os for PC Card interface

· Supports additional 15 GPIOs

· LQFP 128-pin package

1.7. U390 (MX25L3205DMI-12G SOP-16)

FEATURES

GENERAL

· Serial Peripheral Interface compatible -- Mode 0 and Mode 3

· 32M:33,554,432 x 1 bit structure or 16,772,216 x 2 bits (two I/O read mode) structure

· 1024 Equal Sectors with 4K byte each (32Mb)

- Any Sector can be erased individually

· 64 Equal Blocks with 64K byte each (32Mb)

- Any Block can be erased individually

· Single Power Supply Operation

- 2.7 to 3.6 volt for read, erase, and program operations

· Latch-up protected to 100mA from -1V to Vcc +1V

· Low Vcc write inhibit is from 1.5V to 2.5V

PERFORMANCE

• High Performance

- Fast access time: 86MHz serial clock (15pF + 1TTL Load) and 66MHz serial clock (30pF + 1TTL Load)

- Serial clock of two I/O read mode : 50MHz (15pF + TTL Load), which is equivalent to 100MHz

- Fast program time: 1.4ms(typ.) and 5ms(max.)/page (256-byte per page)

- Byte program time: 7us (typical)

- Continuously program mode (automatically increase address under word program mode)

- Fast erase time: 60ms(typ.) /sector (4K-byte per sector) ; 0.7s(typ.) /block (64K-byte per block); 25s(typ.) for 32Mb

· Low Power Consumption

- Low active read current: 25mA(max.) at 86MHz, 20mA(max.) at 66MHz and 10mA(max.) at 33MHz

- Low active programming current: 20mA (max.)

- Low active erase current: 20mA (max.)

- Low standby current: 20uA (max.)

- Deep power-down mode 1uA (typical)

· Typical 100,000 erase/program cycles

SOFTWARE FEATURES

· Input Data Format

- 1-byte Command code

· Advanced Security Features

- Block lock protection

The BP0-BP3 status bit defines the size of the area to be software protection against program and erase instructions

- Additional 512-bit secured OTP for unique identifier

· Auto Erase and Auto Program Algorithm

- Automatically erases and verifies data at selected sector

- Automatically programs and verifies data at selected page by an internal algorithm that automatically times the program pulse widths (Any page to be

44

Page 45

programed should have page in the erased state first)

· Status Register Feature

· Electronic Identification

- JEDEC 1-byte manufacturer ID and 2-byte device ID

- RES command for 1-byte Device ID

- Both REMS and REMS2 commands for 1-byte manufacturer ID and 1-byte device ID

HARDWARE FEATURES

· SCLK Input

- Serial clock input

· SI Input

- Serial Data Input

· SO Output

- Serial Data Output

· WP#/ACC pin

- Hardware write protection and program/erase acceleration

· HOLD# pin

- pause the chip without diselecting the chip

· PACKAGE

- 16-pin SOP (300mil)

- 8-land WSON (8x6mm or6x5mm)

- 8-pin SOP (200mil, 150mil)

- 8-pin PDIP (300mil)

- All Pb-free devices are RoHS Compliant

1.8. U155 (IC TPS5430DDAR SO-8(DDA))

FEATURES

· Wide Input Voltage Range:

– TPS5430: 5.5 V to 36 V

– TPS5431: 5.5 V to 23 V

· Up to 3-A Continuous (4-A Peak) Output Current