Page 1

Evaluation Board Manual

S3F401F

16/32-BIT RISC

MICROPROCESSOR

Dec, 2007

REV 1.00

Page 2

Table of Contents

Chapter 1 Evaluation Board Manual

1. Overview ......................................................................................................................................................1

1.1 Features................................................................................................................................................3

1.2 System Requirements ..........................................................................................................................3

1.3 Board Components...............................................................................................................................4

2. Configuration................................................................................................................................................5

2.1 Detailed Block Configurations...............................................................................................................6

3. Total blocks’ Unit & Jumper Summury.........................................................................................................15

3.1 Function Blocks.....................................................................................................................................15

3.2 Jumper Connection...............................................................................................................................16

3.3 Switches................................................................................................................................................18

4. S3F401F-EVB REV 1.0 Board Schematics .................................................................................................19

Page 3

EVALUATION BOARD MANUAL S3F401F_BD_UM_REV1.00

1 EVALUATION BOARD MANUAL

1. OVERVIEW

S3F401F EVB (Evaluation Board) is a compact platform that is suitable for code development of SAMSUNG's

S3F401F 16-/32-bit RISC microcontroller for an inverter motor and general purpose application.

EVB is consists of several blocks, which can make operate the function of S3F401F. Those functions are from the

followings:

• A 16-/32-bit RISC CPU Core, ARM7TDMI-S

• A built-in 256Kbyte NOR-Flash memory

• An internal 20KB SRAM for stack, data, or code

• An interrupt controller, supporting vectored interrupt

• 6xch 16-bit timers with capture and PWM function

• 1xch 8-bit basic timer & 3-bit watch-dog timer

• Three programmable I/O port groups

• 2xch Inverter motor controller

• 2xch 16-bit Encoder counter

• 15xch 12-bit ADC

• 2xch UART

• 2xch SSP

If you need more detail information about S3F401F, meet the samsung web site.

http://www.samsung.com/global/business/semiconductor/productList.do?fmly_id=223

1

Page 4

EVALUATION BOARD MANUAL S3F401F_BD_UM_REV1.00

Crystal or

Ceramic

Oscillator

CLOCK

MONITOR

I/O

CONTROLLER

ARM7TDMI-S

CORE

INTERRUPT

CONTROLLER

PLL

IMC0/1

BRIDGE

SSP0/1

SSP0/1

AHB

FLASH-ROM

256KB

SRAM

20KB

TAP CONTROLLER

For JTAG

ENC0/1

ENC0/1IMC0/1

UART0/1

UART0/1

APB

BT & WDT

Timer0/1/2/3/4/5

Timer0/1/2/3/4/5

Timer0/1/2/3/4/5

12-BIT ADC

Figure 1. S3F401F Block Diagram

Timer0/1/2/3/4/5

TIMER 0/1/2/3/4/5

2

Page 5

EVALUATION BOARD MANUAL S3F401F_BD_UM_REV1.00

1.1 FEATURES

Micro-Controller S3F401F, ARM7TDMIS, 16/32-bit RISC Microcontroller

External DC 7~12V Board Power Source

Adjustable voltage regulator out is 3.2V

Board Master Power Switch SW6

UART

Support to protocol for RS-232

Physical interface circuit connected to standard PC through DB9(female)

Interface driver IC MAX3221

Synchronous Serial Port

Provide SSP, SPI serial communication with external devices (master or slave)

SSP serial EEPROM (8K * 8bit): X25650

SSP serial EEPROM (4K * 16bit): 64LC40S

LED IO Port output control display

JTAG Connection 20Way JTAG connector (Multi-ICE Interface, Trace 32 etc.)

1.2 SYSTEM REQUIREMENTS

This section describes the hardware and software system requirements.

Software Requirements

ARM Compiler SW

ARM Debugger SW

Hardware Requirements

S3F401F EVB Board Set

Power Supply DC 7~12V ( Recommend Default 12V)

Debugger (Multi-ICE or Trace 32 etc.)

PC(Pentium, 32MB RAM for Windows 95, or 64MB RAM for Windows NT)

COM Port for serial communication

Parallel Port (If using Multi-ICE)

3

Page 6

EVALUATION BOARD MANUAL S3F401F_BD_UM_REV1.00

1.3 BOARD COMPONENTS

The board consists of the followings.

S3F401F Micro-controller

64LC40S and X25650 as a serial EEPROM for SSP

2 x DSUB Connector for RS-232

2 x Header groups for IMC function

1 x Buzzer

6 x Switches: IRQ x 2, Power, Reset

4 x LED: Power x1, IO Port output x 3

A regulator to generate 3.3V

4MHz Crystal as a master system clock source

Switches for ADC input capacitor selection

7-segment (4-digit) display circuit

A standard 20-pin JTAG interface connector

Dual-line header pins for a port level or signal

53 x Jumpers for function setting control

15 x TP (Test Pole) to check specific pins relating to the digital, analog, PLL power and clock

4

Page 7

EVALUATION BOARD MANUAL S3F401F_BD_UM_REV1.00

2. CONFIGURATION

IMC1 HEADER CONNECTOR

Page 1-11

SSP BLOCK

Buzzer

JTAG

12-bit ADC BLOCK

Page 1 -12

MODE SETTING BLOCK

Page 1-7

Page 1-9

POWER BLOCK

Page 1-6

Main OSC

7-SEGMENT

Page 1-10

S3F401FX

IMC0 HEADER CONNECTOR

Page 1-11

UART BLOCK

Page 1-8

Figure 2. S3F401F Evaluation Board Top-view

5

Page 8

EVALUATION BOARD MANUAL S3F401F_BD_UM_REV1.00

2.1 DETAILED BLOCK CONFIGURATIONS

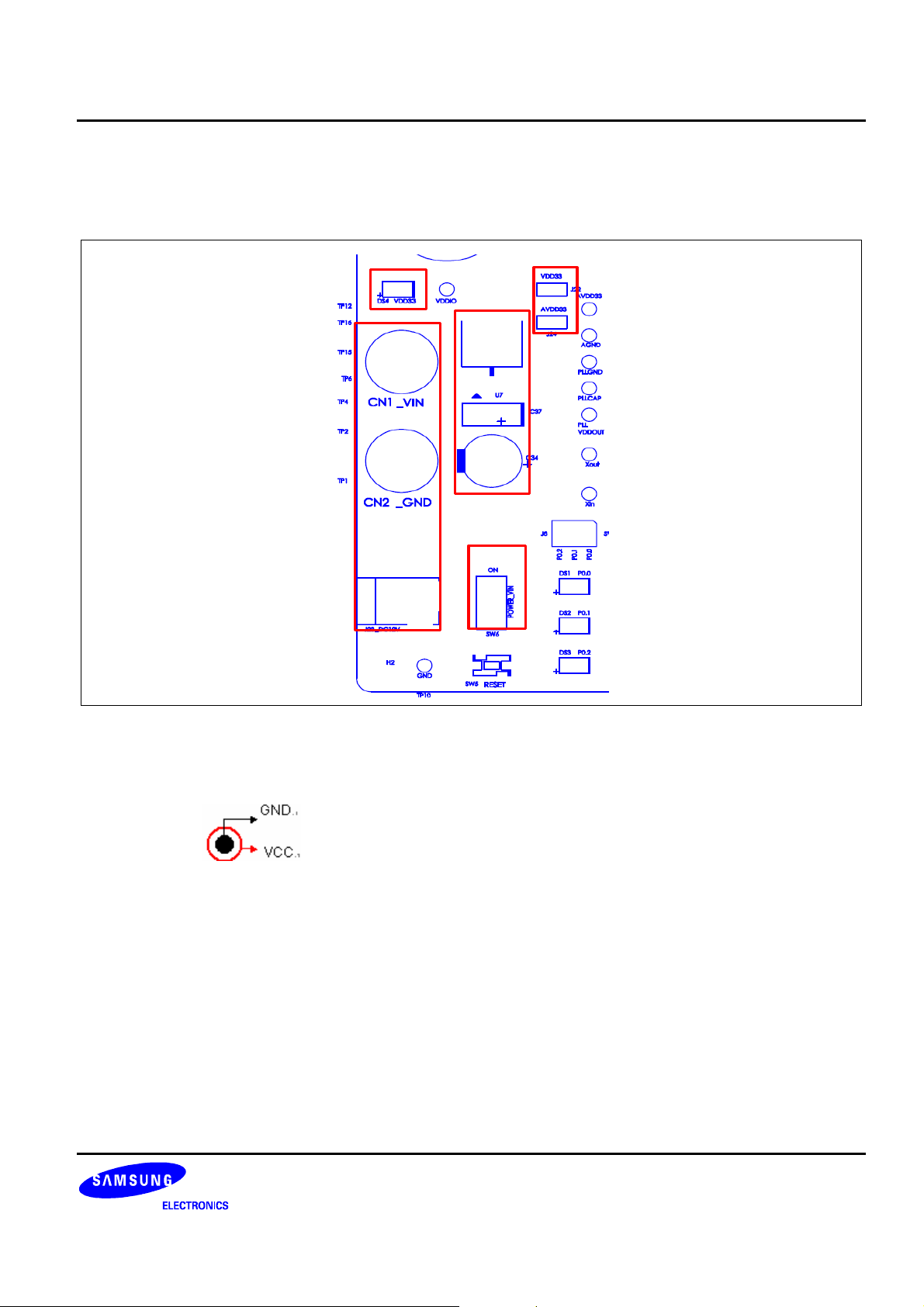

2.1.1 Power Block

4

1

① CN1, CN2, J23: Power Supply Connector

CN1 : VIN

CN2 : GND

J23 : DC adapter connector

5

2

3

② U7: Adjustable Voltage Regulator

3.3V generator J VDD33, VDDCORE, VDDIO

③ SW6: Power Switch

④ DS4: Power Display LED

VDD33 Power-on status display

⑤ J22: Jumper Setting

Selection VDDCORE / VDDIO

1-2 connection: The VDD of each block is connected to VDD33.

6

Page 9

EVALUATION BOARD MANUAL S3F401F_BD_UM_REV1.00

2.1.2 Mode Setting Block

J9 & J10 & J11: Jumper Setting

J9 J10 J11 MD[2:0]

2-3 Connection 2-3 Connection 2-3 Connection NORMAL

1-2 Connection 2-3 Connection 2-3 Connection SPGM

Others Only TEST Mode

7

Page 10

EVALUATION BOARD MANUAL S3F401F_BD_UM_REV1.00

2.1.3 UART Block

④

2

1

3

① U10, U11: UART Driver IC

② P2, P3: UART Connector

③ J25

TXD0 UARTTXD0 is connected to T1IN of MAX3221.

RXD0 UARTRXD0 is connected to R1OUT of MAX3221.

④ J26

TXD1 UARTTXD1 is connected to T1IN of MAX3221

RXD1 UARTRXD1 is connected to R1OUT of MAX3221.

Jumper Setting

Jumper Setting

8

Page 11

EVALUATION BOARD MANUAL S3F401F_BD_UM_REV1.00

9

Page 12

EVALUATION BOARD MANUAL S3F401F_BD_UM_REV1.00

2.1.4 SSP Block

1

① U9: SSP8 serial EEPROM (8K × 8bit)

SW9 ON

SW10 ON

② U8: SSP16 serial EEPROM (4K × 16bit)

FSS0 is connected to P1.16.

RXD0 is connected to P1.14.

CLK0 is connected to P1.15.

TXD0 is connected to P1.13.

2

SW7 ON

SW8 ON

FSS1 is connected to P1.20.

CLK1 is connected to P1.19.

RXD1 is connected to P1.18.

TXD1 is connected to P1.17.

The RDY/nBUSY pin is connected to P2.11.

The RESET pin is connected to P2.10.

10

Page 13

EVALUATION BOARD MANUAL S3F401F_BD_UM_REV1.00

11

Page 14

EVALUATION BOARD MANUAL S3F401F_BD_UM_REV1.00

2.1.5 7-SEGMENT BLOCK

1 2

The assignment of 7-segment control pins on the S3F401F-EVB is the same like this.

① SW1 ON: This Port (P0.0~P0.7) is connected to each segment of 7-segment.

② SW2 ON: This Port (P1.9~P1.12) is connected to latch.

③ U3: 7-segment display

3

12

Page 15

EVALUATION BOARD MANUAL S3F401F_BD_UM_REV1.00

2.1.6 IMC BLOCK

The assignment of IMC pins on the S3F401F-EVB is the same like this.

① J20: A header pin group for MOTOR1

② J21: A header pin group for MOTOR2

1

2

13

Page 16

EVALUATION BOARD MANUAL S3F401F_BD_UM_REV1.00

2.1.7 ADC BLOCK

⑥

4

5

1

① J1: ADC input connector

② J2, J3, J4: J2, J3 and J4 are selected to sample test with AIN0, AIN1 and AIN2

23

③ RV1: Variable Resistor

④ J24: ADC Power Source

Close: When connecting (short), AVDD is same to VDD33.

Open: AVDD is a second (right) pin of J24. So, AVDD should be connected to another powe r.

⑤ J7: 2,3 connection - ADTRG signal is generated by SW4

⑥ SW11, SW12: Control cap for each ADC input port.

14

Page 17

EVALUATION BOARD MANUAL S3F401F_BD_UM_REV1.00

3. TOTAL BLOCKS’ UNIT & JUMPER SUMMURY

3.1 FUNCTION BLOCKS

Block Symbols Description

7-SEGMENT U3 4Digit Segment

J20 MOTOR 1 IMC

J21 MOTOR 2

U14 RS-232 transceiver UART

P41 RS-232 connector

SSP

POWER U11 3.3V generator regulator

LED

BUZZER BZ1 Buzzer

U7

U8

SPI8 interface EEPROM (8K × 8bit)

SPI16 interface EEPROM (4K × 16bit)

J28 SPI block pin assignment

DS1 Red LED

DS2 Green LED

DS3 Yellow LED

15

Page 18

EVALUATION BOARD MANUAL S3F401F_BD_UM_REV1.00

3.2 JUMPER CONNECTION

JP# Description Default Setting

J1 ADC block pin assignment

J2 AIN0 input voltage connector

AIN0~AIN14

Connect (Short)

−

J3 AIN1 input voltage connector

Connect (Short)

J4 AIN2 input voltage connector

J5 SW3_INPUT

J6 Buzzer connector

J7 SW4_INPUT

J8 LED signal connector

VDDIO connects to INT7

T3PWM connects to Buzzer

VDDIO connects to INT8

Port 0.0/0.1/0.2 connect to DS1, DS2, DS3

Connect (Short)

Open

Connect (Short)

Connect ADTRG

Connect (Short)

16

Page 19

EVALUATION BOARD MANUAL S3F401F_BD_UM_REV1.00

3.2 JUMPER CONNECTION (Continued)

JP# Description Default Setting

J9 J9 J10 J11 MD[1:0]

MODE selection

J10 2-3 2-3 2-3 NORMAL

J11

1-2 2-3 2-3 SPGM

All 2-3 connect

:Normal Mode

J12 Port assignment pin Port 2 Open

J13 Port assignment pin Port 1 Open

J14 Port assignment pin Port 0 Open

J15 nTRST The JTAG connects to nTRST Open

J16

J17

Chip socket connection Chip socket board is connected with

S3F401F-EVB.

Use the chip socket

board

J18

J19

J20 MOTOR1 IMC0 and ENC0 signal connector

J21 MOTOR2 IMC1 and ENC1 signal connector

J22 Generated VDD33 voltage from

3.3V connects to VDD33 Join 1-2

U11_regulator (3.3V)

J23 DC Power jack ( 9~18V) GND

VCC

J24 AVDD

J25

UART

-

-

J26

-

-

Open

Open

17

Page 20

EVALUATION BOARD MANUAL S3F401F_BD_UM_REV1.00

3.3 SWITCHES

SW# Description

SW1 7-Segment ON: Port 0.0~0.7 connects to 7segment

SW2 Latch ON: Port 1.9~1.12 connects to latch

SW3 INT7 LOW signal is generated by SW3

SW4 INT8 HIGH signal is generated by SW4

SW5 RESET Reset signal is generated by SW6

SW6 Power_VIN Power on switch

SW7 SSP16 Port connects to EEPROM

SW8 SSP16 Port connects to EEPROM

SW9 SSP8 Port connects to EEPROM

SW10 SSP8 Port connects to EEPROM

SW11 AIN Port connects to ADC

SW12 AIN Port connects to ADC

18

Page 21

EVALUATION BOARD MANUAL S3F401F_BD_UM_REV1.00

4. S3F401F-EVB REV 1.0 BOARD SCHEMATICS

SCH-01 EVB TOP Block Diagram REV 1.0

SCH-02 S3F401F Micro-Controller REV 1.0

SCH-03 System Power Generation REV 1.0

SCH-04 Clock & Mode REV 1.0

SCH-05 ADC, Interrupt & BUZZER REV 1.0

SCH-06 JTAG Connector REV 1.0

SCH-07 UART Communication REV 1.0

SCH-08 SSP Communication REV 1.0

SCH-09 IMC & ENC Signal REV 1.0

SCH-10 7-Segment Display REV 1.0

SCH-11 Expansion Connector REV 1.0

19

Page 22

EVALUATION BOARD MANUAL S3F401F_BD_UM_REV1.00

SCH-01

20

Page 23

EVALUATION BOARD MANUAL S3F401F_BD_UM_REV1.00

SCH-02

21

Page 24

EVALUATION BOARD MANUAL S3F401F_BD_UM_REV1.00

SCH-03

22

Page 25

EVALUATION BOARD MANUAL S3F401F_BD_UM_REV1.00

SCH-04

23

Page 26

EVALUATION BOARD MANUAL S3F401F_BD_UM_REV1.00

SCH-05

24

Page 27

EVALUATION BOARD MANUAL S3F401F_BD_UM_REV1.00

SCH-06

25

Page 28

EVALUATION BOARD MANUAL S3F401F_BD_UM_REV1.00

SCH-07

26

Page 29

EVALUATION BOARD MANUAL S3F401F_BD_UM_REV1.00

SCH-08

27

Page 30

EVALUATION BOARD MANUAL S3F401F_BD_UM_REV1.00

SCH-09

28

Page 31

EVALUATION BOARD MANUAL S3F401F_BD_UM_REV1.00

SCH-10

29

Page 32

EVALUATION BOARD MANUAL S3F401F_BD_UM_REV1.00

SCH-11

30

Loading...

Loading...