Page 1

2003.10.15

现货库存、技术资料、百科信息、热点资讯,精彩尽在鼎好!

S3C2440X RISC MICROPROCESSOR PRODUCT OVERVIEW

PRODUCT OVERVIEW

INTRODUCTION

This manual describes SAMSUNG's S3C2440X 16/32-bit RISC microprocessor. SAMSUNG’s S3C24440X is

designed to provide hand-held devices and general applications with low-power, and high-performance microcontroller solution in small die size. To reduce total system cost, the S3C2440X includes the following components

separate 16KB Instruction and 16KB Data Cache, MMU to handle virtual memory management, LCD Controller

(STN & TFT), NAND Flash Boot Loader, System Manager (chip select logic and SDRAM Controller), 3-ch UART,

4-ch DMA, 4-ch Timers with PWM, I/O Ports, RTC, 8-ch 10-bit ADC and Touch Screen Interface, Camera

interface, IIC-BUS Interface, IIS-BUS Interface, USB Host, USB Device, SD Host & Multi-Media Card Interface, 2ch SPI and PLL for clock generation.

The S3C2440X has been developed using an ARM920T core, 0.13um CMOS standard cells and a memory

complier. Its low-power, simple, elegant and fully static design is particularly suitable for cost- and power-sensitive

applications. It adopts a new bus architecture known as Advanced Micro controller Bus Architecture (AMBA).

The S3C2440X offers outstanding features with its CPU core, a 16/32-bit ARM920T RISC processor designed by

Advanced RISC Machines, Ltd. The ARM920T implements MMU, AMBA BUS, and Harvard cache architecture

with separate 16KB instruction and 16KB data caches, each with an 8-word line length.

By providing a complete set of common system peripherals, the S3C2440X minimizes overall system costs and

eliminates the need to configure additional components. The integrated on-chip functions that are described in this

document include:

• 1.2V internal, 1.8V/2.5V/3.3V memory, 3.3V external I/O microprocessor with 16KB I-Cache/16KB D-

Cache/MMU

• External memory controller (SDRAM Control and Chip Select logic)

• LCD controller (up to 4K color STN and 256K color TFT) with 1-ch LCD-dedicated DMA

• 4-ch DMAs with external request pins

• 3-ch UART (IrDA1.0, 64-Byte Tx FIFO, and 64-Byte Rx FIFO) / 2-ch SPI

• 1-ch multi-master IIC-BUS/1-ch IIS-BUS controller

• SD Host interface version 1.0 & Multi-Media Card Protocol version 2.11 compatible

• 2-port USB Host /1- port USB Device (ver 1.1)

• 4-ch PWM timers & 1-ch internal timer

• WatchDog Timer

• 130-bit general purpose I/O ports / 24-ch external interrupt source

• Power control: Normal, Slow, Idle and Sleep mode

• 8-ch 10-bit ADC and Touch screen interface

• RTC with calendar function

• On-chip clock generator with PLL

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

1-1

Page 2

2003.10.15

PRODUCT OVERVIEW S3C2440X

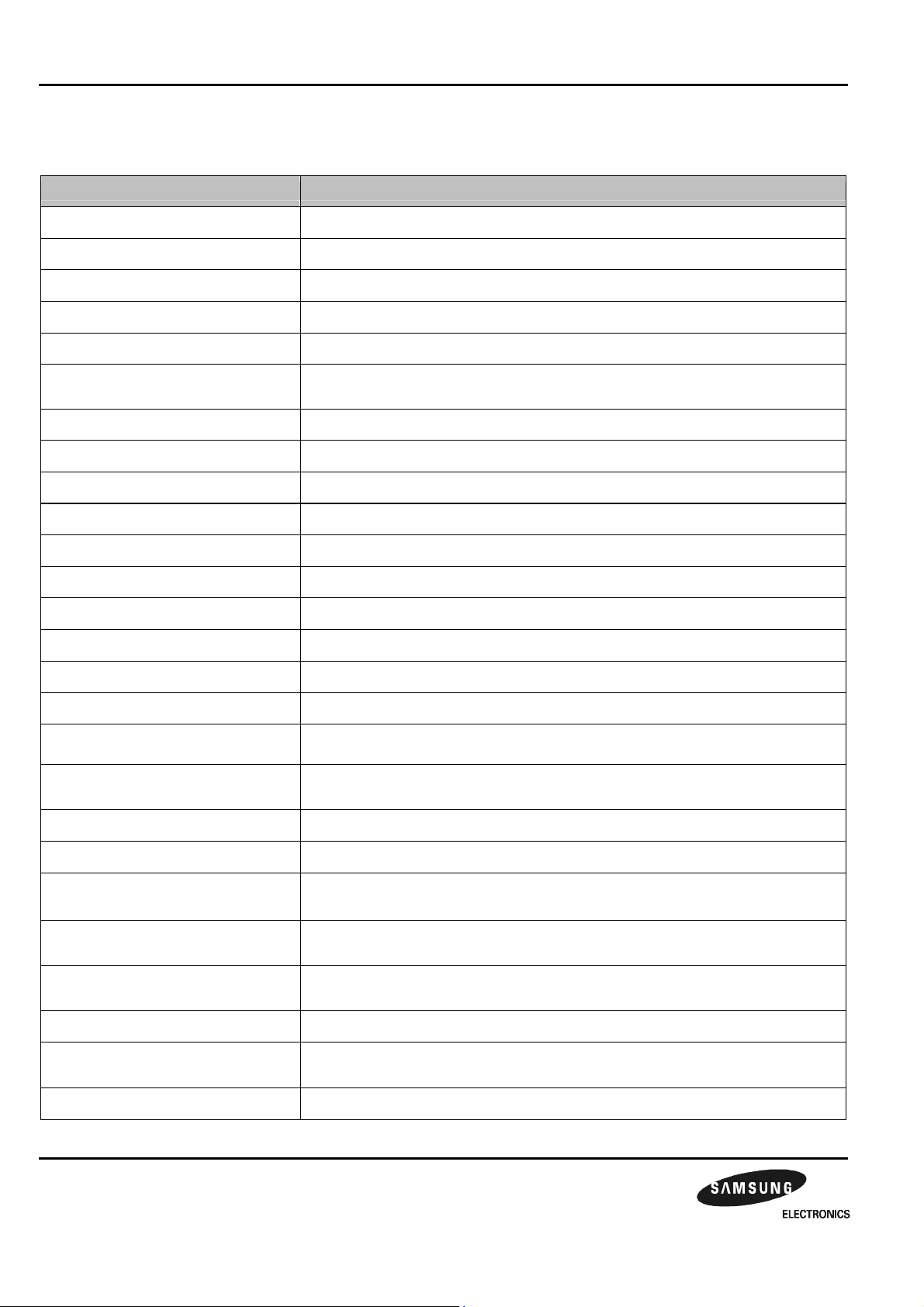

FEATURES

Architecture

• Integrated system for hand-held devices and

general embedded applications.

• 16/32-Bit RISC architecture and powerful

instruction set with ARM920T CPU core.

• Enhanced ARM architecture MMU to support

WinCE, EPOC 32 and Linux.

• Instruction cache, data cache, write buffer and

Physical address TAG RAM to reduce the effect

of main memory bandwidth and latency on

performance.

• ARM920T CPU core supports the ARM debug

architecture.

• Internal Advanced Microcontroller Bus

Architecture (AMBA) (AMBA2.0, AHB/APB).

System Manager

• Little/Big Endian support.

• Address space: 128M bytes for each bank (total

1G bytes).

• Supports programmable 8/16/32-bit data bus

width for each bank.

• Fixed bank start address from bank 0 to bank 6.

• Programmable bank start address and bank size

for bank 7.

• Eight memory banks:

– Six memory banks for ROM, SRAM, and others.

– Two memory banks for ROM/SRAM/

Synchronous DRAM.

• Complete Programmable access cycles for all

memory banks.

• Supports external wait signals to expend the bus

cycle.

• Supports self-refresh mode in SDRAM for power-

down.

NAND Flash Boot Loader

• Supports booting from NAND flash memory.

• 4KB internal buffer for booting.

• Supports storage memory for NAND flash

memory after booting.

• Supports Advanced NAND flash

Cache Memory

• 64-way set-associative cache with I-Cache

(16KB) and D-Cache (16KB).

• 8words length per line with one valid bit and two

dirty bits per line.

• Pseudo random or round robin replacement

algorithm.

• Write-through or write-back cache operation to

update the main memory.

• The write buffer can hold 16 words of data and

four addresses.

Clock & Power Manager

• On-chip MPLL and UPLL:

UPLL generates the clock to operate USB

Host/Device.

MPLL generates the clock to operate MCU at

maximum 400Mhz@ 1.2V.

• Clock can be fed selectively to each function

block by software.

• Power mode: Normal, Slow, Idle, and Sleep

mode

Normal mode: Normal operating mode

Slow mode: Low frequency clock without PLL

Idle mode: The clock for only CPU is stopped.

Sleep mode: The Core power including all

peripherals is shut down.

• Woken up by EINT[15:0] or RTC alarm interrupt

from Sleep mode

• Supports various types of ROM for booting

(NOR/NAND Flash, EEPROM, and others).

1-2

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

Page 3

2003.10.15

S3C2440X PRODUCT OVERVIEW

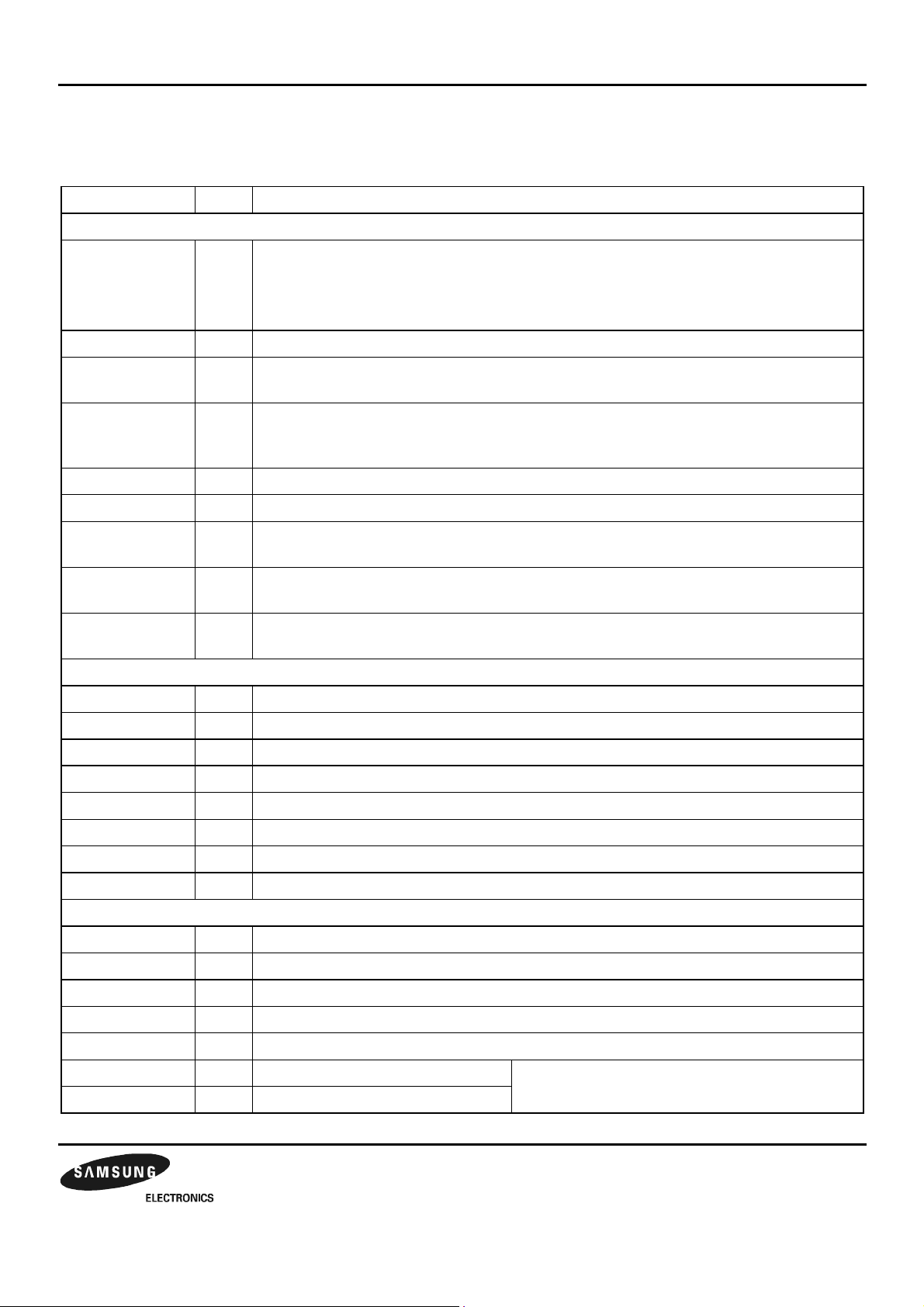

FEATURES (Continued)

Interrupt Controller

• 59 Interrupt sources

(One Watch dog timer, 5 timers, 9 UARTs, 24

external interrupts, 4 DMA, 2 RTC, 2 ADC, 1 IIC,

2SPI,1SDI,2USB,1LCD, 1BatteryFault,1

NAND and 2 Camera)

• Level/Edge mode on external interrupt source

• Programmable polarity of edge and level

• Supports Fast Interrupt request (FIQ) for very

urgent interrupt request

Timer with Pulse Width Modulation (PWM)

• 4-ch 16-bit Timer with PWM / 1-ch 16-bit internal

timer with DMA-based or interrupt-based

operation

• Programmable duty cycle, frequency, and polarity

• Dead-zone generation

• Supports external clock sources

RTC (Real Time Clock)

• Full clock feature: msec, second, minute, hour,

date, day, month, and year

• 32.768 KHz operation

• Alarm interrupt

• Time tick interrupt

General Purpose Input/Output Ports

64-byte Rx FIFO.

DMA Controller

• 4-ch DMA controller

• Supports memory to memory, IO to memory,

memory to IO, and IO to IO transfers

• Burst transfer mode to enhance the transfer rate

A/D Converter & Touch Screen Interface

• 8-ch multiplexed ADC

• Max. 500KSPS and 10-bit Resolution

• Internal FET for direct Touch screen interface

LCD Controller STN LCD Displays Feature

• Supports 3 types of STN LCD panels: 4-bit dual

scan, 4-bit single scan, 8-bit single scan display

type

• Supports monochrome mode, 4 gray levels, 16

gray levels, 256 colors and 4096 colors for STN

LCD

• Supports multiple screen size

– Maximum screen size: 2048x1024

– Recommended screen size: max 800x600

– Maximum virtual screen size is 4 Mbytes.

– Maximum virtual screen size in 256 color mode:

4096x1024, 2048x2048, 1024x4096 and others

• 24 external interrupt ports

• Multiplexed input/output ports

UART

• 3-channel UART with DMA-based or interrupt-

based operation

• Supports 5-bit, 6-bit, 7-bit, or 8-bit serial data

transmit/receive (Tx/Rx)

• Supports external clocks for the UART operation

(UARTCLK)

• Programmable baud rate

• Supports IrDA 1.0

• Loopback mode for testing

• Each channel has internal 64-byte Tx FIFO and

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

TFT(Thin Film Transistor) Color Displays Feature

• Supports 1, 2, 4 or 8 bpp (bit-per-pixel) palette

color displays for color TFT

• Supports 16 bpp non-palette true-color displays

for color TFT

• Supports maximum 16M color TFT at 24 bpp

mode

• Supports multiple screen size

– Maximum screen size: 2048x1024

– Recommended screen size: max 800x600

– Maximum virtual screen size is 4Mbytes.

– Maximum virtual screen size in 64K color mode:

2048x1024, and others

1-3

Page 4

2003.10.15

PRODUCT OVERVIEW S3C2440X

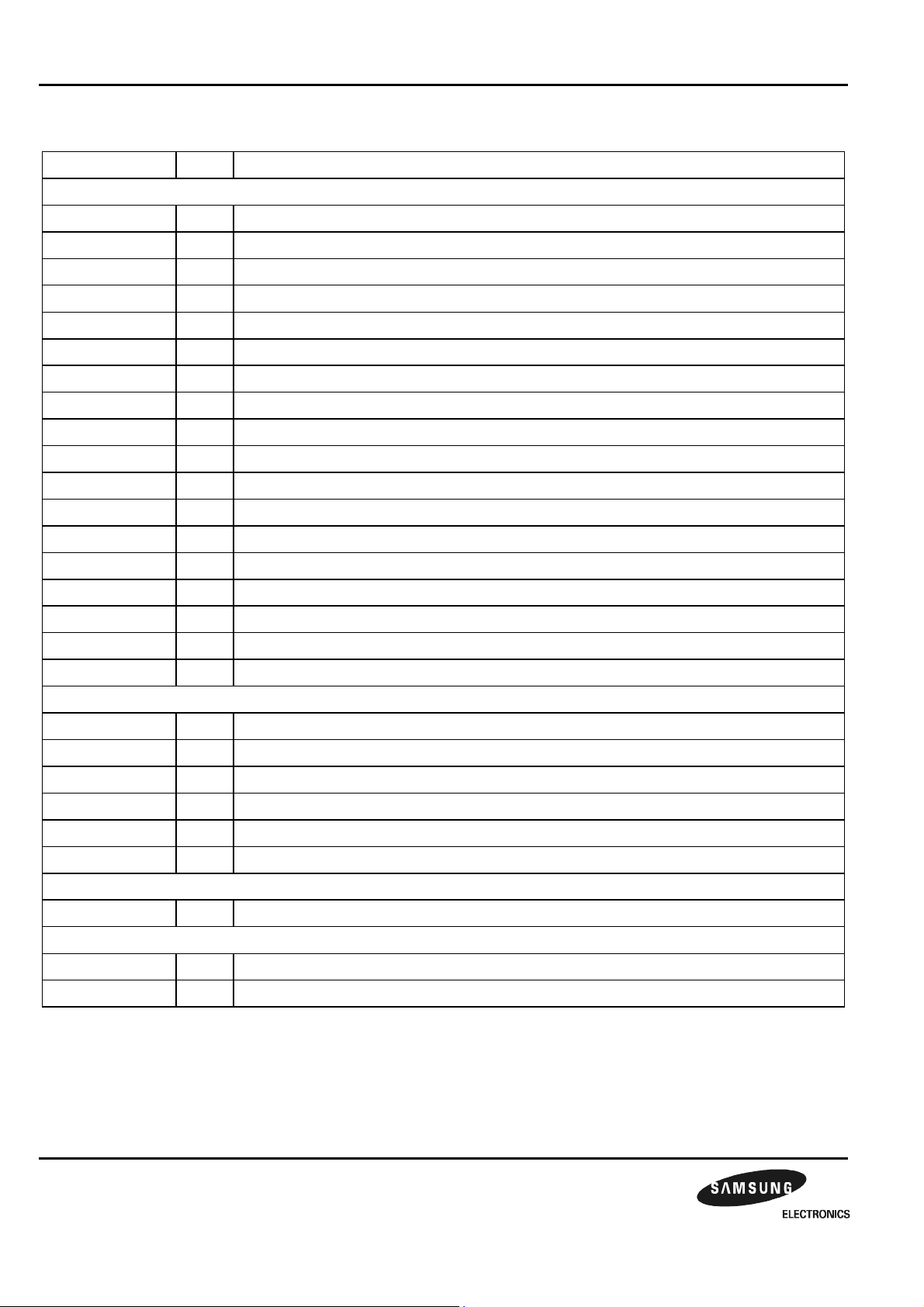

FEATURES (Continued)

Watchdog Timer

• 16-bit Watchdog Timer

• Interrupt request or system reset at time-out

IIC-Bus Interface

• 1-ch Multi-Master IIC-Bus

• Serial, 8-bit oriented and bi-directional data

transferscanbemadeatupto100Kbit/sin

Standard mode or up to 400 Kbit/s in Fast mode.

IIS-Bus Interface

• 1-ch IIS-bus for audio interface with DMA-based

operation

• Serial, 8-/16-bit per channel data transfers

• 128 Bytes (64-Byte + 64-Byte) FIFO for Tx/Rx

• Supports IIS format and MSB-justified data format

USB Host

• 2-port USB Host

• Complies with OHCI Rev. 1.0

• Compatible with USB Specification version 1.1

• Compatible with SDIO Card Protocol version 1.0

• Bytes FIFO for Tx/Rx

• DMA based or Interrupt based operation

• Compatible with Multimedia Card Protocol version

2.11

SPI Interface

• Compatible with 2-ch Serial Peripheral Interface

Protocol version 2.11

• 2x8 bits Shift register for Tx/Rx

• DMA-based or interrupt-based operation

Camera Interface

• ITU601/ITU656-format input support (8-bit)

• YCrCb 4:2:2 to 4:2:0 down-sampling

• Up to 1016 Horizontal resolution support

Operating Voltage Range

• Core: 1.2V

• Memory :1.8V/ 2.5V/3.3V

• I/O : 3.3V

USB Device

• 1-port USB Device

• 5 Endpoints for USB Device

• Compatible with USB Specification version 1.1

SD Host Interface

• Compatible with SD Memory Card Protocol

version 1.0

Operating Frequency

• Up to 400MHz

Package

• 289-FBGA

1-4

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

Page 5

2003.10.15

S3C2440X PRODUCT OVERVIEW

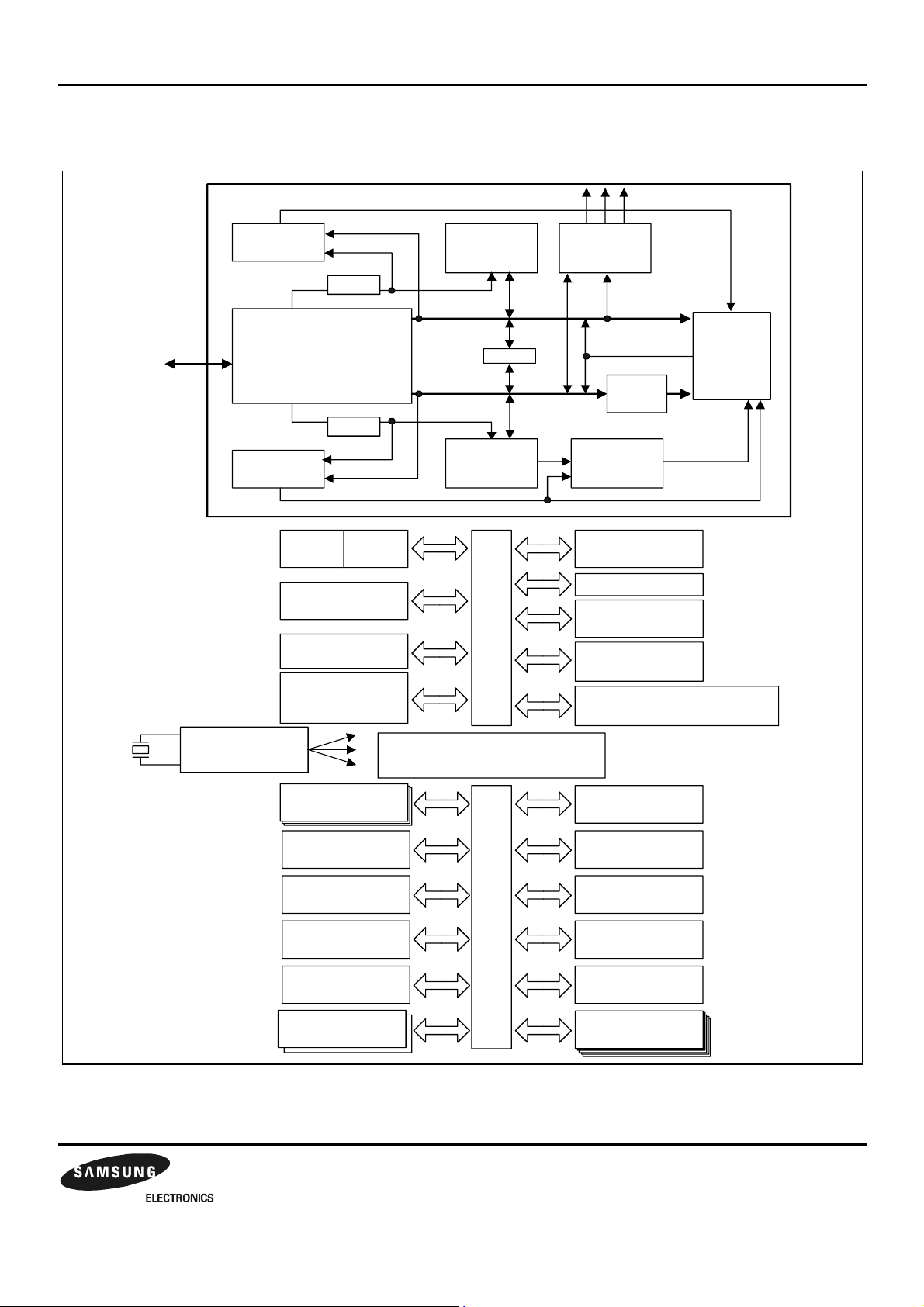

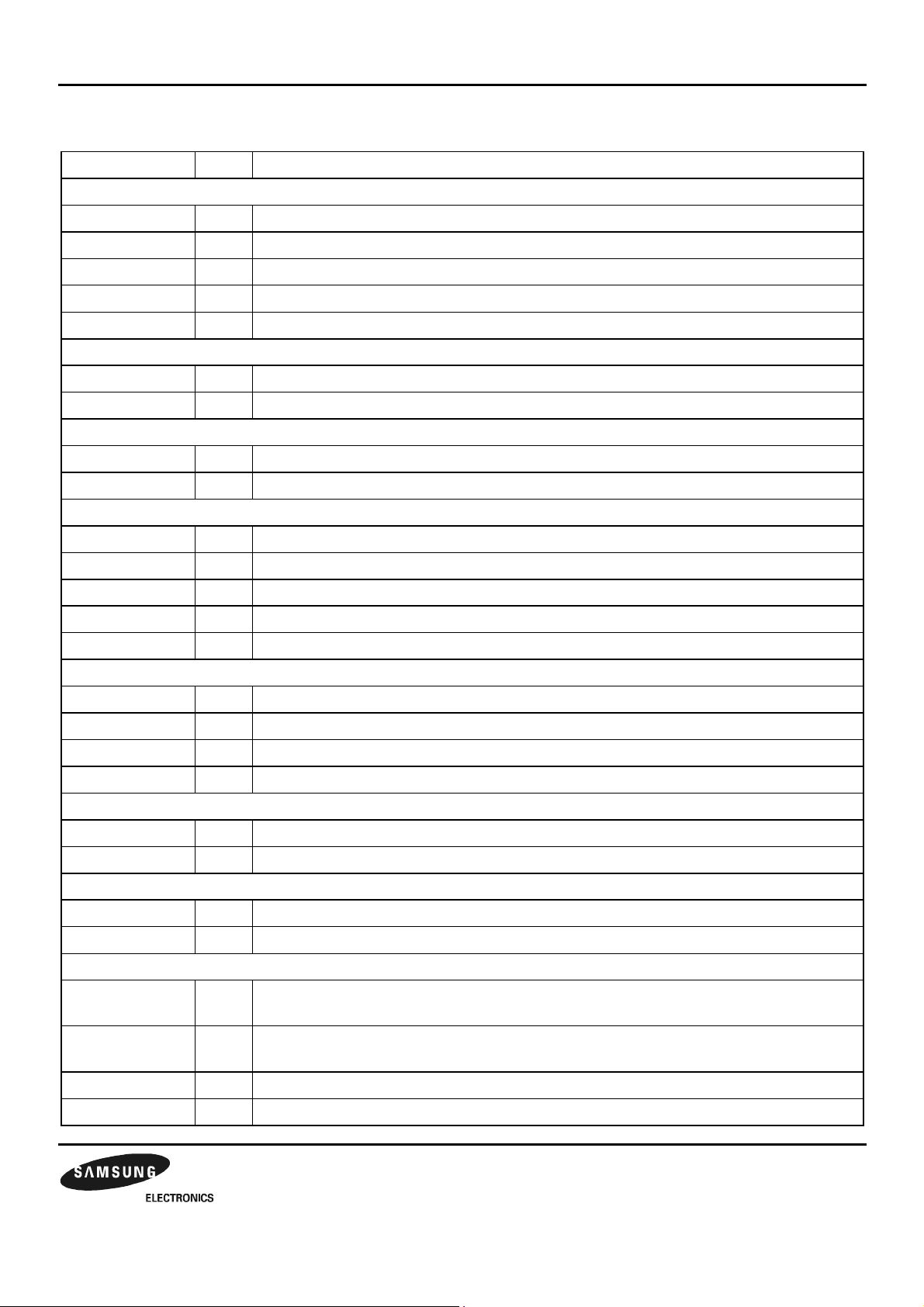

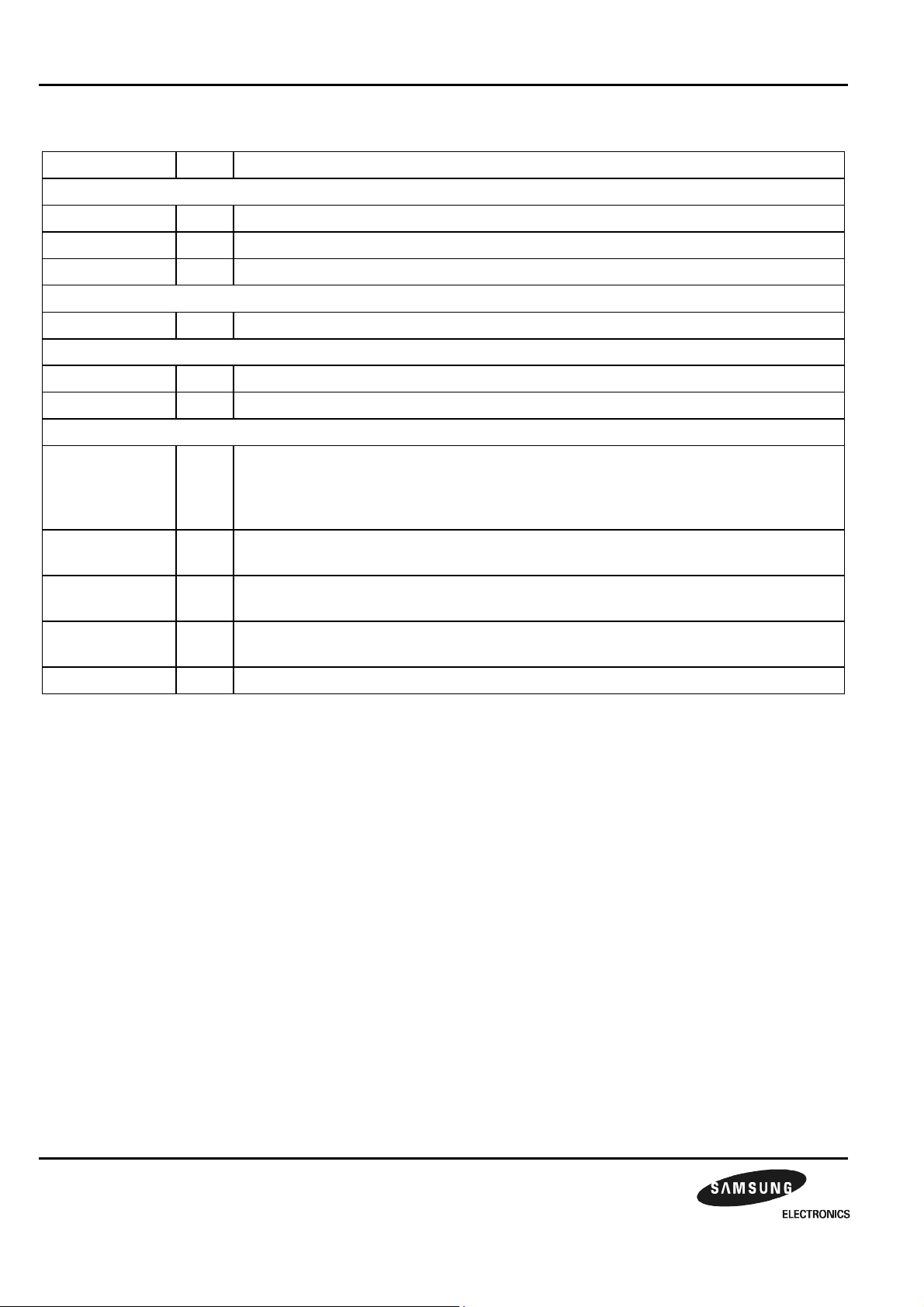

BLOCK DIAGRAM

JTAG

ARM920T

Instruction

MMU

2

A[31:0]

IV

ARM9TDMI

Processor core

(Internal Embedded ICE)

Data

MMU

LCD

CONT.

USB Host CONT.

ExtMaster

NAND Ctrl.

NAND Flash Boot

Loader

C13

C13

IPA[31:0]

DPA[31:0]

LCD

DMA

Instruction

ID[31:0]

DD[31:0]

DVA[31:0]DV2A[31:0]

CACHE

(16KB)

CP15

Data

CACHE

(16KB)

A

H

B

B

U

S

External

Coproc

Interface

Write

Buffer

WriteBack

PA Tag

RAM

BUS CONT.

Arbitor/Decode

Interrupt CONT.

Power

Management

Camera

Interface

Memory CONT.

SRAM/NOR/SDRAM

AMBA

Bus

I/F

WBPA[31:0]

Clock Generator

(MPLL)

Bridge & DMA (4Ch)

UART 0, 1, 2

USB Device

A

P

SDI/MMC

Watchdog

Timer

BUS CONT.

Arbitor/Decode

SPI0,1

SPI

Figure 1-1. S3C2440X Block Diagram

B

B

U

S

I2C

I2S

GPIO

RTC

ADC

Timer/PWM

0 ~ 3, 4(Internal)

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

1-5

Page 6

2003.10.15

PRODUCT OVERVIEW S3C2440X

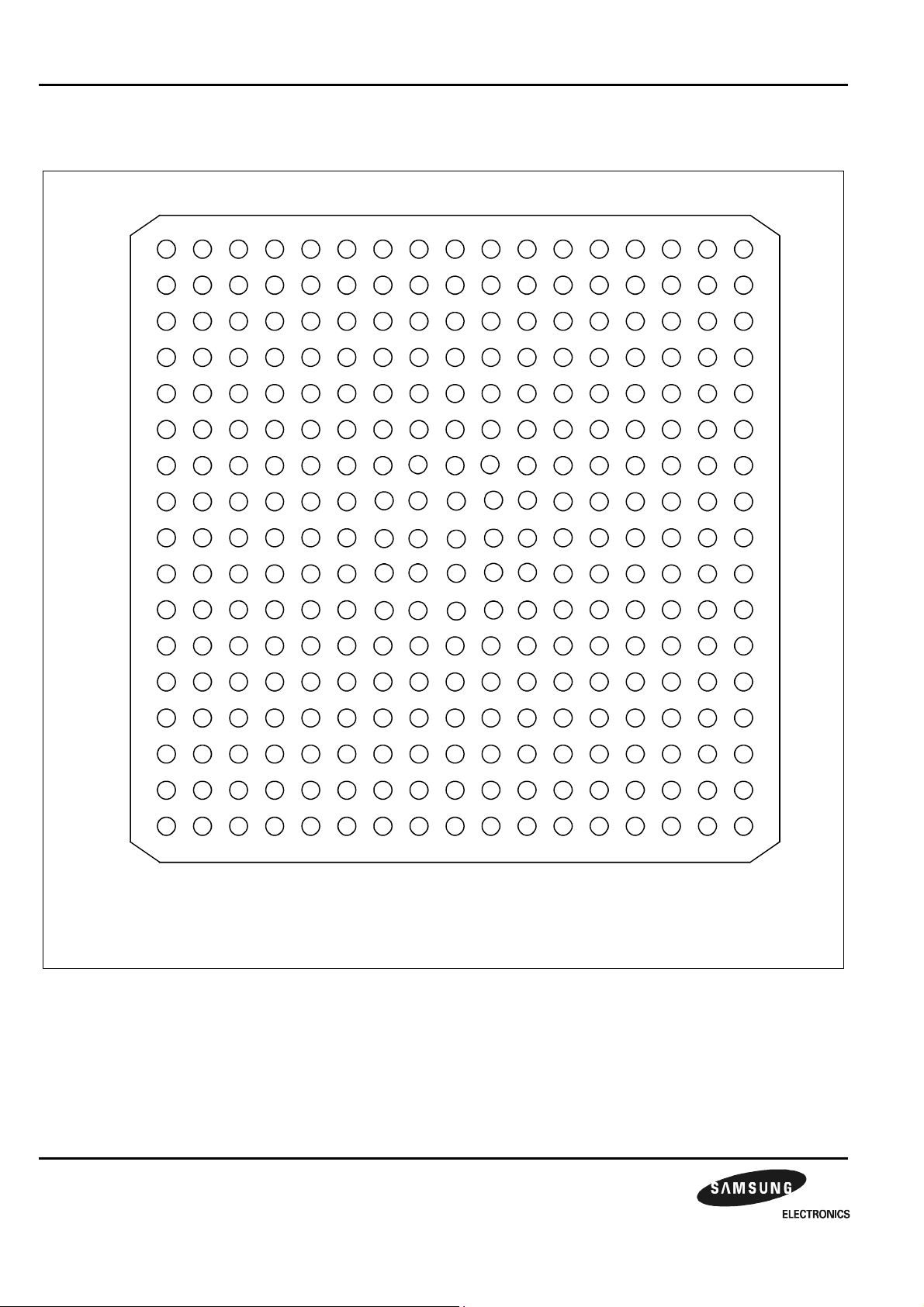

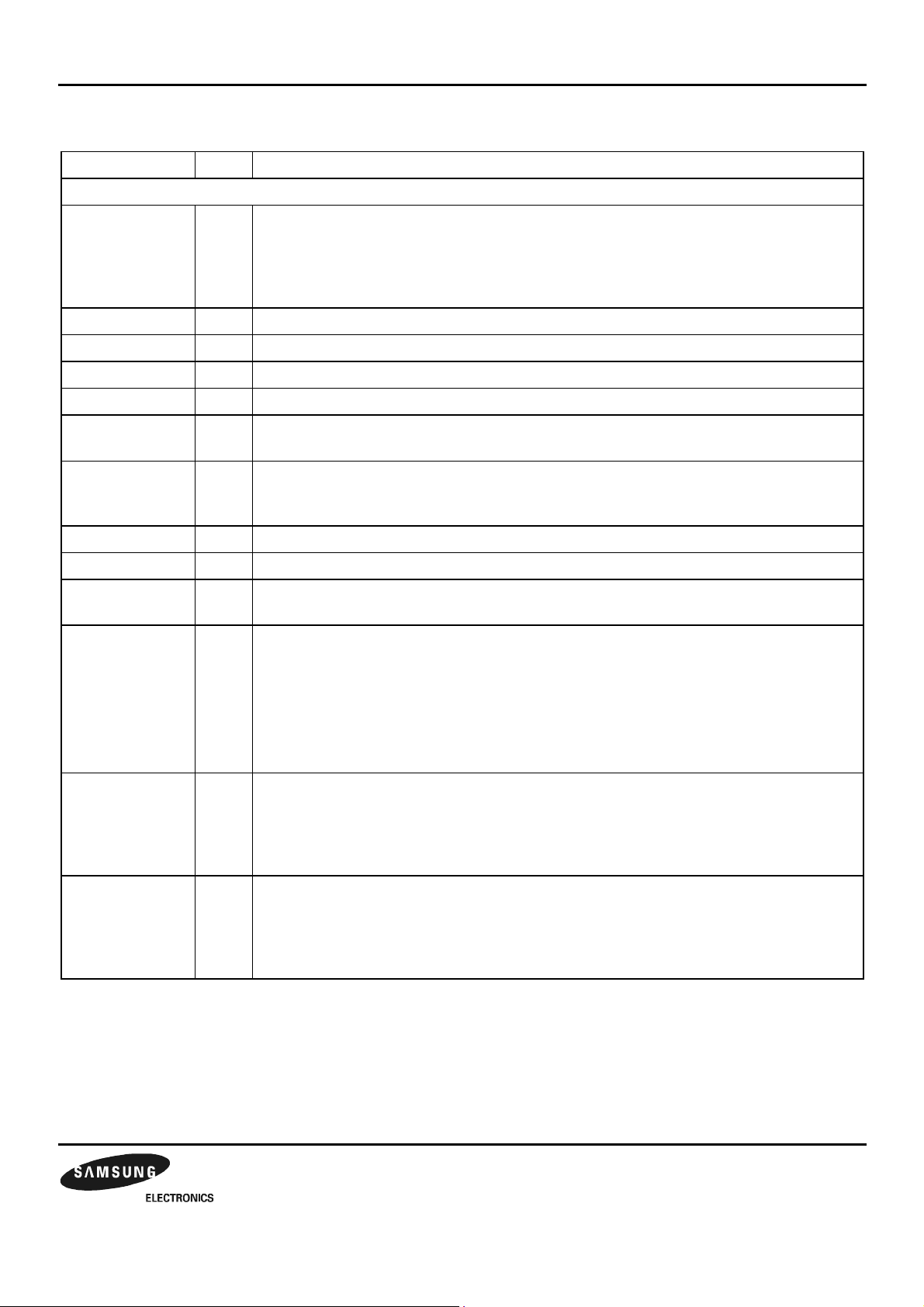

PIN ASSIGNMENTS

U

T

R

P

N

M

L

K

J

H

G

F

E

D

C

B

A

1234567891011121314151617

1-6

BOTTOM VIEW

Figure 1-2. S3C2440X Pin Assignments (289-FBGA)

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

Page 7

2003.10.15

S3C2440X PRODUCT OVERVIEW

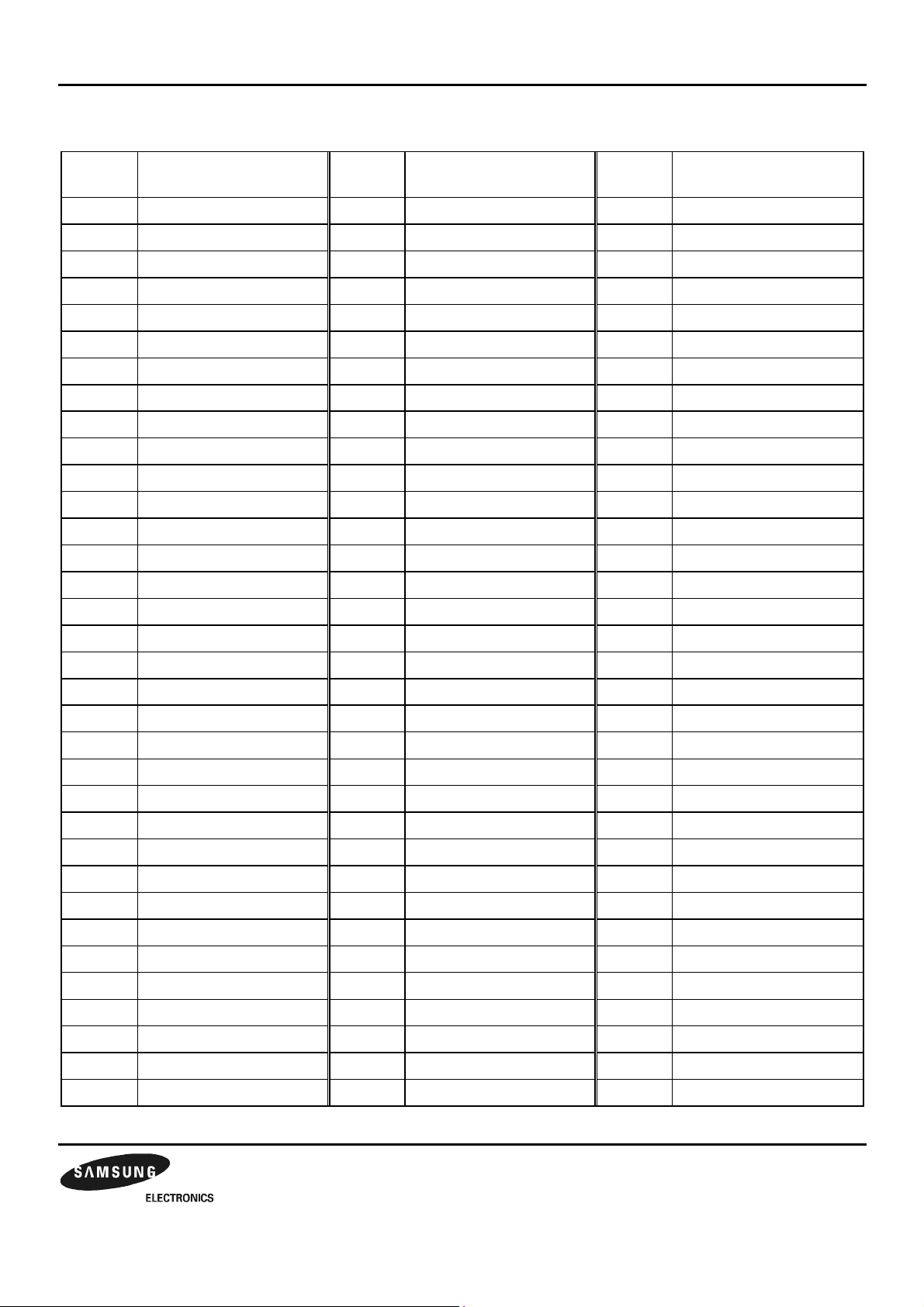

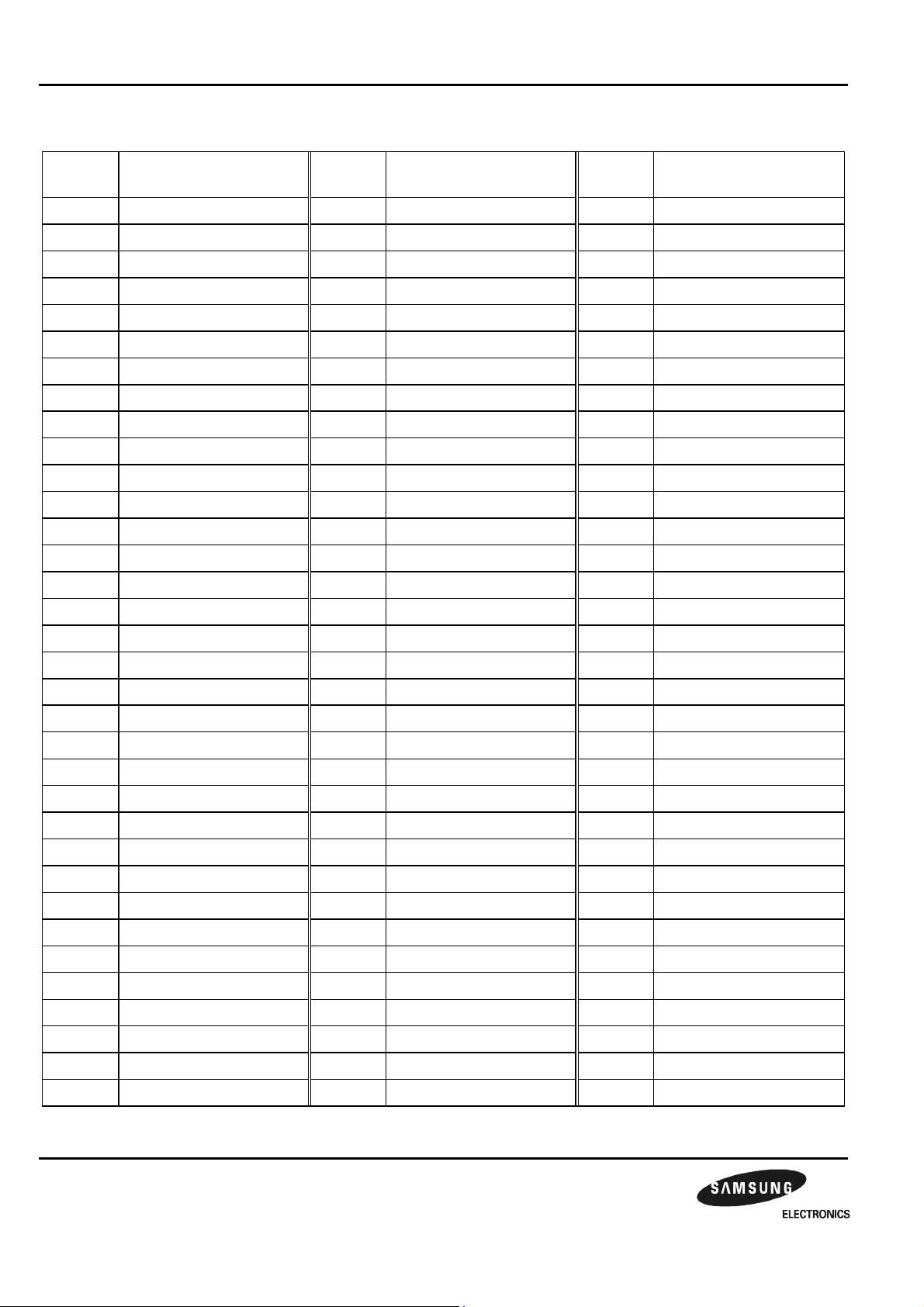

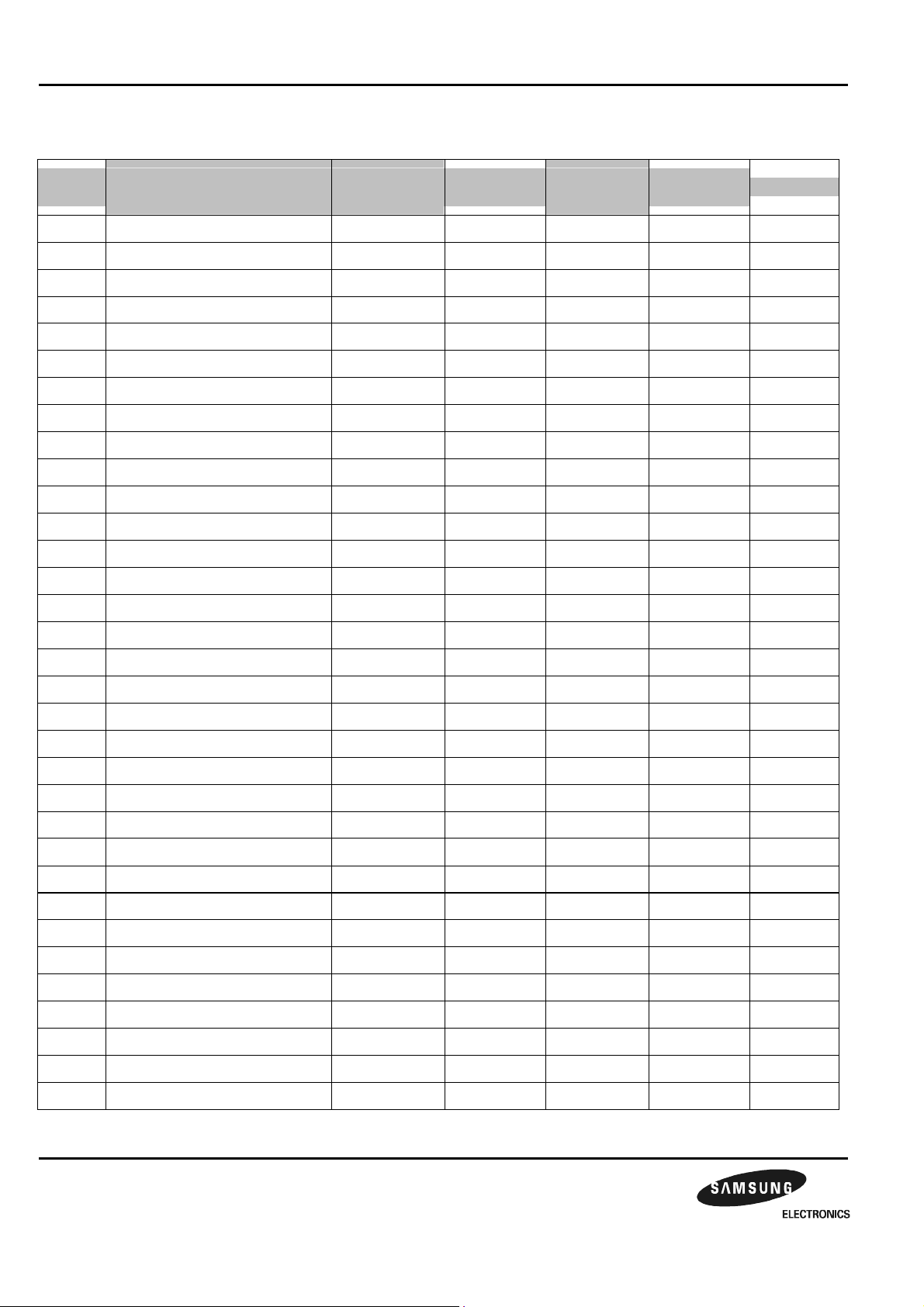

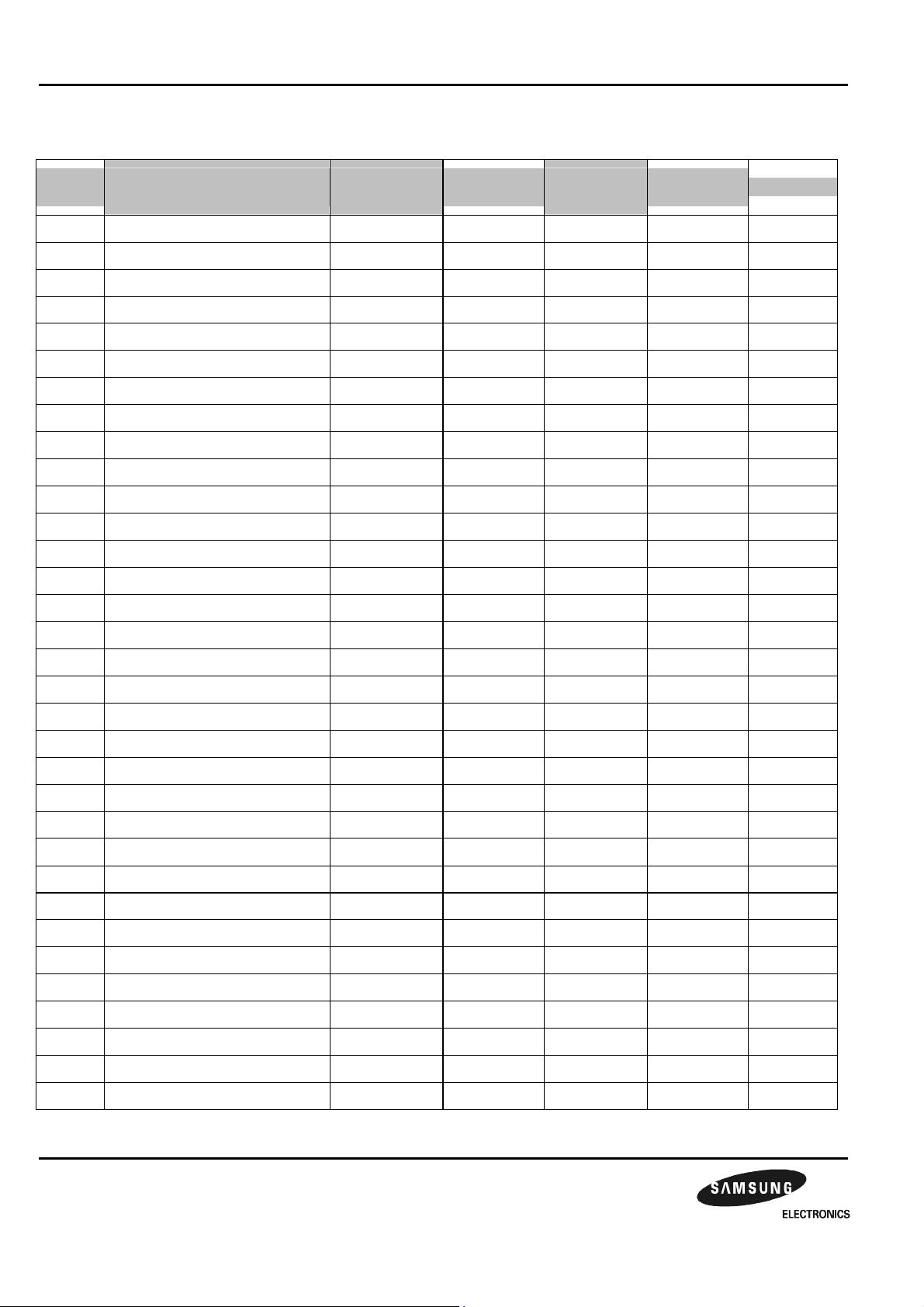

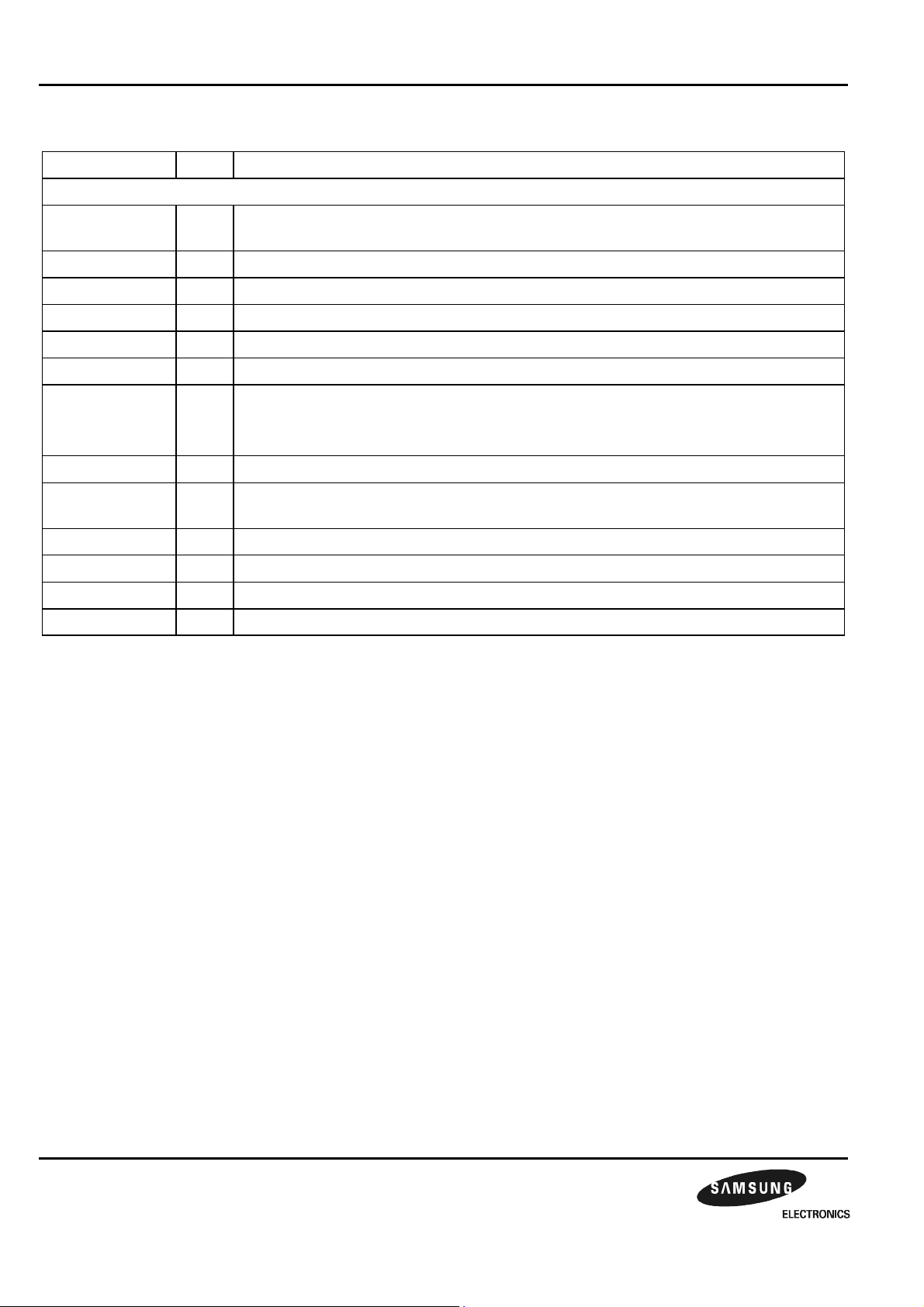

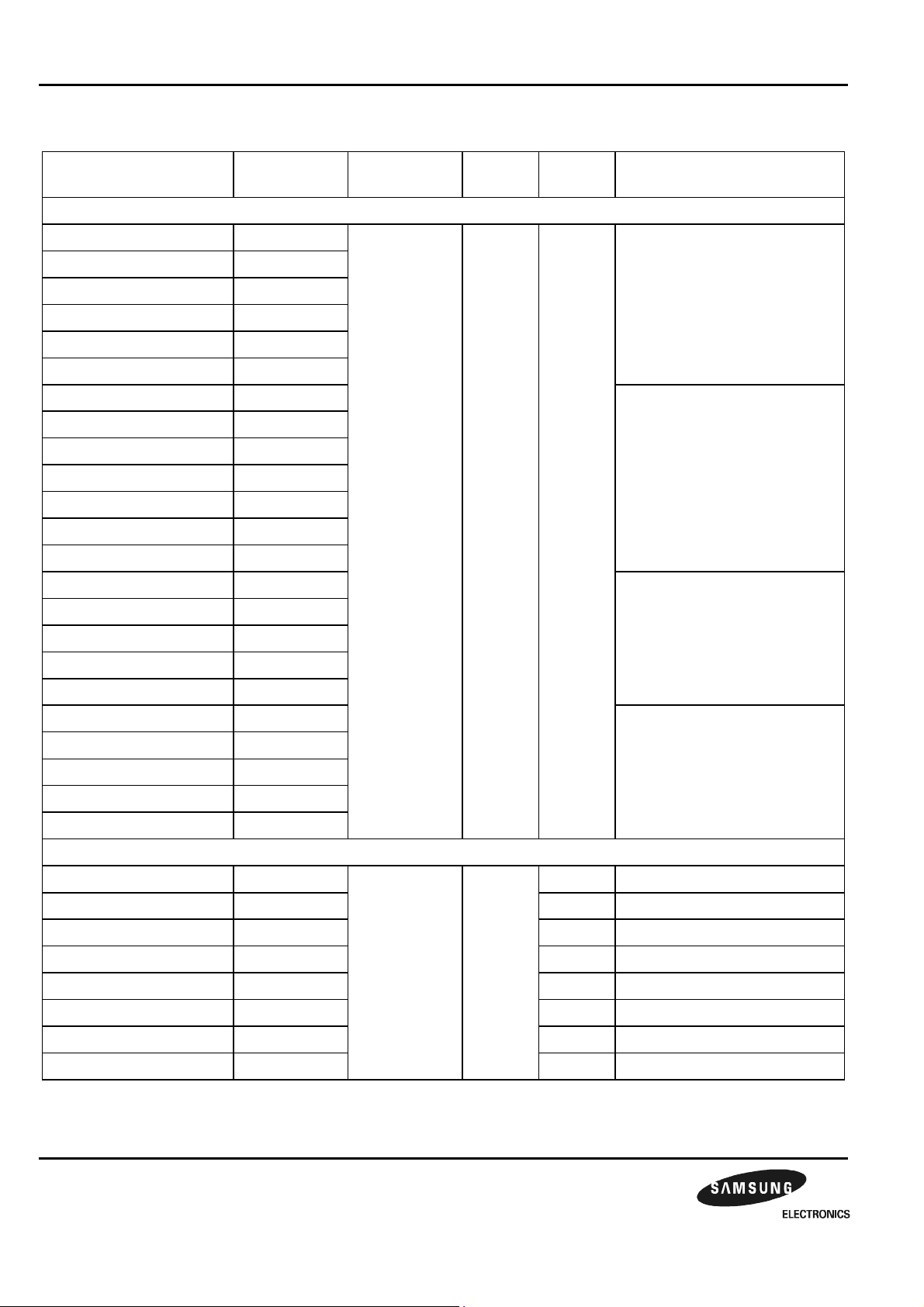

Table 1-1. 289-Pin FBGA Pin Assignments – Pin Number Order (Sheet 1 of 3)

Pin

Number

Pin Name Pin

Number

Pin Name Pin

Number

Pin Name

A1 VDDi C1 VDDMOP E1 nFRE/GPA20

A2 SCKE C2 nGCS5/GPA16 E2 VSSMOP

A3 VSSi C3 nGCS2/GPA13 E3 nGCS7

A4 VSSi C4 nGCS3/GPA14 E4 nWAIT

A5 VSSMOP C5 nOE E5 nBE3

A6 VDDi C6 nSRAS E6 nWE

A7 VSSMOP C7 ADDR4 E7 ADDR1

A8 ADDR10 C8 ADDR11 E8 ADDR6

A9 VDDMOP C9 ADDR15 E9 ADDR14

A10 VDDi C10 ADDR21/GPA6 E10 ADDR23/GPA8

A11 VSSMOP C11 ADDR24/GPA9 E11 DATA2

A12 VSSi C12 DATA1 E12 DATA20

A13 DATA3 C13 DATA6 E13 DATA19

A14 DATA7 C14 DATA11 E14 DATA18

A15 VSSMOP C15 DATA13 E15 DATA17

A16 VDDi C16 DATA16 E16 DATA21

A17 DATA10 C17 VSSi E17 DATA24

B1 VSSMOP D1 ALE/GPA18 F1 VDDi

B2 nGCS1/GPA12 D2 nGCS6 F2 VSSi

B3 SCLK1 D3 nGCS4/GPA15 F3 nFWE/GPA19

B4 SCLK0 D4 nBE0 F4 nFCE/GPA22

B5 nBE1 D5 nBE2 F5 CLE/GPA17

B6 VDDMOP D6 nSCAS F6 nGCS0

B7 ADDR2 D7 ADDR7 F7 ADDR0/GPA0

B8 ADDR9 D8 ADDR5 F8 ADDR3

B9 ADDR12 D9 ADDR16/GPA1 F9 ADDR18/GPA3

B10 VSSi D10 ADDR20/GPA5 F10 DATA4

B11 VDDi D11 ADDR26/GPA11 F11 DATA5

B12 VDDMOP D12 DATA0 F12 DATA27

B13 VSSMOP D13 DATA8 F13 DATA31

B14 VDDMOP D14 DATA14 F14 DATA26

B15 DATA9 D15 DATA12 F15 DATA22

B16 VDDMOP D16 VSSMOP F16 VDDi

B17 DATA15 D17 VSSMOP F17 VDDMOP

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

1-7

Page 8

2003.10.15

PRODUCT OVERVIEW S3C2440X

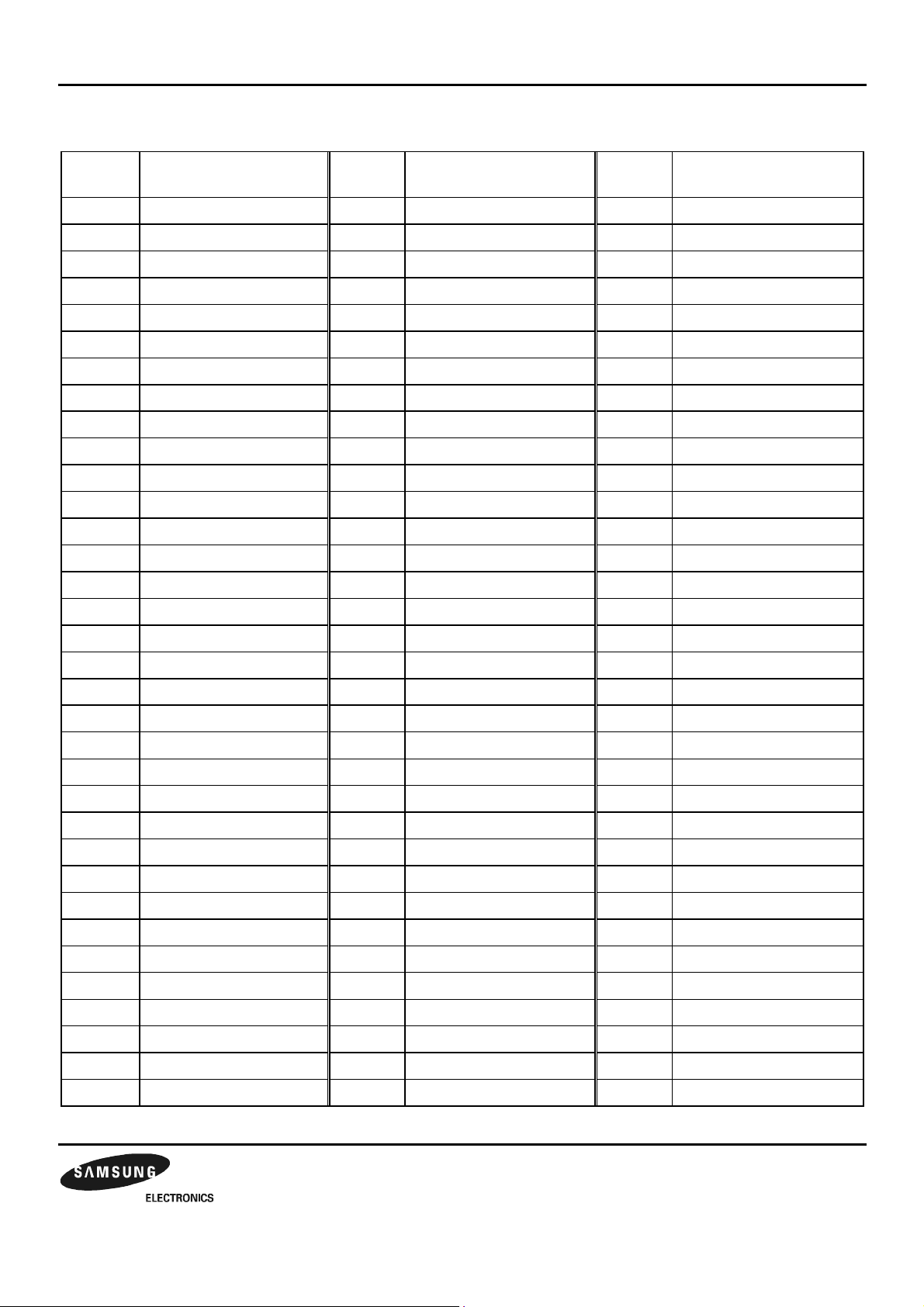

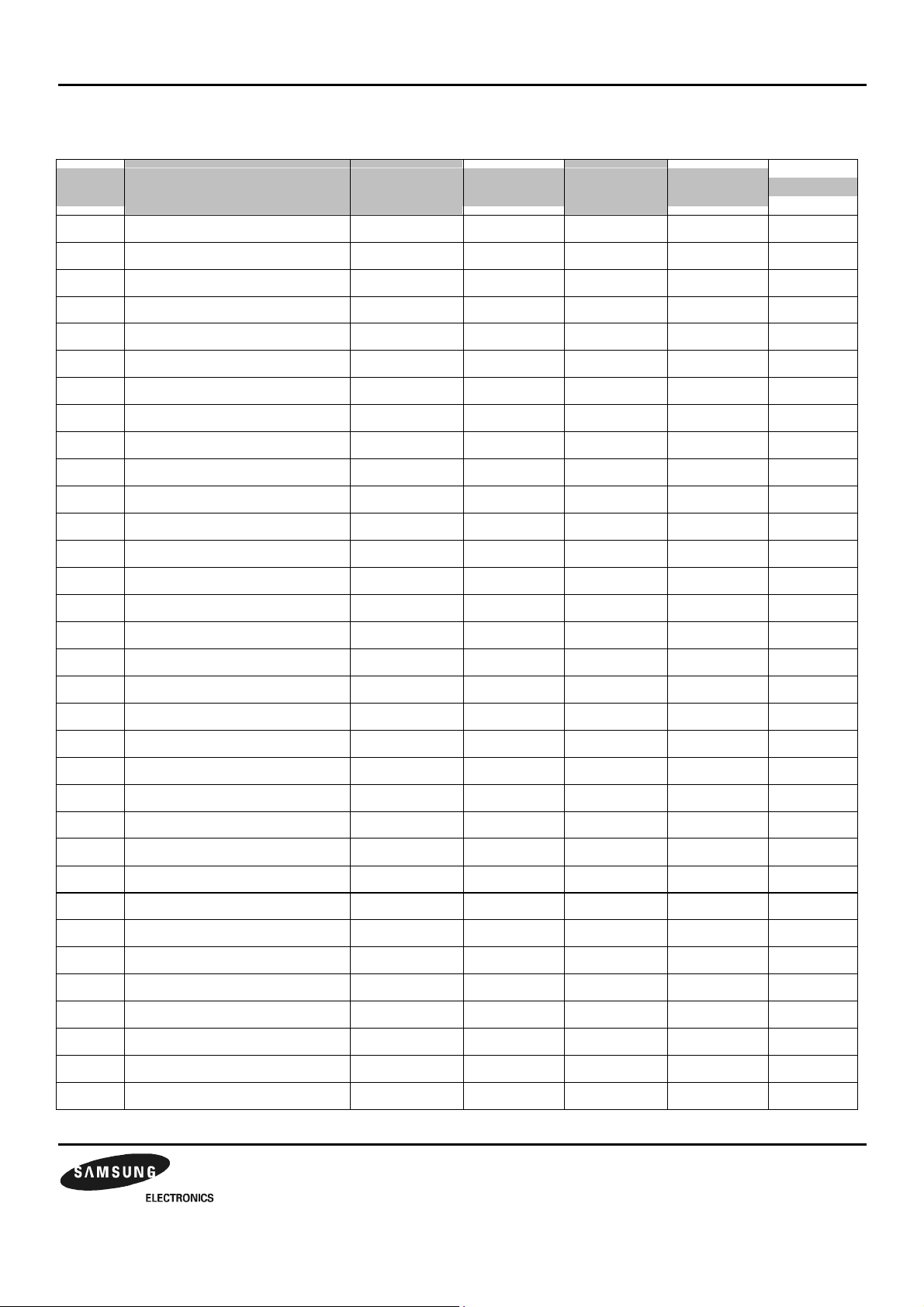

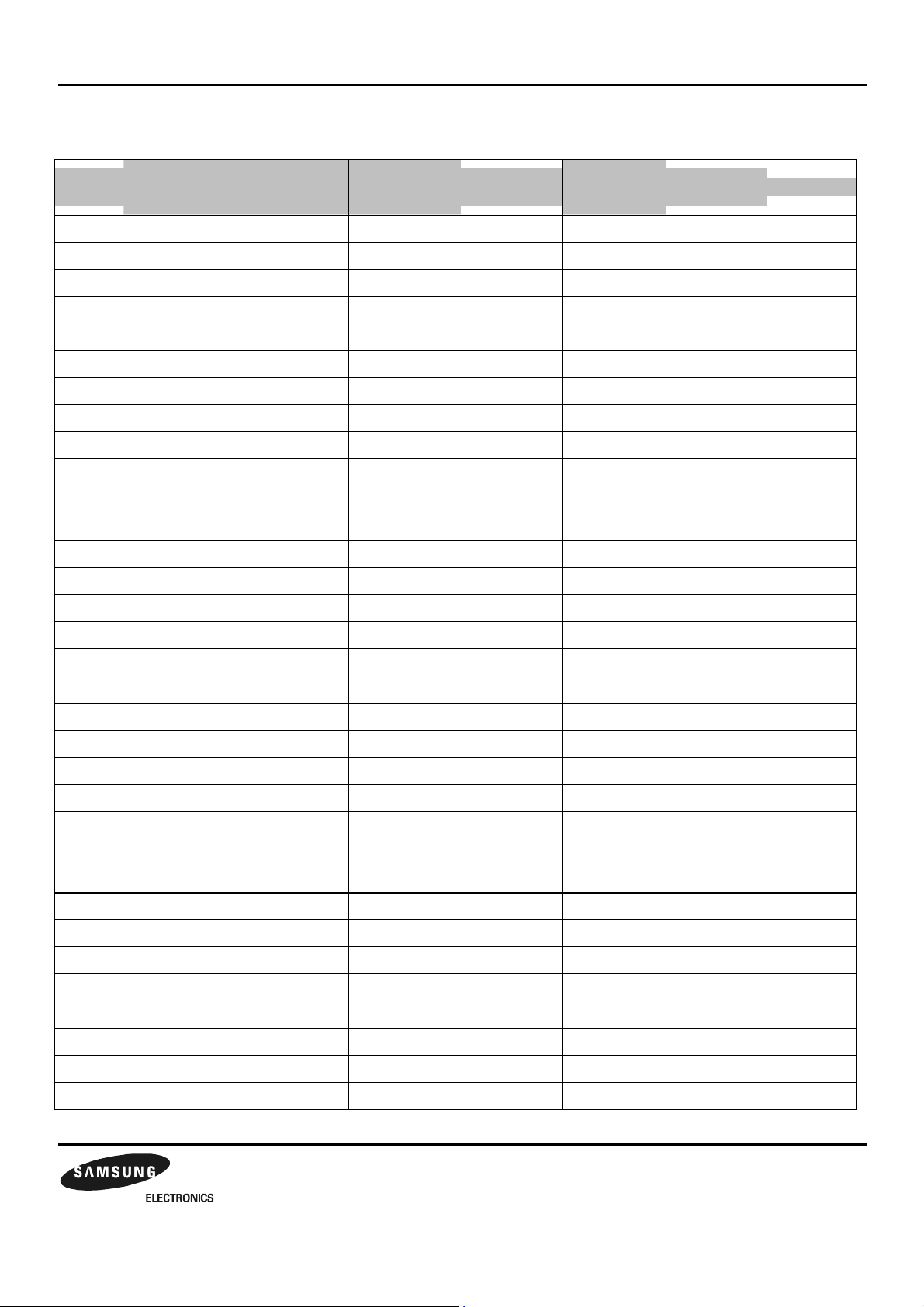

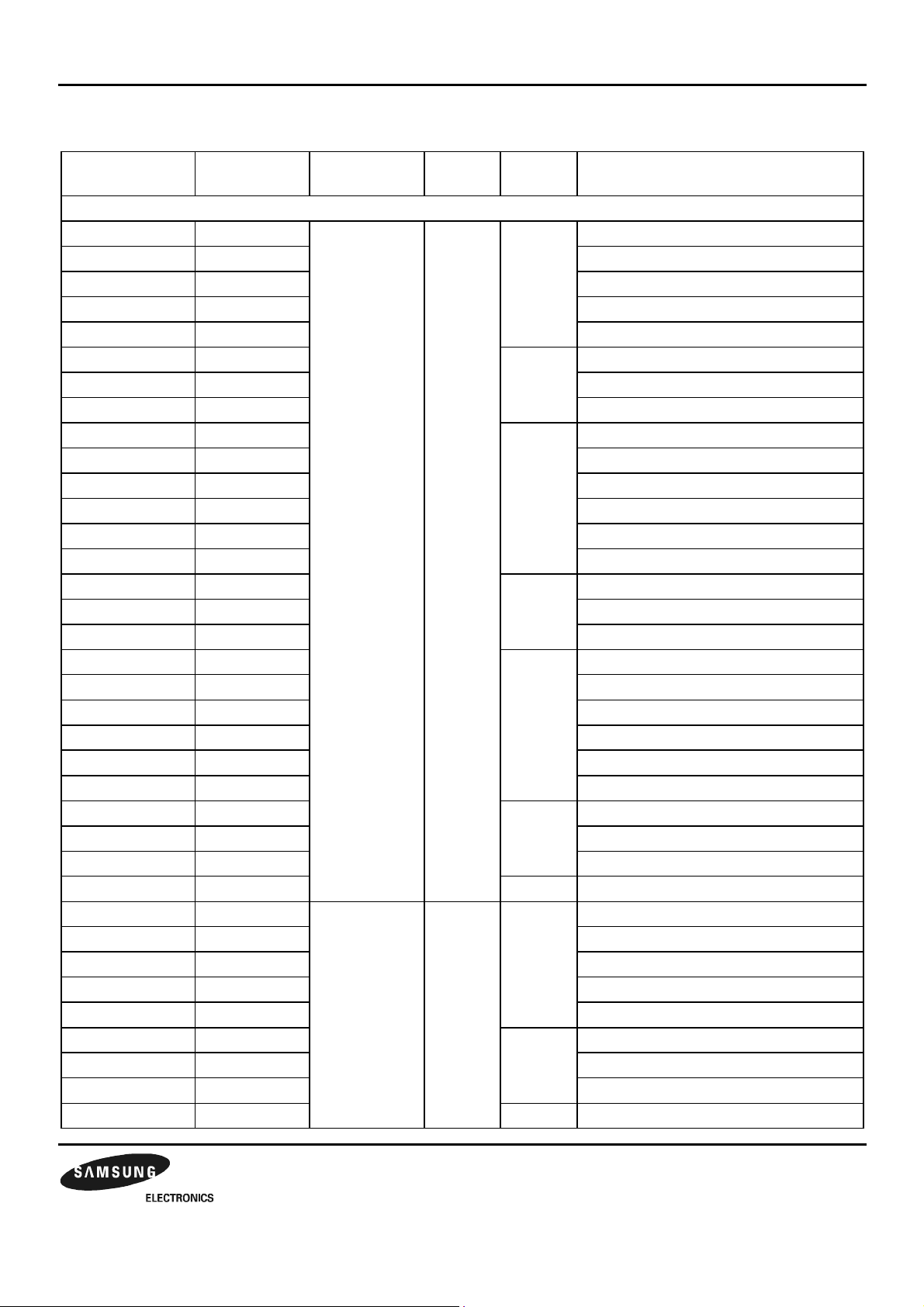

Table 1-1. 289-Pin FBGA Pin Assignments – Pin Number Order (Sheet 2 of 3)

Pin

Number

Pin Name Pin

Number

Pin Name Pin

Number

Pin Name

G1 VSSOP J1 VDDOP L1 LEND/GPC0

G2 CAMHREF/GPJ10 J2 VDDiarm L2 VDDiarm

G3 CAMDATA1/GPJ1 J3 CAMCLKOUT/GPJ11 L3 nXDACK0/GPB9

G4 VDDalive J4 CAMRESET/GPJ12 L4 VCLK/GPC1

G5 CAMPCLK/GPJ8 J5 TOUT1/GPB1 L5 nXBREQ/GPB6

G6 FRnB J6 TOUT0/GPB0 L6 VD1/GPC9

G7 CAMVSYNC/GPJ9 J7 TOUT2/GPB2 L7 VFRAME/GPC3

G8 ADDR8 J8 CAMDATA6/GPJ6 L8 I2SSDI/nSS0/GPE3

G9 ADDR17/GPA2 J9 SDDAT3/GPE10 L9 SPICLK0/GPE13

G10 ADDR25/GPA10 J10 EINT10/nSS0/GPG2 L10 EINT15/SPICLK1/GPG7

G11 DATA28 J11 TXD2/nRTS1/GPH6 L11 EINT22/GPG14

G12 DATA25 J12 PWREN L12 Xtortc

G13 DATA23 J13 TCK L13 EINT2/GPF2

G14 XTIpll J14 TMS L14 EINT5/GPF5

G15 XTOpll J15 RXD2/nCTS1/GPH7 L15 EINT6/GPF6

G16 DATA29 J16 TDO L16 EINT7/GPF7

G17 VSSi J17 VDDalive L17 nRTS0/GPH1

H1 VSSiarm K1 VSSiarm M1 VLINE/GPC2

H2 CAMDATA7/GPJ7 K2 nXBACK/GPB5 M2 LCD_LPCREV/GPC6

H3 CAMDATA4/GPJ4 K3 TOUT3/GPB3 M3 LCD_LPCOE/GPC5

H4 CAMDATA3/GPJ3 K4 TCLK0/GPB4 M4 VM/GPC4

H5 CAMDATA2/GPJ2 K5 nXDREQ1/GPB8 M5 VD9/GPD1

H6 CAMDATA0/GPJ0 K6 nXDREQ0/GPB10 M6 VD6/GPC14

H7 CAMDATA5/GPJ5 K7 nXDACK1/GPB7 M7 VD16/SPIMISO1/GPD8

H8 ADDR13 K8 SDCMD/GPE6 M8 SDDAT1/GPE8

H9 ADDR19/GPA4 K9 SPIMISO0/GPE11 M9 IICSDA/GPE15

H10 ADDR22/GPA7 K10 EINT13/SPIMISO1/GPG5 M10 EINT20/GPG12

H11 VSSOP1 K11 nCTS0/GPH0 M11 EINT17/nRTS1/GPG9

H12 EXTCLK K12 VDDOP M12 VSSA_UPLL

H13 DATA30 K13 TXD0/GPH2 M13 VDDA_UPLL

H14 nBATT_FLT K14 RXD0/GPH3 M14 Xtirtc

H15 nTRST K15 UARTCLK/GPH8 M15 EINT3/GPF3

H16 nRESET K16 TXD1/GPH4 M16 EINT1/GPF1

H17 TDI K17 RXD1/GPH5 M17 EINT4/GPF4

1-8

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

Page 9

2003.10.15

S3C2440X PRODUCT OVERVIEW

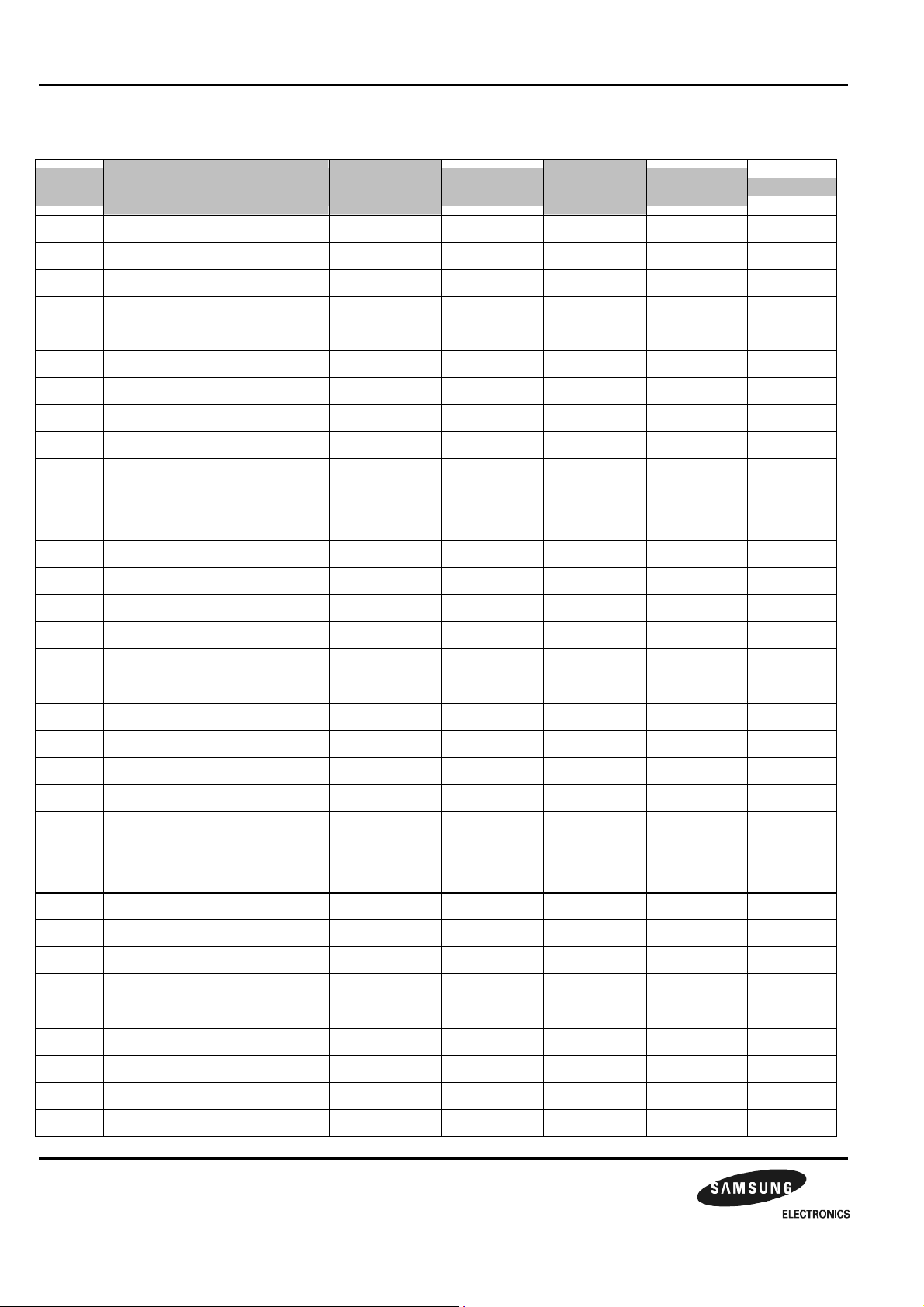

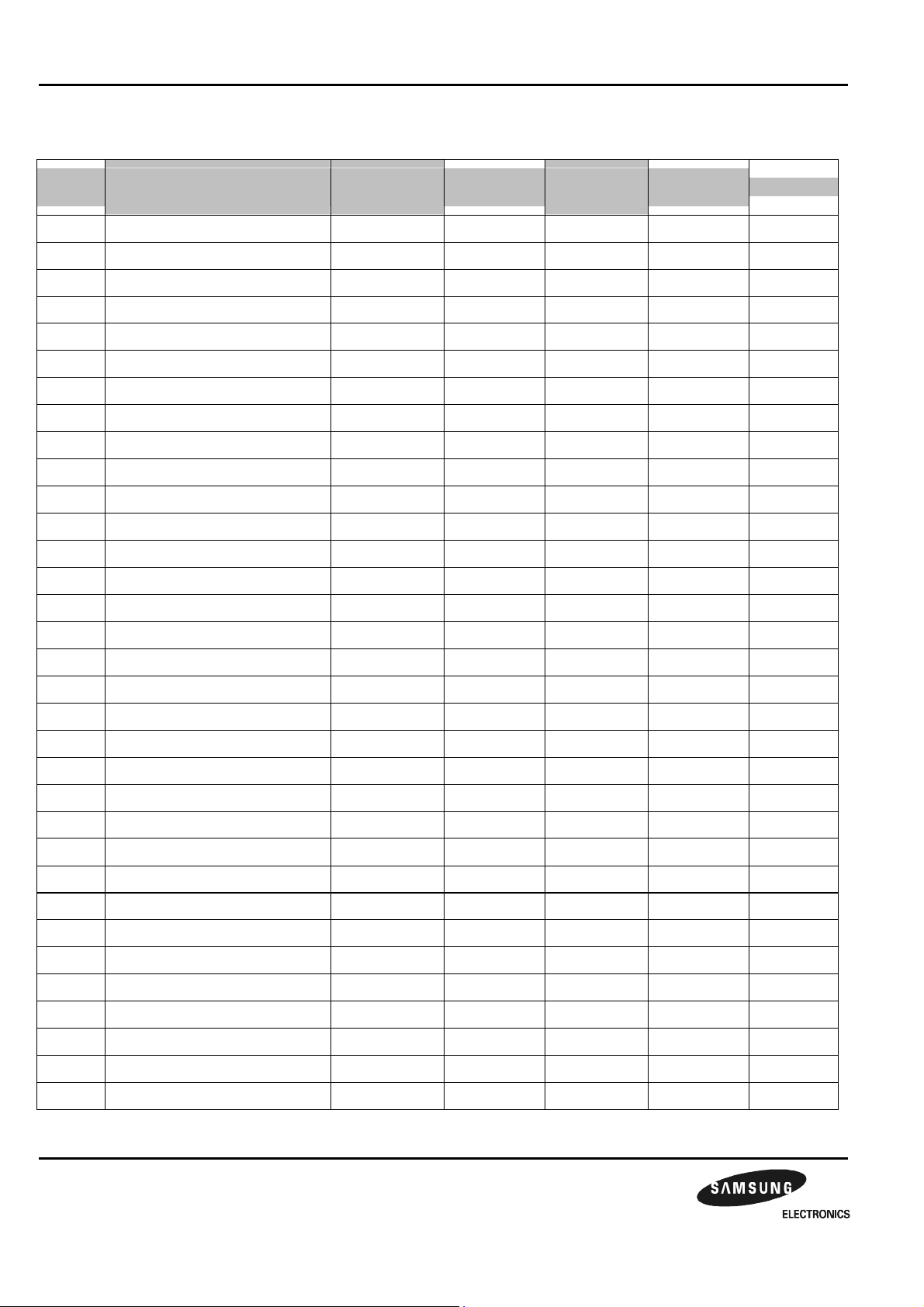

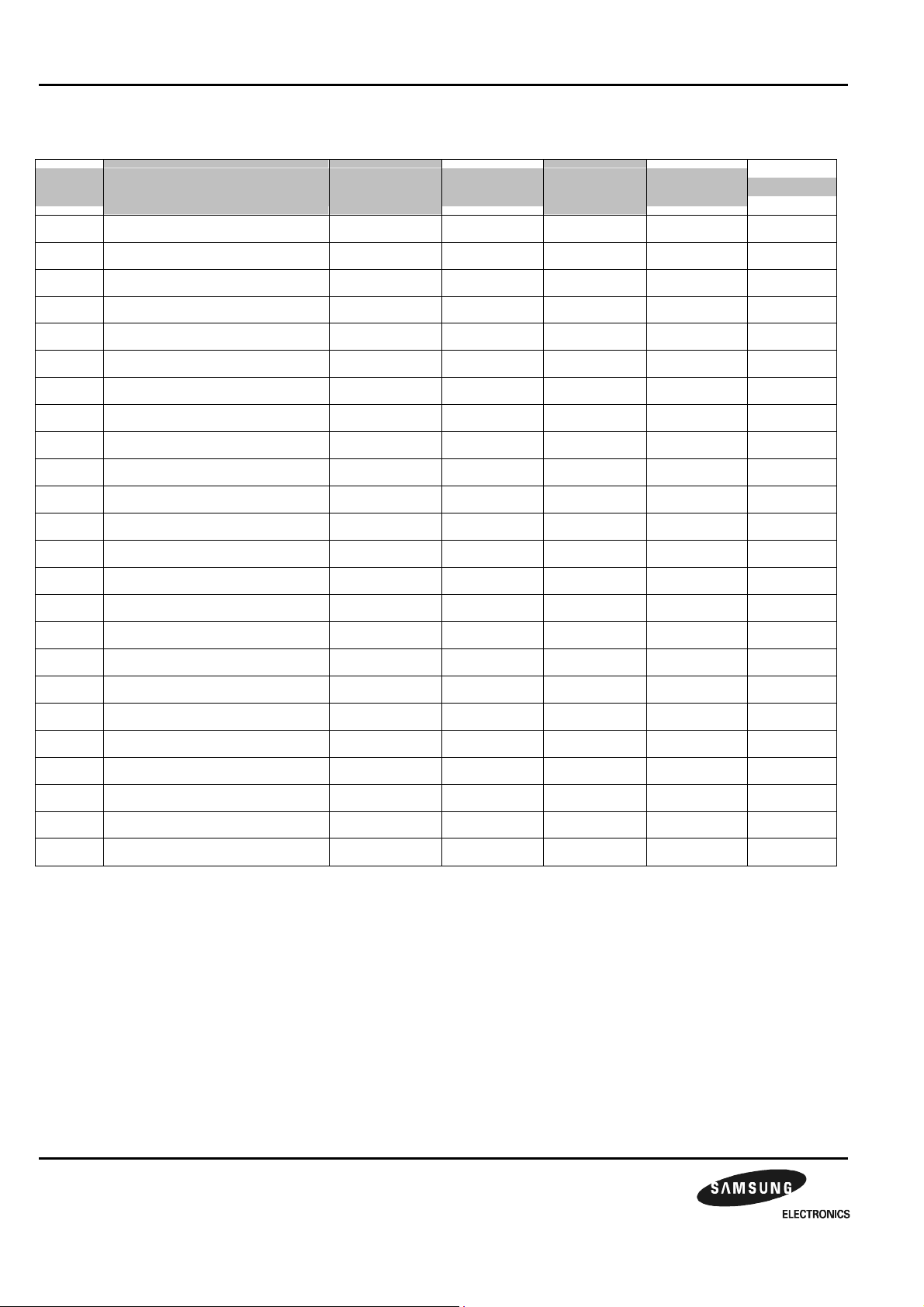

Table 1-1. 289-Pin FBGA Pin Assignments – Pin Number Order (Sheet 3 of 3)

Pin

Number

Pin Name Pin

Number

Pin Name Pin

Number

Pin Name

N1 VSSOP R1 VD3/GPC11 U1 VDDiarm

N2 VD0/GPC8 R2 VD8/GPD0 U2 VDDiarm

N3 VD4/GPC12 R3 VD11/GPD3 U3 VSSOP

N4 VD2/GPC10 R4 VD13/GPD5 U4 VSSiarm

N5 VD10/GPD2 R5 VD18/SPICLK1/GPD10 U5 VD23/nSS0/GPD15

N6 VD15/GPD7 R6 VD21 /GPD13 U6 I2SSDO/I2SSDI/GPE4

N7 VD22/nSS1/GPD14 R7 I2SSCLK/GPE1 U7 VSSiarm

N8 SDCLK/GPE5 R8 SDDAT0/GPE7 U8 IICSCL/GPE14

N9 EINT8/GPG0 R9 CLKOUT0/GPH9 U9 VSSOP

N10 EINT18/nCTS1/GPG10 R10 EINT11/nSS1/GPG3 U10 VSSiarm

N11 DP0 R11 EINT14/SPIMOSI1/GPG6 U11 VDDiarm

N12 DN1/PDN0 R12 NCON U12 EINT19/TCLK1/GPG11

N13 nRSTOUT/GPA21 R13 OM1 U13 EINT23/GPG15

N14 MPLLCAP R14 AIN0 U14 DP1/PDP0

N15 VDD_RTC R15 AIN2 U15 VSSOP

N16 VDDA_MPLL R16 AIN6 U16 Vref

N17 EINT0/GPF0 R17 VSSA_MPLL U17 AIN1

P1 LCD_LPCREVB/GPC7 T1 VSSiarm

P2 VD5/GPC13 T2 VSSiarm

P3 VD7/GPC15 T3 VDDOP

P4 VD12/GPD4 T4 VD17/SPIMOSI1/GPD9

P5 VD14/GPD6 T5 VD19/GPD11

P6 VD20/GPD12 T6 VDDiarm

P7 I2SLRCK/GPE0 T7 CDCLK/GPE2

P8 SDDAT2/GPE9 T8 VDDiarm

P9 SPIMOSI0/GPE12 T9 EINT9/GPG1

P10 CLKOUT1/GPH10 T10 EINT16/GPG8

P11 EINT12/LCD_PWREN T11 EINT21/GPG13

P12 DN0 T12 VDDOP

P13 OM2 T13 OM3

P14 VDDA_ADC T14 VSSA_ADC

P15 AIN3 T15 OM0

P16 AIN7 T16 AIN4

P17 UPLLCAP T17 AIN5

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

1-9

Page 10

2003.10.15

PRODUCT OVERVIEW S3C2440X

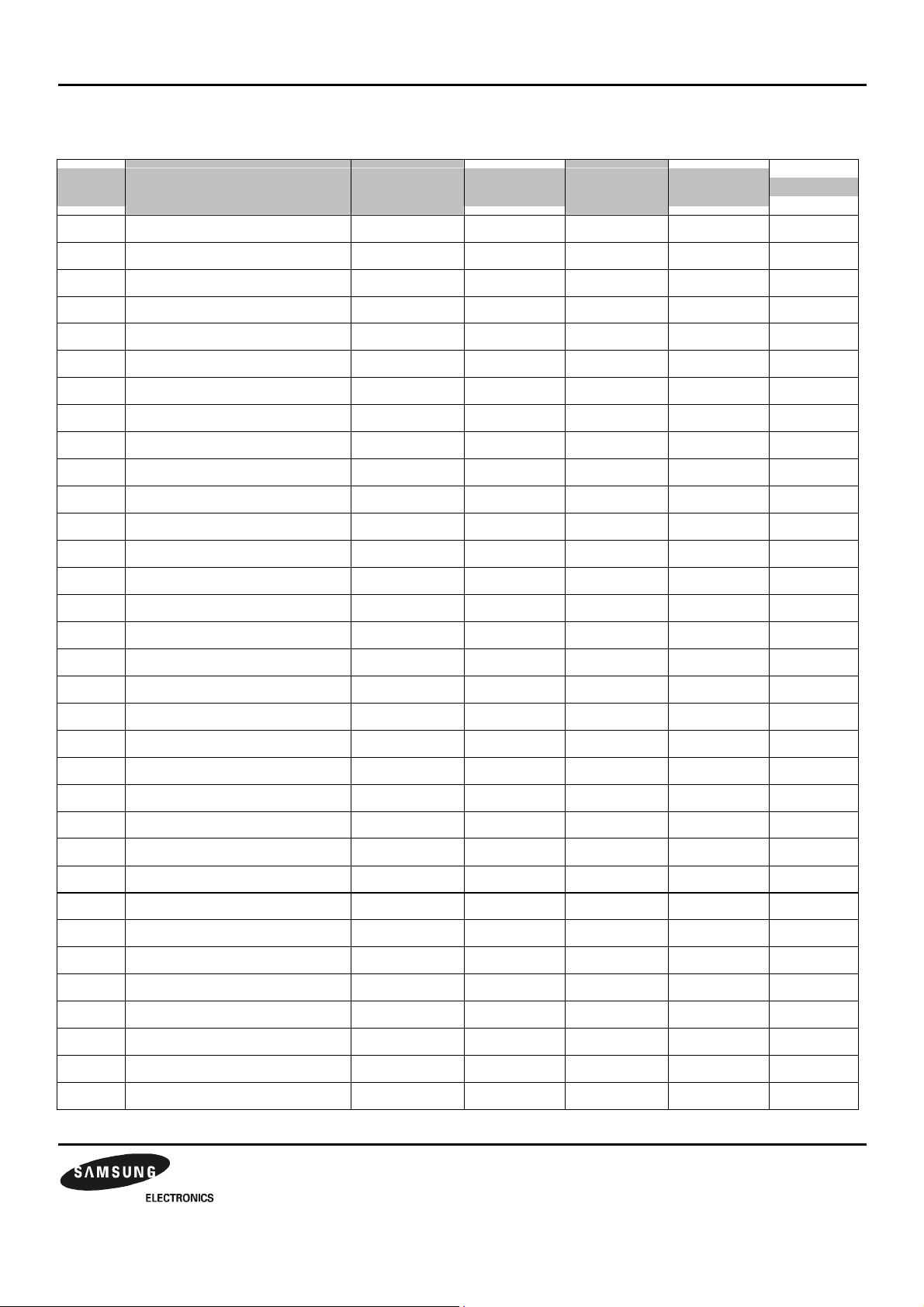

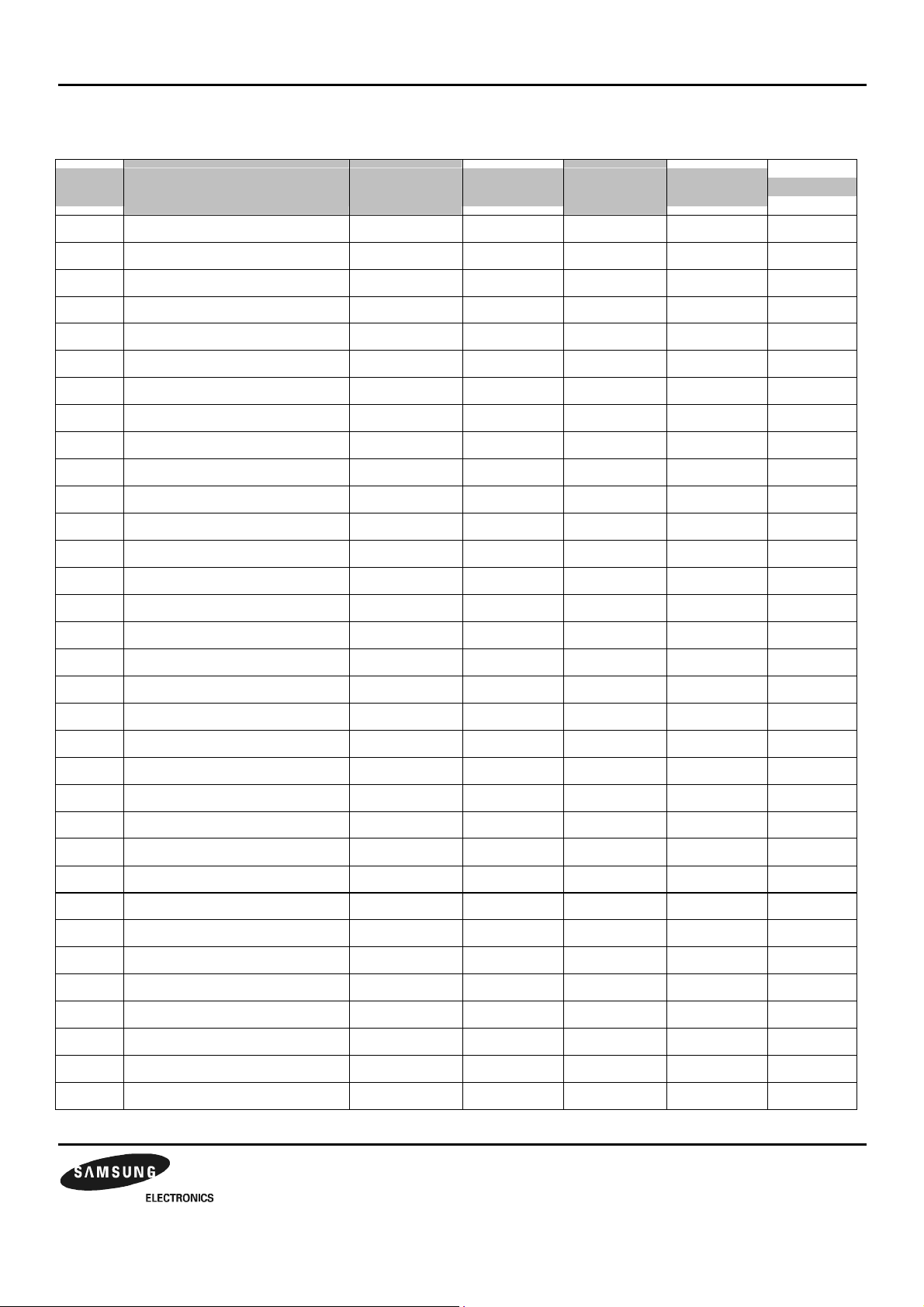

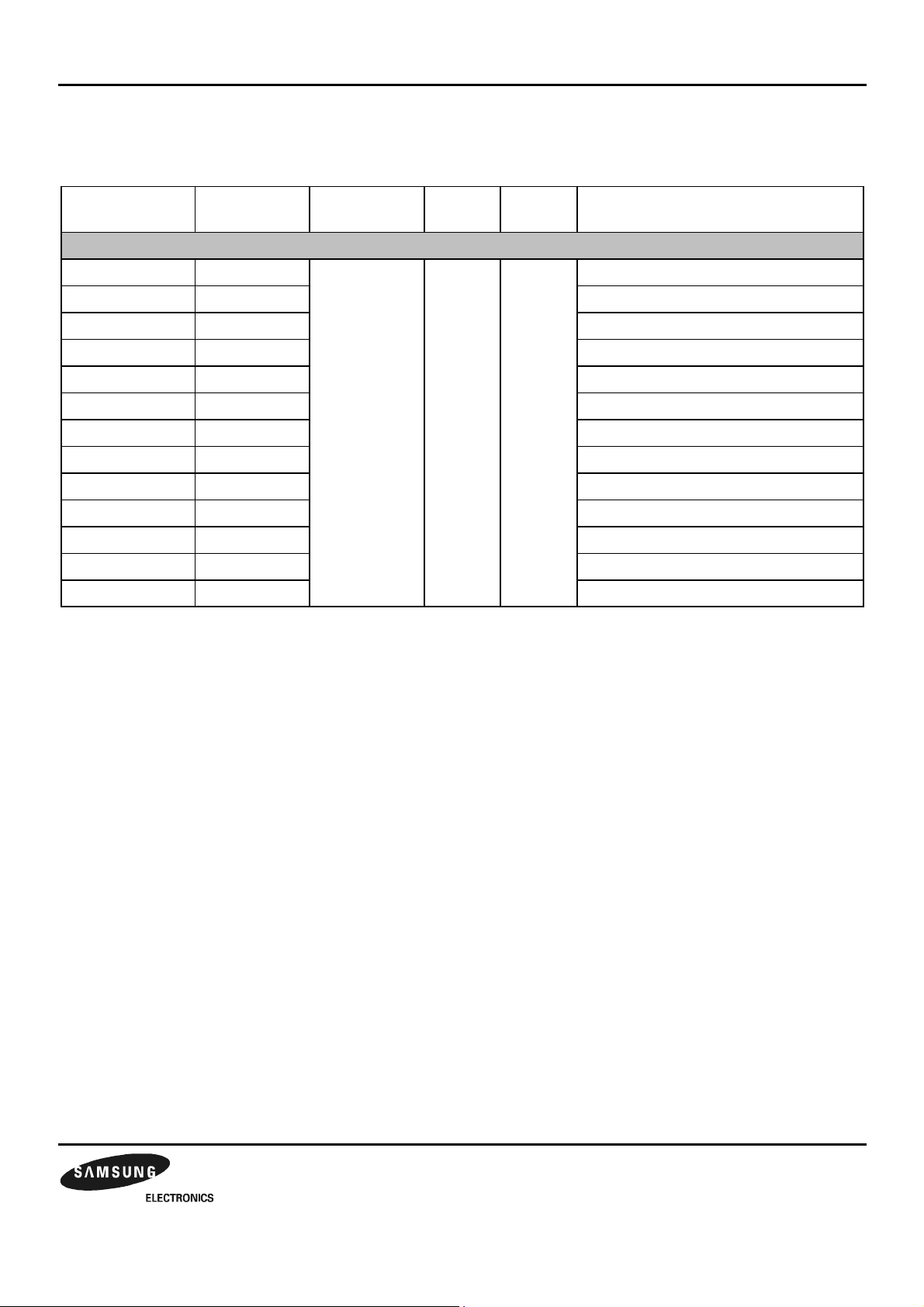

Table 1-2. S3C2440X 289-Pin FBGA Pin Assignments (Sheet 1 of 9)

Pin

Number

Pin

Name

Default

Function

I/O State

@BUS REQ

I/O State

@Sleep

I/O State

@nRESET

F7 ADDR0/GPA0 ADDR0 Hi-z/– O(L)/– O(L) t10s

E7 ADDR1 ADDR1 Hi-z O(L) O(L) t10s

B7 ADDR2 ADDR2 Hi-z O(L) O(L) t10s

F8 ADDR3 ADDR3 Hi-z O(L) O(L) t10s

C7 ADDR4 ADDR4 Hi-z O(L) O(L) t10s

D8 ADDR5 ADDR5 Hi-z O(L) O(L) t10s

E8 ADDR6 ADDR6 Hi-z O(L) O(L) t10s

D7 ADDR7 ADDR7 Hi-z O(L) O(L) t10s

G8 ADDR8 ADDR8 Hi-z O(L) O(L) t10s

B8 ADDR9 ADDR9 Hi-z O(L) O(L) t10s

A8 ADDR10 ADDR10 Hi-z O(L) O(L) t10s

C8 ADDR11 ADDR11 Hi-z O(L) O(L) t10s

B9 ADDR12 ADDR12 Hi-z O(L) O(L) t10s

H8 ADDR13 ADDR13 Hi-z O(L) O(L) t10s

E9 ADDR14 ADDR14 Hi-z O(L) O(L) t10s

I/O Type

C9 ADDR15 ADDR15 Hi-z O(L) O(L) t10s

D9 ADDR16/GPA1 ADDR16 Hi-z/– O(L)/– O(L) t10s

G9 ADDR17/GPA2 ADDR17 Hi-z/– O(L)/– O(L) t10s

F9 ADDR18/GPA3 ADDR18 Hi-z/– O(L)/– O(L) t10s

H9 ADDR19/GPA4 ADDR19 Hi-z/– O(L)/– O(L) t10s

D10 ADDR20/GPA5 ADDR20 Hi-z/– O(L)/– O(L) t10s

C10 ADDR21/GPA6 ADDR21 Hi-z/– O(L)/– O(L) t10s

H10 ADDR22/GPA7 ADDR22 Hi-z/– O(L)/– O(L) t10s

E10 ADDR23/GPA8 ADDR23 Hi-z/– O(L)/– O(L) t10s

C11 ADDR24/GPA9 ADDR24 Hi-z/– O(L)/– O(L) t10s

G10 ADDR25/GPA10 ADDR25 Hi-z/– O(L)/– O(L) t10s

D11 ADDR26/GPA11 ADDR26 Hi-z/– O(L)/– O(L) t10s

R14 AIN0 AIN0 – – AI r10

U17 AIN1 AIN1 – – AI r10

R15 AIN2 AIN2 – – AI r10

P15 AIN3 AIN3 – – AI r10

T16 YM/AIN4 AIN4 –/– –/– AI r10

T17 YP/AIN5 YP –/– –/– AI r10

R16 XM/AIN6 AIN6 –/– –/– AI r10

1-10

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

Page 11

2003.10.15

S3C2440X PRODUCT OVERVIEW

Table 1-2. S3C2440X 289-Pin FBGA Pin Assignments (Sheet 2 of 9)

Pin

Number

Pin

Name

Default

Function

I/O State

@BUS REQ

I/O State

@Sleep

I/O State

@nRESET

I/O Type

P16 XP/AIN7 XP –/– –/– AI r10

H6 CAMDATA0/GPJ0 G PJ0 –/– Hi-z/– I t8

G3 CAMDATA1/GPJ1 GPJ1 –/– Hi-z/– I t8

H5 CAMDATA2/GPJ2 G PJ2 –/– Hi-z/– I t8

H4 CAMDATA3/GPJ3 G PJ3 –/– Hi-z/– I t8

H3 CAMDATA4/GPJ4 G PJ4 –/– Hi-z/– I t8

H7 CAMDATA5/GPJ5 G PJ5 –/– Hi-z/– I t8

J8 CAMDATA6/GPJ6 GPJ6 –/– Hi-z/– I t8

H2 CAMDATA7/GPJ7 G PJ7 –/– Hi-z/– I t8

G5 CAMPCLK/GPJ8 GPJ8 –/– Hi-z/– I t8

G7 CAMVSYNC/GPJ9 GPJ9 –/– Hi-z/– I t8

G2 CAMHREF/GPJ10 GPJ10 –/– Hi-z/– I t8

J3 CAMPCLKOUT/GPJ11 GPJ11 –/– O(L)/– I t8

J4 CAMRESET/GPJ12 GPJ12 –/– O(L)/– I t8

D12 DATA0 DATA0 Hi-z Hi-z,O(L) I b12s

C12 DATA1 DATA1 Hi-z Hi-z,O(L) I b12s

E11 DATA2 DATA2 Hi-z Hi-z,O(L) I b12s

A13 DATA3 DATA3 Hi-z Hi-z,O(L) I b12s

F10 DATA4 DATA4 Hi-z Hi-z,O(L) I b12s

F11 DATA5 DATA5 Hi-z Hi-z,O(L) I b12s

C13 DATA6 DATA6 Hi-z Hi-z,O(L) I b12s

A14 DATA7 DATA7 Hi-z Hi-z,O(L) I b12s

D13 DATA8 DATA8 Hi-z Hi-z,O(L) I b12s

B15 DATA9 DATA9 Hi-z Hi-z,O(L) I b12s

A17 DATA10 DATA10 Hi-z Hi-z,O(L) I b12s

C14 DATA11 DATA11 Hi-z Hi-z,O(L) I b12s

D15 DATA12 DATA12 Hi-z Hi-z,O(L) I b12s

C15 DATA13 DATA13 Hi-z Hi-z,O(L) I b12s

D14 DATA14 DATA14 Hi-z Hi-z,O(L) I b12s

B17 DATA15 DATA15 Hi-z Hi-z,O(L) I b12s

C16 DATA16 DATA16 Hi-z Hi-z,O(L) I b12s

E15 DATA17 DATA17 Hi-z Hi-z,O(L) I b12s

E14 DATA18 DATA18 Hi-z Hi-z,O(L) I b12s

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

1-11

Page 12

2003.10.15

PRODUCT OVERVIEW S3C2440X

Table 1-2. S3C2440X 289-Pin FBGA Pin Assignments (Sheet 3 of 9)

Pin

Number

Pin

Name

Default

Function

I/O State

@BUS REQ

I/O State

@Sleep

I/O State

@nRESET

I/O Type

E13 DATA19 DATA19 Hi-z Hi-z,O(L) I b12s

E12 DATA20 DATA20 Hi-z Hi-z,O(L) I b12s

E16 DATA21 DATA21 Hi-z Hi-z,O(L) I b12s

F15 DATA22 DATA22 Hi-z Hi-z,O(L) I b12s

G13 DATA23 DATA23 Hi-z Hi-z,O(L) I b12s

E17 DATA24 DATA24 Hi-z Hi-z,O(L) I b12s

G12 DATA25 DATA25 Hi-z Hi-z,O(L) I b12s

F14 DATA26 DATA26 Hi-z Hi-z,O(L) I b12s

F12 DATA27 DATA27 Hi-z Hi-z,O(L) I b12s

G11 DATA28 DATA28 Hi-z Hi-z,O(L) I b12s

G16 DATA29 DATA29 Hi-z Hi-z,O(L) I b12s

H13 DATA30 DATA30 Hi-z Hi-z,O(L) I b12s

F13 DATA31 DATA31 Hi-z Hi-z,O(L) I b12s

P12 DN0 DN0 AI us

N11 DP0 DP0 AI us

N12 DN1/PDN0 DN1 –/– AI us

U14 DP1/PDP0 DP1 –/– AI us

N17 EINT0/GPF0 GPF0 –/– Hi-z/– I t8

M16 EINT1/GPF1 GPF1 –/– Hi-z/– I t8

L13 EINT2/GPF2 GPF2 –/– Hi-z/– I t8

M15 EINT3/GPF3 GPF3 –/– Hi-z/– I t8

M17 EINT4/GPF4 GPF4 –/– Hi-z/– I t8

L14 EINT5/GPF5 GPF5 –/– Hi-z/– I t8

L15 EINT6/GPF6 GPF6 –/– Hi-z/– I t8

L16 EINT7/GPF7 GPF7 –/– Hi-z/– I t8

N9 EINT8/GPG0 GPG0 –/– Hi-z/– I t8

T9 EINT9/GPG1 GPG1 –/– Hi-z/– I t8

J10 EINT10/nSS0/GPG2 GPG2 –/–/– Hi-z/Hi-z/– I t8

R10 EINT11/nSS1/GPG3 GPG3 –/–/– Hi-z/Hi-z/– I t8

P11 EINT12/LCD_PWREN/GPG4 GPG4 –/–/– Hi-z/O(L)/– I t8

K10 EINT13/SPIMISO1/GPG5 GPG5 –/–/– Hi-z/Hi-z/– I tt8

R11 EINT14/SPIMOSI1/GPG6 GPG6 –/–/– Hi-z/Hi-z/– I tt8

L10 EINT15/SPICLK1/GPG7 GPG7 –/–/– Hi-z/Hi-z/– I tt8

1-12

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

Page 13

2003.10.15

S3C2440X PRODUCT OVERVIEW

Table 1-2. S3C2440X 289-Pin FBGA Pin Assignments (Sheet 4 of 9)

Pin

Number

Pin

Name

Default

Function

I/O State

@BUS REQ

I/O State

@Sleep

I/O State

@nRESET

I/O Type

T10 EINT16/GPG8 GPG8 –/– Hi-z/– I t8

M11 EINT17/nRTS1/GPG9 GPG9 –/–/– Hi-z/O(H)/– I t8

N10 EINT18/nCTS1/GPG10 GPG10 –/–/– Hi-z/Hi-z/– I t8

U12 EINT19/TCLK1/GPG11 GPG11 –/–/– Hi-z/Hi-z/– I t12

M10 EINT20/GPG12 GPG12 –/– Hi-z/– I t12

T11 EINT21/GPG13 GPG13 –/– Hi-z/– I t12

L11 EINT22/GPG14 GPG14 –/– Hi-z/– I t12

U13 EINT23/GPG15 GPG15 –/– Hi-z/– I t12

H12 EXTCLK EXTCLK – – AI is

P17 UPLLCAP UPLLCAP – – AI r50

N14 MPLLCAP MPLLCAP – – AI r50

H14 nBATT_FLT nBATT_FLT – – I is

D4 nBE0 nBE0 Hi-z Hi-z,O(H) O(H) t10s

B5 nBE1 nBE1 Hi-z Hi-z,O(H) O(H) t10s

D5 nBE2 nBE2 Hi-z Hi-z,O(H) O(H) t10s

E5 nBE3 nBE3 Hi-z Hi-z,O(H) O(H) t10s

R12 NCON NCON – – I is

G6 FRnB FRnB – Hi-z,O(L) I d2s

F3 nFWE/GPA19 GPA19 O(H)/– Hi-z,O(H)/– O(H) t10s

E1 nFRE/GPA20 GPA20 O(H)/– Hi-z,O(H)/– O(H) t10s

F4 nFCE/GPA22 GPA21 O(H)/– Hi-z,O(H)/– O(H) t10s

F5 CLE/GPA17 GPA17 O(L)/– Hi-z,O(L)/– O(L) t10s

D1 ALE/GPA18 GPA18 O(L)/– Hi-z,O(L)/– O(L) t10s

N13 nRSTOUT/GPA21 GPA21 –/– O(L)/– O(L) b8

C5 nOE nOE Hi-z Hi-z,O(H) O (H) t10s

H16 nRESET nRESET – – I is

F6 nGCS0 nGCS0 Hi-z Hi-z,O(H) O(H) t10s

B2 nGCS1/GPA12 GPA12 Hi-z/– Hi-z,O(H)/– O(H) t10s

C3 nGCS2/GPA13 GPA13 Hi-z/– Hi-z,O(H)/– O(H) t10s

C4 nGCS3/GPA14 GPA14 Hi-z/– Hi-z,O(H)/– O(H) t10s

D3 nGCS4/GPA15 GPA15 Hi-z/– Hi-z,O(H)/– O(H) t10s

C2 nGCS5/GPA16 GPA16 Hi-z/– Hi-z,O(H)/– O(H) t10s

D2 nGCS6 nGCS6 Hi-z Hi-z,O(H) O(H) t10s

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

1-13

Page 14

2003.10.15

PRODUCT OVERVIEW S3C2440X

Table 1-2. S3C2440X 289-Pin FBGA Pin Assignments (Sheet 5 of 9)

Pin

Number

Pin

Name

Default

Function

I/O State

@BUS REQ

I/O State

@Sleep

I/O State

@nRESET

E3 nGCS7 nGCS7 Hi-z Hi-z,O(H) O(H) t10s

D6 nSCAS nSCAS Hi-z Hi-z,O(H) O(H) t10s

C6 nSRAS nSRAS Hi-z Hi-z,O(H) O(H) t10s

H15 nTRST nTRST I – I is

E4 nWAIT nWAIT – Hi-z,O(L) I d2s

E6 nWE nWE Hi-z Hi-z,O(H) O(H) t10s

J6 TOUT0/GPB0 GPB0 –/– O(L)/– I t8

J5 TOUT1/GPB1 GPB1 –/– O(L)/– I t8

J7 TOUT2/GPB2 GPB2 –/– O(L)/– I t8

K3 TOUT 3/GPB3 GPB3 –/– O(L)/– I t8

K4 TCLK0/GPB4 GPB4 –/– –/– I t8

K2 nXBACK/GPB5 GPB5 –/– O(H)/– I t8

L5 nXBREQ/GPB6 GPB6 –/– –/– I t8

K7 nXDACK1/GPB7 GPB7 –/– O(H)/– I t8

K5 nXDREQ1/GPB8 GPB8 –/– –/– I t8

I/O Type

L3 nXDACK0/GPB9 GPB9 –/– O(H)/– I t8

K6 nXDREQ0/GPB10 GPB10 –/– –/– I t8

T15 OM0 OM0 – – I is

R13 OM1 OM1 – – I is

P13 OM2 OM2 – – I is

T13 OM3 OM3 – – I is

J12 PWREN PWRENO(H)O(L)O(H)b8

K11 nCTS0/GPH0 GPH0 –/– –/– I t8

L17 nRTS0/GPH1 GPH1 –/– O(H)/– I t8

K13 TXD0/GPH2 GPH2 –/– O(H)/– I t8

K14 RXD0/GPH3 GPH3 –/– –/– I t8

K16 TXD1/GPH4 GPH4 –/– O(H)/– I t8

K17 RXD1/GPH5 GPH5 –/– –/– I t8

J11 TXD2/nRTS1/GPH6 GPH6 –/–/– O(H)/O(H)/– I t8

J15 RXD2/nCTS1/GPH7 GPH7 –/–/– Hi-z/Hi-z/– I t8

K15 UARTCLK/GPH8 GPH8 –/– Hi-z/– I t8

R9 CLKOUT0/GPH9 GPH9 –/– O(L)/– I t12

P10 CLKOUT1/GPH10 GPH10 –/– O(L)/– I t12

1-14

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

Page 15

2003.10.15

S3C2440X PRODUCT OVERVIEW

Table 1-2. S3C2440X 289-Pin FBGA Pin Assignments (Sheet 6 of 9)

Pin

Number

Pin

Name

Default

Function

I/O State

@BUS REQ

I/O State

@Sleep

I/O State

@nRESET

A2 SCKE SCKE Hi-z O(L) O(H) t10s

B4 SCLK0 SCLK0 Hi-z O(L) O(SCLK) t12s

B3 SCLK1 SCLK1 Hi-z O(L) O(SCLK) t12s

P7 I2SLRCK/GPE0 GPE0 –/– Hi-z/– I t8

R7 I2SSCLK/GPE1 GPE1 –/– Hi-z/– I t8

T7 CDCLK/GPE2 GPE2 –/– Hi-z/– I t8

L8 I2SSDI/nSS0/GPE3 GPE3 –/–/– Hi-z/Hi-z/– I t8

U6 I2SSDO/I2SSDI/GPE4 GPE4 –/–/– O(L)/Hi-z/– I t8

N8 SDCLK/GPE5 GPE5 –/– O(L)/– I t8

K8 SDCMD/GPE6 GPE6 –/– Hi-z/– I t8

R8 SDDAT0/GPE7 GPE7 –/– Hi-z/– I t8

M8 SDDAT1/GPE8 GPE8 –/– Hi-z/– I t8

P8 SDDAT2/GPE9 GPE9 –/– Hi-z/– I t8

J9 SDDAT3/GPE10 GPE10 –/– Hi-z/– I t8

K9 SPIMISO0/GPE11 GPE11 –/– Hi-z/– I tt8

I/O Type

P9 SPIMOSI0/GPE12 GPE12 –/– Hi-z/– I tt8

L9 SPICLK0/GPE13 GPE13 –/– Hi-z/– I tt8

U8 IICSCL/GPE14 GPE14 –/– Hi-z/– I d8

M9 IICSDA/GPE15 GPE15 –/– Hi-z/– I d8

J13 TCK TCK I – I is

H17 TDI TDI I – I is

J16 TDO TDO O O O ot

J14 TMS TMS I – I is

L1 LEND/GPC0 GPC0 –/– O(L)/– I t8

L4 VCLK/GPC1 GPC1 –/– O(L)/– I t8

M1 VLINE/GPC2 GPC2 –/– O(L)/– I t8

L7 VFRAME/GPC3 GPC3 –/– O(L)/– I t8

M4 VM/GPC4 GPC4 –/– O(L)/– I t8

M3 LCD_LPCOE/GPC5 GPC5 –/– O(L)/– I t8

M2 LCD_LPCREV/GPC6 GPC6 –/– O(L)/– I t8

P1 LCD_LPCREVB/GPC7 GPC7 –/– O(L)/– I t8

N2 VD0/GPC8 GPC8 –/– O(L)/– I t8

L6 VD1/GPC9 GPC9 –/– O(L)/– I t8

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

1-15

Page 16

2003.10.15

PRODUCT OVERVIEW S3C2440X

Table 1-2. S3C2440X 289-Pin FBGA Pin Assignments (Sheet 7 of 9)

Pin

Number

Pin

Name

Default

Function

I/O State

@BUS REQ

I/O State

@Sleep

I/O State

@nRESET

N4 VD2/GPC10 GPC10 –/– O(L)/– I t8

R1 VD3/GPC11 GPC11 –/– O(L)/– I t8

N3 VD4/GPC12 GPC12 –/– O(L)/– I t8

P2 VD5/GPC13 GPC13 –/– O(L)/– I t8

M6 VD6/GPC14 GPC14 –/– O(L)/– I t8

P3 VD7/GPC15 GPC15 –/– O(L)/– I t8

R2 VD8/GPD0 GPD0 –/– O(L)/– I t8

M5 VD9/GPD1 GPD1 –/– O(L)/– I t8

N5 VD10/GPD2 GPD2 –/– O(L)/– I t8

R3 VD11/GPD3 GPD3 –/– O(L)/– I t8

P4 VD12/GPD4 GPD4 –/– O(L)/– I t8

R4 VD13/USBTXDN1/GPD5 GPD5 –/–/– O(L)/O/– I t8

P5 VD14/USBTXDP1/GPD6 GPD6 –/–/– O(L)/O/– I t8

N6 VD15/USBOEN1/GPD7 GPD7 –/–/– O(L)/O/– I t8

M7 VD16/SPIMISO1/GPD8 GPD8 –/–/– O(L)/Hi-z/– I tt8

I/O Type

T4 VD17/SPIMOSI1/GPD9 GPD9 –/–/– O(L)/Hi-z/– I tt8

R5 VD18/SPICLK1/GPD10 GPD10 –/–/– O(L)/Hi-z/– I tt8

T5 VD19/USBRXDP1/GPD11 GPD11 –/–/– O(L)/Hi-z/– I t8

P6 VD20/USBRXDN1/GPD12 G PD12 –/–/– O(L)/Hi-z/– I t8

R6 VD21/USBRXD1/GPD13 GPD13 –/–/– O(L)/Hi-z/– I t8

N7 VD22/nSS1/GPD14 GPD14 –/–/– O(L)/Hi-z/– I t8

U5 VD23/nSS0/GPD15 GPD15 –/–/– O(L)/Hi-z/– I t8

U16 Vref Vref – – AI ia

G14 XTIpll XTIpll – – AI m26

M14 Xtirtc Xtirtc – – AI nc

G15 XTOpll XTOpll – – AO m26

L12 Xtortc Xtortc – – AO nc

N15 VDD_RTC VDD_RTC P P P drtc

P14 VDDA_ADC VDDA_ADC P P P d33t

N16 VDDA_MPLL VDDA_MPLL P P P d33t

M13 VDDA_UPLL VDDA_UPLL P P P d33t

G4 VDDalive VDDalive P P P d12i

J17 VDDalive VDDalive P P P d12i

1-16

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

Page 17

2003.10.15

S3C2440X PRODUCT OVERVIEW

Table 1-2. S3C2440X 289-Pin FBGA Pin Assignments (Sheet 8 of 9)

Pin

Number

Pin

Name

Default

Function

I/O State

@BUS REQ

I/O State

@Sleep

I/O State

@nRESET

I/O Type

A1 VDDi VDDi P P P d12c

A10 VDDi VDDi P P P d12c

A16 VDDi VDDi P P P d12c

A6 VDDi VDDi P P P d12c

B11 VDDi VDDi P P P d12c

F1 VDDi VDDi P P P d12c

F16 VDDi VDDi P P P d12c

J2 VDDiarm VDDiarm P P P d12c

L2 VDDiarm VDDiarm P P P d12c

T6 VDDiarm VDDiarm P P P d12c

T8 VDDiarm VDDiarm P P P d12c

U1 VDDiarm VDDiarm P P P d12c

U11 VDDiarm VDDiarm P P P d12c

U2 VDDiarm VDDiarm P P P d12c

A9 VDDMOP VDDMOP P P P d33o

B12 VDDMOP VDDMOP P P P d33o

B14 VDDMOP VDDMOP P P P d33o

B16 VDDMOP VDDMOP P P P d33o

B6 VDDMOP VDDMOP P P P d33o

C1 VDDMOP VDDMOP P P P d33o

F17 VDDMOP VDDMOP P P P d33o

J1 VDDOP VDDOP P P P d33o

T12 VDDOP VDDOP P P P d33o

T3 VDDOP VDDOP P P P d33o

K12 VDDOP VDDOP P P P d33o

T14 VSSA_ADC VSSA_ADC P P P st

R17 VSSA_MPLL VSSA_MPLL P P P st

M12 VSSA_UPLL VSSA_UPLL P P P st

A12 VSSi VSSi P P P si

A3 VSSi VSSi P P P si

A4 VSSi VSSi P P P si

B10 VSSi VSSi P P P si

C17 VSSi VSSi P P P si

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

1-17

Page 18

2003.10.15

PRODUCT OVERVIEW S3C2440X

Table 1-2. S3C2440X 289-Pin FBGA Pin Assignments (Sheet 9 of 9)

Pin

Number

Pin

Name

Default

Function

I/O State

@BUS REQ

I/O State

@Sleep

I/O State

@nRESET

F2 VSSi VSSi P P P si

G17 VSSi VSSi P P P si

H1 VSSiarm VSSiarm P P P si

K1 VSSiarm VSSiarm P P P si

T1 VSSiarm VSSiarm P P P si

T2 VSSiarm VSSiarm P P P si

U10 VSSiarm VSSiarm P P P si

U4 VSSiarm VSSiarm P P P si

U7 VSSiarm VSSiarm P P P si

A11 VSSMOP VSSMOP P P P so

A15 VSSMOP VSSMOP P P P so

A5 VSSMOP VSSMOP P P P so

A7 VSSMOP VSSMOP P P P so

B1 VSSMOP VSSMOP P P P so

B13 VSSMOP VSSMOP P P P so

I/O Type

D16 VSSMOP VSSMOP P P P so

D17 VSSMOP VSSMOP P P P so

E2 VSSMOP VSSMOP P P P so

G1 VSSOP VSSOP P P P so

N1 VSSOP VSSOP P P P so

U15 VSSOP VSSOP P P P so

U3 VSSOP VSSOP P P P so

U9 VSSOP VSSOP P P P so

H11 VSSOP VSSOP P P P so

1-18

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

Page 19

2003.10.15

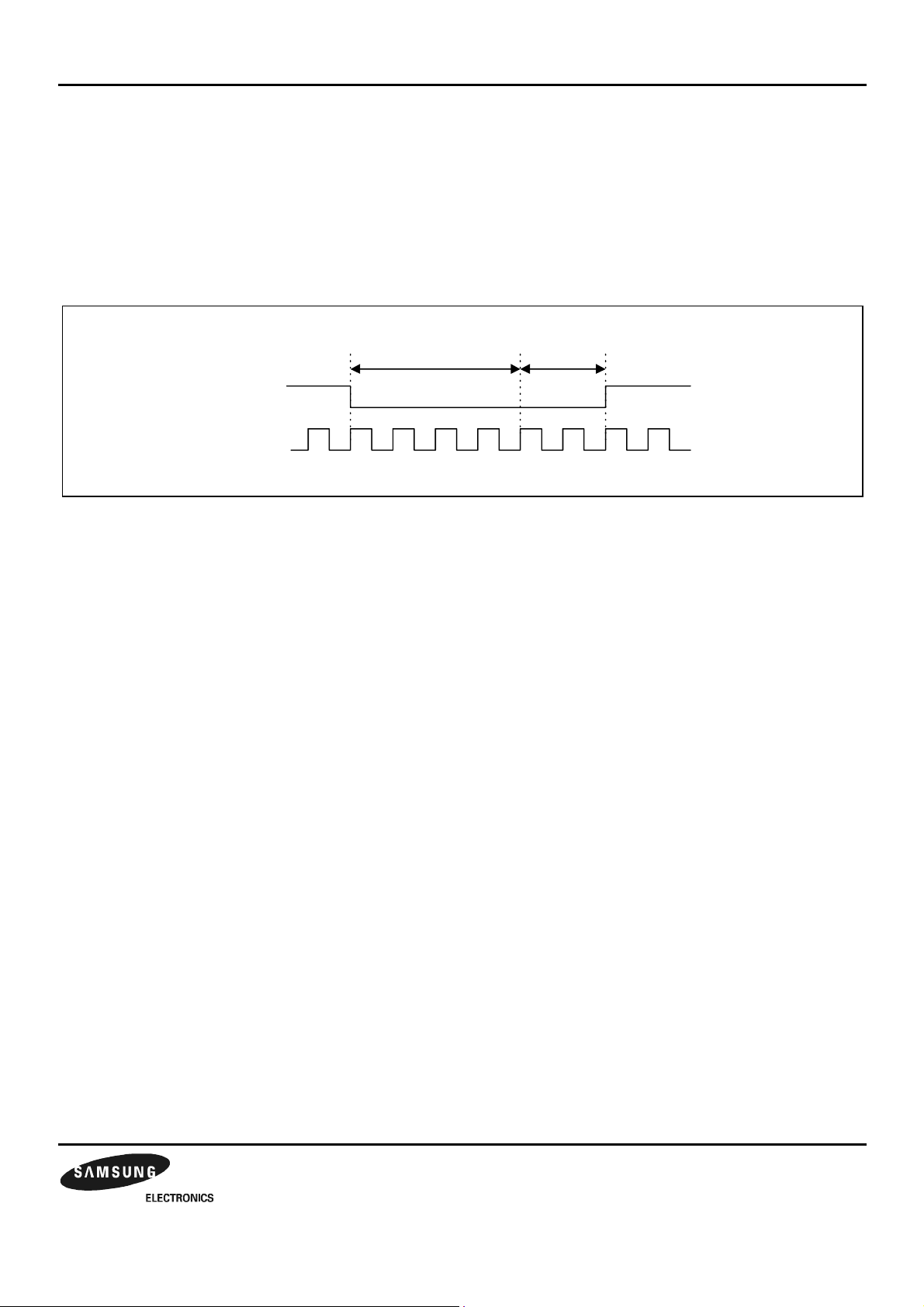

S3C2440X PRODUCT OVERVIEW

NOTE:

1. The @BUS REQ. shows the pin state at the external bus, which i s used by the other bus master.

2. ' – ‘ mark indicates the unchange d pin state at Bus Request mode.

3. Hi-z or Pre means Hi-z or early state and it is det ermined by th e setting of MISCCR register.

4. AI/AO means analog input/analog output.

5. P, I, and O mean power, input and output respectively.

6. The I/O state @nRESET shows the pin status in the @nRESET duration below.

@nRESET4FCLK

nRESET

FCLK

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

1-19

Page 20

2003.10.15

PRODUCT OVERVIEW S3C2440X

7. The t able below shows I/O types and the descriptions.

I/O Type Descriptions

d12i(vdd12ih) 1.2V Vdd for alive power

d12c(vdd12ih_core), si(vssih) 1.2V Vdd/Vss for internal logic

d33o(vdd33oph), so(vssoph) 3.3V Vdd/Vss for external logic

d33t(vdd33th_abb), st(vssbbh_abb) 3.3V Vdd/Vss for analog circuitry

drtc(vdd30th_rtc) 3.0V Vdd for RTC power

t8(phbsu100ct8sm)

Bi-directional pad, LVCMOS schmitt-trigger, 100Kohm pull-up resistor with

control, tri-state, Io=8mA

is(phis) Input pad, LVCMOS schmitt-trigger level

us(pbusb0) USB pad

t10(phtot10cd) 5V tolerant Output pad, Tri-state .

ot(phot8) Output pad, tri-state, Io=8mA

b8(phob8) Output pad, Io=8mA

t16(phot16sm) Output pad, tri-state, medium slew rate, Io=16mA

r10(phiar10_abb) Analog input pad with 10-ohm resistor

ia(phia_abb) Analog input pad

gp(phgpad_option) Pad for analog pin

m26(phsoscm26_2440) Oscillator cell with enable and feedback resistor

tt8(phtbsu100ct8sm)

t12(phbsu100ct12sm)

5V Tolerant Bi-directional pad, LVCMOS schmitt-trigger, 100Kohm pull-up

resistor with control, tri -state, medium slew rate, Io=8mA

Bi-directional pad, LVCMOS schmitt-trigger, 100Kohm pull-up resistor with

control, tri-state, Io=12mA

d2(phtod2) 5v tolerant Output pad , Open Drain , Io=2mA

d8(phbsd8sm) Bi-directional pad, LVCMOS schmitt-trigger, Open Drain, Io=8mA

t10s(phtot10cd_10_2440x)

b12s(phtbsu100ct12cd_12_2440x)

d2s(phtbsd2_2440x)

5V Tolerant output pad, LVCMOS , tri -state, output drive strenth control,

Io=4,6,8,10mA

5V Tolerant Bi-directional pad, LVCMOS schmitt-trigger, 100Kohm pull-up

resistor with control, tri -state,output drive strenth control, Io=6,8,10,12mA

5V Tolerant Bi-directional pad, LVCMOS schmitt-trigger, open-drain, output

drive strenth ignore,

r50(phoar50_abb) Analog Output pad, 50Kohm resistor, Separated bulk-bias

t12s(phtot12cd_12_2440x)

5V Tolerant output pad, LVCMOS , tri -state, output drive strenth control,

Io=6,8,12,16mA

nc(phnc) No connection pad

1-20

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

Page 21

2003.10.15

S3C2440X PRODUCT OVERVIEW

SIGNAL DESCRIPTIONS

Table 1-3. S3C2440X Signal Descriptions (Sheet 1 of 6)

Signal I/O Descriptions

Bus Controller

OM[1:0] I OM[1:0] sets S3C2440X in the TEST mode, which is used only at fabrication. Also, it

determines the bus width of nGCS0. The pull-up/down resistor determines the logic

level during RESET cycle.

00:Nand-boot 01:16-bit 10:32-bit 11:Test mode

ADDR[26:0] O ADDR[26:0] (Address Bus) outputs the memory address of the corresponding bank .

DATA[31:0] IO DATA[31:0] (Data Bus) inputs data during memory read and outputs data during

memory write. The bus width is programmable among 8/16/32-bit.

nGCS[7:0] O nGCS[7:0] (General Chip Select) are activated when the address of a memory is

within the address region of each bank. The number of access cycles and the bank

size can be programmed.

nWE O nWE (Write Enable) indicates that the current bus cycle is a write cycle.

nOE O nOE (Output Enable) indicates that the current bus cycle is a read cycle.

nXBREQ I nXBREQ (Bus Hold Request) allows another bus master to request control of the

local bus. BACK active indicates that bus control has been granted.

nXBACK O nXBACK (Bus Hold Acknowledge) indicates that the S3C2440X has surrendered

control of the local bus to another bus master.

nWAIT I nWAIT requests to prolong a current bus cycle. As long as nWAIT is L, the current

bus cycle cannot be completed.

SDRAM/SRAM

nSRAS O SDRAM Row Address Strobe

nSCAS O SDRAM Column Address Strobe

nSCS[1:0] O SDRAM Chip Select

DQM[3:0] O SDRAM Data Mask

SCLK[1:0] O SDRAM Clock

SCKE O SDRAM Clock Enable

nBE[3:0] O Upper Byte/Lower Byte Enable(In case of 16-bit SRAM)

nWBE[3:0] O Write Byte Enable

NAND Flash

CLE O Command Latch Enable

ALE O Address Latch Enable

nFCE O Nand Flash Chip Enable

nFRE O Nand Flash Read Enable

nFWE O Nand Flash W rite Enable

NCON I Nand Flash Configuration

FRnB I Nand Flash Ready/Busy

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

* If NAND flash controller isn’t used, it has to be

pull-up. (3.3V)

1-21

Page 22

2003.10.15

PRODUCT OVERVIEW S3C2440X

Table 1-3. S3C2440X Signal Descriptions (Sheet 2 of 6)

Signal I/O Descriptions

LCD Control Unit

VD[23:0] O

LCD_PWREN O

VCLK O

VFRAME O

VLINE O

VM O

VSYNC O

HSYNC O

VDEN O

LEND O

STV O

CPV O

LCD_HCLK O

TP O

STH O

LCD_LPCOE O

LCD_LPCREV O

STN/TFT/SEC TFT: LCD Data Bus

STN/TFT/SEC TFT: LCD panel power enable control signal

STN/TFT: LCD clock signal

STN: LCD Frame signal

STN: LCD line signal

STN: VM alternates the polarity of the row and column voltage

TFT: Vertical synchronous signal

TFT: Horizontal synchronous signal

TFT: Data enable signal

TFT: Line End signal

SEC TFT: SEC(Samsung Electronics Company) TFT LCD panel control signal

SEC TFT: SEC(Samsung Electronics Company) TFT LCD panel control signal

SEC TFT: SEC(Samsung Electronics Company) TFT LCD panel control signal

SEC TFT: SEC(Samsung Electronics Company) TFT LCD panel control signal

SEC TFT: SEC(Samsung Electronics Company) TFT LCD panel control signal

SEC TFT: Timing control signal for specific TFT LCD

SEC TFT: Timing control signal for specific TFT LCD

LCD_LPCREVB O

SEC TFT: Timing control signal for specific TFT LCD

CAMERA Interface

CAMRESET O Software Reset to the Camera

CAMCLKOUT O Master Clock to the Camera

CAMPCLK I Pixel clock from Camera

CAMHREF I Horizontal sync signal from Camera

CAMVSYNC I Vertical sync signal from Camera

CAMDATA[7:0] I Pixel data for YCbCr

Interrupt Control Unit

EINT[23:0] I External Interrupt request

DMA

nXDREQ[1:0] I External DMA request

nXDACK[1:0] O External DMA acknowledge

1-22

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

Page 23

2003.10.15

S3C2440X PRODUCT OVERVIEW

Table 1-3. S3C2440X Signal Descriptions (Sheet 3 of 6)

Signal I/O Descriptions

UART

RxD[2:0] I UART receives data input

TxD[2:0] O UART transmits data output

nCTS[1:0] I UART clear to send input signal

nRTS[1:0] O UART request to send output signal

UARTCLK I UART clock signal

ADC

AIN[7:0] AI ADC input[7:0]. If it isn’t used pin, it has to be Low (Ground).

Vref AI ADC Vref

IIC-Bus

IICSDA IO IIC-bus data

IICSCL IO IIC-bus clock

IIS-Bus

I2SLRCK IO IIS-bus channel select clock

I2SSDO O IIS-bus serial data output

I2SSDI I IIS-bus serial data input

I2SSCLK IO IIS-bus serial clock

CDCLK O CODEC system clock

Touch Screen

nXPON O Plus X-axis on-off control signal

XMON O Minus X-axis on-off control signal

nYPON O Plus Y-axis on-off control signal

YMON O Minus Y-axis on-off control signal

USB Host

DN[1:0] IO DATA(–) from USB host

DP[1:0] IO DATA(+) from USB host

USB Device

PDN0 IO DATA(–) for USB peripheral

PDP0 IO DATA(+) for USB peripheral

SPI

SPIMISO[1:0] IO SPIMISO is the master data input line, when SPI is configured as a master.

When SPI is configured as a slave, these pins reverse its role.

SPIMOSI[1:0] IO SPIMOSI is the master data output line, when SPI is configured as a master.

When SPI is configured as a slave, these pins reverse its role.

SPICLK[1:0] IO SPI clock

nSS[1:0] I SPI chip select(only for slave mode)

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

1-23

Page 24

2003.10.15

PRODUCT OVERVIEW S3C2440X

Table 1-3. S3C2440X Signal Descriptions (Sheet 4 of 6)

Signal I/O Description

SD

SDDAT[3:0] IO SD receive/transmit data

SDCMD IO SD receive response/ transmit command

SDCLK O SD clock

General Port

GPn[116:0] IO General input/output ports (some ports are output only)

TIMMER/PWM

TOUT[3:0] O Timer output[3:0]

TCLK[1:0] I External timer clock input

JTAG TEST LOGIC

nTRST I nTRST(TAP Controller Reset) resets the TAP controller at start.

If debugger is used, A 10K pull-up resistor has to be connected.

If debugger(black ICE) is not used, nTRST pin must be issued by a low active

pulse(Typically connected to nRESET).

TMS I TMS (TAP Controller Mode Select) controls the sequence of the TAP controller's

states. A 10K pull-up resistor has to be connected to TMS pin.

TCK I TCK (TAP Controller Clock) provides the clock input for the JTAG logic.

A 10K pull-up resistor must be connected to TCK pin.

TDI I TDI (TAP Controller Data Input) is the serial input for test instructions and data.

A 10K pull-up resistor must be connected to TDI pin.

TDO O TDO (TAP Controller Data Output) is the serial output for test instructions and data.

1-24

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

Page 25

2003.10.15

S3C2440X PRODUCT OVERVIEW

Table 1-3. S3C2440X Signal Descriptions (Sheet 5 of 6)

Signal I/O Description

Reset, Clock & Power

XTOpll AO Crystal Output for internal osc circuit.

When OM[3:2] = 00b, XTIpll is used for MPLL CLK source and UPLL CLK source.

When OM[3:2] = 01b, XTIpll is used for MPLL CLK source only.

When OM[3:2] = 10b, XTIpll is used for UPLL CLK source only.

If it isn't used, it has to be a floating pin.

MPLLCAP AI Loop filter capacitor for main clock.

UPLLCAP AI Loop filter capacitor for USB clock.

XTIrtc AI 32 kHz crystal input for RTC. If it isn’t used, it has to be High (3.3V).

XTOrtc AO 32 kHz crystal output for RTC. If it isn’t used, it has to be Float.

CLKOUT[1:0] O Clock output signal. The CLKSEL of MISCCR register configures the clock output

mode among the MPLL CLK, UPLL CLK, FCLK, HCLK, PCLK.

nRESET ST nRESET suspends any operation in progress and places S3C2440X into a known

reset state. For a reset, nRESET must be held to L level for at least 4 FCLK after the

processor power has been stabilized.

nRSTOUT O For external device reset control(nRSTOUT = nRESET & nWDTRST & SW_RESET)

PWREN O 1.2V core power on-off control signal

nBATT_FLT I Probe for battery state(Does not wake up at Sleep mode in case of low battery state).

If it isn’t used, it has to be High (3.3V).

OM[3:2] I OM[3:2] determines how the clock is made.

OM[3:2] = 00b, Crystal is used for MPLL CLK source and UPLL CLK source.

OM[3:2] = 01b, Crystal is used for MPLL CLK source

and EXTCLK is used for UPLL CLK source.

OM[3:2] = 10b, EXTCLK is used for MPLL CLK source

and Crystal is used for UPLL CLK source.

OM[3:2] = 11b, EXTCLK is used for MPLL CLK source and UPLL CLK source.

EXTCLK I External clock source.

When OM[3:2] = 11b, EXTCLK is used for MPLL CLK source and UPLL CLK source.

When OM[3:2] = 10b, EXTCLK is used for MPLL CLK source only.

When OM[3:2] = 01b, EXTCLK is used for UPLL CLK source only.

If it isn't used, it has to be High (3.3V).

XTIpll AI Crystal Input for internal osc circuit.

When OM[3:2] = 00b, XTIpll is used for MPLL CLK source and UPLL CLK source.

When OM[3:2] = 01b, XTIpll is used for MPLL CLK source only.

When OM[3:2] = 10b, XTIpll is used for UPLL CLK source only.

If it isn't used, XTIpll has to be High (3.3V).

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

1-25

Page 26

2003.10.15

PRODUCT OVERVIEW S3C2440X

Table 1-3. S3C2440X Signal Descriptions (Sheet 6 of 6)

Signal I/O Description

Power

VDDalive P S3C2440X reset block and port status register VDD(1.2V).

It should be always supplied whether in normal mode or in Sleep mode.

VDDi/VDDiarm P S3C2440X core logic VDD(1.2V) for CPU.

VSSi/VSSiarm P S3C2440X core logic VSS

VDDi_MPLL P S3C2440X MPLL analog and digital VDD (1.2 V).

VSSi_MPLL P S3C2440X MPLL analog and digital VSS.

VDDOP P S3C2440X I/O port VDD(3.3V)

VDDMOP P S3C2440X Memory I/O VDD

3.3V : SCLK up to 100MHz

2.5V : SCLK up to 80MHz

VSSOP P S3C2440X I/O port VSS

RTCVDD P RTC VDD (3.0V)

(This pin must be connected to power properly if RTC isn't used)

VDDi_UPLL P S3C2440X UPLL analog and digital VDD (1.2V)

VSSi_UPLL P S3C2440X UPLL analog and digital VSS

VDDA_ADC P S3C2440X ADC VDD(3.3V)

VSSA_ADC P S3C2440X ADC VSS

NOTE:

1. I/O means input/output.

2. AI/AO means analog input/analog output.

3. ST means schmitt-trigger.

4. P means power.

1-26

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

Page 27

2003.10.15

S3C2440X PRODUCT OVERVIEW

S3C2440X SPECIAL REGISTERS

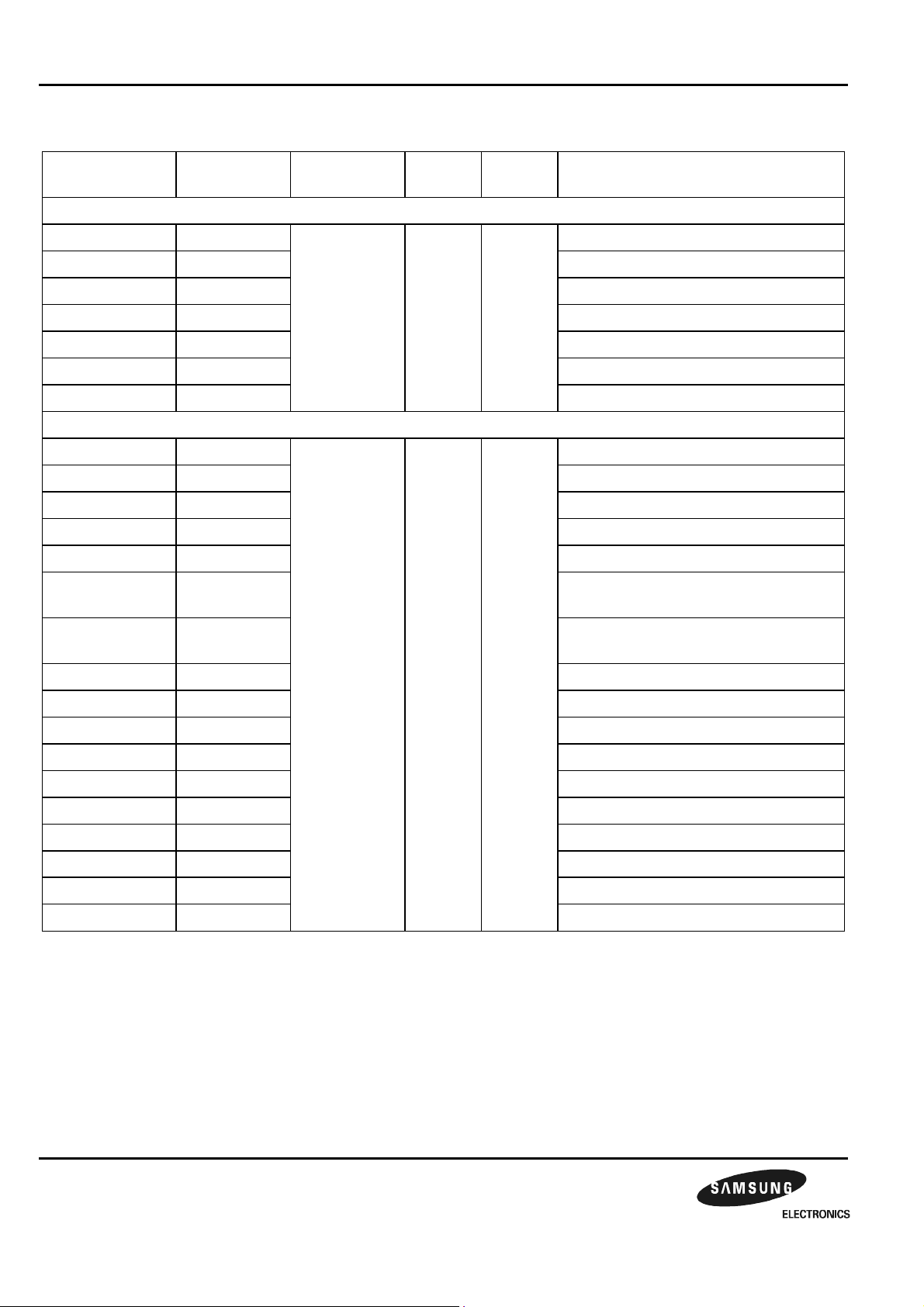

Table 1-4. S3C2440X Special Registers (Sheet 1 of 14)

Register

Name

Address

(B. Endian)

Address

(L. Endian)

Acc.

Unit

Read/

Write

Function

Memory Controller

BWSCON 0x48000000

←

W R/W Bus Width & Wait Status Control

BANKCON0 0x48000004 Boot ROM Control

BANKCON1 0x48000008 BANK1 Control

BANKCON2 0x4800000C BANK2 Control

BANKCON3 0x48000010 BANK3 Control

BANKCON4 0x48000014 BANK4 Control

BANKCON5 0x48000018 BANK5 Control

BANKCON6 0x4800001C BANK6 Control

BANKCON7 0x48000020 BANK7 Control

REFRESH 0x48000024 DRAM/SDRAM Refresh Control

BANKSIZE 0x48000028 Flexible Bank Size

MRSRB6 0x4800002C Mode register set for SDRAM BANK6

MRSRB7 0x48000030 Mode register set for SDRAM BANK7

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

1-27

Page 28

2003.10.15

PRODUCT OVERVIEW S3C2440X

Table 1-4. S3C2440X Special Registers (Sheet 2 of 14)

Register Name Address

(B. Endian)

Address

(L. Endian)

Acc.

Unit

Read/

Write

Function

USB Host Controller

HcRevision 0x49000000

←

W Control and Status Group

HcControl 0x49000004

HcCommonStatus 0x49000008

HcInterruptStatus 0x4900000C

HcInterruptEnable 0x49000010

HcInterruptDisable 0x49000014

HcHCCA 0x49000018 Memory Pointer Group

HcPeriodCuttentED 0x4900001C

HcControlHeadED 0x49000020

HcControlCurrentED 0x49000024

HcBulkHeadED 0x49000028

HcBulkCurrentED 0x4900002C

HcDoneHead 0x49000030

HcRmInterval 0x49000034 Frame Counter Group

HcFmRemaining 0x49000038

HcFmNumber 0x4900003C

HcPeriodicStart 0x49000040

HcLSThreshold 0x49000044

HcRhDescriptorA 0x49000048 Root Hub Group

HcRhDescriptorB 0x4900004C

HcRhStatus 0x49000050

HcRhPortStatus1 0x49000054

HcRhPortStatus2 0x49000058

Interrupt Controller

SRCPND 0X4A000000

←

W R/W Interrupt Request Status

INTMOD 0X4A000004 W Interrupt Mode Control

INTMSK 0X4A000008 R/W Interrupt Mask Control

PRIORITY 0X4A00000C W IRQ Priority Control

INTPND 0X4A000010 R/W Interrupt Request Status

INTOFFSET 0X4A000014 R Interrupt request source offset

SUBSRCPND 0X4A000018 R/W Sub source pending

INTSUBMSK 0X4A00001C R/W Interrupt sub mask

1-28

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

Page 29

2003.10.15

S3C2440X PRODUCT OVERVIEW

Table 1-4. S3C2440X Special Registers (Sheet 3 of 14)

Register

Name

Address

(B. Endian)

Address

(L. Endian)

Acc.

Unit

Read/

Write

Function

DMA

DISRC0 0x4B000000

←

W R/W DMA 0 Initial Source

DISRCC0 0x4B000004 DMA 0 Initial Source Control

DIDST0 0x4B000008 DMA 0 Initial Destination

DIDSTC0 0x4B00000C DMA 0 Initial Destination Control

DCON0 0x4B000010 DMA 0 Control

DSTAT0 0x4B000014 R DMA 0 Count

DCSRC0 0x4B000018 DMA 0 Current Source

DCDST0 0x4B00001C DMA 0 Current Destination

DMASKTRIG0 0x4B000020 R/W DMA 0 Mask Trigger

DISRC1 0x4B000040 DMA 1 Initial Source

DISRCC1 0x4B000044 DMA 1 Initial Source Control

DIDST1 0x4B000048 DMA 1 Initial Destination

DIDSTC1 0x4B00004C DMA 1 Initial Destination Control

DCON1 0x4B000050 DMA 1 Control

DSTAT1 0x4B000054 R DMA 1 Count

DCSRC1 0x4B000058 DMA 1 Current Source

DCDST1 0x4B00005C DMA 1 Current Destination

DMASKTRIG1 0x4B000060 R/W DMA 1 Mask Trigger

DISRC2 0x4B000080 DMA 2 Initial Source

DISRCC2 0x4B000084 DMA 2 Initial Source Control

DIDST2 0x4B000088 DMA 2 Initial Destination

DIDSTC2 0x4B00008C DMA 2 Initial Destination Control

DCON2 0x4B000090 DMA 2 Control

DSTAT2 0x4B000094 R DMA 2 Count

DCSRC2 0x4B000098 DMA 2 Current Source

DCDST2 0x4B00009C DMA 2 Current Destination

DMASKTRIG2 0x4B0000A0 R/W DMA 2 Mask Trigger

DISRC3 0x4B0000C0

←

W R/W DMA 3 Initial Source

DISRCC3 0x4B0000C4 DMA 3 Initial Source Control

DIDST3 0x4B0000C8 DMA 3 Initial Destination

DIDSTC3 0x4B0000CC DMA 3 Initial Destination Control

DCON3 0x4B0000D0 DMA 3 Control

DSTAT3 0x4B0000D4 R DMA 3 Count

DCSRC3 0x4B0000D8 DMA 3 Current Source

DCDST3 0x4B0000DC DMA 3 Current Destination

DMASKTRIG3 0x4B0000E0 R/W DMA 3 Mask Trigger

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

1-29

Page 30

2003.10.15

PRODUCT OVERVIEW S3C2440X

Table 1-4. S3C2440X Special Registers (Sheet 4 of 14)

Register

Name

Address

(B. Endian)

Address

(L. Endian)

Acc.

Unit

Read/

Write

Function

Clock & Power Management

LOCKTIME 0x4C000000

←

W R/W PLL Lock Time Counter

MPLLCON 0x4C000004 MPLL Control

UPLLCON 0x4C000008 UPLL Control

CLKCON 0x4C00000C Clock Generator Control

CLKSLOW 0x4C000010 Slow Clock Control

CLKDIVN 0x4C000014 Clock divider Control

CAMDIVN 0x4C000018 Camera Clock divider Control

LCD Controller

LCDCON1 0X4D000000

←

W R/W LCD Control 1

LCDCON2 0X4D000004 LCD Control 2

LCDCON3 0X4D000008 LCD Control 3

LCDCON4 0X4D00000C LCD Control 4

LCDCON5 0X4D000010 LCD Control 5

LCDSADDR1 0X4D000014 STN/TFT: Frame Buffer Start

Address1

LCDSADDR2 0X4D000018 STN/TFT: Frame Buffer Start

Address2

LCDSADDR3 0X4D00001C STN/TFT: Virtual Screen Address Set

REDLUT 0X4D000020 STN: Red Lookup Table

GREENLUT 0X4D000024 STN: Green Lookup Table

BLUELUT 0X4D000028 STN: Blue Lookup Table

DITHMODE 0X4D00004C STN: Dithering Mode

TPAL 0X4D000050 TFT: Temporary Palette

LCDINTPND 0X4D000054 LCD Interrupt Pending

LCDSRCPND 0X4D000058 LCD Interrupt Source

LCDINTMSK 0X4D00005C LCD Interrupt Mask

TCONSEL 0X4D000060 TCON(LPC3600/LCC3600) Control

1-30

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

Page 31

2003.10.15

S3C2440X PRODUCT OVERVIEW

Table 1-4. S3C2440X Special Registers (Sheet 5 of 14)

Register

Name

Address

(B. Endian)

Address

(L. Endian)

Acc.

Unit

Read/

Write

Function

NAND Flash

NFCONF 0x4E000000

←

W R/W NAND Flash Configuration

NFCONT 0x4E000004 NAND Flash Control

NFCMD 0x4E000008 NAND Flash Command

NFADDR 0x4E00000C NAND Flash Address

NFDATA 0x4E000010 NAND Flash Data

NFMECC0 0x4E000014 NAND Flash Main area ECC0/1

NFMECC1 0x4E000018 NAND Flash Main area ECC2/3

NFSECC 0x4E00001C NAND Flash Spare area ECC

NFSTAT 0x4E000020 NAND Flash Operation Status

NFESTAT0 0x4E000024 NAND Flash ECC Status for I/O[7:0]

NFESTAT1 0x4E000028 NAND Flash ECC Status for I/O[15:8]

NFMECC0 0x4E00002C R NAND Flash Main area ECC0 status

NFMECC1 0x4E000030 NAND Flash Main Area ECC1 status

NFSECC 0x4E000034 NAND Flash Spare Area ECC status

NFSBLK 0x4E000038 R/W NAND Flash start block address

NFEBLK 0x4E00003C NAND Flash end block address

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

1-31

Page 32

2003.10.15

PRODUCT OVERVIEW S3C2440X

Table 1-4. S3C2440X Special Registers (Sheet 6 of 14)

Register

Name

Address

(B. Endian)

Address

(L. Endian)

Acc.

Unit

Read/

Write

Function

Camera Interface

ASIZE 0x4F000000

←

W W A-port Im age Size

STAY1 0x4F000004 R/W Y start address for 1stping-pong memory of A-

port Image

STAY2 0x4F000008 Y start address for 2ndping-pong memory of A-

port Image

STAY3 0x4F00000C Y start address for 3rdping-pong memory of A-

port Image

STAY4 0x4F000010 Y start address for 4thping-pong memory of A-

port Image

AYBURST 0x4F000014 W A-port Image Y data burst length

ACBBURST 0x4F000018 A-port Image Cb data burst length

ACRBURST 0x4F00001C A-port Image Cr data burst length

BSIZE 0x4F000020 B-port Image Size

STBY1 0x4F000024 Y start address for 1stping-pong memory of B-

port Image

STBY2 0x4F000028 Y start address for 2ndping-pong memory of B-

port Image

STBY3 0x4F00002C Y start address for 3rdping-pong memory of B-

port Image

STBY4 0x4F000030 Y start address for 4thping-pong memory of B-

port Image

BYBURST 0x4F000034 B-port Image Y data burst length

BCBBURST 0x4F000038 B-port Image Cb data burst length

BCRBURST 0x4F00003C B-port Image Cr data burst length

ADISTWIDTH 0x4F000040 A Last HREF Distance Width

BDISTWIDTH 0x4F000044 B Last HREF Distance Width

YRATIO 0x4F00004C Y Scale Ratio

CRATIO 0x4F000050 C Scale Ratio

YORIGINAL 0x4F000054 Y Original Size

CORIGINAL 0x4F00005C C Original Size

STACB1 0x4F000074 A Cb 1 Start Address

STACB2 0x4F000078 A Cb 2 Start Address

STACB3 0x4F00007C A Cb 3 Start Address

STACB4 0x4F000080 A Cb 4 Start Address

1-32

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

Page 33

2003.10.15

S3C2440X PRODUCT OVERVIEW

Table 1-4. S3C2440X Special Registers (Sheet 7 of 14)

Register

Name

Address

(B. Endian)

Address

(L. Endian)

Acc.

Unit

Read/

Write

Function

Camera Interface(Continued)

STACR1 0x4F000084

←

W W A Cr 1 Start Address

STACR2 0x4F000088 A Cr 2 Start Address

STACR3 0x4F00008C A Cr 3 Start Address

STACR4 0x4F000090 A Cr 4 Start Address

STBCB1 0x4F00009C B Cb 1 Start Address

STBCB2 0x4F0000A0 B Cb 2 Start Address

STBCB3 0x4F0000A4 B Cb 3 Start Address

STBCB4 0x4F0000A8 B Cb 4 Start Address

STBCR1 0x4F0000AC B Cr 1 Start Address

STBCR2 0x4F0000B0 B Cr 2 Start Address

STBCR3 0x4F0000B4 B Cr 3 Start Address

STBCR4 0x4F0000B8 B Cr 4 Start Address

CTRL 0x4F0000BC Control Register

RDSTAT 0x4F000000 R Status Read Register

RDSTAY 0x4F000014 A Y Start Address Read

RDSTACB 0x4F000018 A Cb Start Address Read

RDSTACR 0x4F00001C A Cr Start Address Read

RDSTACB1 0x4F000020 A Cb1 Start Address Read

RDSTACR1 0x4F000024 A Cr1 Start Address Read

RDSTBY1 0x4F000028 B Y1 Start Address Read

RDSTBY2 0x4F00002C B Y2 Start Address Read

RDSTBY3 0x4F000030 B Y3 Start Address Read

RDSTBY4 0x4F000034 B Y4 Start Address Read

RDSTBY 0x4F000038 B Y Start Address Read

RDSTBCB 0x4F00003C B Cb Start Address Read

RDSTBCR 0x4F000040 B Cr Start Address Read

RDSTBCB1 0x4F000044 B Cb1 Start Address Read

RDSTBCR1 0x4F000048 B Cr1 Start Address Read

RDADISTWIDTH 0x4F00004C A Last HREF Distance Width

RDBDISTWIDTH 0x4F000050 B Last HREF Distance Width

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

1-33

Page 34

2003.10.15

PRODUCT OVERVIEW S3C2440X

Table 1-4. S3C2440X Special Registers (Sheet 8 of 14)

Register

Name

Address

(B. Endian)

Address

(L. Endian)

Acc.

Unit

Read/

Write

Function

UART

ULCON0 0x50000000

←

W R/W UART0LineControl

UCON0 0x50000004 UART 0 Control

UFCON0 0x50000008 UART 0 FIFO Control

UMCON0 0x5000000C UART 0 Modem Control

UTRSTAT0 0x50000010 R UART 0 Tx/Rx Status

UERSTAT0 0x50000014 UART 0 Rx Error Status

UFSTAT0 0x50000018 UART 0 FIFO Status

UMSTAT0 0x5000001C UART 0 Modem Status

UTXH0 0x50000023 0x50000020 B W UART 0 Transmission Hold

URXH0 0x50000027 0x50000024 R UART 0 Receive Buffer

UBRDIV0 0x50000028

←

W R/W UART 0 Baud Rate Divisor

ULCON1 0x50004000 UART 1 Line Control

UCON1 0x50004004 UART 1 Control

UFCON1 0x50004008 UART 1 FIFO Control

UMCON1 0x5000400C UART 1 Modem Control

UTRSTAT1 0x50004010 R UART 1 Tx/Rx Status

UERSTAT1 0x50004014 UART 1 Rx Error Status

UFSTAT1 0x50004018 UART 1 FIFO Status

UMSTAT1 0x5000401C UART 1 Modem Status

UTXH1 0x50004023 0x50004020 B W UART 1 Transmission Hold

URXH1 0x50004027 0x50004024 R UART 1 Receive Buffer

UBRDIV1 0x50004028

←

W R/W UART 1 Baud Rate Divisor

ULCON2 0x50008000 UART 2 Line Control

UCON2 0x50008004 UART 2 Control

UFCON2 0x50008008 UART 2 FIFO Control

UTRSTAT2 0x50008010 R UART 2 Tx/Rx Status

UERSTAT2 0x50008014 UART 2 Rx Error Status

UFSTAT2 0x50008018 UART 2 FIFO Status

UTXH2 0x50008023 0x50008020 B W UART 2 Transmission Hold

URXH2 0x50008027 0x50008024 R UART 2 Receive Buffer

UBRDIV2 0x50008028

←

W R/W UART 2 Baud Rate Divisor

1-34

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

Page 35

2003.10.15

S3C2440X PRODUCT OVERVIEW

Table 1-4. S3C2440X Special Registers (Sheet 9 of 14)

Register

Name

Address

(B. Endian)

Address

(L. Endian)

Acc.

Unit

Read/

Write

Function

PWM Timer

TCFG0 0x51000000

←

W R/W Timer Configuration

TCFG1 0x51000004 Timer Configuration

TCON 0x51000008 Timer Control

TCNTB0 0x5100000C Timer Count Buffer 0

TCMPB0 0x51000010 Timer Compare Buffer 0

TCNTO0 0x51000014 R Timer Count Observation 0

TCNTB1 0x51000018 R/W Timer Count Buffer 1

TCMPB1 0x5100001C Timer Compare Buffer 1

TCNTO1 0x51000020 R Timer Count Observation 1

TCNTB2 0x51000024 R/W Timer Count Buffer 2

TCMPB2 0x51000028 Timer Compare Buffer 2

TCNTO2 0x5100002C R Timer Count Observation 2

TCNTB3 0x51000030 R/W Timer Count Buffer 3

TCMPB3 0x51000034 Timer Compare Buffer 3

TCNTO3 0x51000038 R Timer Count Observation 3

TCNTB4 0x5100003C R/W Timer Count Buffer 4

TCNTO4 0x51000040 R Timer Count Observation 4

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

1-35

Page 36

2003.10.15

PRODUCT OVERVIEW S3C2440X

Table 1-4. S3C2440X Special Registers (Sheet 10 of 14))

Register Name Address

(B. Endian)

Address

(L. Endian)

Acc.

Unit

Read/W

rite

Function

USB Device

FUNC_ADDR_REG 0x52000143 0x52000140 B R/W Function Address

PWR_REG 0x52000147 0x52000144 Power Management

EP_INT_REG 0x5200014B 0x52000148 EP Interrupt Pending and Clear

USB_INT_REG 0x5200015B 0x52000158 USB Interrupt Pending and Clear

EP_INT_EN_REG 0x5200015F 0x5200015C Interrupt Enable

USB_INT_EN_REG 0x5200016F 0x5200016C Interrupt Enable

FRAME_NUM1_REG 0x52000173 0x52000170 R Frame Number Lower Byte

FRAME_NUM2_REG 0x52000177 0x52000174 Frame Number Higher Byte

INDEX_REG 0x5200017B 0x52000178 R/W Register Index

EP0_CSR 0x52000187 0x52000184 Endpoint 0 Status

IN_CSR1_REG 0x52000187 0x52000184 In Endpoint Control Status

IN_CSR2_REG 0x5200018B 0x52000188 In Endpoint Control Status

MAXP_REG 0x52000183 0x52000180 Endpoint Max Packet

OUT_CSR1_REG 0x52000193 0x52000190 Out Endpoint Control Status

OUT_CSR2_REG 0x52000197 0x52000194 Out Endpoint Control Status

OUT_FIFO_CNT1_REG 0x5200019B 0x52000198 R Endpoint Out Write Count

OUT_FIFO_CNT2_REG 0x5200019F 0x5200019C Endpoint Out Write Count

EP0_FIFO 0x520001C3 0x520001C0 R/W Endpoint 0 FIFO

EP1_FIFO 0x520001C7 0x520001C4 Endpoint 1 FIFO

EP2_FIFO 0x520001CB 0x520001C8 Endpoint 2 FIFO

EP3_FIFO 0x520001CF 0x520001CC Endpoint 3 FIFO

EP4_FIFO 0x520001D3 0x520001D0 Endpoint 4 FIFO

EP1_DMA_CON 0x52000203 0x52000200 EP1 DMA Interface Control

EP1_DMA_UNIT 0x52000207 0x52000204 EP1 DMA Tx Unit Counter

EP1_DMA_FIFO 0x5200020B 0x52000208 EP1 DMA Tx FIFO Counter

EP1_DMA_TTC_L 0x5200020F 0x5200020C EP1 DMA Total Tx Counter

EP1_DMA_TTC_M 0x52000213 0x52000210 EP1 DMA Total Tx Counter

EP1_DMA_TTC_H 0x52000217 0x52000214 EP1 DMA Total Tx Counter

1-36

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

Page 37

2003.10.15

S3C2440X PRODUCT OVERVIEW

Table 1-4. S3C2440X Special Registers (Sheet 11 of 14)

Register Name Address

(B. Endian)

Address

(L. Endian)

Acc.

Unit

Read/W

rite

Function

USB Device (Continued)

EP2_DMA_CON 0x5200021B 0x52000218 B R/W EP2 DMA Interface Control

EP2_DMA_UNIT 0x5200021F 0x5200021C EP2 DMA Tx Unit Counter

EP2_DMA_FIFO 0x52000223 0x52000220 EP2 DMA Tx FIFO Counter

EP2_DMA_TTC_L 0x52000227 0x52000224 EP2 DMA Total Tx Counter

EP2_DMA_TTC_M 0x5200022B 0x52000228 EP2 DMA Total Tx Counter

EP2_DMA_TTC_H 0x5200022F 0x5200022C EP2 DMA Total Tx Counter

EP3_DMA_CON 0x52000243 0x52000240 EP3 DMA Interface Control

EP3_DMA_UNIT 0x52000247 0x52000244 EP3 DMA Tx Unit Counter

EP3_DMA_FIFO 0x5200024B 0x52000248 EP3 DMA Tx FIFO Counter

EP3_DMA_TTC_L 0x5200024F 0x5200024C EP3 DMA Total Tx Counter

EP3_DMA_TTC_M 0x52000253 0x52000250 EP3 DMA Total Tx Counter

EP3_DMA_TTC_H 0x52000257 0x52000254 EP3 DMA Total Tx Counter

EP4_DMA_CON 0x5200025B 0x52000258 EP4 DMA Interface Control

EP4_DMA_UNIT 0x5200025F 0x5200025C EP4 DMA Tx Unit Counter

EP4_DMA_FIFO 0x52000263 0x52000260 EP4 DMA Tx FIFO Counter

EP4_DMA_TTC_L 0x52000267 0x52000264 EP4 DMA Total Tx Counter

EP4_DMA_TTC_M 0x5200026B 0x52000268 EP4 DMA Total Tx Counter

EP4_DMA_TTC_H 0x5200026F 0x5200026C EP4 DMA Total Tx Counter

Watchdog Timer

WTCON 0x53000000

←

W R/W Watchdog Timer Mode

WTDAT 0x53000004 Watchdog Timer Data

WTCNT 0x53000008 Watchdog Timer Count

IIC

IICCON 0x54000000

←

W R/W IIC Control

IICSTAT 0x54000004 IIC Status

IICADD 0x54000008 IIC Address

IICDS 0x5400000C IIC Data Shift

IICLC 0x54000010 IIC multi-master line control

IIS

IISCON 0x55000000,02 0x55000000 HW,W R/W IIS Control

IISMOD 0x55000004,06 0x55000004 IIS Mode

IISPSR 0x55000008,0A 0x55000008 IIS Prescaler

IISFCON 0x5500000C,0E 0x5500000C IIS FIFO Control

IISFIFO 0x55000012 0x55000010 HW IIS FIFO Entry

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

1-37

Page 38

2003.10.15

PRODUCT OVERVIEW S3C2440X

Table 1-4. S3C2440X Special Registers (Sheet 12 of 14)

Register

Name

Address

(B. Endian)

Address

(L.

Acc.

Unit

Read/

Write

Function

Endian)

I/O port

GPACON 0x56000000

←

W R/W Port A Control

GPADAT 0x56000004 Port A Data

GPBCON 0x56000010 Port B Control

GPBDAT 0x56000014 Port B Data

GPBUP 0x56000018 Pull-up Control B

GPCCON 0x56000020 Port C Control

GPCDAT 0x56000024 Port C Data

GPCUP 0x56000028 Pull-up Control C

GPDCON 0x56000030 Port D Control

GPDDA1T 0x56000034 Port D Data

GPDUP 0x56000038 Pull-up Control D

GPECON 0x56000040 Port E Control

GPEDAT 0x56000044 Port E Data

GPEUP 0x56000048 Pull-up Control E

GPFCON 0x56000050 Port F Control

GPFDAT 0x56000054 Port F Data

GPFUP 0x56000058 Pull-up Control F

GPGCON 0x56000060 Port G Control

GPGDAT 0x56000064 Port G Data

GPGUP 0x56000068 Pull-up Control G

GPHCON 0x56000070 Port H Control

GPHDAT 0x56000074 Port H Data

GPHUP 0x56000078 Pull-up Control H

GPJCON 0x560000D0 Port J Control

GPJDAT 0x560000D4 Port J Data

GPJUP 0x560000D8 Pull-up Control J

MISCCR 0x56000080 Miscellaneous Control

DCLKCON 0x56000084 DCLK0/1 Control

EXTINT0 0x56000088 External Interrupt Control Register 0

EXTINT1 0x5600008C External Interrupt Control Register 1

EXTINT2 0x56000090 External Interrupt Control Register 2

1-38

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

Page 39

2003.10.15

S3C2440X PRODUCT OVERVIEW

Table 1-4. S3C2440X Special Registers (Sheet 13 of 14)

Register

Name

Address

(B. Endian)

Address

(L. Endian)

Acc.

Unit

Read/

Write

Function

I/O port (Continued)

EINTFLT0 0x56000094

←

WR/WReserved

EINTFLT1 0x56000098 Reserved

EINTFLT2 0x5600009C External Interrupt Filter Control Register 2

EINTFLT3 0x560000A0 External Interrupt Filter Control Register 3

EINTMASK 0x560000A4 External Interrupt Mask

EINTPEND 0x560000A8 External Interrupt Pending

GSTATUS0 0x560000AC

R

External Pin Status

GSTATUS1 0x560000B0 R/W Chip ID

GSTATUS2 0x560000B4 Reset Status

GSTATUS3 0x560000B8 Inform Register

GSTATUS4 0x560000BC Inform Register

MSLCON 0x560000CC Memory Sleep Control Register

RTC

RTCCON 0x57000043 0x57000040 B R/W RTC Control

TICNT 0x57000047 0x57000044 Tick time count

RTCALM 0x57000053 0x57000050 RTC Alarm Control

ALMSEC 0x57000057 0x57000054 Alarm Second

ALMMIN 0x5700005B 0x57000058 Alarm Minute

ALMHOUR 0x5700005F 0x5700005C Alarm Hour

ALMDATE 0x57000063 0x57000060 Alarm Day

ALMMON 0x57000067 0x57000064 Alarm Month

ALMYEAR 0x5700006B 0x57000068 Alarm Year

RTCRST 0x5700006F 0x5700006C RTC Round Reset

BCDSEC 0x57000073 0x57000070 BCD Second

BCDMIN 0x57000077 0x57000074 BCD Minute

BCDHOUR 0x5700007B 0x57000078 BCD Hour

BCDDATE 0x5700007F 0x5700007C BCD Day

BCDDAY 0x57000083 0x57000080 BCD Date

BCDMON 0x57000087 0x57000084 BCD Month

BCDYEAR 0x5700008B 0x57000088 BCD Year

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

1-39

Page 40

2003.10.15

PRODUCT OVERVIEW S3C2440X

Table 1-4. S3C2440X Special Registers (Sheet 14 of 14)

Register

Name

Address

(B. Endian)

Address

(L. Endian)

Acc. Unit Read/

Write

Function

A/D converter

ADCCON 0x58000000

←

W R/W ADC Control

ADCTSC 0x58000004 ADC Touch Screen Control

ADCDLY 0x58000008 ADC Start or Interval Delay

ADCDAT0 0x5800000C R ADC Conversion Data

ADCDAT1 0x58000010 ADC Conversion Data

ADCUPDN 0x58000014 R/W Stylus Up or Down Interrpt status

SPI

SPCON0,1 0x59000000,20

←

W R/W SPI Control

SPSTA0,1 0x59000004,24 R SPI Status

SPPIN0,1 0x59000008,28 R/W SPI Pin Control

SPPRE0,1 0x5900000C,2C SPI Baud Rate Prescaler

SPTDAT0,1 0x59000010,30 SPI Tx Data

SPRDAT0,1 0x59000014,34 R SPI Rx Data

SD interface

SDICON 0x5A000000

←

W R/W SDI Control

SDIPRE 0x5A000004 SDI Baud Rate Prescaler

SDICARG 0x5A000008 SDI Command Argument

SDICCON 0x5A00000C SDI Command Control

SDICSTA 0x5A000010 R/(C) SDI Command Status

SDIRSP0 0x5A000014 R SDI Response

SDIRSP1 0x5A000018 SDI Response

SDIRSP2 0x5A00001C SDI Response

SDIRSP3 0x5A000020 SDI Response

SDIDTIMER 0x5A000024 R/W SDI Data / Busy Timer

SDIBSIZE 0x5A000028 SDI Block Size

SDIDCON 0x5A00002C SDI Data control

SDIDCNT 0x5A000030 R SDI Data Remain Counter

SDIDSTA 0x5A000034 R/(C) SDI Data Status

SDIFSTA 0x5A000038 R SDI FIFO Status

SDIDAT 0x5A00003F 0x5A00003C B R/W SDI Data

SDIIMSK 0x5A000040

←

W SDI Interrupt Mask

1-40

Preliminary product information describes products that are in development,

for which full characterization data and associated errata are not yet available

Specifications and information herein are subject to change without notice.

Page 41

2003.09.25

PRODUCT OVERVIEW S3C2440X